##

# AMD64 Technology

# AMD64 Architecture Programmer's Manual Volume 4: 128-Bit and 256-Bit **Media Instructions**

Publication No. Revision **Date** 26568 3.21 December 2017

#### © 2013 – 2017 Advanced Micro Devices Inc. All rights reserved.

The information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### **Trademarks**

AMD, the AMD Arrow logo, and combinations thereof, and 3DNow! are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

## **Contents**

| Revis | ion Hist                         | oryxxiii                                                                                                                                                                            |

|-------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prefa | About Audien<br>Organi<br>Conven | Xxvii           This Book         xxvii           ice         xxvii           zation         xxvii           ntions and Definitions         xxviii           1 Documents         xl |

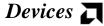

| 1     | <b>Introd</b> 1.1                | Iuction            Syntax and Notation                                                                                                                                              |

|       | 1.1                              | Extended Instruction Encoding                                                                                                                                                       |

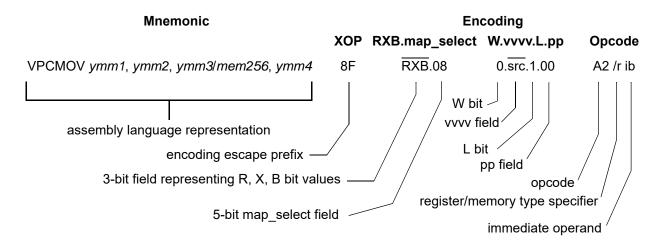

|       | 1.3                              | VSIB Addressing                                                                                                                                                                     |

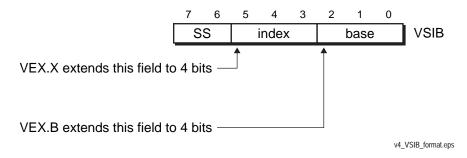

|       | 1.4<br>1.5                       | Enabling SSE Instruction Execution10String Compare Instructions101.5.1 Source Data Format13                                                                                         |

|       |                                  | 1.5.2 Comparison Type141.5.3 Comparison Summary Bit Vector161.5.4 Intermediate Result Post-processing181.5.5 Output Option Selection181.5.6 Affect on Flags19                       |

| 2     | Instru                           | ction Reference                                                                                                                                                                     |

|       |                                  | ADDPD VADDPD                                                                                                                                                                        |

|       |                                  | VADDPS                                                                                                                                                                              |

|       |                                  | VADDSD       27         ADDSS       29                                                                                                                                              |

|       |                                  | ADDSUBPD VADDSUBPD                                                                                                                                                                  |

|       |                                  | ADDSUBPS VADDSUBPS                                                                                                                                                                  |

|       |                                  | AESDEC VAESDEC                                                                                                                                                                      |

|       |                                  | VAESDECLAST                                                                                                                                                                         |

| VAESENC               | 39  |

|-----------------------|-----|

| AESENCLAST            |     |

| VAESENCLAST           | 41  |

| AESIMC                |     |

| VAESIMC               | 43  |

| AESKEYGENASSIST       |     |

| VAESKEYGENASSIST      | 45  |

| ANDNPD                |     |

| VANDNPD               | 47  |

| ANDNPS                |     |

| VANDNPS               | 49  |

| ANDPD                 |     |

| VANDPD.               | 51  |

| ANDPS VANDPS          | 50  |

|                       | 53  |

| BLENDPD VBLENDPD      | 5.5 |

| BLENDPS BLENDPS       | 33  |

| VBLENDPS              | 57  |

| BLENDVPD              | 3 / |

| VBLENDVPD             | 50  |

| BLENDVPS              | 57  |

| VBLENDVPS             | 61  |

| CMPPD                 | 01  |

| VCMPPD                | 63  |

| CMPPS                 |     |

| VCMPPS                | 67  |

| CMPSD                 |     |

| VCMPSD                | 71  |

| CMPSS                 |     |

| VCMPSS                | 75  |

| COMISD                |     |

| VCOMISD               | 79  |

| COMISS                |     |

| VCOMISS               | 82  |

| CVTDQ2PD              |     |

| VCVTDQ2PD             | 84  |

| CVTDQ2PS              |     |

| VCVTDQ2PS             | 86  |

| CVTPD2DQ              | 0.0 |

| VCVTPD2DQ             | 88  |

| CVTPD2PS              | 0.0 |

| VCVTPD2PS             | 90  |

| CVTPS2DQ<br>VCVTPS2DO | 02  |

| CVTPS2PD              | 92  |

| VCVTPS2PD             | 0.4 |

| vCv1F32FD             | 94  |

## AMD64 Technology

| VLDDQU                | 156  |

|-----------------------|------|

| LDMXCSR               |      |

| VLDMXCSR              | 158  |

| MASKMOVDQU            |      |

| VMASKMOVDQU           | 160  |

| MAXPD                 |      |

| VMAXPD                | 162  |

| MAXPS                 |      |

| VMAXPS                | 165  |

| MAXSD                 |      |

| VMAXSD                | 168  |

| MAXSS                 |      |

| VMAXSS                | 170  |

| MINPD                 | 1.50 |

| VMINPD                | 172  |

| MINPS                 | 175  |

| VMINPS                | 1/3  |

| MINSD VMINSD          | 170  |

| MINSS                 | 1/0  |

| VMINSS                | 180  |

| MOVAPD                | 100  |

| VMOVAPD               | 182  |

| MOVAPS                | 102  |

| VMOVAPS               | 184  |

| MOVD                  |      |

| VMOVD                 | 186  |

| MOVDDUP               |      |

| VMOVDDUP              | 188  |

| MOVDQA                |      |

| VMOVDQA               | 190  |

| MOVDQU                |      |

| VMOVDQU               | 192  |

| MOVHLPS               |      |

| VMOVHLPS              | 194  |

| MOVHPD                |      |

| VMOVHPD               | 196  |

| MOVHPS                |      |

| VMOVHPS               | 198  |

| MOVLHPS               |      |

| VMOVLHPS              | 200  |

| MOVLPD                | 202  |

| VMOVLPD               | 202  |

| MOVLPS<br>VMOVI PS    | 20.4 |

| VMOVLPS               | 204  |

| MOVMSKPD<br>VMOVMSKPD | 204  |

| VMOVMSKPD             | ∠∪0  |

## AMD64 Technology

| MOVMSKPS   |

|------------|

| VMOVMSKPS  |

| MOVNTDQ    |

| VMOVNTDQ   |

| MOVNTDQA   |

| VMOVNTDQA  |

| MOVNTPD    |

| VMOVNTPD   |

| MOVNTPS    |

| VMOVNTPS   |

| MOVNTSD    |

| MOVNTSS    |

| MOVQ       |

| VMOVQ      |

| MOVSD      |

| VMOVSD     |

| MOVSHDUP   |

| VMOVSHDUP  |

| MOVSLDUP   |

| VMOVSLDUP  |

| MOVSS      |

| VMOVSS     |

| MOVUPD     |

| VMOVUPD232 |

| MOVUPS     |

| VMOVUPS    |

| MPSADBW    |

| VMPSADBW   |

| MULPD      |

| VMULPD     |

| MULPS      |

| VMULPS243  |

| MULSD      |

| VMULSD     |

| MULSS      |

| VMULSS247  |

| ORPD       |

| VORPD      |

| ORPS       |

| VORPS      |

| PABSB      |

| VPABSB     |

| PABSD      |

| VPABSD     |

| PABSW      |

| VPABSW     |

| PACKSSDW   |

| VPACKSSDW  | . 259   |

|------------|---------|

| PACKSSWB   |         |

| VPACKSSWB  | . 261   |

| PACKUSDW   |         |

| VPACKUSDW  | . 263   |

| PACKUSWB   |         |

| VPACKUSWB  | . 265   |

| PADDB      |         |

| VPADDB     | 267     |

| PADDD      |         |

| VPADDD     | 269     |

| PADDQ      |         |

| VPADDQ     | . 271   |

| PADDSB     | 0.70    |

| VPADDSB    | 273     |

| PADDSW     | 27.5    |

| VPADDSW    | 2/3     |

| PADDUSB    | 277     |

| VPADDUSB   | 211     |

| VPADDUSW   | 270     |

| PADDW      | 215     |

| VPADDW     | 281     |

| PALIGNR    | . 201   |

| VPALIGNR   | 283     |

| PAND       | . 202   |

| VPAND      | 285     |

| PANDN      | . 200   |

| VPANDN     | . 287   |

| PAVGB      | . = 0 , |

| VPAVGB     | 289     |

| PAVGW      |         |

| VPAVGW     | . 291   |

| PBLENDVB   |         |

| VPBLENDVB  | . 293   |

| PBLENDW    |         |

| VPBLENDW   | . 295   |

| PCLMULQDQ  |         |

| VPCLMULQDQ | . 297   |

| PCMPEQB    |         |

| VPCMPEQB   | 299     |

| PCMPEQD    |         |

| VPCMPEQD   | 301     |

| PCMPEQQ    |         |

| VPCMPEQQ   | . 303   |

| PCMPEQW    | 200     |

| VPCMPEQW   | . 305   |

## AMD64 Technology

| PCMPESTRI      |             |

|----------------|-------------|

| VPCMPESTRI     | 307         |

| PCMPESTRM      |             |

| VPCMPESTRM     | 310         |

| PCMPGTB        |             |

| VPCMPGTB       | 313         |

| PCMPGTD        |             |

| VPCMPGTD       | 315         |

| PCMPGTQ        |             |

| VPCMPGTQ       | 317         |

| PCMPGTW        |             |

| VPCMPGTW       | 319         |

| PCMPISTRI      |             |

| VPCMPISTRI     | 321         |

| PCMPISTRM      |             |

| VPCMPISTRM     | 324         |

| PEXTRB         | 225         |

| VPEXTRB.       | 327         |

| PEXTRD         | 220         |

| VPEXTRD        | 329         |

| PEXTRQ VPEXTRQ | 221         |

|                | 331         |

| PEXTRW VPEXTRW | 222         |

| PHADDD         | 333         |

| VPHADDD        | 335         |

| PHADDSW        | 555         |

| VPHADDSW       | 337         |

| PHADDW         | 551         |

| VPHADDW        | 340         |

| PHMINPOSUW     | <i>-</i> 10 |

| VPHMINPOSUW    | 343         |

| PHSUBD         |             |

| VPHSUBD.       | 345         |

| PHSUBSW        |             |

| VPHSUBSW       | 347         |

| PHSUBW         |             |

| VPHSUBW        | 350         |

| PINSRB         |             |

| VPINSRB        | 353         |

| PINSRD         |             |

| VPINSRD        | 356         |

| PINSRQ         |             |

| VPINSRQ        | 358         |

| PINSRW         |             |

| VPINSRW        | 360         |

| PMADDUBSW      |             |

| VPMADDUBSW                              | 362   |

|-----------------------------------------|-------|

| PMADDWD                                 |       |

| VPMADDWD                                | 365   |

| PMAXSB                                  |       |

| VPMAXSB                                 | 367   |

| PMAXSD                                  |       |

| VPMAXSD                                 | 369   |

| PMAXSW                                  |       |

| VPMAXSW                                 | 371   |

| PMAXUB                                  |       |

| VPMAXUB                                 | 373   |

| PMAXUD                                  |       |

| VPMAXUD                                 | 375   |

| PMAXUW                                  |       |

| VPMAXUW                                 | 377   |

| PMINSB                                  |       |

| VPMINSB                                 | 379   |

| PMINSD                                  |       |

| VPMINSD                                 | 381   |

| PMINSW                                  |       |

| VPMINSW                                 | 383   |

| PMINUB                                  |       |

| VPMINUB                                 | 385   |

| PMINUD                                  |       |

| VPMINUD.                                | 387   |

| PMINUW                                  | • • • |

| VPMINUW                                 | 389   |

| PMOVMSKB                                | 201   |

| VPMOVMSKB                               | 391   |

| PMOVSXBD                                | 202   |

| VPMOVSXBD                               | 393   |

| PMOVSXBQ                                | 205   |

| VPMOVSXBQ                               | 393   |

| PMOVSXBW<br>VPMOVSVDW                   | 397   |

| VPMOVSXBW                               | 39/   |

| PMOVSXDQ<br>VPMOVSXDQ                   | 200   |

| PMOVSXWD                                | 399   |

| VPMOVSXWD                               | 401   |

| PMOVSXWQ                                | 401   |

| VPMOVSXWQ                               | 403   |

| PMOVZXBD                                | +03   |

| VPMOVZXBD                               | 405   |

| PMOVZXBO                                | +02   |

| VPMOVZXBQ                               | 407   |

| PMOVZXBW                                | 10/   |

| VPMOVZXBW                               | 400   |

| 1 1 1 1 1 2 1 2 1 2 1 1 1 1 1 1 1 1 1 1 | 107   |

## AMD64 Technology

| PMOVZXDQ             |      |

|----------------------|------|

| VPMOVZXDQ            | 11   |

| PMOVZXWD             |      |

| VPMOVZXWD            | 13   |

| PMOVZXWQ             |      |

| VPMOVZXWQ4           | 15   |

| PMULDQ               |      |

| VPMULDQ              | 17   |

| PMULHRSW             |      |

| VPMULHRSW4           | 19   |

| PMULHUW              |      |

| VPMULHUW             | .21  |

| PMULHW               |      |

| VPMULHW4             | 2:   |

| PMULLD               |      |

| VPMULLD              | -2:  |

| PMULLW VPMULLW       | 2    |

|                      | ٠۷,  |

| PMULUDQ<br>VPMULUDQ4 | 20   |

| POR                  | :۷   |

| VPOR4                | 131  |

| PSADBW               |      |

| VPSADBW              | 3:   |

| PSHUFB               | ٥.   |

| VPSHUFB4             | 35   |

| PSHUFD               |      |

| VPSHUFD4             | 37   |

| PSHUFHW              |      |

| VPSHUFHW4            | 4(   |

| PSHUFLW              |      |

| VPSHUFLW             | 43   |

| PSIGNB               |      |

| VPSIGNB4             | 46   |

| PSIGND               |      |

| VPSIGND4             | 48   |

| PSIGNW               |      |

| VPSIGNW4             | -5(  |

| PSLLD                |      |

| VPSLLD4              | 52   |

| PSLLDQ               | - 4  |

| VPSLLDQ4             | 33   |

| PSLLQ VPSLLQ4        | 5    |

| PSLLW                | ر د. |

| VPSLLW               | .60  |

| PSRAD                | U    |

| I DIG ID             |      |

| VPSRAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSRAW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VPSRAW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSRLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VPSRLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSRLDQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VPSRLDQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PSRLQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VPSRLQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSRLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VPSRLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSUBB AND ADDRESS OF THE PSUBB |

| VPSUBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSUBD 48.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PSUBQ VPSUBQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PSUBSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VPSUBSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PSUBSW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VPSUBSW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PSUBUSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VPSUBUSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PSUBUSW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VPSUBUSW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PSUBW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VPSUBW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PTEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VPTEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PUNPCKHBW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VPUNPCKHBW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |