# iCEcube2 User Guide

August 2017

### Copyright

Copyright © 2017 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synplify Pro are trademarks of Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING OF ACCURACY, COMPLETENESS. WARRANTIES MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL. INCLUDING. WITHOUT LIMITATION. DAMAGES FOR LOSS OF PROFITS. BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

#### **Contact Information**

Lattice Semiconductor Corporation 5555 N.E. Moore Court Hillsboro, Oregon 97124-6421 United States of America Tel: +1 503 268 8000

Fax: +1 503 268 8347 http://www.latticesemi.com.

# TABLE OF CONTENTS

| Preface                                                 | 7          |

|---------------------------------------------------------|------------|

| About this Document                                     |            |

| Software Version                                        | 7          |

| Platform Requirements                                   | 7          |

| Programming Hardware                                    | 7          |

| Programming Software                                    | 8          |

| Chapter 1 Overview                                      |            |

| iCEcube2 Tool Suite                                     |            |

| Design Flow                                             | 10         |

| Chapter 2 Quick Start Guide                             | 11         |

| Creating a Project                                      |            |

| Synthesizing the Design                                 |            |

| Programming the Device                                  |            |

| Addendum:                                               |            |

| Importing Physical Constraints from iCEcube to iCEcube2 | 29         |

| Chapter 3 iCEcube2 Project Setup and Navigation         | 34         |

| Introduction                                            | 34         |

| Project Manager GUI                                     |            |

| Adding/Deleting Design and Constraint Files             |            |

| Selecting Synthesis Tool and Setting synthesis Options  |            |

| Selecting the Target Device and Operating Conditions    |            |

| Output Window                                           |            |

| Simulation Wizard                                       |            |

| PLL Module Generator                                    |            |

| PLL Dynamic Reconfiguration                             |            |

| SPI/I2C Module Generator                                | 5∠         |

| Chapter 4 Lattice Synthesis Engine                      | <u> 60</u> |

| Changing the LSE Tool Options                           |            |

| BRAM Utilization                                        |            |

| Carry Chain Length                                      |            |

| Command Line Options                                    |            |

| Fix Gated Clocks                                        |            |

| FSM Encoding Style                                      |            |

| Intermediate File Dump                                  |            |

| Max Fanout Limit                                        |            |

| Memory Initial Value File Search Path                   |            |

| Number of Critical Paths                                |            |

| Optimization Goal                                       |            |

| Propagate Constants                                     |            |

| RAM Style                                               |            |

| Remove Duplicate Registers                              |            |

| Resolve Mixed Drivers  Resource Sharing                 |            |

| ROM Style                                               |            |

| RW Check on RAM                                         |            |

| Target Frequency                                        |            |

| Top-Level Unit                                          |            |

| Use Carry Chain                                         |            |

| ,                                                       |            |

| Use IO Insertion                                 | 63    |

|--------------------------------------------------|-------|

| Use IO Registers                                 | 63    |

| Optimizing LSE for Area and Speed                | 63    |

| FSM Encoding Style                               | 64    |

| Max Fanout Limit                                 | 64    |

| Optimization Goal                                | 64    |

| Remove Duplicate Registers                       | 64    |

| Resource Sharing                                 |       |

| Target Frequency                                 | 65    |

| LSE Options versus Synplify Pro                  | 65    |

| Coding Tips for LSE                              |       |

| LSE Differences with Synplify Pro                |       |

| About Inferring Memory                           |       |

| Inferring RAM                                    |       |

| Inferring RAM with Synchronous Read              |       |

| Inferring Pseudo Dual-Port RAM                   |       |

| Initializing Inferred RAM                        |       |

| Inferring ROM                                    |       |

| About Verilog Blocking Assignments               |       |

| Inferring DSP Multipliers                        |       |

| Verilog Examples                                 |       |

| VHDL Examples                                    |       |

| Inferring I/O                                    |       |

| Event Inside an Event                            |       |

| HDL Attributes and Directives                    |       |

| black_box_pad_pin                                |       |

| syn_black_box                                    |       |

| syn_encoding                                     |       |

| syn_hier                                         |       |

| syn_keep                                         |       |

| syn_maxfan                                       |       |

| syn_multstyle                                    |       |

| syn_noprune                                      |       |

| syn_pipelinesyn_pipeline                         |       |

| • • •                                            |       |

| syn_preserve                                     |       |

| syn_ramstyle                                     |       |

| syn_romstylesyn_use_carry_chain                  |       |

| · · · · · · · · · · · · · · · · · · ·            |       |

| syn_useioff                                      |       |

| Synthesis Macro                                  |       |

| translate_off/translate_on                       |       |

| Synopsys Design Constraints (SDC)                |       |

| create_clock                                     |       |

| set_false_path                                   |       |

| set_input_delay                                  |       |

| set_max_delay                                    |       |

| set_multicycle_path                              |       |

| set_output_delay                                 | 99    |

| Chapter 5 iCEcube2 Physical Implementation Tools | 100   |

| Overview                                         | . 100 |

| Tools for Physical Implementation                |       |

| Placing and Routing the Design                   | . 101 |

| Floor Planner                                    | . 102 |

| Package View                                                             |     |

|--------------------------------------------------------------------------|-----|

| Pin Constraints Editor                                                   |     |

| Power Estimator                                                          |     |

| Generating a Bitmap                                                      |     |

| Programming the Device                                                   |     |

| Diamond Programmer                                                       |     |

| Memory Initializer                                                       |     |

| Memory initialization file Format (.mem) :                               |     |

| Simulating the Routed Design                                             | 121 |

| Chapter 6 Timing Constraints and Static Timing Analysis                  | 122 |

| Overview                                                                 |     |

| Specifying Constraints Using the Timing Constraints Editor (TCE)         |     |

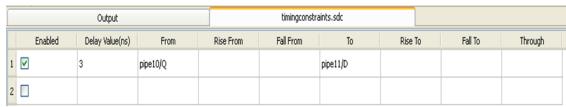

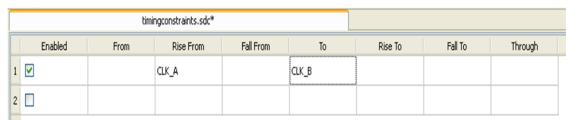

| SDC Constraints in TCE                                                   |     |

| Clock Constraints                                                        |     |

| Generated Clock Constraints                                              |     |

| Source Clock Latency Constraints                                         |     |

| Input Delay Constraints.                                                 |     |

| Output Delay Constraints                                                 |     |

| Max Delay ConstraintsFalse Path Exceptions                               |     |

| Multi Cycle Path Exceptions                                              |     |

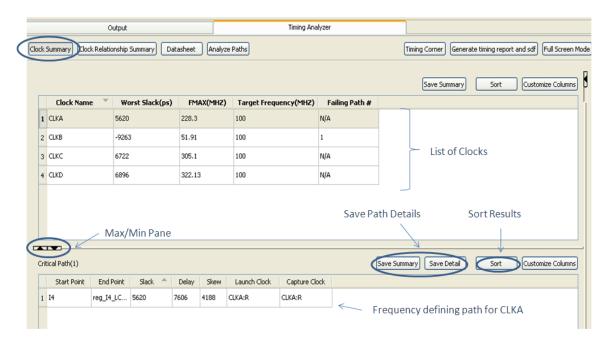

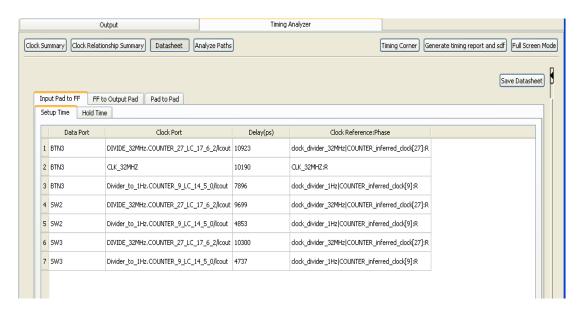

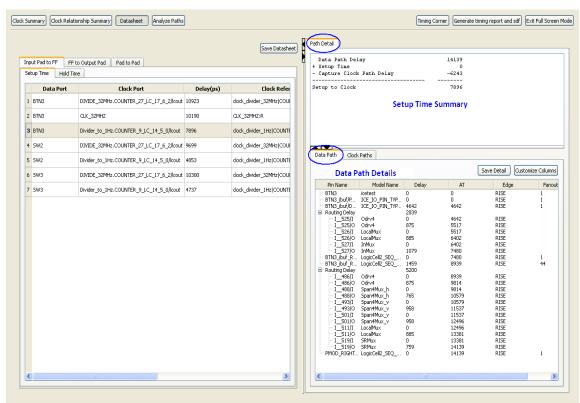

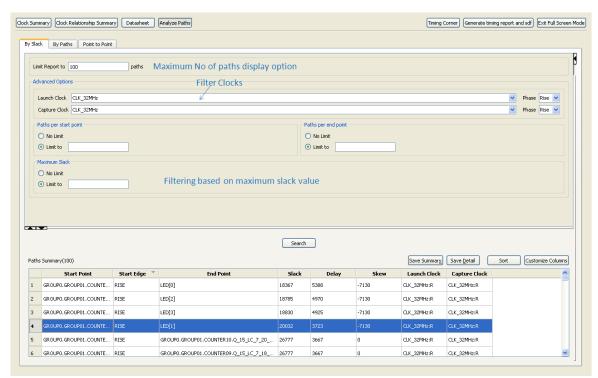

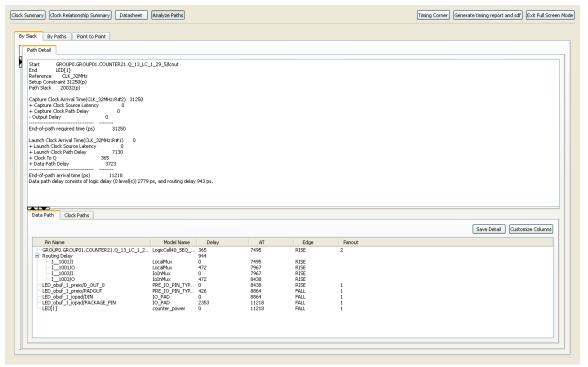

| Analyzing Reports Generated by the Static Timing Analyzer (STA)          |     |

| Clock Summary Pane                                                       |     |

| Clock Relationship Summary                                               |     |

| Data Sheet                                                               |     |

| Analyzing Constrained Paths                                              |     |

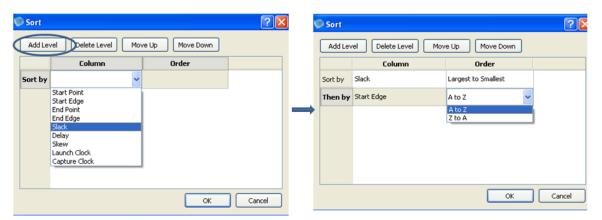

| By Slack                                                                 |     |

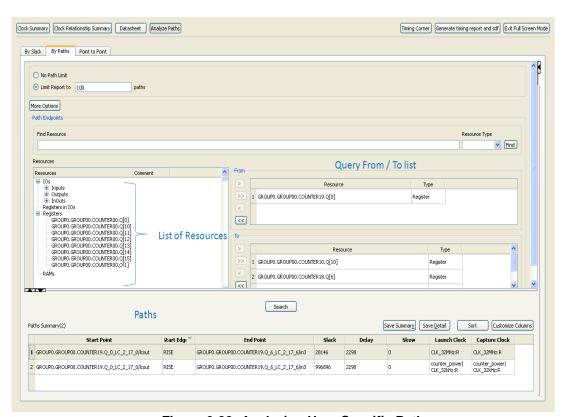

| By Paths                                                                 |     |

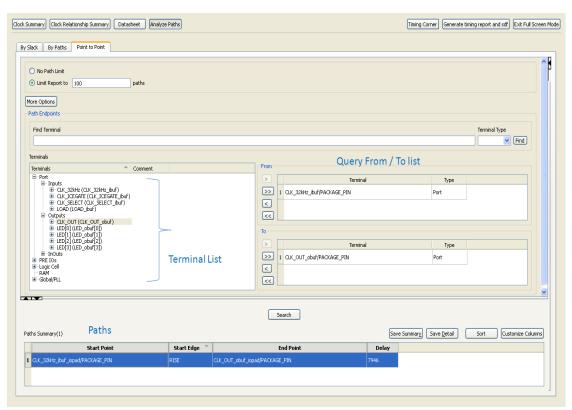

| Point to Point                                                           |     |

| Other Features                                                           | 140 |

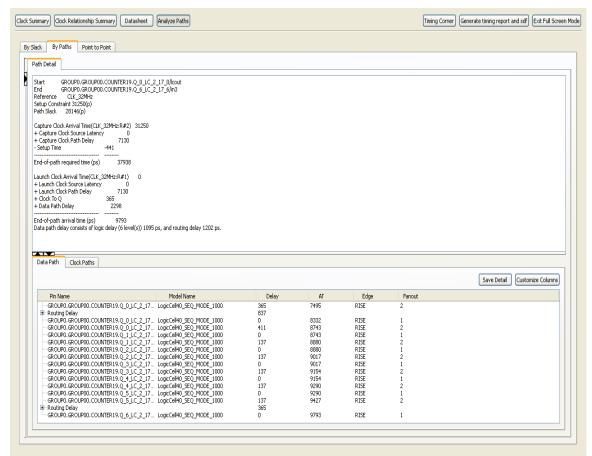

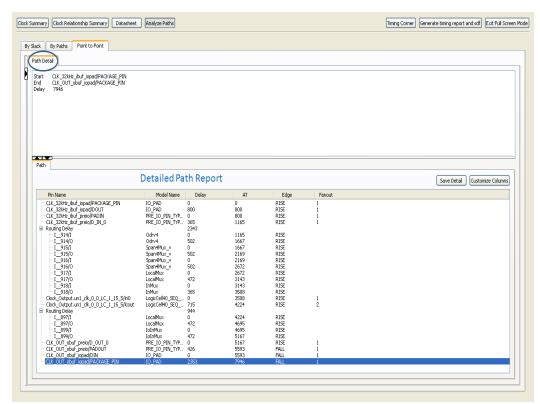

| Detailed Timing Report                                                   | 142 |

| Chapter 7 Physical Constraints in iCEcube2                               | 146 |

| Specifying Physical Constraints after Design Import and Before Placement |     |

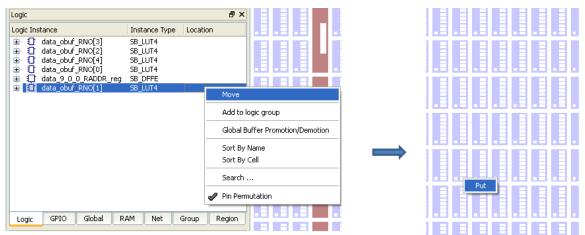

| Absolute Placement                                                       | 147 |

| Constraining Logic or RAMs                                               | 147 |

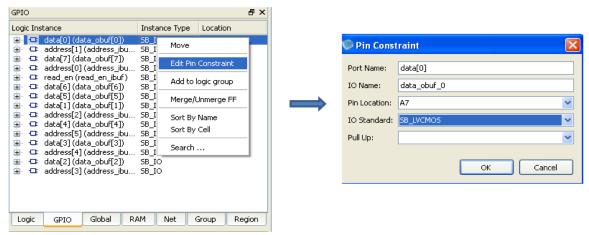

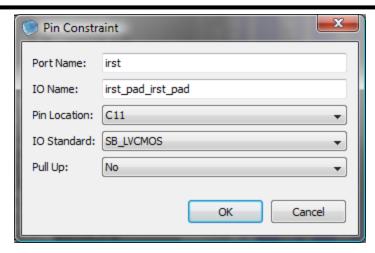

| Constraining IOs                                                         |     |

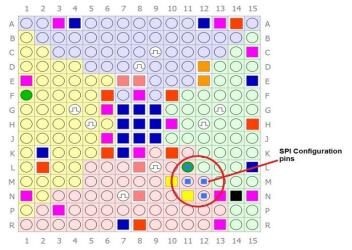

| Constraining SPI Configuration IOs                                       |     |

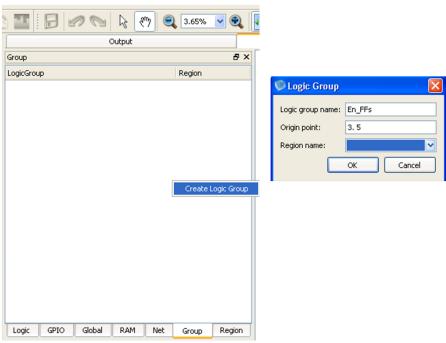

| Relative Placement                                                       |     |

| Region Constraints                                                       |     |

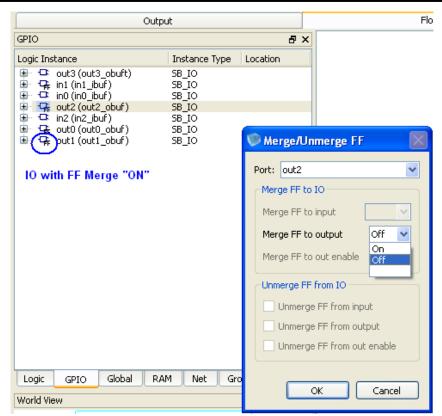

| IO/FF Merge                                                              |     |

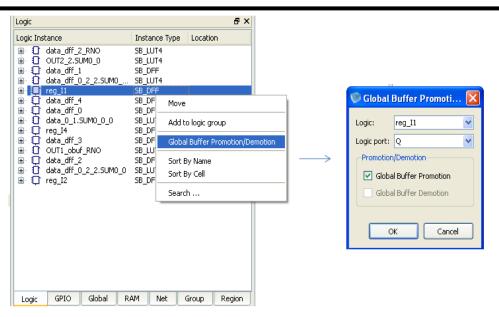

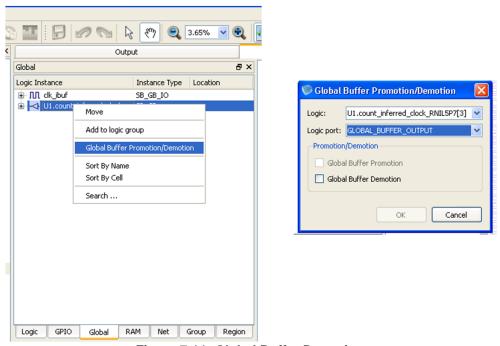

| Global Buffer Promotion/Demotion                                         | 155 |

| Modifying the Device Floor Plan after Placement                          | 15/ |

| Chapter 8 Generating/Integrating Fixed Placement IP Blo                  |     |

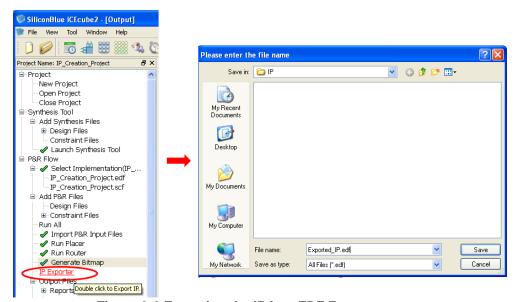

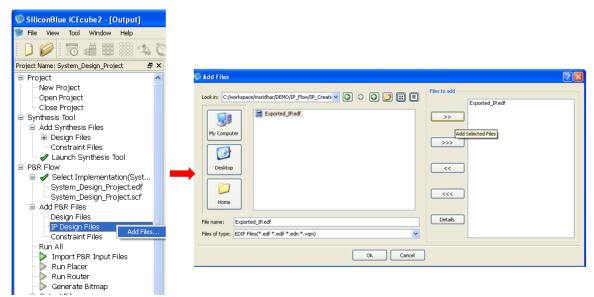

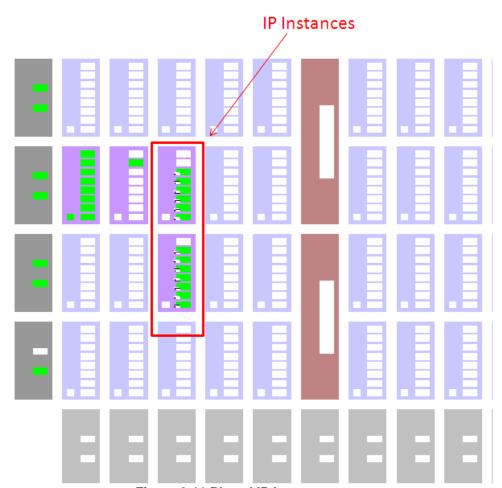

| IP Generation Flow                                                       |     |

| System Design Flow                                                       | 164 |

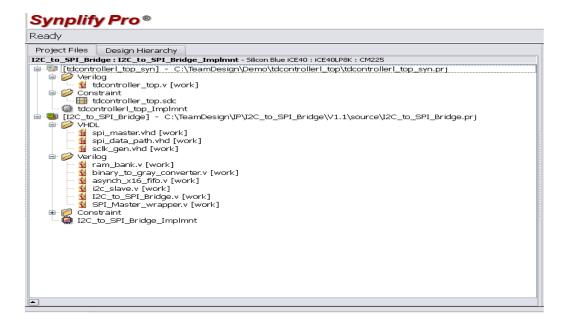

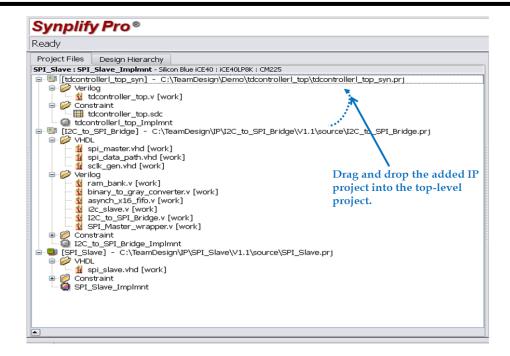

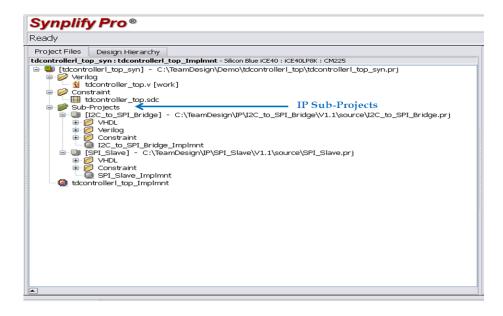

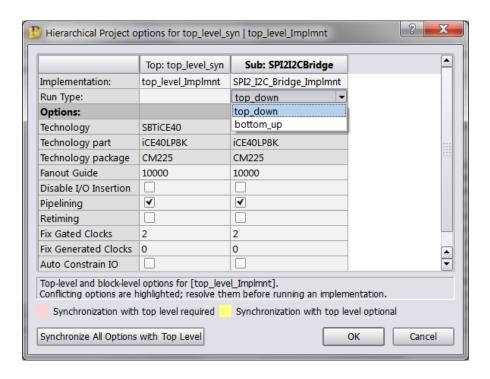

| Chapter 9 Hierarchical Project Flow                                      | 169 |

| Create Top Level Project                                                 | 169 |

| Create Sub-Projects for IP blocks                                        |     |

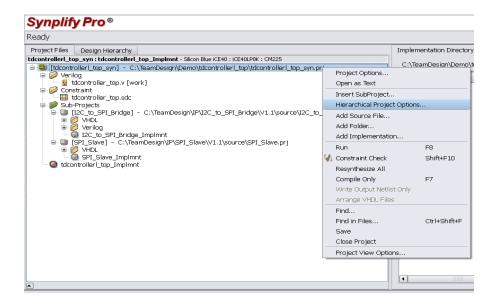

| Synthesize Top Level Project                                             | 175 |

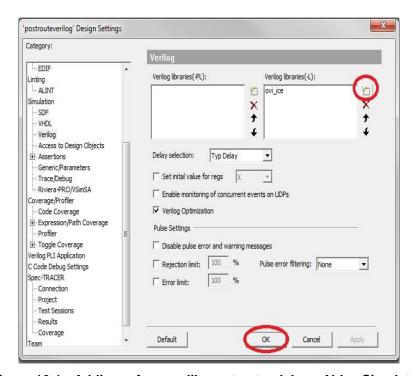

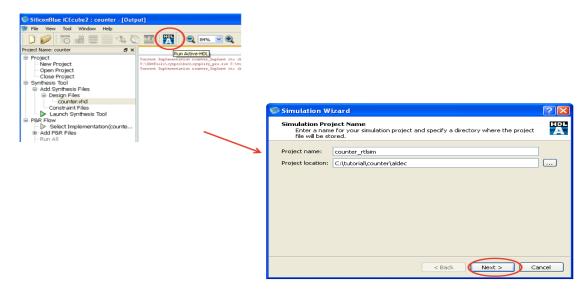

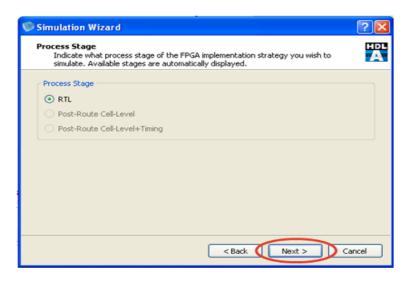

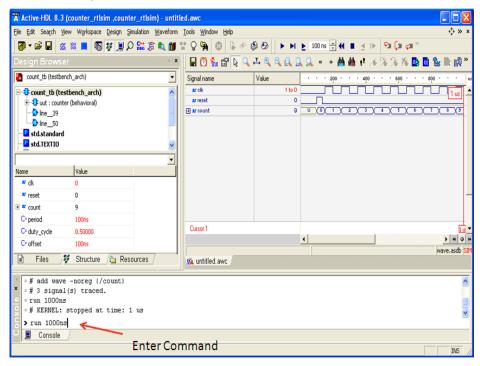

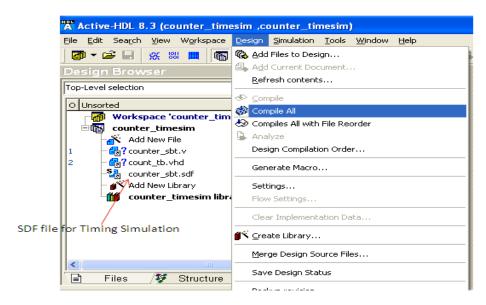

| Chapter 10 Simulating Design with ALDEC Active-HDL       | 178     |

|----------------------------------------------------------|---------|

| ALDEC Active-HDL                                         |         |

| Pre-Compiled iCE Simulation Libraries                    | 178     |

| VHDL                                                     |         |

| VERILOG                                                  | 179     |

| Design                                                   |         |

| Pre-Synthesis Simulation                                 |         |

| Post Place-n-Route Functional Simulation (Verilog/VHDL)  |         |

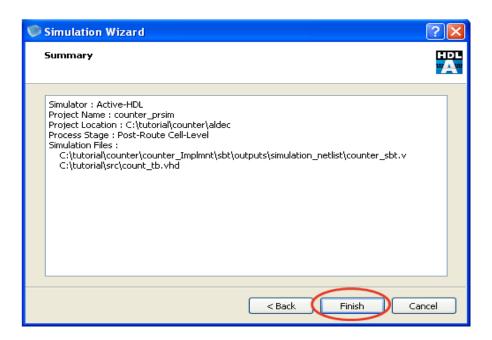

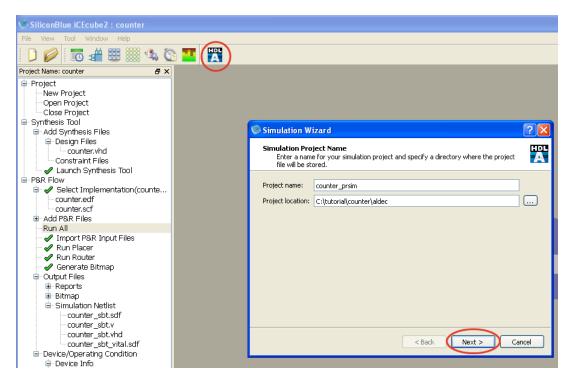

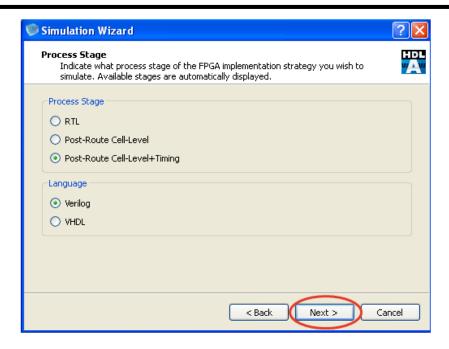

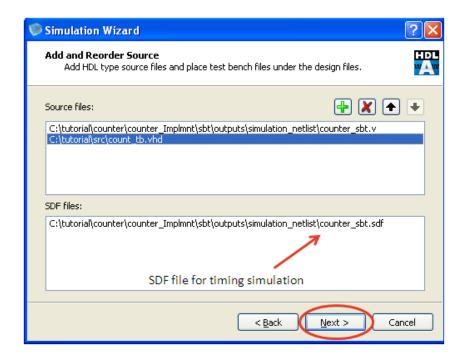

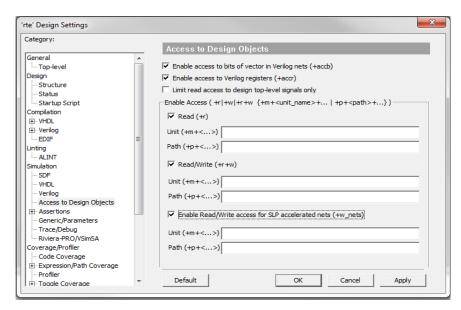

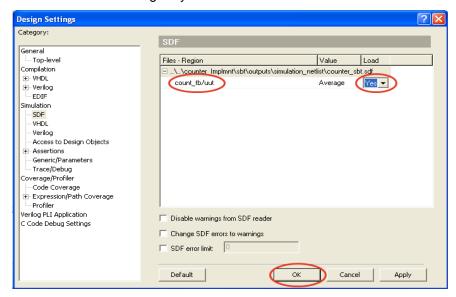

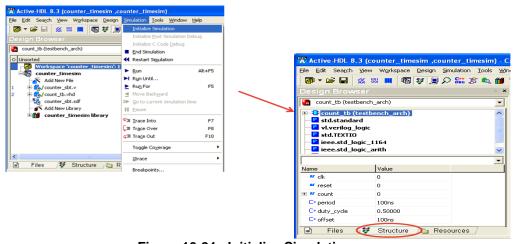

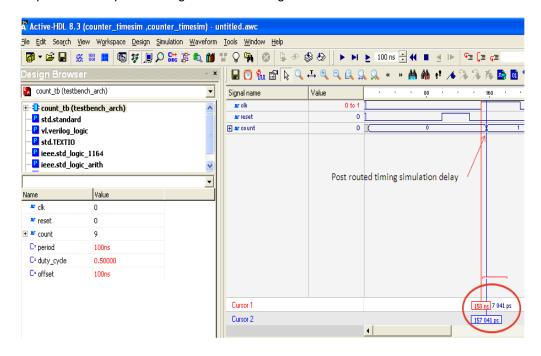

| Post Place-n-Route Timing Simulation (Verilog/VHDL)      | 190     |

| Chapter 11 iCEcube2 Command Line Interface               | 196     |

| Overview                                                 | 196     |

| Running LSE in batch mode                                | 196     |

| Running Synplify-pro in batch mode                       | 197     |

| Running iCEcube2 Backend tools in batch mode             |         |

| Backend tool Options                                     |         |

| Edif Parser                                              |         |

| Placer                                                   |         |

| Router                                                   |         |

| Bitmap                                                   |         |

| Command Line Execution                                   | 201     |

| Chapter 12 High Drive IO with configurable drive strengt | :hs 204 |

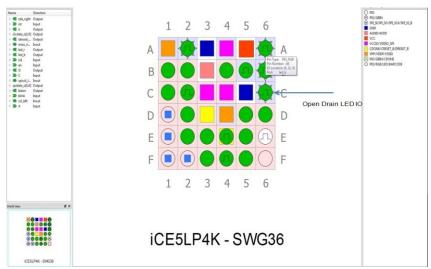

| Chapter 13 Open Drain LED IO                             | 206     |

| Appendix A: PCF Syntax                                   | 207     |

## **Preface**

#### **About this Document**

The *iCEcube2 User Guide* provides iCE FPGA designers with an overview of the software tools and the design process using iCEcube2. This document covers the iCEcube2 tools for Project Setup, Navigation, Synthesis and Physical Implementation on the iCE FGPA device.

For information on the Synopsys Synplify Pro software, please refer to the Synplify Pro documentation provided in the synpbase/doc directory in the iCEcube2 software installation (<icecube2 install dir>/synpbase/doc), and on the Lattice website.

For information on the Aldec Active-HDL design tool, please refer to the Active-HDL documentations available at <icecube2 install dir>/Aldec/Active-HDL/BOOKS.

#### **Software Version**

This User Guide documents the features of iCEcube2 Software Version 2017.08.

For more information about acquiring the iCEcube2 software, please visit the Lattice Semiconductor website: http://www.latticesemi.com.

#### **Platform Requirements**

The iCEcube2 software can be installed on a platform satisfying the following minimum requirements.

A Pentium 4 computer (500 MHz) with 256 MB of RAM, 256MB of Virtual Memory, and running one of the following Operating Systems :

- Windows 10 OS, 32-bit / 64-bit

- Windows 8/8.1 OS, 32-bit / 64-bit

- Windows 7 OS, 32-bit / 64-bit

- Windows XP Professional

- Red Hat Enterprise Linux WS v4, 5, and 6

#### **Programming Hardware**

Here are the following ways to program iCE FPGA devices:

- A third party programmer or a processor, using the programming files generated by the iCEcube2 Physical Implementation Tools. Consult the third party programmer user manual for instructions.

- The iCEblink and iCEman evaluation Board, which not only serves as a vehicle to

evaluate iCE FPGAs, but also includes an integrated device programmer. This

programmer can be used to program devices on the evaluation board, or it can be used

to program devices in a target system. Please visit Lattice Semiconductor website:

http://www.latticesemi.com for additional information on the Evaluation Boards.

- Digilent USB cables to program the external SPI Flash.

• The iCE Programming hardware: iCEcable, iCEprog (Programmer base module) and iCEsab (socket adaptor). Refer to lattice website: <a href="http://www.latticesemi.com">http://www.latticesemi.com</a> for more details on programming hardware.

# **Programming Software**

Standalone Lattice Diamond Programmer software is required to program iCE40 FPGA devices or SPI flash. Download and install the latest standalone programmer from <a href="http://www.latticesemi.com/ispvm">http://www.latticesemi.com/ispvm</a>.

For more information about Diamond Programmer, refer "Diamond Programmer" on page 116.

# Chapter 1 Overview

#### iCEcube2 Tool Suite

The iCEcube2 Tool Suite is comprised of several integrated components, running under either the Microsoft Windows or the Red Hat Linux environments. Please refer to <u>Platform</u> <u>Requirements</u> for additional information on supported operating systems.

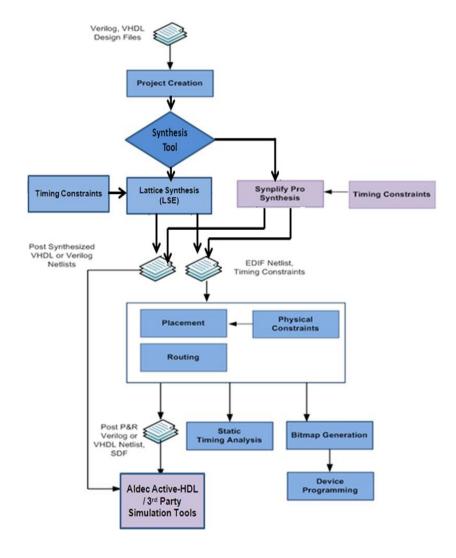

The Figure 1-1 below depicts the design flow using the iCEcube2 Tool Suite. The components in blue signify functionality supported by Lattice Semiconductor's proprietary Synthesis Engine (LSE) and iCEcube2 place and route software, and the components in purple indicate the functionality supported by Synopsys' Synplify Pro synthesis tools and the Aldec Active-HDL simulation tool. The iCEcube2 software, Synopsys Synplify Pro and the Aldec Active-HDL software constitutes the iCEcube2 Tool Suite.

Note: The Aldec Active-HDL tool is available only in Windows environments.

Figure 1-1: The iCEcube2 Design Flow

#### **Design Flow**

The following steps provide an overview of the design flow using the iCEcube2 Tool Suite.

- Create a new project in the iCEcube2 Project Navigator and specify a target device and its operating conditions. Add your HDL (Verilog or VHDL) design files and your Constraint files to the project.

- 2. iCEcube2 software supports Synplify-Pro Synthesis tool and Lattice Synthesis (LSE) tool. Synplify-pro is the default synthesis tool in iCEcube2. Synthesis your design using the selected synthesis tool.

- Perform Placement and Routing using the iCEcube2 place and route tools. iCEcube2 also supports physical implementation tools such as floor planning, allowing users to manually place logic cells and IOs.

- 4. Perform timing simulation of your design using the Aldec Active-HDL simulation tool or any industry-standard HDL simulation tool. The files necessary for simulation are automatically generated by the iCEcube2 Physical Implementation tools, after the routing phase.

- 5. Perform Static Timing Analysis using the iCEcube2 static timing analyzer.

- 6. Generate the device programming and configuration files from the iCEcube2 Physical Implementation tools.

- 7. Program your device using the device programming hardware provided by Lattice.

# Chapter 2 Quick Start Guide

This chapter provides a brief introduction to the iCEcube2 design flow. The goal of this chapter is to familiarize the user with the fundamental steps needed to create a design project, synthesize and implement the design, generate the necessary device configuration files, and program the target device.

Detailed information on tool features and usage is provided in subsequent chapters.

#### **Creating a Project**

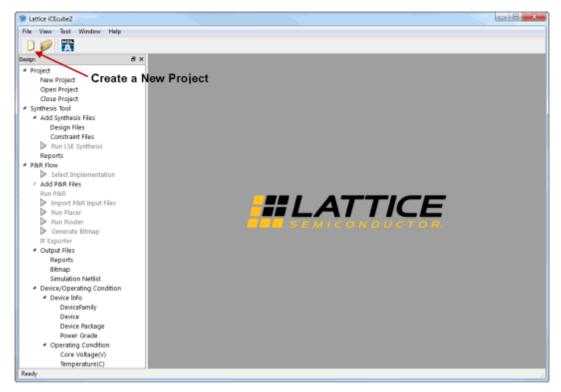

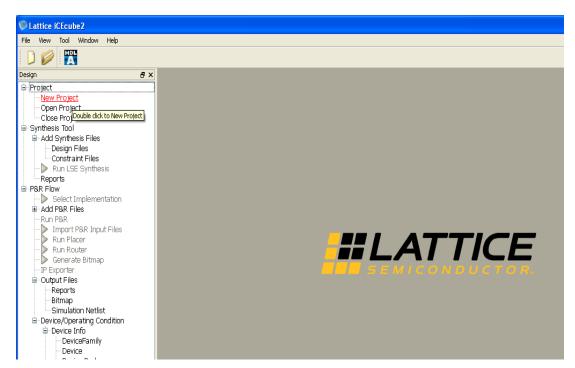

Starting the iCEcube2 software for the first time, you will see the following interface shown in Figure 2-1.

Figure 2-1: Create a New Project

The first step is to create a new design project and add the appropriate design files to your project. You can create a new project by either selecting **File > New Project** from the iCEcube2 menu, or by clicking the **Create a New Project** icon as seen in Figure 2-1. The New Project Wizard GUI is displayed in Figure 2-2.

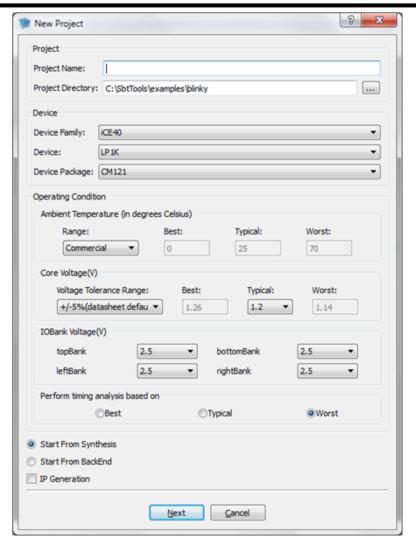

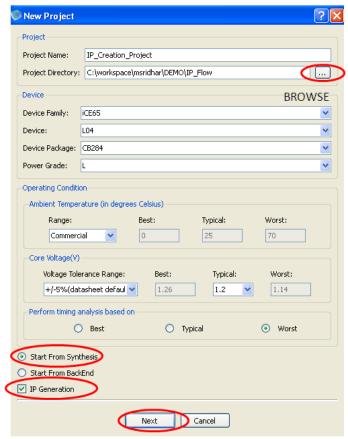

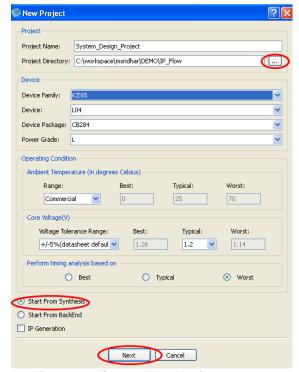

Figure 2-2: New Project Setup Wizard for iCE40 Family

This example is targeted for iCE40 family device. Follow the following steps to setup the project properties.

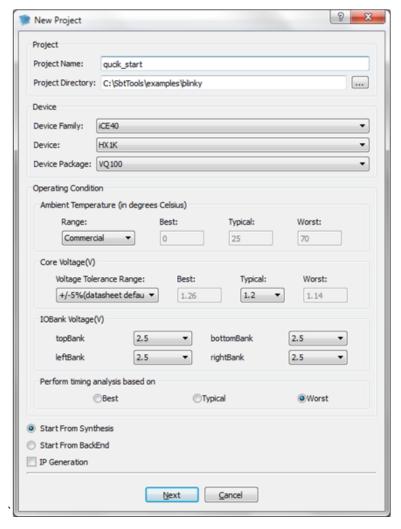

- 1. **Project Name** Field: Specify a project name (quick\_start) in the Project Name field.

- 2. **Project Directory** Field: Specify any directory where you want to place the project directory in the Project Directory field.

- 3. **Device Family** Fields: This section allows you to specify the Lattice iCE device family you are targeting. For this example, change the Device Family to **iCE40**.

- 4. **Device** Fields: This section allows you to specify the Lattice device and package you are targeting. For this example, change the Device to **HX1K** and change the device package to the **VQ100**.

- 5. **Operating Condition** Fields: This section allows you to specify the operating conditions of the device which will be used for timing and power analysis.

- 6. **Start From Synthesis:** This option allows you to start the flow from Synthesis. For current example, select this option.

- 7. Start From BackEnd: This option allows you to start from Post Synthesis flow.

After the above selections the New Project GUI Wizard has the following settings as shown in Figure 2-3.

Figure 2-3: Tutorial Project Settings

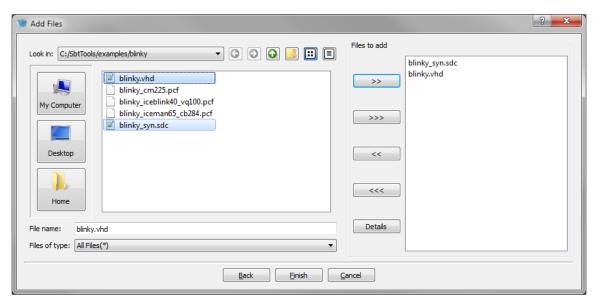

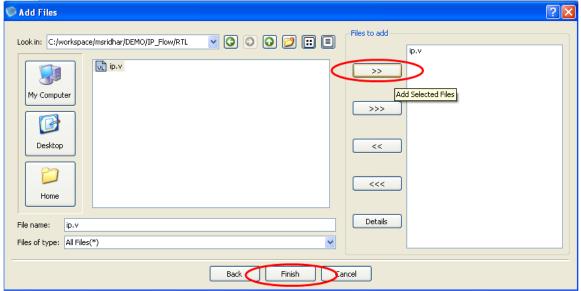

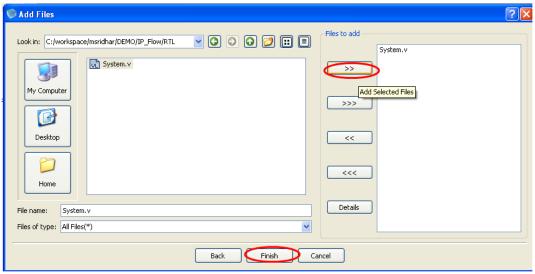

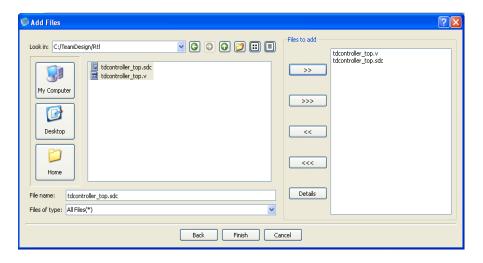

- 8. **Click Next** to go to the **Add Files** dialog box shown in Figure 2-4. You will be prompted to create a new project directory. Click Yes.

- 9. In the **Add Files** dialog box, navigate to: <iCEcube2 installation directory>/examples/blinky Highlight the following files:

blinky.vhd

blinky\_syn.sdc\*

Select each file and click >> to add the selected file, or click >>> to add all the files in the open directory (files can be removed using << and <<<) to your project. Click **Finish** to create the project.

\* The SDC file is a Synopsys constraint file, which contains timing constraint information.

Figure 2-4: Add Files Dialog Box

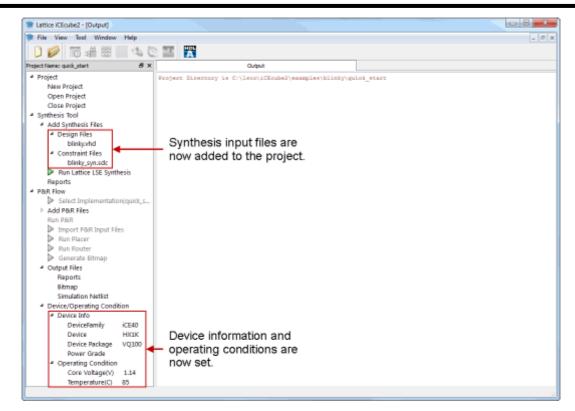

After successfully setting up your project, you will return to the iCEcube2 Project Navigator screen shown in Figure 2-5.

Figure 2-5: iCECube2 Project Navigator View after Completing Project Setup

#### Synthesizing the Design

After a successful project setup, select a synthesis tool:

- In the iCEcube2 window, right-click Synthesis Tool and choose Select Synthesis Tools.

The Select Synthesis Tool dialog box opens.

- 2. Select a tool: Synplify Pro or Lattice LSE.

- 3. Click OK.

The Run <Tool> Synthesis command changes to show the selected tool.

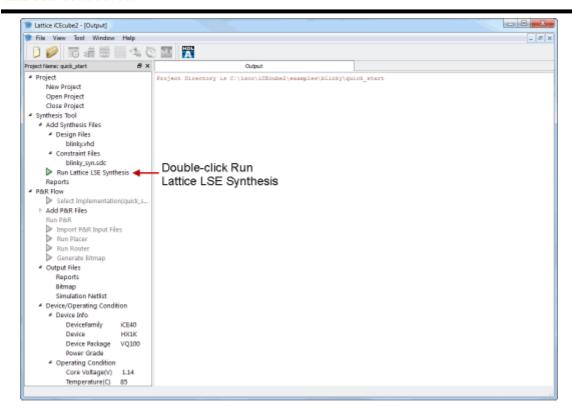

For this tutorial, select Lattice LSE.

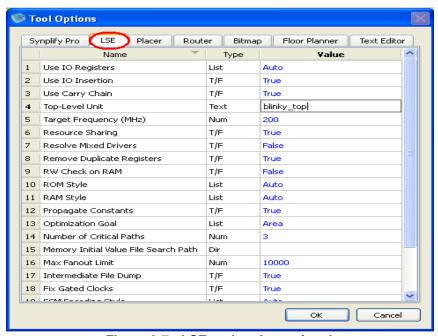

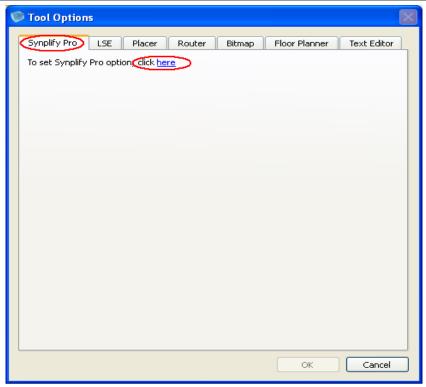

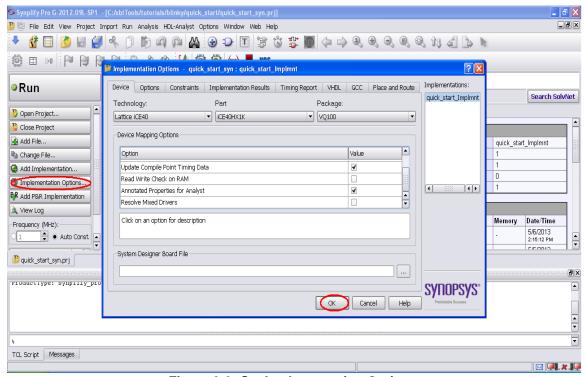

Next, set options for the synthesis tool. Select Tool > Tool Options. In the Tool Options dialog box, click the tab of the tool. To change the value of an option, either click in its Value cell and start typing to replace the value or double-click to edit the value or to see a menu of values. In the Synplify Pro tab, click on the word "here" to open Synplify Pro. Then, in the Synplify Pro window, click Implementation Options.

For now, do not change any option settings. Click Cancel.

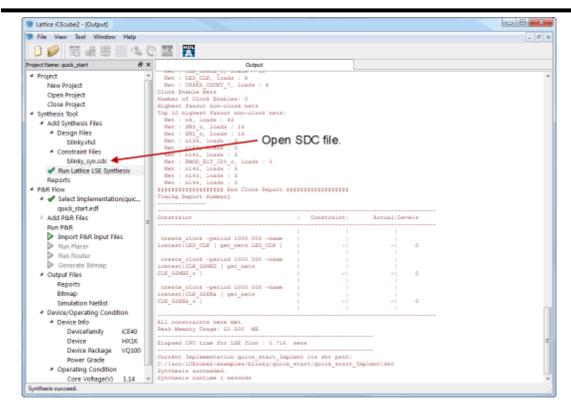

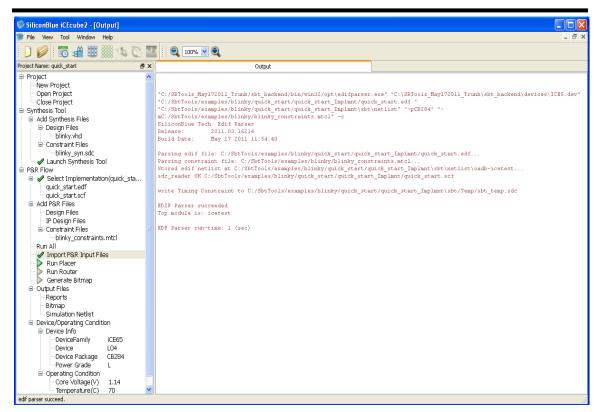

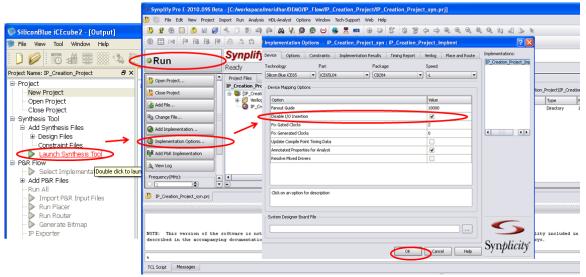

Double-click Run Lattice LSE Synthesis in the project navigator window. See Figure 2-6. This starts the Lattice Synthesis Engine running. See Figure 2-7.

Figure 2-6: Launch Synthesis Tool

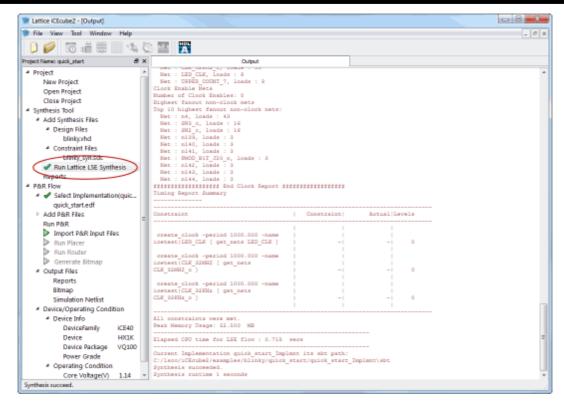

Once synthesis is complete, you will see a green checkmark next to the Run Lattice LSE Synthesis command. The Output tab shows the actions taken along with any warning or error messages. Scroll down toward the bottom to see the area, clock, and timing reports. See Figure 2-7.

Figure 2-7: Synthesis Run Status

#### **View Timing Constraints**

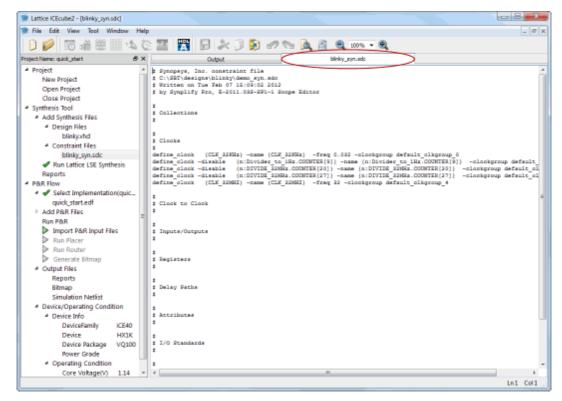

**Double Click** on the **blinky\_syn.sdc** file under the Constraint Files folder. See Figure 2-8. It will open the timing constraints for the project shown in Figure 2-9.

Figure 2-8: Open the SDC File to View Timing Constraints

Figure 2-9: View Timing Constraints

#### **Select Implementation**

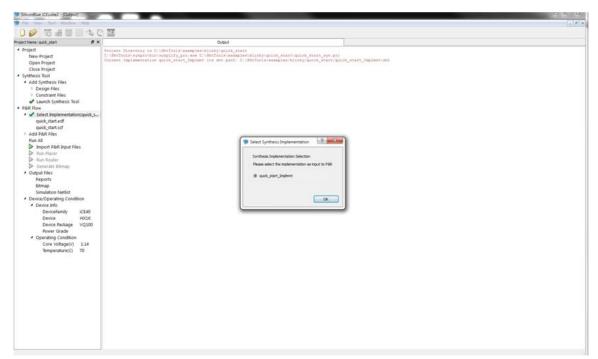

**Double-click** on **Select Implementation**. See Figure 2-10. This will tell iCEcube2 which synthesis implementation to process for place and route. If you have different synthesis implementations, you will be able to select the synthesis implementation you wish to place and route. Since we only have one implementation, **select OK** when the Select Synthesis Implementation dialog box appears.

Figure 2-10: Select Synthesis Implementation

#### **Importing Physical Constraints**

Physical constraints such as pin assignments are stored in a .PCF file (Physical Constraint File). Add the .PCF file to your project.

In the iCEcube2 Project Navigator, Right Click on Constraint Files. Select Add Files... See Figure 2-11.

Note: For information on importing physical constraints from iCEcube to iCEcube2, please refer to the **Importing Physical Constraints from iCEcube to iCEcube2** section at the end of this quick start guide.

Figure 2-11: Add Constraints Files for Place and Route

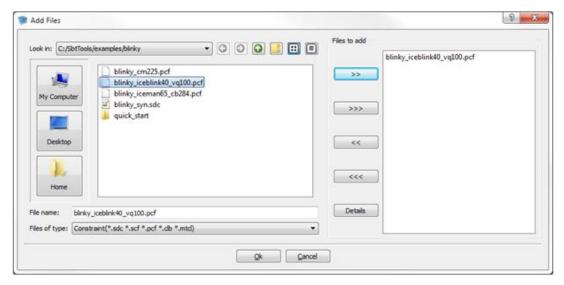

Navigate to the <iCEcube2 Installation Directory>/examples/blinky and **Add blinky.pcf** file. See Figure 2-12.

Figure 2-12: Add .pcf File

#### **Import Place & Route Input Files**

The next step is to import the files for Place and Route. **Double-click** on **Import P&R Input Files** in the Project Navigator. See Figure 2-13. Once completed you will see a green check next to Import P&R Input Files. See Figure 2-14.

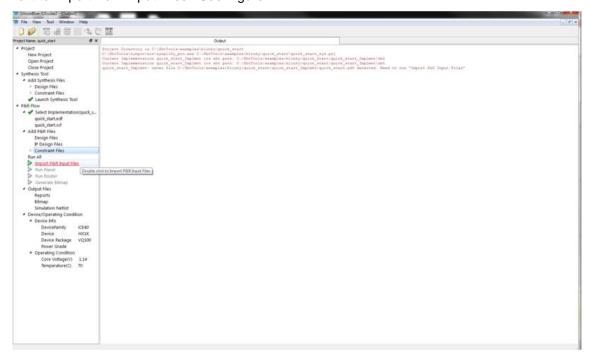

Figure 2-13: Import P&R Input Files

Figure 2-14: Successful Import of P&R Input Files

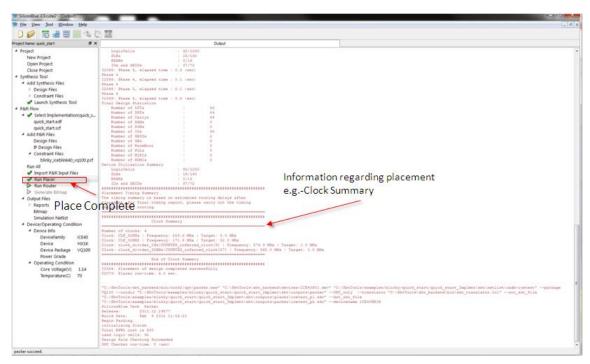

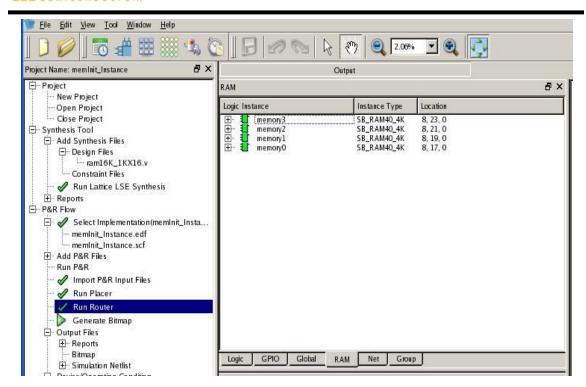

#### Place the Design

Double-click on Run Placer.

Once placement is complete, a green check will appear and the Output window will show information about the placement of the design. See Figure 2-15.

Figure 2-15: Placer Run Status Display

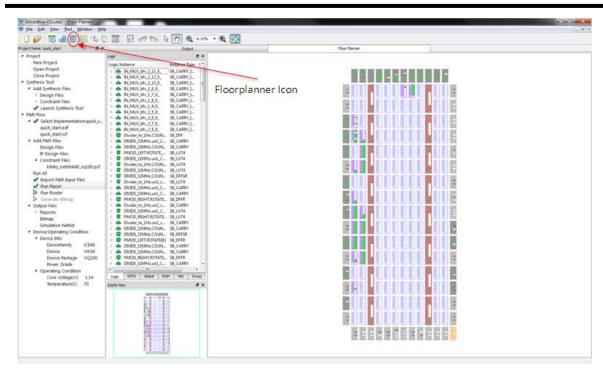

#### **View Floor Planner**

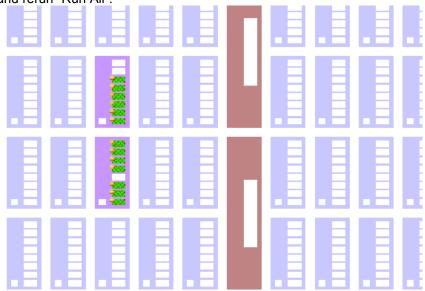

At this point, since placement has been completed, you can view the placement of the design by opening the Floor Planner. You can open the Floor Planner by going to the menu and selecting **Tool > Floor Planner** or you can also select the Floor Planner Icon. See Figure 2-16.

Figure 2-16: Floorplanner View

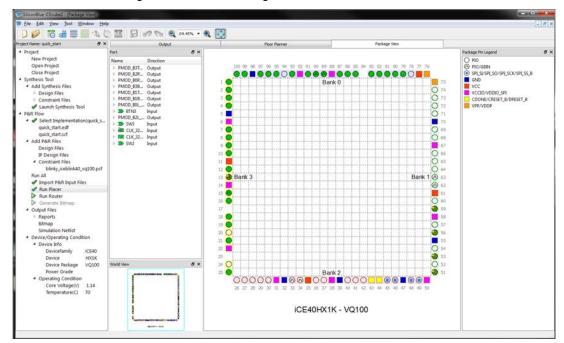

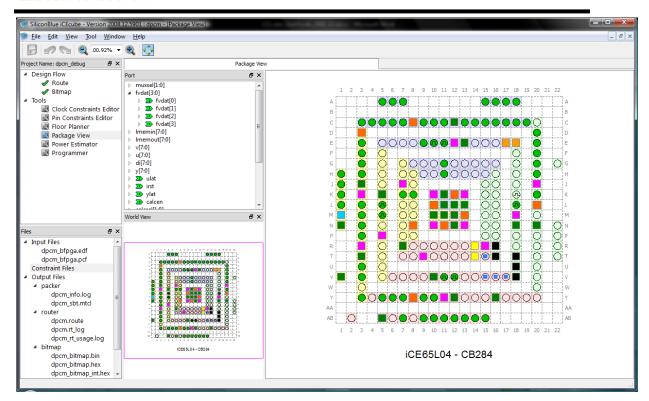

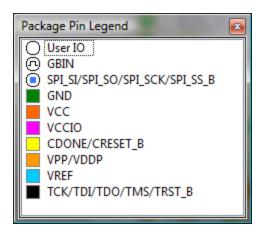

#### View the Package View

You can also see how pins were placed for your design by selecting the Package View. You can select the package viewer by going to the menu and selecting **Tool > Package View** or you can also select the Package View Icon. See Figure 2-17.

Figure 2-17: Package View

#### **Route the Design**

**Double-click on Run Router** in the project navigation window. Place and Route have been separated into different steps as to allow you to re-route the design after making placement modifications in the floor planner without having to re-run the placer.

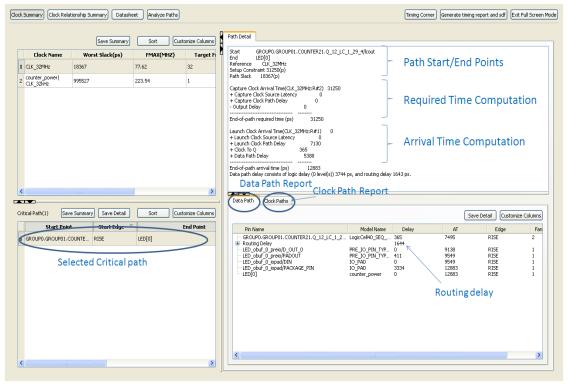

#### **Perform Static Timing Analysis**

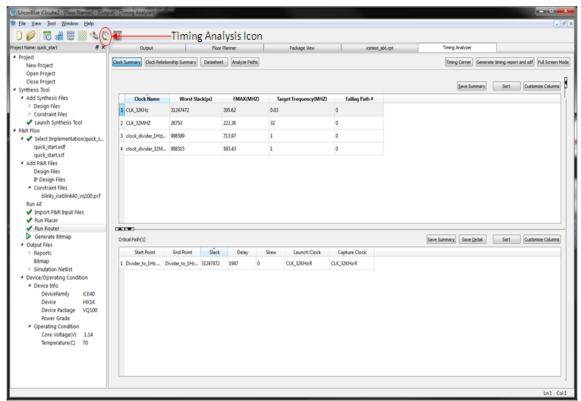

Now that you have routed the design, you can perform timing analysis to check to see if the design meets your timing requirements. To launch the timing analyzer, go to the menu and **select Tool > Timing Analysis**. You can also select the Timing Analysis Icon. See Figure 2-18.

Figure 2-18: Timing Analysis Summary

You can see from the timing analysis that our 32-kHz design is running at over 395 MHz and our 32-MHz clock is running at over 222 MHz (worst case timing). If we were not meeting timing, the timing analyzer would allow you to see your failing paths and do a more in-depth analysis. For this tutorial, we won't go into details on timing slack analysis.

#### **Perform Power Analysis**

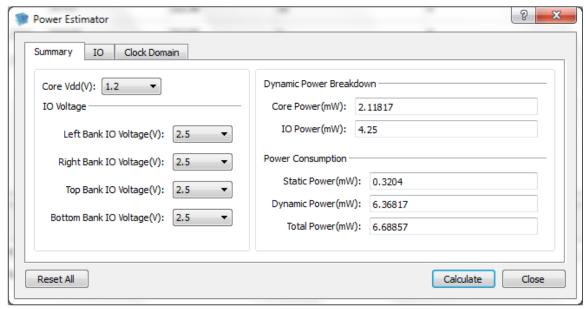

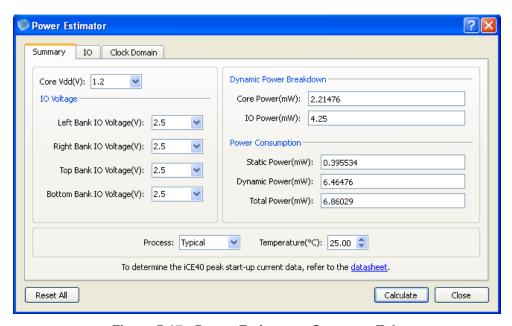

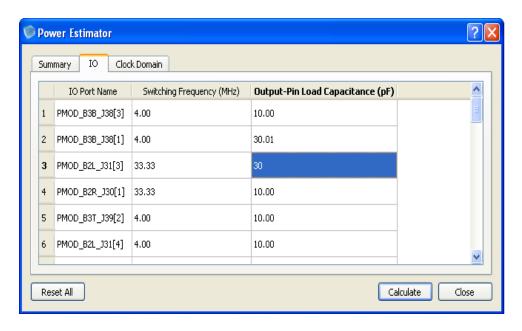

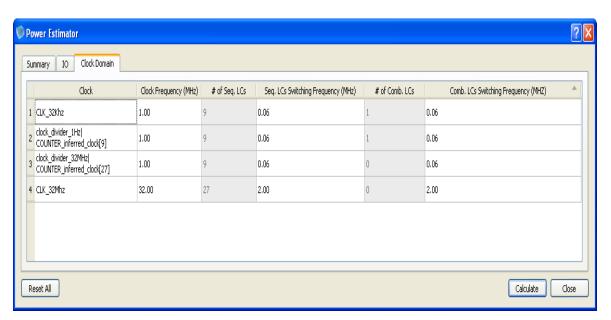

iCEcube2 also comes with power estimator tool. To launch the power estimator, go to the menu and select **Tool > Power Estimator**. You can alternatively select the power estimator icon. There are multiple tabs in the Power Estimator tool including Summary, IO, and Clock Domain as shown in Figure 2-19. On the Summary tab, **change the Core Vdd to 1.2V** and make sure all **IO voltages are at 2.5V**. Then hit **Calculate**. The estimator will update with power information for

both static and dynamic power. For more information on using the IO and Clock Domain tabs, please refer to the detailed section on the Power Estimator tool.

Figure 2-19: Power Estimator

#### **Programming the Device**

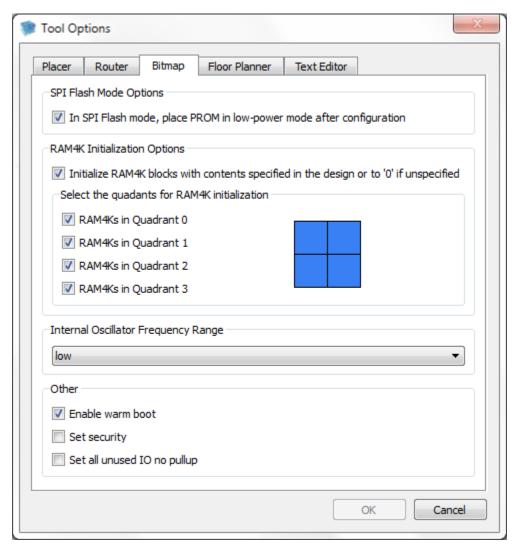

In order to program a device, you will need to generate a programming file. In the project navigator, double click on Generate Bitmap.

You are now ready to program an iCE40 device with the generated bitmap.

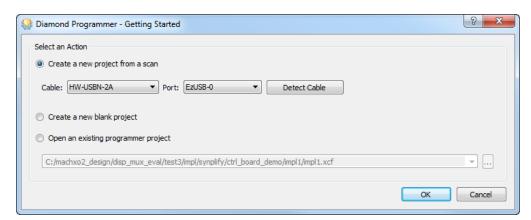

Start the stand-alone Diamond Programmer. In Windows, from the Start menu, **choose Lattice Diamond Programmer** < **version\_number** > **Diamond Programmer**.

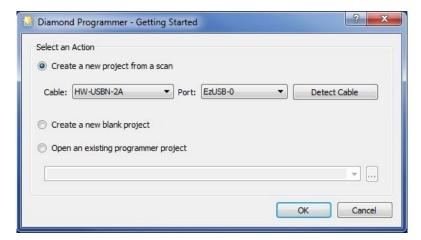

The Diamond Programmer Getting Started dialog box appears, as shown in Figure 2-20.

Figure 2-20: Getting Started Dialog Box

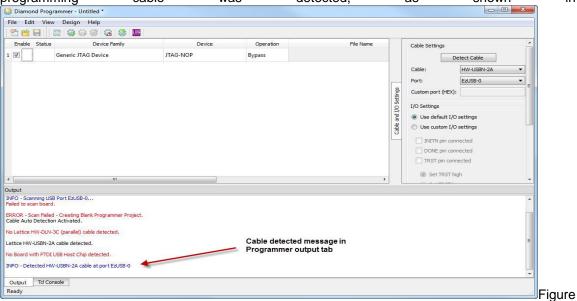

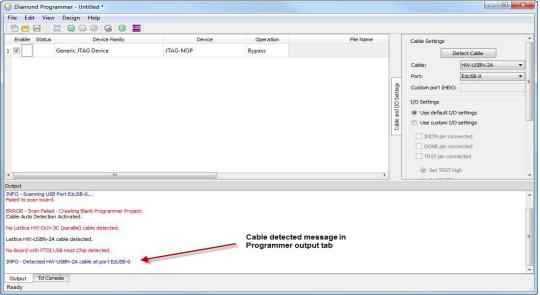

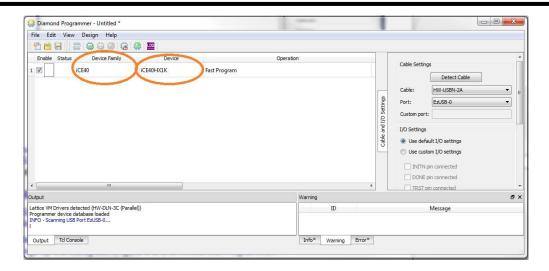

Choose **Create a New Project from a Scan** button and click **OK**. The Diamond Programmer main window appears. In the Cable Settings box in the upper right, click **Detect Cable**.

Diamond Programmer will indicate in the bottom output tab that the Lattice HW-USBN-2A USB programming cable was detected, as shown in

2-21.

Figure 2-21: Diamond Programmer Main Window

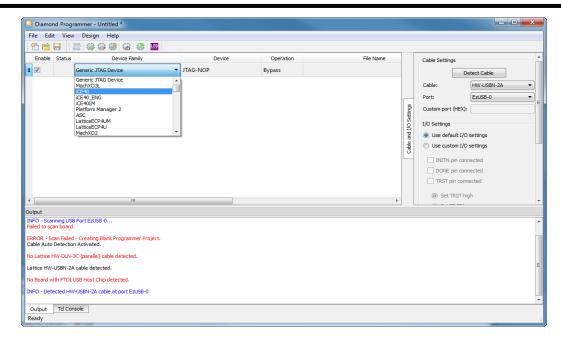

In the Device Family field, click the Generic JTAG Device box and choose **iCE40** from the drop-down menu, as shown in Figure 2-22.

Figure 2-22: Choosing iCE40 Device Family

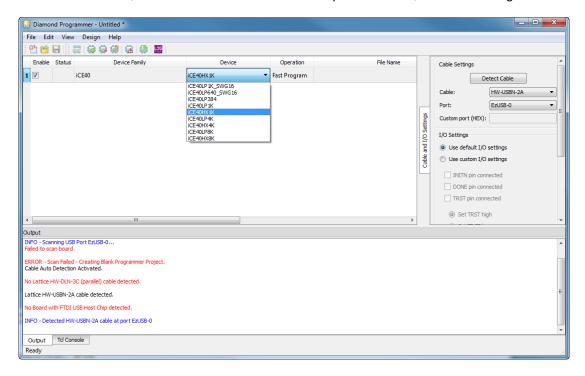

In the Device column, choose iCE40HX1K from the drop-down menu, as shown in Figure 2-23.

Figure 2-23 : Choosing iCE40HX1K Device

There are three basic programming flows for configuring the iCE40 device. This section explains programming iCE40 device using an external SPI Flash device available in iCEblink40-HX1K evaluation board.

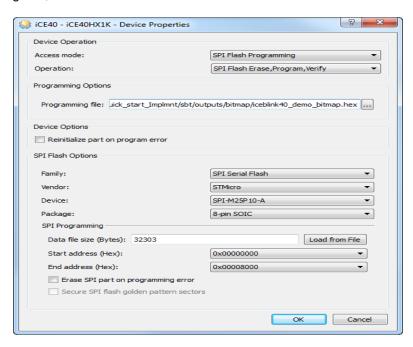

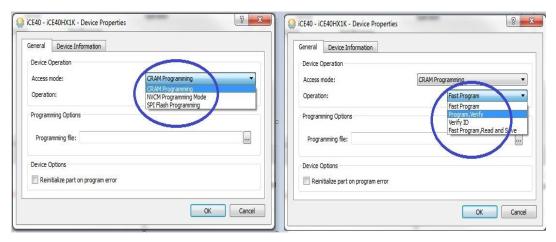

Choose **Edit > Device Properties**, or double-click the Operation box to display the Device Properties dialog box, as shown in Figure 2-24.

In the Device Properties dialog box, set options as follows:

Access Mode: SPI Flash Programming

Operation: SPI Flash Erease, Program, Verify

In the Programming File box, browse to the .hex file you generated with iCEcube2.

In the SPI Flash Options box, choose the following options:

• Family : SPI Serial Flash

• Vendor : STMicro

Device : SPI-M25P 10-APackage : 8-pin SOIC

The Device Properties dialog box should be configured as shown in Figure 2-24. In the Device Properties dialog box, click **OK**.

Figure 2-24: Device Properties Dialog Box

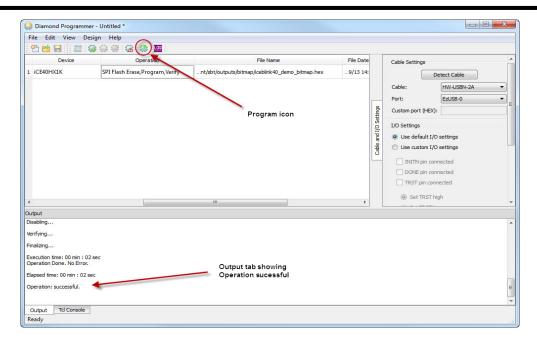

In the Diamond Programmer main window, choose **Design > Program**, or click the Program icon in the toolbar, as shown in Figure 2-25. Once the SPI Flash is programmed, the output tab in the lower left portion of Diamond Programmer indicates Operation **successful**.

Figure 2-25: Program the device.

The external SPI Flash on the Lattice iCEblink40-HX1K evaluation board has been programmed, and the iCE40 is configured from the SPI flash.

#### Addendum:

#### Importing Physical Constraints from iCEcube to iCEcube2

For users who have created physical constraints using iCEcube, this section describes how to import and convert those constraints for use in iCEcube2. This section will demonstrate how to import a .MTCL file from iCEcube and save it into .PCF format used in iCEcube2.

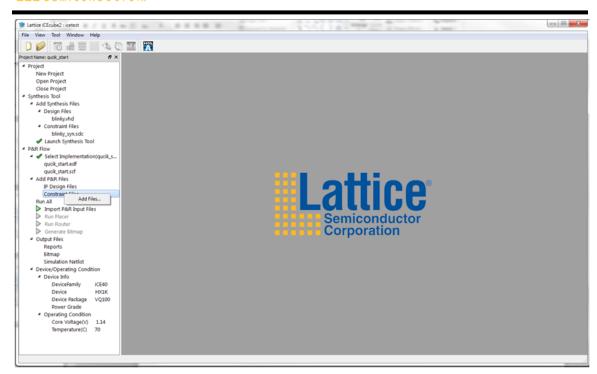

In the iCEcube2 project navigator, **Right-click** on **Constraint Files** and select **Add Files**. See Figure 2-26.

Figure 2-26: Add Constraint File

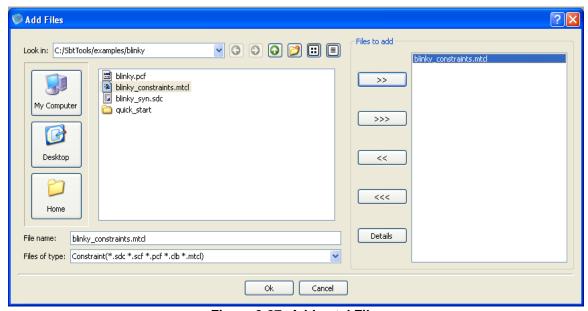

Navigate to the <iCEcube2 Installation Directory>/examples/blinky and **Add blinky.mtcl** file. See Figure 2-27.

Figure 2-27: Add .mtcl File

#### **Import Place & Route Input Files**

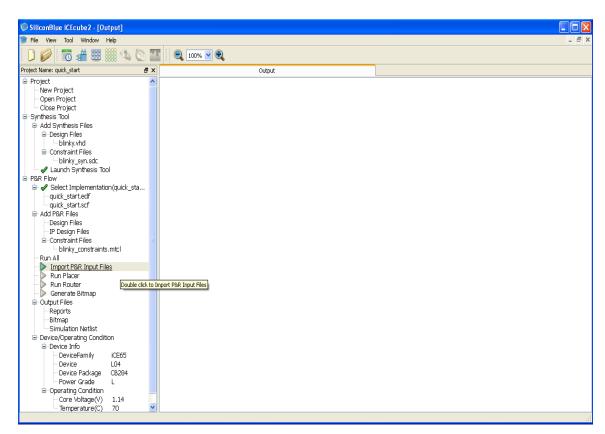

The next step is to import the files for Place and Route. **Double-click on Import P&R Input Files** in the Project Navigator. See Figure 2-28. Once importing of files completed you will see a green check next to Import P&R Input Files. See Figure 2-29.

Figure 2-28: Double-Clock on Import P&R Input Files

Figure 2-29: Successful Import of P & R Input Files

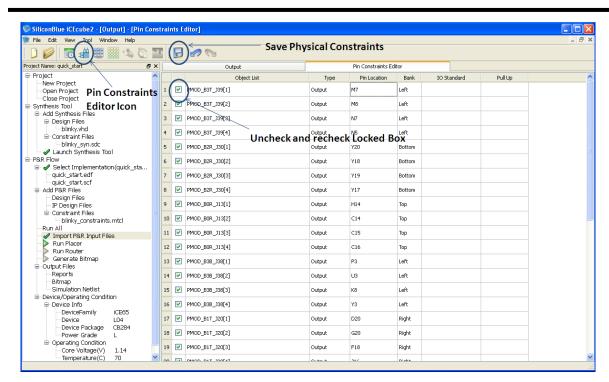

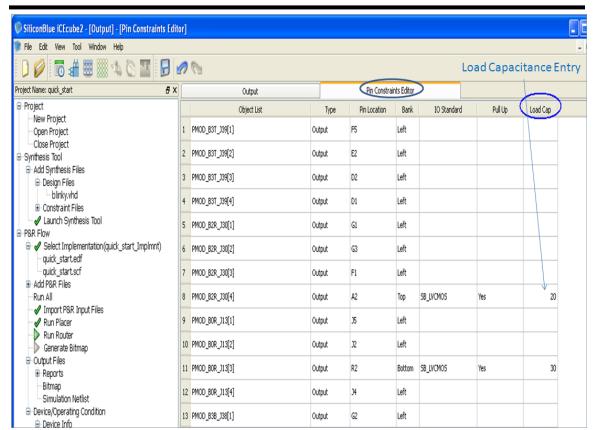

#### Saving Physical Constraints into .pcf Format

Open the Pin Constraints Editor by going to the menu and selecting **Tool > Pin Constraints Editor** or you can also select the Pin Constraints Editor Icon. See Figure 2-30. You will see a list of pin assignments that are locked under the locked column. **Uncheck and Recheck one of the pins under the locked column**. The save icon will now become an active icon. **Click** on the **Save physical constraints icon**. This will bring up a dialog box where you can save the PCF file. **Hit OK**. See Figure 2-31. The .PCF file contains physical constraints in the design used for place and route.

Figure 2-30: Pin Constraints Editor

Figure 2-31: Save Physical Constraints File

# Chapter 3 iCEcube2 Project Setup and Navigation

#### Introduction

This chapter describes the features of the iCEcube2 Project Manager and how to set up a design Project. The primary functions of the Project Manager include project setup, launching the Lattice Synthesis Engine (LSE) or Synplify pro for synthesis, placing and routing the design, launching the Aldec Active-HDL for simulation and launching the software required to Program the target device.

This chapter assumes that the reader is familiar with the New Project creation process as described in *Chapter 2 Quick Start*.

#### **Project Manager GUI**

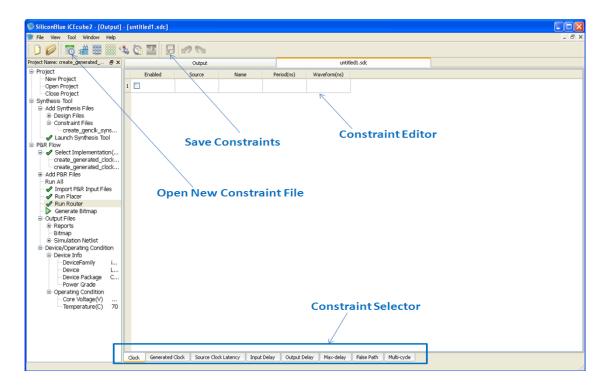

Figure 3-1 below displays the Project Manager GUI. A new project can be opened by clicking on the **New Project** icon or the **File > New Project** menu item. Similarly, an existing project can be opened or closed using **the Open Project** and **Close Project** icons.

Figure 3-1: iCEcube2 Project Flow Manager

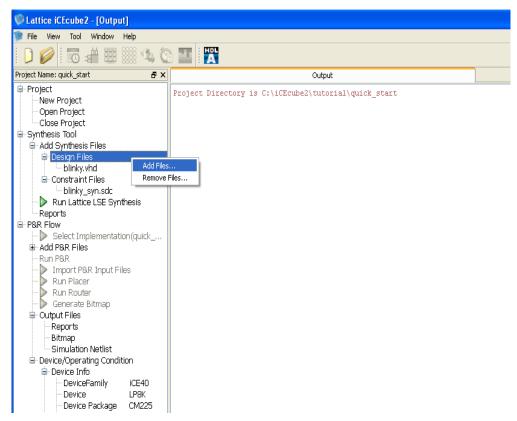

#### **Adding/Deleting Design and Constraint Files**

Design and Constraint files can be added or removed from the project by selecting Design Files or Constraint Files respectively as displayed in Figure 3-2.

Figure 3-2: Adding/Removing Design Files to the design project

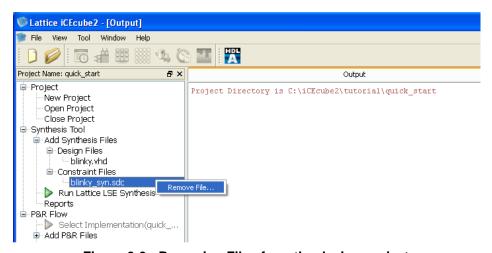

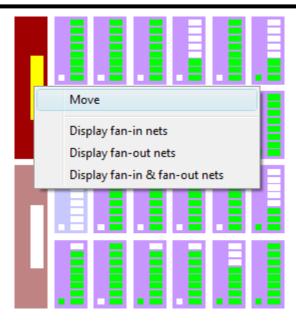

Deleting a specific file can be accomplished by selecting the file name and clicking the **right-button** on the mouse. Figure 3-3 below displays the state of the GUI upon clicking the mouse button.

Figure 3-3: Removing Files from the design project

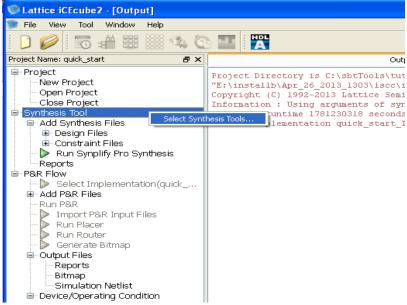

#### Selecting Synthesis Tool and Setting synthesis Options

The iCEcube2 software supports Synplify-pro synthesis tool and Lattice Synthesis tool (LSE) to synthesis the design. In order to change the synthesis tool, click **right-mouse** button on "**Synthesis Tool**" item and select the synthesis tool as shown in Figure 3-5.

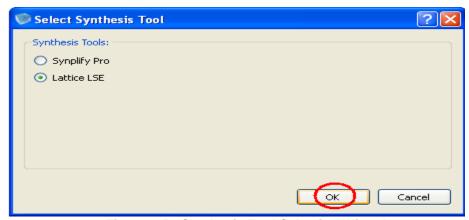

Figure 3-4: Select Synthesis Tool

Figure 3-5: Synthesis Tool Selection Wizard

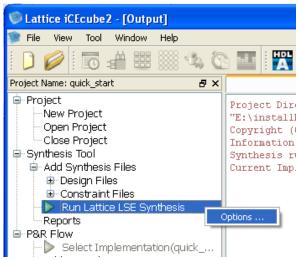

To set the LSE synthesis tool options, click "**right-mouse**" button on the "Run LSE Synthesis" as shown in Figure 3-6.

Figure 3-6: Open LSE Tool Options Wizard

Set the LSE tool options and click on "OK" button to save the changes. Rerun the LSE synthesis.

Figure 3-7: LSE tool options wizard

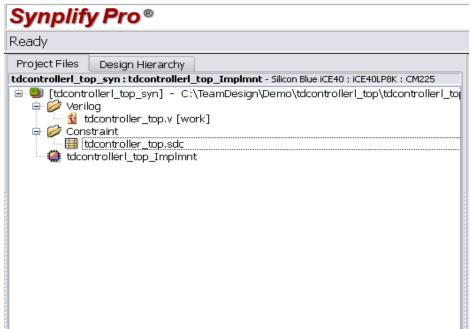

To set the Synplify-Pro synthesis tool options, click "**right-mouse**" button on the "Run Synplify-Pro Synthesis" item. This will pop up the "Tool Options" wizard. In the "Synplify Pro" tab select the word "here" to open the Synplify-Pro GUI.

Figure 3-8: Invoke Synplify-Pro GUI

In the Synplify-Pro window, Select "Implementation Options", set the tool options and save. Rerun the Synplify synthesis.

Figure 3-9: Set Implementation Options

## Selecting the Target Device and Operating Conditions

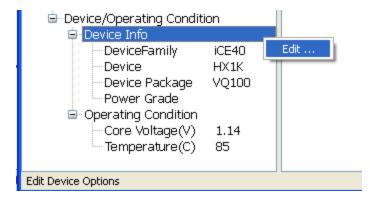

The iCEcube2 software provides the ability to specify the operating conditions for the target device. In order to change the Target Family, Device and/or the Operating Conditions, click the **right-button** on the mouse, in the **Device/Operating Condition** window to display the **Edit** action. This is shown in Figure 3-10.

Figure 3-10: Modifying the Device Selection/Operating Conditions

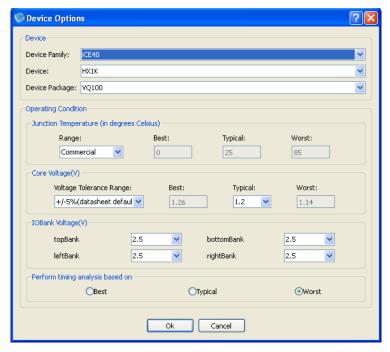

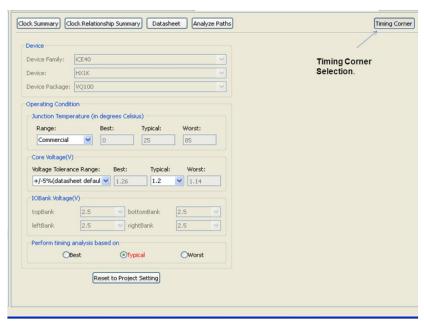

Device options wizard is shown in Figure 3-11.

Figure 3-11: Device Options for iCE40 Family

In order to specify a suitable target **Device**, the following steps need to be performed:

- 1. Specify a **Device Family**

- 2. Specify a **Device** using the drop-down menu

- 3. Select a suitable **Device Package** for the device selected in the previous step

Specifying the **Operating Conditions** for the target device involves the following steps:

#### 1. Junction Temperature

- a. Select an appropriate **Junction Temperature Range** from the options available. Depending on the Power Grade selected for the target device, the software provides built-in options such as **Commercial** and **Industrial** temperature ranges.

- b. If the device's operating conditions do not fall into either the **Commercial** or the **Industrial** temperature ranges, the software also permits the user to specify a customized junction temperature. This is accomplished by selecting the **Custom** option, and manually specifying the **Best, Typical** and **Worst Case** junction temperatures.

- 2. Core Voltage: Select a Voltage Tolerance Range from the provided options.

- 3. **IO Bank Voltage**: This option is available only for iCE40 family as shown in Figure 3-11. Select a bank voltage from the provided options for the top, bottom, left, right banks. The specified IO Voltage values are used by Power Estimator and Static Timing Analysis tools.

In order for **Static Timing Analysis** to be performed at the desired Operating Conditions, the software provides the ability to select the **Best Case**, **Typical Case** or **Worst Case** conditions.

# **Output Window**

The iCEcube2 Project Flow Manager software provides an Output Window to display messages, warnings and errors.

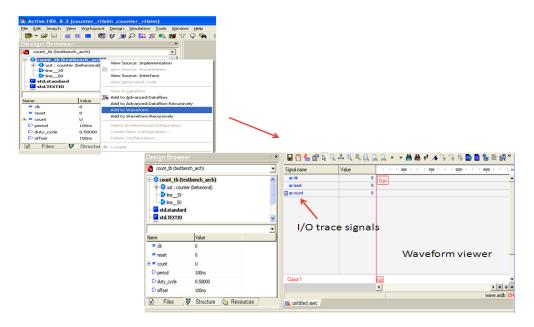

#### Simulation Wizard

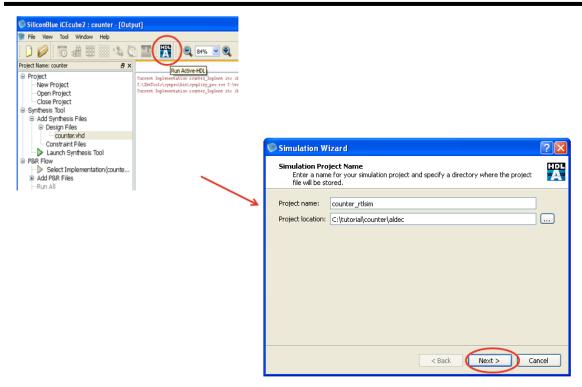

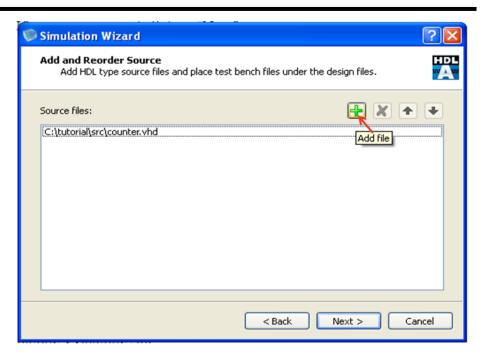

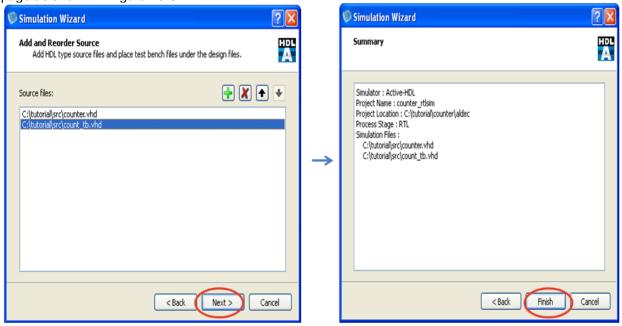

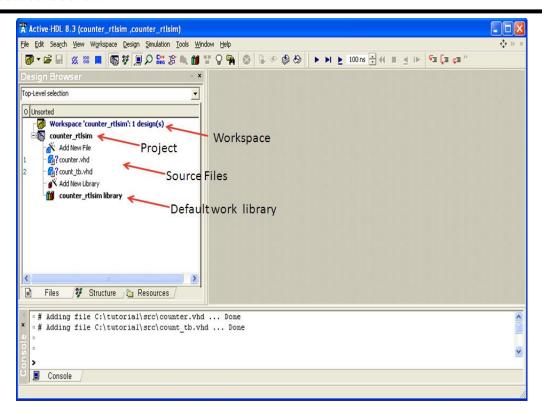

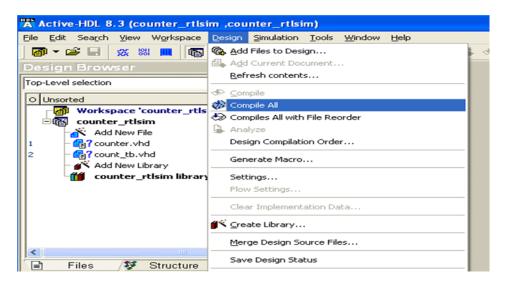

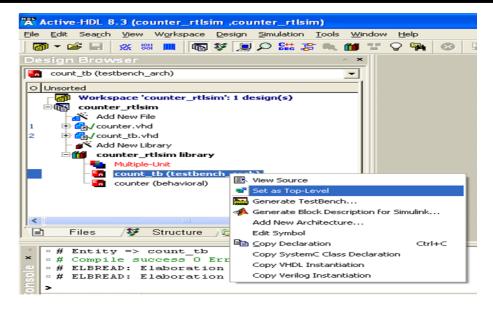

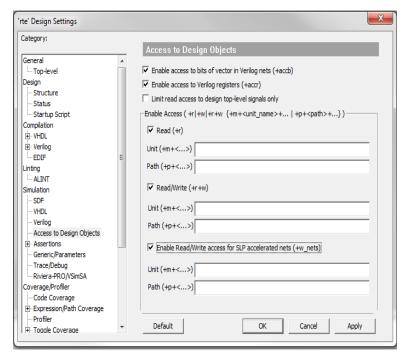

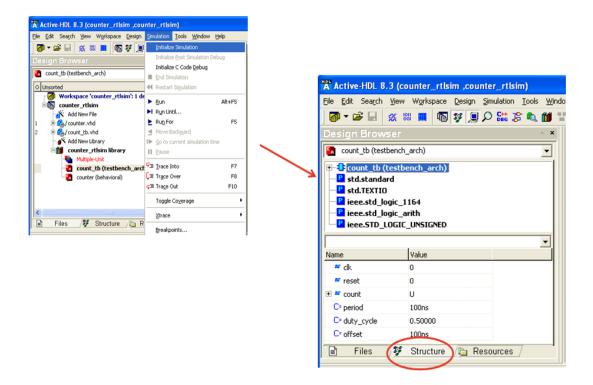

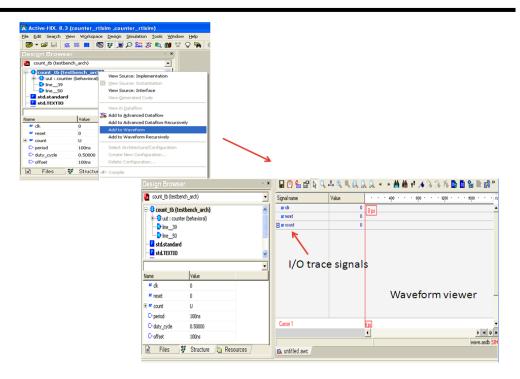

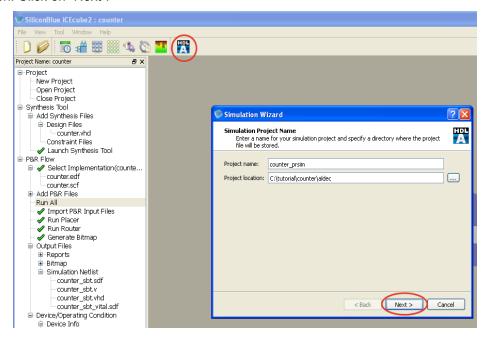

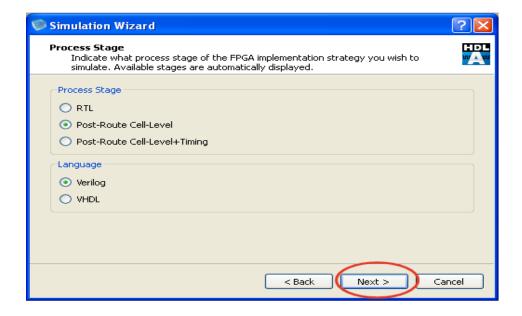

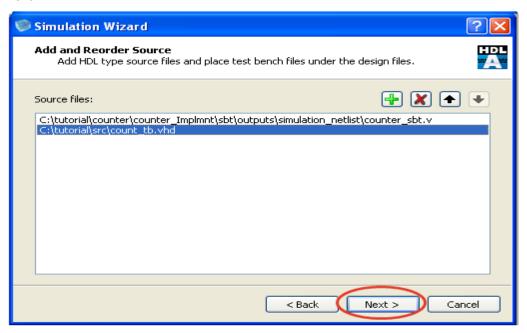

The iCEcube2 windows software installs Aldec Active-HDL, a windows based simulator tool to perform functional and timing verification of the implemented designs. The "Simulation Wizard" in the project navigator allows the user to create a simulation project for Aldec Active-HDL, select the simulation netlist, simulation language and invokes the Aldec Active-HDL interface.

Select Active-HDL icon to invoke the "Simulation Wizard" as shown in Figure 3-12. Refer to chapter "Simulating Design with ALDEC Active-HDL" for more details about simulation wizard and simulation steps with Aldec Active-HDL.

Figure 3-12: Invoking Simulation Wizard.

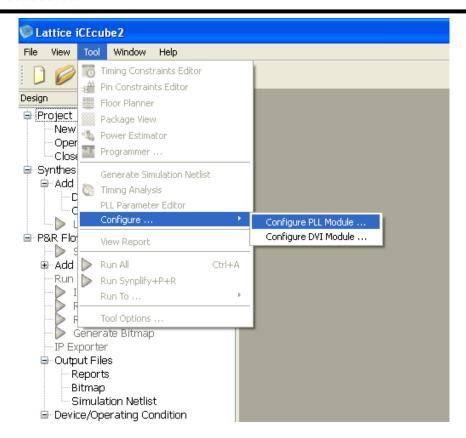

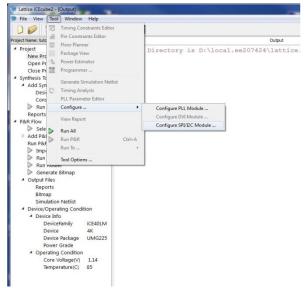

## **PLL Module Generator**

Certain devices of the iCE40 family include a Phase Lock Loop (PLL) function. The PLL function requires configuration before it can be used in a design. To help configure the PLL, the iCEcube2 Project Flow Manager includes a PLL Module Generator, which can be launched from the **Tool > Configure > Configure PLL Module** menu item, as displayed in Figure 3-13.

Figure 3-13: Launching the PLL Module Generator

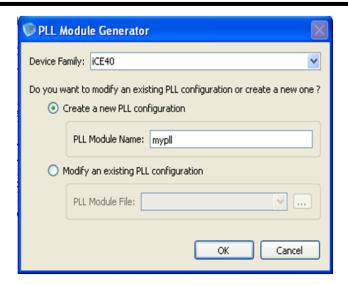

The PLL Module Generator allows the user to create a new PLL configuration, or edit an existing one as shown in Figure 3-14.

The output of the PLL Module Generator is a PLL module file (Verilog), that instantiates a PLL, as configured by the user. A secondary file (wrapper), that includes an instance of the PLL module, is generated in order to help instantiate the PLL module in the user's design. Note that the PLL module file should be included in the list of design files.

Once a PLL module file has been generated, it can be edited, by selecting the "Modify an existing PLL configuration" option (Figure 3-14).

Figure 3-14: Create/Modify a PLL configuration

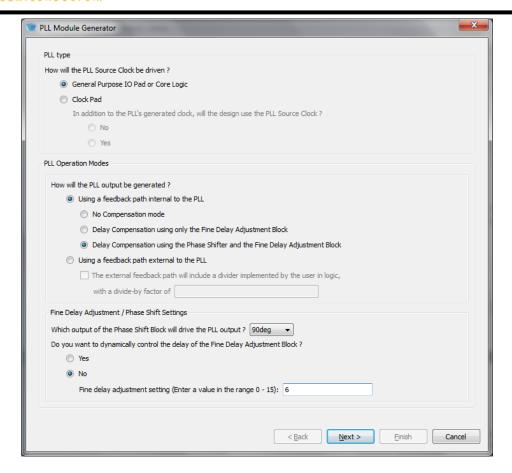

# Configuring the iCE65 PLL

In the PLL Module Generator wizard, select **Device Family** as iCE65 and provide the PLL Module Name. Click on the OK button. The PLL Module Generator launches a wizard to help the user configure the PLL as per the design requirements. This section describes the features of iCE65 family PLL modules.

# PLL Type

The connectivity of the PLL to its surrounding logic determines the PLL Type. The iCEcube2 software supports the following PLL types. These PLL type options can be selected on the first page of the wizard, as displayed in Figure 3-15.

- General Purpose IO Pad or Core Logic: In this scenario, the PLL input (source clock) is driven by a signal from the FPGA fabric. This signal can either be generated on the FPGA core, or it can be an external signal that was brought onto the FPGA using a General Purpose IO pad. The PLL output (generated clock) is available on the FPGA to drive a global clock network, as well as regular routing.

- 2. Clock Pad: The PLL input clock (source) is driven by a dedicated clock pad located in IO Bank 2

- a. The PLL output (generated clock) is available to drive a global clock network, as well as regular routing. The PLL source clock is not available on the FPGA.

- b. The PLL output (generated clock) is available to drive a global clock network, as well a regular routing. The PLL source clock is also available on the FPGA, and can drive a global clock network, as well as regular routing.

Figure 3-15: Selecting the PLL Type and Operation Mode

#### **PLL Operation Modes**

The PLL can be configured to operate in one of multiple modes. An Operation Mode determines the feedback path of the PLL and enables phase alignment of the generated clock with respect to the source clock.

The iCEcube2 software supports the following PLL Operation modes:

- 1. *No Compensation mode:* The PLL can be used for generating the desired output frequency, without the ability to control the phase of the generated clock.

- 2. Delay Compensation using only the Fine Delay Adjustment (FDA) Block: In this mode, the feedback path is internal to the PLL but traverses through a fine delay adjustment circuit that permits user control of the feedback path delay in 16 steps of 0.15 ns each. The delay adjustment can be controlled dynamically through signals connected to the PLL, or it can be fixed i.e. once configured, the delay contributed by the delay block can only be changed upon re-programming the FPGA with a different bit configuration.

- 3. Delay Compensation using the Phase Shifter and the Fine Delay Adjustment (FDA) Block: The Phase Shifter provides four outputs corresponding to a phase shift of 0 degrees, 90 degrees, 180 degrees or 270 degrees. In addition, this feedback path provides additional delay adjustment through the FDA block.

- Delay Compensation using a feedback path external to the PLL: The feedback path traverses through FPGA routing (external to the PLL) followed by the Fine Delay Adjustment (FDA)

Block. Hence, in effect, two delay controls are available – the external path for coarse adjustment and the FDA block for fine delay adjustment.

Figure 3-16: PLL Module Generator - Frequency Specification

**Fine Delay Adjustment:** The delay contributed by the FDA block can be Fixed or controlled dynamically during FPGA operation. If Fixed, it is necessary to provide a number (n) in the range 0-15 to specify the delay contributed to the feedback path. The delay for a setting "n" is calculated as follows

FDA delay = (n+1)\*0.15 ps, where "n" is the value specified by the user, and  $0 \le n \le 15$

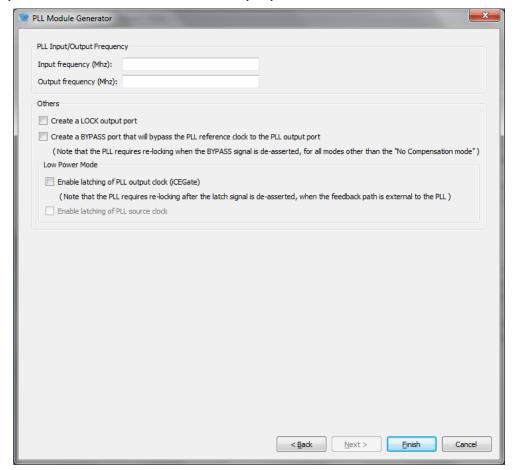

**Frequency Specification:** The input and output frequency of the PLL should be specified in MHz as shown in Figure 3-16. Depending on the values provided by the user, the PLL is internally configured to generate the specified output frequency.

In case the frequency specified is not in the range permitted by the Operation Mode, the software provides appropriate feedback, as displayed in Figure 3-17.

Figure 3-17: Frequency Validation by PLL Configurator

#### Other options:

**LOCK:** A Lock signal is provided to indicate that the PLL has locked on to the incoming signal. Lock asserts High to indicate that the PLL has achieved frequency lock with a good phase lock.

**BYPASS**: A BYPASS signal is provided which both powers-down the PLL core and bypasses it such that the PLL output tracks the input reference frequency.

**Low Power Mode:** A control is provided to dynamically put the PLL into a Lower Power Mode through the iCEGate feature. The iCEGate feature latches the PLL Output signal, and prevents unnecessary toggling.

The RESET (Active Low) port is always generated, and an explicit PLL reset operation is required to initialize the PLL functionality.

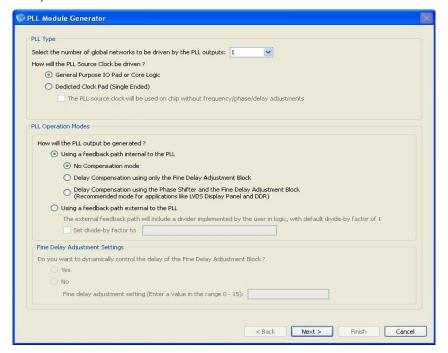

# Configuring the iCE40 PLL

Most devices in the iCE40 family provide two PLL functions, each of which can be configured independently.

In the PLL Module Generator wizard, select **Device Family** as iCE40 and provide the PLL Module Name. Click on the OK button. The PLL Module Generator launches a wizard to help the user configure the PLL as per the design requirements.

## **PLL Type**

The connectivity of the PLL to its surrounding logic determines the PLL Type. The iCEcube2 software supports the following PLL types. These PLL type options can be selected on the first page of the wizard, as displayed in Figure 3-18.

- Select the number of global networks to be driven by the PLL output. Setting the value to "1" generates a PLL which drives a single global clock network, as well as regular routing. Setting the value to "2" generates a PLL which drives two global clock networks as well as two regular routing resources.

- 2. Specify the input to the PLL:

General Purpose IO Pad or Core Logic: In this scenario, the PLL input (source clock) is driven by a signal from the FPGA fabric. This signal can either be generated on the FPGA core, or it can be an external signal that was brought onto the FPGA using a General Purpose IO pad.

Dedicated Clock Pad (Single Ended): The PLL input clock (source) is driven by a dedicated single ended clock pad located in IO Bank 2 (Bottom bank) or IO Bank 0 (Top bank). (In case two global networks were selected in the previous step, the input signal can be used as-is on the logic fabric, i.e. it can bypass the PLL. In the rare situation that this is required, select the check-box, "The PLL source clock will be used on chip without frequency/phase/delay adjustments".)

Figure 3-18: iCE40 PLL - Selecting PLL Type and Operation Modes

## **PLL Operation Modes**

The PLL can be configured to operate in one of multiple modes. An Operation Mode determines the feedback path of the PLL, and enables phase alignment of the generated clock with respect to the source clock.

The iCEcube2 software supports the following PLL Operation modes:

- 1. *No Compensation mode:* The PLL can be used for generating the desired output frequency, without the ability to control the phase of the generated clock.

- 2. Delay Compensation using only the Fine Delay Adjustment (FDA) Block: In this mode, the feedback path is internal to the PLL but traverses through a fine delay adjustment circuit that permits user control of the feedback path delay in 16 steps of 0.15 ns each. The delay adjustment can be controlled dynamically through signals connected to the PLL, or it can be fixed i.e. once configured, the delay contributed by the delay block can only be changed upon re-programming the FPGA with a different bit configuration.

- 3. Delay Compensation using the Phase Shifter and the Fine Delay Adjustment (FDA) Block. For single port PLL types the Phase Shifter provides two outputs corresponding to a phase shift of 0 degrees and 90 degrees. For two port PLL types, the Phase Shifter has two modes:

Divide-by-4 mode and Divide-by-7. In Divide-by-4 mode, the output of B port can be shifted either 0 degrees or 90 degrees w.r.t to A port outputs. In Divide-by-7 mode, the B port output frequency can be set to have a frequency ratio of 3.5:1 or 7:1 w.r.t the port A output frequency. In addition to the delay compensation provided by the phase shifter, this feedback path provides additional delay adjustment through the FDA block.

4. Delay Compensation using a feedback path external to the PLL: The feedback path traverses through FPGA routing (external to the PLL) followed by the Fine Delay Adjustment (FDA) Block. Hence, in effect, two delay controls are available – the external path for coarse adjustment and the FDA block for fine delay adjustment.

**Fine Delay Adjustment:** The delay contributed by the FDA block can be Fixed or controlled dynamically during FPGA operation. If Fixed, it is necessary to provide a number (n) in the range 0-15 to specify the delay contributed to the feedback path. The delay for a setting "n" is calculated as follows

FDA delay = (n+1)\*0.15 ps, where "n" is the value specified by the user, and  $0 \le n \le 15$ .

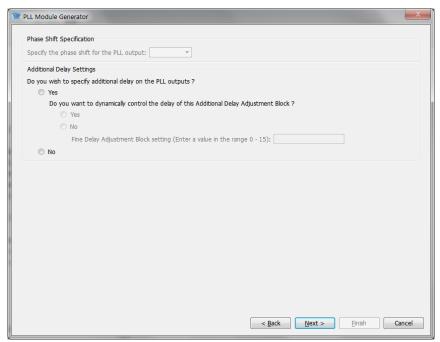

Additional Delay Adjustment: In addition to Fine Delay Adjustment in the feedback path, the user can specify additional delay on the PLL output ports as shown in Figure 3-19. The delay contributed by the delay block can be Fixed or controlled dynamically during FPGA operation. If Fixed, it is necessary to provide a number (n) in the range 0-15 to specify the delay contributed to the feedback path. The delay for a setting "n" is calculated as follows

FDA delay = (n+1)\*0.15 ps, where "n" is the value specified by the user, and  $0 \le n \le 15$ .

This additional delay is applied on the output of single port PLL and port A of two port PLL types.

Phase Shift Specification: Phase Shift specification allows the user to specify 0 degrees or 90 degrees phase shift.

Figure 3-19: iCE40 PLL - Additional Delay and Phase Shift Options

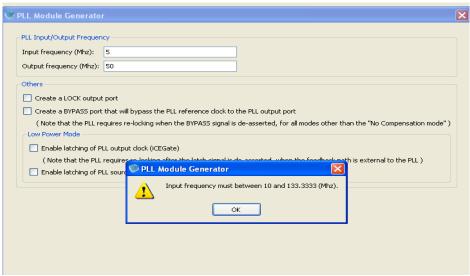

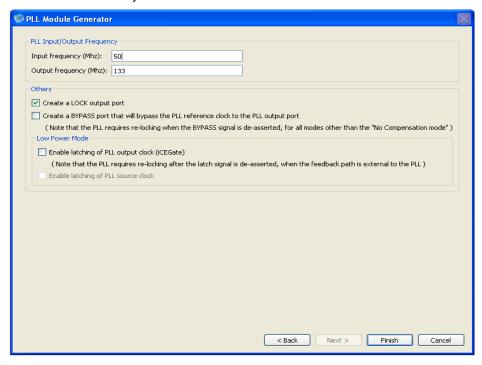

**Frequency Specification:** The input and output frequency of the PLL should be specified in MHz as shown in Figure 3-20. Depending on the values provided by the user, the PLL is internally configured to generate the specified output frequency.

Frequency Specification window also checks for the input and output frequencies given by the user. If the specified frequencies are at a range that cannot be generated by the PLL, then a popup dialog box is displayed as shown in Figure 3-17 asking the user to enter the frequencies in valid range.

**LOCK:** A Lock signal is provided to indicate that the PLL has locked on to the incoming signal. Lock asserts High to indicate that the PLL has achieved frequency lock with a good phase lock.

**BYPASS**: A BYPASS signal is provided which both powers-down the PLL core and bypasses it such that the PLL output tracks the input reference frequency.

**Low Power Mode:** A control is provided to dynamically put the PLL into a Lower Power Mode through the iCEGate feature. The iCEGate feature latches the PLL Output signal, and prevents unnecessary toggling.

The RESET (Active Low) port is always generated, and an explicit PLL reset operation is required to initialize the PLL functionality.

Figure 3-20: iCE40 PLL - Frequency Specification

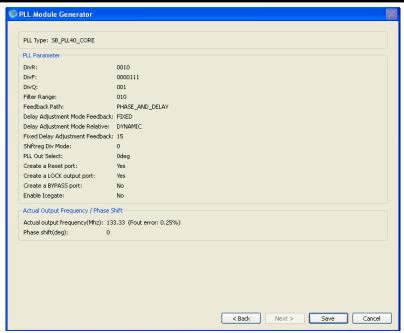

**PLL Summary:** The PLL Configuration summary is shown in Figure 3-21. Click on "Save" to save the PLL configuration file.

Figure 3-21: PLL Summary

## **PLL Dynamic Reconfiguration**

iCE5LP devices supports dynamic reconfiguration of PLL to change the output frequency, phase shift and clock delays at runtime. Reconfiguration of PLL directly accesses the configuration bits and changes the configuration on the fly while the design is running. This allows the user to run the design at different frequencies.

To enable dynamic PLL reconfiguration, user needs to set the TEST\_MODE parameter of the PLL instance. Reconfiguration of PLL is done using the serial data input pin SDI. The configuration bits are latched in a 27 bit shift register (PLLCFGREG) in the PLL block by configuration clock SCLK.

The user can reconfigure the PLL either by using a build in configuration load module or by using external control signals connected to the device.

#### **PLL Reconfiguration Process**

- 1. Assert the PLL RESET (Active low) signal.

- Load the serial configuration bits via SDI pin. The data should be available at positive edge of SCLK and the data is latched at negative edge of SCLK. The shift out bit is available in SDO pin.

- 3. After 27 clock cycles stop the configuration clock signal. The recommended configuration clock frequency range is 2 MHz to 12 MHz.

- 4. At the end of 27 clock cycles, the PLLCFGREG is loaded with 27 bit configuration bit. The first data shifted in is available at PLLCFGREG [26].

- 5. De-assert the RESET signal after 10ns.

- 6. Wait for the PLL to lock.

Dynamic configuration PLL instance model is given below. If the TEST\_MODE is set, the PLL output frequency is based on the PLLCFGREG settings.

Verilog:

```

SB_PLL40_PAD instSBPLL (

.PACKAGEPIN (REFCLK),

.EXTFEEDBACK (),

.DYNAMICDELAY (),

.BYPASS (BYPASS),

.RESETB (RESETB),

.LATCHINPUTVALUE (LATCHINPUTVALUE),

.LOCK (LOCK),

// serial data in

.SDI(SDI),

.SDO(SDO),

// serial data out

.SCLK(SCLK),

// Configuration clock

.PLLOUTCORE (PLLOUTCORE_net),

.PLLOUTGLOBAL (PLLOUTGLOBAL_net)

// INPUT Fin=20MHz, Fout=200MHz

defparam instSBPLL.DIVR = 4'b0001;

defparam instSBPLL.DIVF = 7'b1001111;

defparam instSBPLL.DIVQ = 3'b010;

defparam instSBPLL.FILTER_RANGE = 3'b001;

defparam instSBPLL.FEEDBACK_PATH = "SIMPLE";

defparam instSBPLL.DELAY_ADJUSTMENT_MODE_FEEDBACK= "FIXED";

defparam instSBPLL.FDA_RELATIVE = 4'b0000;

defparam instSBPLL.PLLOUT_SELECT = "GENCLK";

defparam instSBPLL.SHIFTREG_DIV_MODE = 2'b00;

defparam instSBPLL.ENABLE_ICEGATE = 1;

// Enable Dynamic PLL configuration

defparam instSBPLL.TEST_MODE = 1;

```

#### **PLL Configuration Register Mapping**

The following table maps the PLL configuration register bits to PLL parameter settings.

| Configuration<br>Register | PLL Parameter Map | Range/Values | Description                   |

|---------------------------|-------------------|--------------|-------------------------------|

| PLLCFGREG[3:0]            | DIVR              | 0,1,2,15     | REFERENCECLK<br>divider value |

| PLLCFGREG[10:4]           | DIVF              | 0,1,,63      | Feedback divider value        |

| PLLCFGREG[13:11]          | DIVQ              | 1,2,,6       | VCO Divider                   |

| PLLCFGREG[16:14]          | FILTER_RANGE      | 0,1,,7       | PLL Filter Range              |

| PLLCFGREG[25,18,17] | FEEDBACK_PATH                            | 1xx     | SIMPLE Feedback<br>(Internal) |

|---------------------|------------------------------------------|---------|-------------------------------|

|                     |                                          | 000     | DELAY                         |

|                     |                                          | 010/001 | PHASE_AND_DELAY               |

|                     |                                          | 011     | EXTERNAL                      |

| PLLCFGREG[26,21]    | SHIFTREG_DIV_MODE                        | 00      | Divide by 4                   |

|                     |                                          | 01      | Divide by 7                   |

|                     |                                          | 10      | Invalid setting               |

|                     |                                          | 11      | Divide by 5                   |

| PLLCFGREG[20:19],   | PLLOUT_SELECT_PORTB, PLLOUT_SELECT_PORTA | 00      | GENCLK                        |

| PLLCFGREG[24:23]    |                                          | 01      | GENCLK_HALF                   |

|                     |                                          | 10      | SHIFTREG_90deg                |

|                     |                                          | 11      | SHIFTREG_0deg                 |

| PLLCFGREG[22]       | Set PLL Primitive type.                  | 0       | CORE PLL                      |

|                     |                                          | 1       | PAD PLL                       |

The sample configuration register setting for a PAD PLL with 20 MHz reference clock and 200 MHz output frequency is

PLLCFGREG [26:0] =27'b0\_1\_00\_00\_00\_00\_001\_010\_1001111\_0001;

## SPI/I2C Module Generator

iCE40LM, iCE5LP (iCE40 Ultra) device families contains hardened I2C and SPI IP blocks. These devices do not pre-load the hard IP registers during configuration. A soft IP is required to configure the I2C/SPI hard IP blocks in the design.

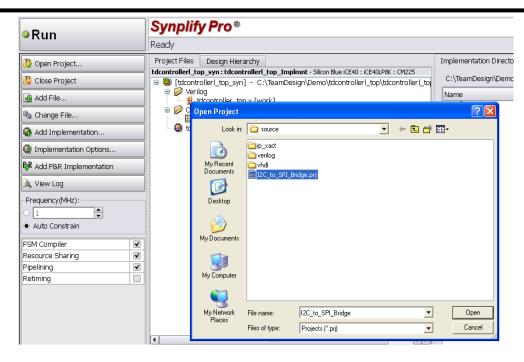

The iCEcube2 Project Flow Manager includes an I2C/SPI Module Generator to generate soft IP modules. Launch the module generator from **Tool > Configure > Configure SPI/I2C Module** menu item, as shown in Figure 3-22.

Figure 3-22 : Launch I2C/SPI Module Generator.

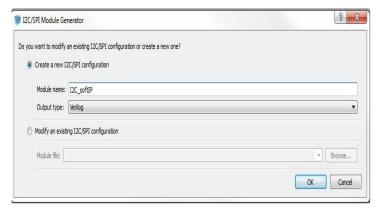

The I2C/SPI Module Generator allows the user to create a new configuration, or edit an existing one as shown in Figure 3-23.

Figure 3-23: Create New I2C/SPI Module

The output of the Module Generator is a module file (Verilog), that instantiates a SPI/I2C, as configured by the user. Note that the I2C/SPI module file should be included in the list of design files.

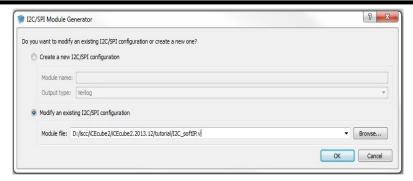

Once an I2C/SPI module file has been generated, it can be edited, by selecting the "Modify an existing PLL configuration" option (Figure 3-24).

Figure 3-24: Modify Existing I2C/SPI configuration

# Configuring I2C/SPI Hard IP

iCE40LM, iCE5LP (iCE40 Ultra) device contains two I2C and SPI hard IP blocks, each of which can be configured independently.

In the I2C/SPI Module Generator wizard, select "Create a new I2C/SPI configuration" and provide the module Name. Click on the OK button. The Module generator launches a wizard to help the user configure the I2C/SPI as per the design requirements. This section explains the options in the wizard to enable and configure the I2C/SPI soft IP wrappers.

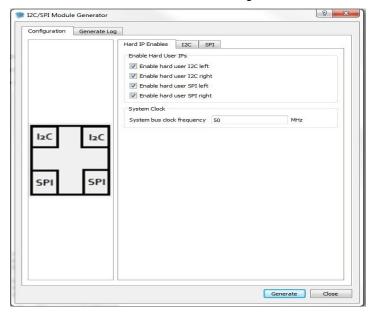

#### **Enable Hard IP**

The 'Hard IP Enables' tab allows the user to enable the required left/right I2C, left/right SPI instances in the wrapper and specify the system bus clock frequency. Selecting the hard IP type enables the I2C and SPI Tabs in the wizard as shown in Figure 3-25.

Figure 3-25: Enable Hard IP

**Enable hard user I2C left:** This option allows the user to enable left I2C on the I2C Tab.

Enable hard user I2C Right: This option allows the user to enable right I2C on the I2C Tab.

Enable hard user SPI Left: This option allows the user to enable left SPI on the SPI Tab.

Enable hard user SPI Right: This option allows the user to enable right SPI on the SPI Tab.

**System Clock:** Specify the system clock frequency in Mhz. This value is used to derive the divider settings of the I2C and SPI hard IP master clocks. "Generate" button is enabled once the value is set in this field.

#### **Configure I2C**

I2C Tab allows the user to configure the left and right I2C blocks independently as shown in Figure 3-26. I2C Tab is enabled only when I2C hard IP is selected in the Hard IP Enables Tab.

Figure 3-26: Configure Left/Right I2C hard IP.

## **I2C Controller General Options:**

**General Call Enable**: This setting enables the I2C General Call response (addresses all devices on the bus using the I2C address 0) in Slave mode. This setting can be modified dynamically by enabling the GCEN bit in the I2C Control Register I2CCR1.

**Wakeup Enable:** Turns on the I2C wakeup on address match. The WKUPEN bit in the I2CCR1 can be modified dynamically allowing the Wake Up function to be enabled or disabled.

**Include IO Buffers:** Include buffers to the I2C\_SCL, I2C\_SDA pins.

**Master Clock (Desired)**: Specify the desired I2C master clock frequency. A calculation is then made to determine a divider value to generate a clock close to this value from the input clock. The frequency of the input System Bus clock is specified on the main/general tab. The divider value is rounded to the nearest integer after dividing the input System Bus clock by the value entered in this field.

**Master Clock (Actual)**: Since it is not always possible to divide the input System Bus clock to the exact value requested by the user, the actual value will be returned in this read-only field.

**I2C Addressing**: This option allows the user to set 7-bit or 10-bit addressing and define the Hard I2C address.

#### **I2C Controller Interrupts:**

**Arbitration Lost Interrupts:** An interrupt which indicates I2C lost arbitration. This interrupt is bit IRQARBL of the register I2CIRQ. When enabled, it indicates that ARBL is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQARBLEN in the register I2CIRQEN.

**TX/RX Ready:** An interrupt which indicates that the I2C transmit data register (I2CTXDR) is empty or that the receive data register (I2CRXDR) is full. The interrupt bit is IRQTRRDY of the register I2CIRQ. When enabled, it indicates that TRRDY is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQTRRDYEN in the register I2CIRQEN.

**Overrun or NACK:** An interrupt which indicates that the I2CRXDR received new data before the previous data. The interrupt is bit IRQROE of the register I2CIRQ. When enabled, it indicates that ROE is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQROEEN in the register I2CIRQEN.

**General Call Interrupts:** An interrupt which indicates that a general call has occurred. The interrupt is bit IRQHGC of the register I2CIRQ. When enabled, it indicates that ROE is asserted. Writing a '1' to this bit clears the interrupt. This option can be changed dynamically by modifying the bit IRQHGCEN in the register I2CIRQEN.

#### I2C SDA delays

This option is available only for iCE5LP (iCE40 Ultra) devices. Using these options, the user can add 50ns delay to the SDA input, output signals.

**SDA input**: By default 50ns is added to the SDA input. Turn off this option if delay is not required. **SDA output**: Turn on this setting to add 50ns delay to the SDA output.

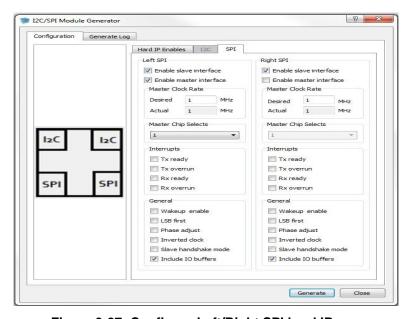

#### **Configure SPI**

SPI Tab allows the user to configure the left and right SPI blocks independently as shown in Figure 3-27. SPI Tab is enabled only when SPI hard IP is selected in the Hard IP Enables Tab.

Figure 3-27: Configure Left/Right SPI hard IP.

**Enable Slave Interface:** This option allows the user to enable Slave Mode interface for the initial state of the SPI block. By default, Slave Mode interface is enabled.

**Enable Master Interface:** This option allows the user to enable Master Mode interface for the initial state of the SPI block. This option can be updated dynamically by modifying the MSTR bit of the register SPICR2.

**Master Clock Rate (Desired):** Specify the desired SPI master clock frequency. A calculation is then made to determine a divider value to generate a clock close to this value from the input System Bus clock frequency. The divider value is rounded to the nearest integer after dividing the input System Bus clock by the value entered in this field.

**Master Clock Rate (Actual):** Since it is not always possible to divide the input System Bus clock exactly to that requested by the user, the actual value will be returned in this read-only field. When both the desired SPI clock and System Bus clock fields have valid data and either is updated, this field returns the value (System Bus Frequency / SPI\_CLK\_DIVIDER), rounded to two decimal places.

**Master Chip Selects:** The core has the ability to provide up to 4 individual chip select outputs for master operation. This field allows the user to prevent extra chip selects from being brought out of the core. This option can be updated dynamically by modifying the register SPICSR.

#### **SPI Controller Interrupts**

**TX Ready:** An interrupt which indicates the SPI transmit data register (SPITXDR) is empty. The interrupt bit is IRQTRDY of the register SPIIRQ. When enabled, indicates TRDY was asserted. Write "1" to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQTRDYEN in the register SPIIRQEN.

**TX Overrun:** An interrupt which indicates the Slave SPI chip select (SPI\_SCSN) was driven low while a SPI Master. The interrupt is bit IRQMDF of the register SPIIRQ. When enabled, indicates MDF (Mode Fault) was asserted. Write "1" to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQMDFEN in the register SPIIRQEN.

**RX Ready:** An interrupt which indicates the receive data register (SPIRXDR) contains valid receive data. The interrupt is bit IRQRRDY of the register SPIIRQ. When enabled, indicates RRDY was asserted. Write "1" to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQRRDYEN in the register SPICSR.

**RX Overrun:** An interrupt which indicates SPIRXDR received new data before the previous data. The interrupt is bit IRQROE of the register SPIIRQ. When enabled, indicates ROE was asserted. Write a "1" to this bit to clear the interrupt. This option can be change dynamically by modifying the bit IRQROEEN in the register SPIIRQEN.

#### **SPI Controller General Options:**

**Wakeup Enable:** The core can optionally provide a wakeup signal to the device to resume from low power mode. This option can be updated dynamically by modifying the bit WKUPEN\_USER in the register SPICR1.

**LSB First:** This setting specifies the order of the serial shift of a byte of data. The data order (MSB or LSB first) is programmable within the SPI core. This option can be updated dynamically by modifying the LSBF bit in the register SPICR2.

**Inverted Clock:** Select this option to invert the clock polarity used to sample input and output data. When selected the edge changes from the rising to the falling clock edge. This option can be updated dynamically by accessing the CPOL bit of register SPICR2.

**Phase Adjust:** An alternate clock-data relationship is available for SPI devices with particular requirements. This option allows the user to specify a phase change to match the application. This option can be updated dynamically by accessing the CPHA bit in the register SPICR2.

**Slave Handshake Mode:** Enables Lattice proprietary extension to the SPI protocol. For use when the internal sup-port circuit (e.g. WISHBONE host) cannot respond with initial data within the time required, and to make the Slave read out data predictably available at high SPI clock rates. This option can be updated dynamically by accessing the SDBRE bit in the register SPICR2.

**Include IO Buffers:** Include buffers to the SPI\_MISO, SPI\_MOSI, SPI\_SCK, SPI\_MCSNO [0] pins.

#### **Generate Module**

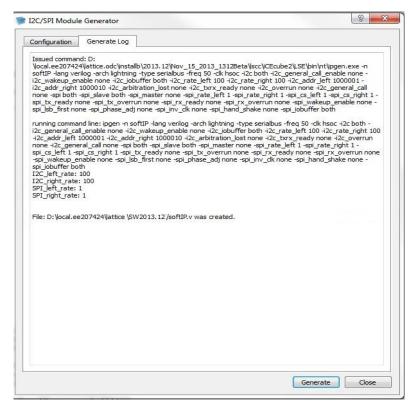

Once the settings are done generate the soft IP module by selecting "Generate" button. The wizard displays the status and the generated file details in the "Generate Log" tab as shown in Figure 3-28.

Figure 3-28: I2C/SPI soft IP module generation.

# Chapter 4 Lattice Synthesis Engine

Lattice Synthesis Engine (LSE) is the integrated synthesis tool that comes with iCEcube2.

This chapter describes:

- LSE tool options

- · HDL coding tips

- · Attributes and directives supported by LSE

- Synopsys design constraints (SDC) supported by LSE

LSE is a synthesis tool custom-built for Lattice products and fully integrated with iCEcube2. Depending on the design, LSE may lead to a more compact or faster placement of the design than another synthesis tool would do.

Also, LSE offers the following advantages:

- More granular control through the tool options

- Enhanced RAM and ROM inference and mapping, including:

- Dual-port RAM in write-through, normal, and read-before-write modes mapped to BRAM

- Clock enable and read enable packing

- Mapping for the minimal number of BRAM blocks

- BRAM mapping for minimal timing

- Post-synthesis Verilog netlist suitable for simulation

# **Changing the LSE Tool Options**

The LSE options can be changed by selecting **Tool > Tool Options > LSE**. This section lists all the tool options associated with LSE. The following sections describe how to set the options to optimize synthesis for either area or speed and some of the differences between LSE and Synplify Pro options.

#### **BRAM Utilization**

Specifies BRAM utilization target setting in percent of total vacant sites. LSE will honor the setting and do the resource computation accordingly. Default is 100 (in percentage).

#### Carry Chain Length

Specifies the maximum number of output bits that get mapped to a single carry chain. Default is 0, which is interpreted as infinite length.

#### **Command Line Options**

Enables additional command line options for the LSE synthesis process. Type in the option and its value (if any) in the Value column.

#### **Fix Gated Clocks**

Turns on (True) or off (False) converting all gated clocks to data enables for best performance. Turn off to save power. Default is True.

## FSM Encoding Style

Specifies the encoding style to use for finite state machines: Binary, Gray, or One-Hot. Default is Auto, meaning that LSE chooses a style for each finite state machine.

## Intermediate File Dump

If you set this to True, LSE will dump about 20 intermediate encrypted Verilog files. If you supply Lattice with these files, they can be decrypted and analyzed for problems. This option is good for analyzing simulation issues.

#### **Max Fanout Limit**

Specifies the maximum fanout setting. LSE will make sure that any net in the design does not exceed this limit. Default is 10000 fanouts.

## **Memory Initial Value File Search Path**

Allows you to specify a path to locate memory initialization files (.mem) used in the design. The software will add the specified paths to the list of directories to search when resolving file references.

To specify a search path, double-click the Value box, and directly enter the path.

#### **Number of Critical Paths**

Specifies the number of critical timing paths to be reported in the timing report.

## **Optimization Goal**

Enables LSE to optimize the design for area, speed, or both. Valid options are:

- Area (default) Optimizes the design for area by reducing the total amount of logic used for design implementation.

- When Optimization Goal is set to Area, LSE ignores the Target Frequency setting and uses 1 MHz instead.

- Timing Optimizes the design for speed by reducing the levels of logic.

- When Optimization Goal is set to Timing and a create\_clock constraint is available in an .ldc file, LSE ignores the Target Frequency setting and uses the value from the create clock constraint instead.

- Balanced Optimizes the design for both area and timing.

#### **Propagate Constants**

When set to True (default), enables constant propagation to reduce area, where possible. LSE will then eliminate the logic used when constant inputs to logic cause their outputs to be constant. You can turn off the operation by setting this option to False.

## RAM Style

Sets the type of random access memory globally to BRAM or registers.

The default is Auto which attempts to determine the best implementation. That is, LSE will map to RAM resources based on the resource availability.

This option will apply a syn\_ramstyle attribute globally in the source to a module or to a RAM instance. To turn off RAM inference, set its value to Registers.

#### Other options are:

- Registers Causes an inferred RAM to be mapped to registers (flip-flops and logic) rather than the technology-specific RAM resources.

- BRAM Causes the RAM to be implemented using the dedicated RAM resources. If your RAM resources are limited, for whatever reason, you can map additional RAMs to registers instead of the dedicated BRAM resources using this attribute.

## Remove Duplicate Registers

Specifies the removal of duplicate registers. When set to True (default), LSE removes a register if it is identical to another register. If two registers generate the same logic, the second one will be deleted and the first one will be made to fan out to the second one's destinations. LSE will not remove duplicate registers if this option is set to False.

#### **Resolve Mixed Drivers**

If a net is driven by a VCC or GND and active drivers, setting this option to True connects the net to the VCC or GND driver.

## **Resource Sharing**

When this is set to True (default), the synthesis tool uses resource sharing techniques to optimize for area. With resource sharing, synthesis uses the same arithmetic operators for mutually exclusive statements; for example, with the branches of a case statement. Conversely, you can improve timing by disabling resource sharing, but at the expense of increased area.

## **ROM Style**

Allows you to globally implement ROM architectures using dedicated, distributed ROM, or a combination of the two (Auto).

This applies the syn\_romstyle attribute globally to the design by adding the attribute to the module or entity. You can also specify this attribute on a single module or ROM instance.

This option specifies a syn\_romstyle attribute globally or on a module or ROM instance with a value of:

- Auto (default) Allows the synthesis tool to choose the best implementation to meet the design requirements for speed, size, and so on.

- BRAM Causes the ROM to be mapped to dedicated BRAM resources. ROM address or data should be registered to map it to an BRAM block. If your ROM resources are limited, for whatever reason, you can map additional ROM to registers instead of the dedicated or distributed RAM resources using this attribute.

- Logic Causes the ROM to be implemented using the normal logic.

Infer ROM architectures using a CASE statement in your code. For the synthesis tool to implement a ROM, at least half of the available addresses in the CASE statement must be assigned a value. For example, consider a ROM with six address bits (64 unique addresses). The CASE statement for this ROM must specify values for at least 32 of the available addresses.

#### **RW Check on RAM**

Adds (True) or does not add (False) the glue logic to resolve read/write conflicts wherever needed. Default is False.

## **Target Frequency**

Specifies the target frequency setting. This frequency applies to all the clocks in the design. If there are some clocks defined in an .sdc file, the remaining clocks will get this frequency setting.

When Optimization Goal is set to Area, LSE ignores the Target Frequency setting and uses 1 MHz instead.

When Optimization Goal is set to Timing and a create\_clock constraint is available in an .sdc file, LSE ignores the Target Frequency setting and uses the value from the create\_clock constraint instead.

## **Top-Level Unit**

It is a good practice to specify the top-level unit (or module) of the design. If you don't, LSE will try to determine the top-level unit. While usually accurate, there is no guarantee that LSE will get the correct unit.

You may also want to change the top-level unit when experimenting with different designs or switching between simulation and synthesis.

If the design is mix of EDIF and Verilog or VHDL, you cannot set an EDIF module as the top-level unit.

## **Use Carry Chain**

Turns on (True) or off (False) carry chain implementation for adders. Default is True. This option is equivalent to the "-use\_carry\_chain" command in LSE.

#### **Use IO Insertion**

Turns on (True) or off (False) the use of I/O insertion. Default is True.

#### **Use IO Registers**

Enables (True) or disables (False) register packing. True forces the synthesis tool to pack all input, output, and I/O registers into I/O pad cells based on timing requirements. Default is Auto, which selects True or False based on how Optimization Goal is set.

You can place the syn\_useioff attribute on an individual register or port. When applied to a register, the synthesis tool packs the register into the pad cell, and when applied to a port, packs all registers attached to the port into the pad cell. The syn\_useioff attribute can be set on a:

- Top-level port

- Register driving the top-level port

- Lower-level port if the register is specified as part of the port declaration

## Optimizing LSE for Area and Speed

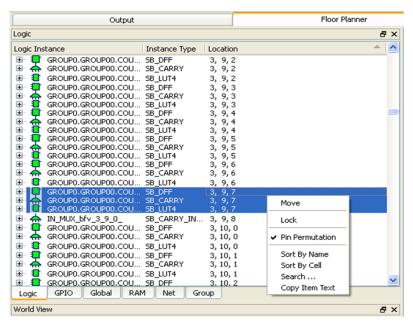

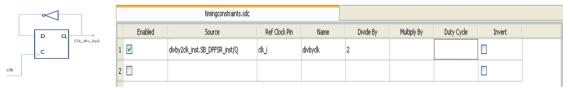

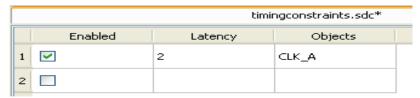

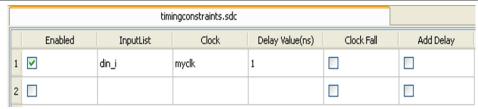

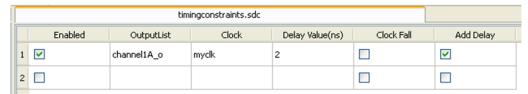

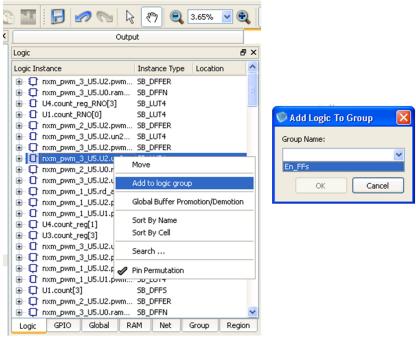

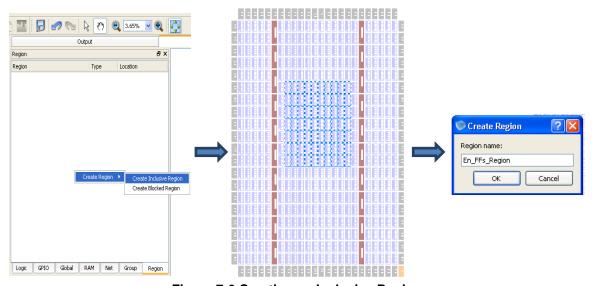

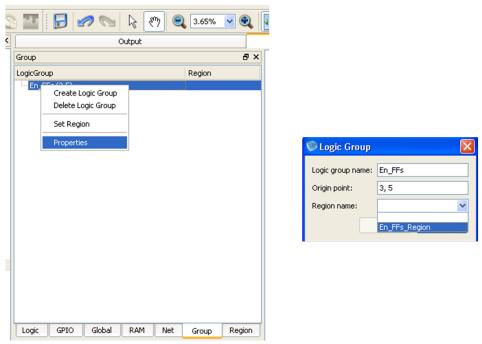

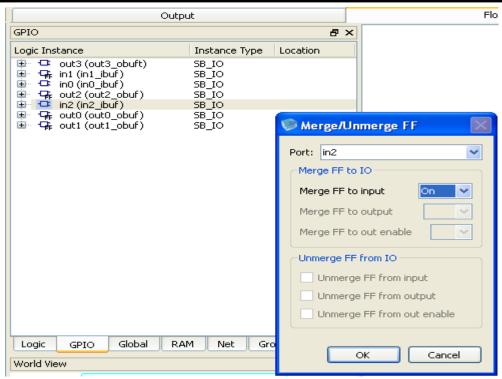

The following strategy settings for LSE can help reduce the amount of FPGA resources that your design requires or increase the speed with which it runs. (For other synthesis tools, see those tools' documentation.) Use these methods along with other, generic coding methods to optimize your design.