**RTL8187SE**

# SINGLE-CHIP WIRELESS LAN NETWORK INTERFACE CONTROLLER w/PCI EXPRESS INTERFACE

# DATASHEET

Rev. 1.0 16 January 2008 Track ID: JATR-1076-21

DRAF1

#### Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan Tel.: +886-3-578-0211. Fax: +886-3-577-6047 www.realtek.com.tw

#### COPYRIGHT

©2008 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any langµAge in any form or by any means without the written permission of Realtek Semiconductor Corp.

#### DISCLAIMER

Realtek provides this document "as is", without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

#### TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### CONFIDENTIALITY

This document is confidential and should not be provided to a third-party without the permission of Realtek Semiconductor Corporation.

#### **USING THIS DOCUMENT**

This document is intended for the software engineer's reference and provides detailed programming information.

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.

#### **REVISION HISTORY**

| Revision Release Date S |            | Summary        |  |  |  |

|-------------------------|------------|----------------|--|--|--|

| 1.0                     | 2008/01/16 | First release. |  |  |  |

ii

# **Table of Contents**

| 1.  | G     | ENER           | RAL DESCRIPTION                                                                        | 1                |

|-----|-------|----------------|----------------------------------------------------------------------------------------|------------------|

| 2.  |       |                | JRES                                                                                   |                  |

| 3.  | SY    | YSTEN          | M APPLICATIONS                                                                         | 4                |

| 4.  | Bl    | LOCK           | K DIAGRAMS                                                                             | 5                |

| 5.  | PI    |                | SIGNMENTS                                                                              | 7                |

|     |       |                |                                                                                        |                  |

|     | 5.1.  |                | CKAGE IDENTIFICATION                                                                   |                  |

| 6.  | PI    | IN DE          | ESCRIPTIONS                                                                            | 8                |

|     | 6.1.  | Pov            | WER MANAGEMENT/ISOLATION INTERFACE                                                     | 8                |

|     | 6.2.  | PCI            | I Express Interface                                                                    | 8                |

|     | 6.3.  | EEI            | PROM INTERFACE                                                                         | 9                |

|     | 6.4.  | Pov            | WER PINS                                                                               | 9                |

|     | 6.5.  |                | D INTERFACE                                                                            |                  |

|     | 6.6.  |                | SEBAND AND RF PINS                                                                     |                  |

|     | 6.7.  |                | UETOOTH CO-EXISTENCE PINS                                                              |                  |

|     | 6.8.  | CLC            | OCK AND OTHER PINS                                                                     | 11               |

| 7.  | El    | EPRO           | DM (93C46 OR 93C56) CONTENTS                                                           |                  |

|     |       |                |                                                                                        |                  |

| 8.  | PO    | CI EXI         | XPRESS <sup>TM</sup>                                                                   | 12               |

|     | 8.1.  | PCI            | I EXPRESS BUS INTERFACE                                                                | 12               |

|     |       | 1.1.           | PCI Express Transmitter                                                                |                  |

|     |       | 1.2.           | PCI Express Receiver                                                                   |                  |

|     | 8.2.  |                | I CONFIGURATION SPACE TABLE                                                            |                  |

|     | 8.3.  |                | I CONFIGURATION SPACE FUNCTIONS                                                        |                  |

|     | 8.4.  |                | I CONFIGURATION SPACE STATUS                                                           |                  |

|     | 8.    | 4.1.           | Status                                                                                 | 17               |

|     | 8.    | 4.2.           | RIDR (Revision ID Register)                                                            |                  |

|     | 8.    | 4.3.           | PIFR (Programming Interface Register)                                                  |                  |

|     |       | 4.4.           | SCR (Sub-Class Register)                                                               |                  |

|     |       | 4.5.           | BCR (Base-Class Register)                                                              |                  |

|     |       | 4.6.           | CLS (Cache Line Size)                                                                  |                  |

|     |       | 4.7.           | LTR (Latency Timer Register)                                                           |                  |

|     |       | 4.8.           | HTR (Header Type Register)                                                             |                  |

|     |       | 4.9.           | BIST (Built-In Self-Test)<br>IOAR (Input Output Address Register)                      |                  |

|     |       | 4.10.<br>4.11. | IOAR (Input Output Address Register)                                                   | 19               |

|     |       | 4.11.<br>4.12. | MEMAR (Memory Address Register)<br>CISPtr (CardBus Card Information Structure Pointer) |                  |

|     |       | 4.12.<br>4.13. | SVID (Subsystem Vendor ID)                                                             |                  |

|     |       | 4.13.<br>4.14. | SVID (Subsystem Vendor ID)                                                             |                  |

|     |       | 4.14.<br>4.15. | ILR (Interrupt Line Register)                                                          |                  |

|     |       | 4.1 <i>6</i> . | IPR (Interrupt Pin Register)                                                           |                  |

|     |       | <i>4.17</i> .  | MNGNT (Minimum Grant Timer: Read only)                                                 |                  |

|     |       | 4.18.          | MXLAT (Maximum Latency Timer: Read only)                                               |                  |

|     | 8.5.  |                | FAULT VALUE AFTER POWER-ON (RSTB ASSERTED)                                             |                  |

|     |       |                |                                                                                        |                  |

| Sir | ngle- | -Chip I        | Wireless LAN Network Interface Controller iii Track ID: JATR-J                         | 1076-21 Rev. 1.0 |

Track ID: JATR-1076-21 Rev. 1.0

| 8.6. PCI Power Management Functions                                 |    |

|---------------------------------------------------------------------|----|

| 8.7. Message Signaled Interrupt (MSI)                               |    |

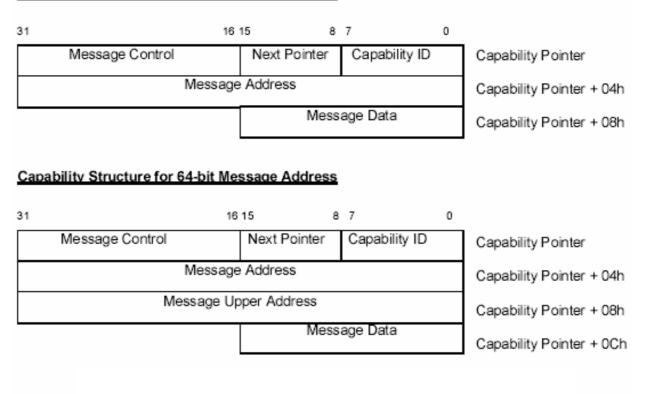

| 8.7.1. MSI Capability Structure in PCI Configuration Space          |    |

| 8.7.2. Message Control                                              |    |

| 8.7.3. Message Address                                              |    |

| 8.7.4. Message Upper Address                                        |    |

| 8.7.5. Message Data                                                 |    |

| 9. FUNCTIONAL DESCRIPTION                                           |    |

| 9.1.1. Transmit                                                     |    |

| 9.1.2. Receive                                                      |    |

| 9.2. LOOPBACK OPERATION                                             |    |

| 9.3. QOS FUNCTIONS                                                  |    |

| 9.4. LED FUNCTIONS                                                  |    |

| 10. APPLICATION DIAGRAM                                             | 40 |

| 11. ELECTRICAL CHARACTERISTICS                                      | 41 |

| 11.1. Temperature Limit Ratings                                     | 41 |

| 11.2. DC CHARACTERISTICS                                            | 41 |

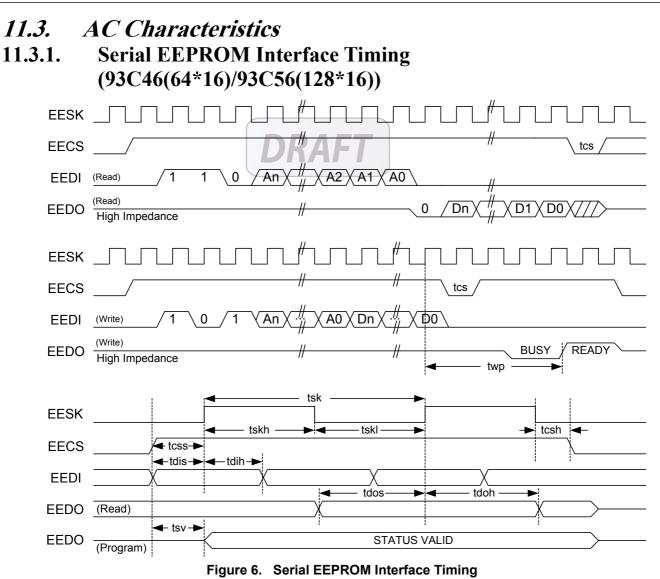

| 11.3. AC CHARACTERISTICS                                            | 42 |

| 11.3.1. Serial EEPROM Interface Timing (93C46(64*16)/93C56(128*16)) |    |

| 11.4. PCI Express Bus Parameters                                    |    |

| 11.4.1. Differential Transmitter Parameters                         |    |

| 11.4.2. Differential Receiver Parameters                            |    |

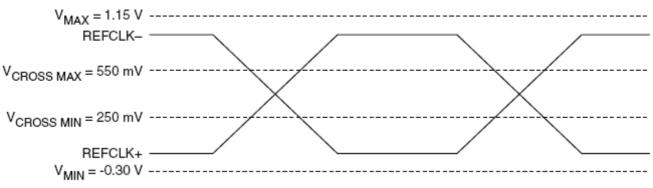

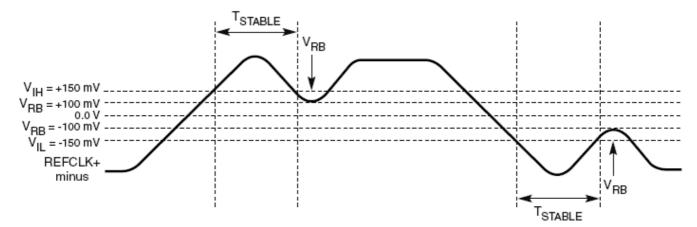

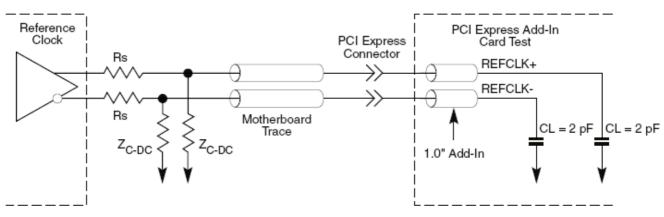

| 11.4.3. REFCLK Parameters                                           |    |

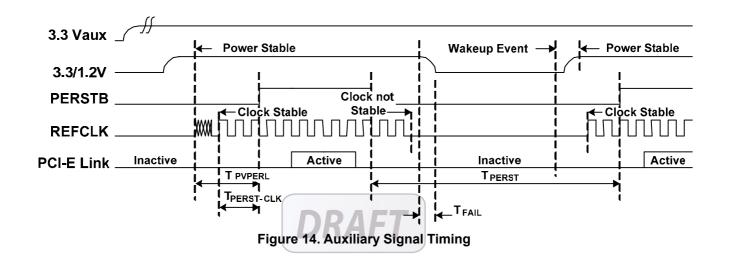

| 11.4.4. Auxiliary Signal Timing Parameters                          |    |

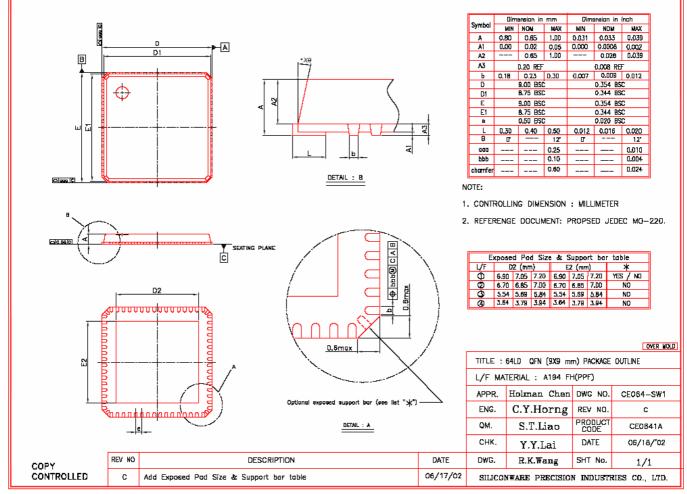

| 12. MECHANICAL DIMENSIONS                                           | 49 |

| 13. ORDERING INFORMATION                                            | 50 |

iv

# List of Tables

| TABLE 1. POWER MANAGEMENT/ISOLATION INTERFACE                                  | 8  |

|--------------------------------------------------------------------------------|----|

| TABLE 2. PCI Express Interface                                                 | 8  |

| TABLE 3. EEPROM INTERFACE                                                      |    |

| TABLE 4. POWER PINS                                                            | 9  |

| TABLE 5.     LED INTERFACE.                                                    |    |

| TABLE 6. BASEBAND AND RF PINS                                                  | 10 |

| TABLE 7. BLUETOOTH CO-EXISTENCE PINS                                           | 11 |

| TABLE 8. CLOCK AND OTHER PINS.                                                 |    |

| TABLE 9. PCI CONFIGURATION SPACE TABLE                                         |    |

| TABLE 10. COMMAND REGISTER IN PCI CONFIGURATION SPACE                          |    |

| TABLE 11. PCI CONFIGURATION SPACE STATUS                                       |    |

| TABLE 12. INPUT OUTPUT ADDRESS REGISTER                                        |    |

| TABLE 13. MEMORY ADDRESS REGISTER                                              |    |

| TABLE 14. PCI CONFIGURATION SPACE TABLE                                        |    |

| TABLE 15. MESSAGE CONTROL                                                      |    |

| TABLE 16. MESSAGE ADDRESS                                                      |    |

| TABLE 17. MESSAGE UPPER ADDRESS                                                |    |

| TABLE 18. MESSAGE DATA                                                         |    |

| TABLE 19. TX DESCRIPTOR FORMAT (BEFORE TRANSMITTING, OWN=1, TX COMMAND MODE 1) |    |

| TABLE 20. TX STATUS DESCRIPTOR                                                 |    |

| TABLE 21. TX STATUS DESCRIPTOR (AFTER TRANSMITTING, OWN=0, TX STATUS MODE)     |    |

| TABLE 22. TX STATUS DESCRIPTOR (AFTER TRANSMITTING, OWN=0, TX STATUS MODE)     |    |

| TABLE 23. RX COMMAND DESCRIPTOR (OWN=1)                                        |    |

| TABLE 24. RX COMMAND DESCRIPTOR (OWN=1)                                        |    |

| TABLE 25. RX STATUS DESCRIPTOR (OWN=0)                                         |    |

| TABLE 26. RX STATUS DESCRIPTOR.                                                |    |

| TABLE 27. TEMPERATURE LIMIT RATINGS                                            |    |

| TABLE 28. DC CHARACTERISTICS                                                   |    |

| TABLE 29. EEPROM ACCESS TIMING PARAMETERS                                      |    |

| TABLE 30. DIFFERENTIAL TRANSMITTER PARAMETERS                                  |    |

| TABLE 31. DIFFERENTIAL RECEIVER PARAMETERS.                                    |    |

| TABLE 32. REFCLK PARAMETERS                                                    |    |

| TABLE 33. AUXILIARY SIGNAL TIMING PARAMETERS                                   |    |

| TABLE 34. ORDERING INFORMATION                                                 | 50 |

v

# **List of Figures**

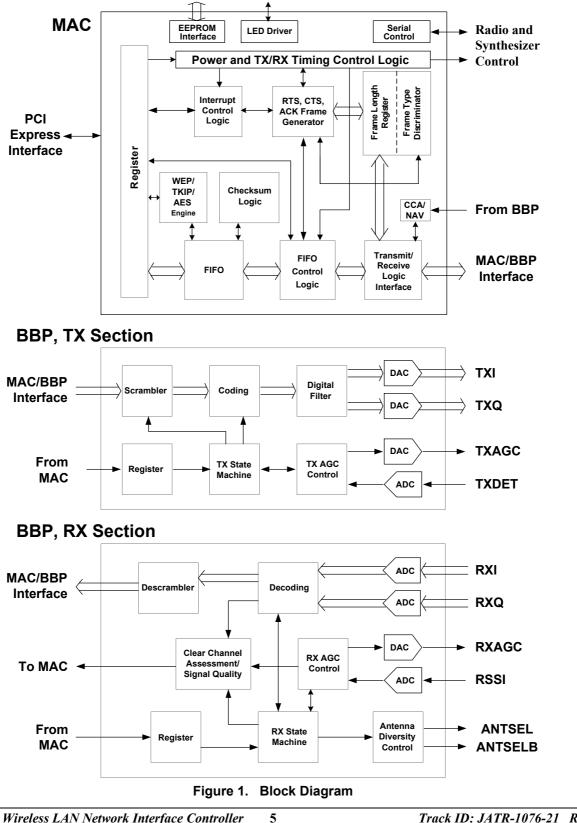

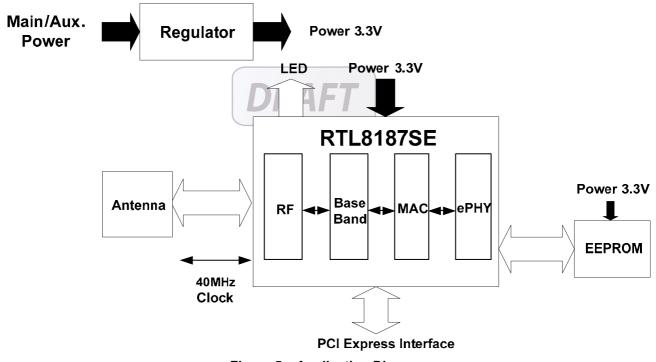

| FIGURE 1. BLOCK DIAGRAM                                                      | 5  |

|------------------------------------------------------------------------------|----|

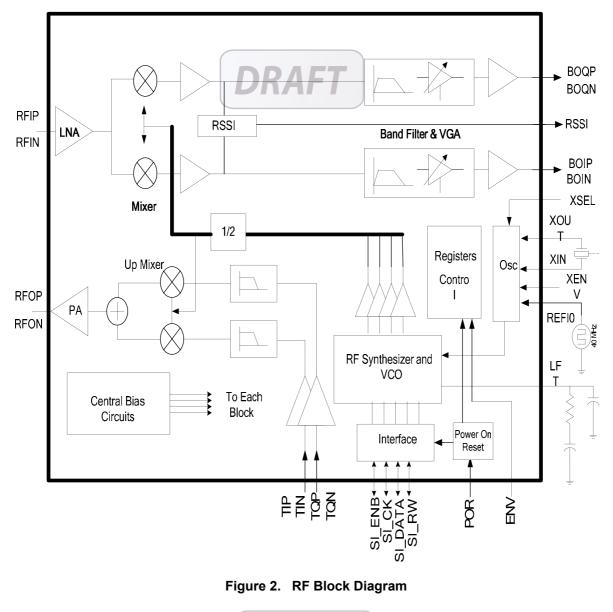

| FIGURE 2. RF BLOCK DIAGRAM                                                   |    |

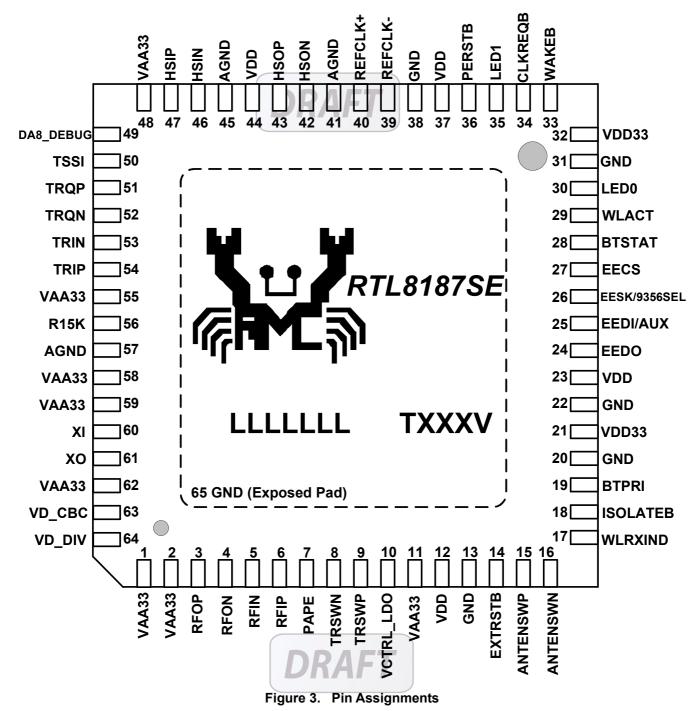

| FIGURE 3. PIN ASSIGNMENTS                                                    | 7  |

| FIGURE 4. MESSAGE CAPABILITY STRUCTURE                                       | 25 |

| FIGURE 5. APPLICATION DIAGRAM                                                |    |

| FIGURE 6. SERIAL EEPROM INTERFACE TIMING                                     | 42 |

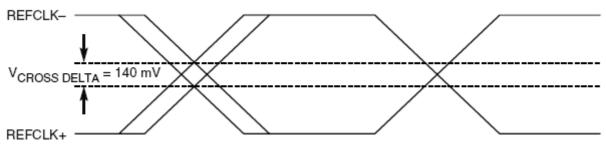

| FIGURE 7. SINGLE-ENDED MEASUREMENT POINTS FOR ABSOLUTE CROSS POINT AND SWING | 46 |

| FIGURE 8. SINGLE-ENDED MEASUREMENT POINTS FOR DELTA CROSS POINT              | 46 |

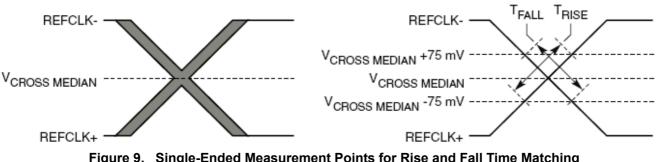

| FIGURE 9. SINGLE-ENDED MEASUREMENT POINTS FOR RISE AND FALL TIME MATCHING    | 46 |

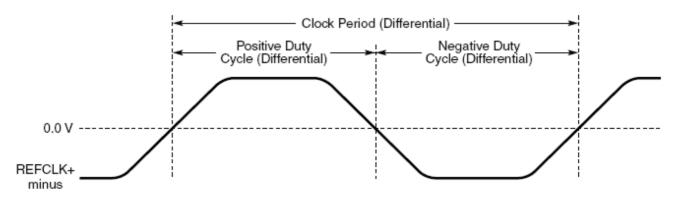

| FIGURE 10. DIFFERENTIAL MEASUREMENT POINTS FOR DUTY CYCLE AND PERIOD         | 47 |

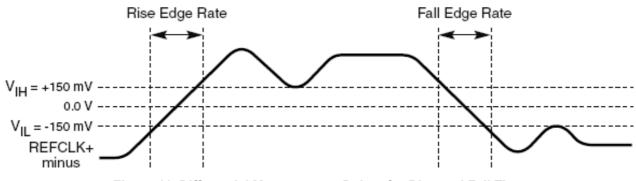

| FIGURE 11. DIFFERENTIAL MEASUREMENT POINTS FOR RISE AND FALL TIME            |    |

| FIGURE 12. DIFFERENTIAL MEASUREMENT POINTS FOR RINGBACK                      | 47 |

| FIGURE 13. REFERENCE CLOCK SYSTEM MEASUREMENT POINT AND LOADING              | 48 |

| FIGURE 14. AUXILIARY SIGNAL TIMING                                           | 48 |

vi

## **1. General Description**

The Realtek RTL8187SE is a low-profile highly integrated cost-effective Single-Chip Wireless LAN network interface controller that integrates a Wireless LAN MAC, a baseband processor, and 2.4GHz RF onto one chip. It provides a PCI Express bus controller, and full compliance with IEEE 802.11 and IEEE 802.11b/g specifications. It also complies with WMM, 802.11e, and CCX specifications.

To reduce protocol overhead, the RTL8187SE supports Short InterFrame Space (SIFS) burst mode to send packets back-to-back. A protection mechanism prevents collisions among 802.11b nodes.

Direct Sequence Spread Spectrum (DSSS), Complementary Code Keying (CCK), and Orthogonal Frequency Division Multiplexing (OFDM) baseband processing are implemented to support all IEEE 802.11b, and 802.11g data rates. Differential phase shift keying modulation schemes, DBPSK and DQPSK with data scrambling capability, are available, along with complementary code keying to provide data rates of 1, 2, 5.5, and 11Mbps, with long or short preamble. A high-speed Fast Fourier Transform (FFT)/Inverse Fast Fourier Transform (IFFT), combined with BPSK, QPSK, 16QAM and 64QAM modulation of the individual sub-carriers, provides data rates of 6, 9, 12, 18, 24, 36, 48 and 54Mbps, with rate-compatible punctured convolutional coding with a coding rate of 1/2, 2/3, and 3/4.

An enhanced signal detector, an adaptive frequency domain equalizer, and a soft-decision Viterbi decoder are built-in to alleviate severe multipath effects. Efficient IQ-imbalance calibration, DC offset, phase noise, frequency offset, and timing offset compensation reduce radio frequency front-end impairments. Selectable digital transmit and receive FIR filters are provided to meet the requirements of transmit spectrum masks, and to reject adjacent channel interference, respectively. Both in the transmitter and receiver, programmable scaling in the digital domain trades the  $q\mu$ Antization noise against the increased probability of clipping. Robust signal detection, symbol boundary detection, and channel estimation perform well at the minimum sensitivity.

The RTL8187SE supports fast receiver Automatic Gain Control (AGC) and antenna diversity functions, and an adaptive transmit power control function to obtain better performance in the analog portions of the transceiver. It also has on-chip digital-to-analog converters and analog-to-digital converters for analog I and Q inputs and outputs, transmit TSSI and receiver RSSI inputs, and transmit and receiver AGC outputs.

It supports Advanced Configuration Power management Interface (ACPI), Legacy PCI power management, and PCI Express power management for modern operating systems that are capable of Operating System directed Power Management (OSPM). PCI MSI (Message Signaled Interrupt) function and PCI Express Device Serial Number Capability are also supported.

In addition to the ACPI feature, the RTL8187SE also supports remote wake-up (including AMD Magic Packet and Microsoft<sup>®</sup> wake-up frame) in both ACPI and APM environments. To support Wake on Wireless LAN from a deep power down state (e.g., D3cold, i.e. main power is off and only auxiliary power exists), the auxiliary power source must be able to provide the needed power. When auxiliary power is applied and the main power remains off, the RTL8187SE is ready and waiting for a Magic Packet or wake-up frame to wake the system up.

The RTL8187SE supports an enhanced link list descriptor-based buffer management architecture, which is an essential part of a design for a modern network interface card. It contributes to lowering CPU utilization. Also, the RTL8187SE features inter-connect PCI Express technology. PCI Express is a high-bandwidth, low pin count, serial, interconnect technology that offers significant improvements in performance over conventional PCI and also maintains software compatibility with existing PCI infrastructure. Support is also provided for Multiple BSSID, Adjustable fallback steps and fallback rates during auto rate fallback, TX Power Tracking, Enhanced three-wire mechanism, Parallel Control Interface between Baseband and RF, and Bluetooth coexistence.

DRAFT

The RTL8187SE keeps network maintenance costs low and eliminates usage barriers. The RTL8187SE is highly integrated and requires no 'glue' logic or external memory.

# 2. Features

64-Pin QFN with 'Green' package

State machine implementation without external memory (RAM, flash) requirement

Complies with IEEE 802.11b/g standards

Supports descriptor-based buffer management

Integrated Wireless LAN MAC and Direct Sequence Spread Spectrum/OFDM Baseband Processor in one chip

Enhanced signal detector, adaptive frequency domain equalizer, and soft-decision Viterbi decoder to alleviate severe multipath effects

Processing Gain compliant with FCC

On-Chip A/D and D/A converters for I/Q Data, AGC, and Adaptive Power Control

Supports both transmit and receive Antenna Diversity

Data rates of 1, 2, 5.5, 6, 9, 11, 12, 18, 24, 36, 48, and 54Mbps

Supports 40MHz OSC as the internal clock source. The frequency deviation of the OSC must be within 25ppm on IEEE 802.11g

PCI Express bus controller

Complies with PCI Express 1.1 and PCI Express Mini Card Electromechanical Specification Revision 1.1

PCI power management Revision 1.2

Supports PCI Express Active State Power Management (ASPM)

3

Provides PCI Express bus data transfers and PCI Express memory space or IO space mapped data transfers of the RTL8187SE's operational registers

Supports ACPI (Rev 1.0, 1.0b, 2.0)

Supports Wake-On-WLAN (WoWLAN) function and remote wake-up (Magic Packet and Microsoft<sup>®</sup> wake-up frame)

Supports auxiliary power auto-detect, and sets the related capability of power management registers in PCI Express configuration space

IEEE 802.11g protection mechanisms for both RTS/CTS and CTS-to-self

Burst-mode support for dramatically enhanced throughput

DSSS with DBPSK and DQPSK, CCK modulations and demodulations supported with long and short preamble

OFDM with BPSK, QPSK, 16QAM and 64QAM modulations and demodulations supported with rate compatible punctured convolutional coding with coding rate of 1/2, 2/3, and 3/4

Efficient IQ-imbalance calibration, DC offset, phase noise, frequency offset and timing offset compensation reduce analog front-end impairments

Selectable digital transmit and receiver FIR filters provided to meet transmit spectrum mask requirements and to reject adjacent channel interference

Programmable scaling both in transmitter and receiver to trade qµAntization noise against the increased probability of clipping

Fast receiver Automatic Gain Control (AGC) & antenna diversity functions

Adaptive transmit power control function

Complies with WMM, 802.11e, and CCX specifications

Complies with 802.11i and 802.11j specifications

Hardware-based IEEE 802.11i encryption/decryption engine, including 64-bit/128-bit WEP, TKIP, and AES

Supports Wi-Fi alliance WPA and WPA2 security

Supports a 32-bit general-purpose timer

Contains two large independent transmit and receive FIFO buffers

Advanced power saving mode when the LAN and wakeup function are not used

Uses 93C46 (64\*16-bit EEPROM) or 93C56 (128\*16-bit EEPROM) to store resource configuration and ID parameter data

LED pins for various network activity indications

Nine GPIO pins supported

Supports digital loopback capability on both ports

Flexible RF transceiver interface for different RF transceiver applications

Built-in 3.3V to 1.8V regulator

3.3V power supply required

0.18µm CMOS process

# DRAFT

# 3. System Applications

Wireless PCI Express adapter

Wireless notebook Mini Card adapter

Wireless system (wireless gateway router, wireless ADSL router, wireless set-top box etc.) with PCI Express or Mini Card slot

•

#### **Block Diagrams** 4.

## **RF** Diagram

# 5. Pin Assignments

# 5.1. Package Identification

Green package is indicated by a 'G' in the location marked 'T' in Figure 3.

# 6. **Pin Descriptions**

The following signal type codes are used in the tables:

| I:  | Input          | AO:    | Analog Output                         |

|-----|----------------|--------|---------------------------------------|

| DI: | Digital Input  |        | Analog Input/Output                   |

| AI: | Analog Input   | T/S:   | Tri-State Bi-Directional Input/Output |

| 0:  | Output         | S/T/S: | Sustained Tri-State                   |

| DO: | Digital Output | O/D:   | Open Drain                            |

## 6.1. Power Management/Isolation Interface

| Table 1. Fower Management/Isolation Interface |      |        |                                                                                                                                                                                                                        |  |

|-----------------------------------------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                                        | Туре | Pin No | Description                                                                                                                                                                                                            |  |

| WAKEB                                         | O/D  | 33     | Power Management Event: Open drain, active low.                                                                                                                                                                        |  |

|                                               |      |        | Used to reactivate the PCI Express slot's main power rails and reference clocks.                                                                                                                                       |  |

| ISOLATEB                                      | DI   | 18     | Isolate Pin: Active low.                                                                                                                                                                                               |  |

|                                               |      |        | Used to isolate the RTL8187SE-GR from the PCI Express bus. The RTL8187SE-GR will not drive its PCI Express outputs (excluding WAKEB) and will not sample its PCI Express input as long as the Isolate pin is asserted. |  |

Table 1 Power Management/Isolation Interface

## 6.2. PCI Express Interface

| Symbol  | Туре | Pin No | Description                                                                                                                     |  |  |

|---------|------|--------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| REFCLK+ | Ι    | 40     | DCI Express Differential Reference Clear Source: 100MIIz + 200mm                                                                |  |  |

| REFCLK- | Ι    | 39     | PCI Express Differential Reference Clock Source: 100MHz ±300ppm.                                                                |  |  |

| HSOP    | 0    | 43     | DCI European Transmit Differential Dain                                                                                         |  |  |

| HSON    | 0    | 42     | PCI Express Transmit Differential Pair.                                                                                         |  |  |

| HSIP    | Ι    | 47     |                                                                                                                                 |  |  |

| HSIN    | Ι    | 46     | PCI Express Receive Differential Pair.                                                                                          |  |  |

| PERSTB  | Ι    | 36     | PCI Express Reset Signal: Active low.                                                                                           |  |  |

|         |      |        | When the PERSTB is asserted at power-on state, the RTL8187SE-GR returns                                                         |  |  |

|         |      |        | to a pre-defined reset state and is ready for initialization and configuration                                                  |  |  |

|         |      |        | after the de-assertion of the PERSTB.                                                                                           |  |  |

| CLKREQB | O/D  | 34     | Reference Clock Request Signal. This signal is used by the RTL8187SE-GR to request starting of the PCI Express reference clock. |  |  |

# Table 2. PCI Express Interface

# 6.3. EEPROM Interface

#### Table 3. EEPROM Interface

| Symbol       | Туре  | Pin No | Description                                                                                                                                                                                                                                                                                                                                   |

|--------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EESK/9356SEL | DO/DI | 26     | EESK in 93C46 (93C56) programming or auto-load mode.                                                                                                                                                                                                                                                                                          |

|              |       |        | Input Pin as 9356 Select Pin at Initial Power-up.                                                                                                                                                                                                                                                                                             |

|              |       | D      | When this pin is pulled high with a 10K resistor, the 93C56 EEPROM is used to store the resource data for the RTL8187SE.                                                                                                                                                                                                                      |

|              |       |        | The RTL8187SE latches the status of this pin at power-up to determine which EEPROM (93C46 or 93C56) is used.                                                                                                                                                                                                                                  |

|              |       |        | After power on and GPIO_EN[5]=1, this pin is GPIO[5].                                                                                                                                                                                                                                                                                         |

| EEDI/AUX     | DO/DI | 25     | EEDI: Output to serial data input pin of EEPROM.                                                                                                                                                                                                                                                                                              |

|              |       |        | AUX: Input pin to detect if Aux. Power exists or not on initial<br>power-on. This pin should be connected to EEPROM. To support<br>wakeup from ACPI D3cold or APM power-down, this pin must be<br>pulled high to Aux. Power via a resistor. If this pin is not pulled high to<br>Aux. Power, the RTL8187SE assumes that no Aux. Power exists. |

|              |       |        | After power on and GPIO_EN[4]=1, this pin is GPIO[4].                                                                                                                                                                                                                                                                                         |

| EEDO         | DI    | 24     | This pin is GPIO[3] after power on and GPIO_EN[3]=1, otherwise, it is EEDO in 93C46 (93C56) programming or auto-load mode.                                                                                                                                                                                                                    |

| EECS         | DO    | 27     | EEPROM Chip Select.                                                                                                                                                                                                                                                                                                                           |

|              |       |        | 93C46 (93C56) chip select.                                                                                                                                                                                                                                                                                                                    |

# 6.4. Power Pins

|           | Table 4. Power Pins |                           |                                                                       |  |  |  |  |

|-----------|---------------------|---------------------------|-----------------------------------------------------------------------|--|--|--|--|

| Symbol    | Туре                | Pin No                    | Description                                                           |  |  |  |  |

| VDD33     | Р                   | 21, 32                    | +3.3V (Digital).                                                      |  |  |  |  |

| VAA33     | Р                   | 1, 2, 11, 48, 55, 58, 59, | +3.3V (Analog).                                                       |  |  |  |  |

|           |                     | 62                        |                                                                       |  |  |  |  |

| VDD       | Р                   | 12, 23, 37, 44            | +1.8V.                                                                |  |  |  |  |

| GND       | Р                   | 13, 20, 22, 31, 38, 65    | Ground (Digital).                                                     |  |  |  |  |

| AGND      | Р                   | 41, 45, 57                | Ground (Analog).                                                      |  |  |  |  |

| VCTRL_LDO | AO                  | 10                        | Reserve this pin for external BJT option to generate 1.8V for digital |  |  |  |  |

|           |                     |                           | core circuit.                                                         |  |  |  |  |

| VD_CBC    | Р                   | 63                        | Reserved for external power transistor.                               |  |  |  |  |

| VD_DIV    | VD_DIV P 64         |                           | Reserved for external power transistor.                               |  |  |  |  |

| <u></u>   | -                   |                           |                                                                       |  |  |  |  |

9

DRAFT

#### *6.5.* **LED** Interface

| Table 5. LED Interface |      |        |                                            |  |  |

|------------------------|------|--------|--------------------------------------------|--|--|

| Symbol                 | Туре | Pin No | Description                                |  |  |

| LED0                   | 0    | 30     | LED Pin.                                   |  |  |

|                        |      |        | a. PWRON: I2C_CK                           |  |  |

|                        |      |        | b. After PWRON & LED_CONTROL=3'h7: GPIO[0] |  |  |

|                        |      |        | c. Other: LED0 —                           |  |  |

| LED1                   | 0    | 35     | LED Pin.                                   |  |  |

|                        |      |        | a. PWRON: I2C_IO                           |  |  |

|                        |      |        | b. After PWRON & LED_CONTROL=3'h7: GPIO[1] |  |  |

|                        |      |        | c. Other: LED1                             |  |  |

#### *6.6.* **Baseband and RF Pins**

|          | Table 6. Baseband and RF Pins |        |                                                                                     |  |  |  |

|----------|-------------------------------|--------|-------------------------------------------------------------------------------------|--|--|--|

| Symbol   | Туре                          | Pin No | Description                                                                         |  |  |  |

| RFOP     | AO                            | 3      | 2 ACHE Differential DE Dewer Amplifier Output                                       |  |  |  |

| RFON     | AO                            | 4      | 2.4GHz Differential RF Power Amplifier Output.                                      |  |  |  |

| RFIN     | AI                            | 5      | 2.4GHz Differential RF Input.                                                       |  |  |  |

| RFIP     | AI                            | 6      | 2.40Hz Differential KF input.                                                       |  |  |  |

| PAPE     | DO                            | 7      | Enable Control for Optional External Power Amplifier                                |  |  |  |

| TRSWN    | DO                            | 8      | Control Signals for Ontional External DE T/D Switch                                 |  |  |  |

| TRSWP    | DO                            | 9      | Control Signals for Optional External RF T/R Switch                                 |  |  |  |

| ANTENSWP | DO                            | 15     | Control Signals for Antonno Switch                                                  |  |  |  |

| ANTENSWN | DO                            | 16     | Control Signals for Antenna Switch                                                  |  |  |  |

| TSSI     | AI                            | 50     | Transmit Signal Strength Indication From External Power Amplifier                   |  |  |  |

| TRQP     | AIO                           | 51     | Via register setting, can be programmed to one of the following four types of pins: |  |  |  |

|          |                               |        | RF TXQP: Input pin for RF TX test RF RXQP: Output pin for RF RX test                |  |  |  |

|          |                               |        | AFE TXQP: Output pin for DAC test AFE RXQP: Input pin for ADC test                  |  |  |  |

| TRQN     | AIO                           | 52     | Via register setting, can be programmed to one of the following four types of pins: |  |  |  |

|          |                               |        | RF TXQN: Input pin for RF TX test RF RXQN: Output pin for RF RX test                |  |  |  |

|          |                               |        | AFE TXQN: Output pin for DAC test AFE RXQN: Input pin for ADC test                  |  |  |  |

| TRIN     | AIO                           | 53     | Via register setting, can be programmed to one of the following four types of pins: |  |  |  |

|          |                               |        | RF TXIN: Input pin for RF TX test RF RXIN: Output pin for RF RX test                |  |  |  |

|          |                               |        | AFE TXIN: Output pin for DAC test AFE RXIN: Input pin for ADC test                  |  |  |  |

| TRIP     | AIO                           | 54     | Via register setting, can be programmed to one of the following four types of pins: |  |  |  |

|          |                               |        | RF TXIP: Input pin for RF TX test RF RXIP: Output pin for RF RX test                |  |  |  |

|          |                               |        | AFE TXIP: Output pin for DAC test AFE RXIP: Input pin for ADC test                  |  |  |  |

#### 6.7. **Bluetooth Co-Existence Pins**

|         | Table 7.    Bluetooth Co-Existence Pins |        |                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|---------|-----------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol  | Туре                                    | Pin No | Description                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| WLRXIND | 0                                       | 17     | Wireless LAN RX Activity Indicator                                                                                                                                                                                 |  |  |  |  |  |  |  |

| BTPRI   | IO                                      | 19     | Bluetooth Priority Pin<br>This pin is GPIO[2] after power on and GPIO_EN[2]=1, otherwise, this pin is<br>BTPRI. The BTPRI signal indicates when an important Bluetooth packet is being<br>transmitted or received. |  |  |  |  |  |  |  |

| BTSTAT  | IO                                      | 28     | Bluetooth Status<br>This pin is GPIO[6] after power on and GPIO_EN[6]=1, otherwise, this pin is<br>BTSTAT. The BTSTAT signal indicates when normal Bluetooth packets are being<br>transmitted or received.         |  |  |  |  |  |  |  |

| WLACT   | 0                                       | 29     | WLAN Activity<br>The WLAN_Active signal indicates when WLAN is either transmitting or<br>receiving in the 2.4GHz ISM band.                                                                                         |  |  |  |  |  |  |  |

#### 6.8. **Clock and Other Pins**

| Symbol    | Туре | Pin No | Description                                    |

|-----------|------|--------|------------------------------------------------|

| R15K      | IO   | 56     | This pin must be pulled low by a 15K resistor. |

| XI        | Ι    | 60     | Input of 40MHz Clock Reference.                |

| XO        | 0    | 61     | Output of 40MHz Clock Reference.               |

| EXTRSTB   | Ι    | 14     | External Reset Pin: Active Low.                |

| DA8_DEBUG | 0    | 49     | Debug Pin.                                     |

#### Tabla 0 Clock and Other Dine

#### 7. EEPROM (93C46 or 93C56) Contents

The RTL8187SE supports the attachment of an external EEPROM. The 93C46 is a 1Kbit EEPROM (the 93C56 is a 2Kbit EEPROM). The EEPROM interface provides the ability for the RTL8187SE to read from, and write data to, an external serial EEPROM device. Values in the external EEPROM allow default fields in PCI configuration space and IO space to be overridden following an internal power on reset, or software EEPROM auto-load command. The RTL8187SE will auto-load values from the EEPROM to these fields in configuration space and IO space. If the EEPROM is not present, the RTL8187SE initialization uses default values for the appropriate Configuration and Operational Registers. Software can read and write to the EEPROM using 'bit-bang' accesses via the 9346CR Register.

Note: It is suggested to obtain Realtek approval before changing the default settings of the EEPROM.

# 8. PCI EXPRESS<sup>TM</sup> 8.1. PCI EXPRESS Bus Interface

The RTL8187SE is compliant with PCI Express<sup>TM</sup> Base Specification Revision 1.1, and runs at 2.5GHz signaling rate with X1 link width, i.e., one transmit and one receive differential pairs. The RTL8187SE supports 4 types of PCI Express messages; interrupt messages, error messages, power management messages, and hot-plug messages. PCI Express lane polarity reversal and link reversal are also supported to ease PCB layout constraints.

## 8.1.1. PCI Express Transmitter

The RTL8187SE's PCI ExpressTM block receives digital data recovered from the WLAN MAC interface and performs data scrambling with Linear Feedback Shift Register (LFSR) and 8B/10B coding technology into 10-bit code groups. Data scrambling is used to reduce the possibility of electrical resonance on the link, and 8B/10B coding technology is used to benefit embedded clocking, error detection, and DC balance by sacrificing the 25 percent overhead to the system through the addition of 2 extra bits. Then, the data code groups are passed through its serializer for packet framing to generate 2.5 Gbps serial data and transmitted onto PCB trace to its upstream device via differential driver.

## 8.1.2. PCI Express Receiver

The RTL8187SE's PCI ExpressTM block receives 2.5Gbps serial data from its upstream device to generate parallel data. The receiver's PLL circuits are resynchronized to maintain bit and symbol lock. Through 8B/10B decoding technology and data descrambling, the original digital data is able to be recovered and then the data is passed to the RTL8187SE's internal WLAN MAC to be transmitted on the air.

# 8.2. PCI Configuration Space Table

Note: The following table assumes Power Management is enabled.

| <u> </u>     |             |      |        | Table 9. PC | CI Configu | ration Spa | ce Table |            |        |        |

|--------------|-------------|------|--------|-------------|------------|------------|----------|------------|--------|--------|

| No.          | Name        | Туре | Bit7   | Bit6        | Bit5       | Bit4       | Bit3     | Bit2       | Bit1   | Bit0   |

| 00h          | VID         | R    | VID7   | VID6        | VID5       | VID4       | VID3     | VID2       | VID1   | VID0   |

| 01h          |             | R    | VID15  | VID14       | VID13      | VID12      | VID11    | VID10      | VID9   | VID8   |

| 02h          | DID         | R    | DID7   | DID6        | DID5       | DID4       | DID3     | DID2       | DID1   | DID0   |

| 03h          |             | R    | DID15  | DID14       | DID13      | DID12      | DID11    | DID10      | DID9   | DID8   |

| 04h          | Command     | R    | 0      | PERRSP      | 0          | 0          | 0        | BMEN       | MEMEN  | IOEN   |

|              |             | W    | -      | PERRSP      | -          | -          | -        | BMEN       | MEMEN  | IOEN   |

| 05h          |             | R    | 0      | 0           | 0          | 0          | 0        | IntDisable | 0      | SERREN |

|              |             | W    | -      | -           | -          | -          | -        | IntDisable | -      | SERREN |

| 06h          | Status      | R    | 0      | 0           | 0          | 1          | IntSt    | 0          | 0      | 0      |

| 07h          |             | R    | DPERR  | SSERR       | RMABT      | RTABT      | STABT    | 0          | 0      | DPD    |

|              |             | W    | DPERR  | SSERR       | RMABT      | RTABT      | STABT    | -          | -      | DPD    |

| 08h          | Revision ID | R    | 0      | 0           | 1          | 0          | 0        | 0          | 1      | 0      |

| 09h          | PIFR        | R    | 0      | 0           | 0          | 0          | 0        | 0          | 0      | 0      |

| 0Ah          | SCR         | R    | 1      | 0           | 0          | 0          | 0        | 0          | 0      | 0      |

| 0Bh          | BCR         | R    | 0      | 0           | 0          | 0          | 0        | 0          | 1      | 0      |

| 0Ch          | CLS         | RW   | CLS7   | CLS6        | CLS5       | CLS4       | CLS3     | CLS2       | CLS1   | CLS0   |

| 0Dh          | LTR         | R    | 0      | 0           | 0          | 0          | 0        | 0          | 0      | 0      |

| 0Eh          | HTR         | R    | 0      | 0           | 0          | 0          | 0        | 0          | 0      | 0      |

| 0Fh          | BIST        | R    | 0      | 0           | 0          | 0          | 0        | 0          | 0      | 0      |

| 10h          | IOAR        | R    | 0      | 0           | 0          | 0          | 0        | 0          | 0      | IOIN   |

|              |             | W    | -      | -           | -          | -          | -        | -          | -      | -      |

| 11h          |             | RW   | IOAR15 | IOAR14      | IOAR13     | IOAR12     | IOAR11   | IOAR10     | IOAR9  | IOAR8  |

| 12h          |             | RW   | IOAR23 | IOAR22      | IOAR21     | IOAR20     | IOAR19   | IOAR18     | IOAR17 | IOAR16 |

| 13h          |             | RW   | IOAR31 | IOAR30      | IOAR29     | IOAR28     | IOAR27   | IOAR26     | IOAR25 | IOAR24 |

| 14h-<br>17h  |             |      |        |             | Res        | erved      |          |            |        |        |

| 18h-         |             |      |        |             | Res        | erved      |          |            |        |        |

| 1Fh<br>20h-  |             |      |        |             | Dec        | erved      |          |            |        |        |

| 2011-<br>27h |             |      |        |             | KC         | serveu     |          |            |        |        |

| 28h-<br>2Bh  |             |      |        |             | Res        | erved      |          |            |        |        |

| 2Ch          | SVID        | R    | SVID7  | SVID6       | SVID5      | SVID4      | SVID3    | SVID2      | SVID1  | SVID0  |

| 2Dh          |             | R    | SVID15 | SVID14      | SVID13     | SVID12     | SVID11   | SVID10     | SVID9  | SVID8  |

| 2Eh          | SMID        | R    | SMID7  | SMID6       | SMID5      | SMID4      | SMID3    | SMID2      | SMID1  | SMID0  |

| 2Fh          |             | R    | SMID15 | SMID14      | SMID13     | SMID12     | SMID11   | SMID10     | SMID9  | SMID8  |

| 30h          | BMAR        | R    | 0      | 0           | 0          | 0          | 0        | 0          | 0      | BROME  |

|              |             | W    | -      | - (         | -          | -          | -        | -          | -      | BROME  |

| 31h          |             | R    | BMAR15 | BMAR14      | BMAR13     | BMAR12     | BMAR11   | 0          | 0      | 0      |

|              |             | W    | BMAR15 | BMAR14      | BMAR13     | BMAR12     | BMAR11   | -          | _      | -      |

| 32h          |             | RW   | BMAR23 | BMAR22      | BMAR21     | BMAR20     | BMAR19   | BMAR18     | BMAR17 | BMAR1  |

| 33h          |             | RW   | BMAR31 | BMAR30      | BMAR29     | BMAR28     | BMAR27   | BMAR26     | BMAR25 | BMAR2  |

| 34h          | Cap_Ptr     | R    | 0      | 1           | 0          | 0          | 0        | 0          | 0      | 0      |

| 35h-         | <u>r</u>    |      | ~      | 1 *         | -          | erved      | I Č      | I          | , v    | Ĭ      |

| 3Bh          |             |      |        |             | 100        |            |          |            |        |        |

| 3Ch          | ILR         | RW   | IRL7   | ILR6        | ILR5       | ILR4       | ILR3     | ILR2       | ILR1   | ILR0   |

|              | IDD         | R    | 0      | 0           | 0          | 0          | 0        | 0          | 0      | 1      |

| 3Dh          | IPR         | K    | 0      | U           | 0          | 0          | 0        | 0          | 0      | 1      |

Single-Chip Wireless LAN Network Interface Controller13w/PCI Express Interface13

Track ID: JATR-1076-21 Rev. 1.0

| No.         | Name                          | Туре | Bit7                    | Bit6                                  | Bit5                     | Bit4                    | Bit3                      | Bit2                   | Bit1                     | Bit0                            |

|-------------|-------------------------------|------|-------------------------|---------------------------------------|--------------------------|-------------------------|---------------------------|------------------------|--------------------------|---------------------------------|

| 3Fh         | MXLAT                         | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 0                               |

| 40h         | PMID                          | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 1                               |

| 41h         | NextPtr                       | R    | 0                       | 1                                     | 0                        | 1                       | 0                         | 0                      | 0                        | 0                               |

| 42h         | PMC                           | R    | Aux I b1                | Aux I b0                              | DSI                      | Reserved                | PMECLK                    | Ŭ                      | Version                  | Ū                               |

| 43h         |                               | R    | PME_D3 <sub>cold</sub>  | PME_D3 <sub>hot</sub>                 | PME D2                   | PME D1                  | PME D0                    | D2                     | D1                       | Aux I b2                        |

| 44h         | PMCSR                         | R    | 0                       | 0                                     |                          | 0                       | 0                         | 0                      | Power                    | State                           |

|             |                               | W    | -                       | -                                     |                          | -                       | -                         | -                      | Power                    | State                           |

| 45h         |                               | R    | PME Status              | - 1)                                  | RAF                      |                         | -                         | -                      | -                        | PME En                          |

|             |                               | W    | PME_Status              | -                                     |                          | -                       | -                         | -                      | -                        | PME_En                          |

| 46-         |                               |      |                         |                                       | Res                      | served                  |                           | •                      |                          | •                               |

| 4Fh         |                               |      |                         |                                       |                          |                         |                           |                        |                          |                                 |

| 50h         | MSIID                         | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 1                      | 0                        | 1                               |

| 51h         | NextPtr                       | R    | 0                       | 1                                     | 1                        | 1                       | 0                         | 0                      | 0                        | 0                               |

| 52h         | Message<br>Control            | R    | 64-bit<br>Address       | Multip                                | ole Message En           | able                    | 0                         | 0                      | 0                        | MSI Enable                      |

|             | Control                       |      | Capable                 |                                       |                          |                         |                           |                        |                          |                                 |

|             |                               | W    | -                       | Multi                                 | ole Message En           | able                    | -                         | -                      | 0                        | MSI Enable                      |

| 53h         |                               |      |                         |                                       |                          | erved. Always r         | eturn 0                   |                        |                          |                                 |

| 54h-        | Message                       | RW   |                         |                                       | 64-bi                    | t Interrupt Mess        | age Address Lo            | )W                     |                          |                                 |

| 57h         | Address Low                   |      |                         |                                       |                          |                         |                           |                        |                          |                                 |

| 58h-<br>5Bh | Message                       | RW   |                         | 64-bit Interrupt Message Address High |                          |                         |                           |                        |                          |                                 |

| 5Ch-        | Address High<br>Message Data  | RW   |                         |                                       |                          | 16-bit Mess             | aga Data                  |                        |                          |                                 |

| 5Dh         | Message Data                  | K W  |                         |                                       |                          | 10-on Mess              | age Data                  |                        |                          |                                 |

| 5E-         |                               |      |                         |                                       | RES                      | ERVED                   |                           |                        |                          |                                 |

| 6Fh         |                               |      |                         |                                       | KL5                      |                         |                           |                        |                          |                                 |

| 70h         | PCIEID                        | R    | 0                       | 0                                     | 0                        | 1                       | 0                         | 0                      | 0                        | 0                               |

| 71h         | NextPtr                       | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 0                               |

| 72h-        | PCIE Cap.                     | R    | 0                       | 0                                     | 0                        | Legacy                  | 0                         | 0                      | 0                        | 1                               |

| 73h         |                               | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 0                               |

| 74h-<br>77h | Device<br>Capability          | R    | L0s_acpt_<br>latency[1] | L0s_acpt_<br>latency[0]               | Entend_<br>tag_support   | 0                       | 0                         | Max_p                  | ayload_size_su           | pport                           |

|             | Register                      | R    | Role Base<br>Error rpt  | 0                                     | 0                        | 0                       | L1_acpt_<br>latency[2]    | L1_acpt_<br>latency[1] | L1_acpt_<br>latency[0]   | L0s_acpt_la<br>tency[2]         |

|             |                               | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 0                               |

|             |                               | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 0                               |

| 78h-<br>79h | Device<br>Control<br>Register | RW   | Ν                       | Max_payload_size                      | e                        | Relaxed_<br>ordering_en | Unsupport_<br>rqst_rpt_en | Fatal_err_<br>rpt_en   | Non_fatal_<br>err_rpt_en | Correct-<br>able_err_<br>rpt_en |

|             | .0                            | RW   | 0                       | Max                                   | _read_request_s          | size                    | No_snoop_en               | Auxpwr_<br>PM_en       | 0                        | Entend_<br>tag_en               |

| 7Ah         | Device Status<br>Register     | R    | 0                       | 0                                     | Transact_<br>ion_pending | AuxPwr_det              | Upsupport_<br>rqst_det    | Fatal_err_det          | Non_fatal_<br>err_det    | Correct-<br>able_err_det        |

|             |                               | W    | 0                       | 0                                     | DA                       |                         | Upsupport_<br>rqst_det    | Fatal_err_det          | Non_fatal_err<br>_det    | Correcta-<br>ble_err_det        |

| 7Bh         |                               | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 0                               |

| 7Ch         | Link                          | R    | 0                       | 0                                     | 0                        |                         | 0                         | 0                      | 0                        | 1                               |

| 7Dh         | Capability<br>Register        | R    | L1_exit_<br>lat[0]      | L0s_exit_<br>lat[2]                   | L0s_exit_<br>lat[1]      | L0s_exit_<br>lat[0]     | ASPM                      | _support               | 0                        | 0                               |

| 7Eh         |                               | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | Clock_PM               | L1_exit_<br>lat[2]       | L1_exit_<br>lat[1]0             |

| 7Fh         |                               | R    | 0                       | 0                                     | 0                        | 0                       | 0                         | 0                      | 0                        | 0                               |

### RTL8187SE Datasheet

| No.         | Name                           | Туре | Bit7                                      | Bit6                         | Bit5                            | Bit4                                          | Bit3                                       | Bit2                             | Bit1                                       | Bit0                                |

|-------------|--------------------------------|------|-------------------------------------------|------------------------------|---------------------------------|-----------------------------------------------|--------------------------------------------|----------------------------------|--------------------------------------------|-------------------------------------|

| 80h         | Link Control<br>Register       | R    | Extended_<br>sync                         | Common_<br>clock             | 0                               | 0                                             | RCB                                        | 0                                | ASPM_                                      | control                             |

|             |                                | W    | Extended_<br>sync                         | Common_<br>clock             | 0                               | 0                                             | RCB                                        | 0                                | ASPM_                                      | control                             |

| 81h         |                                | R    | 0                                         | 0                            | 0                               | 0                                             | 0                                          | 0                                | 0                                          | Enable<br>clock_PM                  |

|             |                                | W    | 0                                         | 0                            | 0                               | 0                                             | 0                                          | 0                                | 0                                          | Enable<br>clock_PM                  |

| 82h         | Link Status                    | R    | 0                                         | 0                            | -0                              | 1                                             | 0                                          | 0                                | 0                                          | 1                                   |

| 83h         | Register                       | R    | 0                                         | 0                            | 0                               | Slot_clock_<br>cfg                            | 0                                          | 0                                | 0                                          | 0                                   |

| 84h         | Slot<br>Capability<br>Register | R    | Slot power<br>Limit[0]                    | Hot-Plug<br>Capable          | Hot-Plug<br>Surprise            | Power<br>indicator<br>present                 | Attn indicator<br>present                  | MRL sensor present               | Power control present                      | Attn button<br>present              |

| 85h         |                                | R    | Slot power<br>Limit scale[0]              | Slot power<br>Limit[7]       | Slot power<br>Limit[6]          | Slot power<br>Limit[5]                        | Slot power<br>Limit[4]                     | Slot power<br>Limit[3]           | Slot power<br>Limit[2]                     | Slot power<br>Limit[1]              |

| 86h         |                                | R    | Physical slot<br>Number[4]                | Physical<br>slot Number[3]   | Physical slot<br>Number[2]      | Physical slot<br>Number[1]                    | Physical slot<br>Number[0]                 | No common<br>Complete<br>support | Electromecha<br>nical interlock<br>present | Slot power<br>Limit<br>scale[1]     |

| 87h         |                                | R    | Physical slot<br>Number[12]               | Physical slot<br>Number[11]  | Physical slot<br>Number[1]      | Physical slot<br>Number[9]                    | Physical slot<br>Number[8]                 | Physical slot<br>Number[7]       | Physical slot<br>Number[6]                 | Physical slot<br>Number[5]          |

| 88h         | Slot Control<br>Register       | RW   | Attn Indicator<br>Control[1]              | Attn Indicator<br>Control[0] | Hot-Plug<br>Interrupt<br>Enable | Command<br>Completed<br>interrupt<br>Enable   | Presence<br>Detect<br>Changed<br>Enable    | MRL Sensor<br>Changed<br>Enable  | Power Fault<br>Detected<br>Enable          | Attn Bottom<br>Pressed<br>Enable    |

| 89h         |                                | RW   | -                                         | -                            | -                               | Data Link<br>Layer State<br>Changed<br>Enable | Electromecha<br>nical Interlock<br>Control | Power<br>Controller<br>Control   | Power<br>Indicator<br>Control[1]           | Power<br>Indicator<br>Control[0]    |

| 8Ah         | Slot Status<br>Register        | R    | Electromecha<br>nical Interlock<br>Status | Presence Detect<br>State     | MRL Sensor<br>State             | Command<br>Completed                          | Presence<br>Detect<br>Changed              | MRL Sensor<br>Changed            | Power Fault<br>Detected                    | Attn Botton<br>pressed              |

| 8Bh         |                                | R    |                                           |                              |                                 | Reversed                                      |                                            |                                  |                                            | Data Link<br>Layer State<br>Changed |

| 8Ch-<br>FFh |                                |      |                                           |                              | Rev                             | versed                                        |                                            |                                  |                                            |                                     |

# 8.3. PCI Configuration Space Functions

The PCI configuration space is intended for configuration, initialization, and catastrophic error handling functions. The functions of the configuration space of the RTL8187SE are described below.

**VID:** Vendor ID. This field will be set to a value corresponding to a PCI Vendor ID in the external EEPROM. If there is no EEPROM, this field will default to a value of 10ECh, which is Realtek Semiconductor's PCI Vendor ID.

**DID:** Device ID. This field will be set to a value corresponding to a PCI Device ID in the external EEPROM. If there is no EEPROM, this field will default to a value of 8185h.

**Command:** The command register is a 16-bit register used to provide coarse control over a device's ability to generate and respond to PCI cycles.

| Bit   | Symbol   | Description                                                                                                                                                                                                                                          |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | -        | Reserved.                                                                                                                                                                                                                                            |

| 10    | INTDIS   | Interrupt Disable.                                                                                                                                                                                                                                   |

|       |          | This Bit enables/disables the RTL8187SE to assert Int# signal.                                                                                                                                                                                       |

|       |          | 1: Force disable assertion of the Int# signal.                                                                                                                                                                                                       |

|       |          | 0: Enable enable assertion of the Int# signal (default value after PCI reset)                                                                                                                                                                        |

| 9     | FBTBEN   | Fast Back-To-Back Enable. Does not apply to PCI Express. Must be hardwired to 0.                                                                                                                                                                     |

| 8     | SERREN   | System Error Enable.                                                                                                                                                                                                                                 |

|       |          | When set to 1, enables reporting of Non-fatal and Fatal errors detected by the device to the Root Complex. Note that errors are reported if enabled either through this bit or through the PCI-Express specific bits in the Device Control register. |

| 7     | ADSTEP   | Address/Data Stepping. Does not apply to PCI Express. Must be hardwired to 0.                                                                                                                                                                        |

| 6     | PERRSP   | Parity Error Response.                                                                                                                                                                                                                               |

|       |          | In the Status register, the Master Data Parity Error bit is set by a Requester if its Parity Error Response bit is set and either of the following two conditions occurs:                                                                            |

|       |          | - If the Requester receives a poisoned Completion.                                                                                                                                                                                                   |

|       |          | - If the Requester poisons a write request.                                                                                                                                                                                                          |

|       |          | If the Parity Error Response bit is cleared, the Master Data Parity Error status bit is never set.                                                                                                                                                   |

| 5     | VGASNOOP | VGA Palette SNOOP. Does not apply to PCI Express. Must be hardwired to 0.                                                                                                                                                                            |

| 4     | MWIEN    | Memory Write and Invalidate Cycle Enable.                                                                                                                                                                                                            |

|       |          | Does not apply to PCI Express. Must be hardwired to 0.                                                                                                                                                                                               |

| 3     | SCYCEN   | Special Cycle Enable. Does not apply to PCI Express. Must be hardwired to 0.                                                                                                                                                                         |

| 2     | BMEN     | Bus Master Enable.                                                                                                                                                                                                                                   |

|       |          | When set to 1, the RTL8187SE is capable of acting as a PCI bus master. When set to 0, it is prohibited from acting as a bus master.                                                                                                                  |

|       |          | For normal operations, this bit must be set by the system BIOS.                                                                                                                                                                                      |