TripStrip II

# Hardware Specification Document

©Sensitech Inc. 800 Cummings Center • Suite 258X Beverly, MA 01915-6197

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 1 of 83

A Carrier Corp. Company

PART NUMBER T82002163

## Federal Communications Commission (FCC) Statement

You are cautioned that changes or modifications not expressly approved by the part responsible for compliance could void the user's authority to operate the equipment

## FCC-Class B

This equipment has been tested and found to comply with the limits for a class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a communications. However, there is no guarantee that interference will not occur in particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

**CONFIDENTIAL – CONTROLLED DOCUMENT**

Page 2 of 83

A Carrier Corp. Company

PART NUMBER T82002163

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 3 of 83

A Carrier Corp. Company

PART NUMBER T82002163

## APPROVALS

| Engineering:     |     |   |  |

|------------------|-----|---|--|

| Name:            |     |   |  |

| Date:            |     |   |  |

| Signature:       |     |   |  |

|                  |     |   |  |

| Quality:         |     |   |  |

| Name:            |     |   |  |

| Date:            |     |   |  |

| Signature:       |     |   |  |

|                  |     |   |  |

| Manufacturing:   |     |   |  |

| Name:            |     | _ |  |

| Date:            |     |   |  |

| Signature:       |     |   |  |

|                  |     |   |  |

| Marketing:       |     |   |  |

| Name:            |     | _ |  |

| Date:            |     |   |  |

| Signature:       |     |   |  |

|                  |     |   |  |

| Technical Servio | es: |   |  |

| Name:            |     | _ |  |

| Date:            |     |   |  |

| Signature:       |     |   |  |

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 4 of 83

A Carrier Corp. Company

PART NUMBER T82002163

| Document Version Information                                                                                                                                | )                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Organization of this Document                                                                                                                               | )                |

| Executive Summary                                                                                                                                           | )                |

| Device General Description                                                                                                                                  | )                |

| Functional Description                                                                                                                                      | )                |

| User Interface                                                                                                                                              | )                |

| FRS in brief                                                                                                                                                | 2                |

| Device Hardware Structure                                                                                                                                   | }                |

| General Hardware Information13                                                                                                                              | ;                |

| Electrical Specification                                                                                                                                    | ;                |

| Mode of Operation13                                                                                                                                         | ;                |

| Power Save Mode "Suspend State"15                                                                                                                           | ;                |

| Power Supply         15           Qty         17           Vendor         17           SEIKO         17           SANYO         17           PCB         17 | 7<br>7<br>7<br>7 |

| Li-ION Charging                                                                                                                                             | l                |

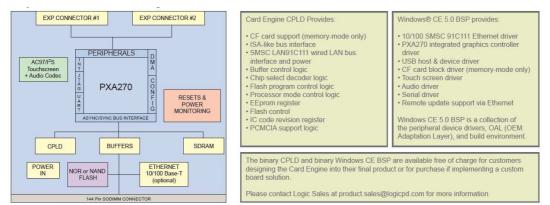

| LogicPD Card Engine                                                                                                                                         | ;                |

| Memory Controller Reset and Initialization                                                                                                                  | ;                |

| Memory Controller                                                                                                                                           | ;                |

| Memory Controller Operation                                                                                                                                 | ŀ                |

| Stacked SDRAM and Flash Memory24                                                                                                                            | ŀ                |

| Stacked SDRAM                                                                                                                                               | ŀ                |

| Stacked Flash Memory                                                                                                                                        | ŀ                |

| Synchronous Dynamic Memory (SDRAM) Interface                                                                                                                | j                |

| Maximum Row Active Time (TRAS)                                                                                                                              | ĵ                |

| Programmable Larger SDRAM Memory Space                                                                                                                      | j                |

| SDRAM State Machine                                                                                                                                         | 1                |

| Synchronous, Static, and Variable-Latency I/O (VLIO)                                                                                                        | )                |

| Interfaces                                                                                                                                                  | )                |

| Asynchronous Static Operation                                                                                                                               | )                |

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 5 of 83

A Carrier Corp. Company

PART NUMBER T82002163

| Asynchronous Flash Memory Interface                   |

|-------------------------------------------------------|

| Memory Controller                                     |

| Synchronous Flash Memory                              |

| ROM Interface                                         |

| SRAM Interface Overview                               |

| Variable-Latency I/O Interface Overview               |

| Memory Controller                                     |

| UARTs                                                 |

| Overview                                              |

| Full-Function UART                                    |

| Bluetooth UART                                        |

| Compatibility with 16550A and 16750                   |

| Features                                              |

| Signal Descriptions                                   |

| Operation                                             |

| Reset                                                 |

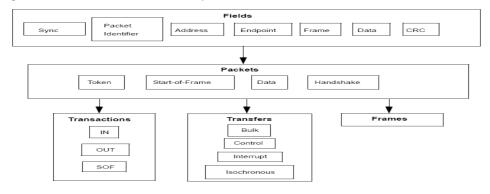

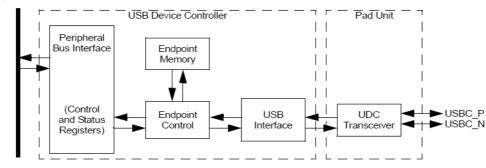

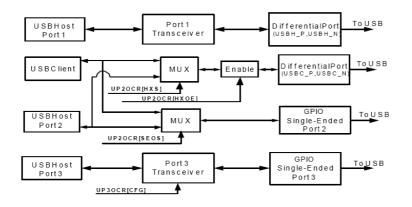

| USB Client Controller:                                |

| Overview                                              |

| Features                                              |

| Signal Descriptions                                   |

| Bidirectional Signals                                 |

| Operation                                             |

| Peripheral Bus Interface and Control/Status Registers |

| Suspend and Resume                                    |

| Sleep Mode Operation                                  |

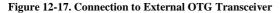

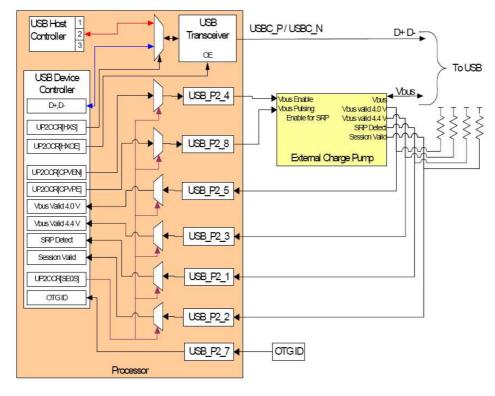

| USB On-The-Go Operation                               |

| On-Chip OTG Transceiver Operation                     |

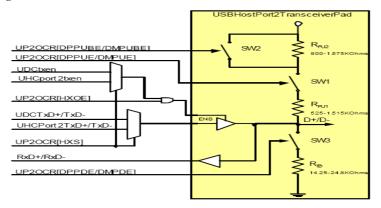

| Interface to External OTG Transceiver                 |

| Interface to External Charge Pump Device              |

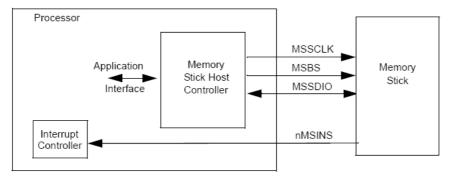

| Memory Stick                                          |

| Overview                                              |

| Features                                              |

| Signal Descriptions                                   |

|                                                       |

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 6 of 83

A Carrier Corp. Company

PART NUMBER T82002163

| Operation                                                                                                  |          |

|------------------------------------------------------------------------------------------------------------|----------|

| Functional Description                                                                                     |          |

| Interrupts                                                                                                 |          |

| Memory Stick Insertion and Removal                                                                         | 49       |

| Reset                                                                                                      | 50       |

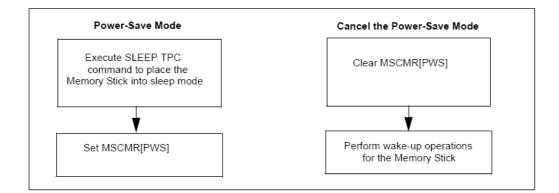

| Power-Save Mode<br>LogicPD Card Engine:<br>Note: Our current Card Engine does support Ethernet             | 51       |

| TempTale Mini                                                                                              | 55       |

| TempTale 4 (Epson TT4)                                                                                     | 59       |

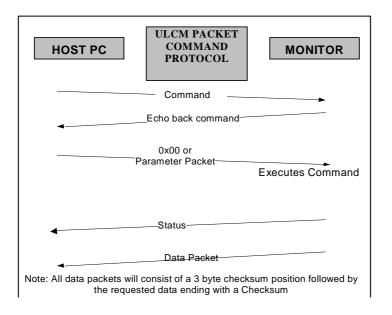

| Command Transmission Paradigm                                                                              | 59       |

| Status Byte Definitions                                                                                    | 59       |

| Communication Layer Descriptions                                                                           | 60       |

| Data Recording Layer                                                                                       | 60       |

| TempTale 4 (OKI TT4)                                                                                       | 62       |

| Communications                                                                                             | 62       |

| Establishing a Connection                                                                                  | 63       |

| Command Protocol                                                                                           |          |

| TT4 Optical Interface Circuit                                                                              |          |

| LCD                                                                                                        | 69       |

| <b>Keypad</b><br>9.0 Battery Low Alert Function:<br>10.0 Line Thermal Head Printer:<br>11.0 Control Board. | 72<br>72 |

| Device System Configuration Information                                                                    |          |

| LogicLoader (LoLoTM)                                                                                       |          |

| LogicLoader Overview                                                                                       |          |

| LogicLoader Basics                                                                                         |          |

| Using LogicLoader for Debugging                                                                            |          |

| Manufacturing Advantages with LoLo                                                                         |          |

| The LogicLoader Shell (loshTM)                                                                             |          |

| Losh Overview                                                                                              |          |

| Losh Basics<br>Using Losh                                                                                  |          |

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 7 of 83

A Carrier Corp. Company

PART NUMBER T82002163

| Program Loading                                                                                                                               |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1 Understanding the Load Command                                                                                                            |          |

| YAFFS (Yet Another Flash File System)                                                                                                         |          |

| 8.1 YAFFS Overview                                                                                                                            |          |

| <ul><li>8.2 Working with YAFFS in LogicLoader</li><li>8.2.1 Developing a Partition Scheme</li><li>8.2.2 Formatting YAFFS Partitions</li></ul> | 79       |

| <ul><li>8.2.3 Adding YAFFS Type Partitions</li><li>8.2.4 Mounting the Partition</li><li>8.2.5 Accessing YAFFS Partitions in an OS</li></ul>   | 80<br>80 |

| 8.3 Summary                                                                                                                                   |          |

| Device System Configuration/Programming                                                                                                       |          |

| Explanation of Script                                                                                                                         |          |

| Appendix:                                                                                                                                     |          |

| List of Error Messages (12.9.08)                                                                                                              |          |

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 8 of 83

A Carrier Corp. Company

PART NUMBER T82002163

#### **Document Version Information**

| Document                              | Version           |

|---------------------------------------|-------------------|

| Functional Requirement Specifications | T85000530, Rev. A |

| Hardware Specifications               | T82002163, Rev. A |

| Firmware                              |                   |

|                                       |                   |

## **Organization of this Document**

This document outlines the TripStripII's specifications in detail. It describes each aspect of the unit's functionality and how the hardware is configured.

#### **Executive Summary**

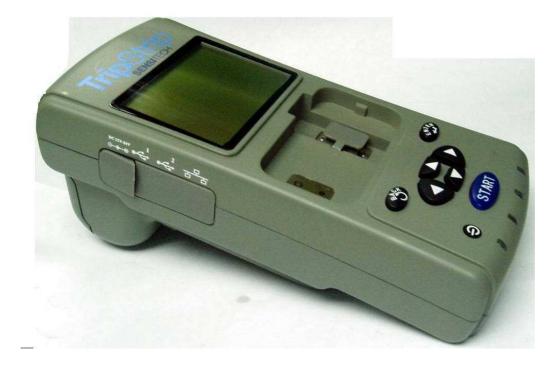

The TripStrip II is a handheld thermal printer which is capable of portable or desktop use. This particular model supersedes the previous TripStrip platform with many functional enhancements such as it will allow the download of 16K TempTale data loggers, TempTale Mini and all TempTale variants. An integral monochrome 4 inch LCD was added to provide the user with a quick view of the monitor data such as display summary and graph as well as menu navigation for unit functionality. The TripStrip II also has a USB host and client to allow further communication channels.

## **Device General Description**

## **Functional Description**

The following is an overview of the TripStrip II and its features.

Note: Input voltage range is 12VDC - 24VDC.

The TripStrip II remote data printer generates graphs from all TempTale 4 variants (2k and 16k) and TempTale Mini 2k. To be specific, TT4 Ambient, TT4 Humidity, TT4 Probe and Dual Sensor, TT4 BIO, TT4 Dry Ice Probe, TT4 Probeless Dry Ice, and TT4 RF. The TripStrip II is available as a Li-ION rechargeable battery-powered unit, shipped fully charged and ready for use. The battery may be recharged by the 15VDC switcher adapter, 12VDC automobile car adapter, or 24VDC Trailer Truck adapter.

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 9 of 83

A Carrier Corp. Company

PART NUMBER T82002163

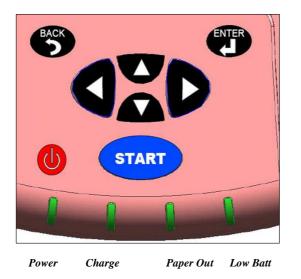

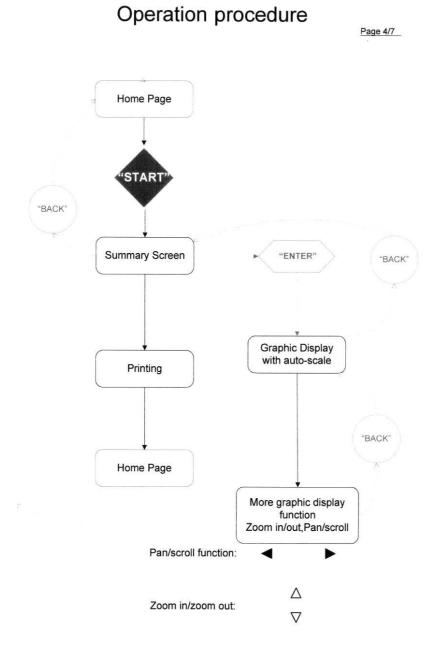

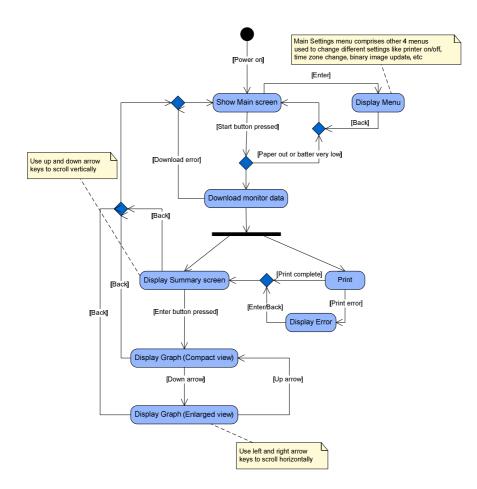

#### User Interface

User presses the Power Button and the unit is powered ON and the Power LED is ON. The Sensitech application program appears momentarily. The user is now able to download any TT4 (2k/16k) or TTmini; except TT4 USB. To download a TT4 unit, the user may place a TT4 on the optical interface and press START. To download a TTmini, the user may connect the TTmini to the RS232 DB9 connector and press START.

Once the user presses START, the TSII auto-detects which UART to begin downloading from. The summary data will appear first and the unit will begin printing (if option is enabled via Menu), then the user will have an option of displaying the graph on the LCD by pressing the ENTER key which defaults to Auto Scale Mode. The user will have the ability to Zoom In/Out of the graph. Zoom interval will be Max Trip Length / 5, regardless of the EEPROM size or monitor type.

Please note: For the ZOOM feature, no matter what type of monitor or EEPROM size, the TSII will take the max trip length and divide it by 5. However, please note due to the resolution, if the monitor data size is less than (approximately) 512K then this will not apply. The user will only see the graph screen and will not be able to ZOOM. (If the EEPROM has more than or equal to 64 points then it will have the zoom feature).

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 10 of 83

A Carrier Corp. Company

PART NUMBER T82002163

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 11 of 83

A Carrier Corp. Company

PART NUMBER T82002163

## FRS in brief

To re-design the current TripStrip TempTale Remote Printer that provides hardcopy printouts of time/temperature data and related information from TempTale monitors.

The current version of the product, while suitable in many applications for most customers has several deficiencies that impede further adoption of TempTale monitoring programs. In addition, the product is RoHS compliant.

The TripStrip is an ancillary product, designed purely as an accessory in support of in-bound and closed loop TempTale monitoring programs, primarily in the food and supermarket segments. In many cases the product is offered to customers as a free or deeply discounted instrument in support of large volume TempTale programs. Within this context product volumes are anticipated to be in the 100-500 units/year range.

The objectives of this project are:

- Eliminate the current TripStrip deficiencies and upgrade the product feature set per the requirements described below.

- Maintain or reduce product costs at/from current level

- Provide product/system "architectural" features consistent with current and potential future product line strategies.

- Minimize development and tooling/capital expense (the product is low-volume, with in-direct ROI potential)

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 12 of 83

A Carrier Corp. Company

PART NUMBER T82002163

**Device Hardware Structure**

## **General Hardware Information**

#### **Electrical Specification**

1.1 SWITCHING POWER SUPPLY Input Voltage: AC 100~240V Frequency:50/60Hz Input Current: 1500mA. Output Voltage: DC 15V Output Current: DC 4000mA 1.2 DC Input: 12-24V \* 15VDC Wall Adapter \* 12 VDC automobile DC adapter \* 24 VDC trailer truck DC adapter 1.2.1 Input current: 2-5A 1.2.2Power Consumption: approximately 15W 1.3. Charging Max Charging Current:3A Charging Voltage: 8.4V +/- 0.1V Charging Time: 3.5hr Discharging current: 2-6A Discharging time: 3hr/2A Environment Specification Operating Temperature: 0-45°C Storage Temperature: 0-45°C Operating Humidity: 0-99% Mechanical Specification Cabinet Size: 270(L)\*135(W)\*110(H) mm Weight: Approximately 1100g Color: Grey

## Mode of Operation

The user presses the platen release button on the unit to load a 50mm paper roll into the frontend of the TripStripII unit. The user will then Power ON device using the POWER button on the Keypad. SENSITECH, INC. window appears. Now, the user is able to navigate through the menus or download/print a TempTale 4 monitor or TempTale Mini. A hand strap located on the rear of the unit provides the user optimal portability support.LED status indicators are visible on the front end of the unit or Power, LowBatt, Charging, and Paper out.

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 13 of 83

A Carrier Corp. Company

PART NUMBER T82002163

2k monitor = 11 seconds to download the data and an additional 49 seconds to print 16k monitor = 1 minute to download and an additional 6 minutes to print

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 14 of 83

A Carrier Corp. Company

PART NUMBER T82002163

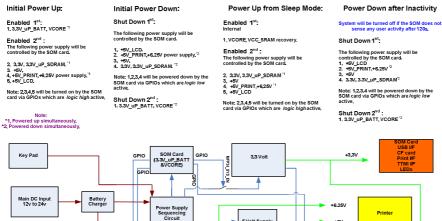

## Power Save Mode "Suspend State"

Suspend state is the PXA270 SOM's hardware power down state, allowing for lower power consumption. The Suspend state is designed to reduce power consumption while the PXA270 is waiting for an event such as a keyboard input. The suspend state is entered using Logic BSP's by asserting the nSUSPEND signal or through software. The PXA270 processor is put into Standby Mode. All power supplies remain active. System context is retained. Internal clocks are stopped except RTC. An internal or external wakeup event can cause the processor to transition back to Run Mode.

**IMPORTANT NOTE:** Although Suspend consumes less power than Run state, it consumes more power than the Standby state. Thus, on a power failure, the PXA270 system will actually leave the Suspend state and transition to the Standby state (the same thing occurs on a SW\_nRESET).

During suspend state, the unit powers OFF the LCD backlight, printer head, and printer control board. When user reinitiates activity, the unit returns to full active state of all devices.

If needed, user may engage the Reset Button located on the right-side of the unit.

### **Power Supply**

The following are methods a user is able to supply power to the TripStripII device to charge/operate: 1. Dual Voltage 120/60 Hz (220/50 Hz) – 15VDC Wall Adapter

- 2. 12 VDC automobile DC adapter

- 3. 24 VDC trailer truck DC adapter

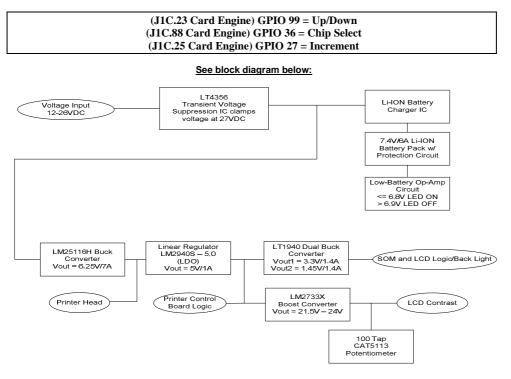

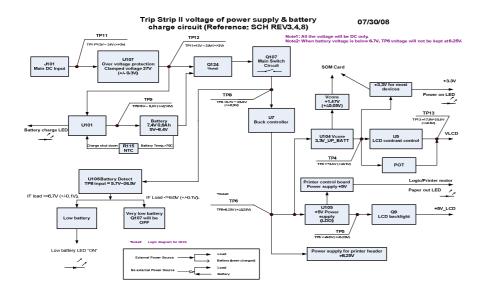

Internally, the TripStripII power supply consists of:

1. LT4356-1, Overvoltage Protection Regulator and Inrush Limiter IC

- The LT4356-1 surge stopper protects loads from high voltage transients.

- It regulates the output during an overvoltage event, such as load dump in automobiles, by controlling the gate of an external N-Channel MOSFET.

- The output is limited to a safe value thereby allowing the loads to continue functioning.

- The LT4356-1 also monitors the voltage drop between the VCC and SNS pins to protect against overcurrent faults.

- An internal amplifier limits the current sense voltage to 50mV.

- In either fault condition, a timer is started inversely proportional to MOSFET stress.

- If the timer expires, the /FLT pin pulls low to warn of an impending power down. If the condition persists, the MOSFET is turned off.

2. LTC4006, 4A, High Efficiency, Standalone Li-Ion Battery Charger

- The LTC4006 is a complete constant-current/constant voltage charger controller for 2-, 3- or 4-cell lithium batteries.

- The PWM controller is a synchronous, quasi-constant frequency, constant off-time architecture that will not generate audible noise even when using ceramic capacitors.

- Charging current is programmable with a single sense resistor to  $\pm 4\%$  typical accuracy.

- Charging current can be monitored as a representative voltage at the IMON pin.

- A timer, programmed by an external resistor, sets the total charge time or is reset to 25% of total charge time after C/10 charging current is reached.

- Charging automatically resumes when the cell voltage falls below 3.9V/cell.

#### © SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 15 of 83

#### A Carrier Corp. Company

PART NUMBER T82002163

- Fully discharged cells are automatically trickle charged at 10% of the programmed current until the cell voltage exceeds 2.5V/cell.

- Charging terminates if the low-battery condition persists for more than 25% of the total charge time.

- The LTC4006 includes a thermistor sensor input that suspends charging if an unsafe temperature condition is detected and automatically resumes charging when the battery temperature returns to within safe limits.

- The LTC4006 charges a 7.4VDC/6A battery pack.

- The battery pack contains 6 Li-ION cells (2S3P topology).

- The battery pack internally contains a Li-ION protection circuit.

#### **Design Note:**

Note during prototype testing, we supplied 15VDC input to the TSII and the L105 inductor on the LTC4006 Charger Circuit reaches approximately 60-62C during charging (in open air). We will look into adding a passive heat sink to dissipate some of the heat. This was also the case when we supplied 24VDC input to the TSII.

After charge is complete, the L105 inductor will reach 29-30 degrees C (in open air). An NTC Thermistor was used to measure the temperature of the L105 inductor.

3. LM339 Low Power Low Offset Voltage Quad Comparator. (Low-battery detection):

The circuit is comprised of two Compartors. If the Vin(+) terminal is Low and the Vin(-) terminal is High, then the output is Low (current will flow). However if the Vin(+) terminal is High and the Vin(-) terminal is Low, then the output is High (current will not flow).

Therefore, If the Load in the variable input (5 - 27VDC) is  $\leq = 6.5VDC$ , then the Low Batt LED will be ON. However, if the variable input is  $\geq 6.8VDC$ , then the Low Batt LED is OFF. The other input VB = 3.3VDC, which is a fixed voltage input.

4. Battery Pack Protection Circuit (model: 033A-BXA)

- Function: Over charge detection, Over discharge detection, Over current detection, Short detection.

- ELECTRIC CHARACTERISTICS (@ 25C) 1) Over charge detection voltage: 8.5V +/- 50mV

- 2) Over charge release voltage: 8.1V +/- 100mV

- 3) Over discharge detection voltage: 4.8V +/- 160mV

- 4) Over current detection: 4.00A ~ 7.00A

- 5) Over charge detection delay time: 0.55S~2.06S

- 6) Over discharge detection delay time: -67~141ms

- 7) Over current detection delay time: 6.3~14.7ms

- 8) Consumption current

- Operating mode : Max 14.2 μA

Power saving mode : Max0.2μA.

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 16 of 83

#### A Carrier Corp. Company

PART NUMBER T82002163

#### PARTS LIST

| Location         | Description               | Specification            | Size      | Qty | Vendor                                                                |

|------------------|---------------------------|--------------------------|-----------|-----|-----------------------------------------------------------------------|

| U1               | PROTECTION<br>IC          | S-8232ABFT-T2            | TSSOP-8   | 1   | SEIKO                                                                 |

| Q1               | N-CH FET                  | FTD2017A                 | TSSOP-8   | 1   | SANYO                                                                 |

| R1 , R2R<br>3,R4 | CHIP<br>RESISTOR          | 1Kohm (J)                | 1608 Size | 4   | YAGEO,TAMA,                                                           |

| R5               | CHIP<br>RESISTOR          | 4.7Mohm (J)              | 1608 Size | 1   | KAMAYA,<br>ROHM ,SEM ,<br>Any Approved Vendor                         |

| R6               | CHIP<br>POWER<br>RESISTOR | R020ohm                  | 6331 Size | 1   | YAGEO,TAMA,<br>KAMAYA,<br>ROHM ,SEM ,<br>Any Approved Vendor          |

| C1,C2,C3         | CHIP<br>CAPACITOR         | 0.1uF 25V (Z )           | 1608 Size | 3   | YAGEO,PHYCOMP,<br>KYOCERA,ROHM,<br>SAMWHA,SEM,<br>Any Approved Vendor |

| <u>PCB</u>       |                           | FR-4,1oz,0.6t,<br>2Layer | 40*7      | 1   |                                                                       |

5. LM25116 Wide Range Synchronous Buck Controller

- The LM25116 is a synchronous buck controller intended for step-down regulator applications from a high voltage or widely varying input supply.

- The control method is based upon current mode control utilizing an emulated current ramp.

- Current mode control provides inherent line feed-forward, cycle by cycle current limiting and ease of loop compensation.

- The use of an emulated control ramp reduces noise sensitivity of the pulse-width modulation circuit, allowing reliable control of very small duty cycles necessary in high input voltage applications.

- The LM25116 drives external high-side and low-side NMOS power switches with adaptive deadtime control.

- A user-selectable diode emulation mode enables discontinuous mode operation for improved efficiency at light load conditions.

- A low quiescent current shutdown disables the controller and consumes less than 10μA of total input current.

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 17 of 83

#### A Carrier Corp. Company

PART NUMBER T82002163

- Additional features include a high voltage bias regulator, automatic switch-over to external bias for improved efficiency, thermal shutdown, frequency synchronization, cycle by cycle current limit and adjustable line under-voltage lockout.

- The device is available in a power enhanced TSSOP-20 package featuring an exposed die attach pad to aid thermal dissipation

- 7-42VDC input voltage and converts it to 6.25VDC/7A.

- This voltage output is for the Print Head.

#### 6. LT1940, Dual Monolithic 1.4A, 1.1MHz Step-Down Switching Regulator

- The LT1940 is a dual current mode PWM step-down DC/DC converter with internal 2A power switches.

- Both converters are synchronized to a single 1.1MHz oscillator and run with opposite phases, reducing input ripple current.

- The output voltages are set with external resistor dividers, and each regulator has independent shutdown and soft-start circuits.

- Each regulator generates a power-good signal when its output is in regulation, easing power supply sequencing and interfacing with microcontrollers and DSPs.

- The LT1940's 1.1MHz switching frequency allows the use of tiny inductors and capacitors, resulting in a very small dual 1.4A output solution.

- Constant frequency and ceramic capacitors combine to produce low, predictable output ripple voltage.

- With its wide input range of 3.6V to 25V

- Converts it to 3.3V/1.4A and 1.45V/1.4A. 1.45V is for VCORE which is the processor's core voltage.

- 3.3V is for the remaining voltages such as I/O and peripheral supply voltage.

#### 7. LM2940, 1A Low Dropout Regulator

- The LM2940 positive voltage regulator features the ability to source 1A of output current with a dropout voltage of typically 0.5V and a maximum of 1V over the entire temperature range.

- Furthermore, a quiescent current reduction circuit has been included which reduces the ground current when the differential between the input voltage and the output voltage exceeds approximately 3V.

- The quiescent current with 1A of output current and an input-output differential of 5V is therefore only 30 mA.

- Higher quiescent currents only exist when the regulator is in the dropout mode (VIN VOUT ≤ 3V).

- The linear regulator (LDO) take a maximum of 26VDC input voltage and converts it to 5V/1A.

- This voltage output is for printer control board logic and boost converter.

8. LM2733, 0.6/1.6 MHz Boost Converters With 40V Internal FET Switch in SOT-23

- The LM2733 switching regulators are current-mode boost converters operating fixed frequency of 1.6 MHz ("X" option).

- The use of SOT-23 package, made possible by the minimal power loss of the internal 1A switch, and use of small inductors and capacitors result in the industry's highest power density.

- Protection is provided through cycle-by-cycle current limiting and thermal shutdown.

- Internal compensation simplifies design and reduces component count.

- Boost Converter takes 3.3VDC from the Buck Converter and boosts the voltage output to 17.8VDC to 25.5VDC.

#### © SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 18 of 83

#### A Carrier Corp. Company

PART NUMBER T82002163

9. The CAT5113 is a single digitally programmable 10K potentiometer designed as a electronic replacement for mechanical potentiometers.

- The CAT5113 contains a 100-tap series resistor array connected between two terminals RH and RL.

- An up/down counter and decoder that are controlled by three input pins, determines which tap is connected to the wiper, RW.

- The wiper setting, stored in nonvolatile memory, is not lost when the device is powered down and is automatically reinstated when power is returned.

- The wiper can be adjusted to test new system values without affecting the stored setting.

- Wiper-control of the CAT5113 is accomplished with three input control pins, /CS, U/D, and /INC.

The /INC input increments the wiper in the direction which is determined by the logic state of the

- The /INC input increments the wiper in the direction which is determined by the logic state of the U/D input.

- The /CS input is used to select the device and also store the wiper position prior to power down.

The digitally programmable potentiometer can be used as a three-terminal resistive divider or as a

- two terminal variable resistor.

During the event of transitioning the Chip Select from a low to a high state, this will Store the LCD Contrast Voltage in Memory.

During the event of transitioning the Chip Select from a low to a high state and Increment low, this will not store the value and return to standby.

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page **19** of **83**

A Carrier Corp. Company

PART NUMBER T82002163

Trip Strip II Power UP / Down Sequence

+5\

+5V\_LCD

VLCD

+3.3V

LCD

7.4 volt 6.0 ah Li ion Battery

NTER\_MEPS

6.25 VDC Printer Supply

© SENSITECH INC.

**CONFIDENTIAL – CONTROLLED DOCUMENT**

LCD\_BL\_EN

5 Volt Supply

VLCD Boost Converter

VLCD\_EN

Page 20 of 83

#### A Carrier Corp. Company

PART NUMBER T82002163

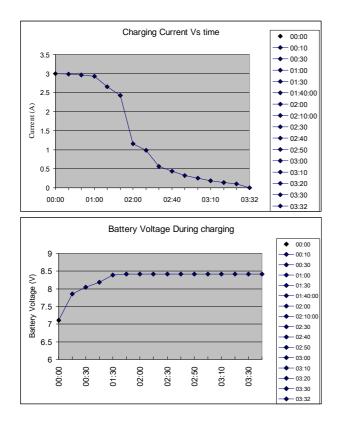

## Li-ION Charging

1. Charging cycle evaluation (Battery is empty before this charge) Chager IC is 4006 and CHG indicator available only

Conditions: Fully Discharge the battery before the charging cycle test. The input power supply is 15V and charging current is 3A

| Charging cycle evaluation                    |                |                           |                      |         |  |

|----------------------------------------------|----------------|---------------------------|----------------------|---------|--|

|                                              | TIME<br>(Hour) | CHARGE<br>CURRENT<br>( A) | BAT<br>VOTAGE(<br>V) | CHG LED |  |

| Start charging                               | 00:00          | 3                         | 7.11                 | ON      |  |

|                                              | 00:10          | 2.98                      | 7.86                 | ON      |  |

|                                              | 00:30          | 2.96                      | 8.05                 | ON      |  |

|                                              | 01:00          | 2.93                      | 8.19                 | ON      |  |

|                                              | 01:30          | 2.65                      | 8.39                 | ON      |  |

|                                              | 01:40:00       | 2.42                      | 8.41                 | ON      |  |

|                                              | 02:00          | 1.16                      | 8.42                 | ON      |  |

|                                              | 02:10:00       | 0.98                      | 8.42                 | ON      |  |

|                                              | 02:30          | 0.56                      | 8.42                 | ON      |  |

|                                              | 02:40          | 0.44                      | 8.42                 | ON      |  |

| Trickle charge                               | 02:50          | 0.32                      | 8.42                 | ON      |  |

| at 1/10 C ;Then the timer auto reset to 1/4T | 03:00          | 0.25                      | 8.42                 | ON      |  |

|                                              | 03:10          | 0.18                      | 8.42                 | ON      |  |

|                                              | 03:20          | 0.14                      | 8.42                 | ON      |  |

|                                              | 03:30          | 0.1                       | 8.42                 | ON      |  |

| Charging completed                           | 03:32          | 0                         | 8.41                 | OFF     |  |

| Total time                                   | 3:32 Hours     |                           |                      |         |  |

Remark: The Max. charging time is around 3 hours. According to specification the charging time is limited to 3 hours ,when charge current is 1/10c then the timer is auto reset <sup>1</sup>/<sub>4</sub> T; So the total time max is 3:45 hours ;and the CHG LED will turn off when charging completed.

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 21 of 83

A Carrier Corp. Company

PART NUMBER T82002163

|                         | Input Voltage (V) | Input Current (A) | Input PD(W) | Output Voltage (V) | Output Current(A) | Output PD(W) | Efficiency(%) |

|-------------------------|-------------------|-------------------|-------------|--------------------|-------------------|--------------|---------------|

|                         | 12                | 2.630             | 31.56       | 7.2                | 3.88              | 27.936       | 88.51711027   |

| CHARGE                  | 24                | 1.400             | 33.6        | 7.5                | 3.8               | 28.5         | 84.82142857   |

| 70/0//                  | 8.4               | 3.530             | 29.652      | 7.14               | 4                 | 28.56        | 96.31728045   |

| 7.2V Output<br>(LM3075) | 24                | 1.330             | 31.92       | 7.14               | 4                 | 28.56        | 89.47368421   |

| 5V                      | 7.13              | 1.120             | 7.9856      | 4.98               | 1                 | 4.98         | 62.36225205   |

| utput(LM2940s-<br>5.0)  | 7.14              | 0.550             | 3.927       | 4.98               | 0.5               | 2.49         | 63.40718105   |

|                         | 7.08              | 0.300             | 2.124       | 3.29               | 0.5               | 1.645        | 77.44821092   |

| 3.3V<br>Dutput(LT1940)  | 7.06              | 0.570             | 4.0242      | 3.28               | 1                 | 3.28         | 81.50688336   |

|                         | 7.09              | 0.162             | 1.14858     | 1.44               | 0.5               | 0.72         | 62.68609936   |

| .45VOutput(LT1<br>940)  | 7.08              | 0.304             | 2.15232     | 1.436              | 1                 | 1.436        | 66.71870354   |

NOTE: THIS WILL NEED TO CHANGE BECAUSE THE LM3075 BUCK CONVERTER HAS BEEN REPLACED.

© SENSITECH INC.

**CONFIDENTIAL – CONTROLLED DOCUMENT**

Page 22 of 83

A Carrier Corp. Company

PART NUMBER T82002163

| 2) External Powe                       | r adapter loading evalu | ation                            |                                            |                                         |                                         |

|----------------------------------------|-------------------------|----------------------------------|--------------------------------------------|-----------------------------------------|-----------------------------------------|

|                                        | Charging at 3A only     | Charging3A+Loading1.<br>45v&0.5A | Charging3A+Loading1.<br>45v&0.5A+3.3V&0.5A | Charging3A+Loading3.3V<br>&1A+7.2V&3.0A | Charging3A+Loading3.3<br>V&1A+7.2V&3.3A |

| AC/DC Adapter<br>Outpout Voltage(V)    | 14.9                    | 14.770                           | 14.89                                      | 14.71                                   | 14.58                                   |

| AC/DC ADAPTER<br>OUTPUT CURRENT<br>(A) | 2.32                    | 2.390                            | 2.56                                       | 4.58                                    | 4.74                                    |

| PD(W)                                  | 34.568                  | 35.300                           | 38.1184                                    | 67.3718                                 | 69.1092                                 |

Note: The adapter 's max PD is 70W.

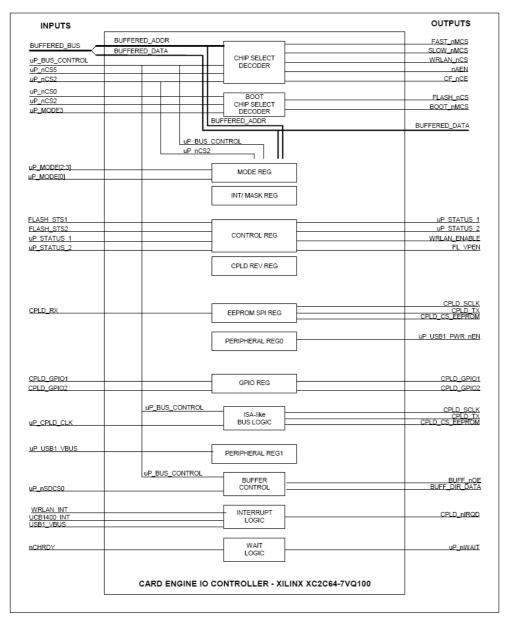

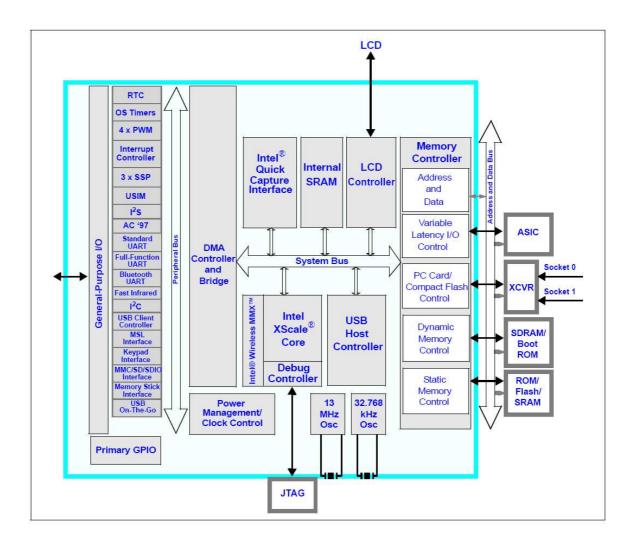

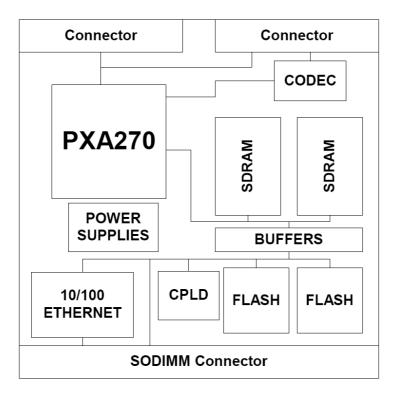

## LogicPD Card Engine

#### Memory Controller Reset and Initialization

The SDRAM interface is disabled on reset. Reset values for the boot ROM are determined by BOOT\_SEL. BOOT ROM is immediately available for reading upon exit from reset, and all memory interface control registers are available for writing.

#### Memory Controller

The internal and external memory-interface structures for the PXA27x processor will be described in detail below. Memory-related registers that configure the memory controller for data transfers to and from static and dynamic memory devices are also described.

The external memory-bus interface for the PXA27x processor supports SDRAM, synchronous, and asynchronous burst-mode and page-mode flash memory, page-mode ROM, SRAM, variable latency I/O (VLIO) memory, PC Card, and CompactFlash expansion memory. Memory types are programmable through the memory-interface configuration registers (see Table 6-44). Memory requests are placed in a four-deep processing queue and processed in the order they are received.

#### Features

The memory controller provides the following features:

- Interfaces to internal synchronous flash and SDRAM devices

- Interfaces to four partitions of SDRAM

- Interfaces to up to 1.0 Gbytes of SDRAM

- Supports 1.8-V JEDEC LP-SDRAM operation at 104 MHz

- Interfaces to six partitions of static memory. Four of these six partitions can be synchronous flash memory.

- Interfaces to up to 384 Mbytes of flash memory

- Interfaces to two sockets of PC Card memory

- Allows an alternate bus master to take control of the bus

- Places the SDRAMs into self-refresh mode before entering sleep, standby, deep-sleep, and

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 23 of 83

A Carrier Corp. Company

PART NUMBER T82002163

frequency-change modes

• Provides signals and controls for fly-by DMA transfers

• Supports non-volatile memory configured as bank 0 from either 16- or 32-bit devices

• Provides three independent output clocks (SDCLK<2:0>) that can be turned on/off separately and can be programmed to be free-running. The clocks can be the same frequency or half the frequency of the input clock, CLK\_MEM. One clock (SDCLK<0>) can also be programmed as one quarter of the input-clock frequency. A fourth output clock (SDCLK<3>) depends on configuration bits used to control SDCLK<0>.

· Provides a programmable power-down mode for saving power

#### Memory Controller Operation

The processor has three different memory spaces: SDRAM, static memory, and PC Card space. SDRAM has four partitions, static memory has six partitions, and PC Card space has two partitions (or sockets). When user software performs a memory burst across the boundary between any two adjacent partitions, the configurations for each partition must be identical. They must have the same external bus width, burst length, and so forth.

In theory, the partitions can be different types of memory sharing the same configuration characteristics. In practice, cross-partition memory bursts are conducted only when the two partitions hold the same memory type. A typical case is a transfer across two SDRAM partitions, 0 and 1, which are mandated to have the same characteristics.

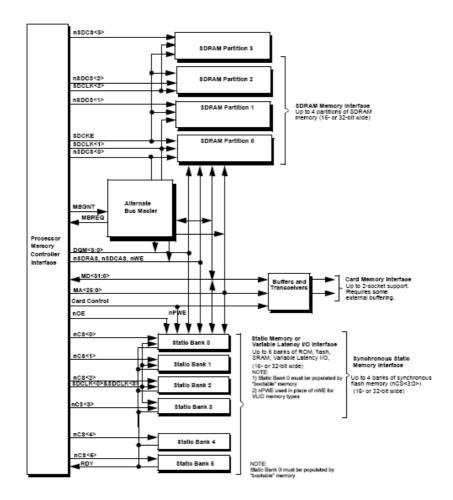

Figure 6-1 is a block diagram of the maximum configuration of the memory controller.

#### Stacked SDRAM and Flash Memory

This section describes memory types that may be supported in the PXA271 and PXA272 processors.

#### Stacked SDRAM

On the Intel® PXA271 processor, SDRAM is stacked and connected to SDRAM partition 0. On systems using the Intel® PXA271 processor, external SDRAM memory chips must not exist within the same SDRAM partition pair as that of the internal stacked SDRAM. This could cause negative signal reflection to the stacked SDRAM device.

For the Intel® PXA271 processor stacked SDRAM, the Intel® PXA27x processor memory controller must be programmed to multiplex the SDRAM address lines out differently because the address lines to the stacked SDRAM are not connected to the usual MA<24:10> lines. The MDCNFG[STACKx] field on a Intel® PXA271 processor must be programmed to 0b01 to send the SDRAM address out on MA<24:23,13:1> for stacked 16-bit SDRAM of this product. For a non stacked part (Intel® PXA270 processor) or flash only stacked part (Intel® PXA272 processor) the MDCNFG[STACKx] field must be programmed to 0b00 to send the SDRAM address out on MA<24:10>.

#### Stacked Flash Memory

A fourth SDCLK, SDCLK<3> is driven by the memory controller, to be used in the PXA271 and PXA272 processors containing stacked flash devices. SDCLK<3> is a buffer duplicate of

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 24 of 83

A Carrier Corp. Company

PART NUMBER T82002163

SDCLK<0> and does not have any control bits of its own to turn it on or off. Use the buffer strength field associated with SDCLK<3> to turn off SDCLK<3> if there is no stacked flash in the system. This buffer strength setting is located in the BSCNTR2 register.

Static partitions 0 and 1 may contain stacked flash. The memory controller must be aware of which static memory partitions contain stacked flash. This is programmed in the SA1111[SXSTACK] field. When a flash device is being written to, the nCS and nWE signals swap functionality from a normal flash write to an off-chip

device. This is shown by timing diagrams in the Intel® PXA27x Processor Family EMTS.

#### Figure 6-1. General Memory Interface Configuration

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 25 of 83

A Carrier Corp. Company

PART NUMBER T82002163

## Synchronous Dynamic Memory (SDRAM) Interface

The processor supports the JEDEC synchronous dynamic memory (SDRAM) interface. The SDRAM interface supports four 16-bit or 32-bit wide partitions of SDRAM. Each partition is allocated 64 or 256 Mbytes of the internal memory map. The actual size of each partition depends on the SDRAM configuration used. The four partitions are divided into two partition pairs: the 0/1 pair and the 2/3 pair. Both partitions in a pair must be identical in size and configuration. Pairs 0/1 and 2/3 can be different. For example, the 0/1 pair can be 100-MHz SDRAM on a 32-bit data bus, while the 2/3 pair can be 50-MHz SDRAM on a 16-bit data bus.

The SDRAM interface includes the following:

- Four partition selects, nSDCS<3:0>

- Four byte mask signals, DQM<3:0>

- 15 multiplexed bank/row/column address signals, MA<24:10>, MA<24:23,14:2>, or

- MA<24:23,13:1>, depending on the MDCNFG[STACKx] setting

- One write enable, nWE

- One column-address strobe (nSDCAS)

- One row-address strobe (nSDRAS)

- One clock enable (SDCKE)

- Two clocks (SDCLK<2:1>)

The processor performs auto-refresh (CBR) during normal operation and supports self-refreshing SDRAM during sleep, deep-sleep, standby, and frequency-change modes. An SDRAM autopowerdown mode bit (MDREFR[APD]) can be set so that the two clocks (SDCLK<2:1>) and the clock-enable signal (SDCKE) to SDRAM are automatically de-asserted whenever none of the corresponding partitions is being accessed.

Each possible SDRAM section of the memory map is referred to as a partition, to distinguish them from banks internal to SDRAM devices.

#### Maximum Row Active Time (TRAS)

The maximum amount of time that any SDRAM row can be active is defined as TRASMAX. When programming MDREFR[DRI], ensure that the refresh cycle time is less than TRASMAX because it is not monitored by the memory controller.

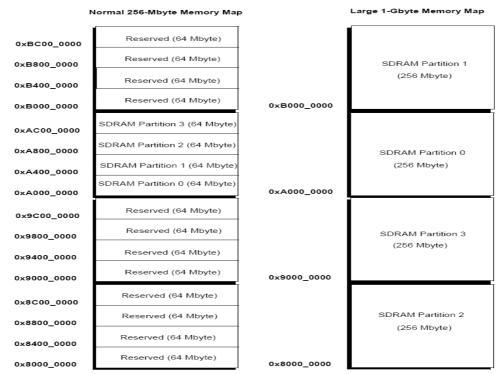

## Programmable Larger SDRAM Memory Space

The read/write MDCNFG register contains control bits for configuring the SDRAM for larger SDRAM configurations than fit in the 64-Mbyte SDRAM partitions. Refer to Table 6-23 for configuration programming. Figure 6-2 shows the programmable option for the SDRAM memory space.

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 26 of 83

A Carrier Corp. Company

PART NUMBER T82002163

#### Programmable SDRAM Memory Map Options (Figure below):

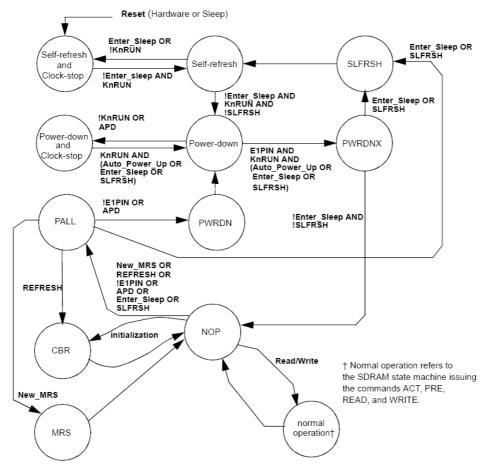

### SDRAM State Machine

Figure 6-4 shows the SDRAM controller states and transitions associated with powering on the PXA27x processor and the SDRAMs properly. Transitions are determined by the overall memory controller state and a few SDRAM power-down, self-refresh status, and control bits. The states that involve multiple SDRAM devices are self-refresh and clock-stop, self-refresh, SLFRSH, PWRDNX, power-down, power-down and clock-stop, PWRDN, PALL, and MRS. The states that involve single SDRAM partitions are ACT, PRE, READ, and WRITE. The MRS command is sent once to configure partition pair 0/1 and a separate MRS command is sent only once to configure partition pair 2/3. The auto-refresh command is issued to memory in the same partition pair at the same time. Therefore, the chip-select signals representing the partition pair are asserted at the same time when the MRS command and auto-refresh is issued from the memory controller to a specific partition pair.

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 27 of 83

A Carrier Corp. Company

PART NUMBER T82002163

#### SDRAM Power-ON State Machine (figure below):

Sleep, deep-sleep, standby, or frequency-change requests cause the SDRAM state machine to enter the self-refresh and clock-stop state. Software must then complete the appropriate reset procedure. Clearing MDREFR[E1PIN] and MDREFR[KnRUN] provides software control of the SDRAM memory system low-power modes.

*Note:* (1) Use these modes with extreme caution, because the resulting states prohibit automatic toggles from mode register set, read, write, and refresh commands.

The Auto\_Power\_Down and Auto\_Power\_Up transitions (made possible by setting the APD bit in MDREFR) provide a completely automatic alternative for minimizing power consumption in the SDRAM system.

(2) Some companion chips require the clock to be present at all times.

Use the following prioritization scheme for transitions out of the NOP state. If enabled with the APD bit, the Auto\_Power\_Down transition occurs when none of the higher priority transitions are asserted. The Auto\_Power\_Up transitions occur when refresh, New\_MRS, or read/write is asserted during the Power\_Down state.

#### © SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 28 of 83

#### A Carrier Corp. Company

PART NUMBER T82002163

Highest Priority- "Enter Sleep" "Set\_SLFRSH" "Clear\_E1PIN" "Refresh" "New\_MRS" "Read/Write" Lowest Priority - "Auto\_Power\_Down" KnRUN = MDREFR[K1RUN] OR MDREFR[K2RUN] Auto\_Power\_Down = MDREFR[APD] Clear\_E1PIN = !(MDREFR[E1PIN]) Set\_SLFRSH = MDREFR[SLFRSH] Enter\_Sleep = Sleep/Deep-Sleep/Standby/ Frequency Change Request and no more transactions to process Auto\_Power\_Up = Read/Write is asserted during the power-down state OR New\_MRS OR Refresh OR !(MDREFR[APD])

#### Synchronous, Static, and Variable-Latency I/O (VLIO)

#### Interfaces

The static memory and VLIO interfaces have six chip selects (nCS<5:0>) and 26 bits of byte address (MA<25:0>) for accesses of up to 64 Mbytes of memory in each of six banks. Alternately, a mode is available to support up to two 128-Mbyte chip selects (nCS<1:0>) with 26 bits of halfword address (MA<0>, MA<25:1>) and two 64-Mbyte chip selects (nCS<5:4>) with 25 bits of byte address (MA<0>). This programmable option resides in the Static Memory Configuration register SA1110[SXENX]. Each chip select is individually programmed to select one of the supported static memory types.

• Non-burst ROM or flash memory (Section 6.4.3.2) is supported on each of nCS<5:0>

• Burst ROM or flash memory with non-burst writes (Section 6.4.3.2) is

supported on each of nCS<5:0>

• SRAM is supported on each of nCS<5:0>

• Variable-latency I/O is supported on each of nCS<5:0>

• Synchronous flash memory is supported on each of nCS<3:0>

The four synchronous-flash memory partitions (nCS<3:0>) are divided into two partition pairs: the 0/1 pair and the 2/3 pair. Both partitions in a pair must be identical in size and configuration. The two pairs can be different. For example, the 0/1 pair can be 66-MHz synchronous flash memory on a 32-bit data bus while the 2/3 pair is 33-MHz synchronous flash memory on a 16-bit data bus. The VLIO interface differs from SRAM in that it allows the use of the data-ready input signal, RDY, to insert a variable number of wait states. For all static memory types, each chip select can be configured individually to a 16-bit or 32-bit wide data bus. The nOE signal is asserted on writes to VLIO devices, and the nWE signal is asserted on writes to all other static devices, both synchronous and asynchronous. For SRAM and VLIO, DQM<3:0> are byte enables for both reads and writes. When the processor comes out of reset, it begins to fetch and execute instructions at address 0x00, which corresponds to memory selected by nCS<0>, which is the required location of the boot ROM. The BOOT\_SEL pin determines the width of the boot memory.

## Asynchronous Static Operation

The static-memory interface is comprised of six chip selects, nCS<5:0>. These six chip selects are

© SENSITECH INC.

**CONFIDENTIAL – CONTROLLED DOCUMENT**

Page 29 of 83

A Carrier Corp. Company

PART NUMBER T82002163

configurable for the following:

- Non-burst ROM or flash memory

- Burst ROM or flash memory

- SRAM

VLIO devices

The VLIO interface differs from SRAM in that it allows the use of a data-ready input signal, RDY, to insert a variable number of memory-cycle wait states. The data bus width for each chip-select region can be programmed to be 16- or 32-bit. The nCS<3:0> signals are also configurable for synchronous static memory. The following list describes the use of nOE,

nWE, and nPWE:

• nOE is asserted for all reads.

• nWE is asserted for flash memory and SRAM writes.

• nPWE is asserted for VLIO writes.

For SRAM and VLIO implementations, DQM<3:0> are used for the write byte-enables, where DQM<3> corresponds to the MSB. The processor supplies 26 bits of byte address for access of up to 64 Mbytes per chip select. This byte address is sent out on the 26 external address pins. If the byte address is unimportant for an application, the lower bit must be truncated for 16-bit systems and the lower two bits must be truncated for 32-bit systems. For reads, the byte address bits is 0. For writes, the byte address bits are summarized in Table 6-10 and Table 6-11.

Table 6-10. 32 Bit Byte Address Bits MA <1.0> for Writes Based on DQM <3.0>

| 101 WITTES Dascu on DQWI <5.0> |          |         |  |  |  |

|--------------------------------|----------|---------|--|--|--|

| Transaction                    | DQM<3:0> | MA<1:0> |  |  |  |

| Word                           | 0b0000   | 0b00    |  |  |  |

| Byte 0                         | 0b1110   | 0b00    |  |  |  |

| Byte 1                         | 0b1101   | 0b01    |  |  |  |

| Byte 2                         | 0b1011   | 0b10    |  |  |  |

| Byte 3                         | 0b0111   | 0b11    |  |  |  |

| Lower half<br>word             | 0b1100   | 0b00    |  |  |  |

| Upper half<br>word             | 0b0011   | 0b10    |  |  |  |

#### Table 6-11. 16-Bit Byte Address Bit MA <0> for Writes Based on DQM <1.0>

| Transaction | DQM<1:0> | MA<0> |

|-------------|----------|-------|

| Half word   | 0b00     | 0b0   |

| Byte 0      | 0b10     | 0b0   |

| Byte 1      | 0b01     | 0b1   |

The MSCx[RTx] fields specify the type of memory:

Non-burst ROM or flash memory

• SRAM

• VLIO

• Burst-of-four ROM or flash memory

© SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 30 of 83

A Carrier Corp. Company

PART NUMBER T82002163

· Burst-of-eight ROM or flash memory

The MSCx[RBWx] fields specify the bus width for the memory space selected by nCS<5:0>. If a 16-bit bus width is specified, transactions occur across data pins MD<15:0>. Use the BOOT\_SEL pin or SXCNFG register to configure nCS<3:0> for synchronous static memory.

#### Asynchronous Flash Memory Interface

The MSCx[RDFx] bit fields define the latency for each read access of non-burst flash memory or the first read access of burst flash memory. The same bit field also controls the nWE de-assertion time during a write cycle to flash memory. The MSCx[RDN] field controls subsequent read access times to burst flash memory. The MSCx[RRR] bit field calculates the minimum period from the nCS signal de-assertion following a read or write and before the start of the read from a different memory.

The following requirements apply to reads from flash memory:

Because flash memory defaults to read-array mode, burst reads from it are permitted, which allows instruction caching and burst reads (DMA and USB host) from flash memory.

Some areas of flash memory might not permit burst reads. When attempting to read from these

areas, do not attempt burst reads. Consult the flash-memory data sheet for more information. Table 6-10. 32-Bit Byte Address Bits MA<1:0> for Writes Based on DQM<3:0>

Transaction DQM<3:0> MA<1:0>

Word 0b0000 0b00

Byte 0 0b1110 0b00

Byte 1 0b1101 0b01

Byte 2 0b1011 0b10

Byte 2 0b1011 0b10

Byte 3 0b0111 0b11

Lower half word 0b1100 0b00

Upper half word 0b1100 0b00

Upper half word 0b0011 0b10

Table 6-11. 16-Bit Byte Address Bit MA<0> for Writes Based on DQM<1:0>

Transaction DQM<1:0> MA<0>

Half word 0b00 0b0

Byte 0 0b10 0b0

Byte 1 0b01 0b1

DQM<1:0>

<

#### Memory Controller

• Software must partition commands and data, then write the commands to flash memory before a read. The memory controller does not insert any commands before flash-memory reads. The following requirements apply to writes to flash memory:

• Flash memory space must be uncacheable and unbuffered.

• Burst writes to flash memory do not exist. Writes to flash memory must be exactly the width of the populated flash devices on the data bus and must be a burst length of one write (for instance, no byte writes to a 32-bit bus, no word writes to a 16-bit bus, no writes of 2 bytes to a 32-bit bus, no writes of 1 byte to a 16-bit bus). The allowable writes are 2 bytes to a 16-bit bus and 4 bytes to a 32-bit bus.

For writes to flash memory, the command and data must be given to the memory controller in separate write instructions. The first instruction carries the command; the next carries the data.

Software must partition commands and data and write them to flash memory in the appropriate sequence. The memory controller does not insert any commands before flash-memory writes.

Because burst writes to flash memory cannot occur, the DMA controller and USB host controller must never write to flash memory. Burst writes to flash memory are not performed.

| © SENSITECI | H INC. |

|-------------|--------|

|-------------|--------|

**CONFIDENTIAL – CONTROLLED DOCUMENT**

Page **31** of **83**

A Carrier Corp. Company

PART NUMBER T82002163

## Synchronous Flash Memory

This section describes how to interface with synchronous flash memory. Synchronous flashmemory operation resets to asynchronous mode (page mode for reads and asynchronous singleword writes). The only way the system can enter synchronous mode (burst-timing synchronous reads and asynchronous single-word writes) is through the Read Configuration register (RCR). Therefore, at boot time, synchronous flash memory operates the same as asynchronous boot ROM. Table 6-12 shows sample programming values for the RCR Synchronous Flash Memory register to ensure proper operation of synchronous flash memory.

Use the values in Table 6-12 as a reference only. Consult the data sheet for the actual part being used. Determine the frequency-configuration code based on the CLK-to-output delay, the CLK period, and the nADV-to-output delay timing parameters for the flash device.

Table 6-12. Sample Read Programming Values for Synchronous Flash Memory (Sheet 1 of 2)

| Bits  | Field Name                   | Value to Program <sup>†</sup>                                     |  |  |  |

|-------|------------------------------|-------------------------------------------------------------------|--|--|--|

| 2:0   | BURST LENGTH                 | 0b010 = 8-word burst                                              |  |  |  |

| 5:3   | reserved                     | 0b000                                                             |  |  |  |

| 6     | CLOCK CONFIGURATION          | 0b1 = Use rising edge of clock                                    |  |  |  |

| 7     | BURST SEQUENCE               | 0b1 = Linear burst order (Intel burst order is not supported)     |  |  |  |

| 8     | WAIT CONFIGURATION           | Not applicable—The processor ignores nWAIT from the flash device. |  |  |  |

| 9     | DATA OUTPUT<br>CONFIGURATION | 0b0 = Hold data for one clock                                     |  |  |  |

| 10    | reserved                     | 0b0                                                               |  |  |  |

| † for | † for configuration register |                                                                   |  |  |  |

#### Table 6-12. Sample Read Programming Values for Synchronous Flash Memory (Sheet 2 of 2)

| Bits                         | Field Name    | Value to Program <sup>†</sup>                                                                                                                                       |

|------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |               | 0b010 -> Code 2 (CAS latency 3)<br>0b011 -> Code 3 (CAS latency 4)                                                                                                  |

|                              |               | 0b100 -> Code 4 (CAS latency 5)                                                                                                                                     |

| 13:11                        | FREQUENCY     | 0b101 -> Code 5 (CAS latency 6)                                                                                                                                     |

| 13.11                        | CONFIGURATION | 0b110 -> Code 6 (CAS latency 7)<br>Choose this value based on the "AC Characteristics—<br>Read-Only<br>Operation" section of the flash-memory device data<br>sheet. |

| 14                           | reserved      | 0b0                                                                                                                                                                 |

| 15                           | READ MODE     | 0b0 = Synchronous operation 0b1 = Asynchronous operation                                                                                                            |

| † for configuration register |               |                                                                                                                                                                     |

#### **ROM Interface**

The processor provides programmable timing for both burst and non-burst ROMs. The value of

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 32 of 83

A Carrier Corp. Company

PART NUMBER T82002163

MSCx[RDF] defines the latency (in memory clock cycles) for the first and all subsequent data beats from non-burst ROMs and the first data beat from a burst ROM. The value of MSCx[RDN] defines the latency for the burst data beats after the first for burst ROMs. Specifying the

MSCx[RRR] value allows a delay on the next access to a different memory space to allow time for the current ROM to three-state the data bus. MSCx[RRR] must be programmed with the maximum TOFF value divided by two, as specified by the ROM manufacturer.

MSC0 < 15:0 > is selected when the address space corresponding to nCS < 0 > is accessed.

#### SRAM Interface Overview

The processor provides a 16- or 32-bit synchronous SRAM interface that uses the DQM pins for byte enables on writes. Bits nCS<5:0> select the SRAM bank to be used. nOE is asserted on reads and nWE is asserted on writes. Address bits MA<25:0> allow up to 64 Mbytes of SRAM per bank to be addressed.

The RDF fields in the MSCx registers define the latencies for a read access. The MSCx[RDN] field controls the nWE low time during a write cycle. MSCx[RRR] is defined as the minimum time from nCS de-assertion to the beginning of a read or write access of any memory bank

Any DMA mode that does not increment the address is not supported for SRAM reads or writes. DCMDx[INCSRCADDR] and DCMDx[INCTRGADDR] clear cause the address not to be incremented. This DMA mode is not supported for SRAM. The only valid memory types for this mode are VLIO and PC Card/CompactFlash devices.

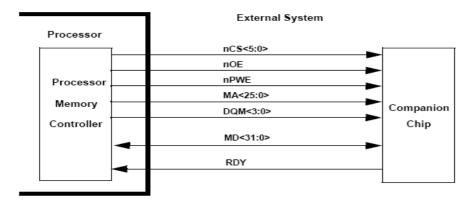

#### Variable-Latency I/O Interface Overview

When a companion chip is used as a VLIO device, its functionality is similar to that of an SRAM with the additional ability to insert a variable number of wait states through the RDY pin. VLIO can be used in the memory space for any of the six static memory locations (nCS<5:0>) by programming the corresponding MSCx[RTx] to 0b100. 13:11 FREQUENCY CONFIGURATION 0b010 -> Code 2 (CAS latency 3) 0b011 -> Code 3 (CAS latency 4) 0b100 -> Code 4 (CAS latency 5) 0b101 -> Code 5 (CAS latency 6) 0b110 -> Code 6 (CAS latency 7) Choose this value based on the "AC Characteristics—Read-Only Operation" section of the flash-memory device data sheet. 14 reserved 0b0 15 READ MODE 0b0 = Synchronous operation 0b1 = Asynchronous operation

Table 6-12. Sample Read Programming Values for Synchronous Flash Memory

Bits Field Name Value to Program

#### Memory Controller

VLIO read accesses differ from SRAM read accesses in that nOE toggles for each beat of a burst. The first nOE assertion occurs two CLK\_MEM cycles after the chip select, nCSx, is asserted. For VLIO writes, nPWE is used instead of nWE, which allows SDRAM refreshes to execute while performing the VLIO transfers.

#### © SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 33 of 83

A Carrier Corp. Company

PART NUMBER T82002163

For both reads and writes from and to VLIO, clearing DCMDx[INCSRCADDR] and DCMDx[INCTRGADDR] causes the source and target addresses not to be incremented to the VLIO interface, which allows port-type VLIO chips to interface with the processor. The only valid memory types for this DMA mode are VLIO and PC Card/CompactFlash devices.

For writes to VLIO, if all byte enables are turned off (masking out the data, DQM = 0b1111), then the write enable is suppressed (nPWE = 1) for this write-beat to VLIO. This suppression can cause a period when nCS is asserted but neither nOE nor nPWE is asserted, which would happen if there is a write of one beat to VLIO with all byte enables turned off. In this case, the memory controller ignores the RDY signal. The RDY signal must not be asserted late if it is to still be asserted, which could interfere with any following transfers. If the VLIO device does not see an nOE or a nPWE, it must not change the state of RDY, keeping it either asserted or de-asserted.

With the exception of the case above, and when entering a frequency change, the memory controller indefinitely waits for the RDY signal to be asserted, which can hang the system if the external VLIO is not responding. To prevent indefinite hangs, set the watchdog timer when starting a VLIO transfer; a watchdog reset occurs if no response is received from the VLIO device. Figure 6-5. Variable-Latency I/O Diagram

## UARTs

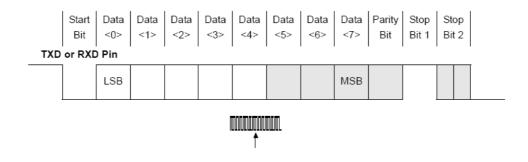

This chapter describes the universal asynchronous receiver/transmitter (UART) serial ports included in the PXA27x processor. The serial ports are controlled using direct-memory access (DMA) or programmed I/O. The PXA27x processor has three UARTs: full-function (FFUART), Bluetooth (BTUART), and standard (STUART). All UARTs use the same programming model.

#### **Overview**

Each serial port contains a UART and a slow infrared-transmit encoder and receive decoder that conform to the IrDA serial-infrared specification.1

Each UART performs serial-to-parallel conversion on data characters received from a peripheral device or a modem and parallel-to-serial conversion on data characters received from the processor. The processor can read a UART's complete status during functional operation. Status information includes the type and condition of transfer operations and error conditions (parity, overrun, framing, or break interrupt) associated with the UART.

Each serial port operates in either FIFO or non-FIFO mode. In FIFO mode, a 64-byte transmit FIFO holds data from the processor until it is transmitted on the serial link, and a 64-byte receive

© SENSITECH INC.

CONFIDENTIAL - CONTROLLED DOCUMENT

Page 34 of 83

A Carrier Corp. Company

PART NUMBER T82002163

FIFO buffers data from the serial link until it is read by the processor. In non-FIFO mode, the transmit and receive FIFOs are bypassed.

Each UART includes a programmable baud-rate generator that can divide the input clock by 1 to (216 - 1). This produces a 16X clock that can be used to drive the internal transmit and receive logic. Software can program interrupts to meet its requirements, which minimizes the number of computations required to handle the communications link. Each UART operates in an environment that is either controlled by software and can be polled or is interrupt-driven. All three UARTs support the 16550A and 167502 functions, but are slightly different in the features

supported.

## Full-Function UART

The FFUART supports modem-control capability. The maximum baud rate is 921,600 bps.

## **Bluetooth UART**

The BTUART is a high-speed UART that supports baud rates up to 921,600 bps and can be connected to a Bluetooth module. It supports the functions in the feature list, but supports only two modem control pins (nCTS and nRTS).

1. Infrared Data Association, Serial Infrared Physical Layer Link Specification, October 17, 1995, Version 1.1

2. The 16550A was originally produced by National Semiconductor Inc. The 16750 is produced as the TL16C750 by Texas Instruments.

The STUART supports all functions in the feature list, but does not support modem-control capability. The maximum baud rate is 921,600 bps.

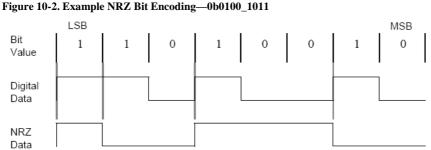

## Compatibility with 16550A and 16750

The UARTs are functionally compatible with the 16550A and 16750 industry standards. Each

- UART supports most of the 16550A and 16750 functions, as well as the following features: • DMA requests for transmit and receive data services

- Divid requests for transmit and receiv

Slow infrared-asynchronous interface

- Non-return-to-zero (NRZ) encoding/decoding function

- 64-byte transmit/receive FIFO buffers

- Programmable receive FIFO trigger threshold

- Auto baud-rate detection

- Auto flow

## Features

The UARTs share the following features:

• Functionally compatible with the 16550A and 16750

Ability to add or delete standard asynchronous communication bits (start, stop, and parity) in the serial data

• Independently controlled transmit, receive, line status, and data-set interrupts

• Programmable baud-rate generator that allows the internal clock to be divided by 1 to (216 - 1)

to generate an internal 16X clock

- Modem control functions (nCTS, nRTS, nDSR, nDTR, nRI, and nDCD)

- Auto-flow capability controls data I/O without generating interrupts:

- nRTS (output) controlled by UART receive FIFO

- nCTS (input) from modem controls UART transmitter

- Fully programmable serial interface:

- 5-, 6-, 7-, or 8-bit characters

- Even, odd, and no-parity detection

## © SENSITECH INC.

CONFIDENTIAL – CONTROLLED DOCUMENT

Page 35 of 83

A Carrier Corp. Company

PART NUMBER T82002163

-1, 1<sup>1</sup>/<sub>2</sub>, or 2 stop-bit generation

- Baud-rate generation up to 921 kbps for all UARTs

- False start-bit detection

- 64-byte transmit FIFO

- 64-byte receive FIFO

- Complete status-reporting capability

- Ability to generate and detect line breaks

- Internal diagnostic capabilities that include:

- Loopback controls for communications-link fault isolation

- Break, parity, and framing-error simulation

- Fully prioritized interrupt system controls

- Separate DMA requests for transmit and receive data services

• Slow infrared asynchronous interface that conforms to the Infrared Data Association (IrDA) specification

## Signal Descriptions

Table 10-1 lists and describes each external signal that is connected to a UART module. The pins transmit digital CMOS-level signals and are connected to the PXA27x processor through GPIOs. Refer to Section 24, "General-Purpose I/O Controller" for details on the GPIOs.

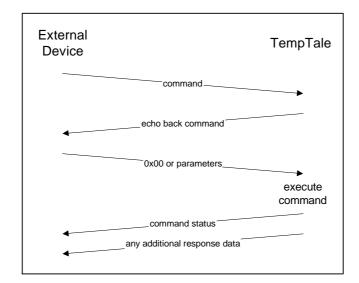

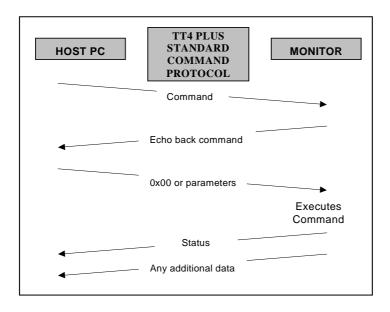

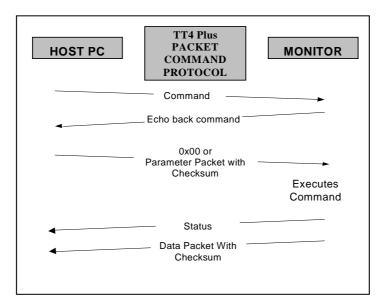

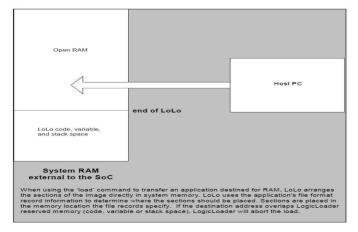

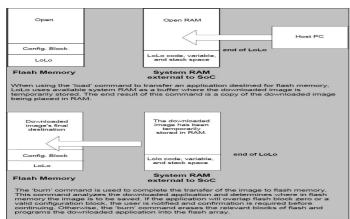

#### Table 10-1. UARTs I/O Signal Descriptions (Sheet 1 of 2)