# BLE121LR

DATA SHEET

Sunday, 08 June 2014

Version 1.12

## Copyright © 2000-2014 Bluegiga Technologies

All rights reserved.

Bluegiga Technologies assumes no responsibility for any errors which may appear in this manual. Furthermore, Bluegiga Technologies reserves the right to alter the hardware, software, and/or specifications detailed here at any time without notice and does not make any commitment to update the information contained here. Bluegiga's products are not authorized for use as critical components in life support devices or systems.

The WRAP is a registered trademark of Bluegiga Technologies

The *Bluetooth* trademark is owned by the Bluetooth SIG Inc., USA and is licensed to Bluegiga Technologies. All other trademarks listed herein are owned by their respective owners.

## **VERSION HISTORY**

| Version | Comment                                                               |

|---------|-----------------------------------------------------------------------|

| 1.1     | First release                                                         |

| 1.11    | Standard gain mode option for the receiver added. Figure 22 corrected |

| 1.12    | FCC and IC info added                                                 |

# TABLE OF CONTENTS

| 1           | Bl                                                       | LE121L                                                                                        | R Product numbering                                                                            | 6                                                              |

|-------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2           | Pi                                                       | inout ar                                                                                      | nd Terminal Description                                                                        | 7                                                              |

|             | 2.1                                                      | I/O F                                                                                         | Ports                                                                                          | 10                                                             |

|             | 2.                                                       | .1.1                                                                                          | I/O Configurations                                                                             | 10                                                             |

|             | 2.                                                       | .1.2                                                                                          | Reserved I/O's                                                                                 | 10                                                             |

|             | 2.2                                                      | UAF                                                                                           | Т                                                                                              | 10                                                             |

| 3           | El                                                       | lectrica                                                                                      | Characteristics                                                                                | 11                                                             |

|             | 3.1                                                      | Abso                                                                                          | plute Maximum Ratings                                                                          | 11                                                             |

|             | 3.2                                                      | Rec                                                                                           | ommended Operating Conditions                                                                  | 11                                                             |

|             | 3.3                                                      | DC                                                                                            | Characteristics                                                                                | 11                                                             |

|             | 3.4                                                      | Curr                                                                                          | ent Consumption                                                                                | 12                                                             |

|             | 3.5                                                      | RF (                                                                                          | Characteristics                                                                                | 13                                                             |

| 4           | Pł                                                       | hysical                                                                                       | Dimensions                                                                                     | 17                                                             |

| 5           | Po                                                       | ower-O                                                                                        | n Reset and Brownout Detector                                                                  | 19                                                             |

|             |                                                          |                                                                                               |                                                                                                |                                                                |

| 6           | D                                                        | esign G                                                                                       | uidelines                                                                                      | 20                                                             |

| -           | Do<br>6.1                                                | U                                                                                             | uidelines<br>eral Design Guidelines                                                            |                                                                |

|             |                                                          | Gen                                                                                           |                                                                                                | 20                                                             |

|             | 6.1                                                      | Gen<br>Layo                                                                                   | eral Design Guidelines                                                                         | 20<br>20                                                       |

|             | 6.1<br>6.2<br>6.3                                        | Gen<br>Layo<br>BLE                                                                            | eral Design Guidelines<br>out Guide Lines                                                      | 20<br>20<br>21                                                 |

|             | 6.1<br>6.2<br>6.3<br>So                                  | Gen<br>Layo<br>BLE<br>olderino                                                                | eral Design Guidelines<br>out Guide Lines<br>121LR-A Layout Guide                              | 20<br>20<br>21<br>23                                           |

| 7           | 6.1<br>6.2<br>6.3<br>So<br>Bl                            | Gen<br>Layo<br>BLE<br>oldering<br>lock dia                                                    | eral Design Guidelines<br>out Guide Lines<br>121LR-A Layout Guide<br>g Recommendations         | 20<br>20<br>21<br>23<br>24                                     |

| 7<br>8<br>9 | 6.1<br>6.2<br>6.3<br>So<br>Bl                            | Gen<br>Layo<br>BLE<br>olderino<br>lock dia<br>ertificat                                       | eral Design Guidelines<br>out Guide Lines<br>121LR-A Layout Guide<br>g Recommendations<br>gram | 20<br>20<br>21<br>23<br>24<br>27                               |

| 7<br>8<br>9 | 6.1<br>6.2<br>6.3<br>So<br>Bl<br>Co                      | Gen<br>Layo<br>BLE<br>olderino<br>lock dia<br>ertificat<br>Blue                               | eral Design Guidelines<br>out Guide Lines<br>121LR-A Layout Guide                              | 20<br>20<br>21<br>23<br>24<br>27<br>27                         |

| 7<br>8<br>9 | 6.1<br>6.2<br>6.3<br>Si<br>Bi<br>Ci<br>9.1<br>9.2        | Gen<br>Layo<br>BLE<br>oldering<br>lock dia<br>ertificat<br>Blue<br>FCC                        | eral Design Guidelines<br>out Guide Lines                                                      | 20<br>20<br>21<br>23<br>24<br>27<br>27<br>27                   |

| 7<br>8<br>9 | 6.1<br>6.2<br>6.3<br>Si<br>Bi<br>Ci<br>9.1<br>9.2        | Gen<br>Layo<br>BLE<br>olderino<br>lock dia<br>ertificat<br>Blue<br>FCC                        | eral Design Guidelines<br>put Guide Lines                                                      | 20<br>20<br>21<br>23<br>24<br>27<br>27<br>27<br>28             |

| 7<br>8<br>9 | 6.1<br>6.2<br>6.3<br>So<br>Bl<br>Co<br>9.1<br>9.2<br>9.2 | Gen<br>Layo<br>BLE<br>oldering<br>lock dia<br>ertificat<br>Blue<br>FCC<br>.2.1<br>CE .        | eral Design Guidelines<br>but Guide Lines                                                      | 20<br>20<br>21<br>23<br>24<br>27<br>27<br>27<br>28<br>30       |

| 7<br>8<br>9 | 6.1<br>6.2<br>6.3<br>Si<br>Bl<br>Ci<br>9.1<br>9.2<br>9.3 | Gen<br>Layo<br>BLE<br>oldering<br>lock dia<br>ertificat<br>Blue<br>FCC<br>.2.1<br>CE .<br>MIC | eral Design Guidelines                                                                         | 20<br>20<br>21<br>23<br>24<br>27<br>27<br>27<br>28<br>30<br>30 |

blue giga

### DESCRIPTION

BLE121LR is a Bluetooth Smart Long Range targeted for Bluetooth Smart module applications where the best possible RF performance and range are required. At +8 dBm TX power and -98 dBm sensitivity BLE121LR has best-in-class RF performance and can provide Bluetooth Smart connectivity up to 450 meters. BLE121LR integrates all features required for a Bluetooth Smart application: Bluetooth radio, software stack and GATT based profiles. and it can also host end user applications, which means no external micro controller is required in size, price or power constrained devices. BLE121LR Bluetooth Smart module also has flexible hardware interfaces to connect to different peripherals or sensors. Although BLE121LR *Bluetooth* Smart Lona Range Module is target for applications requiring high RF performance, it is still has relatively low power consumption and can be power using a standard 3V coin cell batteries.

#### **APPLICATIONS:**

- Smart home accessories

- beacon devices

- Health and fitness sensors

- Medical sensors

- iPhone and iPad accessories

- Security and proximity tags

### **KEY FEATURES:**

- Bluetooth v. 4.0 Single Mode Compliant

- Master and slave modes

- Up to eight connections

- Integrated *Bluetooth* Smart Stack

- o GAP, ATT and GATT

- o Bluetooth Smart profiles

- Best-in-Class RF Performance

- Transmit power : +8 dBm

- Receiver sensitivity: -98 dBm

- Range up to 450 meters

- Low Current Consumption

- Transmit: 36 mA (+8 dBm)

- Receive: 33 mA (-98 dBm)

- Power mode 3: 0.5 uA

- Flexible Peripheral Interfaces

- UART and SPI

- o I2C, PWM and GPIO

- o 12-bit ADC

- Host Interfaces:

- o UART

- Programmable 8051 Processor for Stand-alone Operation

- Simple Bluegiga BGScript<sup>™</sup> scripting language for quick application development

- o Bluegiga Profile Toolkit<sup>™</sup> allowing the quick development of GATT based profiles

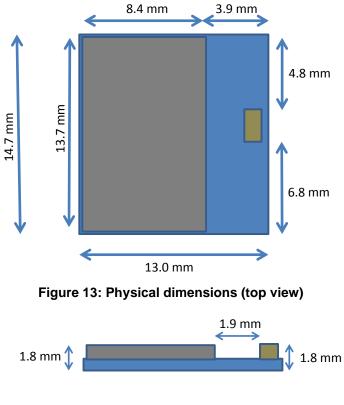

- Dimensions: 14.7 x 13.0 x 1.8 mm

- *Bluetooth*, CE, FCC, IC, South Korea and Japan qualified

# 1 BLE121LR Product numbering

## Available products and product codes

| Product code     | Description                                                         |

|------------------|---------------------------------------------------------------------|

| BLE121LR-A-M256K | BLE121LR with an embedded chip antenna and with 256k internal flash |

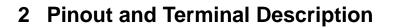

### Figure 1: BLE121LR

| Pin Number               | Pin Name | Pad Type       | Description      |

|--------------------------|----------|----------------|------------------|

| 1-3, 14, 15,<br>22 31-36 | GND      | GND            | GND              |

| 13                       | AVDD     | Supply voltage |                  |

| 23                       | DVDD     | Supply voltage |                  |

| 7                        | Reset    | Reset          | Active low reset |

### Table 1: Supply and RF Terminal Descriptions

| Pin Number | Pin Name | Pad Type | Description                                                           |

|------------|----------|----------|-----------------------------------------------------------------------|

| 6          | P0_0     | I/O      | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping |

| 5          | P0_1     | I/O      | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping |

| 4          | P0_2     | I/O      | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping |

| 8          | P0_3     | I/O      | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping |

| P0_4 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0_5 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P0_6 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P0_7 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P1_2 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P1_3 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P1_4 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P1_5 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P1_6 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P2_0 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P2_1 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

| P2_2 | I/O                                                                                  | Configurable Input/Output. See Table 4:<br>Peripheral I/O Pin Mapping                                                                                                                                                         |

|      | P0_5<br>P0_6<br>P0_7<br>P1_2<br>P1_3<br>P1_3<br>P1_4<br>P1_5<br>P1_6<br>P2_0<br>P2_1 | P0_5       I/O         P0_6       I/O         P0_7       I/O         P1_2       I/O         P1_3       I/O         P1_4       I/O         P1_5       I/O         P1_6       I/O         P2_0       I/O         P2_1       I/O |

Table 2: Configurable I/O Terminals

| Pin Number | Pin Name   | Pad Type  | Description                                            |

|------------|------------|-----------|--------------------------------------------------------|

| 24         | SCL        | I2C clock |                                                        |

| 25         | SDA        | I2C data  |                                                        |

| 18         | DCDC_CNTRL | Output    | On / by-pass control for an external<br>DCDC converter |

Table 3: Non-configurable Terminals

| PERIPHERAL /<br>FUNCTION |       | P0 |    |    |    |    |    |    | P1 |        |    |    |    |    | P2 |        |        | HARDWARE.XML Example (* |    |   |                                                                        |  |  |

|--------------------------|-------|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|--------|--------|-------------------------|----|---|------------------------------------------------------------------------|--|--|

|                          |       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | 7      | 6  | 5  | 4  | 3  | 2  | 1      | 0      | 2                       | 1  | 0 |                                                                        |  |  |

| ADC                      |       | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |        |    |    |    |    |    |        |        |                         |    |   |                                                                        |  |  |

| USART 0 SPI (**          | Alt.1 |    |    | С  | SS | MO | MI |    |    |        |    |    |    |    |    |        |        |                         |    |   | <usart <="" alternate="1" channel="0" mode="spi_master" td=""></usart> |  |  |

|                          | Alt.2 |    |    |    |    |    |    |    |    |        |    | MO | MI | С  | SS |        |        |                         |    |   | <usart <="" alternate="2" channel="0" mode="spi_master" td=""></usart> |  |  |

| USART 0 UART             | Alt.1 |    |    | RT | СТ | ТΧ | RX |    |    |        |    |    |    |    |    |        |        |                         |    |   | <usart <="" alternate="1" channel="0" mode="uart" td=""></usart>       |  |  |

| USART U UART             | Alt.2 |    |    |    |    |    |    |    |    | D<br>C |    | ТΧ | RX | RT | СТ |        |        |                         |    |   | <usart <="" alternate="2" channel="0" mode="uart" td=""></usart>       |  |  |

| USART 1 SPI (**          | Alt.1 |    |    | MI | МΟ | С  | SS |    |    | D      |    |    |    |    |    | R      | R      |                         |    |   | <usart <="" alternate="1" channel="1" mode="spi_master" td=""></usart> |  |  |

|                          | Alt.2 |    |    |    |    |    |    |    |    | С      | MO | С  | SS |    |    | Е      | Е      |                         |    |   | <usart <="" alternate="2" channel="1" mode="spi_master" td=""></usart> |  |  |

| USART 1 UART             | Alt.1 |    |    | RX | ТΧ | RT | СТ |    |    | С      |    |    |    |    |    | S<br>E | S<br>E |                         |    |   | <usart <="" alternate="1" channel="1" mode="uart" td=""></usart>       |  |  |

| 00/11110/111             | Alt.2 |    |    |    |    |    |    |    |    | 0      | ТΧ | RT | СТ |    |    | R      | R      |                         |    |   | <usart <="" alternate="2" channel="1" mode="uart" td=""></usart>       |  |  |

| TIMER 1                  | Alt.1 |    | 4  | 3  | 2  | 1  | 0  |    |    | Ν      |    |    |    |    |    | V      | V      |                         |    |   | <timer <="" alternate="1" index="1" td=""></timer>                     |  |  |

|                          | Alt.2 | 3  | 4  |    |    |    |    |    |    | T<br>R |    |    |    |    | 0  | E      | E      |                         |    |   | <timer <="" alternate="2" index="1" td=""></timer>                     |  |  |

| TIMER 3                  | Alt.1 |    |    |    |    |    |    |    |    | 0      |    |    | 1  | 0  |    |        |        |                         |    |   | <timer <="" alternate="1" index="3" td=""></timer>                     |  |  |

|                          | Alt.2 |    |    |    |    |    |    |    |    | L      | 0  |    |    |    |    |        |        |                         |    |   | <timer <="" alternate="2" index="3" td=""></timer>                     |  |  |

| TIMER 4                  | Alt.1 |    |    |    |    |    |    |    |    |        |    |    |    |    |    |        |        |                         |    |   | <timer <="" alternate="1" index="4" td=""></timer>                     |  |  |

|                          | Alt.2 |    |    |    |    |    |    |    |    |        |    |    |    |    |    |        |        |                         |    | 0 | <timer <="" alternate="2" index="4" td=""></timer>                     |  |  |

| DEBUG                    |       |    |    |    |    |    |    |    |    |        |    |    |    |    |    |        |        | DC                      | DD |   |                                                                        |  |  |

| OBSSEL                   |       |    |    |    |    |    |    |    |    |        |    | 5  | 4  | 3  | 2  |        |        |                         |    |   |                                                                        |  |  |

\*) Refer to BLE Configuration Guide for detailed settings

\*\*) SS is the slave select signal when BLE121LR is set as SPI slave. When set as SPI master, any available I/O can be used as chip select signal of BLE121LR

NOTE: Pins configured as peripheral I/O signals do not have pull-up / -down capability

Table 4: Peripheral I/O Pin Mapping

# 2.1 I/O Ports

## 2.1.1 I/O Configurations

Each I/O port can be configured as an input or output. When configured as input, each I/O port can also be configured with internal pull-up, pull-down or tri-state. Pull-down or pull-up can only be configured to whole port, not individual pins. Unused I/O pins should have defined level and not be floating. See the BLE Configuration Guide for more information about the configuration.

During reset the I/O pins are configured as inputs with pull-ups.

Note: Pins configured as peripheral I/O signals do not have pull-up / -down capability

## 2.1.2 Reserved I/O's

The high current driving pins P1\_0 and P1\_1 are reserved for the internal RF front end control. These pins are not exposed in BLE121LR and they can't be used for application purposes.

P1\_7 is also used for the RF front end control but as an output it can be used to control the external DCDC for lowering the peak current drawn from the battery. The function of P1\_7 can't be altered. If external DCD is not used then P1\_7 should be left not connected.

# 2.2 UART

UART baud rate can be configured up 2 Mbps. See the BLE Configuration Guide for more information. Following table lists commonly used baud rates for BLE121LR

| Baud rate (bps) | Error (%) |

|-----------------|-----------|

| 2400            | 0.14      |

| 4800            | 0.14      |

| 9600            | 0.14      |

| 14 400          | 0.03      |

| 19 200          | 0.14      |

| 28 800          | 0.03      |

| 38 400          | 0.14      |

| 57 600          | 0.03      |

| 76 800          | 0.14      |

| 115 200         | 0.03      |

| 230 400         | 0.03      |

### Table 5: Commonly used baud rates for BLE121LR

# **3** Electrical Characteristics

# 3.1 Absolute Maximum Ratings

**Note:** These are absolute maximum ratings beyond which the module can be permanently damaged. These are not maximum operating conditions. The maximum recommended operating conditions are in the Table 7.

| Rating                   | Min     | Max     | Unit |

|--------------------------|---------|---------|------|

| Storage Temperature      | -40     | +85     | °C   |

| AVDD, DVDD               | -0.3    | 3.9     | V    |

| Other Terminal Volatages | VSS-0.4 | VDD+0.4 | V    |

### **Table 6: Absolute Maximum Ratings**

## 3.2 Recommended Operating Conditions

| Rating                       | Min | Max | Unit |

|------------------------------|-----|-----|------|

| Operationg Temperature Range | -40 | +85 | °C   |

| AVDD, DVDD (*,**,***         | 2.0 | 3.6 | V    |

### **Table 7: Recommended Operating Conditions**

- \*) All supply nets must have the same voltage

- \*\*) Supply voltage noise should be less than 10mVpp. Excessive noise at the supply voltage will reduce the RF performance.

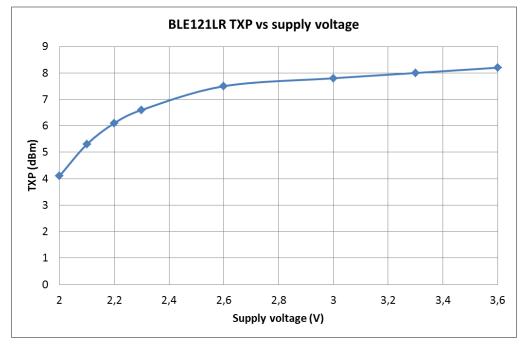

- \*\*\*) The supply voltage has an impact on the TX power, see Figure 7.

# 3.3 DC Characteristics

| Parameter                               | Test Conditions  | Min | Тур | Мах | Unit |

|-----------------------------------------|------------------|-----|-----|-----|------|

| Logic-0 input voltage                   |                  |     |     | 0.5 | V    |

| Logic-1 input voltage                   | DVDD =3V0        | 2.5 |     |     | V    |

| Logic-0 input current                   | Input equals 0V  | -50 |     | 50  | nA   |

| Logic-1 input current                   | Input equals VDD | -50 |     | 50  | nA   |

| I/O pin pull-up and pull-down resistors |                  |     | 20  |     | kΩ   |

For detailed I/O terminal characteristic and timings refer to the CC2541 datasheet available in (<u>http://www.ti.com/lit/ds/symlink/cc2541.pdf</u>)

### Table 8: DC Characteristic

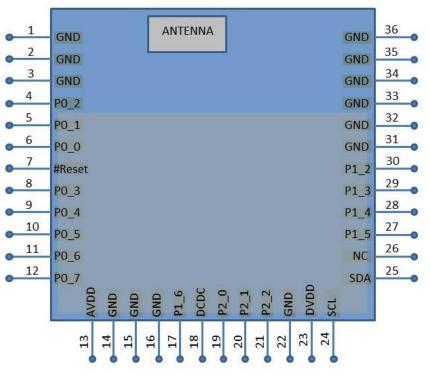

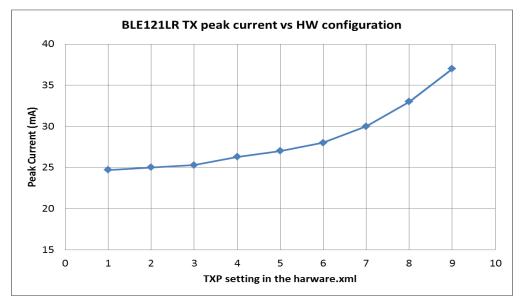

# 3.4 Current Consumption

| Power mode   | hardware.xml                                                           | Min | Тур | Max | Unit |

|--------------|------------------------------------------------------------------------|-----|-----|-----|------|

| Transmit     | <txpower power="1"></txpower><br><slow clock="" enable="true"></slow>  |     | 25  |     | mA   |

|              | <txpower power="9"></txpower><br><slow clock="" enable="true"></slow>  |     | 36  |     | mA   |

|              | <txpower power="9"></txpower><br><slow clock="" enable="false"></slow> |     | 38  |     | mA   |

| Receive      | <slow clock="" enable="true"></slow>                                   |     | 28  |     | mA   |

|              | <slow clock="" enable="false"></slow>                                  |     | 33  |     | mA   |

| Power mode 1 |                                                                        |     | 2.7 |     | mA   |

| Power mode 2 |                                                                        |     | 1.3 |     | μA   |

| Power mode 3 |                                                                        |     | 0.5 |     | μA   |

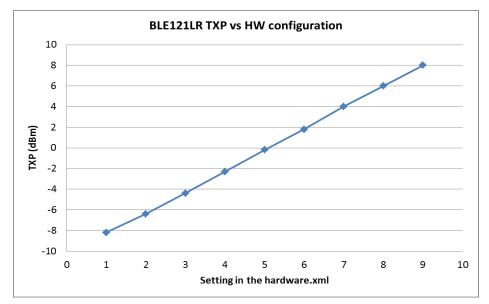

Figure 2: BLE121LR TX peak current as a function of the setting in the HW configuration file

Figure 3: BLE121LR TX peak current as a function of hardware.xml TXP setting (Example: <txpower power="<u>9</u>" bias="5" />)

Figure 4: Typical current consumption profile while advertising

# 3.5 RF Characteristics

| Rating                                                | Min | Тур    | Мах | Unit |

|-------------------------------------------------------|-----|--------|-----|------|

| Transmit power                                        |     | 8      |     | dBm  |

| Transmit power variation within BT band               |     | 1      | 1.8 | dB   |

| Transmit power variation within the temperature range |     | +/-1.5 |     | dB   |

| Sensitivity (Default, high gain mode, PER 30.8%)      |     | -98    |     | dBm  |

| Sensitivity (standard gain mode, PER 30.8%) (*        |     | -92    |     | dBm  |

\*) Standard gain mode can be set using an API command. Please refer to the Bluetooth Smart Software API Reference document.

### Figure 5: BLE121LR RF characteristics

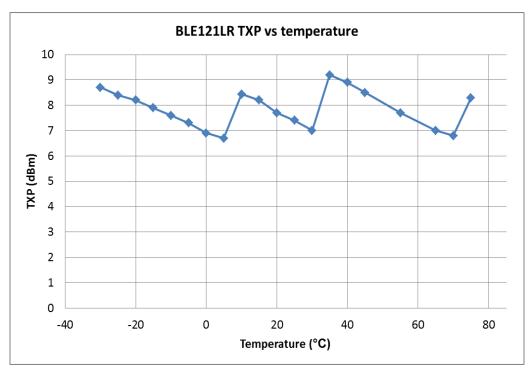

Figure 6: Typical transmit power as a function of temperature

Figure 7: BLE121LR transmit power as a function of supply voltage

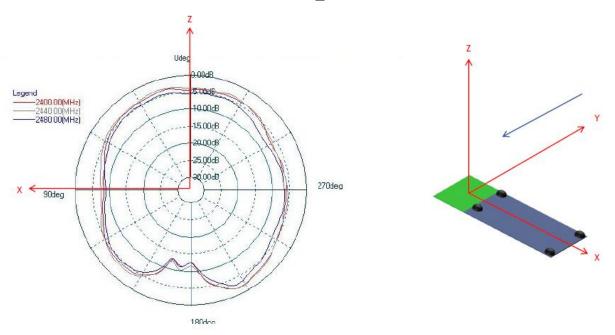

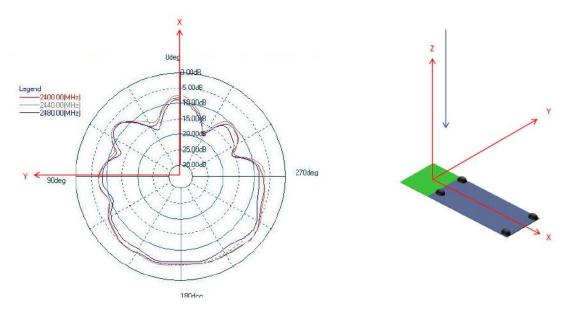

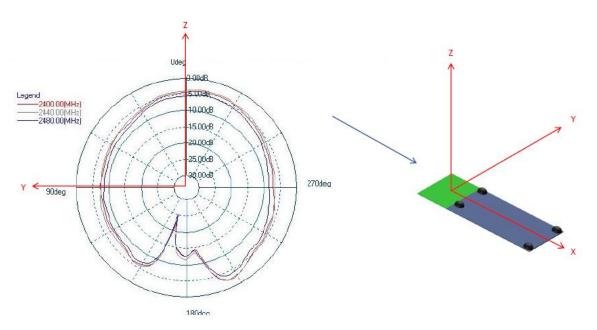

Figure 9: Radiation pattern of BLE121LR when mounted to the DKBLE

Figure 10: Radiation pattern of BLE121LR when mounted to the DKBLE

Figure 11: Radiation pattern of BLE121LR when mounted to the DKBLE

# **4** Physical Dimensions

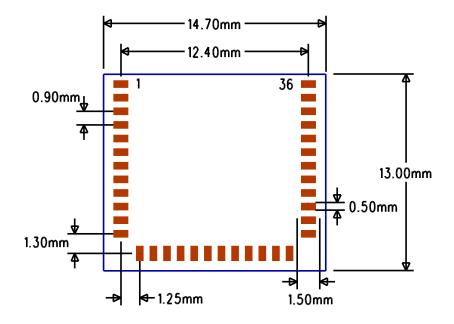

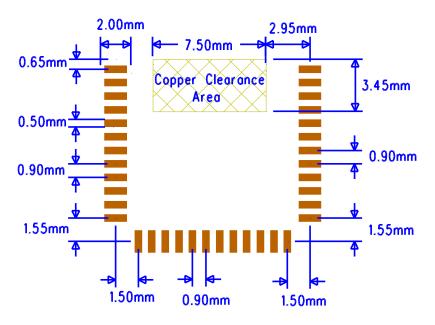

Figure 12: Footprint of BLE121LR (top view)

Figure 14: Physical dimensions (side view)

Bluegiga Technologies Oy

Figure 15: Recommended land pattern for BLE121LR-A

# 5 Power-On Reset and Brownout Detector

BLE121LR includes a power-on reset (POR), providing correct initialization during device power on. It also includes a brownout detector (BOD) operating on the regulated 1.8-V digital power supply only. The BOD protects the memory contents during supply voltage variations which cause the regulated 1.8-V power to drop below the minimum level required by digital logic, flash memory, and SRAM. When power is initially applied, the POR and BOD hold the device in the reset state until the supply voltage rises above the power-on-reset and brownout voltages.

# 6 Design Guidelines

## 6.1 General Design Guidelines

BLE121LR can be used directly with a coin cell battery. Due to relatively high internal resistance of a coin cell battery it is recommended to place a 100uF capacitor in parallel with the battery. The internal resistance of a coin cell battery is initially in the range of 10 ohms but the resistance increases rapidly as the capacity is used. Basically the higher the value of the capacitor the higher is the effective capacity of the battery and thus the longer the life time for the application. The minimum value for the capacitor depends on the end application and the maximum transmit power used. The leakage current of a 100uF capacitor is in the range of 0.5 uA to 3 uA and generally ceramic capacitors have lower leakage current than tantalum or aluminum electrolytic capacitors.

Optionally TI's TPS62730 can be used to reduce the current consumption during TX/RX and data processing stages. TPS62730 is an ultra-low power DC/DC converter with by-pass mode and will reduce the current consumption during transmission nominally by ~20% when using 3V coin cell battery.

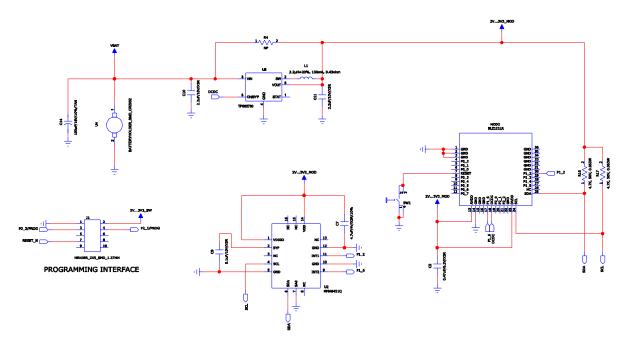

# Figure 16: Example schematic for BLE121LR with a coin cell battery, TPS62730 DCDC converter and an I2C accelerometer

## 6.2 Layout Guide Lines

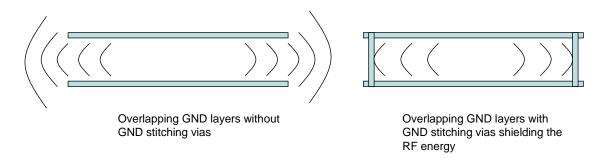

Use good layout practices to avoid excessive noise coupling to supply voltage traces or sensitive analog signal traces. If using overlapping ground planes use stitching vias separated by max 3 mm to avoid emission from the edges of the PCB. Connect all the GND pins directly to a solid GND plane and make sure that there is a low impedance path for the return current following the signal and supply traces all the way from start to the end.

A good practice is to dedicate one of the inner layers to a solid GND plane and one of the inner layers to supply voltage planes and traces and route all the signals on top and bottom layers of the PCB. This

arrangement will make sure that any return current follows the forward current as close as possible and any loops are minimized.

Figure 18: Use of stitching vias to avoid emissions from the edges of the PCB

# 6.3 BLE121LR-A Layout Guide

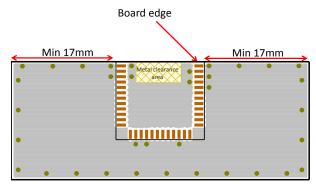

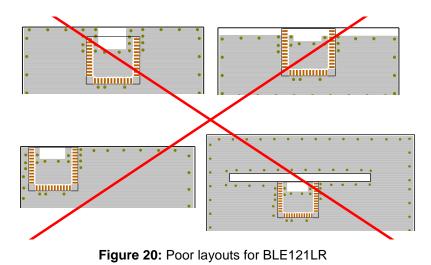

For optimal performance of the antenna place the module at the edge of the PCB as shown in the Figure 19. Do not place any metal (traces, components, battery etc.) within the clearance area of the antenna. Connect all the GND pins directly to a solid GND plane. Place the GND vias as close to the GND pins as possible. Use good layout practices to avoid any excessive noise coupling to signal lines or supply voltage lines. Do not place plastic or any other dielectric material in touch with the antenna.

Figure 19: Recommended layout for BLE121LR-A

# 7 Soldering Recommendations

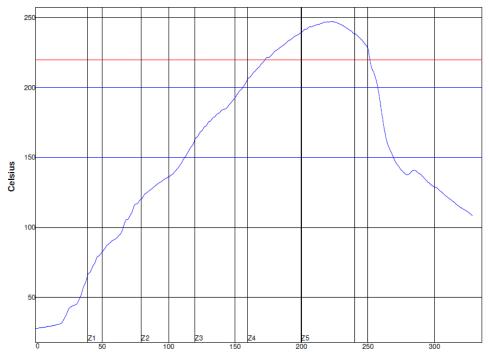

BLE121LR is compatible with industrial standard reflow profile for Pb-free solders. The reflow profile used is dependent on the thermal mass of the entire populated PCB, heat transfer efficiency of the oven and particular type of solder paste used. Consult the datasheet of particular solder paste for profile configurations.

Bluegiga Technologies will give following recommendations for soldering the module to ensure reliable solder joint and operation of the module after soldering. Since the profile used is process and layout dependent, the optimum profile should be studied case by case. Thus following recommendation should be taken as a starting point guide.

- Refer to technical documentations of particular solder paste for profile configurations

- Avoid using more than one flow.

- Reliability of the solder joint and self-alignment of the component are dependent on the solder volume. Minimum of 150µm stencil thickness is recommended.

- Aperture size of the stencil should be 1:1 with the pad size.

- A low residue, "no clean" solder paste should be used due to low mounted height of the component.

Figure 21: Reference reflow profile

# 8 Block diagram

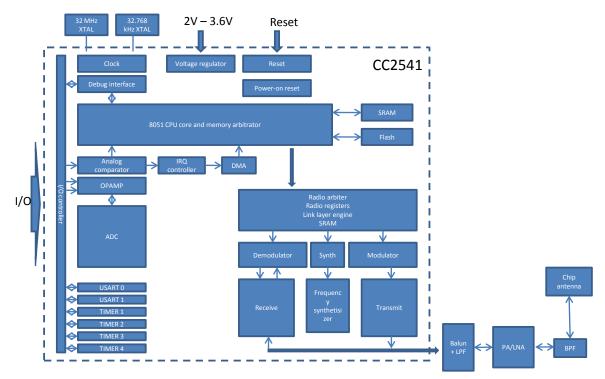

BLE121LR is based on TI's CC2541 chip. Embedded 32 MHz and 32.678 kHz crystals are used for clock generation. Matched balun and low pass filter provide optimal radio performance with extremely low spurious emissions.

Figure 22: Simplified block diagram of BLE121LR

### **CPU and Memory**

The 8051 CPU core is a single-cycle 8051-compatible core. It has three different memory access buses (SFR, DATA, and CODE/XDATA), a debug interface, and an 18-input extended interrupt unit.

The memory arbiter is at the heart of the system, as it connects the CPU and DMA controller with the physical memories and all peripherals through the SFR bus. The memory arbiter has four memory-access points, access of which can map to one of three physical memories: an SRAM, flash memory, and XREG/SFR registers. It is responsible for performing arbitration and sequencing between simultaneous memory accesses to the same physical memory.

The SFR bus is a common bus that connects all hardware peripherals to the memory arbiter. The SFR bus also provides access to the radio registers in the radio register bank, even though these are indeed mapped into XDATA memory space.

The 8-KB SRAM maps to the DATA memory space and to parts of the XDATA memory spaces. The SRAM is an ultralow-power SRAM that retains its contents even when the digital part is powered off (power modes 2 and 3).

The 256 KB flash block provides in-circuit programmable non-volatile program memory for the device, and maps into the CODE and XDATA memory spaces.

#### Peripherals

Writing to the flash block is performed through a flash controller that allows page-wise erasure and 4-bytewise programming.

A versatile five-channel DMA controller is available in the system, accesses memory using the XDATA memory space, and thus has access to all physical memories. Each channel (trigger, priority, transfer mode,

addressing mode, source and destination pointers, and transfer count) is configured with DMA descriptors that can be located anywhere in memory. Many of the hardware peripherals (AES core, flash controller, USARTs, timers, ADC interface, etc.) can be used with the DMA controller for efficient operation by performing data transfers between a single SFR or XREG address and flash/SRAM.

Each CC2541 contains a unique 48-bit IEEE address that can be used as the public device address for a *Bluetooth* device. Designers are free to use this address, or provide their own, as described in the *Bluetooth* specification.

The interrupt controller services a total of 18 interrupt sources, divided into six interrupt groups, each of which is associated with one of four interrupt priorities. I/O and sleep timer interrupt requests are serviced even if the device is in a sleep mode (power modes 1 and 2) by bringing the CC2541 back to the active mode.

The debug interface implements a proprietary two-wire serial interface that is used for in-circuit debugging. Through this debug interface, it is possible to erase or program the entire flash memory, control which oscillators are enabled, stop and start execution of the user program, execute instructions on the 8051 core, set code breakpoints, and single-step through instructions in the code. Using these techniques, it is possible to perform in-circuit debugging and external flash programming elegantly.

The I/O controller is responsible for all general-purpose I/O pins. The CPU can configure whether peripheral modules control certain pins or whether they are under software control, and if so, whether each pin is configured as an input or output and if a pullup or pulldown resistor in the pad is connected. Each peripheral that connects to the I/O pins can choose between two different I/O pin locations to ensure flexibility in various applications.

The sleep timer is an ultra-low power timer that uses an external 32.768-kHz crystal oscillator. The sleep timer runs continuously in all operating modes except power mode 3. Typical applications of this timer are as a real-time counter or as a wake-up timer to exit power modes 1 or 2.

Timer 1 is a 16-bit timer with timer/counter/PWM functionality. It has a programmable prescaler, a 16-bit period value, and five individually programmable counter/capture channels, each with a 16-bit compare value. Each of the counter/capture channels can be used as a PWM output or to capture the timing of edges on input signals. It can also be configured in IR generation mode, where it counts timer 3 periods and the output is ANDed with the output of timer 3 to generate modulated consumer IR signals with minimal CPU interaction.

Timer 2 is a 40-bit timer used by the *Bluetooth* low energy stack. It has a 16-bit counter with a configurable timer period and a 24-bit overflow counter that can be used to keep track of the number of periods that have transpired. A 40-bit capture register is also used to record the exact time at which a start-of-frame delimiter is received/transmitted or the exact time at which transmission ends. There are two 16-bit timer-compare registers and two 24-bit overflow-compare registers that can be used to give exact timing for start of RX or TX to the radio or general interrupts.

Timer 3 and timer 4 are 8-bit timers with timer/counter/PWM functionality. They have a programmable prescaler, an 8-bit period value, and one programmable counter channel with an 8-bit compare value. Each of the counter channels can be used as PWM output.

USART 0 and USART 1 are each configurable as either an SPI master/slave or a UART. They provide double buffering on both RX and TX and hardware flow control and are thus well suited to high-throughput full-duplex applications. Each USART has its own high-precision baud-rate generator, thus leaving the ordinary timers free for other uses. When configured as SPI slaves, the USARTs sample the input signal using SCK directly instead of using some oversampling scheme, and are thus well-suited for high data rates.

The AES encryption/decryption core allows the user to encrypt and decrypt data using the AES algorithm with 128-bit keys. The AES core also supports ECB, CBC, CFB, OFB, CTR, and CBC-MAC, as well as hardware support for CCM.

The ADC supports 7 to 12 bits of resolution with a corresponding range of bandwidths from 30-kHz to 4-kHz, respectively. DC and audio conversions with up to eight input channels (I/O controller pins) are possible. The inputs can be selected as single-ended or differential. The reference voltage can be internal, AVDD, or a single-ended or differential external signal. The ADC also has a temperature-sensor input channel. The ADC can automate the process of periodic sampling or conversion over a sequence of channels.

The I<sup>2</sup>C module provides a digital peripheral connection with two pins and supports both master and slave

Bluegiga Technologies Oy

operation. I<sup>2</sup>C support is compliant with the NXP I2C specification version 2.1 and supports standard mode (up to 100 kbps) and fast mode (up to 400 kbps). In addition, 7-bit device addressing modes are supported, as well as master and slave modes..

The ultralow-power analog comparator enables applications to wake up from PM2 or PM3 based on an analog signal. Both inputs are brought out to pins; the reference voltage must be provided externally. The comparator output is connected to the I/O controller interrupt detector and can be treated by the MCU as a regular I/O pin interrupt.

### RF front end

RF front end includes balun, power amplifier, low noise amplifier, band pass filter, and a ceramic chip antenna with matching network. Optimal matching combined with effective low pass filter provides extremely low inband spurious emissions and harmonics.

# 9 Certifications

BLE121LR is compliant to the following specifications.

## 9.1 Bluetooth

ТВА

## 9.2 FCC and IC

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) this device may not cause harmful interference, and

- (2) this device must accept any interference received, including interference that may cause undesired operation.

Any changes or modifications not expressly approved by Bluegiga Technologies could void the user's authority to operate the equipment.

### FCC RF Radiation Exposure Statement:

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. End users must follow the specific operating instructions for satisfying RF exposure compliance. This transmitter meets both portable and mobile limits as demonstrated in the RF Exposure Analysis. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter except in accordance with FCC multi-transmitter product procedures.

### IC Statements:

This device complies with Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser) gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for successful communication.

### OEM Responsibilities to comply with FCC and Industry Canada Regulations

The BLE121LR module has been certified for integration into products only by OEM integrators under the following condition:

• The transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter except in accordance with FCC multi-transmitter product procedures.

As long as the condition above is met, further transmitter testing will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed (for example, digital device emissions, PC peripheral requirements, etc.).

**IMPORTANT NOTE:** In the event that the above condition can not be met (for certain configurations or colocation with another transmitter), then the FCC and Industry Canada authorizations are no longer considered valid and the FCC ID and IC Certification Number can not be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC and Industry Canada authorization.

### End Product Labeling

The BLE121LR module is labeled with its own FCC ID and IC Certification Number. If the FCC ID and IC Certification Number are not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. In that case, the final end product must be labeled in a visible area with the following:

### "Contains Transmitter Module FCC ID: QOQBLE121LR"

### "Contains Transmitter Module IC: 5123A-BGTBLE121LR"

or

"Contains FCC ID: QOQBLE121LR"

"Contains IC: 5123A-BGTBLE121LR"

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module or change RF related parameters in the user manual of the end product.

### 9.2.1 FCC et IC

### Déclaration d'IC :

Ce dispositif est conforme aux normes RSS exemptes de licence d'Industrie Canada. Son fonctionnement est assujetti aux deux conditions suivantes : (1) ce dispositif ne doit pas provoquer de perturbation et (2) ce dispositif doit accepter toute perturbation, y compris les perturbations qui peuvent entraîner un fonctionnement non désiré du dispositif.

Selon les réglementations d'Industrie Canada, cet émetteur radio ne doit fonctionner qu'avec une antenne d'une typologie spécifique et d'un gain maximum (ou inférieur) approuvé pour l'émetteur par Industrie Canada. Pour réduire les éventuelles perturbations radioélectriques nuisibles à d'autres utilisateurs, le type d'antenne et son gain doivent être choisis de manière à ce que la puissance isotrope rayonnée équivalente (P.I.R.E.) n'excède pas les valeurs nécessaires pour obtenir une communication convenable.

# Responsabilités des OEM quant à la conformité avec les réglementations de FCC et d'Industrie Canada

Les modules BLE121LR ont été certifiés pour entrer dans la fabrication de produits exclusivement réalisés par des intégrateurs dans les conditions suivantes :

• Le module transmetteur ne doit pas être installé ou utilisé en concomitance avec une autre antenne

ou un autre transmetteur.

Tant que ces deux conditions sont réunies, il n'est pas nécessaire de procéder à des tests supplémentaires sur le transmetteur. Cependant, l'intégrateur est responsable des tests effectués sur le produit final afin de se

Bluegiga Technologies Oy

mettre en conformité avec d'éventuelles exigences complémentaires lorsque le module est installé (exemple : émissions provenant d'appareils numériques, exigences vis-à-vis de périphériques informatiques, etc.)

**REMARQUE IMPORTANTE :** En cas d'inobservance de ces conditions (en ce qui concerne certaines configurations ou l'emplacement du dispositif à proximité d'un autre émetteur), les autorisations de FCC et d'Industrie Canada ne seront plus considérées valables et l'identification de FCC et le numéro de certification d'IC ne pourront pas être utilisés sur le produit final. Dans ces cas, l'intégrateur OEM sera chargé d'évaluer à nouveau le produit final (y compris l'émetteur) et d'obtenir une autorisation indépendante de FCC et d'Industrie Canada.

### Étiquetage du produit final

Le module BLE121LR est étiqueté avec sa propre identification FCC et son propre numéro de certification IC. Si l'identification FCC et le numéro de certification IC ne sont pas visibles lorsque le module est installé à l'intérieur d'un autre dispositif, la partie externe du dispositif dans lequel le module est installé devra également présenter une étiquette faisant référence au module inclus. Dans ce cas, le produit final devra être étiqueté sur une zone visible avec les informations suivantes :

### « Contient module émetteur identification FCC : QOQBLE121LR »

### « Contient module émetteur IC : 5123A-BGTBLE121LR »

ou

### « Contient identification FCC : QOQBLE121LR »

### « Contient IC : 5123A-BGTBLE121LR »

Dans le guide d'utilisation du produit final, l'intégrateur OEM doit s'abstenir de fournir des informations à l'utilisateur final portant sur les procédures à suivre pour installer ou retirer ce module RF ou pour changer les paramètres RF.

9.3 CE

ТВА

9.4 MIC Japan

ТВА

9.5 KCC (Korea)

TBA

.

# **10 Contact Information**

| Sales:                    | sales@bluegiga.com                                |

|---------------------------|---------------------------------------------------|

| Technical support:        | http://www.bluegiga.com/support                   |

| Orders:                   | orders@bluegiga.com                               |

| www:                      | www.bluegiga.com                                  |

| Head Office / Finland:    |                                                   |

|                           | Phone: +358-9-4355 060                            |

|                           | Fax: +358-9-4355 0660                             |

|                           | Sinikalliontie 5A                                 |

|                           | 02630 ESPOO                                       |

|                           | FINLAND                                           |

| Postal address / Finland: |                                                   |

|                           | P.O. BOX 120                                      |

|                           | 02631 ESPOO                                       |

|                           | FINLAND                                           |

| Sales Office / USA:       |                                                   |

|                           | Phone: +1 770 291 2181                            |

|                           | Fax: +1 770 291 2183                              |

|                           | Bluegiga Technologies, Inc.                       |

|                           | 3235 Satellite Boulevard, Building 400, Suite 300 |

|                           | Duluth, GA, 30096, USA                            |

| Sales Office / Hong-Kong: |                                                   |

|                           | Bluegiga Technologies Ltd.                        |

|                           | Phone: +852 3972 2186                             |

|                           |                                                   |