# Sipeed M1w User Manual v1.0

## **Characteristic:**

- CPU: RISC-V Dual Core

64bit, with FPU, 400Mhz

standard Frequence(Can be overclocked)

- Image Identification: QVGA@60FPS/VGA@30FPS

- Voice Recognition:Support up to 8 microphones

- Deep learning framework:

TensorFlow/Keras/Darknet

Peripheral: FPIOA、UART、GPIO、SPI、I<sup>2</sup>C、 I<sup>2</sup>S、WDT、TIMER、RTC etc.

Wireless Function(Optional): Support 2.4G 802.11.b/g/n

Version 1.0

Sipeed

Copyright © 2019

www.sipeed.com

| Update record |                                              |

|---------------|----------------------------------------------|

| V1.0          | Edited on April 23, 2019 ; Original document |

|               |                                              |

|               |                                              |

|               |                                              |

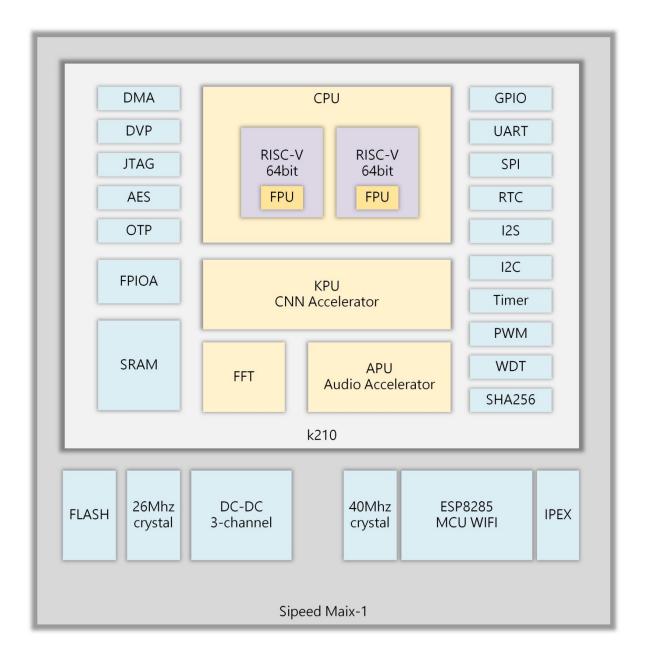

| Powerful dual-core 64-bit open architecture-based processor with rich community resources  FPU Specifications  IEEE754-2008 compliant high-performance pipelined FPU  Bebugging Support  High-speed UART and JTAG interface for debugging  Supports the fixed-point model that the mainstream training framework trains according to specific restriction rules  There is no direct limit on the number of network layers, and each layer of convolutional neural network parameters can be configured separately, includ- ing the number of input and output channels, and the input and output line width and column height  Support for 1x1 and 3x3 convolution kernels  Support for any form of activation function  The maximum supported neural network parameter size for real-time work is 5MiB to 5.9MiB  The maximum supported network parameter size when working in non-real time is (flash size - software size)  Up to 8 channels of audio input data, ie 4 stereo channels  Simultaneous scanning pre-processing and beamforming for sound sources in up to 16 directions  Supports one active voice stream output  16-bit wide internal audio signal processing  Support for 12-bit, 16-bit, 24-bit, and 32-bit input data | FEATURES OVERVIEW                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FPU Specifications  IEEE754-2008 compliant high-performance pipelined FPU  High-speed UART and JTAG interface for debugging  • Supports the fixed-point model that the mainstream training framework trains according to specific restriction rules  • There is no direct limit on the number of network layers, and each layer of convolutional neural network parameters can be configured separately, includ- ing the number of input and output channels, and the input and output line width and column height  • Support for 1x1 and 3x3 convolution kernels  • Support for any form of activation function  • The maximum supported neural network parameter size for real-time work is 5MiB to 5.9MiB  • The maximum supported network parameter size when working in non-real time is (flash size - software size)  • Up to 8 channels of audio input data, ie 4 stereo channels  • Simultaneous scanning pre-processing and beamforming for sound sources in up to 16 directions  • Supports one active voice stream output  • 16-bit wide internal audio signal processing                                                                                                                                                      | CPU: RISC-V Dual Core 64bit, 400Mh adjustable | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Debugging Support  High-speed UART and JTAG interface for debugging  Supports the fixed-point model that the mainstream training framework trains according to specific restriction rules  There is no direct limit on the number of network layers, and each layer of convolutional neural network parameters can be configured separately, includ- ing the number of input and output channels, and the input and output line width and column height  Support for 1x1 and 3x3 convolution kernels  Support for any form of activation function  The maximum supported neural network parameter size for real-time work is 5MiB to 5.9MiB  The maximum supported network parameter size when working in non-real time is (flash size - software size)  Up to 8 channels of audio input data, ie 4 stereo channels  Simultaneous scanning pre-processing and beamforming for sound sources in up to 16 directions  Supports one active voice stream output  16-bit wide internal audio signal processing                                                                                                                                                                                                                                  | 501.6                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Supports the fixed-point model that the mainstream training framework trains according to specific restriction rules  There is no direct limit on the number of network layers, and each layer of convolutional neural network parameters can be configured separately, includ- ing the number of input and output channels, and the input and output line width and column height  Support for 1x1 and 3x3 convolution kernels  Support for any form of activation function  The maximum supported neural network parameter size for real-time work is 5MiB to 5.9MiB  The maximum supported network parameter size when working in non-real time is (flash size - software size)  Up to 8 channels of audio input data, ie 4 stereo channels  Simultaneous scanning pre-processing and beamforming for sound sources in up to 16 directions  Supports one active voice stream output  16-bit wide internal audio signal processing                                                                                                                                                                                                                                                                                                       | ·                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| training framework trains according to specific restriction rules  • There is no direct limit on the number of network layers, and each layer of convolutional neural network parameters can be configured separately, includ- ing the number of input and output channels, and the input and output line width and column height  • Support for 1x1 and 3x3 convolution kernels  • Support for any form of activation function  • The maximum supported neural network parameter size for real-time work is 5MiB to 5.9MiB  • The maximum supported network parameter size when working in non-real time is (flash size - software size)  • Up to 8 channels of audio input data, ie 4 stereo channels  • Simultaneous scanning pre-processing and beamforming for sound sources in up to 16 directions  • Supports one active voice stream output  • 16-bit wide internal audio signal processing                                                                                                                                                                                                                                                                                                                                        | Debugging Support                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| channels  • Simultaneous scanning pre-processing and beamforming for sound sources in up to 16 directions  • Supports one active voice stream output  • 16-bit wide internal audio signal processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Neural Network Processor (KPU)                | training framework trains according to specific restriction rules  • There is no direct limit on the number of network layers, and each layer of convolutional neural network parameters can be configured separately, includ- ing the number of input and output channels, and the input and output line width and column height  • Support for 1x1 and 3x3 convolution kernels  • Support for any form of activation function  • The maximum supported neural network parameter size for real-time work is 5MiB to 5.9MiB  • The maximum supported network parameter size when |  |  |

| widths • Multi-channel direct raw signal output • Up to 192kHz sample rate • Built-in FFT unit supports 512-point FFT of audio data •Uses system DMAC to store output data in system memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Audio Processor (APU)                         | channels <ul> <li>Simultaneous scanning pre-processing and beamforming for sound sources in up to 16 directions</li> <li>Supports one active voice stream output</li> <li>16-bit wide internal audio signal processing</li> <li>Support for 12-bit, 16-bit, 24-bit, and 32-bit input data widths</li> <li>Multi-channel direct raw signal output</li> <li>Up to 192kHz sample rate</li> <li>Built-in FFT unit supports 512-point FFT of audio data</li> <li>Uses system DMAC to store output data in system memory</li> </ul>                                                    |  |  |

| The SRAM is split into two parts, 6MiB of on-chip Static Random-Access Memory (SRAM) general-purpose SRAM memory and 2MiB of on-chip Al SRAM memory, for a total of 8MiB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Static Random-Access Memory (SRAM)            | general-purpose SRAM memory and 2MiB of on-chip Al SRAM memory, for a total of 8MiB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Field Programmable IO Array (FPIOA/IOMUX)  FPIOA allows users to map 255 internal functions to 48 free IOs on the chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Field Programmable IO Array (FPIOA/IOMUX)     | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Digital Video Port (DVP)  Maximum frame size 640x480                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital Video Port (DVP)                      | Maximum frame size 640x480                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| FFT Accelerator  The FFT accelerator is a hardware implementation of the Fast Fourier Transform (FFT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FFT Accelerator                               | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| SOFTWARE FEATURES       |                                                      |

|-------------------------|------------------------------------------------------|

| FreeRtos & Standard SDK | Support FreeRtos and Standrad development kit.       |

| MicroPython Support     | Support MicroPython on M1                            |

| Machine vision          | Machine vision based on convolutional neural network |

| Machine hearing         | High performance microphone array processor          |

| HARDWARE FEATURES                       |              |

|-----------------------------------------|--------------|

| Supply voltage of external power supply | 4.8V ~ 5.2V  |

| Supply current of external power supply | >600mA       |

| Temperature rise                        | <30K         |

| Range of working temperature            | -30°C ~ 85°C |

| RF FEATURES               |                                                                                                |

|---------------------------|------------------------------------------------------------------------------------------------|

| MCU : ESP8285             | Tensilica L106 32-bit MCU                                                                      |

| Wireless Standard         | 802.11 b/g/n                                                                                   |

| Frequency Range           | 2400Mhz - 2483.5Mhz                                                                            |

| TX Power(Conduction test) | 802.11.b: +15dBm(±2dBm)<br>802.11.g: +10dBm(±2dBm)(54Mbps)<br>802.11.n: +10dBm(±2dBm) (65Mbps) |

| Antenna Connector         | IPEX 3.0x3.0mm                                                                                 |

| Wi-Fi mode                | Station/SoftAP/SoftAP+Station                                                                  |

| Power up the device, first time setup with MaixPy in K210 |                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.Connecting hardware                                     | Connect TXD, RXD, 5V, GND with computer by USB-TTL module                                                                                                                                                                                                                                                            |  |  |  |

| 2.Using the serial port tool                              | LINUX:  Use minicom ore screen tool  Minicom: sudo apt update sudo apt install minicom sudo minicom -s  # Then set the serial port number according to the prompt and the baud rate is 115200. Do not know how to search using the search tool.  # Set Backspace to DEL function  # Set linewrap to Yes sudo minicom |  |  |  |

|                 | Screen: sudo apt update sudo apt install screen sudo screen /dev/ttyUSB0 115200 Then click the Enter button to see the interactive interface of MaixPy. |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | WINDOWS: Use tools like putty or xshell                                                                                                                 |

| 3.Run your code | Reference MicroPython official turorial                                                                                                                 |

| Control ESP8285        |                                             |

|------------------------|---------------------------------------------|

| 1.Use serial port tool | Set baudrate in 115200                      |

| 2.Send AT commands     | Reference ESP8266_at_instruction_set_en.pdf |

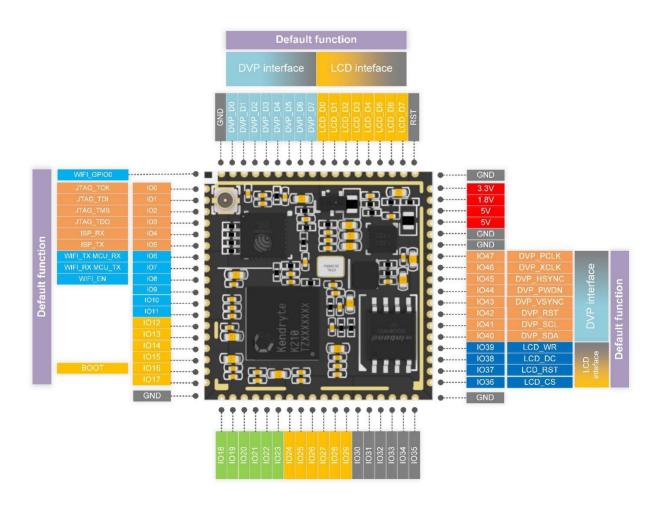

## Maix-1 pin map

### Maix-1 block diagram

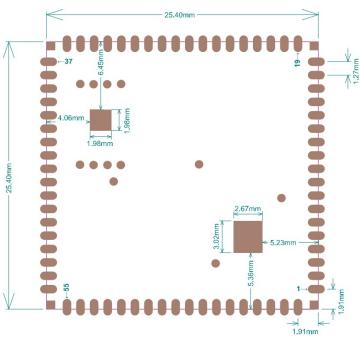

#### Size Information

Size: 25.4 x 25.4 x 3.3 mm

| number | Pin               | number | Pin         | number | Pin       | number | Pin    |

|--------|-------------------|--------|-------------|--------|-----------|--------|--------|

| 1      | JTAG_TCK          | 19     | MIC_BCK     | 37     | LCD_CS    | 55     | RST    |

| 2      | JTAG_TDI          | 20     | MIC_WS      | 38     | LCD_RST   | 56     | LCD_D7 |

| 3      | JTAG_TMS          | 21     | MIC_DAT3    | 39     | LCD_DC    | 57     | LCD_D6 |

| 4      | JTAG_TDO          | 22     | MIC_DAT2    | 40     | LCD_WR    | 58     | LCD_D5 |

| 5      | ISP_RX            | 23     | MIC_DAT1    | 41     | DVP_SDA   | 59     | LCD_D4 |

| 6      | ISP_TX            | 24     | MIC_DAT0    | 42     | DVP_SCL   | 60     | LCD_D3 |

| 7      | WIFI_TX<br>MCU_RX | 25     | MIC_LED_DAT | 43     | DVP_RST   | 61     | LCD_D2 |

| 8      | WIFI_RX<br>MCU_TX | 26     | SPI0_CS1    | 44     | DVP_VSYNC | 62     | LCD_D1 |

| 9      | WIFI_EN           | 27     | SPI0_MISO   | 45     | DVP_PWDN  | 63     | LCD_D0 |

| 10     | 109               | 28     | SPI0_SCLK   | 46     | DVP_HSYNC | 64     | DVP_D7 |

| 11     | IO10              | 29     | SPI0_MOSI   | 47     | DVP_XCLK  | 65     | DVP_D6 |

| 12     | IO11              | 30     | SPI0_CS0    | 48     | DVP_PCLK  | 66     | DVP_D5 |

| 13     | LED_G             | 31     | MIC0_WS     | 49     | GND       | 67     | DVP_D4 |

| 14     | LED_B             | 32     | MIC0_DATA   | 50     | GND       | 68     | DVP_D3 |

| 15     | LED_R             | 33     | MIC0_BCK    | 51     | 5V        | 69     | DVP_D2 |

| 16     | IO15              | 34     | 12S_WS      | 52     | 5V        | 70     | DVP_D1 |

| 17     | BOOT<br>KEY0      | 35     | I2S_DA      | 53     | 1V8       | 71     | DVP_D0 |

| 18     | IO17              | 36     | I2S_BCK     | 54     | 3V3       | 72     | GND    |

Note: The small square pad in the lower right corner of the dimension drawing is WIFI\_GPIO0, and the other three corners are GND.

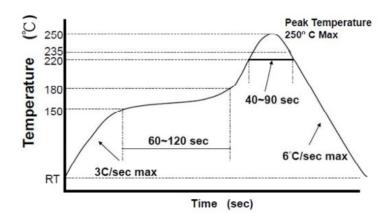

# Reflow profile guideline

| Resource                                           |                              |

|----------------------------------------------------|------------------------------|

| Website                                            | www.sipeed.com               |

| Github                                             | https://github.com/Lichee-Pi |

| BBS                                                | http://bbs.sipeed.com        |

| Wiki                                               | maixpy.sipeed.com            |

| SDK Relevant information                           | dl.sipeed.com/MAIX/SDK       |

| HDK Relevant information                           | dl.sipeed.com/MAIX/HDK       |

| E-mail(Technical Support and Business Cooperation) | support@sipeed.com           |

| telgram link                                       | https://t.me/sipeed          |

### **FCC STATEMENT**

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference.

- (2) This device must accept any interference received, including interference that may cause undesired operation.

Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

Please notice that if the FCC identification number is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. This exterior label can use wording such as the following: "Contains FCC ID: 2AS7P-SIPEED-M1W" any similar wording that expresses the same meaning may be used. This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with a minimum distance of 20cmbetween the radiator & your body. This transmitter must not be co-located or operating inconjunction with any other antenna or transmitter.

Manufacturer's Name: SHENZHEN SIPEED TECHNOLOGY Co., LTD

Sample Description: Sipeed M1w

Trade Mark: S Sipeed

Model number: Sipeed M1w

Operating Temperature: -30° C to 85° C.This product is a fixed location. To comply with RF exposure requi rements, a minimum separation distance of 20cm must be maintained between the user's body and the device, including the antenna. Use only the supplied or an approved antenna. This device in compliance with the essential requirements and other relevant provisions of Directive 2014/53/EU. All essential radio test suites have been carried out.

- 1. CAUTION: RISK OF EXPLOSION IF BATTERY IS REPLACED BY AN INCORRECT TYPE. DISPOSE OF **USED BATTERIES ACCORDING TO THE INSTRUCTIONS**

- 2. The device complies with RF specifications when the device used at 20cm from your body This product can be used across EU member states

#### CE -NB RF Specification:

| Function  | Operation Frequency | Max RF<br>Outputpower<br>(dBm) | Limit<br>(dBm) |

|-----------|---------------------|--------------------------------|----------------|

| 2.4G WIFI | 2412-2472MHz        | 12.26                          | 20             |

#### Disclaimer and copyright notice

The information in this document, including the URL address for reference, is subject to change without notice.

The documentation is provided by Sipeed™ without warranty of any kind, including any warranties of merchantability, and any proposal, specification or sample referred to elsewhere. This document is not intended to be a liability, including the use of information in this document to infringe any patent rights.

Copyrights © 2019 Sipeed Limited. All rights reserved.