# **LE920A4 Auto**Hardware User Guide

1VV0301261 Rev. 3.31 - 2017-02-16

# **Applicability Table**

This documentation applies to the following products:

**Table 1: Applicability Table**

| Module Name | Description                                     |

|-------------|-------------------------------------------------|

| LE920A4-NA  | North America regional variant (AT&T, T-Mobile) |

| LE920A4-NV  | North America regional variant (Verizon)        |

| LE920A4-EU  | Europe regional variant                         |

| HE920A-EU   | Non-LTE Europe variant                          |

| LE920A4-CN  | China variant                                   |

| LE920A4-AP  | APAC variant                                    |

#### SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Telit assumes no liability resulting from any inaccuracies or omissions in this document, or from use of the information obtained herein. The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies or omissions. Telit reserves the right to make changes to any products described herein and reserves the right to revise this document and to make changes from time to time in the content hereof with no obligation to notify any person of revisions or changes. Telit does not assume any liability arising out of the application or use of any product, software, or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

It is possible that this publication may contain references to, or information about Telit products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Telit intends to announce such Telit products, programming, or services in your country.

#### Copyrights

This instruction manual and the Telit products described in this instruction manual may be, include, or describe copyrighted Telit material, such as computer programs stored in semiconductor memories or other media. Laws in Italy and other countries preserve for Telit and its licensors certain exclusive rights for copyrighted material, including the exclusive right to copy, reproduce in any form, distribute, and make derivative works of the copyrighted material. Accordingly, any copyrighted material of Telit and its licensors contained herein or in the Telit products described in this instruction manual may not be copied, reproduced, distributed, merged, or modified in any manner without the express written permission of Telit. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit, as arises by operation of law in the sale of a product.

#### **Computer Software Copyrights**

Telit and third-party software (SW) products described in this instruction manual may include copyrighted Telit and other third-party computer programs stored in semiconductor memories or other media. Laws in Italy and other countries preserve for Telit and other third-party SW certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Telit or other third-party SW computer programs contained in the Telit products described in this instruction manual may not be copied (reverse engineered) or reproduced in any manner without the express written permission of Telit or the third-party SW supplier. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit or other third-party SW, except for the normal non-exclusive, royalty free license to use that arises by operation of law in the sale of a product.

#### **Usage and Disclosure Restrictions**

#### **License Agreements**

The software described in this document is the property of Telit and its licensors. It is furnished by an express license agreement only and may be used only in accordance with the terms of such an agreement.

## **Copyrighted Materials**

Software and documentation are copyrighted materials. Making unauthorized copies is prohibited by law. No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, without prior written permission of Telit.

#### **High Risk Materials**

Components, units, or third-party products used in the product described herein are NOT fault-tolerant and are NOT designed, manufactured, or intended for use as on-line control equipment in the following hazardous environments requiring fail-safe controls: the operation of nuclear facilities, aircraft navigation or aircraft communication systems, air traffic control, life support, or weapons systems ("high risk activities"). Telit and its supplier(s) specifically disclaim any expressed or implied warranty of fitness for such high risk activities.

#### **Trademarks**

TELIT and the stylized T logo are trademarks and/or registered trademarks of Telit Communications S.p.A. in the Unites States and/or other countries. All other product or service names are the property of their respective owners.

Copyright © 2016 Telit Communications S.p.A.

## **Contents**

| 1. | Intro | troduction                                         |    |  |

|----|-------|----------------------------------------------------|----|--|

|    | 1.1.  | Scope                                              | 13 |  |

|    | 1.2.  | Audience                                           | 13 |  |

|    | 1.3.  | Contact Information, Support                       | 13 |  |

|    | 1.4.  | Text Conventions                                   | 14 |  |

|    | 1.5.  | Related Documents                                  | 15 |  |

|    | 1.6.  | Abbreviations                                      | 15 |  |

| 2. | Gen   | eral Product Description                           | 17 |  |

|    | 2.1.  | Overview                                           | 17 |  |

|    | 2.2.  | Applications                                       | 17 |  |

|    | 2.3.  | General Functionality and Main Features            | 18 |  |

|    | 2.4.  | Block Diagram                                      | 21 |  |

|    | 2.5.  | Environmental Requirements                         | 22 |  |

|    |       | 2.5.1. Temperature Range                           | 22 |  |

|    |       | 2.5.2. RoHS Compliance                             | 22 |  |

|    | 2.6.  | Frequency Bands                                    | 23 |  |

|    |       | 2.6.1. RF Bands per Regional Variant               | 23 |  |

|    |       | 2.6.2. Reference Table of RF Bands Characteristics | 24 |  |

|    | 2.7.  | Sensitivity                                        | 26 |  |

|    | 2.8.  | LE920A4 Mechanical Specifications                  | 27 |  |

|    |       | 2.8.1. Dimensions                                  | 27 |  |

|    |       | 2.8.2. Weight                                      | 27 |  |

| 3. | LE92  | OA4 Module Connections                             | 28 |  |

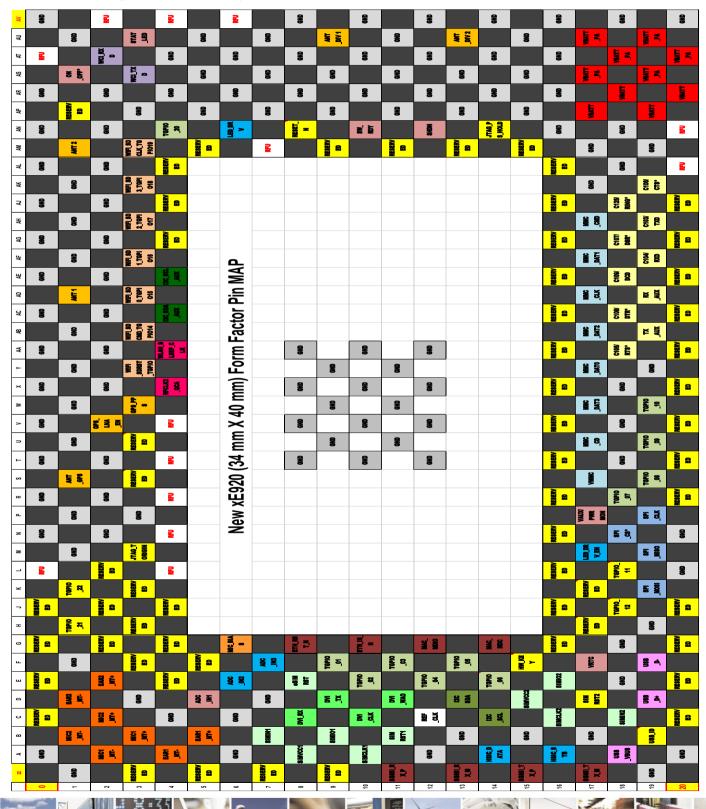

|    | 3.1.  | Pin-out                                            | 28 |  |

|    | 3.2.  | LE920A4 Signals That Must Be Connected             | 44 |  |

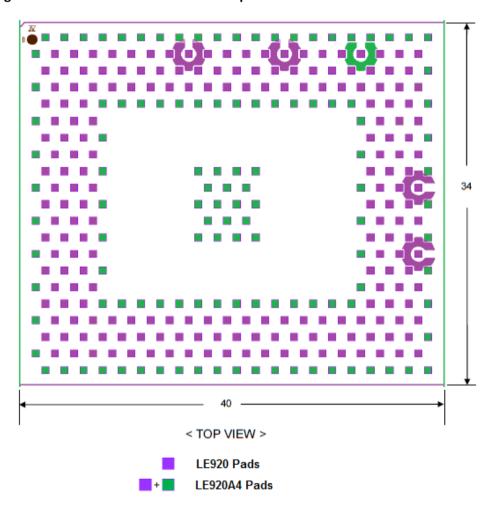

|    | 3.3.  | LGA Pads Layout                                    | 46 |  |

|    | 3.4.  | Backward Compatibility to LE920                    | 47 |  |

| 4. | Elect | trical Specifications                              | 48 |  |

|    | 4.1.  | Absolute Maximum Ratings – Not Operational         | 48 |  |

|    |       |                                                    |    |  |

|    | 4.2. | Recommended Operating Conditions                             | 48 |

|----|------|--------------------------------------------------------------|----|

|    | 4.3. | Logic Level Specifications                                   | 49 |

|    |      | 4.3.1. 1.8V Pads - Absolute Maximum Ratings                  | 49 |

|    |      | 4.3.2. 1.8V Standard GPIOs                                   | 49 |

|    |      | 4.3.3. 1.8V SD Card Pads                                     | 50 |

|    |      | 4.3.4. 1.8V SIM Card Pads                                    | 50 |

|    |      | 4.3.5. Dual Voltage Pads - Absolute Maximum Ratings          | 51 |

|    |      | 4.3.6. SD Card Pads @ 2.95V                                  | 51 |

|    |      | 4.3.7. SIM Card Pads @2.95V                                  | 52 |

| 5. | Hard | lware Commands                                               | 53 |

|    | 5.1. | Turning on the LE920A4 Module                                | 53 |

|    | 5.2. | Initialization and Activation State                          | 53 |

|    | 5.3. | Turning off the LE920A4 Module                               | 55 |

|    |      | 5.3.1. Shutdown by Software Command                          | 55 |

|    |      | 5.3.2. Hardware Shutdown                                     | 56 |

|    |      | 5.3.3. Unconditional Hardware Reset                          | 57 |

|    |      | 5.3.4. Unconditional Hardware Shutdown                       | 58 |

| 6. | Pow  | er Supply                                                    | 59 |

|    | 6.1. | Power Supply Requirements                                    | 59 |

|    | 6.2. | General Design Rules                                         | 61 |

|    |      | 6.2.1. Electrical Design Guidelines                          | 61 |

|    |      | 6.2.1.1. + 5V Input Source Power Supply – Design Guidelines  | 61 |

|    |      | 6.2.1.2. + 12V Input Source Power Supply – Design Guidelines | 62 |

|    |      | 6.2.1.3. Battery Source Power Supply – Design Guidelines     | 64 |

|    |      | 6.2.2. Thermal Design Guidelines                             | 65 |

|    |      | 6.2.3. Power Supply PCB Layout Guidelines                    | 66 |

| 7. | Ante | enna(s)                                                      | 67 |

|    | 7.1. | GSM/WCDMA/LTE Antenna Requirements                           | 67 |

|    | 7.2. | GSM/WCDMA/LTE Antenna – PCB Line Guidelines                  | 68 |

|    | 7.3. | GSM/WCDMA/LTE Antenna – Installation Guidelines              | 69 |

|    |      |                                                              |    |

|    | 7.4. | Antenna Diversity Requirements                | 69   |

|----|------|-----------------------------------------------|------|

|    | 7.5. | GNSS Antenna Requirements                     | 70   |

|    |      | 7.5.1. Combined GNSS Antenna                  | 70   |

|    |      | 7.5.2. Linear and Patch GNSS Antenna          | 70   |

|    |      | 7.5.3. Front End Design Considerations        | 70   |

|    |      | 7.5.4. GNSS Antenna – PCB Line Guidelines     | 71   |

|    |      | 7.5.5. GNSS Antenna – Installation Guidelines | 71   |

| 8. | Harc | lware Interfaces                              | . 72 |

|    | 8.1. | USB Port                                      | 73   |

|    | 8.2. | HSIC Interface                                | 74   |

|    | 8.3. | Ethernet Connectivity (optional)              | 74   |

|    |      | 8.3.1. SGMII Interface                        | 74   |

|    |      | 8.3.2. Ethernet Control interface             | 74   |

|    | 8.4. | Serial Ports                                  | 75   |

|    |      | 8.4.1. Modem Serial Port 1 Signals            | 75   |

|    |      | 8.4.2. Modem Serial Port 2                    | 76   |

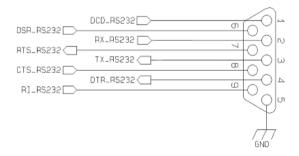

|    |      | 8.4.3. RS232 Level Translation                | 77   |

|    | 8.5. | Peripheral Ports                              | 78   |

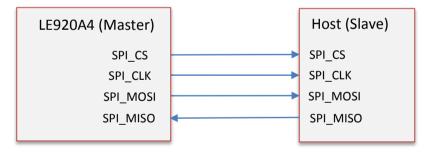

|    |      | 8.5.1. SPI – Serial Peripheral Interface      | 79   |

|    |      | 8.5.2. I2C - Inter-integrated Circuit         | 79   |

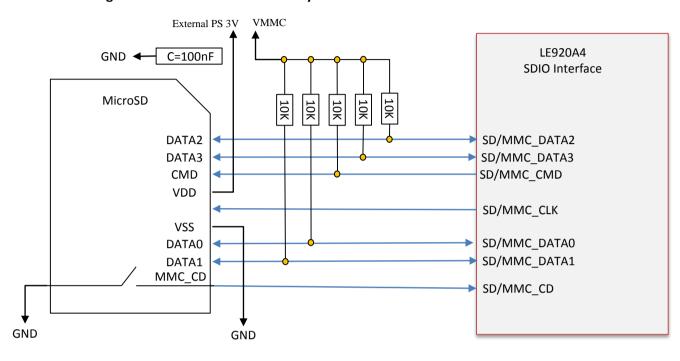

|    |      | 8.5.3. SD/MMC Card Interface                  | 81   |

|    |      | 8.5.4. WiFi SDIO Interface                    | 83   |

|    | 8.6. | Audio Interface                               | 84   |

|    |      | 8.6.1. Analog Audio                           | 84   |

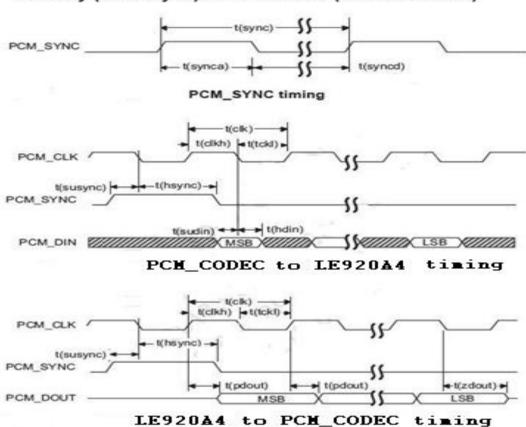

|    |      | 8.6.2. Digital Audio                          | 85   |

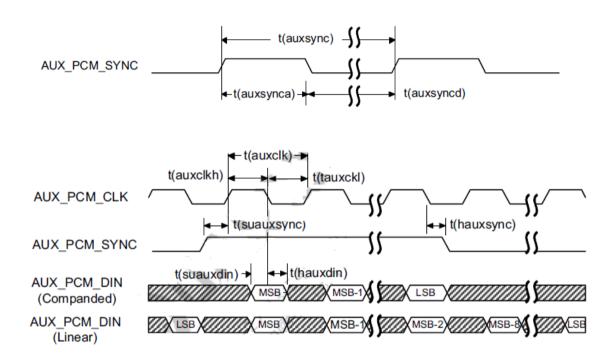

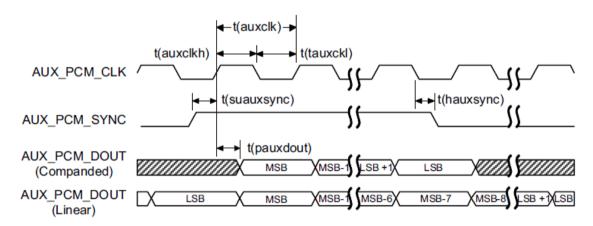

|    |      | 8.6.2.1. Short Frame Timing Diagrams          | 86   |

|    |      | 8.6.2.2. Long Frame Timing Diagrams           | 88   |

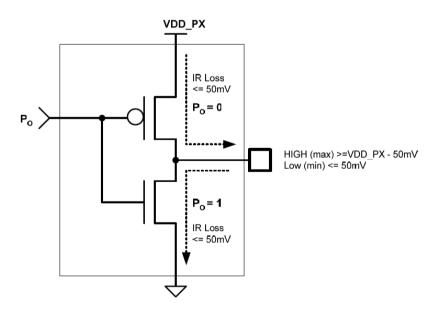

|    | 8.7. | General Purpose I/O                           | 90   |

|    |      | 8.7.1. Using a GPIO Pad as Input              | 92   |

|    |      | 8.7.2. Using a GPIO Pad as an interrupt       | 92   |

|    |      |                                               |      |

|     | 8.7.3. Using a GPIO Pad as Output                 | 92  |

|-----|---------------------------------------------------|-----|

| 9.  | Miscellaneous Functions                           | 93  |

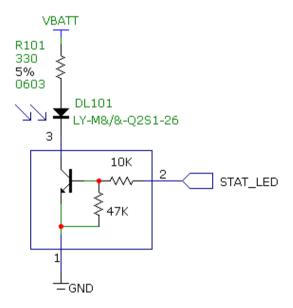

|     | 9.1. Indication of Network Service Availability   | 93  |

|     | 9.2. RTC – Real Time Clock                        | 94  |

|     | 9.3. VAUX Power Output                            | 94  |

|     | 9.4. ADC Converter                                | 94  |

|     | 9.4.1. Description                                | 94  |

|     | 9.4.2. Using the ADC Converter                    | 95  |

|     | 9.5. Using the Temperature Monitor Function       | 95  |

|     | 9.6. Fuel Gauge (optional)                        | 95  |

|     | 9.7. GNSS Characteristics                         | 96  |

| 10. | Mounting the Module on your Board                 | 97  |

|     | 10.1. General                                     | 97  |

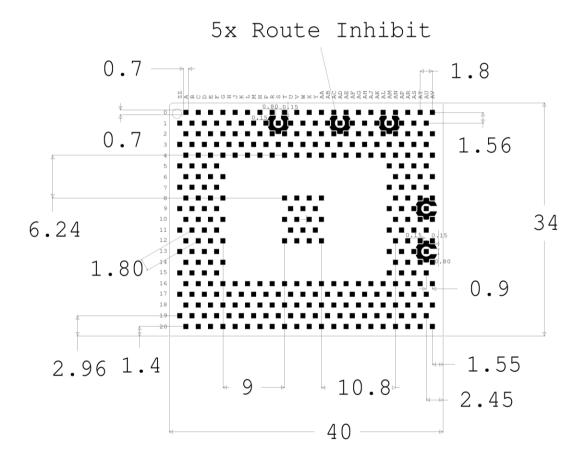

|     | 10.2. Finishing & Dimensions                      | 97  |

|     | 10.3. Recommended Footprint for the Application   | 98  |

|     | 10.4. Stencil                                     | 99  |

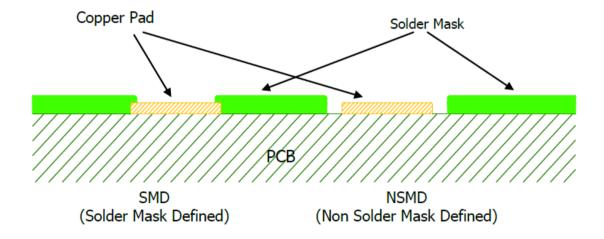

|     | 10.5. PCB Pad Design                              | 99  |

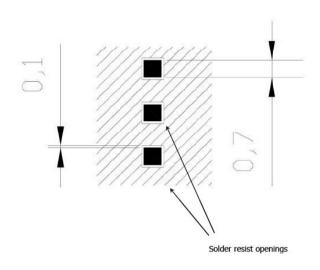

|     | 10.6. Recommendations for PCB Pad Dimensions (mm) | 100 |

|     | 10.7. Solder Paste                                | 101 |

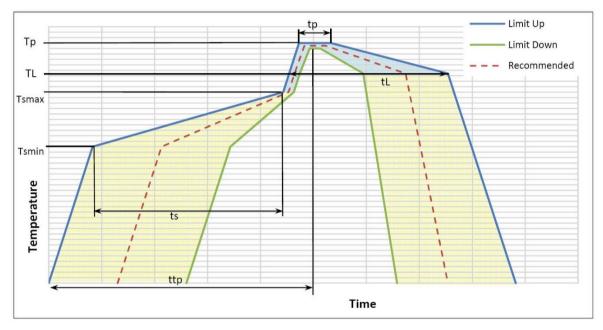

|     | 10.7.1.Solder Reflow                              | 101 |

| 11. | Application Guide                                 | 103 |

|     | 11.1. Debug of the LE920A4 Module in Production   | 103 |

|     | 11.2. Bypass Capacitor on Power Supplies          | 104 |

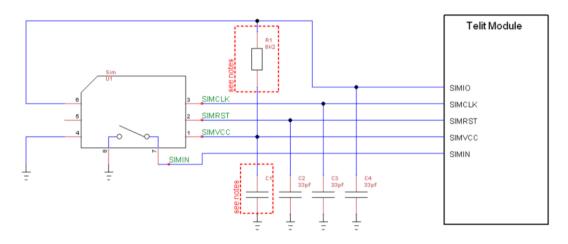

|     | 11.3. SIM Interface                               | 105 |

|     | 11.3.1.SIM Schematic Example                      | 105 |

|     | 11.4. EMC Recommendations                         | 106 |

|     | 11.5. Download and Debug Port                     | 106 |

|     | 11.5.1. Fast Boot Mode                            | 106 |

|     | 11.5.2.Recovery Boot Mode                         | 106 |

|     | 11.6. Antenna Detection                           | 107 |

|     |                                                   |     |

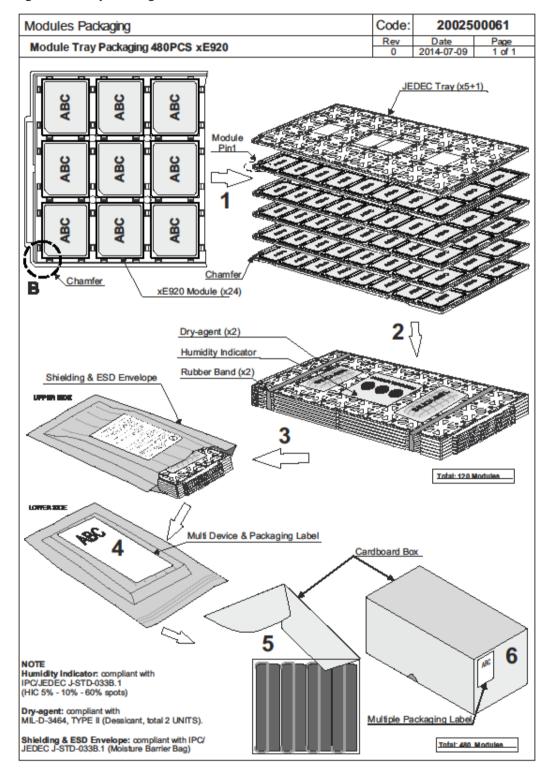

| <b>12.</b> | Packing System                    |     |

|------------|-----------------------------------|-----|

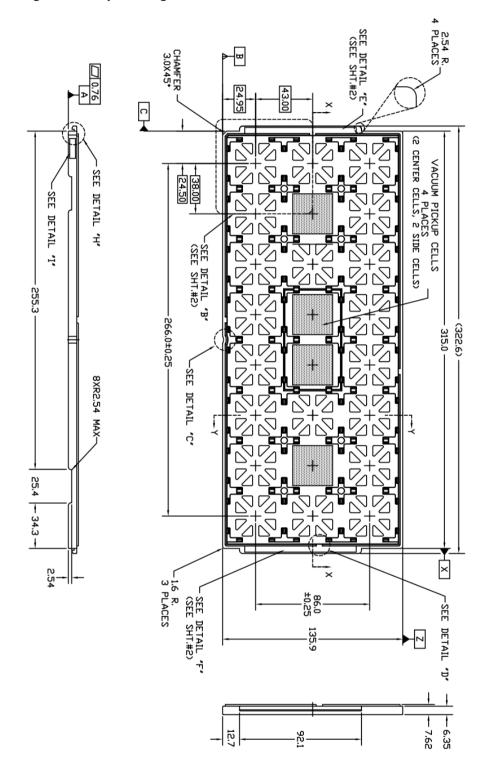

|            | 12.1. Tray                        |     |

|            | 12.2. Tape & Reel                 | 111 |

|            | 12.3. Moisture Sensitivity        | 112 |

| 13.        | Safety Recommendations            | 113 |

| 14.        | Conformity assessment issues      | 114 |

|            | 14.1. FCC/ISED Regulatory notices | 114 |

| 15.        | Document History                  | 117 |

## **List of Tables**

| Table 1: Applicability Table                                    | 2  |

|-----------------------------------------------------------------|----|

| Table 2: Related Documents                                      | 15 |

| Table 3: Main Features                                          | 18 |

| Table 4: RF Bands per Regional Variant                          | 23 |

| Table 5: RF Bands Characteristics                               | 24 |

| Table 6: LE20A4 Pin-out                                         | 28 |

| Table 7: Mandatory Signals                                      | 44 |

| Table 8: Absolute Maximum Ratings – Not Operational             | 48 |

| Table 9: Recommended Operating Conditions                       | 48 |

| Table 10: Absolute Maximum Ratings - Not Functional             | 49 |

| Table 11: Operating Range – Interface Levels (1.8V CMOS)        | 49 |

| Table 12: Operating Range – SD Card Pads Working at 1.8V        | 50 |

| Table 13: Operating Range – SIM Pads Working at 1.8V            | 50 |

| Table 14: Absolute Maximum Ratings - Not Functional             | 51 |

| Table 15: Operating Range – For SD Card Pads Operating at 2.95V | 51 |

| Table 16: Operating Range – For SIM Pads Operating at 2.95V     | 52 |

| Table 17: Power Supply Requirements                             | 59 |

| Table 18: LE920A4 Current Consumption                           | 59 |

| Table 19: GSM / WCDMA/ LTE Antenna Requirements                 | 67 |

| Table 20: Antenna Line on PCB Requirements                      | 67 |

| Table 21: Antenna Diversity Requirements                        | 69 |

| Table 22: Antenna Line on PCB Requirements                      | 71 |

| Table 23: LE920A4 Hardware Interfaces                           | 72 |

| Table 24: USB Interface Signals                                 | 73 |

| Table 25: Ethernet Control Interface Signals                    | 74 |

| Table 26: Modem Serial Port 1 Signals                           | 75 |

| Table 27: Modem Serial Port 2 Signals                           | 77 |

| Table 28: SPI Signals                                           | 79 |

| Table 29: SD Card Signals                                       | 81 |

| Table 30: WiFi SDIO Interface                                   | 83 |

| Table 31: Analog Audio Signals                                  | 84 |

| Table 32: Digital Audio Interface (DVI) Signals                 | 85 |

| Table 33: PCM_CODEC Timing Parameters                           | 87 |

| Table 34: AUX_PCM_CODEC Timing Parameters                       | 89 |

| Table 35: Primary GPIOs                                         | 90 |

| Table 36: Additional GPIOs                                      | 91 |

| Table 37: Network Service Availability Indication               | 93 |

| Table 38: Operating Range – VAUX Power Supply                   | 94 |

| Table 39: ADC Parameters                                        | 94 |

|                                                                 |    |

| Table 40: GNSS Characteristics                 | 96  |

|------------------------------------------------|-----|

| Table 41: Recommendations for PCB Pad Surfaces | 100 |

| Table 42: Solder Profile Characteristics       | 102 |

| Table 43: SIM Interface – C1 Range             | 105 |

| Table 44: EMC Recommendations                  | 106 |

| Table 45: Tray Packing                         | 108 |

| Table 46: Tray Packing Quantities              | 108 |

| Table 47: Document Revision History            | 117 |

# **List of Figures**

| Figure 1: LE920A4 Block Diagram                                   | 21         |

|-------------------------------------------------------------------|------------|

| Figure 2: LGA Pads Layout                                         | 46         |

| Figure 3: LE920A4 vs. LE920 Pin-out Comparison                    | 47         |

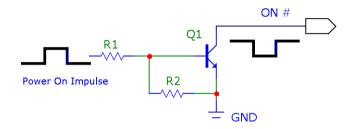

| Figure 4: Power-on Circuit                                        | 53         |

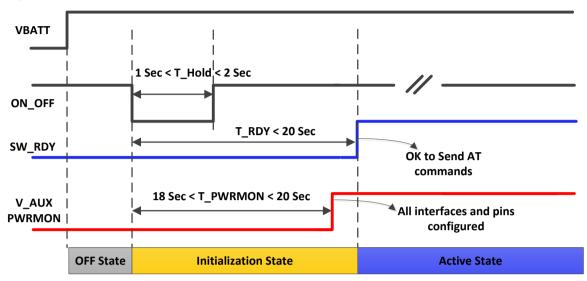

| Figure 5: LE920A4 Initialization and Activation                   | 54         |

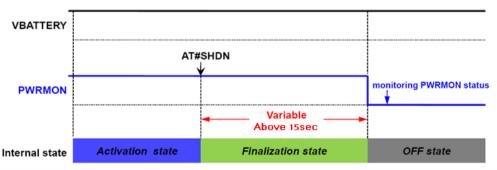

| Figure 6: Shutdown by Software Command                            | 55         |

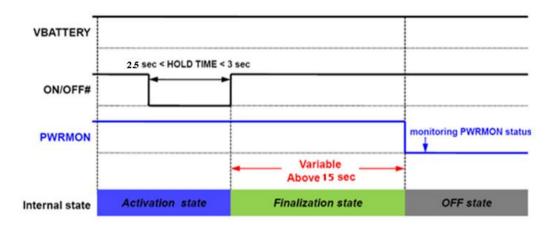

| Figure 7: Hardware Shutdown via ON_OFF                            | 56         |

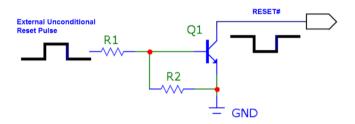

| Figure 8: Circuit for Unconditional Hardware Reset                | 57         |

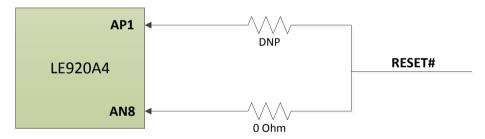

| Figure 9: Alternate Connection of RESET_N Pad                     | 57         |

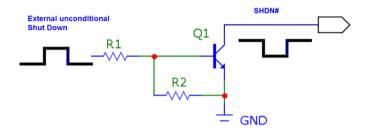

| Figure 10: Circuit for Unconditional Hardware Shutdown            | 58         |

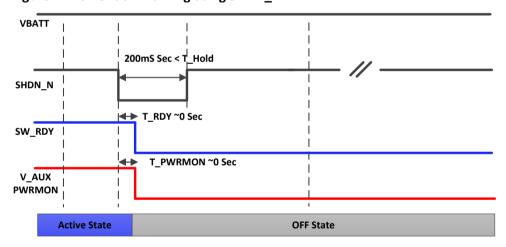

| Figure 11 Power down timing using SHDN_N                          | 58         |

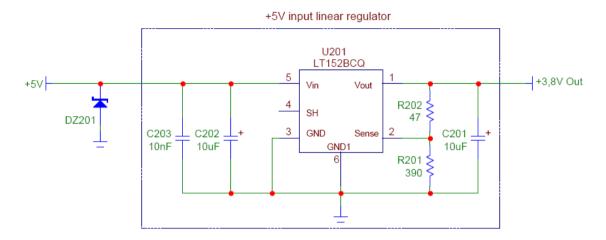

| Figure 12: Example of Linear Regulator with 5V Input              | 62         |

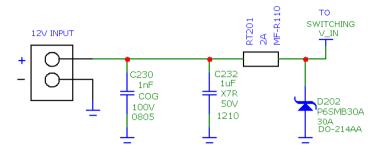

| Figure 13: Example of Switching Regulator with 12V Input – Part 1 | 63         |

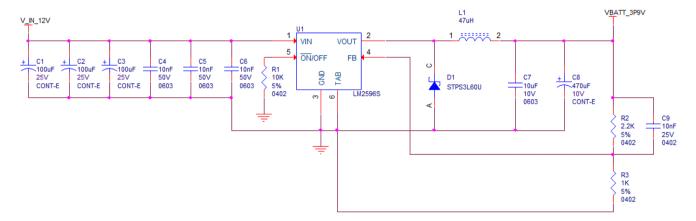

| Figure 14: Example of Switching Regulator with 12V Input – Part 2 | 63         |

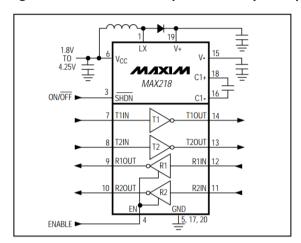

| Figure 15: RS232 Level Adaption Circuitry Example                 | 78         |

| Figure 16: RS232 Serial Port Lines Connection Layout              | 78         |

| Figure 17: SPI Signal Connectivity                                | <b>7</b> 9 |

| Figure 18: SD Interface Connectivity                              | 82         |

| Figure 19: Primary PCM Timing                                     | 86         |

| Figure 20: Auxiliary PCM Timing                                   | 88         |

| Figure 21: GPIO Output Pad Equivalent Circuit                     |            |

| Figure 22: Status LED Reference Circuit                           | 93         |

| Figure 23: Fuel Gauge Connectivity Example                        | 95         |

| Figure 24: LE920A4 Mechanical Dimensions                          | 97         |

| Figure 25: Recommended Footprint (Top View)                       | 98         |

| Figure 26: PCB Pad Design                                         | 99         |

| Figure 27: PCB Pad Dimensions                                     | 100        |

| Figure 28: Solder Reflow Profile                                  | 101        |

| Figure 29: SIM Schematics                                         | 105        |

| Figure 30: Tray Packing                                           | 109        |

| Figure 31: Tray Drawing                                           | 110        |

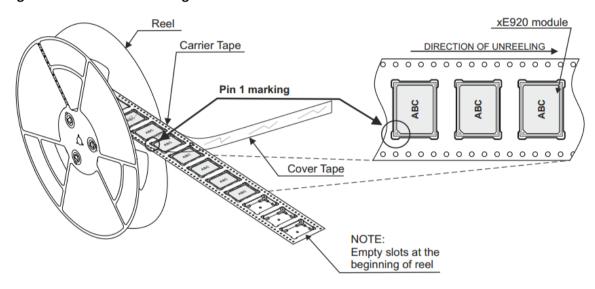

| Figure 32: Module Positioning into the Carrier                    | 111        |

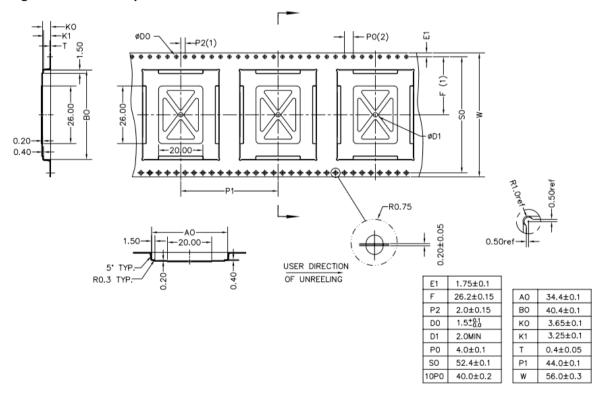

| Figure 33: Carrier Tape Detail                                    | 111        |

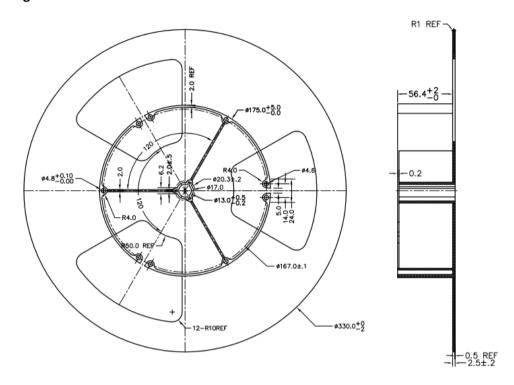

| Figure 34: Reel Detail                                            | 112        |

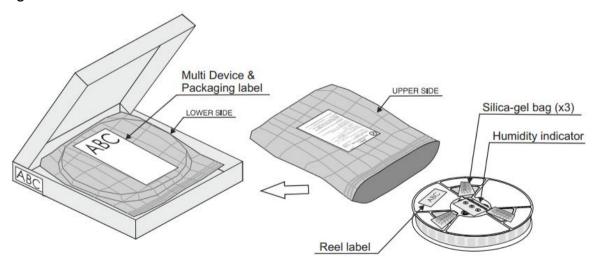

| Figure 35: Reel Box Detail                                        | 112        |

## 1. Introduction

## 1.1. Scope

This document introduces the Telit LE920A4 module and presents possible and recommended hardware solutions for developing a product based on the LE920A4 module. All the features and solutions detailed in this document are applicable to all LE920A4 variants, where "LE920A4" refers to the variants listed in the applicability table.

If a specific feature is applicable to a specific product only, it will be clearly marked.

#### NOTE:

LE920A4 refers to all modules listed in the Applicability Table.

This document takes into account all the basic functions of a wireless module; a valid hardware solution is suggested for each function, and incorrect solutions and common errors to be avoided are pointed out.

Obviously, this document cannot embrace every hardware solution or every product that can be designed. Obviously, avoiding invalid solutions must be considered mandatory. Where the suggested hardware configurations need not be considered mandatory, the information given should be used as a guide and a starting point for properly developing your product with the Telit LE920A4 module.

#### NOTE:

The integration of the GSM/GPRS/EGPRS/WCDMA/HSPA+/LTE LE920A4 cellular module within a user application must be done according to the design rules described in this manual.

#### 1.2. Audience

This document is intended for Telit customers, especially system integrators, about to implement their applications using the Telit LE920A4 module.

# 1.3. Contact Information, Support

For general contact, technical support, to report documentation errors and to order manuals, contact Telit's Technical Support Center (TTSC) at:

- TS-EMEA@telit.com

- TS-NORTHAMERICA@telit.com

- TS-LATINAMERICA@telit.com

- TS-APAC@telit.com

#### Alternatively, use:

http://www.telit.com/en/products/technical-support-center/contact.php

For detailed information about where you can buy the Telit modules or for recommendations on accessories and components, visit:

#### http://www.telit.com

To register for product news and announcements or for product questions contact Telit's Technical Support Center (TTSC).

Our aim is to make this guide as helpful as possible. Keep us informed of your comments and suggestions for improvements.

Telit appreciates feedback from the users about the information provided.

## 1.4. Text Conventions

The following conventions are used to emphasize specific types of information:

#### **DANGER:**

This information MUST be followed or catastrophic equipment failure or bodily injury may occur.

#### **CAUTION or WARNING:**

Alerts the user to important points about integrating the module. If these points are not followed, the module and end user equipment may fail or malfunction.

#### NOTE:

Tip or Information – Provides advice and suggestions that may be useful when integrating the module.

All dates are in ISO 8601 format, that is, YYYY-MM-DD.

#### 1.5. **Related Documents**

#### **Table 2: Related Documents**

| Document Title                                                                                                                     | Document Number |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Ref 1: LE920A4 AT Command User Guide                                                                                               | 80490ST10778A   |

| Ref 2: LE920A4 Software Guide                                                                                                      | 1VV0301332      |

| Ref 3: Generic EVB HW User Guide                                                                                                   | 1VV0301249      |

| Ref 4: LE920A4 Interface Board HW User Guide                                                                                       | 1VV0301248      |

| Ref 5: xE920 Audio Settings Application Note                                                                                       | 80404NT10095A   |

| Ref 6: LE920 Hardware User Guide                                                                                                   | 1VV0301026      |

| Ref 7: SIM Integration Design Guide Application Note Rev10                                                                         | 80000NT10001A   |

| Ref 8: Telit_LE920A4_LE910Cx_Wi-Fi_Interface_Application_Note_r1                                                                   | 80490NT11511A   |

| Ref 9: Antenna Detection Application Note                                                                                          | 80000NT10002A   |

| Ref 10: High-Speed Inter-Chip USB Electrical Specification, version 1.0 (a supplement to the USB 2.0 specification, Section 3.8.2) |                 |

#### **Abbreviations** 1.6.

| Term    | Definition                                  |

|---------|---------------------------------------------|

| ADC     | Analog-to-digital converter                 |

| AE      | Application-enabled                         |

| DAC     | Digital-to-analog converter                 |

| DTE     | Data Terminal Equipment                     |

| FDD     | Frequency division duplex                   |

| GLONASS | Global orbiting navigation satellite system |

| GNSS    | Global navigation satellite system          |

| GPIO    | General-purpose input/output                |

| Term  | Definition                                  |

|-------|---------------------------------------------|

| GPRS  | General packet radio services               |

| GPS   | Global positioning system                   |

| GSM   | Global system for mobile communications     |

| HSIC  | High-speed inter-chip                       |

| 12C   | Inter-integrated circuit                    |

| LTE   | Long term evolution                         |

| SD    | Secure digital                              |

| SGMII | Serial Gigabit media-independent interface  |

| SIM   | Subscriber identity module                  |

| SOC   | System-on-Chip                              |

| SMX   | SmartMX                                     |

| SPI   | Serial peripheral interface                 |

| UART  | Universal asynchronous receiver transmitter |

| UMTS  | Universal mobile telecommunications system  |

| USB   | Universal serial bus                        |

| WCI   | Wireless Coexistence Interface              |

| WCDMA | Wideband code division multiple access      |

# 2. General Product Description

## 2.1. Overview

LE920A4 is Telit's platform for automotive telematics on-board units (OBU's) for applications, such as automotive telematics and eCall, based on the following technologies:

- 4G cellular for voice and data communication

- GNSS GPS, GLONASS, BeiDou, Galileo, QZSS, for positioning service

- Embedded security

- ARM Trust Zone services

- Hardware security processor (optional)

- Designed for automotive markets<sup>1</sup> quality needs

In its most basic use case, LE920A4 can be applied as a wireless communication front-end for telematics products, offering GNSS and mobile communication features to an external host CPU through its rich interfaces.

LE920A4 can further support customer software applications and security features. LE920A4 provides a software application development environment with sufficient system resources for creating rich on-board applications. Thanks to a dedicated application processor and embedded security resources, product developers and manufacturers can create products that guarantee fraud prevention and tamper evidence without extra effort for additional security precautions.

LE920A4 can be self-sufficient and serve as a fully integrated solution for applications, such as location-based cellular telematics, navigation, road pricing and eCall. In such a case, the customer would simply complement the module with a power supply, speaker amplifier, microphone, antennas, and an HMI (if applicable).

LE920A4 is available in hardware variants as listed in Table 1: Applicability Table. The designated RF band sets per each variant are detailed in Section 2.6.1, RF Bands per Regional Variant.

# 2.2. Applications

LE920A4 can be used for telematics applications where tamper-resistance, confidentiality, integrity, and authenticity of end-user information are required, for example:

- Emergency call

- Telematics services

- Road pricing

- Pay-as-you-drive insurance

- Stolen vehicles tracking

- Internet connectivity

<sup>&</sup>lt;sup>1</sup> In accordance with Telit's Robustness Validation, using AEC-Q100-defined qualification tests.

# 2.3. General Functionality and Main Features

The LE920A4 family of automotive cellular modules features LTE and multi-RAT modem together with an on-chip powerful application processor and a rich set of interfaces.

The major functions and features are listed below.

**Table 3: Main Features**

| Function         | Features                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Modem            | Multi-RAT cellular modem for voice and data communication                                                                  |

|                  | o LTE FDD/TDD Cat4 (150/50 Mbps DL/UL)                                                                                     |

|                  | o GSM/GPRS/EDGE                                                                                                            |

|                  | o WCDMA up to DC HSPA+, Rel.9                                                                                              |

|                  | o TD-SCDMA (China variant only)                                                                                            |

|                  | Support for European eCall , US E911, and ERA Glonass                                                                      |

|                  | Support for SIM profile switching                                                                                          |

|                  | <ul> <li>Regional variants with optimal choice of RF bands for worldwide coverage<br/>of countries and MNOs</li> </ul>     |

|                  | <ul> <li>State-of-the-art GNSS solution with GPS/GLONASS/BeiDou/Galileo/QZSS receiver</li> </ul>                           |

| Audio subsystem  | Embedded analog codec with two microphone inputs                                                                           |

|                  | Embedded analog codec with one stereo or two mono outputs                                                                  |

|                  | PCM/I2S digital audio interface                                                                                            |

|                  | Up to 48 kHz sample rate, 16 bit words                                                                                     |

| Two USIM ports – | Class B and Class C support                                                                                                |

| dual voltage     | Hot swap support                                                                                                           |

|                  | Clock rates up to 4 MHz                                                                                                    |

| Application      | Application processor to run customer application code                                                                     |

| processor        | 32 bit ARM Cortex-A7 up to 1.2 GHz running the Linux operating system                                                      |

|                  | <ul> <li>Flash + DDR are large enough to allow for customer's own software<br/>applications</li> </ul>                     |

|                  | Default memory configuration is 4Gb (512MB) Flash + 2Gb (256MB) RAM                                                        |

|                  | • Other memory configuration can be supported upon request, for example: 2Gbit Flash + 2Gbit DDR, 4Gbit Flash + 4Gbit DDR. |

| Function   | Features                                                                                                                                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interfaces | Rich set of interfaces, including:                                                                                                                      |

|            | <ul> <li>SD/MMC Card Interface supporting SD3.0 standard</li> </ul>                                                                                     |

|            | <ul> <li>SDIO for external WiFi transceiver supporting SDIO3.0 standard</li> </ul>                                                                      |

|            | SGMII for external Ethernet transceiver (optional)                                                                                                      |

|            | o Compliant with IEEE802.3                                                                                                                              |

|            | o Full duplex operation at 1 Gbps                                                                                                                       |

|            | <ul> <li>Half/full duplex operation at 10/100 Mbps</li> </ul>                                                                                           |

|            | <ul> <li>Support for VLAN tagging</li> </ul>                                                                                                            |

|            | <ul> <li>Support for IEEE1588, PTP (Precision Time Protocol)</li> </ul>                                                                                 |

|            | <ul> <li>USB2.0 – USB port is typically used for:</li> </ul>                                                                                            |

|            | <ul> <li>Flashing of firmware and module configuration</li> </ul>                                                                                       |

|            | <ul> <li>Production testing</li> </ul>                                                                                                                  |

|            | <ul> <li>Accessing the Application Processor's file system</li> </ul>                                                                                   |

|            | <ul> <li>AT command access</li> </ul>                                                                                                                   |

|            | <ul> <li>High-speed WWAN access to external host</li> </ul>                                                                                             |

|            | <ul> <li>Diagnostic monitoring and debugging</li> </ul>                                                                                                 |

|            | <ul> <li>Communication between Java application environment and an external<br/>host CPU</li> </ul>                                                     |

|            | <ul> <li>NMEA data to an external host CPU</li> </ul>                                                                                                   |

|            | • HSIC                                                                                                                                                  |

|            | <ul> <li>High-speed 480 Mbps (240 MHz DDR) USB transfers are 100% host driver<br/>compatible with traditional USB cable connected topologies</li> </ul> |

|            | <ul> <li>Bidirectional data strobe signal (STROBE)</li> </ul>                                                                                           |

|            | <ul> <li>Bidirectional data signal (DATA)</li> </ul>                                                                                                    |

|            | <ul> <li>No power consumption unless a transfer is in progress</li> </ul>                                                                               |

|            | Maximum trace length 10 cm                                                                                                                              |

|            | <ul> <li>Signals driven at 1.2V standard LVCMOS levels</li> </ul>                                                                                       |

|            | <ul> <li>Peripheral Ports – SPI, I2C, UART</li> </ul>                                                                                                   |

|            | • GPIOs                                                                                                                                                 |

|            | Analog audio I/F                                                                                                                                        |

|            | Antenna ports                                                                                                                                           |

| Function                             | Features                                                                                                                                                       |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Major software                       | Advanced security features                                                                                                                                     |  |  |  |  |

| features                             | <ul> <li>Boot integrity of firmware up to customer applications</li> </ul>                                                                                     |  |  |  |  |

|                                      | Disable/secure re-enable of debug                                                                                                                              |  |  |  |  |

|                                      | <ul> <li>Embedded security</li> </ul>                                                                                                                          |  |  |  |  |

|                                      | FOTA (optional)                                                                                                                                                |  |  |  |  |

|                                      | Telit Unified AT command set                                                                                                                                   |  |  |  |  |

|                                      | <ul> <li>Java VM (optional) with the following features:</li> </ul>                                                                                            |  |  |  |  |

|                                      | Rich and standardized application environment for customer applications                                                                                        |  |  |  |  |

|                                      | <ul> <li>State-of-the-art and high performance Java SE8 embedded Virtual<br/>Machine</li> </ul>                                                                |  |  |  |  |

|                                      | <ul> <li>Oracle Java SE8 Embedded, Compact Profile 1</li> </ul>                                                                                                |  |  |  |  |

|                                      | o JIT-enabled                                                                                                                                                  |  |  |  |  |

| Form factor                          | Form factor (40x34mm), accommodating the multiple RF bands in each region variant                                                                              |  |  |  |  |

| Environment and quality requirements | The entire module is designed and qualified by Telit for satisfying the environment and quality requirements for use in automotive applications <sup>2</sup> . |  |  |  |  |

| Single supply module                 | The module generates all its internal supply voltages.                                                                                                         |  |  |  |  |

| RTC                                  | RTC is maintained as long as VBATT is supplied                                                                                                                 |  |  |  |  |

| Operating temperature                | Range -40 °C to +85 °C (conditions as defined in Section 2.5.1, Temperature Range)                                                                             |  |  |  |  |

$<sup>^{\</sup>mathrm{2}}$  In accordance with Telit's Robustness Validation, using AEC-Q100-defined qualification tests

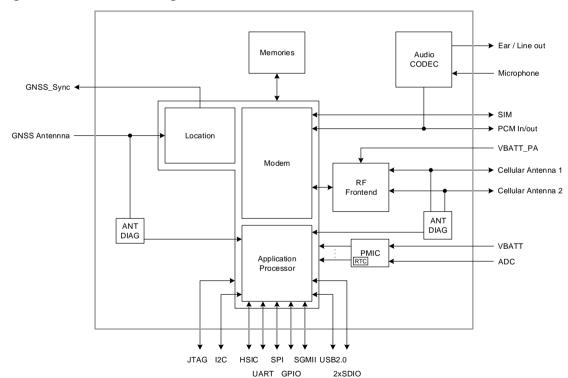

# 2.4. Block Diagram

Figure 1 shows an overview of the internal architecture of the LE920A4 module.

It includes the following sub-functions:

- Application processor, Modem subsystem and Location processing with their external interfaces. These three functions are contained in a single SOC.

- RF front end, including antenna diagnosis circuitry

- Analog Audio codec for attaching external speaker amplifier and microphone

- Rich IO interfaces. Depending on which LE920A4 software features are enabled, some of

its interfaces that are exported through multiplexing may be used internally and thus may

not be usable by the application.

- PMIC with the RTC function inside

Figure 1: LE920A4 Block Diagram

## 2.5. Environmental Requirements

## 2.5.1. Temperature Range

| Operating         |

|-------------------|

| temperature range |

-20 ~ +55°C

This range is defined by 3GPP (the global standard for wireless mobile communication). Telit guarantees its modules to comply with all the 3GPP requirements and to have full functionality of the module with in this range.

-40 ~ +85°C

Telit guarantees full functionality within this range as well. However, there may possibly be some performance deviations in this extended range relative to 3GPP requirements, which means that some RF parameters may deviate from the 3GPP specification in the order of a few dB. For example: receiver sensitivity or maximum output power may be slightly degraded.

Even so, all the functionalities, such as call connection, SMS, USB communication, UART activation etc., will be maintained, and the effect of such degradations will not lead to malfunction.

-40°C ~ +95°C

eCall must be functional (until the module is broken)

Storage and nonoperating temperature range -40°C ~ +105°C

## 2.5.2. RoHS Compliance

As a part of the Telit corporate policy of environmental protection, the LE920A4 complies with the RoHS (Restriction of Hazardous Substances) directive of the European Union (EU directive 2011/65/EU).

# 2.6. Frequency Bands

The operating frequencies in GSM850, EGSM900, DCS1800, PCS1900, WCDMA & LTE modes conform to the 3GPP specifications.

## 2.6.1. RF Bands per Regional Variant

Table 4 summarizes all region variants within the LE920A4 family, showing the supported band sets in each variant.

**Table 4: RF Bands per Regional Variant**

| Region<br>Variant              | LTE FDD                          | LTE TDD         | HSPA+          | TD-<br>SCDMA | 2G         |

|--------------------------------|----------------------------------|-----------------|----------------|--------------|------------|

| LE920A4-NA                     | 2, 4, 5, 7(*), 12                | -               | 2, 4, 5        | -            | 2, 5       |

| LE920A4-NV<br>(TBD)            | 2, 4, 5, 7(*), 13                | -               | 2, 5           | -            | -          |

| LE920A4-EU                     | 1, 3, 5(*), 7, 8, 20, 28(*)      | -               | 1, 3, 5(*), 8  | -            | 3, 8       |

| HE920A-EU<br>(Non-LTE,<br>TBD) | -                                | -               | 1, 3, 5, 8     | -            | 2, 3, 5, 8 |

| LE920A4-CN                     | 1, 3, 5, 8, 26                   | 38, 39, 40, 41M | 1, 5, 8        | 34, 39       | 3, 8       |

| LE920A4-AP<br>(TBD)            | 1, 3, 5, 7, 8, 19, 21, 26,<br>28 | -               | 1, 3, 5, 8, 19 | -            | 2, 3, 5, 8 |

(\*) Indicates optional bands, with a different schedule than the standard configuration Band 41M for China: 2,555-2,655 MHz

## 2.6.2. Reference Table of RF Bands Characteristics

**Table 5: RF Bands Characteristics**

| Mode               | Freq. Tx (MHz)     | Freq. Rx (MHz)  | Channels                               | Tx-Rx Offset |

|--------------------|--------------------|-----------------|----------------------------------------|--------------|

| PCS 1900           | 1850.2 ~<br>1909.8 | 1930.2 ~ 1989.8 | 512~810                                | 80 MHz       |

| DCS 1800           | 1710 ~ 1785        | 1805 ~ 1880     | 512 ~ 885                              | 95 MHz       |

| GSM 850            | 824.2 ~ 848.8      | 869.2 ~ 893.8   | 128 ~ 251                              | 45 MHz       |

| EGSM 900           | 890 ~ 915          | 935 ~ 960       | 0~124                                  | 45 MHz       |

|                    | 880 ~ 890          | 925 ~ 935       | 975 ~ 1023                             | 45 MHz       |

| WCDMA 2100 – B1    | 1920 ~ 1980        | 2110 ~ 2170     | Tx: 9612 ~ 9888<br>Rx: 10562 ~ 10838   | 190 MHz      |

| WCDMA 1900 – B2    | 1850 ~ 1910        | 1930 ~ 1990     | Tx: 9262 ~ 9538<br>Rx: 9662 ~ 9938     | 80 MHz       |

| WCDMA 1800 – B3    | 1710 ~ 1785        | 1805 ~ 1880     | Tx: 937 ~ 1288<br>Rx: 1162 ~ 1513      | 95 MHz       |

| WCDMA AWS – B4     | 1710 ~ 1755        | 2110 ~ 2155     | Tx: 1312 ~ 1513<br>Rx: 1537 ~ 1738     | 400 MHz      |

| WCDMA 850 – B5     | 824 ~ 849          | 869 ~ 894       | Tx: 4132 ~ 4233<br>Rx: 4357 ~ 4458     | 45 MHz       |

| WCDMA 900 – B8     | 880~915            | 925 ~ 960       | Tx: 2712 ~ 2863<br>Rx: 2937 ~ 3088     | 45 MHz       |

| WCDMA 1800 – B9    | 1750 ~ 1784.8      | 1845 ~ 1879.8   | Tx: 8762 ~ 8912<br>Rx: 9237 ~ 9387     | 95 MHz       |

| WCDMA 800 – B19    | 830 ~ 845          | 875 ~ 890       | Tx: 312 ~ 363<br>Rx: 712 ~ 763         | 45 MHz       |

| TDSCDMA 2000 – B34 | 2010 ~ 2025        | 2010 ~ 2025     | Tx: 10054 ~ 10121<br>Rx: 10054 ~ 10121 | 0 MHz        |

| Mode               | Freq. Tx (MHz)     | Freq. Rx (MHz)  | Channels                             | Tx-Rx Offset |

|--------------------|--------------------|-----------------|--------------------------------------|--------------|

| TDSCDMA 1900 – B39 | 1880 ~ 1920        | 1880 ~ 1920     | Tx: 9404 ~ 9596<br>Rx: 9404 ~ 9596   | 0 MHz        |

| LTE 2100 – B1      | 1920 ~ 1980        | 2110 ~ 2170     | Tx: 18000 ~ 18599<br>Rx: 0 ~ 599     | 190 MHz      |

| LTE 1900 – B2      | 1850 ~ 1910        | 1930 ~ 1990     | Tx: 18600 ~ 19199<br>Rx: 600 ~ 1199  | 80 MHz       |

| LTE 1800 – B3      | 1710 ~ 1785        | 1805 ~ 1880     | Tx: 19200 ~ 19949<br>Rx: 1200 ~ 1949 | 95 MHz       |

| LTE AWS – B4       | 1710 ~ 1755        | 2110 ~ 2155     | Tx: 19950 ~ 20399<br>Rx: 1950 ~ 2399 | 400 MHz      |

| LTE 850 – B5       | 824 ~ 849          | 869 ~ 894       | Tx: 20400 ~ 20649<br>Rx: 2400 ~ 2649 | 45 MHz       |

| LTE 2600 – B7      | 2500 ~ 2570        | 2620 ~ 2690     | Tx: 20750 ~ 21449<br>Rx: 2750 ~ 3449 | 120 MHz      |

| LTE 900 – B8       | 880 ~ 915          | 925 ~ 960       | Tx: 21450 ~ 21799<br>Rx: 3450 ~ 3799 | 45 MHz       |

| LTE 1800 – B9      | 1749.9 ~<br>1784.9 | 1844.9 ~ 1879.9 | Tx: 21800 ~ 2149<br>Rx: 3800 ~ 4149  | 95 MHz       |

| LTE AWS+ – B10     | 1710 ~ 1770        | 2110 ~ 2170     | Tx: 22150 ~ 22749<br>Rx: 4150 ~ 4749 | 400 MHz      |

| LTE 700a – B12     | 699 ~ 716          | 729 ~ 746       | Tx: 23010 ~ 23179<br>Rx: 5010 ~ 5179 | 30 MHz       |

| LTE 700c – B13     | 777 ~ 787          | 746 ~ 756       | Tx: 27210 ~ 27659<br>Rx: 9210 ~ 9659 | -31 MHz      |

| LTE 700b – B17     | 704 ~ 716          | 734 ~ 746       | Tx: 23730 ~ 23849<br>Rx: 5730 ~ 5849 | 30 MHz       |

| Mode               | Freq. Tx (MHz)     | Freq. Rx (MHz)  | Channels                               | Tx-Rx Offset |

|--------------------|--------------------|-----------------|----------------------------------------|--------------|

| LTE 800 – B19      | 830 ~ 845          | 875 ~ 890       | Tx: 24000 ~ 24149<br>Rx: 6000 ~ 6149   | 45 MHz       |

| LTE 800 – B20      | 832 ~ 862          | 791 ~ 821       | Tx: 24150 ~ 24449<br>Rx: 6150 ~ 6449   | -41 MHz      |

| LTE 1500 – B21     | 1447.9 ~<br>1462.9 | 1495.9 ~ 1510.9 | Tx: 24450 ~ 24599<br>Rx: 6450 ~ 6599   | 48 MHz       |

| LTE 850+ – B26     | 814 ~ 849          | 859 ~ 894       | Tx: 26690 ~ 27039<br>Rx: 8690 ~ 9039   | 45 MHz       |

| LTE 700 – B28      | 703 ~ 748          | 758 ~ 803       | Tx: 27210 ~ 27659<br>Rx: 9210 ~ 9659   | 45 MHz       |

| LTE TDD 2600 – B38 | 2570 ~ 2620        | 2570 ~ 2620     | Tx: 37750 ~ 38250<br>Rx: 37750 ~ 38250 | 0 MHz        |

| LTE TDD 1900 – B39 | 1880 ~ 1920        | 1880 ~ 1920     | Tx: 38250 ~ 38650<br>Rx: 38250 ~ 38650 | 0 MHz        |

| LTE TDD 2300 – B40 | 2300 ~ 2400        | 2300 ~ 2400     | Tx: 38650 ~ 39650<br>Rx: 38650 ~ 39650 | 0 MHz        |

| LTE TDD 2500 – B41 | 2496 ~ 2690        | 2496 ~ 2690     | Tx: 39650 ~ 41590<br>Rx: 39650 ~ 41590 | 0 MHz        |

# 2.7. Sensitivity

LE920A4 maximum sensitivity levels are as follow:

- -108 dBm (TBD) @ 2G

- -111 dBm (TBD) @ 3G

- -102 dBm (TBD) @ 4G FDD (BW=5 MHz)

# 2.8. LE920A4 Mechanical Specifications

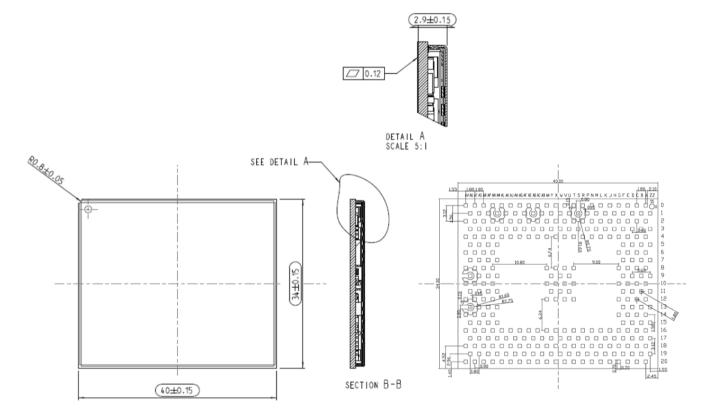

#### 2.8.1. Dimensions

The LE920A4 module's overall dimensions are:

• Length: 34 mm, +/- 0.15 mm tolerance

• Width: 40 mm, +/- 0.15 mm tolerance

• Thickness: 2.9 mm, +/- 0.15 mm tolerance

## 2.8.2. Weight

The nominal weight of the LE920A4 module is 9.0 gram.

# 3. LE920A4 Module Connections

## 3.1. Pin-out

#### Table 6: LE20A4 Pin-out

| PAD     | Signal                        | 1/0 | Function                                        | Туре  | Comment                 |  |  |  |

|---------|-------------------------------|-----|-------------------------------------------------|-------|-------------------------|--|--|--|

| USB HS  | USB HS 2.0 Communication Port |     |                                                 |       |                         |  |  |  |

| D19     | USB_D+                        | 1/0 | USB differential data(+)                        |       |                         |  |  |  |

| F19     | USB_D-                        | 1/0 | USB differential data(-)                        |       |                         |  |  |  |

| A18     | USB_VBUS                      | Al  | Power sense for the internal USB transceiver    | Power | 2.5V-5.5V               |  |  |  |

| B19     | USB_ID                        | Al  | USB ID for supporting USB2.0 OTG                |       |                         |  |  |  |

| Asynchr | onous UART                    |     |                                                 |       |                         |  |  |  |

| AH19    | C103/TXD                      | ı   | Serial data input (TXD) from DTE                | 1.8V  |                         |  |  |  |

| AF19    | C104/RXD                      | 0   | Serial data output to DTE                       | 1.8V  |                         |  |  |  |

| AA18    | C105/RTS                      | I   | Input for Request To Send signal (RTS) from DTE | 1.8V  |                         |  |  |  |

| AK19    | C106/CTS                      | 0   | Output for Clear To Send signal (CTS) to DTE    | 1.8V  |                         |  |  |  |

| AG18    | C107/DSR                      | О   | Output for Data Set Ready (DSR) to DTE          | 1.8V  | Alternate Fn<br>GPIO_32 |  |  |  |

| AC18    | C108/DTR                      | I   | Input for Data Terminal Ready (DTR) from DTE    | 1.8V  | Alternate Fn<br>GPIO_34 |  |  |  |

| AE18    | C109/DCD                      | 0   | Output for Data Carrier Detect (DCD) to DTE     | 1.8V  | Alternate Fn<br>GPIO_33 |  |  |  |

| AJ18    | C125/RING                     | О   | Output for Ring Indication (RI) to DTE          | 1.8V  | Alternate Fn<br>GPIO_31 |  |  |  |

| Asynchr | Asynchronous Auxiliary UART   |     |                                                 |       |                         |  |  |  |

| AB19    | TX_AUX                        | О   | Auxiliary UART (Tx Data to DTE)                 | 1.8V  |                         |  |  |  |

| AD19    | RX_AUX                        | I   | Auxiliary UART (Rx Data from DTE)               | 1.8V  |                         |  |  |  |

| PAD       | Signal                            | 1/0 | Function                                    | Туре      | Comment    |  |  |  |

|-----------|-----------------------------------|-----|---------------------------------------------|-----------|------------|--|--|--|

| SPI – Sei | SPI – Serial Peripheral Interface |     |                                             |           |            |  |  |  |

| P19       | SPI_CLK                           | 0   | SPI clock output                            | 1.8V      |            |  |  |  |

| M19       | SPI_MISO                          | ı   | SPI data Master Input Slave Output          | 1.8V      |            |  |  |  |

| K19       | SPI_MOSI                          | 0   | SPI data Master Output Slave Input          | 1.8V      |            |  |  |  |

| N18       | SPI_CS                            | 0   | SPI chip select output                      | 1.8V      |            |  |  |  |

| SD/MM     | C Card Interface                  |     |                                             |           |            |  |  |  |

| AH17      | SD/MMC_CMD                        | О   | SD command                                  | 1.8/2.95V |            |  |  |  |

| AD17      | SD/MMC_CLK                        | 0   | SD card clock                               | 1.8/2.95V |            |  |  |  |

| Y17       | SD/MMC_DATA0                      | 1/0 | SD Serial Data 0                            | 1.8/2.95V |            |  |  |  |

| AF17      | SD/MMC_DATA1                      | 1/0 | SD Serial Data 1                            | 1.8/2.95V |            |  |  |  |

| AB17      | SD/MMC_DATA2                      | 1/0 | SD Serial Data 2                            | 1.8/2.95V |            |  |  |  |

| W17       | SD/MMC_DATA3                      | 1/0 | SD Serial Data 3                            | 1.8/2.95V |            |  |  |  |

| U17       | SD/MMC_CD                         | I   | SD card detect input                        | 1.8V      | Active Low |  |  |  |

| S17       | VMMC                              | -   | Power supply for MMC card pull-up resistors | 1.8/2.95V |            |  |  |  |

| WiFi (SD  | IO) Interface                     |     |                                             | 1         |            |  |  |  |

| AB3       | WiFi_SD_CMD                       | 0   | WiFi SD command                             | 1.8V      |            |  |  |  |

| AM3       | WiFi_SD_CLK                       | 0   | WiFi SD clock                               | 1.8V      |            |  |  |  |

| AD3       | WiFi_SD_DATA0                     | 1/0 | WiFi SD Serial Data 0                       | 1.8V      |            |  |  |  |

| AF3       | WiFi_SD_DATA1                     | 1/0 | WiFi SD Serial Data 1                       | 1.8V      |            |  |  |  |

| АН3       | WiFi_SD_DATA2                     | 1/0 | WiFi SD Serial Data 2                       | 1.8V      |            |  |  |  |

| AK3       | WiFi_SD_DATA3                     | 1/0 | WiFi SD Serial Data 3                       | 1.8V      |            |  |  |  |

| Y3        | WiFi_SDRST                        | 0   | WiFi Reset / Power enable control           | 1.8V      | Active Low |  |  |  |

| AA4       | WLAN_SLEEP_CLK                    | 0   | WiFi Sleep clock output                     | 1.8V      |            |  |  |  |

| PAD     | Signal                | 1/0 | Function                                     | Туре      | Comment                              |

|---------|-----------------------|-----|----------------------------------------------|-----------|--------------------------------------|

| X4      | RFCLK2_QCA            | О   | WiFi low-noise RF clock output               | 1.8V      |                                      |

| LTE-WiF | i Coexistence         |     |                                              |           | '                                    |

| AS3     | WCI_TX                | О   | Wireless coexistence interface TXD           | 1.8V      |                                      |

| AT2     | WCI_RX                | 1   | Wireless coexistence interface RXD           | 1.8V      |                                      |

| SIM Car | d Interface 1         |     |                                              |           |                                      |

| A10     | SIMCLK1               | О   | External SIM 1 signal – Clock                | 1.8/2.85V |                                      |

| B11     | SIMRST1               | О   | External SIM 1 signal – Reset                | 1.8/2.85V |                                      |

| В9      | SIMIO1                | I/O | External SIM 1 signal - Data I/O             | 1.8/2.85V | Internally PU<br>20 kΩ to<br>SIMVCC1 |

| В7      | SIMIN1                | ı   | External SIM1 signal - Presence              | 1.8V      | Active low                           |

| A8      | SIMVCC1               | -   | External SIM1 signal – power supply for SIM1 | 1.8/2.85V |                                      |

| E8      | Reserved for ESIM_RST | ı   | Reserved for eSIM signal – Reset             | 1.8/2.85V | Reserved                             |

| SIM Car | d Interface 2         |     |                                              |           |                                      |

| C16     | SIMCLK2               | О   | External SIM 2 signal – Clock                | 1.8/2.85V |                                      |

| D17     | SIMRST2               | 0   | External SIM 2 signal – Reset                | 1.8/2.85V |                                      |

| E16     | SIMIO2                | I/O | External SIM 2 signal – Data I/O             | 1.8/2.85V | Internally PU<br>20kΩ to<br>SIMVCC2  |

| C18     | SIMIN2                | ı   | External SIM 2 signal – Presence             | 1.8V      | Active low                           |

| D15     | SIMVCC2               | -   | External SIM2 signal – Power supply for SIM2 | 1.8/2.85V |                                      |

| Analog  | Audio interface       |     |                                              |           |                                      |

| B5      | EAR1_MT+              | АО  | Earphone signal output1, phase +             | Audio     |                                      |

| A4      | EAR1_MT-              | АО  | Earphone signal output1, phase -             | Audio     |                                      |

|         | 1                     |     | I.                                           |           | -                                    |

| PAD       | Signal                | 1/0 | Function                                    | Туре  | Comment             |

|-----------|-----------------------|-----|---------------------------------------------|-------|---------------------|

| В3        | MIC1_MT+              | Al  | Mic signal input1, phase +                  | Audio |                     |

| A2        | MIC1_MT-              | Al  | Mic signal input1, phase -                  | Audio |                     |

| G6        | MICBIAS               | АО  | Mic BIAS                                    | Audio |                     |

| E2        | EAR2_MT+              | АО  | Earphone signal output2, phase +            | Audio |                     |

| D1        | EAR2_MT-              | АО  | Earphone signal output2, phase -            | Audio |                     |

| C2        | MIC2_MT+              | Al  | Mic signal input2, phase +                  | Audio |                     |

| B1        | MIC2_MT-              | Al  | Mic signal input2, phase -                  | Audio |                     |

| Digital \ | /oice Interface (DVI) |     |                                             |       |                     |

| D11       | DVI_WA0               | О   | Digital Voice interface (WA0 master output) | 1.8V  |                     |

| C8        | DVI_RX                | 1   | Digital Voice interface (Rx)                | 1.8V  |                     |

| D9        | DVI_TX                | О   | Digital Voice interface (Tx)                | 1.8V  |                     |

| C10       | DVI_CLK               | О   | Digital Voice interface (CLK master output) | 1.8V  |                     |

| C12       | REF_CLK               | О   | Reference clock for external Codec          | 1.8V  |                     |

| General   | Purpose Digital I/O   |     |                                             | 1     | <u>'</u>            |

| F9        | GPIO_01               | 1/0 | GPIO_01                                     | 1.8V  | Alternate Fn<br>I2C |

| E10       | GPIO_02               | 1/0 | GPIO_02                                     | 1.8V  | Alternate Fn<br>I2C |

| F11       | GPIO_03               | 1/0 | GPIO_03                                     | 1.8V  | Alternate Fn<br>I2C |

| E12       | GPIO_04               | 1/0 | GPIO_04                                     | 1.8V  | Alternate Fn<br>I2C |

| F13       | GPIO_05               | 1/0 | GPIO_05                                     | 1.8V  | Alternate Fn        |

| E14       | GPIO_06               | 1/0 | GPIO_06                                     | 1.8V  | Alternate Fn<br>I2C |

| PAD        | Signal          | 1/0      | Function                                                    | Туре   | Comment      |

|------------|-----------------|----------|-------------------------------------------------------------|--------|--------------|

| W19        | GPIO_10         | 1/0      | GPIO_10                                                     | 1.8V   | Alternate Fn |

| AN4        | GPIO_20         | 1/0      | GPIO_20                                                     | 1.8V   |              |

| RF Section | on              |          |                                                             |        |              |

| AD1        | Antenna         | 1/0      | GSM/EDGE/UMTS/LTE main antenna<br>(50 Ohm)                  | RF     |              |

| AU9        | ANT_DIV         | ı        | UMTS/LTE antenna diversity input (50 Ohm)                   | RF     |              |

| GPS Sec    | tion            | <u>'</u> |                                                             | 1      | '            |

| S1         | ANT_GPS         | ı        | GPS antenna (50 Ohm)                                        | RF     |              |

| V2         | GPS_LNA_EN      | 0        | Enables the external regulator for GPS LNA                  | 1.8V   |              |

| W3         | GPS_SYNC        | 0        | GPS sync signal for Dead Reckoning                          | 1.8V   |              |

| Miscella   | neous Functions |          |                                                             |        |              |

| AN8        | RESET_N         | 1        | Reset input                                                 |        | Active low   |

| AS1        | ON_OFF_N        | ı        | Power ON / Power OFF input                                  |        | Active low   |

| AN12       | SHDN_N          | ı        | Unconditional Shutdown input                                |        | Active low   |

| P17        | VAUX/PWRMON     | 0        | Supply output for external accessories / Power ON monitor   | 1.8V   |              |

| D5         | ADC_IN1         | Al       | Analog/Digital Converter Input 1                            | Analog |              |

| E6         | ADC_IN2         | Al       | Analog/Digital Converter Input 2                            | Analog |              |

| F7         | ADC_IN3         | AI       | Analog/Digital Converter Input 3                            | Analog |              |

| AU3        | STAT_LED        | 0        | Status Indicator LED                                        | 1.8V   |              |

| AN10       | SW_RDY          | 0        | Indicates that the boot sequence has completed successfully | 1.8V   |              |

| SGMII Ir   | nterface        |          |                                                             |        |              |

| ZZ11       | SGMII_RX_P      | AI       | SGMII receive - plus                                        | PHY    |              |

| PAD                            | Signal     | 1/0 | Function                                 | Туре  | Comment                        |  |  |

|--------------------------------|------------|-----|------------------------------------------|-------|--------------------------------|--|--|

| ZZ13                           | SGMII_RX_M | AI  | SGMII receive - minus                    | PHY   |                                |  |  |

| ZZ15                           | SGMII_TX_P | AO  | SGMII transmit - plus                    | PHY   |                                |  |  |

| ZZ17                           | SGMII_TX_M | АО  | SGMII transmit - minus                   | PHY   |                                |  |  |

| Ethernet PHY Control Interface |            |     |                                          |       |                                |  |  |

| G14                            | MAC_MDC    | О   | MAC to PHY Clock                         | 2.85V |                                |  |  |

| G12                            | MAC_MDIO   | 1/0 | MAC to PHY Data                          | 2.85V |                                |  |  |

| G8                             | ETH_RST_N  | 0   | Ethernet PHY Reset                       | 2.85V |                                |  |  |

| G10                            | ETH_INT_N  | ı   | Ethernet PHY Interrupt                   | 2.85V |                                |  |  |

| HSIC Interface                 |            |     |                                          |       |                                |  |  |

| A14                            | HSIC_DATA  | 1/0 | High-speed inter-chip interface - data   | 1.2V  |                                |  |  |

| A16                            | HSIC_STB   | 1/0 | High-speed inter-chip interface - strobe | 1.2V  |                                |  |  |

| I2C Inter                      | rface      |     |                                          | '     | <u>'</u>                       |  |  |

| C14                            | I2C_SCL    | 1/0 | I2C clock                                | 1.8V  | Internally PU<br>2.2kΩ to 1.8V |  |  |

| D13                            | I2C_SDA    | I/O | I2C Data                                 | 1.8V  | Internally PU<br>2.2kΩ to 1.8V |  |  |

| Power S                        | upply      |     |                                          |       |                                |  |  |

| AP17                           | VBATT      | -   | Main Power Supply (Digital Section)      | Power |                                |  |  |

| AP19                           | VBATT      | -   | Main Power Supply (Digital Section)      | Power |                                |  |  |

| AR18                           | VBATT      | -   | Main Power Supply (Digital Section)      | Power |                                |  |  |

| AR20                           | VBATT      | -   | Main Power Supply (Digital Section)      | Power |                                |  |  |

| AS17                           | VBATT_PA   | -   | Main Power Supply (RF Section)           | Power |                                |  |  |

| AS19                           | VBATT_PA   | -   | Main Power Supply (RF Section)           | Power |                                |  |  |

| AT18                           | VBATT_PA   | _   | Main Power Supply (RF Section)           | Power |                                |  |  |

| PAD  | Signal   | 1/0 | Function                       | Туре  | Comment |

|------|----------|-----|--------------------------------|-------|---------|

| AU17 | VBATT_PA | -   | Main Power Supply (RF Section) | Power |         |

| AU19 | VBATT_PA | -   | Main Power Supply (RF Section) | Power |         |

| AT20 | VBATT_PA | -   | Main Power Supply (RF Section) | Power |         |

| A0   | GND      | -   | Ground                         |       |         |

| N0   | GND      |     | Ground                         |       |         |

| RO   | GND      | -   | Ground                         |       |         |

| то   | GND      | -   | Ground                         |       |         |

| V0   | GND      | -   | Ground                         |       |         |

| X0   | GND      | -   | Ground                         |       |         |

| AA0  | GND      | -   | Ground                         |       |         |

| AC0  | GND      | -   | Ground                         |       |         |

| AE0  | GND      | -   | Ground                         |       |         |

| AG0  | GND      | -   | Ground                         |       |         |

| AJ0  | GND      | -   | Ground                         |       |         |

| AL0  | GND      | -   | Ground                         |       |         |

| AN0  | GND      | -   | Ground                         |       |         |

| AR0  | GND      | -   | Ground                         |       |         |

| AV0  | GND      | -   | Ground                         |       |         |

| ZZ1  | GND      | -   | Ground                         |       |         |

| F1   | GND      | -   | Ground                         |       |         |

| M1   | GND      | -   | Ground                         |       |         |

| P1   | GND      | -   | Ground                         |       |         |

| U1   | GND      | -   | Ground                         |       |         |

| PAD | Signal | 1/0 | Function | Туре | Comment |

|-----|--------|-----|----------|------|---------|

| W1  | GND    | -   | Ground   |      |         |

| Y1  | GND    | -   | Ground   |      |         |

| AB1 | GND    | -   | Ground   |      |         |

| AF1 | GND    | -   | Ground   |      |         |

| AH1 | GND    | -   | Ground   |      |         |

| AK1 | GND    | -   | Ground   |      |         |

| AU1 | GND    | -   | Ground   |      |         |

| N2  | GND    | -   | Ground   |      |         |

| R2  | GND    | -   | Ground   |      |         |

| T2  | GND    | -   | Ground   |      |         |

| X2  | GND    | -   | Ground   |      |         |

| AA2 | GND    | -   | Ground   |      |         |

| AC2 | GND    | -   | Ground   |      |         |

| AE2 | GND    | -   | Ground   |      |         |

| AG2 | GND    | -   | Ground   |      |         |

| AJ2 | GND    | -   | Ground   |      |         |

| AL2 | GND    | -   | Ground   |      |         |

| AN2 | GND    | -   | Ground   |      |         |

| AR2 | GND    | -   | Ground   |      |         |

| D3  | GND    | -   | Ground   |      |         |

| Р3  | GND    | -   | Ground   |      |         |

| AP3 | GND    | -   | Ground   |      |         |

| C4  | GND    | -   | Ground   |      |         |

| PAD | Signal | 1/0 | Function | Туре | Comment |

|-----|--------|-----|----------|------|---------|

| AR4 | GND    | -   | Ground   |      |         |

| AT4 | GND    | -   | Ground   |      |         |

| AP5 | GND    | -   | Ground   |      |         |

| AS5 | GND    | -   | Ground   |      |         |

| AU5 | GND    | -   | Ground   |      |         |

| A6  | GND    | -   | Ground   |      |         |

| C6  | GND    | -   | Ground   |      |         |

| AR6 | GND    | -   | Ground   |      |         |

| AT6 | GND    | -   | Ground   |      |         |

| D7  | GND    | -   | Ground   |      |         |

| AP7 | GND    | -   | Ground   |      |         |

| AS7 | GND    | -   | Ground   |      |         |

| AU7 | GND    | -   | Ground   |      |         |

| T8  | GND    | -   | Ground   |      |         |

| V8  | GND    | -   | Ground   |      |         |

| X8  | GND    | -   | Ground   |      |         |

| AA8 | GND    | -   | Ground   |      |         |

| AR8 | GND    | -   | Ground   |      |         |

| AT8 | GND    | -   | Ground   |      |         |

| AV8 | GND    | -   | Ground   |      |         |

| U9  | GND    | -   | Ground   |      |         |

| W9  | GND    | -   | Ground   |      |         |

| Y9  | GND    | -   | Ground   |      |         |

| PAD  | Signal | 1/0 | Function | Туре | Comment |

|------|--------|-----|----------|------|---------|

| AP9  | GND    | -   | Ground   |      |         |