**INSTRUCTION MANUAL**

# DT830A 300-WATT DIGITAL UHF TRANSMITTER

AXCERA, LLC 103 FREEDOM DRIVE, P.O. Box 525 LAWRENCE, PA 15055-0525 USA (724) 873-8100 • FAX (724) 873-8105 www.axcera.com • info@axcera.com

### TABLE OF CONTENTS

#### CHAPTER 1 INTRODUCTION

| 1.1 Manual Overview                                          | 1-1 |

|--------------------------------------------------------------|-----|

| 1.2 Assembly Designation Numbers                             | 1-1 |

| 1.3 Safety                                                   | 1-1 |

| 1.4 Maintenance                                              |     |

| 1.5 Material Return Procedure                                | 1-2 |

| 1.6 Warranty for Axcera Products – Limited One-Year Warranty | 1-3 |

### CHAPTER 2 SYSTEM DESCRIPTION

| 2.1 | System Overview                        | 2-1 |

|-----|----------------------------------------|-----|

|     | 2.1.1 8-VSB Modulator Tray             | 2-1 |

|     | 2.1.2 UHF Digital Exciter Tray         | 2-1 |

|     | 2.1.3 UHF Digital RF Output Components |     |

|     | 2.1.4 Transmitter Power Requirements   | 2-2 |

| 2.2 | Control and Status                     | 2-3 |

|     | 2.2.1 8-VSB Digital Modulator          | 2-3 |

|     | 2.2.2 UHF Digital Exciter Tray         | 2-4 |

|     | 2.2.3 UHF Amplifier Trays              | 2-6 |

|     | Remote Connections                     |     |

# CHAPTER 3 INSTALLATION AND SETUP PROCEDURES

| 3.1 Site Considerations                    | 3-1 |

|--------------------------------------------|-----|

| 3.2 Unpacking the Cabinets                 | 3-4 |

| 3.3 Installation of the Cabinets and Trays | 3-5 |

| 3.4 Setup and Operation Procedures         | 3-5 |

#### CHAPTER 4 CIRCUIT DESCRIPTIONS

| 4.1 UHF Exciter Tray                                                                                                                                                                      |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1.1 UHF Filter                                                                                                                                                                          | 4-1 |

| 4.1.2 UHF Generator Board                                                                                                                                                                 |     |

| 4.1.3 10-MHz Reference Generator Board                                                                                                                                                    |     |

| 4.1.4 PLL Board                                                                                                                                                                           |     |

| 4.1.5 Power Entry Module Assembly                                                                                                                                                         |     |

| 4.1.6 IF Phase Corrector Board                                                                                                                                                            |     |

| 4.1.7 ALC Board                                                                                                                                                                           |     |

| 4.1.8 Visual/Aural Metering Board                                                                                                                                                         |     |

| 4.1.9 UHF Upconverter Board                                                                                                                                                               |     |

| 4.1.10 Transmitter Control Board                                                                                                                                                          |     |

| 4.1.11 +12V(4A)/-12V(1A) Power Supply Board                                                                                                                                               |     |

| 4.1.12 5-Section Delay Equalizer Board, 44 MHz                                                                                                                                            |     |

| <ul> <li>4.1.8 Visual/Aural Metering Board</li> <li>4.1.9 UHF Upconverter Board</li> <li>4.1.10 Transmitter Control Board</li> <li>4.1.11 +12V(4A)/-12V(1A) Power Supply Board</li> </ul> |     |

# TABLE OF CONTENTS (continued)

| 4.2 8-VSB Digital Modulator                               | 4-20 |

|-----------------------------------------------------------|------|

| 4.2.1 Vector Modulator Board                              | 4-20 |

| 4.2.2 Switch Board                                        | 4-21 |

| 4.2.3 Local Oscillator Board                              | 4-21 |

| 4.2.4 LED Board                                           | 4-22 |

| 4.2.5 VSB Modulator Interface Board                       | 4-22 |

| 4.2.6 VSB Filter Board                                    | 4-22 |

| 4.2.7 DC Power Supply Board                               | 4-23 |

| 4.2.8 VSB IF Filter Board                                 |      |

| 4.2.9 VSB Symbol Generator Board                          | 4-23 |

| 4.3 UHF Amplifier Trays                                   |      |

| 4.3.1 1-Watt Amplifier Board Assembly                     | 4-23 |

| 4.3.2 1-Watt Amplifier Board                              | 4-24 |

| 4.3.3 4-Way Splitter Assembly                             |      |

| 4.3.4 4-Way Splitter Board                                | 4-24 |

| 4.3.5 Coupler Board Assembly                              | 4-25 |

| 4.3.6 Dual Peak Detector Enclosure                        | 4-25 |

| 4.3.7 Dual Peak Detector Board, Single Supply             | 4-25 |

| 4.3.8 Dual Stage Amplifier Assembly, Mid Band, Class AB   | 4-26 |

| 4.3.9 Generic Dual Stage Amplifier Board, Class AB        | 4-27 |

| 4.3.10 Amplifier Protection Board                         | 4-27 |

| 4.3.11 Amplifier Control Board                            | 4-28 |

| 4.3.12 Single Stage Amplifier Assembly, Mid Band, Class A | 4-30 |

| 4.3.13 Generic Single Stage Amplifier Board, Class A      |      |

| 4.3.14 Variable Gain/Phase Board Enclosure                | 4-31 |

| 4.3.15 Variable Gain/Phase Board                          |      |

| 4.3.16 4-Way Combiner Assembly                            | 4-33 |

# CHAPTER 5 DETAILED ALIGNMENT PROCEDURES

| 5.1 | UHF Exciter Tray                                           | 5-1 |

|-----|------------------------------------------------------------|-----|

|     | 5.1.1 Delay Equalization Adjustment                        |     |

|     | 5.1.2 IF Phase Corrector Adjustment                        | 5-3 |

|     | 5.1.3 UHF Generator Board                                  | 5-4 |

|     | 5.1.4 10-MHz Reference Generator Board                     | 5-4 |

|     | 5.1.5 PLL Board                                            | 5-4 |

| 5.2 | UHF Amplifier Trays                                        | 5-6 |

|     | 5.2.1 Phase and Gain Adjustment of the UHF Amplifier Trays | 5-7 |

# TABLE OF CONTENTS (continued)

| 5.3 8-VSB Modulator                                    | 5-8  |

|--------------------------------------------------------|------|

| 5.3.1 VSB Modulator Interface Board                    |      |

| 5.3.2 VSB Symbol Generator Board                       | 5-9  |

| 5.3.3 VSB Filter Board                                 |      |

| 5.3.4 Switch Board                                     | 5-13 |

| 5.3.5 Local Oscillator Board                           | 5-13 |

| 5.3.6 VSB Vector Modulator Board                       | 5-14 |

| 5.3.7 DC Power Supply Board                            | 5-14 |

| 5.3.8 VSB IF Filter Board                              | 5-15 |

| 5.3.9 LED Board                                        | 5-15 |

| 5.3.10 Offset Adjust                                   | 5-15 |

| 5.3.11 Local Oscillator Leak-Through Adjustment        | 5-15 |

| 5.3.12 I and Q Baseband Frequency Response Adjustments |      |

| 5.3.13 Gain and Quadrature Adjustments                 | 5-16 |

| 5.3.14 Output Level Adjust                             | 5-16 |

| 5.4 Output Power Level                                 | 5-17 |

|                                                        |      |

#### APPENDICES

| APPENDIX A SA | AMPLE LOG REPO | RT SHEET |

|---------------|----------------|----------|

|---------------|----------------|----------|

- APPENDIX B TYPICAL OPERATIONAL READINGS

- APPENDIX C ASSEMBLY DRAWINGS AND PARTS LISTS

- APPENDIX D SUBASSEMBLY DRAWINGS AND PARTS LISTS

- APPENDIX E DT830A SYSTEM SPECIFICATIONS

# LIST OF FIGURES

| 2-1 | Remote Interface Panel2-                 | 8 |

|-----|------------------------------------------|---|

| 3-1 | 1 kW Minimum Ventilation Configuration3- | 4 |

| 5-1 | Typical Digital Spectrum5-               | 3 |

# LIST OF TABLES

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12 | DT830A Major Assemblies and Trays2-1Digital Modulator Display2-3Digital Modulator Control Pushbuttons2-4Digital Modulator Status Indicators2-4Digital Modulator Sample2-4UHF Exciter Tray Meters2-4UHF Exciter Tray Controls2-5UHF Exciter Tray Fault Indicators2-5UHF Exciter Tray Samples2-6UHF Amplifier Tray Meters2-6UHF Amplifier Tray Status Indicators2-7UHF Amplifier Tray Controls2-7 |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-13                                                                                | UHF Amplifier Tray Sample                                                                                                                                                                                                                                                                                                                                                                       |

| 2-14                                                                                | UHF Exciter Remote Connections2-9                                                                                                                                                                                                                                                                                                                                                               |

| 2-15                                                                                | UHF Amplifier Tray Remote Connections                                                                                                                                                                                                                                                                                                                                                           |

| 4-1                                                                                 | Fuses, Idling Currents, and Voltage Settings for the<br>Class AB Amplifier Devices                                                                                                                                                                                                                                                                                                              |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8                                | Jumper Positions on the 6-dB Pad5-1Center Frequencies for the Delay Equalizer Sections5-3PLL Board Switch Positions5-5PLL Board Switch Positions for Channel Frequencies5-58-VSB Modulator Connections5-8Jumper Configurations for the Symbol Generator Board5-10Jumper Configurations for the VSB Filter Board5-12DIP Switch Settings5-13                                                      |

| 5.0                                                                                 | Dir Switch Settings                                                                                                                                                                                                                                                                                                                                                                             |

# Chapter 1 Introduction

This manual explains the installation, setup, alignment, and maintenance procedures for the DT830A 300-watt digital UHF transmitter. It is important that you read all of the instructions, especially the safety information in this chapter, before you begin to install or operate the unit.

# 1.1 Manual Overview

This instruction manual is divided into five chapters and supporting appendices. Chapter 1, Introduction, contains information on safety, the Axcera method of assigning assembly designation numbers, maintenance, return procedures, and warranties. The second chapter describes the transmitter and its system control and status indicators and remote control connections. Chapter 3 explains how to unpack, install, set up, and operate the transmitter. Chapter 4, Circuit Descriptions, describes the circuits that make up the trays and assemblies in the transmitter. Chapter 5, Detailed Alignment Procedures, provides information on adjusting the system assemblies for optimal operation. The appendices contain sample log sheets, typical operational readings, assembly and subassembly drawings and parts list, and product information for vendorsupplied products used in the transmitter.

# **1.2 Assembly Designation Numbers**

Axcera has assigned assembly numbers, such as Ax (x=1,2,3...), to all assemblies, trays, and boards that are referenced in the text of this manual and shown on the block diagrams and interconnect drawings provided in the appendices. These supporting documents are arranged in increasing numerical order in the appendices. Section titles in the text for assembly or tray descriptions or alignment procedures also indicate the associated part number(s) and the relevant appendices. Sections describing vendor-supplied items, such as meters and power supplies, do not contain this information.

# 1.3 Safety

The 300-watt UHF transmitters manufactured by Axcera are designed to be easy to use and repair while providing protection from electrical and mechanical hazards. Listed throughout the manual are notes, cautions, and warnings concerning possible safety hazards that may be encountered while operating or servicing the transmitter. Please review these warnings and familiarize yourself with the operation and servicing procedures before working on the transmitter.

**Read All Instructions** – All of the operating and safety instructions should be read and understood before operating this equipment.

**Retain Manuals** – The manuals for the transmitter should be retained at the transmitter site for future reference. We provide two sets of manuals for this purpose; one set can be left at the office while one set can be kept at the site.

# Heed Notes, Warnings, and

**Cautions** – All of the notes, warnings, and cautions listed in this safety section and throughout the manual must be followed.

**Follow Instructions** – All of the operating and use instructions for the transmitter should be followed.

**Cleaning** – Unplug or otherwise disconnect power from the equipment before cleaning. Do not use liquid or aerosol cleaners. Use a damp cloth for cleaning. **Ventilation** – Openings in the cabinets and tray front panels are provided for ventilation. To ensure reliable operation, and to protect the unit from overheating, these openings must not be blocked.

**Servicing** – Do not attempt to service this product until becoming familiar with the equipment. If in doubt, refer all servicing questions to qualified Axcera service personnel.

### Replacement Parts - When

replacement parts are used, be sure that the parts have the same functional and performance characteristics as the original part. Unauthorized substitutions may result in fire, electric shock, or other hazards. Please contact the Axcera Technical Service Department if you have any questions regarding service or replacement parts.

Caution: Because the capacitors used in the high-voltage circuits have the potential of recharging themselves, care must be taken when handling them. The capacitors should first be shorted with a grounding stick and then a piece of wire should be connected across the terminals until they can be put into service. Remember to remove the shorting wire before energizing the high-voltage supply.

# 1.4 Maintenance

The DT830A is designed with components that require little or no periodic maintenance except for the routine cleaning of the fans and the front panels of the trays.

The amount and time interval between cleanings depends on the conditions within the transmitter room. While the electronics have been designed to function even if covered with dust, a heavy buildup of dust, dirt, or insects will hinder the effectiveness of the cooling of the components. This could lead to a thermal shutdown or the premature failure of the affected trays.

When the front panels of the trays become dust covered, the top covers should be removed and any accumulated foreign material should be removed. A vacuum cleaner, utilizing a small, wandtype attachment, is an excellent way to suction out the dirt. Alcohol and other cleaning agents should not be used unless you are certain that the solvents will not damage components or the silkscreened markings on the trays and boards. Water-based cleaners can be used, but do not saturate the components. The fans and heatsinks should be cleaned of all dust or dirt to permit the free flow of air for cooling purposes.

It is recommended that the operating parameters of the transmitter be recorded from the meters on the trays and the system metering control panel at least once a month. It is suggested that this data be retained in a rugged folder or envelope for the life of the equipment. A sample format for a log sheet is provided in Appendix A. Photocopies of the log sheet should be made for future data entries.

# **1.5 Material Return Procedure**

To insure the efficient handling of equipment or components that have been returned for repair, Axcera requests that each returned item be accompanied by a Material Return Authorization Number (MRA#).

An MRA# can be obtained from any Axcera field service engineer by calling the Axcera Field Service Department at (724) 873-8100. This procedure applies to all items sent to the Field Service Department regardless of whether the item was originally manufactured by Axcera.

#### Note: To prevent damage to the product during shipping, Axcera will supply a shipping container to the customer at no cost.

When equipment is sent to the field on loan, an MRA# is included with the unit. The MRA# is intended to be used for the return of the unit to Axcera. In addition, all shipping material should be retained for the return of the unit to Axcera. Replacement assemblies are also sent with an MRA# to allow for the proper routing of the exchanged hardware. Failure to close out this type of MRA# will normally result in the customer being invoiced for the value of the loaner item or the exchange assembly.

When shipping an item to Axcera, please include the MRA# on the packing list and on the Axcera-provided shipping container. The packing slip should also include contact information and a brief description of why the unit is being returned.

Please forward all MRA items to:

#### Axcera 103 Freedom Drive P.O. Box 525 Lawrence, PA 15055-0525 USA

For more information concerning this procedure, call Axcera Field Service at **(724) 873-8100** or by fax at **(724) 873-8105**.

Axcera can also be contacted through email at info@axcera.com and on the Web at www.axcera.com.

#### **1.6 Warranty for Broadcast Products** - Limited One-Year Warranty

Axcera warrants each new product that it has manufactured and sold against defects in material and workmanship under normal use and service for a period of one (1) year from the date of shipment from Axcera's plant, when operated in accordance with Axcera's operating instructions. This warranty shall not apply to tubes, fuses, batteries, or bulbs.

Warranties are valid only when and if (a) Axcera receives prompt written notice of breach within the period of warranty, (b) the defective product is properly packed and returned by the buyer (transportation and insurance prepaid), and (c) Axcera determines, in its sole judgment, that the product is defective and not subject to any misuse, neglect, improper installation, negligence, accident, or (unless authorized in writing by Axcera) repair or alteration. Axcera's exclusive liability for any personal and/or property damage (including direct, consequential, or incidental) caused by the breach of any or all warranties, shall be limited to the following: (a) repairing or replacing (in Axcera's sole discretion) any defective parts free of charge (F.O.B. Axcera's plant) and/or (b) crediting (in Axcera's sole discretion) all or a portion of the purchase price to the buyer.

Equipment furnished by Axcera, but not bearing its trade name, shall bear no warranties other than the special hoursof-use or other warranties extended by or enforceable against the manufacturer at the time of delivery to the buyer. NO WARRANTIES, WHETHER STATUTORY, EXPRESSED, OR IMPLIED, AND NO WARRANTIES OF **MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR** FREEDOM FROM INFRINGEMENT, OR THE LIKE, OTHER THAN AS SPECIFIED IN PATENT LIABILITY **ARTICLES, AND IN THIS ARTICLE,** SHALL APPLY TO THE EQUIPMENT FURNISHED HEREUNDER.

# Chapter 2 System Description

The DT830A is a complete 300-watt (average) UHF solid-state digital television transmitter that operates at a nominal average output power of 300 watts.

### 2.1 System Overview

The DT830A consists of the assemblies and trays listed in Table 2-1.

| MAJOR ASSEMBLY NUMBER | TRAY/ASSEMBLY NAME                  |

|-----------------------|-------------------------------------|

| A4                    | UHF digital exciter tray            |

| A6 and A7             | UHF amplifier trays                 |

| A11                   | Coupler assembly                    |

| A2                    | AC distribution assembly            |

| A19                   | 8-VSB modulator tray                |

| A12                   | Input and remote interface assembly |

| A8                    | UHF "tee"                           |

#### Table 2-1. DT830A Major Assemblies and Trays

#### 2.1.1 (A19) 8-VSB Modulator Tray (1075164; Appendix C)

The 8-VSB modulator accepts an MPEG-2 transport stream input and outputs an 8 VSB IF signal centered at 44 MHz. To operate the modulator, the MPEG is connected to one of the three connectors on the rear panel, depending on the format of the MPEG data stream. The formats presently available are SMPTE 310M, Differential Serial TTL, and ECL. In addition, the modulator has an internal test source that can generate an MPEG data stream for test purposes. This signal is then modulated to a 44 MHz IF and fed to the output at J1.

### 2.1.2 (A4) UHF Digital Exciter Tray (1294-1111; Appendix C)

The output from the modulator connects to J6 on the rear of the UHF exciter tray, which is wired to J18 on the IF delay equalizer board, 44 MHz (1072090) and exits the board at J10. The processed digital IF signal is then wired to the ALC board (1265-1305) at J32. With digital IF input selected, the jumper W11 on J29 is connected between pins 2 and 3 on the ALC board; the digital IF is wired through the K3 and K4 relays to the rest of the ALC board. The LED DS5, digital IF modulator enable, should be lit. The ALC board has the capability to switch between two different IF inputs; in this case, only the digital IF input is used. The output of the ALC board (0 dBm peak) connects to (A11) the UHF upconverter board (1265-1310) in the upconverter section of the UHF digital exciter. The upconverter takes the LO and heterodynes it with the IF; the signal is then filtered to produce the RF onchannel output.

The (A15-A1) UHF generator board (1565-1109) is mounted in the UHF Generator Enclosure (1519-1144) for EMI and RFI protection. The board contains a VCXO circuit and additional circuitry to multiply the VCXO frequency by eight. The output is split and provides an input to the x8 multiplier circuitry as well as a sample for the PLL board.

The amplified eighth harmonic is then fed to the SMA output jack of the board at J3.

Typical output level of the signal is +16 dBm nominal.

The (A14-A1) 10-MHz reference generator board (1519-1126) is located in (A10) the 10-MHz reference kit (1286-1108). The board contains a highstability crystal oscillator that provides a 10-MHz output that is used as reference frequency for the transmitter. The board is mounted within an enclosed assembly that helps to maintain the operating temperature of the oscillator board.

The (A13) PLL board (1286-1104) is part of the phase lock loop (PLL) circuit, which provides the automatic frequency control (AFC) voltage, that connects to the VCXO assembly, and maintains the accurate output frequency of the VCXO. The AFC is generated by comparing a sample of the 10-MHz reference to a sample of the VCXO frequency. The PLL board uses an external 10-MHz signal as the reference unless it is missing, then an internally generated 10-MHz signal is used.

A sample of the signal from the UHF generator board connects to SMA jack J9, the sample input on the board. The signal is amplified by U8 and coupled to U9, a divide by 20/21 IC. A sample of the signal at the output of U8 is connected to J10, the sample output jack on the board, which is typically connected to the front panel of the tray.

The selected 10-MHz reference connects to amplifier IC U1 whose output is split. A sample of the 10-MHz reference is cabled to jack J3, the 10-MHz output jack, which is connected to J5 on the rear of the tray.

If the 50 kHz from the 10-MHz reference and the 50-kHz from the UHF generator board become unlocked, the red Unlock LED, lights and the Lock LED, located on the LED display board, is extinguished.

### 2.1.3 UHF Digital RF Output Components

The RF output of the UHF exciter is fed to an (A5) splitter and then to two UHF amplifier trays that amplify the RF signal to approximately 300 watts. A forward power sample from the 4-way combiner board inside each tray is connected to the dual peak detector board that provides a peak-detected forward sample to the amplifier control board. This board supplies the sample to the front panel meter of the UHF amplifier tray.

Before exiting the UHF amplifier tray, the RF is fed through a circulator to protect the tray from high VSWR conditions. The reject port of the circulator provides a reject sample to the 4-way combiner board that supplies the reflected sample to the dual peak detector board. The reflected sample connects to the amplifier control board that provides the sample to the front panel meter of the tray. The output of (A6 and A7) the UHF amplifier trays are combined in a tee and then provide approximately 550 watts average power. The output is connected to a bandpass filter and then to the output coupler assembly. There is a coupler on the output of the bandpass filter that provides -40 dB forward and reflected samples to the system control panel. The bandpass filter is tuned to provide high out-of-band rejection of unwanted products. The 7/8" coupler assembly provides two forward power samples and one reflected power sample. The forward and reflected samples are cabled to the visual/aural metering boards in the UHF exciter. The forward and reflected samples are processed to provide detected power output samples to the transmitter control board. The transmitter control board connects the forward and reflected power output samples to the front panel meter for monitoring.

# 2.1.5 Transmitter Power Requirements

The transmitter needs an AC input of 220 VAC at 40 amps, or 80 amps for the upgradeable version, connected to it in order to operate. The 220 VAC input connects to terminal block (TB1) in the upper right rear of the cabinet and is part of the (A2) AC distribution panel. The AC distribution panel contains four circuit breakers, six in the upgradeable version, which supply the AC to the rest of the transmitter.

The input AC from TB1 is connected to (CB1) the main AC circuit breaker (40 amps for DT830A and 80 amps for the upgradeable version) which distributes the 220 VAC to the terminal block (TB2). TB2 has three MOVs mounted to the terminal block: one is connected from each leg of the input AC to ground and the other one is connected across the two legs.

The input AC is wired from TB2 through three circuit breakers, CB2, CB3 and CB4, CB5 and CB6 are used in the upgradeable version, to the rest of the transmitter. CB2 (10 amps) supplies the AC voltage to the IEC outlet strip (A1) into which the UHF exciter and any other optional accessories are connected. CB3 (20 amps) supplies AC through J5 to (A6) the UHF amplifier tray. CB4 (20 amps) supplies AC through J6 to (A7) the UHF amplifier tray. In the upgradeable version, CB5 (20 amps) supplies AC through J6 to (A8) the UHF amplifier tray and CB6 (20 amps) supplies AC through J6 to (A9) UHF amplifier tray. .When the UHF exciter circuit breaker is switched on, +12 VDC is supplied to the UHF amplifier tray for the operation of the LED status indicators in the tray.

# 2.2 Control and Status

Control and status indications of the transmitter are provided by the meters and LED indicators on the front panel of the UHF exciter. The switches and LED indicators are part of the transmitter control board (1265-1311) which is mounted so that the switches and the LEDs can be operated or viewed from the front panel of the UHF exciter. Switch S1 is an Operate/Standby switch that controls the output of the transmitter by providing the Enables, when in Operate, needed to turn on the switching power supplies in the two or four UHF amplifier trays. In Operate, the green LED DS2 is on and in Standby the amber LED DS1 is on.

If the transmitter does not switch to Operate when S1 is switched to Operate, check that a dummy jumper plug, with a jumper between pins 23 and 24, is connected to jack J11 on the rear of the UHF exciter tray or with a jumper between pins 21 and 22 on jack J9 on (A17) the (optional) input and remote interface panel. This jumper provides the interlock needed for the transmitter to operate. If the interlock is present, the green LED DS5 on the transmitter control board should be lit. The front panel of the UHF exciter also has an LED for VSWR cutback (amber LED DS7).

# 2.2.1 (A19) 8-VSB Digital Modulator (1075164; Appendix C)

| DISPLAY | FUNCTION                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCD     | Provides a three-line readout of the internal<br>functions, external inputs, and status. See<br>Chapter 4, Detailed Alignment Procedures,<br>for a listing of display parameters. |

Table 2-2. Digital Modulator Display

The front panel has three pushbuttons for the control of the external and internal functions.

| PUSHBUTTON     | FUNCTION                                     |

|----------------|----------------------------------------------|

| Menu           | Controls which menu is displayed on the      |

| мени           | LCD readout                                  |

|                | Moves the active line up one position on the |

| Up Arrow (↑)   | LCD display                                  |

|                | Moves the active line down one position on   |

| Down Arrow (↓) | the LCD display                              |

There are four front panel status indicator LEDs.

| LED                | FUNCTION                                                                                                  |

|--------------------|-----------------------------------------------------------------------------------------------------------|

| MPEG (Green)       | Indicates the presence of an MPEG-2 signal;<br>can be internal or external depending on<br>menu selection |

| REF (Green)        | Indicates the presence of an external 10<br>MHz reference source                                          |

| PLL Locked (Green) | Indicates that the phase-locked loop circuit is functioning and locked                                    |

| Power (Green)      | Indicates that the DC power supply is<br>functioning                                                      |

| SAMPLE             | DESCRIPTION                    |

|--------------------|--------------------------------|

| Front panel sample | Sample of the 44 MHz IF output |

# 2.2.2 (A4) UHF Digital Exciter Tray (1294-1111; Appendix C)

| Table 2-6. UHF Exciter Tray | / Meters |

|-----------------------------|----------|

|-----------------------------|----------|

| METER              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Meter (A4-A18)     | Reads power in terms of a percentage of<br>the calibrated output power level on the<br>upper scale. The voltage level is read on<br>one of the bottom two scales. A full scale<br>reading on the top scale is 0-120%, which<br>is equivalent to the full-rated 300 watts or<br>1000 watts in the upgradeable version,<br>average power. Also reads % Exciter<br>Power, % Reflected Power, and ALC<br>reading. |

| Switch (S3), meter | Selects the desired ALC voltage reading, %<br>Exciter Power, % Output Power, and %<br>Reflected Power                                                                                                                                                                                                                                                                                                         |

| ALC<br>(0-1 V)     | Reads the ALC voltage level, .8 VDC, on the 0-10 scale                                                                                                                                                                                                                                                                                                                                                        |

| METER                  | FUNCTION                                                                                                      |

|------------------------|---------------------------------------------------------------------------------------------------------------|

| % Exciter<br>(0-120)   | Reads the % Exciter Output Power level<br>needed to attain 100% output of the<br>transmitter on the top scale |

| % Output power         | Reads the % Output Power of the                                                                               |

| (0-120)                | transmitter on the top scale                                                                                  |

| % Reflected<br>(0-120) | Reads the % Reflected Output Power, <5%, on the top scale                                                     |

| SWITCH                              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter (S1)<br>Operate/Standby | The momentary switch (S1) applies a<br>ground to K1, a latching relay on<br>the transmitter control board. K1 will switch<br>either to Operate or to Standby<br>depending on which direction S1 is pushed.<br>When switched to Operate, the low Enable<br>commands are applied to the two or four<br>600-watt amplifier trays. These Enables will<br>turn on the 600-watt amplifier trays. The<br>opposite occurs when the transmitter is<br>switched to Standby.                                                                                                                                                                                        |

| Mode Select (S2)<br>Auto/Manual     | The momentary contact switch (S2) applies<br>a ground to K2, a latching relay on the<br>transmitter control board. K2 will switch the<br>transmitter to Automatic or Manual<br>depending on which direction S2 is pushed.<br>In Automatic, the Video Fault command<br>from the ALC board will control the<br>operation of the transmitter. The<br>transmitter will switch to Standby, after a<br>slight delay, if the input video is lost. It will<br>quickly switch back to Operate when the<br>video is restored. In Manual, the transmitter<br>is controlled by the operator using the front<br>panel Operate/Standby switch or by remote<br>control. |

| Power adjust (R1)                   | Pot A20 sets the ALC level on the ALC<br>board to set the output power of<br>the transmitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Table 2-7. UHF Exciter Tray Controls

| Table 2-8. UHF Exciter | Tray Fault Indicators |

|------------------------|-----------------------|

|------------------------|-----------------------|

| INDICATOR                | FUNCTION                                                                                                                                                                                                                              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSWR cutback (DS7 amber) | Indicates that the reflected power level of the transmitter has increased above 20% which will automatically cut back the output power level to 20%. The fault is generated on the transmitter control board in the UHF exciter tray. |

| SAMPLE          | DESCRIPTION                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| f(s)            | A sample of the channel oscillator output,<br>taken from the sample jack of the channel<br>oscillator assembly                              |

| Exciter O/P     | An output power sample of the exciter taken from the UHF upconverter board                                                                  |

| Transmitter O/P | A forward power sample of the transmitter<br>taken from the visual/aural metering board<br>before the signal reaches the bandpass<br>filter |

#### 2.2.3 (A6 and A7) UHF Amplifier Trays (1294-1112 Low Band, 1294-1113 Mid Band or 1294-1114 High Band ; Appendix C)

| METER              | FUNCTION                                                                                                                                                                                                                                    |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Meter (A6)         | Reads power in terms of a percent of the calibrated power output value. A full-scale reading is 100%, which is equivalent to the full-rated 300 watts of average power. Also reads % Reflected Power, power supply, and AGC voltage levels. |

| Switch (S2), meter | Selects the desired % Power or the voltage reading                                                                                                                                                                                          |

| % Output pwr       | Displays the % Output Power of the tray                                                                                                                                                                                                     |

| % Refl (Reflected) | Displays the % Reflected Output Power of the tray, <10% on the top scale                                                                                                                                                                    |

| Power supply       | Reads the power supply voltage, +26.5 VDC, on middle scale                                                                                                                                                                                  |

| AGC voltage        | Reads the AGC voltage level, +1 to +2<br>VDC, on the bottom scale                                                                                                                                                                           |

Table 2-10. UHF Amplifier Tray Meters

| INDICATOR              | FUNCTION                                                                                                                                                                                                                                                                                                                                          |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable (DS4 green)     | Indicates that an Enable, Operate,<br>command is applied to the UHF amplifier<br>tray from the UHF exciter tray                                                                                                                                                                                                                                   |

| Overdrive (DS2 red)    | Indicates that the level of the drive is too<br>high. The protection circuit will limit the<br>drive to the set threshold. The fault is<br>generated on the amplifier control board.                                                                                                                                                              |

| VSWR cutback (DS1 red) | Indicates that the reflected power level of<br>the tray has increased above 50%, which<br>will automatically cut back the output power<br>level to 50%. The fault is generated on<br>the amplifier control board.                                                                                                                                 |

| Overtemp (DS3 red)     | Indicates that the temperature of (A5-A6-<br>A3 and A5-A6-A4) one or both of the two<br>thermal switches mounted on the heatsink<br>assembly for the output amplifiers is above<br>175° F. When this fault occurs, the Enable<br>to the switching power supply in the<br>affected amplifier tray is removed<br>immediately and it will shut down. |

| Input fault (DS5 red)  | Indicates that the input RF level to the amplifier tray dropped below 0 dBm                                                                                                                                                                                                                                                                       |

Table 2-12. UHF Amplifier Tray Controls

| CONTROL        | FUNCTION                                                                          |

|----------------|-----------------------------------------------------------------------------------|

| Phase (A10-R5) | Adjusts the phase of the RF output with a range of approximately 90°              |

| Gain (A11-R6)  | Adjusts the gain of RF output when the amplifier control board is in the AGC mode |

| Table 2-13. | UHF  | Amplifier    | Trav  | Sample |

|-------------|------|--------------|-------|--------|

| 10010 2 101 | 0111 | <i>,p</i> c. | in ay | Sample |

| SAMPLE             | DESCRIPTION                                                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------|

| Module O/P (0 dBm) | A sample of the combined output of the four dual-stage amplifier boards taken from the dual peak detector board |

# 2.3 Remote Connections

The IF input to the transmitter connects to the rear of the UHF exciter or to (A12) the input and remote interface panel (Figure 2-1). Jacks J10 and J11 on the rear of the UHF exciter provide connections for the remote monitoring and operation of the transmitter. Jack J11 should have a dummy plug connected to it with a jumper between pins 23 and 24 that provides the interlock needed to operate the transmitter. If remote connections are made to the transmitter, they should be made through the plug in J10 or J11 in the positions noted on the interconnect drawing (1127833).

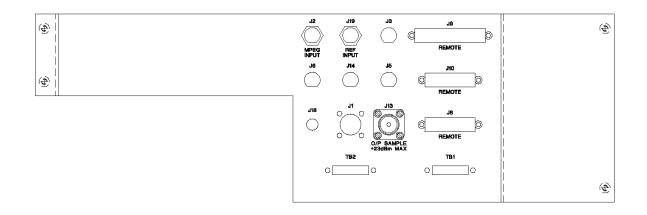

Figure 2-1. Remote Interface Panel

The remote connections shown in Tables 2-14 and 2-15 are made if (A12) the input and remote interface assembly is present in the system. The remote

connections are made to jacks J9 and J10 on the assembly. Refer to the interconnect drawing (1127833) for the proper pin remote connections.

| FUNCTION                                | REMOTE JACK/PIN<br>NUMBER       | INTERFACE TYPE                                                        |

|-----------------------------------------|---------------------------------|-----------------------------------------------------------------------|

| Transmitter Enable Interlock            | J9-21                           | J9-21 and 22 must be                                                  |

| Transmitter Enable Interlock<br>Rtn     | J9-22                           | jumpered for normal<br>operation; (1176-1038)<br>jumper jack is used. |

|                                         | Remote Control Command          | ls                                                                    |

| Transmitter Standby                     |                                 | Contact closure                                                       |

| (Disable)                               | 39-9                            |                                                                       |

| Transmitter<br>Standby/Operate Rtn      | J9-10                           |                                                                       |

| Transmitter Operate<br>(Enable)         | J9-11                           | Contact closure                                                       |

| Transmitter Manual                      | J9-15                           | Contact closure                                                       |

| Transmitter Auto/Manual<br>Rtn          | J9-16                           |                                                                       |

| Transmitter Auto                        | J9-17                           | Contact closure                                                       |

| Power Level Raise (optional)            | J9-27                           | Contact closure                                                       |

| Pwr Level Raise/Lower Rtn<br>(optional) | J9-28                           |                                                                       |

| Power Level Lower<br>(optional)         | J9-29                           | Contact closure                                                       |

|                                         | <b>Remote Status Indication</b> | S                                                                     |

| Transmitter Operate                     |                                 | 50 mA max current sink                                                |

| (Enable) Ind                            | J9-12                           | So ma max current sink                                                |

| Operate/Standby Ind.<br>Return          | J9-13                           |                                                                       |

| Transmitter Standby (Disable) Ind       | J9-14                           | 50 mA max current sink                                                |

| Transmitter Auto Indicator              | J9-18                           | 50 mA max current sink                                                |

| Auto/Manual Indicator<br>Return         | J9-19                           |                                                                       |

| Transmitter Manual<br>Indicator         | J9-20                           | 50 mA max current sink                                                |

| VSWR Cutback Indicator                  | J9-23                           | 50 mA max current sink                                                |

| VSWR Cutback Indicator<br>Return        | J9-24                           |                                                                       |

| FUNCTION                 | REMOTE JACK/PIN<br>NUMBER | INTERFACE TYPE              |  |  |

|--------------------------|---------------------------|-----------------------------|--|--|

| Remote Metering          |                           |                             |  |  |

|                          |                           |                             |  |  |

| Digital Output Power     | J9-1                      | 1V full scale at $1k\Omega$ |  |  |

| Digital Output Power Rtn | J9-2                      | source resistance           |  |  |

|                          |                           |                             |  |  |

| Reflected Power          | J9-5                      | 1V full scale at $1k\Omega$ |  |  |

| Reflected Power Rtn      | J9-6                      | source resistance           |  |  |

|                          |                           |                             |  |  |

| Exciter Output Power     | J9-7                      | 1V full scale at $1k\Omega$ |  |  |

| Exciter Output Power Rtn | J9-8                      | source resistance           |  |  |

| Table 2-15.UHF Amplifier Tray Remote Connections |

|--------------------------------------------------|

|--------------------------------------------------|

| FUNCTION                                 | REMOTE JACK/PIN<br>NUMBER | INTERFACE TYPE                            |

|------------------------------------------|---------------------------|-------------------------------------------|

| Forward Output Power (A6)<br>UHF Amp     | J10-1                     | 1V full scale at 1kΩ<br>source resistance |

| Forward Output Power (A6)<br>Rtn         | J10-2                     |                                           |

| Reflected O/P Power (A6)<br>UHF Amp      | J10-3                     | 1V full scale at 1kΩ<br>source resistance |

| Reflected O/P Power (A6)<br>Rtn          | J10-4                     |                                           |

| Forward Output Power (A7)<br>UHF Amp     | J10-6                     | 1V full scale at 1kΩ<br>source resistance |

| Forward Output Power (A7)<br>Rtn         | J10-7                     |                                           |

| Forward O/P Power (A8)<br>UHF Amp        | J10-10                    | 1V full scale at 1kΩ<br>source resistance |

| Forward Output Power (A8)<br>UHF Amp Rtn | J10-11                    |                                           |

| Reflected O/P Power (A8)<br>UHF Amp      | J10-12                    | 1V full scale at 1kΩ<br>source resistance |

| Reflected O/P Power (A8)<br>Rtn          | J10-13                    |                                           |

| Forward O/P Power (A9)<br>UHF Amp        | J10-14                    | 1V full scale at 1kΩ<br>source resistance |

| Forward Output Power (A9)<br>UHF Amp Rtn | J10-15                    |                                           |

| Reflected O/P Power (A9)<br>UHF Amp      | J10-16                    | 1V full scale at 1kΩ<br>source resistance |

| Reflected O/P Power (A9)<br>Rtn          | J10-17                    |                                           |

# Chapter 3 Installation and Setup Procedures

There are special considerations that need to be taken into account before the DT830A can be installed. For example, if the installation is completed during cool weather, a heat-related problem may not surface for many months, suddenly appearing during the heat of summer. This section provides planning information for the installation and set up of the transmitter.

# 3.1 Site Considerations

The transmitter requires an AC input line of 220 VAC with a rating of 40 amps and 80 amps for the upgradeable version Make sure that the proposed site for the transmitter has the voltage requirements that are needed.

The DT830A is designed and built to provide long life with a minimum of maintenance. The environment in which it is placed is important and certain precautions must be taken. The three greatest dangers to the transmitter are heat, dirt, and moisture. Heat is usually the greatest problem, followed by dirt, and then moisture. Over-temperature can cause heat-related problems such as thermal runaway and component failure. Each amplifier trav in the transmitter contains a thermal interlock protection circuit that will shut down that tray until the temperature drops to an acceptable level.

A suitable environment for the transmitter can enhance the overall performance and reliability of the transmitter and maximize revenues by minimizing down time. A properly designed facility will have an adequate supply of cool, clean air, free of airborne particulates of any kind, and without excessive humidity. An ideal environment will require temperature in the range of 40° F to 70° F throughout the year, reasonably low humidity, and a dust-free room. This is rarely attainable in the real world. However, the closer the environment is to this design, the greater the operating capacity of the transmitter.

The fans and blowers designed and built into the transmitter will remove the heat from within the trays, but additional means are required for removing this heat from the building. To achieve this, a few considerations should be taken into account. The first step is to determine the amount of heat to be removed. There are generally three sources of heat that must be considered. The first and most obvious is the heat from the 300-watt transmitter itself.

The second source of heat is other equipment in the same room. This number is calculated in the same way as the equation for BTUs. The third source of heat is equally obvious but not as simple to calculate. This is the heat coming through the walls, roof, and windows on a hot summer day. Unless the underside is exposed, the floor is usually not a problem. Determining this number is usually best left up to a qualified HVAC technician. There are far too many variables to even estimate this number without detailed drawings of the site showing all construction details. The sum of these three sources is the total amount of heat that must be removed. There may be other sources of heat, such as personnel, and all should be taken into account.

Now that the amount of heat that must be removed is known, the next step is to determine how to accomplish this. The options are air conditioning, ventilation, or a combination of the two. Air conditioning is always the preferred method and is the only way to create anything close to an ideal environment. Ventilation will work quite well if the ambient air temperature is below 100° F, or about 38° C, and the humidity is be kept at a reasonable level. In addition, the air stream must be adequately filtered to ensure that no airborne particulate of any kind will be carried into the transmitter. The combination of air conditioning for summer and ventilation during the cooler months is acceptable when the proper cooling cannot be obtained through the use of ventilation alone and using air conditioning throughout the year is not feasible.

Caution: The operation of air conditioning and ventilation simultaneously is not recommended. This can cause condensation in transmitters. For tube type transmitters, this can be especially serious if the condensation forms in the tube cavity and creates damaging arcs.

The following precautions should be observed regarding air conditioning systems:

- Air conditioners have an ARI nominal cooling capacity rating. In selecting an air conditioner, do not assume that this number can be equated to the requirements of the site. Make certain that the contractor uses the actual conditions that are to be maintained at the site in determining the size of the air conditioning unit. With the desired conditioned room temperature under 80° F, the unit must be derated, possibly by a substantial amount.

- Do not have the air conditioner blowing directly onto the transmitter. Condensation may occur on, or worse in, the transmitter under certain conditions.

- Do not isolate the front of the transmitter from the back with the thought of air conditioning only the

front of the unit. Cooling air is drawn in at the front of all transmitters and in the front and back of others. Any attempt to isolate the front from the rear will adversely affect the cooling air flow.

- 4. Interlocking the transmitter with the air conditioner is recommended to keep the transmitter from operating without the necessary cooling.

- 5. The periodic cleaning of all filters is a must.

When using ventilation alone, the following general statements apply:

- 1. The blower, with attendant filters, should be on the inlet, thereby pressurizing the room and preventing the ingress of dirt.

- The inlet and outlet vents should be on the same side of the building, preferably the leeward side. As a result, the pressure differential created by wind will be minimized. Only the outlet vent may be released through the roof.

- 3. The inlet and outlet vents should be screened with 1/8" hardware cloth (preferred) or galvanized hardware cloth (acceptable).

- 4. Cooling air should enter the room as low as practical but in no case higher than four feet above the floor. The inlet must be located where dirt, leaves, snow, etc., will not be carried in with the cooling air.

- 5. The exhaust should be located as high as possible. Some ducting is usually required to insure the complete flushing of heated air with no stagnant areas.

- 6. The filter area must be adequate to insure a maximum air velocity of 300 feet per minute through the

filter. This is not a conservative number but a never-exceed number. In a dusty or remote location, this number should be reduced to 150 CFM.

- The inlet and outlet(s) must have automatic dampers that close any time the ventilation blower is off.

- 8. In those cases in which transmitters are regularly off for a portion of each day, a temperature-differential sensor that controls a small heater must be installed. This sensor will monitor inside and outside temperatures simultaneously. If the inside temperature falls to within 5° F of the outside temperature, the heater will come on. This will prevent condensation when the ventilation blower comes on and applies even in the summer.

- 9. A controlled-air bypass system must be installed to prevent the temperature in the room from falling below 40° F during transmitter operation.

- 10. The blower should have two speeds, which are thermostatically controlled, and interlocked with the transmitter.

- 11. The blower on high speed must be capable of moving the required volume of air into a half inch of water pressure at the required elevation. The free air delivery method must not be used.

- 12. Regular maintenance of the filters, if used, can not be overemphasized.

- 13. Tube transmitters should not rely on the internal blower to exhaust cooling air at elevations above 4000 feet. For external venting, the air vent on the cabinet top must be increased to an 8" diameter for a 1-kW transmitter and to 10" for 5-kW and 10-kW transmitters. An equivalent rectangular duct may be used but, in all cases, the outlet must be increased in area by 50% through the outlet screen.

- 14. It is recommended that a site plan be submitted to Axcera for comments before installation commences.

In calculating the blower requirements, filter size, and exhaust size, if the total load is known in watts, 2000 CFM into 1/2" of water will be required for each 5000 watts. If the load is known in BTUs, 2000 CFM into 1/2" of water will be required for each 17,000 BTUs. The inlet filter must be a minimum of seven square feet, larger for dusty and remote locations, for each 5000 watts or 17,000 BTUs. The exhaust must be at least four square feet at the exhaust screen for each 5000 watts or 17,000 BTUs.

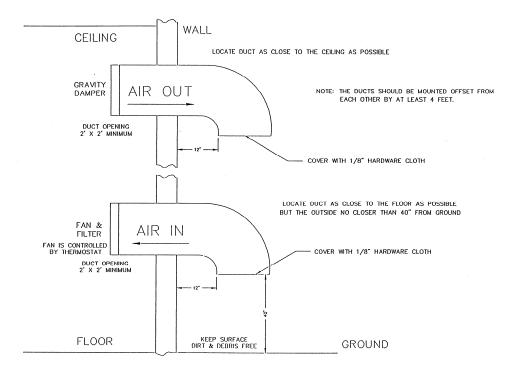

The information presented in this section is intended to serve only as a general guide and may need to be modified for unusually severe conditions. A combination of air conditioning and ventilation should not be difficult to design (see Figure 3-1). System interlocking and thermostat settings should be reviewed with Axcera. As with any equipment installation, it is always good practice to consult the manufacturer when questions arise. Axcera can be contacted at (724) 873-8100.

Figure 3-1. 1 kW Minimum Ventilation Configuration

### 3.2 Unpacking the Cabinets

#### Note: Air conditioning and any related heat exhaust ducts should be in place before continuing with the installation of the transmitter.

Thoroughly inspect the cabinet and all other materials upon their arrival. Axcera certifies that upon leaving our facility the equipment was undamaged and in proper working order. The shipping containers should be inspected for obvious damage that is indicative of rough handling. Check for dents and scratches or broken switches, meters, or connectors. Any claims against in-transit damage should be directed to the carrier. Inform Axcera as to the extent of any damage as soon as possible.

Remove the cabinet with trays, UHF tee assembly, bandpass filter, digital modulator, (optional) trap filter, directional coupler, and the installation material from the crates and boxes. Remove the straps that hold the cabinet to the shipping skid and slide the cabinet from the skid. Remove the plastic wrap and foam protection from around the cabinet. Do not remove any labeling or tags from any cables or connectors; these are identification markers that make assembly of the transmitter much easier.

Remove the four L-brackets, mounted on the front panel rails, which held the trays in place during shipment. The trays are mounted in the cabinet using Chassis Trak cabinet slides. The trav slides are on the top and bottom of the UHF amplifier trays and on the sides of the UHF exciter and digital modulator trays. Inspect the trays for any loose hardware or connectors, tightening where needed. Open the rear door and inspect the interior for packing material, carefully removing any that is found. Slowly slide each tray in and out to verify that they do not rub against each other and have no restrictions to free movement.

Caution: Each UHF amplifier tray has a hardline coaxial cable connected to the bottom panel. The tray will not slide out unless this cable is first removed. To pull the tray out for test purposes, use the extender coaxial cable included in the installation material kit for connections from the tray to the output cable.

Adjustments to the position of the trays may be necessary. To accomplish this, loosen the cabinet slide mounting bolts that hold the front of the slide to the mounting frame of the cabinet and move the tray up or down as needed to correct for the rubbing.

The air intake to the transmitter is intended for room air only. The cabinet should be positioned with consideration given to adequate air intake and exhaust, the opening of the rear door, access to the trays (including sliding them out for testing), the main AC hookup, and the installation of the output transmission line. The cabinet should be grounded using copper strapping material and should also be permanently mounted to the floor of the site using the holes in the bottom of the cabinet.

# 3.3 Installation of the Cabinets and Trays

Once the cabinet is in place and the trays are checked for damage, the main AC hookup is ready to be made.

#### Caution: Before connecting the 230 VAC, make certain that all of the circuit breakers associated with the transmitter are switched off.

The main AC input circuit to the transmitter should be a 40-amp, 80-amp for upgradeable version, 230-VAC line, using AWG 8 wire inside of a 1-1/4" conduit. The 230-VAC input connections (terminals 1 and 2 [230 VAC] and terminal 3 [chassis ground]) are made to terminal block TB1, which is part of (A2)

the AC distribution panel near the rear door of the transmitter. Line 2 is the neutral for international systems using 220 VAC hot and neutral.

The RF output at J2 of (A11) the coupler assembly, which is 7/8" rigid coax, should connect to the transmission line that is connected to the antenna system.

The MPEG digital source input connects to J3, ECL, or TTL, depending on the configuration, at the rear panel of (A19) the modulator or J2 on (A12) the remote interface panel. Remote functions connect to the rear of (A4) the UHF exciter or to (A12) the input and remote interface panel mounted on the rear top of the transmitter. A plug is connected to jack J11 with pins 23 and 24 jumpered together on the UHF exciter or to jack J9 with pins 21 and 22 jumpered together on the (optional) remote interface panel. These are 37-pin, "D"-connectors that provide the interlock for the transmitter. Jacks J10 and J11 on the UHF exciter, and jacks J9 and J10 on the (optional) remote interface panel, are used to connect the remote control functions to the transmitter.

This completes the unpacking and installation procedures for the DT830A Digital UHF Transmitter. Refer to the setup and operation procedures that follow before applying power to the transmitter.

# 3.4 Setup and Operation Procedures

The transmitter should initially be turned on with the RF output of the bandpass filter/coupler assembly terminated into a dummy load of at least 500 watts. If a load is not available, check that the output of the coupler assembly is connected to the antenna.

Switch on the main AC, UHF exciter, digital modulator, and the amplifier #1 and #2, amplifier #3 and #4 are used after upgrade, circuit breakers located on the AC distribution panel facing the rear of the cabinet and mounted behind the rear door. On the UHF exciter tray, switch the Operate/Standby switch to Standby.

Move the Operate/Standby switch, located on the UHF exciter tray, to Operate. Observe the power supply reading, +26.5 VDC, on the front panel of the UHF amplifier trays.

Note: If the transmitter does not switch to Operate when the Operate/Standby switch is switched to Operate, check that an external interlock plug, with a jumper wired from pins 23 to 24, is connected to jack J11 on the rear of the UHF exciter. Or, if (A17) the optional input and remote interface assembly is present in the system, the external interlock plug, with a jumper wired from pins 21 to 22, should be connected to jack J9 on the assembly.

Observe the front panel meter reading in the % Output Power position on the UHF exciter tray; after allowing several minutes of warm-up time, it should read 100%. If necessary, readjust the screwdriver adjust power pot on the front panel of the UHF exciter for 100%. As you are checking the power level, check the meter reading in the % Reflected Power position. If the % Reflected Power is very high (above 10%), a problem with the output coaxial lines is present and needs to be checked. A center bullet missing from the 7/8" rigid coax lines or loose bolts on the connections can cause this problem. Return the Operate/ Standby switch to Standby.

The gain and phase controls on the front panel of the UHF amplifier tray were adjusted at the factory to attain 100% output of the transmitter and should not need to be readjusted. Refer to the Test Data Sheet for the transmitter to compare the final reading from the factory with the reading on the tray after the setup. They should be very similar. If a reading is off by a significant amount, refer to the phasing and power adjustment procedures for the UHF amplifier tray in Chapter 5, Detailed Alignment Procedures, of this manual before trying to make any adjustments.

If a dummy load is connected to the transmitter, switch the transmitter to Standby and switch off the main AC circuit breaker. Remove the dummy load and make all of the connections needed to connect the transmitter to the antenna. Switch the main AC circuit breaker on and the Operate/Standby switch to operate. Adjust the output power screwdriver pot to attain 100% output.

If the transmitter is already connected to the antenna, check that the output is 100%. If necessary, adjust the power screwdriver pot.

If a problem occurred during the setup and operation procedures, refer to Chapter 5, Detailed Alignment Procedures, of this manual for more information.

This completes the setup and operation procedures for the DT830A transmitter. The transmitter can now be operated normally.

# Chapter 4 Circuit Descriptions

#### 4.1 (A4) UHF Exciter Tray (1294-1111; Appendix C)

#### 4.1.1 (A12 and A18) UHF Filter (1007-1101; Appendix D)

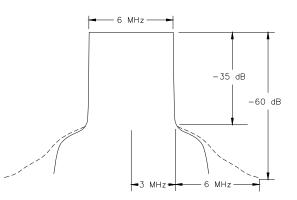

The UHF filter is a tunable two-section cavity filter that is typically tuned for a bandwidth of 5 MHz and has a loss of -1 dB through the filter.

# 4.1.2 (A15-A1) UHF Generator Board (1565-1109; Appendix D)

The UHF generator board is mounted in the UHF Generator Enclosure (1519-1144) for EMI and RFI protection. The board contains a VCXO circuit and additional circuitry to multiply the VCXO frequency by eight. The VCXO produces an output of  $\approx$  67 MHz to 132 MHz, depending on the desired channel frequency. Course adjustment to the frequency is made by C11, while fine adjustments are accomplished by the AFC voltage from (A11) the PLL board (1286-1104). The VCXO frequency level is adjusted by C6, L2, and L4. The output is split and provides an input to the x8 multiplier circuitry as well as a sample for the PLL board.

The x8 circuitry consists of three identical x2 broadband frequency doublers. The input signal at the fundamental frequency is fed through a 6-dB pad consisting of R21, R24, and R25 to amplifier U3. The output of the amplifier stage is directed through a bandpass filter consisting of L8 and C32, which is tuned to the fundamental frequency (67 MHz to 132 MHz). The voltage measured at TP1 is typically +.6 VDC. The first doubler stage consists of Z1 with bandpass filter L9 and C34 tuned to the second harmonic (134 MHz to 264 MHz). The harmonic is amplified by U4 and again bandpass filtered at the second harmonic by C38 and L11 (134 MHz to 264 MHz). The

voltage measured at TP2 is typically +1.2 VDC. The next doubler stage consists of Z2 with bandpass filter C40 and L12 tuned to the fourth harmonic of the fundamental frequency (268 MHz to 528 MHz). The fourth harmonic is then amplified by U5 and fed through another bandpass filter tuned to the fourth harmonic consisting of L14 and C44 (268 MHz to 528 MHz). The voltage measured at TP3 is typically +2.0 VDC. The final doubler stage consists of Z3 with bandpass filter C46 and L15 tuned to the eighth harmonic of the fundamental frequency (536 MHz to 1056 MHz). The signal is amplified by U6 and U7 to a typical value of from +2 to +4 VDC as measured at TP4. The amplified eighth harmonic is then fed to the SMA output jack of the board at J3.

Typical output level of the signal is +16 dBm nominal.

The +12 VDC for the board enters through jack J4-3 and is filtered by L22 and C54-C58 before being distributed to the circuits on the board.

#### 4.1.3 (A14-A1) 10-MHz Reference Generator Board (1519-1126; Appendix D)

The 10-MHz reference generator board is located in (A10) the 10-MHz reference kit (1286-1108). The board contains a highstability crystal oscillator that provides a 10-MHz output that is used as reference frequency for the transmitter. The board is mounted within an enclosed assembly that helps to maintain the operating temperature of the oscillator board.

The oscillator operates at 10 MHz. Transistor Q1 is the oscillating transistor with the frequency of oscillation set by the crystal Y1. L2, C2, and C3 have second-order effects on the frequency, with C2 and C3 used to pull the oscillator exactly on frequency. Capacitors C4 and C5 provide the positive feedback necessary for oscillation.

The output of the oscillator is buffered by Q2 and Q3. L4 and C12 form a 40-MHz bandpass filter. The 40-MHz signal passes through a digital divider IC U4, which divides the signal down to 10 MHz. Transistor Q5 provides a buffered, 10-MHz output at jack J1.

The crystal is heated in an enclosed crystal oven (HR-1) that is internally set at 60° C. The oscillator board is heated by a separate oven that is set at 50° C. U1 is a temperature sensor/controller IC that monitors the temperature of the oscillator assembly and controls the operation of Q4 and U2. The operating temperature of the assembly is set by adjusting R15. If the temperature of the assembly falls below 50° C, U1 will bias O4 on, which in turn increases the amount of current flow through U2. The flange of U2 is thermally connected to the heatsink of the assembly. The temperature of the heatsink will increase as the current through U2 increases. As a result, U2 will dissipate more power in the form of heat, and the temperature of the assembly will increase. If the assembly temperature rises above 50° C, the opposite action will occur, thus lowering the temperature of the assembly.

The +12 VDC enters the board at J2 and is filtered by L1 and C1 before it is applied to the remaining circuits on the board.

### 4.1.4 (A13) PLL Board (1286-1104; Appendix D)