# **NFC Module**

XYZ-NFC-001 Data Sheet

## **Features**

I2C interface.

I<sub>2</sub>C-bus interface up to 400 kBd in Fast mode, up to 3400 kBd in High-speed mode

FIFO buffer handles 64 byte send and receive

Flexible interrupt modes

Hard reset with low power function

Power-down mode per software

Programmable timer

Internal oscillator for connection to 27.12 MHz quartz crystal

2.5 V to 5.5 V power supply

CRC coprocessor

Programmable I/O pins

Internal self-test

## Pin description

| Pin | Symbol  | Туре | Description              |

|-----|---------|------|--------------------------|

| 1   | VCC_IN  | PWR  | Digital Power Supply     |

| 2   | GND     | PWR  | Digital Ground           |

| 3   | NRSTPD  | 1    | Not Reset and Power Down |

| 4   | IRQ     | 0    | Interrupt Request        |

| 5   | I2C_SDA | 1/0  | I2C data                 |

| 6   | I2C_SCL | I    | I2C address              |

## **Electrical Characteristics**

| Symbol | Parameter              | Min | Тур | Max | Unit |

|--------|------------------------|-----|-----|-----|------|

| VDD    | digital supply voltage | 2.5 |     | 5.5 | V    |

| IDD    | digital supply current |     |     | 400 | mA   |

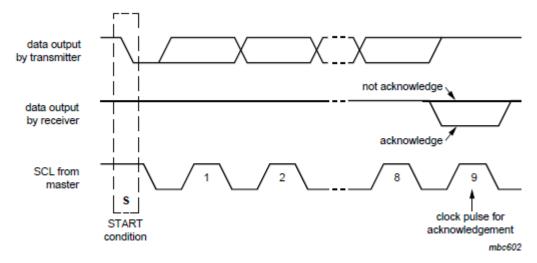

## **Acknowledge**

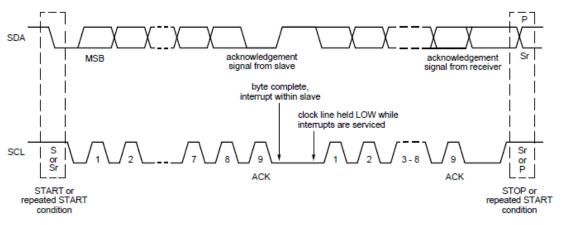

An acknowledge must be sent at the end of one data byte. The acknowledge-related clock pulse is generated by the master. The transmitter of data, either master or slave, releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver pulls down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse.

The master can then generate either a STOP (P) condition to stop the transfer or a repeated START (Sr) condition to start a new transfer.

A master-receiver indicates the end of data to the slave-transmitter by not generating an acknowledge on the last byte that was clocked out by the slave. The slave-transmitter releases the data line to allow the master to generate a STOP (P) or repeated START (Sr) condition.

## Acknowledge on the I2C-bus

Data transfer on the I2C-bus

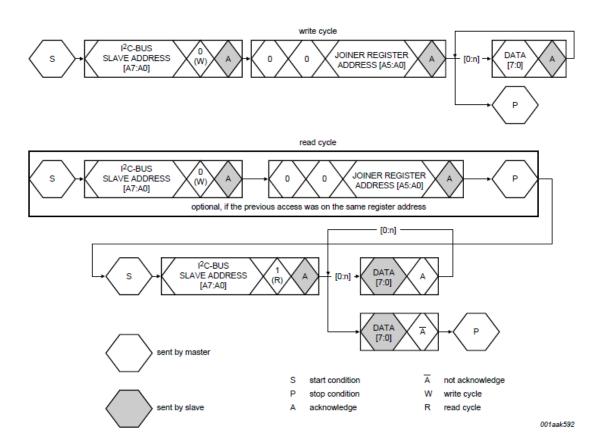

## Register read access

To read out data from a specific register address in the Module, the host controller must use the following procedure:

• Firstly, a write access to the specific register address must be performed as indicated

in the frame that follows

- The first byte of a frame indicates the device address according to the I2C-bus rules

- The second byte indicates the register address. No data bytes are added

- The Read/Write bit is 0

After the write access, read access can start. The host sends the device address of the PN512. In response, the Module sends the content of the read access register. In one frame all data bytes can be read from the same register address. This enables fast FIFO buffer access or register polling.

The Read/Write (R/W) bit is set to logic 1.

Register read and write access

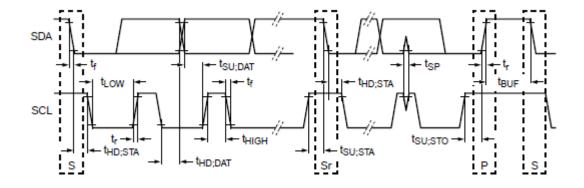

## **I2C-bus timing**

| Symbol              | Parameter                                     | Conditions                                                  | Fast mode |     | High-speed<br>mode |      | Unit |

|---------------------|-----------------------------------------------|-------------------------------------------------------------|-----------|-----|--------------------|------|------|

|                     |                                               |                                                             | Min       | Max | Min                | Max  | 1    |

| f <sub>SCL</sub>    | SCL clock frequency                           |                                                             | 0         | 400 | 0                  | 3400 | kHz  |

| t <sub>HD;STA</sub> | hold time (repeated) START condition          | after this period,<br>the first clock pulse<br>is generated | 600       | -   | 160                | -    | ns   |

| t <sub>su;sta</sub> | set-up time for a repeated<br>START condition |                                                             | 600       | -   | 160                | -    | ns   |

| t <sub>su;sто</sub> | set-up time for STOP condition                |                                                             | 600       | -   | 160                | -    | ns   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                   |                                                             | 1300      | -   | 160                | -    | ns   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                  |                                                             | 600       | -   | 60                 | -    | ns   |

| t <sub>HD;DAT</sub> | data hold time                                |                                                             | 0         | 900 | 0                  | 70   | ns   |

|                     |                                               |                                                             |           |     |                    |      |      |

| t <sub>SU;DAT</sub> | data set-up time                              |                                                             | 100       | -   | 10                 | -    | ns   |

| t <sub>SU;DAT</sub> | data set-up time                                 |                     | 100 | -   | 10  | -  | ns |

|---------------------|--------------------------------------------------|---------------------|-----|-----|-----|----|----|

| t <sub>r</sub>      | rise time                                        | SCL signal          | 20  | 300 | 10  | 40 | ns |

| t <sub>f</sub>      | fall time                                        | SCL signal          | 20  | 300 | 10  | 40 | ns |

| t <sub>r</sub>      | rise time                                        | SDA and SCL signals | 20  | 300 | 10  | 80 | ns |

| t <sub>f</sub>      | fall time                                        | SDA and SCL signals | 20  | 300 | 10  | 80 | ns |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition |                     | 1.3 | -   | 1.3 | -  | μS |

## **Federal Communication Commission Interference Statement**

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

#### **FCC Caution:**

Any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference, and

- (2) This device must accept any interference received, including interference that may cause undesired operation.

#### **FCC Radiation Exposure Statement:**

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter.

#### **IMPORTANT NOTE:**

In the event that these conditions can not be met (for example certain laptop configurations or co-location with another transmitter), then the FCC authorization is no longer considered valid and the FCC ID can not be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

## **End Product Labeling:**

The final end product must be labeled in a visible area with the following:

[Contains FCC ID: 2AB9W-NFC001]

#### Manual Information to the End User

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module.