# **Quality Handbook**

Corporate, Quality Systems and Customer Interface Systems Overview

www.microchip.com

## CONTENTS

| Introduction                                                                                                                                                    | 3                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Core Business Culture                                                                                                                                           | 3                                 |

| <b>Company Vision, Mission and</b><br><b>Guiding Values</b><br>Vision                                                                                           | <b>4</b><br>4                     |

| Mission                                                                                                                                                         | 4                                 |

| Guiding Values                                                                                                                                                  | 4                                 |

| Culture and Policy Towards Quality                                                                                                                              | 5                                 |

| Microchip's Quality Policy                                                                                                                                      | 5                                 |

| Quality Certifications                                                                                                                                          | 5                                 |

| Quality Management System (QMS)<br>Quality Documentation<br>Document Management System                                                                          | <b>6</b><br>7<br>7                |

| Process/Product Realization<br>New Technology Development<br>New Product Development                                                                            | <b>8</b><br>8<br>8                |

| Manufacturing Quality<br>Statistical Techniques and<br>Defect Prevention                                                                                        | <b>11</b><br>12                   |

| Product Traceability                                                                                                                                            | 13                                |

| Qualification System<br>Die Qualification Methods<br>Package Qualification Methods<br>Ongoing Reliability<br>Reliability Monitoring Methods<br>Reliability Data | <b>14</b><br>15<br>16<br>17<br>17 |

| Total Endurance™ Software                                                                                                                                       | 18                                |

| Monitoring and Measurement             | 19 |

|----------------------------------------|----|

| Establishing Quality Goals/            |    |

| Key Process Indicators (KPIs)          | 19 |

| Internal Quality System Audits         | 20 |

| Corrective and Preventive Action       |    |

| System (CA/PA System)                  | 20 |

| Other Improvement Tools and Techniques | 21 |

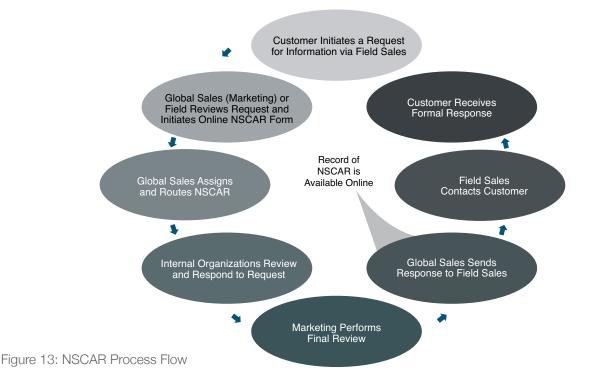

| Customer Support                       | 22 |

| Customer Interface System              | 22 |

| Order Entry and Delivery               | 22 |

| Return Material (RMA)                  | 22 |

| Failure Analysis                       | 23 |

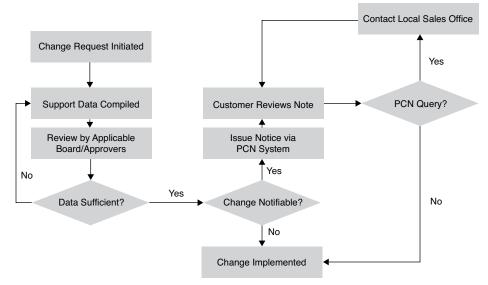

| Change Management and                  |    |

| Customer Communication                 | 24 |

| Contract and Specification Review      | 25 |

| Customer Satisfaction Survey           | 26 |

| Development System Returns             | 26 |

| Worldwide Website                      | 26 |

| Technical Assistance                   | 26 |

Microchip Technology Inc. is a leading provider of microcontroller, analog and Flash-IP solutions, providing low-risk product development, lower total system cost and faster time-to-market for thousands of diverse customer applications worldwide. Headquartered in Chandler, Arizona, Microchip offers outstanding technical support along with dependable delivery and quality.

The purpose of this handbook is to provide you with an overview of Microchip's core business culture, Quality Management System (QMS) and customer interface systems that are designed and deployed to ensure excellence in product quality, customer service and overall customer satisfaction.

## CORE BUSINESS CULTURE

At the center of Microchip's core business culture are our Mission, Guiding Values and Aggregate System Model. These corporate principles provide our employees with constancy of purpose while allowing them the flexibility to be creative and innovative to meet customer needs. Our Aggregate System Model defines the interrelationship of all our business systems and resources to achieve our mission and strategic goals. This model is designed so that our company culture, systems, practices, policies and employees work in unison to achieve Microchip's performance potential.

# COMPANY VISION, MISSION AND GUIDING VALUES

Our Vision and Mission Statement define our business and our direction for success. Our Guiding Values provide the core principles that define our culture and the way we do business. They establish the framework for all decision making regarding the quality of our products or services, or the way we treat our customers, suppliers and employees, or the way we determine our business strategies.

#### Vision

Be the very best embedded control solution company ever.

#### Mission

Microchip Technology Incorporated is a leading supplier of field-programmable embedded control solutions by delivering the popular PIC<sup>®</sup> microcontrollers; a broad spectrum of innovative analog products, related non-volatile memory products and Flash-IP solutions. In order to contribute to the ongoing success of customers, shareholders and employees, our mission is to focus resources on high value, high quality products and to continuously improve all aspects of our business, providing an industry leading return on investment.

## **Guiding Values**

**Quality Comes First:** We are on a relentless quest for perfection and are committed to the goal of zero defects. We will perform correctly the first time and maintain ISO/TS 16949 quality system certification to ensure customer satisfaction. We employ the aggregate system so that all employees anticipate problems and implement root cause solutions using effective and standardized improvement methods. We believe that quality is built-in and not inspected out and that when quality comes first, reduced costs follow.

**Customers Are Our Focus:** We establish successful customer partnerships by exceeding customer expectations for products, services and attitude. We start by listening to our customers, earning our credibility by producing quality products, delivering comprehensive services and meeting commitments. We believe each employee must effectively serve their internal customers in order for Microchip's external customers to be properly served.

**Continuous Improvement is Essential:** We utilize the concept of "Vital Few" to establish our priorities. We concentrate our resources on continuously improving Vital Few while empowering each employee to make continuous improvements in their area of responsibility. We strive for constructive and honest self-criticism to identify improvement opportunities.

**Employees Are Our Greatest Strength:** We design jobs and provide opportunities promoting employee teamwork, productivity, creativity, pride in work, trust, integrity, fairness, involvement, development and empowerment. We base recognition, advancement and compensation on an employee's achievement of excellence in team and individual performance. We provide for employee health and welfare by offering competitive and comprehensive employee benefits.

**Products And Technology Are Our Foundation:** We make ongoing investments and advancements in the design and development of our manufacturing process, device, circuit, system and software technologies to provide timely, innovative, reliable and cost effective products that give our customers the freedom to innovate for today and tomorrow.

**Total Cycle Times Are Optimized:** We focus resources to optimize cycle times to our internal and external customers by empowering employees to achieve efficient cycle times in their area of responsibility. We believe that cycle time reduction is achieved by streamlining processes through the systematic removal of barriers to productivity.

**Safety Is Never Compromised:** We place our concern for safety of our employees and community at the forefront of our decisions, policies and actions. We are all individually and collectively responsible for safety.

**Profits and Growth Provide for Everything We Do:** We strive to generate and maintain industry leading rates of company profits and growth, as they allow continued investment in the future, enhanced employee opportunity, and represent the overall success of Microchip.

**Communication Is Vital:** We encourage appropriate, honest, constructive and timely communication in company, customer, investor, government and community relationships to resolve issues, exchange information and share knowledge.

Suppliers, Representatives and Distributors Are Our Partners: We strive to maintain professional and mutually beneficial partnerships with those suppliers, representatives, distributors, design houses and consultants who are an integral link in the achievement of our mission and guiding values.

**Professional Ethics Are Practiced:** We manage our business and treat customers, employees, shareholders, investors, suppliers, channel partners, community and government in a manner that exemplifies our honesty, ethics and integrity. We recognize our short and long term fiscal, social and environmental responsibilities and are proud to serve as an equal opportunity employer.

# CULTURE AND POLICY TOWARDS QUALITY

At Microchip, every organization, business unit and individual owns the quality of their output, which encompasses products, software, processes and services. Our progressive culture is due to a consciously designed working environment in which all organizations understand and embrace the company's Quality Policy and practice a common set of values to achieve the company's quality goals. The relatively flat organizational structure provides a flexible framework within which multiple disciplines can work together and provide customers with high-quality results that are consistent with their technical and business needs.

## MICROCHIP'S QUALITY POLICY

In order to meet or exceed customer expectations at a reduced cost, we encourage our employees to support continuous improvement, anticipate problems and implement root cause solutions.

# QUALITY CERTIFICATIONS

Microchip Technology Inc. is an ISO/TS 16949 certified company. A set of common certifications for Microchip's corporate and other facilities around the world is available for viewing online at <a href="https://www.microchip.com/quality">www.microchip.com/quality</a>. Additional certificates include ISO 14001 and OHSAS 18001.

#### **Corporate Office**

Chandler, AZ, USA

#### Manufacturing

- Fabrication Sites: Tempe (AZ), Gresham (OR)

- Assembly and Test Sites: Thailand

#### **Product Design and Development**

- Chandler (AZ)

- Chennai (India)

- Bucharest (Romania)

- St. Sulpice (Switzerland)

- Hauppauge (NY)

- Austin (TX)

- San Jose (CA)

- Bangalore (India)

- Norristown (PA)

- Karlsruhe (Germany)

- Manilla (Philippines)

# QUALITY MANAGEMENT SYSTEM (QMS)

Microchip's Quality Management System (QMS) serves as the foundation for customer satisfaction and continuous improvement in all aspects of operation. The QMS is based on a customer-supplier partnership and provides a framework for managing the activities used to develop and deliver quality products that consistently satisfy customer and other external requirements. This QMS is deeply rooted in Microchip's culture, corporate mission, company values, business principles, actions and results. Improvement to the QMS is an ongoing process that cascades throughout Microchip's organization.

Microchip's quality system has undergone tremendous expansion over the years due to organizational growth, product diversity, acquisitions and global environmental initiatives. In spite of the many changes, Microchip has continued to maintain and improve upon our core QMS infrastructure, our business practices and our quest towards achieving zero defects. The strength of this strategy lies in an adherence and improvement to a 'value-added' based QMS framework centered on the ISO/TS 16949 standard that is aimed at the development of a quality management system which provides for continual improvement and emphasizes defect prevention.

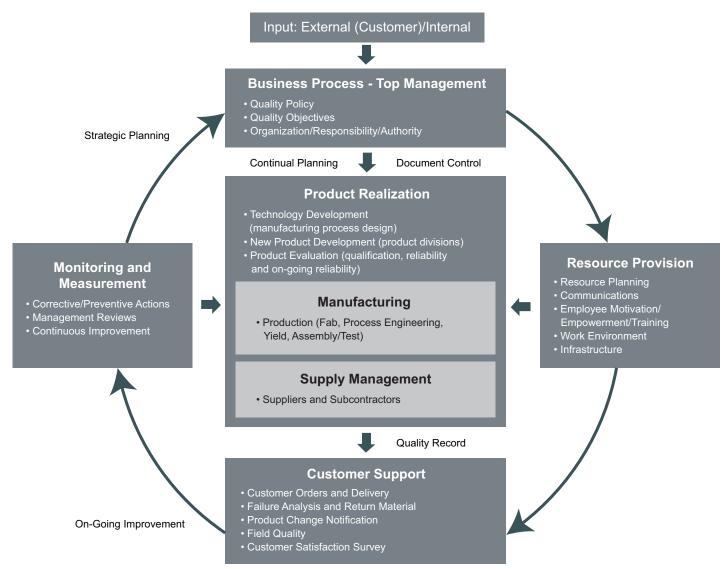

Figure 1 illustrates the key elements within Microchip's QMS. Based on customer feedback, internal needs and findings, Microchip's business processes enable the appropriate individuals to review and make decisions on how to best realize and transform these inputs into actionable activities, business practices, results and deliverables utilizing the processes and systems embedded within the QMS (resource provision, monitoring and measurement and customer support).

Figure 1: Microchip's Quality Managment System

## **Quality Documentation**

Activities affecting quality are defined and formally communicated via documented procedures. These documents include criteria for ensuring all necessary products and process control activities have been completed and that requirements have been satisfied. All documents are reviewed and approved for accuracy and are maintained under revision control.

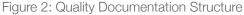

The Quality System documentation structure can be represented by various levels of information, as depicted in Figure 2.

**Quality Policy, Mission, Vision and Values**: Provide fundamental guidance for managing business operations and activities within the organization.

**Quality Manual:** Describes the organization's Quality Management System and serves as the basis for all other quality-related documentation. Quality Management includes all the activities that the organization carries out in an effort to implement the company's quality policy. These activities include quality planning, quality control, quality assurance and quality improvement. **Departmental Operations Guide (DOG):** Describes the fundamental roles and responsibilities of the individual departments within an organization, including process-based inputs, outputs and key performance indicators.

**Process Instruction:** General procedures and/or detailed instructions for quality-related activities.

**Quality Records:** Provide objective evidence which shows how well a quality requirement is being met or how well a quality process is performing. These records serve to document what has happened in the past.

#### **Document Management System**

Microchip utilizes a centralized electronic document management system to help the company streamline documents and enable employees to efficiently share and communicate information across all Microchip locations worldwide. The company's Corporate Document Management Organization is responsible for maintaining the accuracy and integrity of the various levels of documentation (including records) by ensuring that:

- Documents are approved for adequacy prior to issue

- Documents are reviewed and updated per established processes

- · Documents are revision controlled and are available at point of use

- Obsolete documents are prevented from unintended use

- Records are properly stored and remain legible, readily identifiable and retrievable

## PROCESS/PRODUCT REALIZATION

#### **New Technology Development**

The electronics and semiconductor industry is constantly advancing and improving. Microchip is committed to providing customers with a variety of innovative and high-performance solutions to meet their design challenges. Engaging in new technology research and development is a vital element in Microchip's strategy of implementing new processes and products. Microchip's technology development activities focus on introducing new fabrication processes that serve as a platform for designing and manufacturing new and improved products.

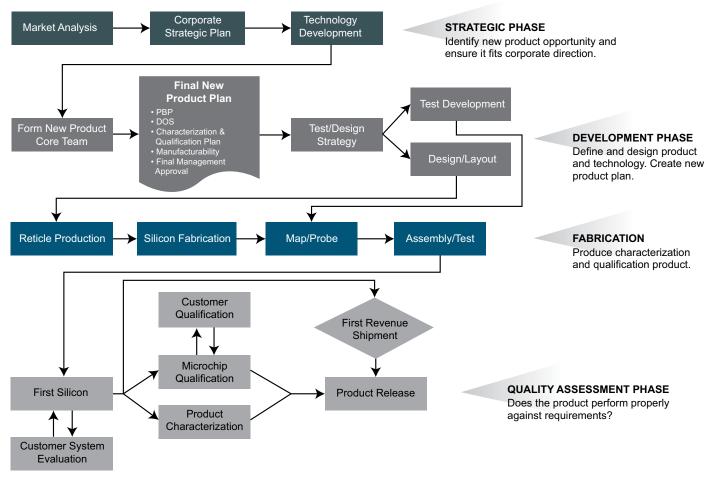

Microchip's new technology development program utilizes a phased approach based on the Advanced Product Quality Planning (APQP) methodology (see Figure 3).

Once a technology is chosen and the program's goals and objectives are defined, a cross-functional development team – consisting of representatives from the design, modeling, process integration, technology development engineering, manufacturing engineering, and quality/reliability organizations — is assembled to launch the project and oversee the program through implementation. Typically, a product driver is identified and used during the development activities. The team seeks inputs and assistance from representatives from manufacturing and other support organizations throughout the various phases of the program. The primary inputs to a technology development project are the Technology Objective Specification (TOS), the Technology Business Plan (TBP) and the Design Objective Specification (DOS) of the product used in validating the technology.

The key components of Phase III are initial process development; engagement with manufacturing to plan for equipment, tooling, and facilities requirements; and the establishment of a process qualification plan with well-defined acceptance criteria. In Phase IV, the design parameters of the process are confirmed using a manufactured version of the product to validate that both process and product requirements are met.

A successful technology development project results in a stable and reproducible process that can be released to the production environment for the development of new products.

#### **New Product Development**

New product development activities are also based on the APQP methodology. Product planning is driven by representatives from the various product divisions, who are responsible for ensuring that product design requirements are met. They also ensure that the necessary controls are in place so that the products and processes achieve the desired functional performance objectives and quality goals. Throughout the product development process, systematic and analytical techniques aimed at proactively identifying and eliminating potential failure modes are applied to prevent the release of a deficient design and to ensure its manufacturability during volume production.

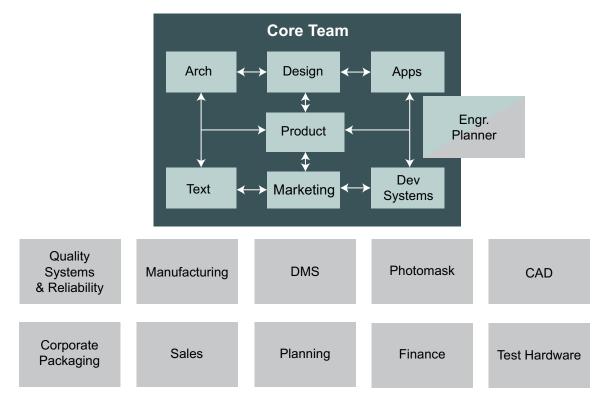

The new product development (NPD) work flow is depicted in Figure 4. New product ideas can originate from customers, market studies, or from internal product design and development teams. Marketing analysis and technical feasibility reviews are performed for those ideas that fit into the Company's strategic direction. Once a decision has been made to proceed with a new product concept, a cross-functional NPD team is formed to define and formalize a detailed product plan and implementation strategy (Figure 5). The team is typically composed of core members, but also utilizes a variety of skill sets and expertise provided through representatives of supporting organizations.

During the product planning phase, the team establishes the project timeline; functional requirements for the product; the resources (staff, procedures, hardware, software, materials, etc.) needed to execute the plan; the verification and validation plans; and the quality criteria necessary for product acceptance and release. Throughout the program, the NPD cross-functional team tracks

the progress of the project via key milestones that have been defined according to the methodology outlined by the APQP product development work flow. A Design Objective Specification (DOS) is created to define and document the specific product requirements and functional performance goals. This document is required as an input to the device design activities and to formulate the production methodology. The new product development process is subdivided into a number of phases. Each phase is comprised of a collection of related process steps that, when completed, comprise a major product development milestone. At each milestone, the NPD team members convene and review the objectives and requirements for that milestone. The team utilizes an online product tracker that contains comprehensive lists (e.g. checklists) of crucial tasks that need to be completed at the end of that milestone. This ensures that important steps are not overlooked and that any identified issues are ultimately resolved before completion of the milestone and/or prior to product release. If all requirements are satisfied and approved by all team members, the team proceeds to work towards fulfilling the requirements and objectives of the next NPD milestone.

Typical milestones and reviews occur at:

- Design Objectives Specification Review: This review is for the NPD team responsible for post-silicon activities and

product release, to understand and assess the design requirements of the product and its feasibility for manufacturability.

- **Pre-Silicon Design Review:** This review occurs during and/or at the end of each device design. The Pre-Silicon Design Review enables other designers and organizations to perform a feasibility review on the DOS requirements from a device design perspective. As the design activities progress, the team verifies the device design to the DOS using simulation and other analytical techniques with the objective of minimizing the possibility of errors and incompatibilities prior to first silicon tape-out.

- Stream-Out Review Fabrication: The product development team revalidates the feasibility of the development project just prior to the tape-out of first silicon. At this point in the development project, the team is expected to have clear plans leading toward a whole product solution. These plans, along with a revalidation of the prior review material, represent the vast majority of this review. Upon team approval of this review, the device reticle is produced to build first silicon necessary for validation activities.

- Release to Production (RTP): The review at RTP allows the team to validate the design and manufacturability, using 'built' silicon, via functional testing, device characterization and through extensive qualification and reliability testing. This aspect of the review focuses on whether or not the team has met the requirements of a production-worthy product. If the validation results meet the acceptance criteria, and if all other requirements of APQP requirements have been completed (e.g. designation of special characteristics; creation/review of Failure Mode Effects Analysis (FMEA); development of control plans to identify critical process steps and their associated control specifications, etc.), the product is released to production. RTP review also gauges how close the team is to having a whole product solution. This aspect of the review focuses on customer deliverables, sales collateral and the ability to service customer demand.

Figure 4: New Product Development

Figure 5: Cross-Functional New Product Development Team

# MANUFACTURING QUALITY

The manufacturing quality portion of this handbook consists of the processes that aid in the transformation of silicon to final product.

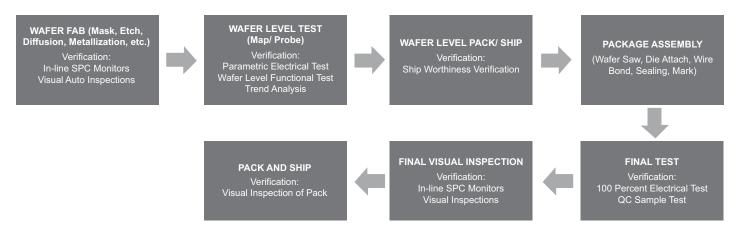

Microchip is a global competitor providing local services to the world's technology centers. Microchip's manufacturing capabilities include wafer fabrication, wafer probing, assembly and final product test as illustrated in Figure 6. Specifications are maintained under revision control for all fabrication, assembly and test operations.

After the product design and process have been successfully validated, the product is formally released to production. The wafer fabrication process consists of several sub-processes, generally performed as follows:

• A layer of oxide is grown on the surface of a silicon wafer. Because the oxide can be removed by etching, it provides a tool for placing

- patterns (mask) onto the wafer and selectively introducing the dopants required by the specific device.

- After oxidation, a photo resist chemical is dispensed on the wafer. The wafer is aligned with the mask and exposed to ultra-violet light to produce a pattern on the wafer. The wafer is 'etched' to leave specific areas of exposed silicon for implantation of dopants to a prescribed concentration and profiles.

- Dopants are further diffused into the wafer by placing the wafers in furnaces where heat is applied.

- A deposition process is used to deposit a thin film of specific material over the wafer for the purpose of isolation, planarization, providing a conductive layer, or adding a protective layer.

- The sub-process cycle is repeated several times, depending on the device under fabrication.

The final fabrication operation involves putting a protective seal over the circuit by depositing a thin coating of material over the entire wafer surface. The completed wafers are sent to Map and Probe for wafer level testing, where failed die are identified. After test, the wafers are packed and sent for package, assembly and test.

During assembly, individual good and bad die are separated. Once the package type has been determined, the die is attached to an appropriate carrier (e.g., lead frame paddle for plastic packages). The device is then processed through wire bond, where thin wires are used to connect the die bonding pads to the package leads. Packages are then sealed with a lid or molding compound and marked with the part number and other product identifiers. The packages are processed through electrical test, quality control sample test and final visual inspection to verify functional and visual/mechanical performance.

Figure 6: General Wafer Fabrication, Assembly and Test Flow

SPC monitors, tests and inspections are utilized throughout the manufacturing process to ensure that process control and product performance requirements have been met and to drive problem resolution and continuous improvement throughout the manufacturing operations.

#### **Qualification and Training of Employees**

Microchip's corporate training philosophy addresses both the technical and human aspects of doing business. As part of the employee development process, managers and supervisors identify the quality-related responsibilities for each employee, define the employee's training needs and ensure that the employee completes all necessary training to perform his or her job.

Microchip's Employee Development organization offers a wide range of courses which focus on enabling employees to develop the necessary skills to perform their jobs well. Programs have been created in support of Microchip's Strategic Vision and Guiding Values, addressing the requirements

of production specialists, engineers, technicians, managers and team leaders, project managers and administrative and support personnel. Courses are offered on technical subjects, manufacturing operations, leadership, project management, problem solving, decision making, statistics, quality improvement, team building and business practices. In addition, employees routinely attend external seminars, universities and distance learning programs to enhance their technical and management expertise.

The Manufacturing Training organizations are responsible for developing employee training plans and for qualifying and certifying personnel for the various processes and tools they operate. In addition, manufacturing personnel are trained in cleanroom protocols, basic SPC and control charting, the Microchip Quality Management System and other subjects that promote problem solving and continuous improvement.

#### **Statistical Techniques and Defect Prevention**

Microchip employs various statistical techniques to characterize, control and reduce variability of production processes. To do this, the Engineering and Manufacturing organizations establish minimum process requirements and apply appropriate statistical analysis techniques including:

- Design analysis and elimination of potential problems and failure mechanisms.

- A reference standard for the process based on process qualification and capability studies.

- Statistical tools to provide real-time process analysis and feedback.

- Statistical tools (e.g., design of experiments, Pareto analysis, trend charts, probability plots, reliability analysis techniques) to identify top problems, assignable cause and direct improvement actions through internal corrective and preventive action systems.

Specific applications of these techniques are:

- Engineering's application of continuous improvement is based on FMEA methodology used during product development, verification and validation and enhancement activities.

- In-line process control using statistical process control (SPC) charts and parametric electrical testing to monitor performance and alert operators of abnormal conditions.

- Off-line analysis of designed experiments (DOE), defect density data, yield and parametric electrical test data.

- The establishment of acceptance limits and monitoring of final test and outgoing quality levels.

- Device reliability predictions based on ongoing reliability monitor results.

Microchip emphasizes that the effective implementation of these statistical techniques is dependent upon the existence and adequate application of all other basic elements of the total quality system.

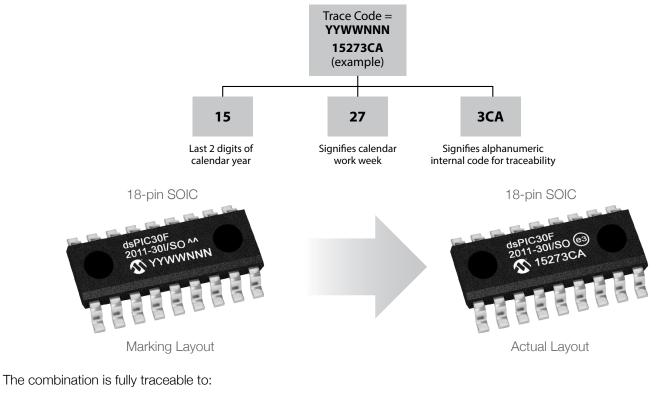

#### **Product Traceability**

Product identification and traceability of material within the manufacturing operation is important to ensure correct lot processing, proper material control and to support problem-solving efforts during all stages of production and delivery. Microchip's traceability system has been designed to provide forward and backward traceability data based on the information contained within the part marking scheme. Product traceability is initiated during the order-entry process and continues through manufacturing and the final shipment of the product to the customer. As part of Microchip's standard part marking scheme, parts or packages are physically marked with a unique 7-digit trace code: – YYWWNNN, where:

- Wafer lot number and location

- Assembly lot number and location

- Test lot number and location

- Final shipment to the customer

- Associated logs and records

Note: Where package size does not allow for the full 7-digit trace code, marking abbreviated formats have been defined to support traceability requirements.

# QUALIFICATION SYSTEM

Microchip's qualification process is directed at ensuring that new products are evaluated, characterized and qualified per specified requirements. The process provides a statistical basis to determine and validate the levels of expected quality and reliability. As inputs to the process come from several functions of the organization, the qualification process is conducted in a cross-functional team environment. The team operates using a fully documented qualification process which sets forth guidelines for standard qualifications, monitoring and sampling procedures. A set of baseline specifications is maintained that states which changes require re-qualification. These process changes can only be made after successful demonstration of reliability performance. This procedure results in a reliable field performance, while enabling the smooth phase-in of improved designs and product capability.

Listed below are the types of qualification tests typically performed to confirm product performance to design objectives (see Table 1 and Table 2). Also provided is a brief description of test purpose and method/conditions. Detailed testing procedures and acceptance criteria are documented in Microchip's Worldwide Quality Conformance Requirements specification.

New New product New assembly process/package/ qualification site qualification assembly/qualification Required tests Develop (Process/Product/ respective Package/Assemblyqualification please see tables below for plan(s) die/package qualifications) Resolve through No Yes Pass Review Failure Analysis all tests? Qualification Data Yes Repeat No Data tests? within specs? Yes No Cancel Qualification Qualification Report **NOTE:** Changes are reviewed/approved through the Change Control Board. Customers are notified through PCN. See "Customer Support" for additional details.

The Die Qualification Flow can be summarized as below:

Figure 7: Die Qualification Flow

## Table 1: Die Qualification Methods

| Die Tests                                            | Industry Standard                                          | Test Purpose                                                                                                                                                                          | Method/Condition                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ELFR (Early Life<br>Failure Rate)                    | MIL-STD-883<br>Method 1005 or<br>AEC-Q100-008              | The test is designed to<br>accelerate random failure<br>modes.                                                                                                                        | 125°C for 48 hours or 150°C for 24 hours at the maximum V <sub>DD</sub> at which the device is guaranteed. Tri-temp test at 1 and 48 hours at 125°C or 0 and 24 hours for the 150°C test. Typical sample size/lot = 800.                                                                                                                                                                                                                    |

| Dynamic Life<br>Test or HTOL                         | MIL-STD-883,<br>Method 1005                                | Test is designed to<br>accelerate random<br>failure modes. Devices<br>are exercised at high<br>temperature to simulate<br>field life.                                                 | 125°C for 1008 hours or 150°C for 408 hours at the maximum Vbb at which the device is guaranteed. Tri-temp test at 0, 48 and 1008 hours at 125°C or 0, 24 and 408 hours for the 150°C test. Typical sample size/lot = 600.                                                                                                                                                                                                                  |

| Retention Bake                                       | MIL-STD-883,<br>Method 1033                                | Used to accelerate<br>charge loss/gain in the<br>memory cells.                                                                                                                        | 150°C for 1008 hours or 504 hours at 175°C. Room and hot temp test at 0, 168 and 1008 hours or 0, 96, 504 hours for the 175°C test. Test only required for devices with non-volatile memory that can be rewritten—EEPROM, Flash, etc. The devices must be preconditioned with endurance. Typical sample size/lot = 231                                                                                                                      |

| Endurance<br>Cycle (EEPROM/<br>Flash)                | MIL-STD-883,<br>Method 1033<br>or AEC-Q100-005             | Continuous write/erase<br>cycles are used to<br>accelerate potential failure<br>modes, which may occur<br>in the memory array and<br>peripheral circuitry during<br>normal operation. | Erase/Write (block/page/byte) cycles per qualification plan, with<br>equivalent maximum cycles that are guaranteed by the data sheet.<br>Typical sample size/lot = 308 (231 for EDR-Bake; 77 for EDR DLT).                                                                                                                                                                                                                                  |

| Endurance +<br>DLT                                   | MIL-STD-883,<br>Method 1033<br>and 1005 or<br>AEC-Q100-008 | Test is for devices with<br>non-volatile memory<br>that can be rewritten<br>(EEPROM, Flash, etc.).                                                                                    | Same requirements as the individual Endurance and DLT tests, with the exception that this DLT, tri-temp testing must be performed at each read point. This test is only required for devices with non-volatile memory that can be rewritten—EEPROM, Flash, etc. Typical sample size/lot = 77.                                                                                                                                               |

| ESD - HBM                                            | QCI-30510<br>(JS-001)                                      | Test is used to determine<br>the sensitivity of the<br>ESD protection circuitry<br>of a component to<br>electrostatic discharge.                                                      | Should meet 2000V. Required 500V, 1000V and 2000V testing.<br>Engineering data can be collected above 2000V (i.e. 4000V).<br>Pre- and post-room and hot temperature testing. Typical sample<br>sizes/lot = # of voltage steps ×3 devices.                                                                                                                                                                                                   |

| ESD – Machine<br>Model                               | QCI-30510<br>(JESD-A115)                                   |                                                                                                                                                                                       | Should meet minimum 200V Required 100V and 200V testing.<br>Engineering data can be collected above 200V (e.g., 300V, 400V).<br>Pre- and post-room and hot temperature testing. Typical sample<br>sizes/lot = # of voltage steps ×3 devices.                                                                                                                                                                                                |

| ESD Induced<br>Latch-Up Test                         | JESD78                                                     | To categorize the latch-<br>up susceptibility for all<br>microcircuits.                                                                                                               | Must be performed to determine product capability for engineering information. Data collected is for information only and not required for qualification of release to production. Typical sample size/lot = $5$ .                                                                                                                                                                                                                          |

| Charge Device<br>Model ESD Test                      | AEC Q100-011<br>(ANSI/ ESD STM 5.3.1)                      | To categorize the<br>electrostatic sensitivity<br>using charge device<br>model for microcircuits.                                                                                     | Should meet a minimum of 500V on all pins with corner pins at 750V. Required 250V, 500V on all pins with corner pins at 750V. Engineering data can be collected at 1000V and 2000V. Customer may request data for their specific package. Pre- and post-room and hot temperature testing. Typical sample size/lot = $\#$ of voltage steps ×3 devices.                                                                                       |

| Latch-up<br>Current Injection<br>and Over<br>Voltage | QCI-30521<br>(JESD78)                                      |                                                                                                                                                                                       | $\pm 100$ mA injection on I/O pins with a clamp of 1.5× maximum VsuppLy on the positive injection and 0.5× maximum VsuppLy on the negative injection (not to exceed VABS/MSV). VsuppLy pin shall be stressed at 1.5× maximum VsuppLy with a 100 mA clamp (not to exceed VABS/MSV). Stress 6 devices per temperature (room and maximum operating temperature). Pre- and post-room and hot temperature testing. Typical sample size/lot = 12. |

| Electrical<br>Distribution                           | AEC Q-100-009                                              |                                                                                                                                                                                       | Data log parameters at room, hot, and cold temperatures at Vcc min/max and Frequency min/max. Typical sample size/lot = 30.                                                                                                                                                                                                                                                                                                                 |

## Table 2: Package Qualification Methods

| Package Tests                                  | Industry Standard                         | Test Purpose                                                                                                                                                                                                  | Method/Condition                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bond Strength                                  | MIL-STD-883 Method<br>2011                | To ensure that lead bonded<br>devices meet established<br>lead bond strength limits<br>and to ensure that no bond<br>degradation occurs during the<br>sealing process.                                        | Devices are subjected to simulated seal cycle using a heater<br>plate and pre-seal units are pulled (2 grams for aluminum<br>and 3 grams for gold—0.001" diameter wire). Bond Shear:<br>JESD22-B116. Bonds of pre-sealed units are sheared and<br>examined visually. The shear force shall exceed the minimum<br>recommended bond shear value mentioned in the standard.<br>Typical sample size/lot = 15. |

| Coplanarity                                    | QCI-33003                                 | To verify the coplanarity on leads.                                                                                                                                                                           | Lead > 4 mils out of common plane is considered fail. Typical sample size/lot = 30.                                                                                                                                                                                                                                                                                                                       |

| HAST                                           | JESD22-A110                               | To determine the effects of<br>high temperature and high<br>humidity on package.                                                                                                                              | Devices tested are subjected to 130°C, 85% RH or110°C,<br>85% RH at 264 hours and maximum data sheet operating<br>voltage. After 96 hours the devices are functionally tested at<br>25°C and hot temperature. Typical sample size/lot = 231.                                                                                                                                                              |

| UHAST                                          | JESD22-A118                               | To determine the effects of<br>high temperature and high<br>humidity without electrical bias<br>on package.                                                                                                   | Devices are exposed to conditions of 130°C, 85% RH for 96 hours or 110°C, 85% RH for 264 hours—full functional test at 25°C. Typical sample size/lot = 231.                                                                                                                                                                                                                                               |

| Temperature –<br>Humidity Without<br>Bias (TH) | JESD22-J101                               |                                                                                                                                                                                                               | 85°C 85% RH, 1000 hours. Typical sample size/lot = 231.                                                                                                                                                                                                                                                                                                                                                   |

| High<br>Temperature<br>Storage Life<br>(HTSL)  | MIL-STD-883 Method<br>1033 or JESD22-A103 | To determine the effects<br>of time and temperature,<br>under storage conditions,<br>for thermally activated<br>failure mechanisms and<br>time-to-failure distributions of<br>solid state electronic devices. | Devices are subjected to 175°C, 504 hours—functionally tested at 25°C hot temperature. Typical sample size/lot = 45.                                                                                                                                                                                                                                                                                      |

| Physical<br>Dimensions                         | JESD22-B100                               | To verify that the external<br>physical dimensions of the<br>device conform to drawing<br>dimensions.                                                                                                         | JESD22-B100. Dimensions verified for body, lead length, space between leads, etc. Typical sample size/lot = 2.                                                                                                                                                                                                                                                                                            |

| Lead Integrity                                 | JESD22-B105                               | To check the resistance of the leads to metal fatigue.                                                                                                                                                        | Devices are subjected to 3 bend stress cycles, followed with a visual inspection. Specification-appropriate sample sizes.                                                                                                                                                                                                                                                                                 |

| Solderability                                  | JESD22-B102                               | To evaluate the solderability of terminations that are joined by soldering.                                                                                                                                   | Specimens are immersed in flux and dipped in a 245°C, $\pm$ 5°C molten solder bath. Typical sample size/lot = 22.                                                                                                                                                                                                                                                                                         |

| Temperature<br>Cycle                           | JESD22-A104                               | To determine the resistance<br>of a part exposed to extremes<br>of high and low temperatures<br>and to the effect of alternate<br>exposures to these extremes.                                                | JESD22-A104. Devices are subjected to 500 thermal cycles alternating between –65°C and +150°C. Typical sample size = 231.                                                                                                                                                                                                                                                                                 |

| Tin Whisker                                    | JESD22-A121                               |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                           |

| Visual                                         |                                           | To perform a visual inspection<br>of the device for visual/<br>mechanical criteria.                                                                                                                           | PI-91081B. Devices are inspected for defects or damage to case, leads or seals, or illegible markings. Specification-appropriate sample sizes.                                                                                                                                                                                                                                                            |

| Endpoint<br>Electrical                         |                                           | To determine device functionality.                                                                                                                                                                            | Devices are tested to electrical test specifications.<br>Specification-appropriate sample sizes.                                                                                                                                                                                                                                                                                                          |

| Lead Finish                                    | MIL-STD-883 Method<br>2025                | To determine the integrity of all primary and undercoat lead finishes.                                                                                                                                        | A bend stress is applied to randomly selected leads from each device. Specification-appropriate sample sizes.                                                                                                                                                                                                                                                                                             |

## **Ongoing Reliability**

Once a product has been qualified, Microchip employs a reliability monitor system to verify that the level of quality and reliability demonstrated during the qualification process is maintained over time.

Listed below are the types of monitor tests typically performed to confirm continued product attribute performance (see Table 3). The test methods and conditions are equivalent to those performed during qualification.

Occasionally tests are combined to create sequential tests (commonly used reliability tests executed one after another using the same devices). Microchip performs sequential testing to simulate the interaction of worst-case environmental conditions experienced in field applications. Surface-mount devices are preconditioned (bake, moisture soak, convection reflow) prior to the package tests to accurately emulate the assembly process performed by customers. As a result, Microchip's reliability monitor data provides a clear indication of expected field reliability.

## Table 3: Reliability Monitoring Methods

| Test                         | Industry Standard                             | Die/Package | Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|-----------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lead Integrity               | JB105, condition A/C                          |             | Typical sample size/lot = 45.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| UHAST                        | JESD22-A118                                   | Package     | 130°C 85% RH for 96 hours or 110°C 85% RH for 264 hours. Typical                                                                                                                                                                                                                                                                                                                                                                                            |

| Electrical Test              | PDC/Test spec at room or hot                  |             | sample size/lot = 77.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Temperature Cycle            | JESD22-A014                                   | Package     | -65°C to 150°C, 100 cycles 25°C. Typical sample size/lot = 77.                                                                                                                                                                                                                                                                                                                                                                                              |

| Electrical Test              | PDC/Test spec at room or hot                  |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Solderability                | JESD22-B102                                   | Package     | 245°C solder. Typical sample size/lot = 5.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HAST                         | JESD22-A110                                   | Package     | 130°C 85% RH or 110°C 85% RH at 264 hours maximum data sheet operating voltage for 96 hours. Typical sample size/lot = 77.                                                                                                                                                                                                                                                                                                                                  |

| Electrical Test              | PDC/Test spec at room or hot                  |             | operating voltage for so nours. Typical sample size/lot = $TT$ .                                                                                                                                                                                                                                                                                                                                                                                            |

| ELFR                         | MIL-STD-883<br>Method 1005 or<br>AEC-Q100-008 | Die         | 125°C for 48 hours or 150°C for 24 hours, at the maximum Vbb at which<br>the device is guaranteed. Electrically test to proper programs listed<br>in PDC/test specification. Pre-testing may require an additional 25°C<br>insertion to program the burn-in pattern. Post-stress-testing to be done<br>at maximum temperature only. Typical sample size/lot = 77.                                                                                           |

| Dynamic Life Test<br>or HTOL | MIL-STD-883<br>Method 1005                    | Die         | 125°C for 1008 hours or 150°C for 408 hours, at the maximum Vod<br>at which the device is guaranteed. Electrically test to proper programs<br>listed in PDC/test specification. Testing at read points should be done<br>at 85°C only. Pre-testing may require an additional 25°C insertion to<br>program the burn-in pattern. Typical sample size/lot = 77.                                                                                                |

| Retention Bake               | MIL-STD-883,<br>Method 1033                   | Die         | 150°C for 1008 hours or 175°C for 504 hours. Electrically test to proper programs listed in PDC/test specification. Testing at read points should be done at 85°C only. Pre-testing may require an additional 25°C insertion to program the burn-in pattern. Typical sample size/lot = 77.                                                                                                                                                                  |

| Endurance<br>(Pre-condition) | MIL-STD-883<br>Method 1033<br>QCI-30540       | Die         | Erase/Write (page) cycles at 85°C followed by two 48-hour, 150°C bakes.<br>Erase/Write (block/page/byte) cycles per qualification plan, with equivalent maximum cycles that are guaranteed by the data sheet. Electrically test to proper programs listed in PDC/test specification. Testing at read points should be done at 85°C only. Pre-testing may require an additional 25°C insertion to program the burn-in pattern. Typical sample size/lot = 77. |

#### **Reliability Data**

Microchip's products provide competitive leadership in reliability with demonstrated performance.

Detailed Microchip product reliability reports are published quarterly and are accessible via Microchip's website at www.microchip.com.

#### Total Endurance<sup>™</sup> Software

Endurance is the measure of the number of times an EEPROM can be erased and rewritten. Since differing criteria are often used by suppliers when determining EEPROM endurance, it is important that the specific conditions of the study used in this determination be well understood. Unfortunately, the conditions used rarely fit the application being used by the customer. As a result, the actual EEPROM endurance performance in the application may not meet the data sheet specification or the customer's requirements. The

task of determining the true "in-application" endurance prior to implementation becomes guesswork.

Microchip has developed a way to eliminate this guesswork. Through an extensive examination of technology, application and environmental conditions, Microchip has developed a software model capable of accurately predicting EEPROM endurance. This Windows® based endurance prediction tool, called Total Endurance software, allows the user of the software to perform a "what if" analysis of their application and fine tune their design to achieve established reliability requirements. Trade-offs can be examined for several variables. These variables include device type, voltage, temperature, cycling mode, data pattern, number of bytes/cycles, erase/write cycles per day, application life and PPM. These variables have been chosen because they can be directly modified by the customer. The model uses these inputs to generate numerical and graphical outputs of the endurance characteristics for the conditions provided.

The model itself was developed from the results of a comprehensive 2<sup>(7-4)</sup> factorial experiment conducted by a cross-functional team of Microchip engineers. A comparison of model data to endurance data taken from reliability monitors of Microchip's EEPROM products showed a good fit between curves.

The Total Endurance software is available from local sales representatives, distributors and the Microchip website.

## MONITORING, MEASUREMENT AND CONTINUOUS IMPROVEMENT

Continuous improvement is a long-term strategy that Microchip follows to improve overall business operations in terms of customer value, customer satisfaction, quality, cost and time to market. Microchip believes that it must constantly measure the effectiveness of its processes in order to fulfill its Quality Policy and Quality Objectives with the goal of producing high-quality products that exceed customer expectations.

Microchip's quality and continuous improvement program is based on the concept of 'Zero Defects,' a management tool aimed at the reduction of defects though prevention and 'doing it right the first time'. (Reference: Zero Defects: A New Dimension in Quality Assurance). Microchip utilizes a process-based, data-driven approach to improving the quality of its processes, products and systems. This section describes some of the processes, methodologies and techniques that are utilized by Microchip in its quest to achieve 'Zero Defects'.

Figure 8: Zero Defects Concept

#### Establishing Quality Goals/Key Process Indicators (KPIs)

Quality goals and KPIs are established as a means to define, measure, monitor and track performance over time towards the attainment of the stated organizational goals. The goals and KPIs are quantifiable measures that are used to determine if performance is meeting strategic and operational quality (and other) goals that are crucial to the success of the organization. Quality goals and KPIs are instituted across all product and process lines and functional organizations. Indicators primarily focus on quality performance, delivery performance and cycle-times, among other performance metrics.

#### **Internal Quality System Audits**

One of the most important goals of an internal quality audit program is to measure the effectiveness of an organization's Quality Management System. Internal audit results are an important tool that Microchip management uses to assess the health of the company's Quality Management System and to direct improvement initiatives.

Microchip's Internal Audit program entails performing a systemic evaluation of Microchip's processes to:

- Ensure conformance to Microchip's Quality Management System that is based on ISO9001 and ISO/TS 16949 standard requirements

- · Assess if processes/procedures have been implemented successfully

- Evaluate the effectiveness of achieving defined Quality Goals and KPI targeted improvements

- Evaluate data concerning the reduction and elimination of problems

- Provide recommendations for improving operations

Audit results are documented, and any conformance issues are formally managed and resolved through the company's Corporate Corrective and Preventive Action System.

#### **Corrective and Preventive Action System (CA/PA System)**

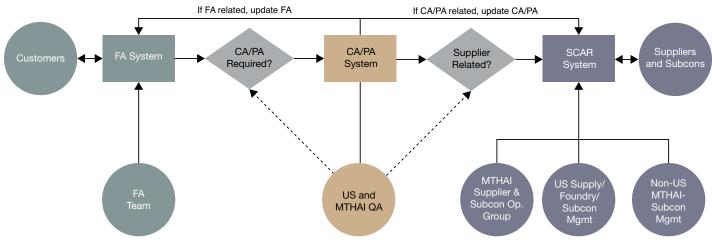

Microchip's integrated Corporate Corrective/Preventive Action System (CA/PA System) aims to consolidate the various types of corrective and preventive actions that are initiated as a result of a customer incident and/or external and internal findings (e.g., customer audits, ISO/TS audits, internal audits, supplier issues, etc.). Based on the eight disciplines (8D) approach to problem solving, the goal of the integrated CA/PA System is to ensure that action requests are formally assigned, that the root cause is identified and that corrective/preventive actions are implemented and are effective. The system utilizes a centralized and integrated database (refer to Figure 9), and is accessible to the worldwide organization. The CA/PA System includes formal assignment and tracking of issues through all phases of problem solving. Records of assigned/completed CA/PAs are maintained along with any supporting documentation.

Figure 9: CA/PA System

#### **Other Improvement Tools and Techniques**

Microchip utilizes a variety of improvement tools and techniques to understand processes, collect and analyze data, identify causes, generate ideas and make informed decisions on continuous improvement activities. Listed below are some of the types of tools and techniques routinely used within the company.

- Statistical Process Control (SPC): A statistics-based quality tool that is applied in order to monitor and control a process. Monitoring and controlling the process ensures that it operates at its full potential.

- **Capability Studies:** A statistical technique used to measure the variability of the output of a process and compare that variability with the product specifications.

- Design and Process FMEAs: A preventive methodology for identifying all potential failure modes, determining their effect on the operation of the product/process, and identifying actions to mitigate the potential of failure.

- **Measurement System Analysis:** A statistics-based method of determining how much the variation within the measurement process contributes to overall process variability.

- **Design of Experiments (DOE):** Systematic method to determine the relationship between factors affecting a process and the output of that process in order to manage process inputs and optimize the outputs.

- **5 Why Analysis:** An iterative, interrogative technique used to investigate the cause-and-effect relationship underlying a particular problem with the goal of determining the root cause of the problem.

- Statistical Bin Limits (SBL): A wafer-level testing technique that uses a statistical method to determine the typical fallout level of each bin at unit probe.

- Dynamic Part Average Testing (PAT): Represents the application of statistical techniques for the removal of abnormal parts during wafer testing. Test limits are set up to identify and remove outliers (die whose electrical parameters are statistically different from the typical part).

- **Good Die in a Bad Neighborhood:** Works on the rationale that defects are normally clustered. The technique identifies a good/passing die that may be surrounded by failing die. These good die are then removed as a precaution.

- Fail-Proofing Methodologies: A method of mistake-proofing a process to remove any opportunity for error (e.g. barcode-based entry/processing, automated part presence/position loading and verification, automated recipe loading and verification, etc.)

- Lean Manufacturing Concepts: 5S, Kaizen and process mapping are some of the lean manufacturing principles that are incorporated into daily production activities and process improvements.

## CUSTOMER SUPPORT

#### **Customer Interface System**

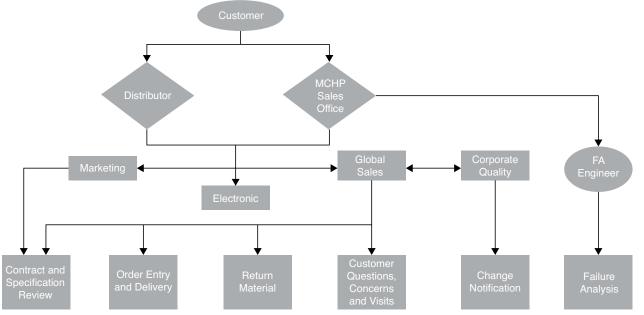

Microchip uses a combination of direct sales and distributors to market our products worldwide (Figure 10). The direct sales force is divided into three geographic regions: Americas, Europe and Asia/Pacific. The efforts of the direct sales force are supported by a network of national and regional distributors. To provide consistent support to our customers, both direct sales and distributors have access to Microchip's corporate interfaces: Marketing and Global Sales. This structure simplifies the communication with customers and encourages a strong working relationship between our customers and our sales support. Our sales support team also has an electronic link to customer-specific data, providing them with the capability to quickly respond to customers' needs.

Figure 10: Customer Interface System

## Order Entry and Delivery

Customers who are interested in placing orders should contact their local Microchip sales office, sales representative or distributor. Orders can be placed by telephone, fax, EDI or customer-provided purchasing documentation. After the order has been received, confirmed and scheduled, the sales contact will email the customer an acknowledgment of the order, including the Standard Terms that apply to the order. If any changes to the order are required, the customer should notify the local Microchip sales representative or distributor to initiate the change request.

## **Return Material (RMA)**

Microchip strives to ship products that exceed customers' quality expectations. In the event that a return is necessary, Microchip employs a 'Return Material Authorization' (RMA) procedure to efficiently handle customer returns. A customer who wishes to return material should contact the local Microchip sales representative or distributor. After the RMA request has been received and approved, an acknowledgment of the RMA authorization will be sent to the customer. The Microchip sales representative or distributor will contact the customer with instructions on how to process the returns. Any credit and/ or replacement parts will be issued upon receipt based on part lead times and urgency of request.

## Failure Analysis

If a product needs to be returned for Failure Analysis (FA), the customer should contact the local Microchip sales office or sales representative to initiate a request. Microchip's Failure Analysis teams are highly qualified and skilled on analytical techniques and laboratory failure analysis tools. Failure Analysis support is available for customers in the Americas, Europe and Asia.

The sales contact or Field Application Engineer (FAE) gathers the necessary information, completes and submits the Online FA Request Form with all the appropriate data. Upon receipt of the physical part(s) and the FA Information Form, a Failure Analysis Tracking Number is assigned and an initial evaluation is performed. The results of the initial analysis are forwarded to the customer via the contact identified on the FA Information Form. To facilitate the accurate assessment of the problem, Microchip's Failure Analysis Engineers work closely with the customer and Field Technical Application Engineers. Once the cause of the failure is identified, a corrective action is initiated (see Figure 9 in CA/PA System section), and the FA Final Report is completed and distributed to the customer via the FAE.

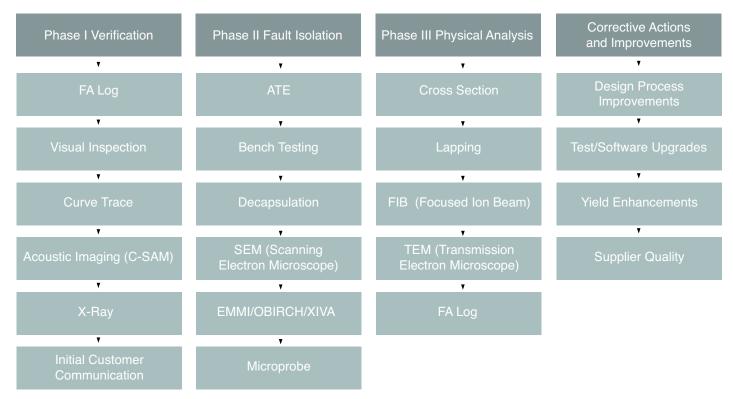

A brief outline of the failure analysis process is shown below.

Figure 11: Failure Analysis Process

#### Phase I (Verification)

An initial evaluation involves a series of non-destructive testing and inspection. Curve tracing, acoustic microscopy, X-ray, low magnification visual inspection and diagnostic testing (ATE) are used to verify the customer's reported failure mode(s). After the testing is complete, an Initial Response report is sent to the customer detailing the results of the analysis.

If the failure cannot be verified through ATE, the Failure Analysis Engineer will attempt to duplicate the customer's failure mode via a bench set up. If the FA Engineer cannot duplicate the failure mode he or she will work with the FAEs, to duplicate the customer's methods of failure identification. If the failure cannot be reproduced at this point, the device can be sent back to the customer for further testing.

#### Phase II (Fault Isolation) and Phase III (Physical Analysis)

If the failure has been confirmed after ATE/bench testing, typically the next step is to try to isolate the failure to a specific location on the die. Fault isolation requires destructive testing to isolate the failure and may include several different methods. Decapsulation is done to expose the die/silicon. Emission/EMMI/SEM/E-Beam tools are used as permitted and required to detect visible and infrared light. Focused Ion Beam (FIB) tools may be needed to provide pads for microprobing. This is performed as needed to isolate the failure to a particular circuit block or contact. Delayering is done to remove the device's passivation, metal and IMD layers to identify the underlying structures and the potential failure mode.

While this is a basic outline, the process for Phases II and III may not necessarily follow these steps in the exact order described and may vary depending on the product. Below is a list of the equipment used to perform the operations described above.

| Activity/Analysis/Operation | Equipment                                                                                                                                                                                                       |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inspection                  | High-/Low-Power Optical Microscope, Confocal Microscope, Scanning Acoustic Microscope, Scanning Electron Microscope, X-ray, 3D Confocal Microscope                                                              |

| Defect Localization         | Light Emission Microscope, OBRICH, Microprobe                                                                                                                                                                   |

| Sample Preparation          | Auto Chemical Decapsulation Machine, Laser Decapsulation Machine, Cross Sectioning, Reactive Ion<br>Etcher, Ion Coater, Backside Polishing, Cross Section (package level), Ion Milling, Target Surfacing System |

| Material Analysis           | EDS/FTIR                                                                                                                                                                                                        |

#### **Final Report**