# AN3077 Application note

## Safety application guide for SPC56ELx family

## Introduction

This document is the safety application guide for the SPC56ELx. It provides the conditions of use for the SPC56ELx in ASIL D applications.

January 2018 DocID16384 Rev 12 1/82

Contents AN3077

## **Contents**

| 1 | Pref | ace                                                    |

|---|------|--------------------------------------------------------|

| 2 | Gene | eral information                                       |

|   | 2.1  | Mission profile                                        |

|   | 2.2  | Safe state                                             |

|   | 2.3  | Failure indication time                                |

|   | 2.4  | Error handling                                         |

|   | 2.5  | Sphere of Replication                                  |

| 3 | Fund | tional safety requirements for application software 12 |

|   | 3.1  | Application software requirements                      |

|   |      | 3.1.1 Mandatory software requirements                  |

|   |      | 3.1.2 Recommended software requirements                |

|   |      | 3.1.3 Implementation details                           |

|   | 3.2  | System Status and Configuration Module (SSCM)          |

|   |      | 3.2.1 Configuration                                    |

|   |      | 3.2.2 Checking                                         |

|   | 3.3  | Self-Test Control Unit (STCU)                          |

|   |      | 3.3.1 Configuration                                    |

|   |      | 3.3.2 Checking                                         |

|   | 3.4  | Reset Generation Module (MC_RGM)                       |

|   | 3.5  | Clock configuration                                    |

|   | 3.6  | SRAM                                                   |

|   | 3.7  | Flash memory                                           |

|   | 3.8  | Interrupt Controller (INTC)                            |

|   | 3.9  | Semaphore Unit (SEMA4)                                 |

|   | 3.10 | Enhanced Direct Memory Access (eDMA) requests          |

|   | 3.11 | Periodic Interrupt Timer (PIT)                         |

|   | 3.12 | Communication peripherals                              |

|   | 3.13 | I/O peripherals                                        |

|   |      | 3.13.1 Read Digital Inputs                             |

|   |      | 3.13.2 Read PWM Input                                  |

|   |      | 3.13.3 Read Encoder Inputs                           |

|---|------|------------------------------------------------------|

|   |      | 3.13.4 Write Digital Outputs                         |

|   |      | 3.13.5 Write PWM Outputs                             |

|   |      | 3.13.6 Other requirements for I/O peripherals        |

|   | 3.14 | Cross Triggering Unit (CTU)                          |

|   |      | 3.14.1 Synchronize Sequential Read Input             |

|   | 3.15 | ADC                                                  |

|   |      | 3.15.1 Read Analog Inputs                            |

|   |      | 3.15.2 Other requirements                            |

|   | 3.16 | Temperature sensors                                  |

|   | 3.17 | Software Watchdog Timer (SWT)                        |

|   | 3.18 | Redundancy Control Checking Unit (RCCU) 4            |

|   | 3.19 | Cyclic Redundancy Checker Unit (CRC) 4               |

|   | 3.20 | Clock Monitor Unit (CMU)                             |

|   | 3.21 | Frequency-Modulated Phase-Locked Loop (FMPLL) 49     |

|   | 3.22 | Internal RC Oscillator (IRCOSC)                      |

|   | 3.23 | Power Management Unit (PMU) 50                       |

|   | 3.24 | Memory Protection Unit (MPU)                         |

|   | 3.25 | Register Protection Module                           |

|   | 3.26 | Error Correction Status Module (ECSM)                |

|   | 3.27 | Fault Collection and Control Unit (FCCU)             |

| 4 | Func | tions of external devices for ASIL D applications 56 |

|   | 4.1  | External Watchdog Function (EXWD) 56                 |

|   | 4.2  | Power Supply and Monitor Function (PSM)              |

|   | 4.3  | Error Out Monitor Function (ERRM)                    |

|   |      | 4.3.1 Both FCCU pins connected to external device    |

|   |      | 4.3.2 Single FCCU pin connected to external device   |

|   | 4.4  | PWM Output monitored by external ASIC (PWMA) 58      |

| 5 | Scen | arios for automotive applications: Motor control 59  |

|   | 5.1  | Application example 1 59                             |

|   |      | 5.1.1 Functional safety related inputs               |

|   |      | 5.1.2 Functional safety related outputs              |

|   | 5.2  | Application example 2                                |

| 9 | Revi  | sion his | story                             | . 76 |

|---|-------|----------|-----------------------------------|------|

|   | 8.3   | Docun    | ment references                   | . 75 |

|   | 8.2   | Acron    | yms and abbreviations             | . 74 |

|   | 8.1   | Conve    | entions and terminology           | . 74 |

| 8 | Furt  | her info | ormation                          | . 74 |

| 7 | I/O p | oin/ball | configuration                     | . 69 |

|   | 6.4   | Fault    | coverage and execution time       | . 68 |

|   | 6.3   | UTES     | T mode ECC logic check            | . 68 |

|   | 6.2   | Data p   | oattern - Walking 0               | . 67 |

|   | 6.1   | Overv    | riew                              | . 67 |

| 6 | ECC   | logic to | est                               | . 67 |

|   |       | 5.3.2    | Functional safety related outputs | 65   |

|   |       | 5.3.1    | Functional safety related inputs  | 64   |

|   | 5.3   | Applic   | cation example 3                  | . 64 |

|   |       | 5.2.2    | Functional safety related outputs | 63   |

|   |       | 5.2.1    | Functional safety related inputs  | 62   |

|   |       |          |                                   |      |

AN3077 List of tables

## List of tables

| Table 1.  | Temperature profile for packaged device                             | 9  |

|-----------|---------------------------------------------------------------------|----|

| Table 2.  | Temperature profile for bare die device                             | 9  |

| Table 3.  | List of Software BIST and/or test for Double Read Digital inputs    | 20 |

| Table 4.  | List of Software BIST and/or test for Read PWM Inputs               | 22 |

| Table 5.  | List of Software BIST and/or test for Read Encoder Inputs           | 25 |

| Table 6.  | List of Software BIST and/or test for SinIgle Write Digital Outputs | 27 |

| Table 7.  | List of Software BIST and/or test for Double Write Digital Outputs  | 29 |

| Table 8.  | List of Software BIST and/or test for Double Write PWM Outputs      | 31 |

| Table 9.  | List of Software BIST and/or test for Single Write PWM Outputs      | 33 |

| Table 10. | List of Software BIST and/or test for Cross Triggering Unit (CTU)   | 36 |

| Table 11. | List of Software BIST and/or test for Single Read analog Input      | 43 |

| Table 12. | List of Software BIST and/or test for Double Read Analog Input      | 46 |

| Table 13. | PMU monitored supplies                                              | 50 |

| Table 14. | Functional safety inputs for application example 1                  |    |

| Table 15. | Functional safety outputs for application example 1                 | 60 |

| Table 16. | Functional safety inputs for application example 2                  | 62 |

| Table 17. | Functional safety outputs for application example 2                 | 63 |

| Table 18. | Functional safety inputs for application example 3                  | 64 |

| Table 19. | Functional safety outputs for application example 3                 | 65 |

| Table 20. | Data pattern used by the ECC logic test                             |    |

| Table 21. | Physical pin displacement on internal die                           | 71 |

| Table 22. | List of conventions and terminology                                 | 74 |

| Table 23. | Acronyms and abbreviations                                          |    |

| Table 24. | Document revision history                                           | 76 |

List of figures AN3077

## List of figures

| Figure 1.  | Double Read Digital Input                                            | 19 |

|------------|----------------------------------------------------------------------|----|

| Figure 2.  | Double Read PWM Input                                                | 21 |

| Figure 3.  | Double encoder read input                                            | 24 |

| Figure 4.  | Write Digital Output With Read Back                                  | 26 |

| Figure 5.  | Double Write Digital Output                                          | 28 |

| Figure 6.  | Double Write PWM Output configuration                                | 30 |

| Figure 7.  | Single Write PWM Output With Read Back configuration                 | 32 |

| Figure 8.  | Single Read Analog Input configuration                               | 38 |

| Figure 9.  | Software BISTs to test the multiplexing circuitry (ADC_SWTEST_TEST1) | 40 |

| Figure 10. | Implementation of ADC_SW_TEST1 through the ADC presample feature     | 41 |

| Figure 11. | Software BISTs to test the multiplexing circuitry (ADC_SWTEST_TEST2) | 41 |

| Figure 12. | Implementation of ADC_SW_TEST2 through the ADC presample feature     | 42 |

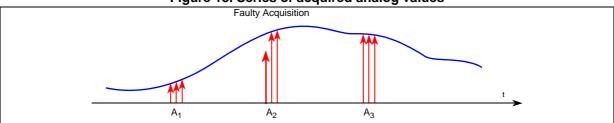

| Figure 13. | Series of acquired analog values                                     |    |

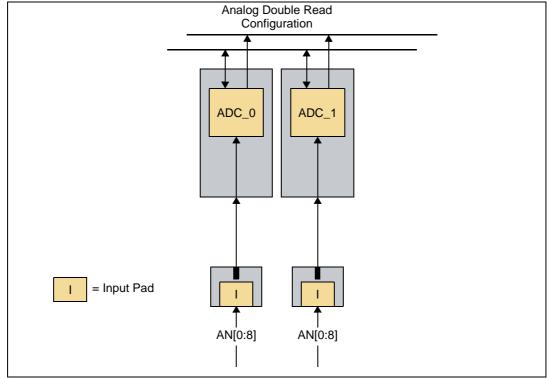

| Figure 14. | Double Read Analog Inputs configuration                              | 45 |

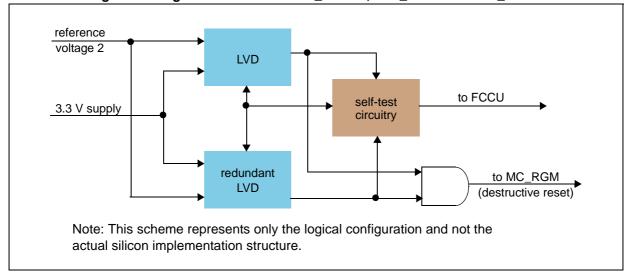

| Figure 15. | Logic scheme of the LVD_DIG and HVD_DIG                              | 51 |

| Figure 16. | Logic scheme of the LVD_FLASH, LVD_GPIO and LVD_VREG                 | 52 |

| Figure 17. | Example of QFP144 pin/pad adjacency                                  | 69 |

| Figure 18. | BGA balls non-adjacent, die pads adjacent                            | 70 |

| Figure 10  | RGA halls adjacent, die nade non-adjacent                            | 70 |

AN3077 Preface

## 1 Preface

This document discusses requirements and assumptions for the use of the SPC56ELx Microcontroller Unit (MCU) in ASIL D applications. It prescribes several measures as mandatory (or mandatory under certain preconditions, for example, if a certain module is used) whereby the measure described was assumed to be in place when analyzing the safety of the MCU.

This document considers:

- The system assembly that contains the SPC56ELx MCU

- The "Safety Element out of Context" section in the "Road vehicles Functional safety -Part 10: Guideline [ISO/DIS 26262-10]" standard

- Certain assumptions about the assembly's functional safety needs based on that standard

and determines whether a measure is mandatory or not based on these factors.

What this means for designers using the SPC56ELx MCU is that if they don't fulfill a specific Safety Application Guide (SAG) prescription they either have to show to their ISO 26262 assessor that the alternative solution is similarly efficient concerning the safety requirement in question (for example, provides the same coverage, avoids Common Cause Failure (CCF) as effectively, and so on), or they have to specify the increased failure rate/reduced Safe Failure Fraction (SFF) they estimate to incur due to the deviation. Otherwise, the assessor will not recognize the MCU certificate that the customer received with the MCU.

This document also contains guidelines on how to configure and operate the SPC56ELx for ASIL D applications. These guidelines are preceded by one of the following bold text statements:

- Implementation hint

- Recommended

- Example

These guidelines are considered to be useful approaches for the specific topics under discussion, but are not mandatory. The user will need to use discretion in deciding whether these measures are appropriate for their applications.

This document is valid only under the assumption that the MCU is used in automotive applications for use cases requiring a fail-silent or a fail-indicate MCU.

**Mandatory:** This document is valid only if the environmental conditions given in the SPC56ELx data sheet are maintained.

The cores in the SPC56ELx can be configured to operate in either Lock-Step Mode (LSM) or Decoupled Parallel Mode (DPM). In LSM, the outputs of a set of replicated modules, identified as the Sphere of Replication (SoR, see Section 2.5: Sphere of Replication for details), are compared to ensure that the operations or transactions that are executed are identical on a clock per clock basis.

**Mandatory:** This document is based on the assumption that the SPC56ELx is configured to operate in LSM.

As for all devices, device errata must be taken into account during system design and implementation. For a safety-related device such as the SPC56ELx, this also concerns safety-related activities such as system safety concept development.

Preface AN3077

**Mandatory:** The device shall be handled according to JEDEC standards J-STD-020 and J-STD-033.

**Mandatory:** To cover the ISO-07-6.5.4 and ISO-07-6.4.2.1, customers shall report all field failures of the devices to silicon supplier.

**Mandatory:** This document is valid only if the conditions given in the addendum are met (see *Section 8.3: Document references*).

AN3077 General information

## 2 General information

## 2.1 Mission profile

The assumed mission profile is:

- Lifetime: 20 years

- Total operating hours: 12000 hours

- Trip time: 10 hours (Trip time is defined as the maximum time of operation of the MCU without power-on reset)

- Fault Tolerant Time Interval (FTTI, also named Process Safety Time (PST)): 10 ms (maximum time between the first faulty output and a failure indication or reset)

Temperature profiles for packaged devices (*Table 1*) and bare die (*Table 2*) are shown below.

Note:

The temperature profile is an assumption of the SPC56ELx safety analysis and shall be fulfilled during integration into an ASIL D compliant system.

| Table 1. Temperature prome for packaged device |                    |  |

|------------------------------------------------|--------------------|--|

| Temperature range (°C)                         | Operation time (h) |  |

| 125–135                                        | 120                |  |

| 110–120                                        | 960                |  |

| 90–100                                         | 7680               |  |

| 30_40                                          | 3240               |  |

Table 1. Temperature profile for packaged device

Table 2. Temperature profile for bare die device

| Temperature range (°C) | Operation time (h) |

|------------------------|--------------------|

| 120–125                | 120                |

| 100–110                | 960                |

| 80–90                  | 7680               |

| 20–30                  | 3240               |

## 2.2 Safe state

By definition, the Safe states of the SPC56ELx are as follows:

- Completely unpowered

- Reset

- All pins except possibly the error output pins (FCCU\_F[0:1]) are tristated.

- · Operating correctly

- Outputs depend on application.

- Explicitly indicating an internal error

- Error output pins FCCU\_F[0:1] are in a state indicating an error, and the state of other I/O pins will not be reliable.

General information AN3077

Defining these states as safe for the MCU means that the overall system must react safely to the SPC56ELx being in, and entering, any of these states. For the 'Completely unpowered' and 'Reset' states the addition of a pullup or pulldown resistor on relevant signals may be necessary. If an 'Explicit indication of internal error' occurs on FCCU\_F[0:1], the application must not depend on the MCU for continued operation. This also means that the system must be able to remain in a safe state without any additional actions from the MCU.

Mandatory: The system must transit to a safe state when there is an indication of an error.

Depending on the configuration the system may disable, or reset, the SPC56ELx as a reaction to the error signal.

If a system continuously switches between a standard operating state and the reset state, without any device shutdown, the system is not considered to be in a Safe state.

Mandatory: The application must identify and signal such switching as a failure condition.

## 2.3 Failure indication time

The SPC56ELx failure indication time must be taken into consideration when determining application safety strategies, because it must be less than the FTTI.

Failure indication time has three components, two of which are influenced by configuration settings: **recognition time + internal processing time + indication time**.

Each component of failure indication time is described as follows:

- Recognition time is the maximum of the recognition time of all involved safety mechanisms. The three mechanisms with the longest time are:

- ADC<sup>(a)</sup> recognition time is the most demanding HW test in terms of timing. The self-test requires the ADC conversion to complete a full test. A single full test takes at least 70 µs<sup>(b)</sup>.

- Recognition time related to the FMPLL loss of clock: it depends on how the FMPLL is configured, but is approximately 20 μs.

- Diagnostic cycle time of software self-tests. This time depends closely on the software implementation.

- Internal processing time lasts maximum 10 RC clock cycles (RC is the internal safe clock with nominal frequency of 16 MHz).

- **Indication time**, the time to notify an observer about the failure, depends on indication protocol configured in the Fault Collection and Control Unit (FCCU):

- Dual Rail protocol and time switching protocol:

- FCCU configured as "fast switching mode": indication delay is maximum 64

µs. As soon as FCCU receives a fault signal, FCCU reports the failure to the

outside world via output pin (if properly configured).

10/82 DocID16384 Rev 12

\_

a. ADC recognition time shall be used only if ADC is used by the safety function.

b. This value takes into account the steps needed to run the three ADC hardware self-tests.

AN3077 General information

FCCU configured as "slow switching mode": an indication delay could occur.

The maximum delay is equal to the period of the error out signal. This parameter shall be configured equal to its minimum which is 128 μs.

Bi-stable protocol: indication delay is maximum 64 μs. As soon as the FCCU receives a fault signal, it reports the failure to the outside world via output pin (FCCU\_F[0:1], if properly configured).

If the configured reaction to a fault is an interrupt, an additional delay (interrupt latency) can occur until the interrupt handler is able to start executing (for example, higher priority IRQs, XBAR contention, register saving, and so on).

General failure rate, or the Failure Modes, Effects and Diagnostic Analysis (FMEDA) report, is available upon request when covered by an NDA (contact your ST representative).

## 2.4 Error handling

Error handling can be split into two categories:

- · Handling of errors during runtime

- Handling of errors during boot time (for example, Logic Built-In Self-Test (LBIST), Memory Built-In Self-Test (MBIST))

Mandatory: Runtime errors shall be handled in a time shorter than the FTTI.

**Mandatory:** Boot time failures shall be handled before the safety function starts.

Note:

Implementation hint: To satisfy this requirement regarding the LBIST/MIBST, Self-Test Control Unit (STCU) status condition shall be checked by application software before safety application starts (See "Integrity SW Operations" section of the "Self-Test Control Unit (STCU)" chapter in the SPC56ELx Reference Manual for details).

## 2.5 Sphere of Replication

Sphere of Replication (SoR) is used for the duplication of critical components of critical components on the SPC56ELx. The following modules are included in the SoR:

- e200z4 Cores

- Enhanced Direct Memory Access (eDMA)

- Interrupt Controller (INTC)

- Crossbar Switch (XBAR)

- Memory Protection Unit (MPU)

- Flash memory controller

- Static RAM Controller (SRAMC)

- System Timer Module (STM)

- Software Watchdog Timer (WDT)

- Peripheral Bridge (PBRIDGE)

## 3 Functional safety requirements for application software

This section gives an overview of necessary, or recommended, measures when using the individual modules of the SPC56ELx. If a module is implemented without following the text of this section, the safety certificate for the module, or the entire MCU, may not be validated. It is possible to ignore aspects of the text if equivalent measures that are taken can be shown to manage the same failures.

Modules not explicitly covered by this document do not require any software measures.

The modules covered by the SoR reach very high Diagnostic Coverage (DC) without dedicated measures at application or system levels.

## 3.1 Application software requirements

Application software shall be developed according to ASIL D requirements.

## 3.1.1 Mandatory software requirements

The following sections contain **Mandatory** design constraints for using the SPC56ELx devices in an ASIL D system:

- Section 3.2: System Status and Configuration Module (SSCM)

- Section 3.3: Self-Test Control Unit (STCU)

- Section 3.4: Reset Generation Module (MC\_RGM)

- Section 3.5: Clock configuration

- Section 3.7: Flash memory

- Section 3.8: Interrupt Controller (INTC)

- Section 3.10: Enhanced Direct Memory Access (eDMA) requests

- Section 3.11: Periodic Interrupt Timer (PIT)

- Section 3.13: I/O peripherals

- Section 3.14: Cross Triggering Unit (CTU)

- Section 3.15: ADC

12/82

- Section 3.16: Temperature sensors

- Section 3.17: Software Watchdog Timer (SWT)

- Section 3.19: Cyclic Redundancy Checker Unit (CRC)

- Section 3.20: Clock Monitor Unit (CMU)

- Section 3.21: Frequency-Modulated Phase-Locked Loop (FMPLL)

- Section 3.22: Internal RC Oscillator (IRCOSC)

- Section 3.23: Power Management Unit (PMU)

- Section 3.25: Register Protection Module

- Section 3.27: Fault Collection and Control Unit (FCCU)

DocID16384 Rev 12

## 3.1.2 Recommended software requirements

The following sections contain **Recommended** design constraints for using the SPC56ELx devices in an ASIL D system:

- Section 3.6: SRAM

- Section 3.12: Communication peripherals

- Section 3.13: I/O peripherals

- Section 3.16: Temperature sensors

- Section 3.18: Redundancy Control Checking Unit (RCCU)

- Section 3.19: Cyclic Redundancy Checker Unit (CRC)

- Section 3.24: Memory Protection Unit (MPU)

- Section 3.25: Register Protection Module

- Section 3.26: Error Correction Status Module (ECSM)

## 3.1.3 Implementation details

The following sections contain implementation details for using the SPC56ELx devices in an ASIL D system:

- Section 3.2: System Status and Configuration Module (SSCM)

- Section 3.5: Clock configuration

- Section 3.7: Flash memory

- Section 3.8: Interrupt Controller (INTC)

- Section 3.10: Enhanced Direct Memory Access (eDMA) requests

- Section 3.13: I/O peripherals

- Section 3.14: Cross Triggering Unit (CTU)

- Section 3.16: Temperature sensors

- Section 3.17: Software Watchdog Timer (SWT)

- Section 3.19: Cyclic Redundancy Checker Unit (CRC)

- Section 3.20: Clock Monitor Unit (CMU)

- Section 3.21: Frequency-Modulated Phase-Locked Loop (FMPLL)

- Section 3.23: Power Management Unit (PMU)

- Section 3.25: Register Protection Module

- Section 3.27: Fault Collection and Control Unit (FCCU)

Note: A section may contain **Mandatory** constraints, **Recommended** constraints, **Implementation hints** or any combination of the three.

## 3.2 System Status and Configuration Module (SSCM)

## 3.2.1 Configuration

**Mandatory:** Before executing the safety functions, the SSCM shall be configured to inhibit unintentional execution of the BAM code.

Note: Rationale: Since BAM code is not intended to be executed by ASIL D applications, any execution of the BAM, or part of it, must be inhibited.

Note: **Implementation hint:** This requirement is satisfied by writing SSCM\_ERROR[RAE] = 1. Each access to the BAM memory area produces a Machine Check exception.

#### 3.2.2 Checking

**Mandatory:** After boot, but before executing any safety function, the application software needs to read SSCM\_STATUS[LSM] to verify that the device runs in the selected mode of operation:

- Decoupled Parallel Mode (DPM) SSCM STATUS[LSM] = 0

- Lock Step Mode (LSM) SSCM\_STATUS[LSM] = 1

Note: Rationale: To check if the MCU started in LSM

## 3.3 Self-Test Control Unit (STCU)

## 3.3.1 Configuration

The STCU does not require any configuration written by application software. The default STCU configuration is to execute LBIST/MBIST and to react to detected faults by triggering a Non-Critical Fault (NCF) that signals the FCCU (See "Self-Test Control Unit (STCU)" chapter in the SPC56ELx Reference Manual for details).

**Mandatory:** LBISTs and MBISTs shall be configured to be executed once per trip time (trip time defined in *Section 2.1: Mission profile*).

## 3.3.2 Checking

Note:

**Mandatory:** Once after boot, before the safety application starts, application software shall carry out some STCU checking steps for ensuring STCU reliability.

Note: Implementation hint: See "Integrity SW Operations" section of the "Self-Test Control Unit (STCU)" chapter in the SPC56ELxReference Manual for details.

**Rationale:** STCU manages the execution, and checks the result, of the LBISTs and MBISTs. The STCU's correct behavior must be verified by checking the expected results with software.

The Integrity SW should confirm that all MBISTs and LBISTs finished successfully with no additional errors flagged. This software confirmation prevents a fault within the STCU itself from incorrectly indicating that the self-test passed.

This is an additional safety layer since the STCU propagates the LBIST/MBIST and internal faults using the NCF signals of the FCCU. So, reading STCU\_LBS, STCU\_LBE, STCU\_MBSL, STCU\_MBSH, STCU\_MBEL, STCU\_MBEH and STCU\_ERR registers helps increase the STCU auto-test coverage.

## 3.4 Reset Generation Module (MC\_RGM)

A redundant fault notification path is achieved through the use of the MC\_RGM and the FCCU. MC\_RGM configuration is application dependent.

**Mandatory:** However, to have the redundant notification path, both MC\_RGM and FCCU shall be configured to react to critical application faults.

Note: Rationale: To have two notification paths in case of an error

## 3.5 Clock configuration

The system starts by using the internal RC oscillator clock (IRCOSC) as its source (See "Oscillators" chapter in the *SPC56ELx* Reference Manual and *Section 3.22: Internal RC Oscillator (IRCOSC)* below for details on IRCOSC configuration).

**Mandatory:** Before safety functions are executed, the FMPLLs must be configured to use the external oscillator (XOSC) as their source clock.

Note: **Rationale:** Since the IRCOSC is used by the CMUs as reference to monitor the output of the two PLLs, it can not be used as input of these PLLs.

Note: Implementation hint: MC\_CGM\_AC3\_SC[SELCTL] and MC\_CGM\_AC4\_SC[SELCTL] must be set to 1 to select the XOSC.

**Mandatory:** All safety relevant modules shall be clocked with an FMPLL generated clock signal.

Note: Rationale: To reduce the impact of glitches stemming from the external quartz crystal and its hardware connection to the MCU

Note: Implementation hint: This requirement is fulfilled by appropriately programming the Clock Generation Module (MC\_CGM) Clock Divider Configuration and Clock Select Control registers and Mode Entry Module (MC\_ME) MC\_ME\_<mode>\_MC registers (See "Clock Generation Module (MC\_CGM)" and "Mode Entry Module (MC\_ME)" chapters in the SPC56ELx Reference Manual for details).

**Mandatory:** The bypass functionality of the XOSC must be disabled.

Note: **Rationale:** To decrease the interference which may be caused by the crystal oscillator, its output shall be filtered by the internal oscillator.

Note: **Implementation Hint:** To disable the bypass mode, the OSCBYP flag of the OSC\_CTL register shall be set to 0.

## 3.6 SRAM

The system SRAM is protected against hardware dormant faults by hardware BISTs (See "MBIST partitioning" section in the "Self-Test Control Unit (STCU)" of the *SPC56ELx* Reference Manual). This test runs at boot, but some software actions are requested (See Section 3.3: Self-Test Control Unit (STCU)).

Moreover, the system SRAM is also protected by a single error correction/dual error detection (SEC/DED) ECC scheme. The SRAM SEC/DED concerns data and addresses and thus provides diagnostic coverage to logic addresses.

## 3.7 Flash memory

Non-volatile memory (NVM) flash memory is protected with an SEC/DED ECC scheme.

The single-bit correction reporting functionality is not available as described for flash memory ECC (See errata e3320). In case single-bit corrections need to be tracked, the workaround in the errata shall be used. Be aware that the workaround has a higher

Caution:

probability than the original mechanism to miss corrections if several of them occur a short time

To support the detection of dormant faults in the entire memory array and addressing logic, and to check the integrity of the logic used for flash memory programming, the following BISTs must be enabled by software:

Mandatory: Array Integrity Self Check – This BIST is based on functionality built into

the flash memory control logic. It calculates a MISR signature over the array content

and thus validates the content of the array as well as the decoder logic. The calculated

MISR value is dependent on the array content and must be validated by software.

Frequency: This check must be performed at boot time.

Note: Rationale: To check the integrity of the flash memory array content

Note: Implementation hint: This BIST must be started by application software; its result must be validated by reading the corresponding registers in the flash memory controller after it has been finished (See "Array integrity self check" section in the "Flash memory" chapter of the SPC56ELx Reference Manual for detailed information about this BIST).

Mandatory: Write operation – When writing flash memory, the corresponding SW driver must validate the correctness of the programming of flash memory by checking the value of C90FL\_MCR[PEG]. Furthermore, the data that was written must be read back, then verified by SW that it compares with the intended data value.

Frequency: After every write operation or after a series of write operations

Note: Rationale: To verify that the written data is coherent with the expected data

• **Mandatory:** Flash memory ECC logic test – This BIST tests the (digital) logic within the flash memory that is responsible for detecting and correcting faults (ECC logic) in the read data.

Note: **Rationale:** The intention of this test is to assure that correct data is not accidently modified, and single-bit errors are correctly updated.

Reading a set of data words from flash memory and comparing it with expected values is a software initiated function that is controlled by the application.

Frequency: Once per FTTI

Note: Implementation hint: Section 6: ECC logic test explains how to perform flash memory data compared with SW.

## 3.8 Interrupt Controller (INTC)

No specific hardware protection is provided against spurious or missing interrupt requests caused by Electromagnetic Interface (EMI) on the interrupt lines, or bit flips in the interrupt registers of the peripherals<sup>(c)</sup>.

**Mandatory:** Applications that are not resilient against such errors must include detection or protection measures.

Note: Rationale: To manage spurious or missing interrupt requests

c. INTC is a replicated module. No software action is needed to detect faults inside this module.

16/82

Implementation hint: A possible way to detect spurious interrupts is to check corresponding interrupt status in the interrupt status register of the related peripheral before executing the Interrupt Service Routine (ISR) service code.

## 3.9 Semaphore Unit (SEMA4)

Semaphore modules are only used in DPM. Failures of the SEMA4 module may cause unwanted interrupts in LSM. Each SEMA4 unit is connected to both replicated INTC modules. This means that even in LSM when SEMA4 units are not used, a corrupted SEMA4 could trigger continuous interrupts to both INTCs. To avoid this possible failure the INTC shall have the SEMA4 interrupt masked (for example, SEMA4 units have the lowest priority in the INTCs).

**Mandatory**: Application software shall keep these interrupt sources masked by programming the interrupt controller appropriately.

## 3.10 Enhanced Direct Memory Access (eDMA) requests

**Mandatory:** For ASIL D applications, protection against spurious or missing safety relevant eDMA requests must be implemented<sup>(d)</sup>. The methodology used to satisfy this requirement is application dependent.

Note: Rationale: To manage spurious or missing eDMA transfer requests

Note: Implementation hint: Some implementations which can satisfy these requirements are:

- Counting the number of eDMA transfers triggered inside a control period and compare this with what is the expected value.

- If the eDMA is used to manage the analog acquisition with the Cross-Triggering Unit (CTU) and ADC, the number of the converted ADC channels is saved in the CTU FIFO together with the acquired value. The eDMA transfers this value from the CTU FIFO to a respective SRAM location. Spurious or missing transfer requests can be detected by comparing the converted channel with what is expected.

**Mandatory**: Designers must not use the Periodic Interrupt Timer (PIT) module to trigger an eDMA transfer request for ASIL D applications.

Note: Rationale: To avoid a faulty PIT (which is not redundant) from triggering an unexpected eDMA transfer

## 3.11 Periodic Interrupt Timer (PIT)

**Mandatory**: For ASIL D applications the PIT module must be used in such a way that a possible failure is detected by the Software Watchdog Timer (SWT).

Note: Rationale: To catch possible PIT failures

**Mandatory**: If the PIT is used by ASIL D applications, a checksum of its configuration registers must be calculated and compared with the expected value to verify that the PIT

d. eDMA is a replicated module. No software action is needed to detect faults inside this module.

DocID16384 Rev 12

configuration is correct. **Frequency:** Once per FTTI

Note: Rationale: To verify that the PIT remains at its expected configuration

## 3.12 Communication peripherals

The SPC56ELx includes the following communication peripherals:

- FlexCAN

- DSPI

- FlexRay

- LINFlexD

**Recommended:** An appropriate safety software protocol should be utilized (for example, Fault Tolerant Communication Layer, FTCOM) for any communication peripheral employed to meet ASIL D application requirements.

## 3.13 I/O peripherals

The following sections cover the use of the following peripherals:

- System Integration Unit Lite (SIUL)

- eTimer

- FlexPWM

These modules shall be used to implement the following functions if they are part of the application safety function:

- Read Inputs

- Read Digital Inputs

- Read PWM Inputs

- Read Encoder Inputs

- Write Outputs

- Write Digital Outputs

- Write PWM Outputs

These are the safety functions assumed during analysis of the SPC56ELx.

## 3.13.1 Read Digital Inputs

For ASIL D applications, digital inputs used for safety purposes are assumed to be acquired redundantly as described in the following section.

Note:

Implementation hint: If sufficient diagnostic coverage can be obtained by a plausibility check on a single acquisition for a specific application, a plausibility check can replace a redundant acquisition. This hint is a special case of deviation from mandatory requirements as described in the Preface.

## 3.13.1.1 Double Read Digital Inputs

#### 3.13.1.1.1 Hardware elements

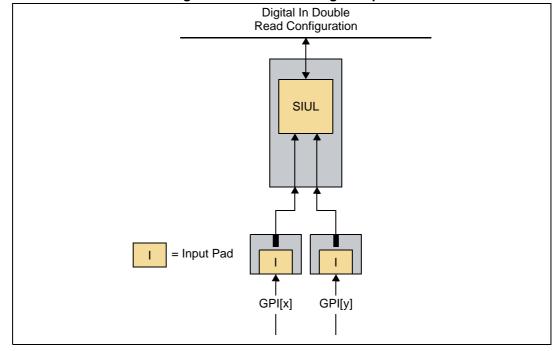

Double read operation of a digital input is implemented by two general purpose inputs (GPI) of the SIUL unit. SIUL must be configured to allow an input signal to be read from its assigned pad. To minimize CCFs, the two input pads must not be physically adjacent (see Section 7: I/O pin/ball configuration for details).

#### 3.13.1.1.2 Safety Integrity Functions

**Mandatory:** Safety integrity is achieved by replicated reading and software comparison by the processing function. The application shall implement the following tests:

SIUL\_SWTEST\_REGCRC

Note: **Rationale:** To verify that the configuration of the two pads used corresponds with the expected configuration, and to avoid a CCF caused by incorrectly configured pads

GPI\_SWTEST\_CMP

Note: Rationale: To verify that the two input values match.

Figure 1. Double Read Digital Input

## 3.13.1.1.3 Software test implementation

SIUL SWTEST REGCRC

The SIUL configuration registers are read, then a CRC is calculated. The CRC calculation is compared to the expected CRC value.

Implementation hint: The eDMA and CRC modules may be used to implement this Safety Integrity Function (SIF) to avoid overloading the CPU.

GPI SWTEST CMP

This software test is used to execute the comparison between the double reads performed by the independent channels.

#### 3.13.1.1.4 Implementation details

The only hardware element that can be used for the safety function is the general purpose input/output (GPIO).

Note:

**Implementation hint:** Every I/O pad that is not dedicated to a single function can be configured as GPIO (ADC pads are an exception to this rule, as they can only be configured as inputs).

Caution:

Redundant GPIO shall be selected in a non-contiguous way from the pin perspective to minimize CCF (see Section 7: I/O pin/ball configuration for details).

**Mandatory:** The pads shall be configured via the appropriate pad configuration registers (PCRn) in the SIUL module.

Note:

**Rationale:** To configure pads used by this safety function, and avoid CCF caused by improper configuration of the pads.

Table 3. List of Software BIST and/or test for Double Read Digital inputs

| Software BIST or test | Frequency                  |

|-----------------------|----------------------------|

| SIUL_SWTEST_REGCRC    | Once after programming     |

| GPI_SWTEST_CMP        | Once for every acquisition |

## 3.13.2 Read PWM Input

For ASIL D applications, digital inputs used for safety purposes are always assumed to be acquired redundantly as described in the following section.

Read PWM Input means any input read related to signal transitions (rise or fall). This may also include the time that the signal was high, low or both.

#### 3.13.2.1 Double Read PWM Inputs

#### 3.13.2.1.1 Hardware elements

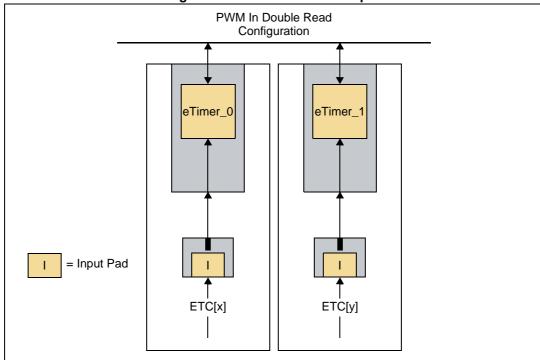

A Double Read PWM Input is implemented by two channels, one channel provided by eTimer\_0 and the other by eTimer\_1. The SIUL module must be configured (via the appropriate SIUL\_PCRn) to provide configuration and input direction of the input pads. To minimize CCFs, these input pads must not be physically adjacent (see Section 7: I/O pin/ball configuration for details).

## 3.13.2.1.2 Safety Integrity Functions

Safety integrity is achieved by reading each input then comparing the values in the processing function (See *Figure 2*).

**Mandatory:** The software tests that the application must implement are:

- ETIMER0\_SWTEST\_REGCRC

- ETIMER1\_SWTEST\_REGCRC

- SIUL\_SWTEST\_REGCRC

Note: **Rationale:** To verify that the configuration of the modules used by this safety function compare to the expected configuration

**Mandatory:** In addition, the double reads must be compared by the application with the implementation of the following test: ETIMERI\_SWTEST\_CMP.

Note: Rationale: To verify that the two sets of data match.

Figure 2. Double Read PWM Input

#### 3.13.2.1.3 Software test implementation

ETIMER0\_SWTEST\_REGCRC

The eTimer\_0 configuration registers are read and a CRC checksum is computed. The checksum is compared with the expected value.

ETIMER1\_SWTEST\_REGCRC

The eTimer\_1 configuration registers are read and a CRC checksum is computed. The checksum is compared with the expected value.

SIUL\_SWTEST\_REGCRC

The configuration registers of the SIUL are read and a CRC checksum is computed. The checksum is compared with the expected value.

**Implementation hint:** The eDMA and CRC modules should be used to implement these SIFs to avoid overloading the CPU.

ETIMERI\_SWTEST\_CMP

This software BIST is used to execute the comparison between the double reads performed by a channel on eTimer\_0 and another channel on eTimer\_1. The comparison must take into account possible approximation because of different capturing of the input asynchronous signals.

#### 3.13.2.1.4 Implementation details

The following hardware elements shall be used for the safety function:

- eTimer\_0 channels

- eTimer\_1 channels

**Mandatory**: The user must select one channel from the eTimer\_0 module and another from the eTimer\_1.

Note: Rationale: To avoid CCF (eTimer\_0 and eTimer\_1 belonging to different lakes)

**Mandatory:** The pads shall be configured via the appropriate pad configuration registers (SIUL\_PCR*n*).

Note: Rationale: To configure pads used by this safety function

Table 4. List of Software BIST and/or test for Read PWM Inputs

| Software BIST or test | Frequency                  |

|-----------------------|----------------------------|

| ETIMERO_SWTEST_REGCRC | Once after programming     |

| ETIMER1_SWTEST_REGCRC | Once after programming     |

| SIUL_SWTEST_REGCRC    | Once after programming     |

| ETIMERI_SWTEST_CMP    | Once for every acquisition |

## 3.13.3 Read Encoder Inputs

For ASIL D applications, encoder inputs used for safety purposes are assumed to be acquired redundantly as described in the following section.

Read Encoder Input means any input read related to signal transitions (rise or fall). This may also include signals coming from an encoder.

#### 3.13.3.1 Double Read Encoder Inputs

#### 3.13.3.1.1 Hardware elements

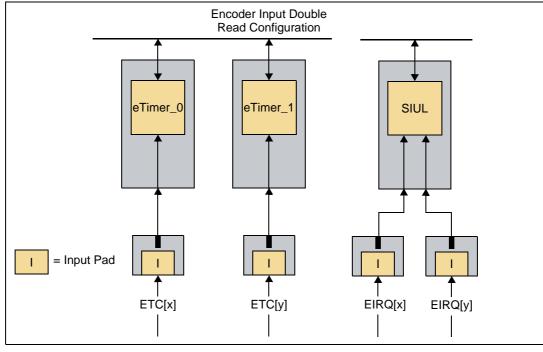

A Double Read Encoder Input is implemented using two channels that can be provided by:

- eTimer 0

- eTimer\_1

- SIUL

When both channels are provided by the timer units, the signals of one encoder must be addressed to eTimer\_0 and the signals of the other encoder must be addressed to eTimer\_1. Alternatively, one or both channels can be provided by the SIUL, which supports

22/82 DocID16384 Rev 12

interrupt based reading of encoder signals. This means the SIUL must use general purpose inputs which have edge detection interrupts (See *Figure 3* for details).

Mandatory: One channel must be addressed by eTimer\_0, and the other by eTimer\_1.

Note: Rationale: Two different eTimers must be used to avoid CCF (eTimer\_0 and eTimer\_1

belonging to different lakes).

For each signal, the SIUL can provide additional channels to support interrupt-based reading.

**Mandatory:** In this configuration, the SIUL must be correctly configured to forward one or two interrupt-based event readings.

Note: Rationale: To configure pads used by this safety function

Mandatory: The input pads must not be physically adjacent (see Section 7: I/O pin/ball

configuration for details).

Note: Rationale: To minimize CCF

#### 3.13.3.1.2 Safety Integrity Functions

The safety integrity is achieved by duplicate reads and software comparison by the processing function (See *Figure 3*).

**Mandatory:** The application software must implement the following tests:

ETIMERO SWTEST REGCRC

ETIMER1\_SWTEST\_REGCRC

SIUL\_SWTEST\_REGCRC

Note: Rationale: To verify that the configuration of the modules used by this safety function

compares with what is expected

Rationale: To avoid CCF caused by improper configuration of the pads

Mandatory: The application software must implement the test ENCI\_SWTEST\_CMP, which

compares signals acquired from each channel.

Note: Rationale: To verify that the two sets of data match.

Figure 3. Double encoder read input

#### 3.13.3.1.3 Software test implementation

ETIMERO SWTEST REGCRC

The eTimer\_0 configuration registers are read, then a CRC checksum is computed. This computed checksum is compared to the expected value.

• ETIMER1 SWTEST REGCRC

The eTimer\_1 configuration registers are read, then a CRC checksum is computed. This computed checksum is compared to the expected value.

SIUL\_SWTEST\_REGCRC

The configuration registers of the SIUL are read, then a CRC checksum is computed. This computed checksum is compared to the expected value.

Note: Implementation hint: The eDMA and CRC modules should be used to implement this SIF to avoid overloading the CPU.

ENCI SWTEST CMP

This software test is used to execute the comparison between the double reads performed by one of the following:

- one channel on eTimer 0 and one channel on eTimer 1

- one channel on eTimer\_1 and one channel on the SIUL

- one channel on eTimer 0 and one channel on the SIUL

- two channels on the SIUL

The comparison must take into account possible approximation because of different captured values of the input asynchronous signals and the execution of interrupt based event reads. Approximation required by different behavior of the encoded inputs must be handled at the application level.

57

#### 3.13.3.1.4 Implementation details

The following hardware elements shall be used for the safety function:

- eTimer\_0 channels

- eTimer 1 channels

- External interrupt via GPIO pins (configured via the SIUL)

The user must select one channel from eTimer\_0 and one from eTimer\_1. The external interrupt pins are optional.

**Mandatory:** The pads shall be configured via the appropriate pad configuration registers (SIUL PCR*n*).

Note: Rationale: To configure pads used by this safety function

Table 5. List of Software BIST and/or test for Read Encoder Inputs

| Software BIST or test | Frequency                  |

|-----------------------|----------------------------|

| ETIMERO_SWTEST_REGCRC | Once after programming     |

| ETIMER1_SWTEST_REGCRC | Once after programming     |

| SIUL_SWTEST_REGCRC    | Once after programming     |

| ENCI_SWTEST_CMP       | Once for every acquisition |

## 3.13.4 Write Digital Outputs

For ASIL D applications, digital outputs used for safety purposes are assumed to be written either redundantly or with read back as described in the following section.

Note:

**Application-dependent option:** If a sufficient diagnostic coverage can be reached by a plausibility check on a single output channel for a specific application, a plausibility check can replace a redundant write or a direct read back.

The element safety function Write Digital Out is implemented as either:

- Single Write Digital Out With Read Back

- Double Write Digital Out

#### 3.13.4.1 Single Write Digital Outputs With Read Back

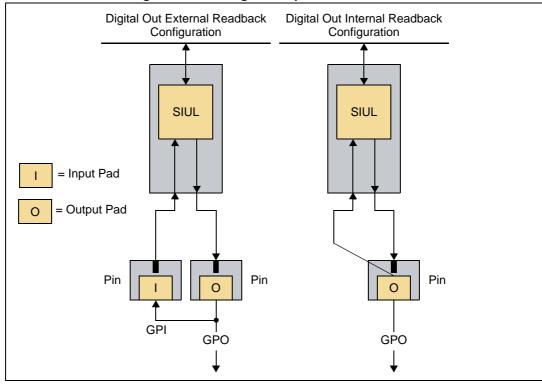

The SIUL hardware element is used to perform a single Write Digital Output With Read Back.

**Mandatory:** The read back must be implemented in one of the two modes shown in *Figure 4*.

Note:

Rationale: To verify if written data compares with the expected data

**Mandatory:** The SIUL element must be correctly configured to provide the output write and the pad directions as follows:

- External read back SIUL is configured to read back the signal from an additional pad, and the loopback is performed outside the device. In this configuration, only half of the available digital outputs are available as safety outputs.

- Internal read back<sup>(e)</sup> SIUL is configured to read back the pad value via an internal read path. All pads dedicated to digital input/output are capable of reading the pad digital status using the input logic.

Note: Rationale: To verify if written data is coherent with the expected data

**Mandatory:** The application software must implement the software test to check the correct configuration of the pads, SIUL\_SWTEST\_REGCRC, and to compare the read back with the digital output write. GPOERB\_SWTEST\_CMP is used for external read back and GPOIRB\_SWTEST\_CMP is used for internal read back.

Figure 4. Write Digital Output With Read Back

#### 3.13.4.1.1 Software test implementation

• SIUL\_SWTEST\_REGCRC

The SIUL configuration registers are read and a CRC checksum is computed. This CRC checksum is compared with what is expected.

Note: Rationale: To avoid CCF caused by incorrect configuration of the pads

Note: Implementation hint: The eDMA and CRC modules should be used to implement this SIF to avoid overloading the CPU.

GPOERB\_SWTEST\_CMP

This software test is used to execute the comparison between the desired output values and the value read back via external read back configuration. After writing the output value, the test must read the value of the digital input.

26/82

e. Internal read back does not cover package faults (e.g., wire bond, etc.).

Note: Rationale: To verify if the read data compares with the written data

GPOIRB\_SWTEST\_CMP

This software test is used to execute the comparison between the desired output values and the value read back via internal read back configuration. After writing the output value, the test must read the status of the digital input.

Note: Rationale: To verify if the read data compares with the written data

#### 3.13.4.1.2 Implementation details

The SIUL hardware element shall be used for the safety function. Every pad that is not dedicated to a single function can be configured as GPIO. Pads dedicated to ADC are an exception to this rule, as they can be configured as inputs only.

The pads shall be configured via the appropriate pad configuration registers (PCRn) in the SIUL module.

Table 6. List of Software BIST and/or test for SinIgle Write Digital Outputs

| Software BIST or test | Frequency              |

|-----------------------|------------------------|

| SIUL_SWTEST_REGCRC    | Once after programming |

| GPOERB_SWTEST_CMP     | Once every write       |

| GPOIRB_SWTEST_CMP     | Once every write       |

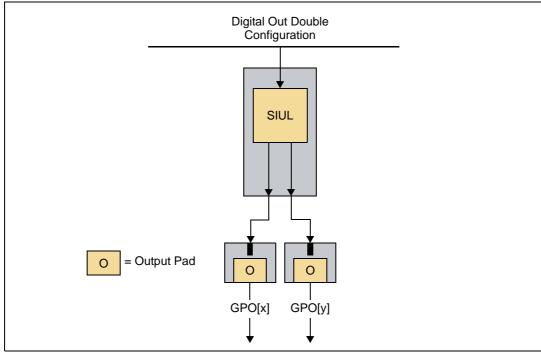

#### 3.13.4.2 **Double Write Digital Outputs**

The SIUL is used to perform a Double Write Digital Output.

Mandatory: The SIUL must be configured to correctly define the configuration of the output pads used. The software must perform a double write.

Note: Rationale: To configure pads used by this safety function

> Mandatory: To guarantee the integrity of the two output channels, the application shall test the SIUL configuration implementing the SIUL\_SWTEST\_REGCRC.

Rationale: To avoid a CCF caused by incorrect configuration of the pads Note:

Mandatory: The application must implement the double output write as defined by the

GPODW\_SWAPP\_WRITE.

Rationale: To write a digital output by exploiting redundancy Note:

Figure 5. Double Write Digital Output

#### 3.13.4.2.1 Software test implementation

SIUL SWTEST REGCRC

The configuration registers of the SIUL are read and a CRC is computed. This CRC value is compared with what is expected.

Note: Implementation hint: The eDMA and CRC modules should be used to implement this SIF to avoid overloading the CPU.

GPODW\_SWAPP\_WRITE

**Mandatory:** The output write of a redundant channel must be implemented following this guideline:

- The two outputs are written with a single instruction to the appropriate register.

- The output register is read back.

Note: Rationale: To minimize CCF of the SIUL

Note: Implementation hint: To write two or more GPIOs with a single instruction, the Masked Parallel GPIO Pad Data Out register (MPGPDOx) register can be used.

Application software shall verify that the two GPIOs used are in the same MPGPDOx register.

To protect the value of the other GPIOs that belong to the same MPGPDOx, the MASK field of the MPGPDOx register needs to be properly configured.

### 3.13.4.2.2 Implementation details

The only hardware element that can be used for the safety function is the GPIO.

Note: Every pad that is not dedicated to a single function can be configured as GPIO. ADCs are an exception to this rule, as they can be configured as inputs only.

47/

28/82 DocID16384 Rev 12

The pads shall be configured via the appropriate pad configuration registers (PCRn) in the SIUL module.

Table 7. List of Software BIST and/or test for Double Write Digital Outputs

| Software BIST or test | Frequency              |

|-----------------------|------------------------|

| SIUL_SWTEST_REGCRC    | Once after programming |

| GPODW_SWAPP_WRITE     | Once every write       |

#### 3.13.5 **Write PWM Outputs**

For ASIL D applications, PWM outputs used for safety purposes are assumed to be written either redundantly or with read back as described in the following section.

The element safety function Write PWM Output is implemented as Double Write PWM Outputs or Single Write PWM Outputs With Read Back.

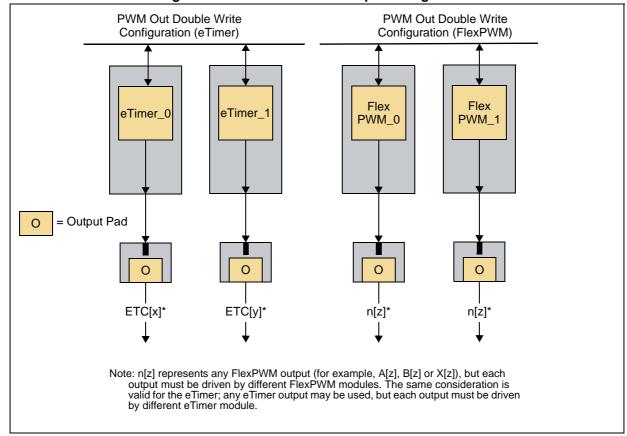

#### 3.13.5.1 **Double Write PWM Outputs**

The hardware elements eTimer\_0 and eTimer\_1 or FlexPWM\_0 and FlexPWM\_1 are used to perform a Double Write PWM Output.

Mandatory: These units must be configured to implement two PWM channels. The SIUL must be configured to define the configuration of the output pads used. The software must perform a double write.

Mandatory: Redundant pads must not be adjacent and pad configuration/data registers must be separate SIUL registers (see Section 7: I/O pin/ball configuration for details).

Note: Rationale: To avoid CCF

> Mandatory: To guarantee the integrity of the two output channels, the application should test the SIUL configuration implementing the SIUL\_SWTEST\_REGCRC.

Rationale: To avoid CCF caused by incorrect configuration of the pads Note:

> Mandatory: The application software must implement a test for the eTimer\_0 and eTimer\_1 configuration (ETIMER0\_SWTEST\_REGCRC, ETIMER1\_SWTEST\_REGCRC) or for the FlexPWM\_0 and FlexPWM\_1 configuration (FLEXPWM0\_SWTEST\_REGCRC, FLEXPWM1\_SWTEST\_REGCRC) and a software write (PWMDW\_SWAPP\_WRITE).

Note: Rationale: To verify that the configuration of the modules used by this safety function

adhere to the expected configuration

Figure 6. Double Write PWM Output configuration

### 3.13.5.1.1 Software test implementation

SIUL\_SWTEST\_REGCRC

The SIUL configuration registers are read and a CRC checksum is computed. The CRC checksum is compared to the expected value.

ETIMER0\_SWTEST\_REGCRC

The eTimer\_0 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

• ETIMER1\_SWTEST\_REGCRC

The eTimer\_1 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

FLEXPWM0\_SWTEST\_REGCRC

The FlexPWM\_0 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

FLEXPWM1\_SWTEST\_REGCRC

The FlexPWM\_01 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

Note: Implementation hint: The eDMA and CRC modules should be used to implement this SIF to avoid overloading the CPU.

• PWMDW\_SWAPP\_WRITE

30/82 DocID16384 Rev 12

3.13.5.1.2

**Mandatory:** The output write of a redundant PWM channel must be implemented by writing the new output values to both the PWM channels. The customer can decide whether to use both eTimers (eTimer\_0, eTimer\_1) or both FlexPWMs (FlexPWM\_0, FlexPWM\_1), See *Figure 6*.

Rationale: To write a digital output by exploiting redundancy, and modules must belong to

different lakes to decrease the probability of CCF

The following hardware elements shall be used for the safety function:

• eTimer 0 channels

Implementation details

- eTimer 1 channels

- FlexPWM 0 channels

- FlexPWM\_1 channels

**Mandatory:** The pads shall be configured via the appropriate pad configuration registers (PCRn) in the SIUL module.

Note: Rationale: To configure pads used by this safety function

Table 8. List of Software BIST and/or test for Double Write PWM Outputs

| Software BIST or test                 | Frequency                             |

|---------------------------------------|---------------------------------------|

| SIUL_SWTEST_REGCRC                    | Once after programming <sup>(1)</sup> |

| ETIMER0_SWTEST_REGCRC <sup>(2)</sup>  | Once after programming                |

| ETIMER1_SWTEST_REGCRC <sup>(2)</sup>  | Once after programming                |

| FLEXPWM0_SWTEST_REGCRC <sup>(3)</sup> | Once after programming                |

| FLEXPWM1_SWTEST_REGCRC <sup>(3)</sup> | Once after programming                |

| PWMDW_SWAPP_WRITE                     | Once every write                      |

If a change in a single SIUL configuration register is capable of affecting both the output and the read-back paths, then SIUL\_SWTEST\_REGCRC must be executed every FTTI. In all other cases configuration errors are covered by the software comparison.

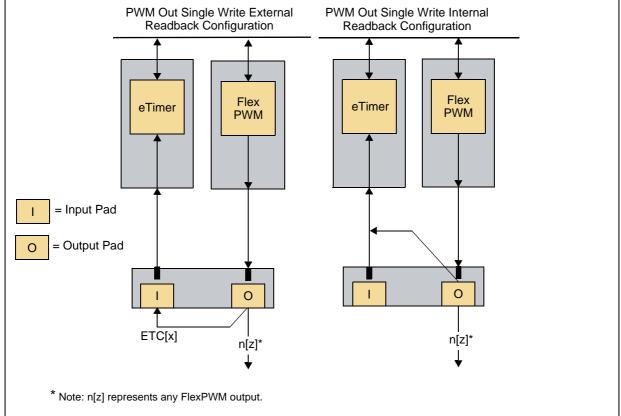

## 3.13.5.2 Single Write PWM Outputs With Read Back

The hardware elements eTimer\_0 and FlexPWM\_1 or eTimer\_1 and FlexPWM\_0 are used to perform a Write PWM Output With Read Back<sup>(f)</sup>. These units must be configured to implement one PWM output channel and (via internal read back) the eTimer\_0 input PWM channel. The SIUL must be configured to define the configuration of the output pads used. The software must perform a write operation followed by a read operation. To guarantee the integrity of the configuration of the channels, the application should test the SIUL configuration implementing the SIUL\_SWTEST\_REGCRC (to avoid a common failure caused by misconfiguration of the pads).

f. eTimer\_0 and FlexPWM\_0 (eTimer\_1 and FlexPWM\_1) cannot be used in combination due to the same LBIST partition assignment.

DocID16384 Rev 12

<sup>2.</sup> This software BIST is needed only if the eTimer channels are used for the safety function

<sup>3.</sup> This software BIST is needed only if the FlexPWM channels are used for the safety function

Implementation hint: A single channel of the eTimer is used with a multiplexing of the internal read back of the different output of the FlexPWM. The read back paths are limited to six signals, two for each sub-module of the FlexPWM.

Mandatory: The application software must implement software tests for eTimer 0 and eTimer\_1 configurations:

- FLEXPWM0\_SWTEST\_REGCRC

- FLEXPWM1\_SWTEST\_REGCRC

- ETIMERO\_SWTEST\_REGCRC

- ETIMER1\_SWTEST\_REGCRC

Note:

Rationale: To verify that the configuration of the modules used by this safety function adheres to the expected configuration

Mandatory: The application software must write to the output port and then compare the written value via the read back (See item PWMRB\_SWTEST\_CMP below).

Note: Rationale: To verify that written data is what is expected

Figure 7. Single Write PWM Output With Read Back configuration PWM Out Single Write External PWM Out Single Write Internal

#### 3.13.5.2.1 Software test implementation

SIUL SWTEST REGCRC

The SIUL configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

• ETIMERO SWTEST REGCRC

The eTimer\_0 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

ETIMER1 SWTEST REGCRC

The eTimer\_1 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

• FLEXPWM0 SWTEST REGCRC

The FlexPWM\_0 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

FLEXPWM1\_SWTEST\_REGCRC

The FlexPWM\_1 configuration registers are read and a CRC checksum is computed. The checksum is compared to the expected value.

Note: Implementation hint: The eDMA and CRC modules should be used to implement this SIF to avoid overloading the CPU.

PWMRB SWTEST CMP

This procedure output compares the PWM read back provided by a single channel of the eTimer\_0 (eTimer\_1) with the expected values that have been written to the FlexPWM\_1 (FlexPWM\_0) output channel.

### 3.13.5.2.2 Implementation details

The following hardware elements shall be used for the safety function:

- eTimer 0 channels

- eTimer 1 channels

- FlexPWM\_0 channels

- FlexPWM 1 channels

**Mandatory:** The pads shall be configured via the appropriate pad configuration registers (PCRn) in the SIUL module.

Note: Rationale: To configure pads used by this safety function

Table 9. List of Software BIST and/or test for Single Write PWM Outputs

| Software BIST or test                 | Frequency              |

|---------------------------------------|------------------------|

| SIUL_SWTEST_REGCRC                    | Once after programming |

| ETIMERO_SWTEST_REGCRC <sup>(1)</sup>  | Once after programming |

| ETIMER1_SWTEST_REGCRC <sup>(1)</sup>  | Once after programming |

| FLEXPWM0_SWTEST_REGCRC <sup>(2)</sup> | Once after programming |

| FLEXPWM1_SWTEST_REGCRC <sup>(2)</sup> | Once after programming |

| PWMRB_SWTEST_CMP                      | Once every write       |

- 1. This software BIST is needed only if the eTimer channels are used for the safety function.

- $2. \quad \text{This software BIST is needed only if the FlexPWM channels are used for the safety function}.$

## 3.13.6 Other requirements for I/O peripherals

Mandatory: Other requirements related to I/O peripherals include the following:

• In the eTimer module, the capture flag (eTimer\_n\_STS[ICFn]) must be used.

Note: Rationale: To detect missing eTimer\_n acquisition

• If the eTimer counter is used to decode a primary and secondary external input as quadrature encoded signals, the eTimer watchdog must be used (See "Counting Modes" section of the SPC56ELx Reference Manual).

Note: Rationale: To detect stalled quadrature counting

## 3.14 Cross Triggering Unit (CTU)

The CTU generates some triggers based on input events (FlexPWMs, eTimers, and/or external pins).

The trigger can be caused by:

- A pulse

- An interrupt

- An ADC command (or a stream of consecutive commands)

- All of these

**Mandatory:** The CTU shall be appropriately configured so that the output triggers are generated within the desired time schedule with respect to the input event(s).

Note: Rationale: To avoid erratic output trigger generation

For each trigger, a set of ADC commands and pulses to be generated can be defined.

If the application safety function includes the read of some inputs synchronized with some events (FlexPWMs, eTimers, and/or external pins), the customer can use the CTU module for this purpose. The software needed for targeting the ASIL D is listed in Section 3.14.1: Synchronize Sequential Read Input.

For a detailed description on how the CTU works (triggered and sequential mode), its configuration and use, refer to the SPC56ELx Reference Manual.

## 3.14.1 Synchronize Sequential Read Input

The CTU can be used if the customer needs to synchronize the reading of some inputs with some events (FlexPWMs, eTimers, and/or external pins).

**Mandatory:** If this function is part of the application safety function, the safety integrity is achieved by a mix of hardware mechanisms and software safety integrity functions implemented at the application level:

- CTU HWSWTEST TRIGGERNUM

- CTU\_SWTEST\_TRIGGERTIME

- CTU HWSWTEST TRIGGEROVERRUN

- CTU\_HWSWTEST\_ADCCOMMAND (only if the input is an analog signal)

- CTU SWTEST ETIMERCOMMAND

- CTU\_HW\_CFGINTEGRITY

Note: These functions are mandatory only if the CTU is used.

34/82 DocID16384 Rev 12

Note:

Note:

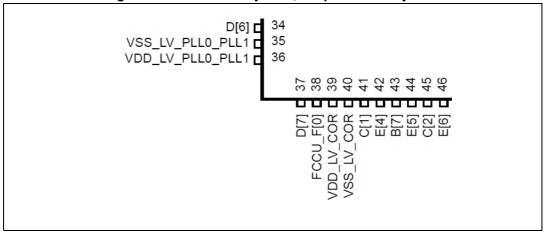

## 3.14.1.1 Software test implementation

CTU\_HWSWTEST\_TRIGGERNUM

If the reload signal occurs before all the triggers are generated, an overrun indication is flagged and the application software must handle the error indication.

Note: **Rationale:** Tests if all the triggers configured within a control period have been generated and serviced.

Note: Implementation hint: The Cross Triggering Unit Error Flag register (CTUEFR) shows information about the overrun status.

CTU\_SWTEST\_TRIGGERTIME

Application software must configure one eTimer channel to capture the time at which each trigger event occurs.

In triggered mode, the time instant of each trigger within one control period is captured and stored in a FIFO. Application software has to check the FIFO values against the expected ones according to CTU configuration.

In sequential mode, one eTimer channel is needed to check the correct time of a single trigger with respect to the corresponding event.

Note: Rationale: To verify if triggers are generated at the correct time

Implementation hint: Some eTimer inputs are internally connected to the CTU output. eTIMER\_2 input/outputs are not connected to pins on LQFP144 package. Use eTIMER\_2 channels for implementing this safety function to keep the channels from eTIMER\_0 or eTIMER\_1 units for functions using port pins (See "Enhanced Motor Control Timer (eTimer)" in the SPC56ELx Reference Manual for details).

**Implementation hint:** eTimer capture register implements a two entry FIFO, but in CTU triggered mode up to 8 time values need to be stored. To avoid FIFO overflow condition, eTimer can be configured to trigger a eDMA transfer to move the captured value to specific RAM location.

CTU\_HWSWTEST\_TRIGGEROVERRUN

This hardware mechanism checks if a new trigger, that requires an action by a subunit currently busy, occurs. In this case, an overrun interrupt is generated and the application software must handle the error condition.

Over-run detection mechanism shall be enabled by software during CTU configuration.

Note: **Rationale:** Checks if a new trigger occurs that requires an action by a subunit (such as ADC command generator) which is currently busy, occurs.

Implementation hint: To enable the over-run detection, the IEE flag in the Cross Triggering Unit Interrupt/eDMA register (CTUIR) register shall be asserted. This interrupt is shared between several sources of error. The user can discriminate among them by reading the CTUEFR register.

CTU\_HWSWTEST\_ADCCOMMAND

The CTU stores in its internal FIFOs both the value provided by each ADC conversion and the channel number. Application software must check the ADC channel number sequence against what is expected for each FIFO. Moreover, invalid commands issued by the CTU are flagged and the corresponding error must be handled by the application software.

Note: **Rationale:** To detect if the incorrect channel has been acquired, or if the incorrect ADC result FIFO is selected

DocID16384 Rev 12

**Implementation hint:** To enable invalid command detection, the IEE flag in the CTUIR register must be asserted.

This interrupt is shared between several sources of error. The user can discriminate among them by reading the CTUEFR register.

This safety integrity function needs to be implemented only when reading analog signals.

CTU SWTEST ETIMERCOMMAND

Application software must configure one channel of eTimer\_0 or eTimer\_1 to count the number of eTimer commands generated within a CTU control period and must check the number against the expected one.

Note: Rationale: To verify the correctness of the number of generated commands

Note: Implementation hint: Some eTimer inputs are internally connected to the CTU output (See the SPC56ELx Reference Manual for details).

CTU HW CFGINTEGRITY

This hardware mechanism ensures the consistency of the CTU configuration at the beginning of each CTU control period.

The configuration registers are all double-buffered. If the configuration is only partial when the control period starts, the previous configuration is used and an error condition is flagged, which must be handled by the application software.

Note: Rationale: Ensure the consistency of the CTU configuration

Note:

Implementation hint: The CTU uses a safe reload mechanism. The General Reload Enable (GRE) bit in the Cross Triggering Unit Control Register (CTUCR) shall be used to detect partial or incomplete CTU update.

To enable the interrupt in case of error during reload, the IEE flag in the CTUIR register shall be asserted.

This interrupt is shared between several sources of error. The user can discriminate among them by reading the CTUEFR register.

#### 3.14.1.2 Implementation details

The following hardware elements shall be used for the safety function:

- CTU

- One eTimer channel

Table 10. List of Software BIST and/or test for Cross Triggering Unit (CTU)

| Software BIST or test       | Frequency                                                                             |

|-----------------------------|---------------------------------------------------------------------------------------|

| CTU_HWSWTEST_TRIGGERNUM     | Once for every control period (< FTTI)                                                |

| CTU_SWTEST_TRIGGERTIME      | Once for every CTU control period (triggered mode) or every trigger (sequential mode) |

| CTU_HWSWTEST_TRIGGEROVERRUN | Once for every trigger                                                                |

| CTU_HWSWTEST_ADCCOMMAND     | Once for every ADC command                                                            |

| CTU_SWTEST_ETIMERCOMMAND    | Once for every control period (< FTTI)                                                |

| CTU_HW_CFGINTEGRITY         | Once for every control period (< FTTI)                                                |

#### 3.14.1.3 Other requirements for CTU module usage

**Mandatory:** The only other requirement related to the CTU is that if the CTU is used to read an analog signal through the ADC, the software shall verify the Invalid Command Error flag (CTU\_CTUEFR[ICR]) after programming the ADC command lists.

Note: Rationale: To check the presence of invalid commands

### 3.15 ADC

If the ADC is used in a safety function, the following sections must be observed if an ADC BIST is to be performed.

It is important to note that the ADC is part of the temperature measuring safety integrity function, and it is therefore required that the HWBIST functions be executed once after the boot even if the ADC is not in application use.

### 3.15.1 Read Analog Inputs

The customer has two options for reading analog inputs:

- Single Read Analog Inputs

- Double Read Analog Inputs

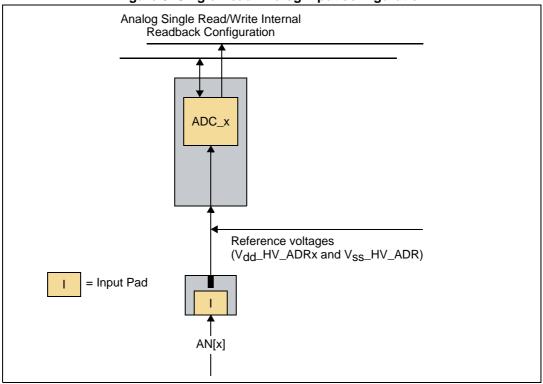

### 3.15.1.1 Single Read Analog Inputs

#### 3.15.1.1.1 Hardware elements

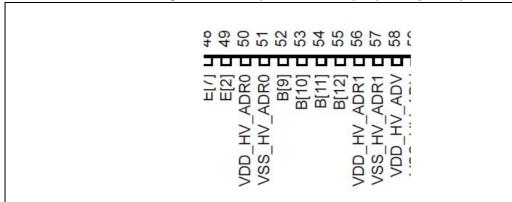

The single-read analog input uses a single-analog-input channel either of ADC\_0 or ADC\_1 to acquire an analog voltage signal (See *Figure 8*).

To support a high diagnostic coverage two known reference supply voltages are utilized by two software tests which are described in the following sections (ADC\_SWTEST\_TEST1 and ADC\_SWTEST\_TEST2).

The reference supply voltages are the following:

- V<sub>DD HV ADR0</sub> (ADC\_0 high reference voltage)

- V<sub>DD\_HV ADR1</sub> (ADC\_1 high reference voltage)

- V<sub>SS HV ADR0</sub> (ADC\_0 low reference voltage)

- V<sub>SS\_HV ADR1</sub> (ADC\_1 low reference voltage)

The SIUL unit must be configured properly to correctly enable the input pads. The pads used for analog inputs are only of type INPUTS.

#### 3.15.1.1.2 Safety Integrity Functions

**Mandatory:** The safety integrity is achieved by dedicated hardware BIST<sup>(g)</sup>:

Note: Rationale: Hardware BIST to check the integrity of the ADC, both analog and digital parts:

SUPPLY SELF-TESTRESISTIVE-CAPACITIVE SELF-TESTCAPACITIVE SELF-TEST

g. These hardware BISTs need some software to activate them. This software shall be developed by the customer.

**Mandatory:** By dedicated software test implemented at the application level:

- ADC\_SWTEST\_TEST1

- ADC\_SWTEST\_TEST2

- ADC\_SWTEST\_VALCHK

- ADC0\_SWTEST\_REGCRC

- ADC1 SWTEST REGCRC

- SIUL\_SWTEST\_REGCRC

- ADC\_SWTEST\_ADCOVERSAMPLING

Figure 8. Single Read Analog Input configuration

#### 3.15.1.1.3 Hardware BIST

Three types of self-test algorithms have been implemented in the ADC hardware:

- SUPPLY SELF-TEST

- RESISTIVE-CAPACITIVE SELF-TEST

- CAPACITIVE SELF-TEST

### 3.15.1.1.3.1 Hardware BIST implementation

The hardware BISTs shall be activated by the application in one of the following modes:

- CPU mode

- CTU mode

In CPU mode, the application software takes care of the hardware self-test activation and checks the test flow and the timing.

38/82 DocID16384 Rev 12

In CTU mode, the CTU module takes care of the hardware self-test activation, flow monitoring, and timing. It is important to note that in this operating mode, the CPU does not take part in running the hardware self-test.

HW self-tests use analog watchdogs to verify the outcome of self-test conversions. The reference thresholds of these watchdogs are saved in test sector (See "Test flash memory" section and "Test flash information" table in the SPC56ELx Reference Manual).

**Mandatory**: Before running the HW self-test, the customer must copy these thresholds from the test sector into the watchdog registers (See "Self test analog watchdog" section of the SPC56ELx Reference Manual).

Note: Rationale: To set the correct threshold for the self-tests

Note: Implementation hint: Since user can not directly read the test sector, an SSCM feature, called Test Flash Enable, shall be exploited. This action is performed through the following steps:

- 1. If code is executing in flash memory, it jumps to execute from RAM.

- 2. Write SSCM\_SCTR[TFE] = 1.

- 3. Test sector is readable at the offset 0x0 of the flash memory address space (See "System Status and Configuration Module (SSCM)" of the Reference Manual).

- 4. Thresholds are copied from the test sector to the respective register.

- 5. Write SSCM SCTR[TFE] = 0.

- 6. Code can continue execution from the flash memory.

BAM implements an access method to read the test sector.

**Mandatory:** Since the BAM is not developed according to the safety standard, a safety application is not allowed to read the test sector through the BAM access method.

Additionally, a watchdog timer is implemented to check the sequence of the self-test algorithms.

**Mandatory:** The customer must enable the watchdog timer for CPU mode and CTU mode. The programmable watchdog timeout is the FTTI<sup>(h)</sup>.

Note: Rationale: To check the sequence of the self-test algorithms

Every hardware BIST is activated via a dedicated command sent to the ADC. Refer to the "Self-testing" section in the "ADC" chapter of the *SPC56ELx Reference Manual* to have all detailed instructions for implementing one of these modes.

The supply self-test must be executed without interleaved user conversion.

#### **3.15.1.1.4** Software tests

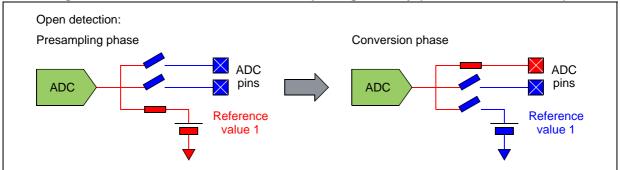

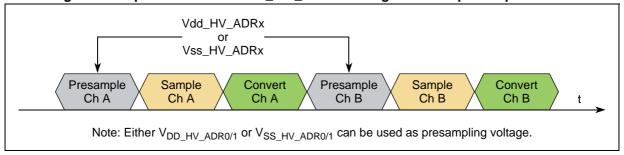

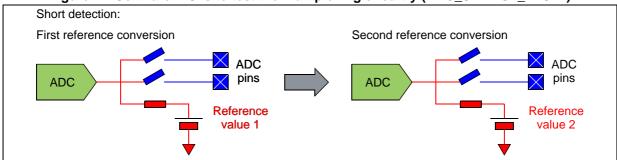

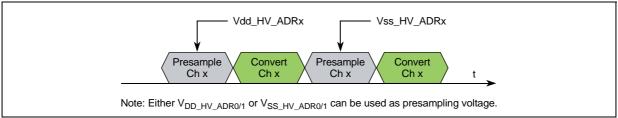

ADC\_SWTEST\_TEST1

This software BIST exploits the presampling feature of the ADC. Presampling allows to precharge or discharge the ADC internal capacitor before it starts the sampling and conversion phases of the analog input coming from pads. During presampling phase,

h. This action is not mandatory in case of Double Read Analog Inputs.

39/82

the ADC samples the internally generated voltage while in the sampling phase the ADC samples analog input coming from pads (See *Figure 10*).

Reference voltage which can be used during presampling phase is either  $V_{DD\_HV\_ADR0/1}$  or  $V_{SS\_HV\_ADR0/1}$ .