# **Mailbox Client Intel® FPGA IP User Guide**

Updated for Intel® Quartus® Prime Design Suite: 21.3

IP Version: 20.1.0

**UG-20087 | 2021.11.10**Latest document on the web: **PDF | HTML**

# **Contents**

| 1. | Mailbox Client Intel FPGA IP User Guide                                         | 3  |

|----|---------------------------------------------------------------------------------|----|

|    | 1.1. Device Family Support                                                      | 4  |

|    | 1.2. Parameters                                                                 |    |

|    | 1.3. Mailbox Client Intel FPGA Core Interface Signals                           | 6  |

|    | 1.3.1. Clock and Reset Interfaces                                               |    |

|    | 1.3.2. Avalon Memory-Mapped Interface                                           | 7  |

|    | 1.3.3. AXI Target Interface                                                     | 7  |

|    | 1.4. Mailbox Client Intel FPGA IP Avalon MM Memory Map                          | 9  |

|    | 1.4.1. Interrupt Enable Register                                                | 10 |

|    | 1.4.2. Interrupt Status Register                                                |    |

|    | 1.4.3. Timer Registers                                                          | 12 |

|    | 1.5. Commands and Responses                                                     | 14 |

|    | 1.5.1. Operation Commands                                                       | 14 |

|    | 1.5.2. Error Code Responses                                                     | 22 |

|    | 1.5.3. Error Code Recovery                                                      | 24 |

|    | 1.6. Specifying the Command and Response FIFO Depths                            | 25 |

|    | 1.7. Enabling Cryptographic Services                                            |    |

|    | 1.8. Using the Mailbox Client Intel FPGA IP                                     |    |

|    | 1.9. Mailbox Client Intel FPGA IP Core Use Case Examples                        |    |

|    | 1.10. Nios II HAL Driver                                                        |    |

|    | 1.10.1. Driver API                                                              |    |

|    | 1.11. Mailbox Client Intel FPGA IP User Guide Archives                          |    |

|    | 1.12. Document Revision History for the Mailbox Client Intel FPGA IP User Guide | 37 |

| 2. | Appendix: CONFIG_STATUS and RSU_STATUS Error Code Descriptions                  | 42 |

# 1. Mailbox Client Intel FPGA IP User Guide

The Mailbox Client Intel FPGA IP is a bridge between a host and the secure device manager (SDM). Available for Intel® Stratix® 10 and Intel Agilex™ devices, you use the Mailbox Client Intel FPGA IP to send commands and receive status from SDM peripheral clients. The Mailbox Client defines functions that the SDM runs.

The following pre-defined functions are available:

- Reading the Chip ID

- Reading temperature sensors

- Reading voltage sensors

- Reading and writing external quad serial peripheral interface (SPI) flash memory

- Performing remote system updates (RSU)

- Enabling cryptographic services<sup>(1)</sup>

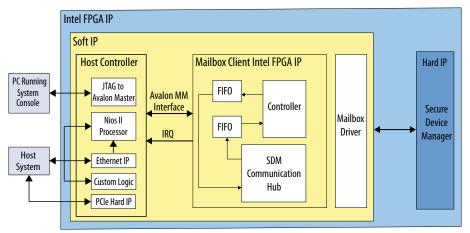

The following block diagram shows how to use the Mailbox Client Intel FPGA IP in an interactive session. The diagram also emphasizes different ways of communicating with IP through the Host Controller.

Figure 1. **Mailbox Client Intel FPGA IP System Block Diagram**

This block diagram includes the following components:

<sup>(1)</sup> This feature is available for Intel Agilex devices in Intel Quartus® Prime software version 21.3 or later.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

- Host Controller: provides possible ways of accessing the Mailbox Client Intel FPGA

IP. Use any of the specified ways to communicate with the host controller:

- System Console with the JTAG to Avalon<sup>®</sup> Master Bridge Intel FPGA IP. The System Console provides a Tcl Console pane that you can use to run the IP functions. The JTAG to Avalon Master Bridge Intel FPGA IP translates the commands it receives from the System Console to Avalon Memory-Mapped (Avalon MM) format that the Mailbox Client Intel FPGA IP requires.

- Nios<sup>®</sup> II processor: sends commands to the Mailbox Client Intel FPGA IP.

- Custom logic: It sends commands to the Mailbox Client Intel FPGA IP.

- PCIe\* Hard IP

- Ethernet IP

- Mailbox Client Intel FPGA IP: drives commands and receives responses from the SDM. This component includes FIFOs with a maximum depth of 1024 entries to store commands and responses. The Mailbox Client Intel FPGA IP interrupt indicates when the input FIFO in full and when the output FIFO contains valid data. You can size these FIFOs to accommodate the commands the you intend to send.

Intel provides a reference design that uses the System Console and the JTAG master to drive the Mailbox Client Intel FPGA IP. In the Intel Design Store, search for Intel Agilex Mailbox Client Intel FPGA IP Core Design Example (QSPI flash Access and Remote System Update) to view the design.

#### **Related Information**

- Avalon Interface Specifications

- Secure Device Manager in Intel Stratix 10 Devices

- Operation Commands on page 14

- Analyzing and Debugging Designs with System Console

- Agilex Mailbox Client Intel FPGA IP Core Design Example (QSPI flash Access and Remote System Update)

# 1.1. Device Family Support

The following lists the device support level definitions for Intel FPGA IPs:

- Advance support The IP is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- **Preliminary support** The IP is verified with preliminary timing models for this device family. The IP meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- **Final support** The IP is verified with final timing models for this device family. The IP meets all functional and timing requirements for the device family and can be used in production designs.

#### **Table 1.** Device Family Support

| Device Family    | Support |

|------------------|---------|

| Intel Stratix 10 | Final   |

| Intel Agilex     | Final   |

#### **Related Information**

- Mailbox Client Intel FPGA IP Release Notes

- Mailbox Client with Avalon Streaming Interface Intel FPGA IP Release Notes

# 1.2. Parameters

| Parameter Name                                      | Value                               | Description                                                                                                                                                                                  |  |  |  |  |

|-----------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mailbox Client Parameters                           |                                     |                                                                                                                                                                                              |  |  |  |  |

| Command FIFO Depth 1 - 1024                         |                                     | Depth of the command FIFO                                                                                                                                                                    |  |  |  |  |

| Response FIFO Depth                                 | 1 - 1024 Depth of the response FIFO |                                                                                                                                                                                              |  |  |  |  |

| Crypto Memory Timeout 0x00002710 Value - 0x7FFFFFFF |                                     | The timeout for the cryptographic service. Specify value within the minimum and maximum timeout value.  • 0x7FFFFFFF: Maximum memory timeout value  • 0x002710: Minimum memory timeout value |  |  |  |  |

| Memory Target Parameters                            |                                     |                                                                                                                                                                                              |  |  |  |  |

| HAS_OFFLOAD <sup>(2)</sup> 0, 1                     |                                     | Enables the cryptographic offloading feature. When set, enables the crypto AXI target interface.                                                                                             |  |  |  |  |

<sup>(2)</sup> This feature is only available for Intel Agilex devices.

# 1.3. Mailbox Client Intel FPGA Core Interface Signals

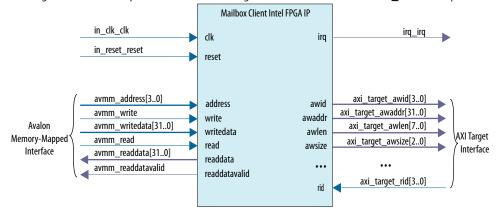

The host communicates with the Mailbox Client Intel FPGA over its Avalon Memory-Mapped (Avalon MM) interface. For Intel Agilex devices, the AXI target interface is available if you enabled **HAS\_OFFLOAD** parameter.

Through the AXI interface, the crypto service has access to the lowest 1GB of memory, with a maximum data size of 512 MB per each read and write operation.

The following figure illustrates the Mailbox Client Intel FPGA IP interfaces.

#### Figure 2. Mailbox Client Intel FPGA IP Interfaces

The AXI target interface is only available in the Intel Agilex devices with enabled HAS\_OFFLOAD parameter.

Note: For information about the AXI target interface, refer to Table 4 on page 7.

#### **Related Information**

- Intel Stratix 10 Configuration User Guide

For information about including the Reset Release IP in your design.

- Intel Agilex Configuration User Guide

For information about including the Reset Release IP in your design.

#### 1.3.1. Clock and Reset Interfaces

Table 2. Clock and Reset Interfaces

| Signal Role | Width | Direction | Description                                                                                                                                                                                                                                                                                                                                    |

|-------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk         | 1     | Input     | Input clock to clock the IP. The maximum frequency is 250 MHz.                                                                                                                                                                                                                                                                                 |

| reset       | 1     | Input     | Reset that resets the IP.                                                                                                                                                                                                                                                                                                                      |

|             |       |           | To reset the IP, assert the reset signal high for at least 2 clk cycles.                                                                                                                                                                                                                                                                       |

|             |       |           | To ensure the Mailbox Client Intel FPGA IP functions correctly when the device enters user mode, your design must include the Reset Release Intel FPGA IP to hold the reset until the FPGA fabric entered user mode. Intel recommends using a reset synchronizer when connecting the user reset or output of the Reset Release IP to the reset |

|             | '     | 1         | continued                                                                                                                                                                                                                                                                                                                                      |

| Signal Role | Width | Direction | Description                                                                                                                                                                                                                                                                                                                |

|-------------|-------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |       |           | port of the Mailbox Client IP. To implement the reset synchronizer, use the Reset Bridge Intel FPGA IP available in the Platform Designer.                                                                                                                                                                                 |

|             |       |           | Note: For IP instantiation and connection guidelines in the Platform Designer, refer to the Required Communication and Host Components for the Remote System Update Design Example figure in the Intel Stratix 10 Configuration User Guide.  Note: For IP instantiation guidelines, refer to the Configuration User Guide. |

| irq         | 1     | Output    | Interrupt signal. Drives the value of the AND of the interrupt status and interrupt enable registers.                                                                                                                                                                                                                      |

# 1.3.2. Avalon Memory-Mapped Interface

The Avalon MM interface is standard memory-mapped interface. For detailed definitions of these signals, refer to the *Avalon Memory-Mapped Interfaces* chapter in the *Avalon Interface Specifications*.

**Table 3.** Avalon Memory-Mapped Interface

| Signal Role        | Width | Direction | Description                |

|--------------------|-------|-----------|----------------------------|

| avmm_address       | 4     | Input     | Avalon MM address.         |

| avmm_write         | 1     | Input     | Avalon MM write request.   |

| avmm_read          | 1     | Input     | Avalon MM read request.    |

| avmm_writedata     | 32    | Input     | Avalon MM write data bus.  |

| avmm_readdata      | 32    | Output    | Avalon MM read data bus.   |

| avmm_readdatavalid | 1     | Output    | Avalon MM read data valid. |

#### **Related Information**

- Avalon Interface Specifications

- Avalon Memory-Mapped Interface Signal Roles

# 1.3.3. AXI Target Interface

The AXI target interface is standard advanced extensible interface (AXI). This interface is accessible when you enabled the crypto services features. The crypto services features are available for the Intel Agilex devices.

#### **Table 4. AXI Target Interface**

The table displays command, response, and urgent interface signals.

| Signal Role                              | Width | Direction | Description           |  |  |  |

|------------------------------------------|-------|-----------|-----------------------|--|--|--|

| AXI Target Clock and Reset Signals       |       |           |                       |  |  |  |

| axi_in_clk                               | 1     | Input     | AXI* interface clock. |  |  |  |

| axi_in_reset                             | 1     | Input     | AXI interface reset.  |  |  |  |

| AXI Target Write Address Channel Signals |       |           |                       |  |  |  |

|                                          |       |           | continued             |  |  |  |

| Signal Role                          | Width             | Direction | Description                                                                                                                        |  |  |

|--------------------------------------|-------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| axi_target_awid                      | 4                 | Output    | AXI identification tag for write transaction.                                                                                      |  |  |

| axi_target_awaddr                    | 32                | Output    | AXI address of the first transfer in a write transaction.                                                                          |  |  |

| axi_target_awlen                     | 8                 | Output    | AXI length. Identifies the exact number of data transfers in a write transaction.                                                  |  |  |

| axi_target_awsize                    | 3                 | Output    | AXI size. Identifies the number of bytes in each data transfer in a write transaction.                                             |  |  |

| axi_target_awburst                   | 2                 | Output    | AXI burst type. Indicates how address changes between each transfer in a write transaction.                                        |  |  |

| axi_target_awlock                    | 1                 | Output    | Provides information about the atomic characteristics of a AXI write transaction.                                                  |  |  |

| axi_target_awcache                   | 4                 | Output    | Indicates how a write transaction is required to progress through a system.                                                        |  |  |

| axi_target_awprot                    | 3                 | Output    | Protection attributes of a write transaction: privilege, security level, and access type.                                          |  |  |

| axi_target_awqos                     | 4                 | Output    | Quality of Service identifier for a write transaction                                                                              |  |  |

| axi_target_awvalid                   | 1                 | Output    | AXI valid signal for a write transaction. Indicates that the write address channel signals are valid.                              |  |  |

| axi_target_awuser                    | 5                 | Output    | User-defined extension for the write address channel.                                                                              |  |  |

| axi_target_awready                   | 1                 | Input     | AXI ready signal for write address. Indicates that a transfer on the write address channel can be accepted.                        |  |  |

| AXI Target Write Data Cha            | nnel Signals      |           |                                                                                                                                    |  |  |

| axi_target_wdata                     | 64                | Output    | AXI write data.                                                                                                                    |  |  |

| axi_target_wlast                     | 1                 | Output    | AXI write transaction last data transfer. Indicates whether the current transfer is the last data transfer in a write transaction. |  |  |

| axi_target_wready                    | 1                 | Input     | AXI ready signal for write data. Indicates that a write data channel transfer can be accepted.                                     |  |  |

| axi_target_wvalid                    | 1                 | Output    | AXI valid signal for write data. Indicates that a write data channel signals are valid.                                            |  |  |

| axi_target_wstrb                     | 8                 | Output    | AXI write strobes. Indicates the byte lane holding valid data.                                                                     |  |  |

| AXI Target Write Response            | e Channel Signals |           |                                                                                                                                    |  |  |

| axi_target_bid                       | 4                 | Input     | AXI identification tag for write response.                                                                                         |  |  |

| axi_target_bresp                     | 2                 | Input     | AXI write response. Indicates write response status.                                                                               |  |  |

| axi_target_bvalid                    | 1                 | Input     | AXI valid signal for write response. Indicates that the write response channel signals are valid.                                  |  |  |

| axi_target_bready                    | 1                 | Output    | AXI ready signal for write response. Indicates that the write response channel transfer can be accepted.                           |  |  |

| AXI Target Read Data Channel Signals |                   |           |                                                                                                                                    |  |  |

| continued                            |                   |           |                                                                                                                                    |  |  |

| Signal Role                 | Width          | Direction | Description                                                                                                                      |

|-----------------------------|----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| axi_target_rdata            | 64             | Input     | AXI read data.                                                                                                                   |

| axi_target_rresp            | 2              | Input     | AXI read response. Indicates read transfer status.                                                                               |

| axi_target_rlast            | 1              | Input     | AXI read transaction last data transfer. Indicates whether the current transfer is the last data transfer in a read transaction. |

| axi_target_rready           | 1              | Output    | AXI read data channel ready signal. Indicates that a transfer on the read data channel can be accepted.                          |

| axi_target_rvalid           | 1              | Input     | AXI valid signal for read data channel. Indicates that the read data channel signals are valid.                                  |

| axi_target_rid              | 4              | Input     | AXI identification tag for read data and response.                                                                               |

| AXI Target Read Response Cl | hannel Signals |           |                                                                                                                                  |

| axi_target_arid             | 4              | Output    | AXI identification tag for read address transaction.                                                                             |

| axi_target_araddr           | 32             | Output    | AXI address of the first transfer in a read transaction.                                                                         |

| axi_target_arlen            | 8              | Output    | AXI length. Identifies the number of data transfers during the read transaction.                                                 |

| axi_target_arsize           | 3              | Output    | AXI size.  Identifies the number of bytes in each data transfer in a read transaction.                                           |

| axi_target_arburst          | 2              | Output    | AXI burst type. Indicates how address changes between each transfer in a read transaction.                                       |

| axi_target_arlock           | 1              | Output    | Provides information about the atomic characteristics of a AXI read transaction.                                                 |

| axi_target_arcache          | 4              | Output    | Indicates how a read transaction is required to progress through a system.                                                       |

| axi_target_arprot           | 3              | Output    | Protection attributes of a read transaction: privilege, security level, and access type.                                         |

| axi_target_arqos            | 4              | Output    | Quality of Service identifier for a read transaction.                                                                            |

| axi_target_arvalid          | 1              | Output    | AXI valid signal for read transaction. Indicates that the read address channel signals are valid.                                |

| axi_target_aruser           | 5              | Output    | AXI user-defined extension for the read address channel.                                                                         |

| axi_target_arready          | 1              | Input     | AXI read address channel ready signal. Indicates that a transfer on the read address channel can be accepted.                    |

# 1.4. Mailbox Client Intel FPGA IP Avalon MM Memory Map

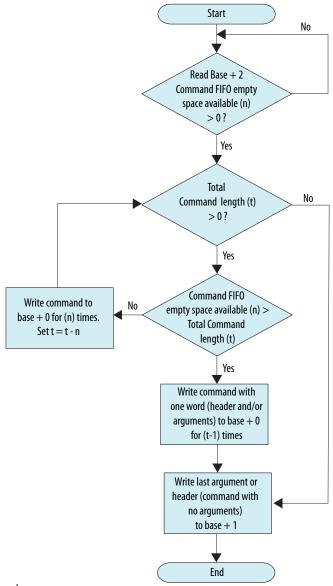

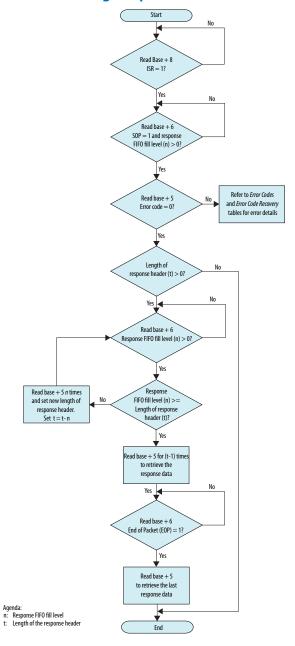

# Table 5. Avalon MM Memory Map

| Offset (word)    | R/W | 31                      | 30:2 | 1 | 0         |  |

|------------------|-----|-------------------------|------|---|-----------|--|

| Base address + 0 | W   | Command                 |      |   |           |  |

| Base address + 1 | W   | Command last word (eop) |      |   |           |  |

|                  |     |                         |      |   | continued |  |

| Offset (word)     | R/W | 31 30:2                          |          | 1 | 0 |                                  |  |  |     |

|-------------------|-----|----------------------------------|----------|---|---|----------------------------------|--|--|-----|

| Base address + 2  | R   | Command FIFO empty space         |          |   |   |                                  |  |  |     |

| Base address + 3  | N/A |                                  | Reserved |   |   |                                  |  |  |     |

| Base address + 4  | N/A |                                  | Reserved |   |   |                                  |  |  |     |

| Base address + 5  | R   | Response data                    |          |   |   |                                  |  |  |     |

| Base address + 6  | R   | Response FIFO fill level EOP SOP |          |   |   | Response FIFO fill level EOP SOP |  |  | SOP |

| Base address + 7  | R/W | Interrupt enable register (IER)  |          |   |   |                                  |  |  |     |

| Base address + 8  | R   | Interrupt status register (ISR)  |          |   |   |                                  |  |  |     |

| Base address + 9  | R/W | Timer 1 Timer 1 period enable    |          |   |   |                                  |  |  |     |

| Base address + 10 | R/W | Timer 2 Timer 2 period enable    |          |   |   |                                  |  |  |     |

# 1.4.1. Interrupt Enable Register

Use the Interrupt Enable register to enable or disable interrupts.

# **Table 6.** Interrupt Enable Register

Note:

These enable bits do not prevent the value of interrupt status bit from showing up in ISR, they only prevent the interrupt status bit from causing interrupt output assertion.

| Bit  | Fields                                               | Access | Default<br>Value | Description                                                                                                                                                                                                        |  |  |

|------|------------------------------------------------------|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31:8 | Reserved                                             |        |                  |                                                                                                                                                                                                                    |  |  |

| 7    | EN_CRYPTO_ERROR_<br>RECOVERY_PROGRESS <sup>(3)</sup> | R/W    | 0x0              | The enable interrupt bit for crypto service error recovery progress status.  1: Enable the crypto service error recovery progress interrupt  0: Disable the crypto service error recovery progress interrupt       |  |  |

| 6    | EN_CRYPTO_<br>MEMORY_TIMEOUT <sup>(3)</sup>          | R/W    | 0x0              | The enable interrupt bit for the crypto service client-side memory timeout.  1: Enable the crypto service client-side memory timeout interrupt  0: Disable the crypto service client-side memory timeout interrupt |  |  |

| 5    | EN_BACKPRESSURE_TIMEOUT                              | R/W    | 0x0              | The enable interrupt bit for SDM backpressure timeout.  1: Enable the SDM backpressure timeout interrupt  0: Disable the SDM backpressure timeout interrupt                                                        |  |  |

| 4    | EN_EOP_TIMEOUT                                       | R/W    | 0x0              | The enable interrupt bit for EN_EOP_TIMEOUT.  1: Enable the EOP timeout interrupt  0: disable the EOP timeout interrupt  continued                                                                                 |  |  |

<sup>(3)</sup> The crypto service feature is only available for Intel Agilex devices.

| Bit | Fields               | Access | Default<br>Value | Description                                                                                                                      |

|-----|----------------------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 3   | EN_COMMAND_INVALID   | R/W    | 0x0              | The enable interrupt bit for COMMAND_INVALID.  1: Enable the command invalid interrupt  0: Disable the command invalid interrupt |

| 2   | Reserved             | _      | _                | Reserved.                                                                                                                        |

| 1   | EN_CMD_FIFO_NOT_FULL | R/W    | 0x0              | The enable for the command FIFO full interrupt.  1: Enable the FIFO full interrupt  0: Disable the FIFO full interrupt           |

| 0   | EN_DATA_VALID        | R/W    | 0x0              | The enable for the data valid interrupt.  1: Enable the data valid interrupt  0: Disable the data valid interrupt                |

# 1.4.2. Interrupt Status Register

Use the interrupt\_status register to monitor the status of the FIFO and identify invalid commands.

Your logic can poll the error bits of the interrupt\_status register. Or, you can configure the EN\_COMMAND\_INVALID bit of the interrupt enable register to interrupt when an error occurs.

When an error occurs, the Mailbox Client IP clears all pending responses. Your logic should not expect any response from Mailbox Client IP after an error occurs. Your logic must assert reset for a minimum of 10 clock cycles to reset the Mailbox Client IP.

**Table 7.** Interrupt Status Register

| Bit  | Fields                                            | Access | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|------|---------------------------------------------------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31:8 | Reserved                                          |        |                  |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 7    | CRYPTO_ERROR_RECOVERY_<br>PROGRESS <sup>(4)</sup> | R      | 0x0              | Error recovery flow progress interrupt for the cryptographic (crypto) flow.  1: Indicates that the crypto error recovery is in progress. You may use this bit to report the progress of the soft IP error recovery. While in recovery, the SDM is unable to perform read/write operations from the memory.  0: Indicates the crypto error recovery is completed.                                |  |  |

| 6    | CRYPTO_MEMORY_TIMEOUT(4)                          | R      | 0x0              | Cryptographic services timer for memory target interrupt. Timeout value is set by <b>Crypto Memory Timeout Value</b> parameter in the Mailbox Client IP.  1: Indicates that the timeout occurred in either the memory target write or read path in the AXI transaction. You must reset the Mailbox Client IP (in_reset and axi_in_reset) and your memory target device.  0: No timeout occurred |  |  |

| 5    | BACKPRESSURE_TIMEOUT                              | R      | 0x0              | SDM backpressure timer interrupt.                                                                                                                                                                                                                                                                                                                                                               |  |  |

|      |                                                   |        |                  | continued                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

<sup>(4)</sup> The crypto service feature is only available for Intel Agilex devices.

| Bit | Fields            | Access | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                   |        |                  | 1: The SDM backpressure timer has timeout. Indicates that a fatal error occurred in SDM. You must reset the device. To reset, reconfigure or power cycle the device.     0: The SDM backpressure timer has not timeout.                                                                                                                                                |

| 4   | EOP_TIMEOUT       | R      | 0×0              | End of Packet (EOP) timer interrupt.  1: Indicates that the EOP timer has timeout. You must reset the Mailbox Client IP.  0: The EOP timer has not timeout. Indicates that the Mailbox Client IP did not receive the full command with EOP due to:  Mailbox did not receive the last argument with EOP.  Mailbox already received all arguments without the EOP in it. |

| 3   | COMMAND_INVALID   | R      | 0x0              | Invalid command interrupt. Indicates a mismatch between the command length specified in the command header and the number of words sent. Hardware clears this bit.  1: Indicates that the command is invalid. You must reset the Mailbox client.  0: The command is valid.                                                                                             |

| 2   | Reserved          | _      | _                | Reserved.                                                                                                                                                                                                                                                                                                                                                              |

| 1   | CMD_FIFO_NOT_FULL | R      | 0x0              | Command FIFO is not full interrupt.  1: Indicates command FIFO is not full. The client can drive data.  0: Indicates the FIFO is full.  The FIFO automatically clears this bit. You do not need to clear this bit manually.                                                                                                                                            |

| 0   | DATA_VALID        | R      | 0×0              | Data valid interrupt.  1: Indicates that valid data is available. The master can read.  0: Indicates the FIFO is empty. The FIFO automatically clears this bit. You do not need to clear this bit manually.                                                                                                                                                            |

# 1.4.3. Timer Registers

Use timer registers to monitor and address incomplete transactions between host and the Mailbox Client IP.

#### **Incomplete Command Transaction Error**

When a host fails to send the last command word to the Mailbox Client IP or the system stops sending data before the last word, the incomplete command transaction error occurs. Timer 1 allows you to set a specific transaction time period to complete each command. When the timer's timeout occurs, ISR[4] is set to indicate the error. To recover the system, you must reset the Mailbox Client IP.

Table 8. Timer 1 Register

| Bit  | Fields         | Access | Default<br>Value <sup>(5)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------------|--------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31   | Timer 1 enable | R/W    | 0x0                             | Timer 1 period enable bit. The bit is enabled once.  1: Enable timer 1  0: Disable timer 1  If a time out occurs, the timer 1 register becomes disabled. You must apply the Mailbox Client Intel FPGA IP reset.  To start the timer 1, you must re-enable it again.                                                                                                                                                                                                                                                                                                   |

| 30:0 | Timer 1 period | R/W    | 0x7FF_FFFF                      | When enabled, the timer counts down the specified period as the maximum number of clock cycles the system has not received a valid command.  The timer 1 starts the count down as soon as the transaction writes the first data word into the Command FIFO (base address +0).  The timer resets when the Mailbox Client Intel FPGA IP receives complete command transaction, indicated by successfully writing the last word into the command last word register (base address +1). When the timer 1 resets itself, it returns to its default or other defined value. |

#### **SDM Backpressure Error**

SDM typically backpressures while it processes commands and sends responses. The SDM backpressure error occurs when SDM backpressures for some time period not allowing you to write any data into the Mailbox fabric and SDM. The timer 2, by setting a specific wait time, allows you detect the long wait and take steps to recover your system. When a timer's timeout occurs, <code>ISR[5]</code> is set to indicate an error. Note that this is a fatal error received from SDM, possibly indicating a system error. Resetting the Mailbox Client won't recover the system.

**Table 9.** Timer 2 Register

| Bit  | Fields         | Access | Default<br>Value <sup>(6)</sup> | Description                                                                                                                                                                                                                                                          |

|------|----------------|--------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31   | Timer 2 enable | R/W    | 0x0                             | Timer 2 period enable bit. The bits is enabled once.  1: Enable timer 2  0: Disable timer 2  If a time out occurs, the timer 2 register becomes disabled. You must apply the Mailbox Client Intel FPGA IP reset.  To start the timer 2, you must re-enable it again. |

| 30:0 | Timer 2 period | R/W    | 0x7FF_FFFF                      | When enabled, the timer counts down the specified period as the maximum number of clock cycles the system has not asserted ready high signal. The SDM backpressures commands sent by host to the Mailbox Client Intel FPGA IP.                                       |

<sup>(5)</sup> Resetting the Mailbox Client IP resets the timer 1 register to the default value.

<sup>(6)</sup> Resetting the Mailbox Client IP resets the timer 2 register to the default value.

# 1.5. Commands and Responses

The host controller communicates with the SDM using command and response packets via the Mailbox Client Intel FPGA IP.

The first word of the command and response packets is a header that provides basic information about the command or response.

#### Figure 3. Command and Response Header Format

| 31 30 29 28 | 27 26 25 | 24 | 23 | 22 2 | 1 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6    | 5     | 4     | 3   | 2 | 1 | 0 |

|-------------|----------|----|----|------|------|----|----|-----|----|----|----|----|----|----|----|---|---|-----|------|-------|-------|-----|---|---|---|

| Reserved    | ID       |    | 0  |      |      |    | L  | eng | th |    |    |    |    | 0  |    |   | C | omn | nano | d/Eri | ror C | ode |   |   |   |

Note:

The LENGTH field in the command header must match the command length of corresponding command.

The following table describes the fields of the header command.

Table 10. Command and Response Header Description

| Header                     | Bit     | Description                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Reserved                   | [31:28] | Reserved.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ID                         | [27:24] | The command ID. The response header returns the ID specified in the command header. Refer to <i>Operation Commands</i> for command descriptions.                                                                                                                                                                                                            |  |  |  |  |  |

| 0                          | [23]    | Reserved.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| LENGTH                     | [22:12] | Number of words of arguments following the header. The IP responds with an error if a wrong number of words of arguments is entered for a given command.                                                                                                                                                                                                    |  |  |  |  |  |

| Reserved                   | [11]    | Reserved. Must be set to 0.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Command Code/Error<br>Code | [10:0]  | Command Code specifies the command. The Error Code indicates whether the command succeeded or failed.  In the command header, these bits represent command code. In the response header, these bits represent error code. If the command succeeds, the Error Code is 0. If the command fails, refer to the error codes defined in the Error Code Responses. |  |  |  |  |  |

# 1.5.1. Operation Commands

# **Resetting Quad SPI Flash**

Important:

For Intel Stratix 10 devices, do not reset the quad SPI flash when used as the configuration device and data storage device with FPGA. Resetting the quad SPI flash during the FPGA configuration and reconfiguration, or in the QSPI's READ/WRITE/ERASE operations, causes undefined behavior for quad SPI flash and the FPGA. To recover from the unresponsive behavior, you must power cycle your device. To reset the quad SPI flash via the external host, you must first complete the FPGA configuration and reconfiguration, or a quad SPI operation, and only then toggle the reset. The quad SPI operation is complete when the exclusive access to the quad SPI flash is closed by issuing the QSPI\_CLOSE command via the Mailbox Client Intel FPGA IP.

Important:

For Intel Agilex devices, you must connect the serial flash or quad SPI flash reset pin to the AS\_nRST pin. The SDM must fully control the QSPI reset. Do not connect the quad SPI reset pin to any external host.

**Table 11.** Command List and Description

| Command             | Code<br>(Hex) | Command<br>Length <sup>(7)</sup> | Response<br>Length <sup>(7)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|---------------|----------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOOP                | 0             | 0                                | 0                                 | Sends an OK status response.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GET_IDCODE          | 10            | 0                                | 1                                 | The response contains one argument which is the ${\tt JTAG}$ ${\tt IDCODE}$ for the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GET_CHIPID          | 12            | 0                                | 2                                 | The response contains 64-bit CHIPID value with the least significant word first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GET_USERCODE        | 13            | 0                                | 1                                 | The response contains one argument which is the 32-bit JTAG USERCODE that the configuration bitstream writes to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GET_VOLTAGE         | 18            | 1                                | 1                                 | The GET_VOLTAGE command has a single argument which is a bitmask specifying the channels to read. Bit 0 specifies channel 0, bit 1 specifies channel 1, and so on.  The response includes a one-word argument for each bit set in the bitmask. The voltage returned is an unsigned fixed-point number with 16 bits below the binary point. For example, a voltage of 0.75V returns 0x0000C000. <sup>(8)</sup> (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GET_<br>TEMPERATURE | 19            | 1                                | n <sup>(10)</sup>                 | The GET_TEMPERATURE command returns the temperature or temperatures of the core fabric or transceiver channel locations you specify.  For Intel Stratix 10 devices, use the sensor_req argument to specify the locations. The sensor_req includes the following fields:  Bits[31:9]: Reserved.  Bits[8:0]: Sensor mask. Specifies the TSD location.  The channels return the temperatures for the following locations:  Channel 0: Samples the temperature from the core fabric.  Channels 1- 6: Samples the temperature from the specified transceiver tile.  Channels 7-8: Samples the temperature from the high-bandwidth DRAM memory (HBM2) stacks.  For Intel Agilex devices, use the sensor_req argument to specify the locations. The sensor_req includes the following fields:  Bits[31:28]: Reserved.  Bits[27:16]: Sensor Location. Specifies the TSD location.  Bits[15:0]: Sensor mask. Specifies the sensors to read for the sensor location specified. The response contains one word for each temperature requested. If omitted, the command reads channel 0. The least significant bit (Isb) corresponds to channel 15. |

|                     |               |                                  |                                   | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

<sup>(7)</sup> This number does not include the command or response header.

<sup>(10)</sup> Index n depends on the number of sensor masks.

<sup>(8)</sup> Refer to *Intel Stratix 10 Analog to Digital Converter User Guide* for more information about reading voltage sensors on Intel Stratix 10 devices.

<sup>(9)</sup> Refer to *Intel Agilex Power Management User Guide for more information* about temperature sensor channels and locations.

| Command              | Code<br>(Hex) | Command<br>Length <sup>(7)</sup> | Response<br>Length <sup>(7)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | Description                                                                                                                       |  |  |  |  |

|----------------------|---------------|----------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                      |               |                                  |                                   | the binary                                                                                                                                                                                                                                                                                                                                                                                                                               | point. For examp                        | s a signed fixed value with 8 bits below<br>ble, a temperature of 10°C returns<br>ture -1.5°C returns 0xFFFFFE80.                 |  |  |  |  |

|                      |               |                                  |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                          | ode which is any                        | invalid Location, the command returns<br>value in the range 0x80000000                                                            |  |  |  |  |

|                      |               |                                  |                                   | For Intel Stratix 10 devices, refer to the <i>Temperature Sensor</i> Channels and Locations in the Intel Stratix 10 Analog to Digital  Converter User Guide for more information about sensor locations.                                                                                                                                                                                                                                 |                                         |                                                                                                                                   |  |  |  |  |

|                      |               |                                  |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | er to the <i>Intel Agilex Power Management</i><br>lation about local build-in temperature                                         |  |  |  |  |

| RSU_IMAGE_<br>UPDATE | 5C            | 2                                | 0                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                          | econfiguration fro<br>an application im | m the data source that can be either the lage.                                                                                    |  |  |  |  |

| 0.22                 |               |                                  |                                   | This command takes an optional 64-bit argument that specifies the reconfiguration data address in the flash. When sending the argument to the IP, you first send bits [31:0] followed by bits [63:32]. If you do not provide this argument its value is assumed to be 0.                                                                                                                                                                 |                                         |                                                                                                                                   |  |  |  |  |

|                      |               |                                  |                                   | • Bit [31                                                                                                                                                                                                                                                                                                                                                                                                                                | :0]: The start add                      | dress of an application image.                                                                                                    |  |  |  |  |

|                      |               |                                  |                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                        | :32]: Reserved (                        | •                                                                                                                                 |  |  |  |  |

|                      |               |                                  |                                   | Once the device processes this command, it returns the response header to response FIFO before it proceeds to reconfigure the device. Ensure the host PC or host controller stops servicing other interrupts and focuses on reading the response header data to indicate the command completed successfully. Otherwise, the host PC or host controller may not be able to receive the response once the reconfiguration process started. |                                         |                                                                                                                                   |  |  |  |  |

|                      |               |                                  |                                   | Once the device proceeds with reconfiguration, the link between the external host and FPGA is lost. If you use PCIe in your design, you need to re-enumerate the PCIe link.                                                                                                                                                                                                                                                              |                                         |                                                                                                                                   |  |  |  |  |

|                      |               |                                  |                                   | Important                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | quad SPI, you must follow instructions etting Quad SPI Flash on page 14.                                                          |  |  |  |  |

| RSU_GET_SPT          | 5A            | 0                                | 4                                 | partition to                                                                                                                                                                                                                                                                                                                                                                                                                             | ables that the RS                       | e quad SPI flash location for the two sub-<br>U uses: SPT0 and SPT1.<br>ins the following information:                            |  |  |  |  |

|                      |               |                                  |                                   | Word                                                                                                                                                                                                                                                                                                                                                                                                                                     | Name                                    | Description                                                                                                                       |  |  |  |  |

|                      |               |                                  |                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPT0[63:32]                             |                                                                                                                                   |  |  |  |  |

|                      |               |                                  |                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPT0[31:0]                              | SPT0 address in quad SPI flash.                                                                                                   |  |  |  |  |

|                      |               |                                  |                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPT1[63:32]                             |                                                                                                                                   |  |  |  |  |

|                      |               |                                  |                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPT1[31:0]                              | SPT1 address in quad SPI flash.                                                                                                   |  |  |  |  |

| CONFIG_<br>STATUS    | 4             | 0                                | 6                                 | Reports th                                                                                                                                                                                                                                                                                                                                                                                                                               | e status of the la<br>to check the conf | <br>st reconfiguration. You can use this<br>figuration status during and after<br>e contains the following information:           |  |  |  |  |

|                      |               |                                  |                                   | Word                                                                                                                                                                                                                                                                                                                                                                                                                                     | Summary                                 | Description                                                                                                                       |  |  |  |  |

|                      |               |                                  |                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                        | State                                   | Describes the most recent configuration related error. Returns 0 when there are no configuration errors.                          |  |  |  |  |