**Speech Synthesizers**

Li,

Linear Products

# Linear Products Data Book Guide

| Data Book                                                                                        | Contents                                                                                                                                                                                                                                     | Document No.        |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| <ul> <li>Linear Circuits Vol 1<br/>Amplifiers, Comparators,<br/>and Special Functions</li> </ul> | Operational Amplifiers<br>Voltage Comparators<br>Video Amplifiers<br>Hall-Effect Devices<br>Timers and Current Mirrors<br>Magnetic-Memory Interface<br>Frequency-to-Voltage Converters<br>Sonar Ranging Circuits/Modules<br>Sound Generators | SLYD003<br>1989     |

| <ul> <li>Linear Circuits Vol 2<br/>Data Acquisition<br/>and Conversion</li> </ul>                | A/D and D/A Converters<br>DSP Analog Interface<br>Analog Switches and Multiplexers<br>Switched-Capacitor Filters                                                                                                                             | SLYD004<br>1989     |

| <ul> <li>Linear Circuits Vol 3<br/>Voltage Regulators and<br/>Supervisors</li> </ul>             | Supervisor Functions<br>Series-Pass Voltage Regulators<br>Shunt Regulators<br>Voltage References<br>DC-to-DC Converters<br>PWM Controllers                                                                                                   | SLYD005<br>1989     |

| <ul> <li>Telecommunications<br/>Circuits</li> </ul>                                              | Equipment Line Interfaces<br>Subscriber Line Interfaces<br>Modems and Receivers/Transmitters<br>Ringers, Detectors, Tone Encoders<br>PCM Interface<br>Transient Suppressors                                                                  | SCTD001A<br>1988/89 |

| <ul> <li>Optoelectronics and<br/>Image Sensors</li> </ul>                                        | Optocouplers<br>CCD Image Sensors and Support<br>Phototransistors<br>IR-Emitting Diodes<br>Hybrid Displays                                                                                                                                   | SOYD002A<br>1990    |

| <ul> <li>Interface Circuits</li> </ul>                                                           | High-Voltage (Display) Drivers<br>High-Power (Peripheral/Motor) Drivers<br>Line Drivers, Receivers, Transceivers<br>EIA RS-232, RS-422, RS-423, RS-485<br>IBM 360/370, IEEE 802.3, CCITT<br>Military Memory Interface                        | SLYD002<br>1987     |

| • Speech System Manuals                                                                          | TSP50C4X Family                                                                                                                                                                                                                              | SPSS010<br>1990     |

November 1989

# TSP50C4X Family Speech Synthesizers Design Manual

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

> Copyright © 1984, 1990 by Texas Instruments Incorporated Revised 1990

# Contents

| Section | Title                          | Page |

|---------|--------------------------------|------|

| 1       | Introduction                   | 1-1  |

| 1.1     | Applications                   | 1-1  |

| 1.2     | Description                    | 1-2  |

| 1.3     | Features                       | 1-3  |

| 1.4     | Device Comparison              | 1-3  |

| 1.5     | Masked Options                 | 1-3  |

| 1.6     | Pin Assignment and Description | 1-5  |

| 1.7     | Introduction to LPC            | 1-11 |

| 1.7.1   | The Vocal Tract                | 1-11 |

| 1.7.2   | The LPC Model                  | 1-11 |

| 1.7.3   | LPC Data Compression           | 1-12 |

|         |                                |      |

| 2       | TSP50C4X Architecture          | 2-1  |

| 2.1     | ROM                            | 2-2  |

| 2.2     | Program Counter                | 2-3  |

| 2.3     | Program Counter Stack          | 2-3  |

| 2.4     | RAM                            | 2-3  |

| 2.5     | ALU                            | 2-4  |

| 2.6     | A Register                     | 2-4  |

| 2.7     | X Register                     | 2-4  |

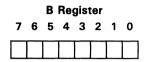

| 2.8     | B Register                     | 2-5  |

| 2.9     | Status Flag                    | 2-5  |

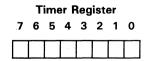

| 2.10    | Timer Register                 | 2-5  |

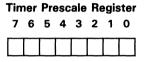

| 2.11    | Timer Prescale Register        | 2-6  |

| 2.12    | Pitch Register                 | 2-6  |

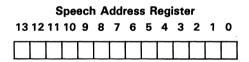

| 2.13    | Speech Address Register        | 2-6  |

| 2.14    | Parallel-to-Serial Register    | 2-7  |

| 2.15    | Interface Logic                | 2-7  |

| 2.16    | Port A (Master Option)         | 2-7  |

| 2.17    | Port A (Slave Option)          | 2-8  |

| 2.18    | Port B                         | 2-8  |

| 2.19    | Port C                         | 2-8  |

| 2.20    | Port D                         | 2-8  |

| 2.21    | IRT Pin                        | 2-9  |

| Section        | Title                                            | Page        |

|----------------|--------------------------------------------------|-------------|

| 2.22<br>2.22.1 | Speech Synthesizer Use of RAM by the Synthesizer | 2-9<br>2-10 |

| 2.22.2         | Context Switch                                   | 2-12        |

| 2.22.3         |                                                  | 2-12        |

| 2.22.4         | Timing Requirements                              | 2-12        |

| 2.22.5         | Voicing Control                                  | 2-15        |

| 2.22.6         | Frame Length Control                             | 2-15        |

| 2.22.7         | Digital-to-Analog Converter and Output Buffer    | 2-15        |

| 3              | Electrical Specifications                        | 3-1         |

| 3.1            | Absolute Maximum Ratings Over Free-Air           |             |

|                | Temperature Range                                | 3-1         |

| 3.2            | Recommended Operating Characteristics-DC         | 3-1         |

| 3.3            | Recommended Operating Characteristics-AC         | 3-1         |

| 3.4            | Electrical Characteristics                       | 3-2         |

| 3.5            | Oscillator                                       | 3-2         |

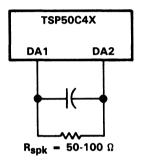

| 3.6            | Direct Speaker Driver                            | 3-3         |

| 4              | TSP50C4X Assembler                               | 4-1         |

| 4.1            | Source Statement Format                          | 4-1         |

| 4.1.1          | Label Field                                      | 4-2         |

| 4.1.2          | Command Field                                    | 4-2         |

| 4.1.3          | Operand Field                                    | 4-2         |

| 4.1.4          | Comment Field                                    | 4-2         |

| 4.2            | Constants                                        | 4-2         |

| 4.2.1          | Decimal Integer Constants                        | 4-3         |

| 4.2.2          | Binary Integer Constants                         | 4-3         |

| 4.2.3          | Hexadecimal Integer Constants                    | 4-3         |

| 4.2.4          | Character Constants                              | 4-3         |

| 4.2.5          | Assembly-Time Constants                          | 4-4         |

| 4.3            | Symbols                                          | 4-4         |

| 4.3.1          | Predefined Symbol "\$"                           | 4-4         |

| 4.3.2          | Character String                                 | 4-5         |

| 4.4            | Expressions                                      | 4-5         |

| 4.4.1          | Arithmetic Operators in Expressions              | 4-5         |

| 4.4.2          | Parentheses in Expressions                       | 4-5         |

| 4.5            | Invoking the Assembler                           | 4-6         |

| 4.5.1          | Assembler Input and Output Files                 | 4-6         |

| 4.5.2          | Assembly Source File                             | 4-6         |

| Section  | Title                           | Page |

|----------|---------------------------------|------|

| 4.5.3    | Assembly Binary Object File     | 4-6  |

| 4.5.4    | Assembly Tagged Object File     | 4-7  |

| 4.5.5    | Assembly Listing File           | 4-7  |

| 4.6 Op   | tions and Switches              | 4-7  |

| 4.6.1    | Command Line Options            | 4-7  |

| 4.6.1.1  | BYTE Unlist Option              | 4-8  |

| 4.6.1.2  | DATA Unlist Option              | 4-8  |

| 4.6.1.3  | XREF Unlist Option              | 4-8  |

| 4.6.1.4  | TEXT Unlist Option              | 4-8  |

| 4.6.1.5  | WARNING Unlist Option           | 4-8  |

| 4.6.1.6  | 8K Assembly Mode Option         | 4-8  |

| 4.6.2    | Complete XREF Switch            | 4-9  |

| 4.6.3    | Object Module Switch            | 4-9  |

| 4.6.4    | Listing File Switch             | 4-9  |

| 4.6.5    | Page Eject Disable Switch       | 4-9  |

| 4.6.6    | Error to Screen Switch          | 4-9  |

| 4.6.7    | Binary Code File Disable Switch | 4-9  |

| 4.7 As   | sembler Directives              | 4-10 |

| 4.7.1    | AORG Directive                  | 4-11 |

| 4.7.2    | BYTE Directive                  | 4-12 |

| 4.7.3    | BES Directive                   | 4-12 |

| 4.7.4    | BSS Directive                   | 4-13 |

| 4.7.5    | COPY Directive                  | 4-13 |

| 4.7.6    | DATA Directive                  | 4-13 |

| 4.7.7    | EQU Directive                   | 4-14 |

| 4.7.8    | EVEN Directive                  | 4-14 |

| 4.7.9    | END Directive                   | 4-15 |

| 4.7.10   | IDT Directive                   | 4-15 |

| 4.7.11   | LIST Directive                  | 4-16 |

| 4.7.12   | OPTION Directive                | 4-16 |

| 4.7.12.1 | BUNLST                          | 4-16 |

| 4.7.12.2 | DUNLST                          | 4-17 |

| 4.7.12.3 | FUNLST                          | 4-17 |

| 4.7.12.4 | LSTUNL                          | 4-17 |

| 4.7.12.5 | OBJUNL                          | 4-17 |

| 4.7.12.6 | PAGEOF                          | 4-17 |

| 4.7.12.7 | RXREF                           | 4-17 |

| 4.7.12.8 | SCRNOF                          | 4-17 |

v

| Section      | Title              | Page         |

|--------------|--------------------|--------------|

| 4.7.12.      | 9 TUNLST           | 4-17         |

| 4.7.12.      | 10 WARNOF          | 4-17         |

| 4.7.12.      |                    | 4-18         |

| 4.7.12.      | 12 8KASM           | 4-18         |

| 4.7.12.      | 13 990             | 4-18         |

| 4.7.13       | PAGE Directive     | 4-18         |

| 4.7.14       | RBYTE Directive    | 4-18         |

| 4.7.15       | RDATA Directive    | 4-19         |

| 4.7.16       | RTEXT Directive    | 4-19         |

| 4.7.17       | TEXT Directive     | 4-20         |

| 4.7.18       | TITL Directive     | 4-20         |

| 4.7.19       | UNL Directive      | 4-21         |

|              |                    |              |

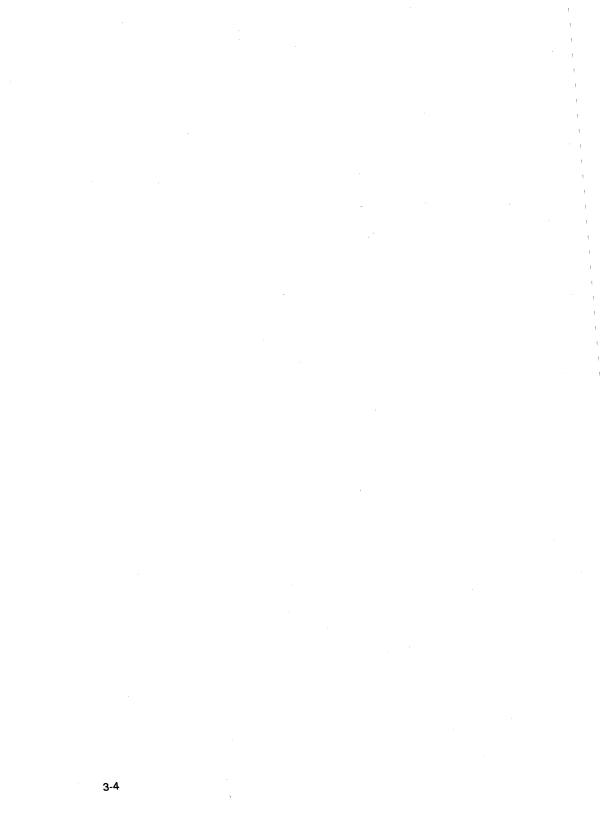

| 5            | Instruction Set    | 5-1          |

| 5.1          | Instruction Format | 5-3          |

| 5.2          | ACAA               | 5-4          |

| 5.3          | AMAAC              | 5-5          |

| 5.4          | ANEC               | 5-6          |

| 5.5          | BR                 | 5-7          |

| 5.6          | CALL               | 5-8          |

| 5.7          | CLA                | 5-9          |

| 5.8          | CLB                | 5-10         |

| 5.9          | CLX                | 5-11<br>5-12 |

| 5.10         |                    | 5-12         |

| 5.11<br>5.12 | EXTRM              | 5-13         |

| 5.12         | EXTSG              | 5-14         |

| 5.13         | IBC                | 5-15         |

| 5.14         |                    | 5-17         |

| 5.15         | INTD               | 5-10         |

| 5.10         | INTE               | 5-20         |

| 5.18         | INTER.             | 5-20         |

| 5.19         | INTRM              | 5-22         |

| 5.20         | IXC                | 5-22         |

| 5.20         | LUAA               | 5-23         |

| 5.22         | LUSPS              | 5-24         |

| 5.23         | POP                | - 00         |

| Section | Title | Page |

|---------|-------|------|

| 5.24    | RBITM | 5-27 |

| 5.25    | RETI  | 5-28 |

| 5.26    | RETN  | 5-29 |

| 5.27    | RSECT | 5-30 |

| 5.28    | RSRDY | 5-31 |

| 5.29    | SALA  | 5-32 |

| 5.30    | SARA  | 5-33 |

| 5.31    | SBITM | 5-34 |

| 5.32    | SBR   | 5-35 |

| 5.33    | SETOF | 5-36 |

| 5.34    | SMAAN | 5-37 |

| 5.35    | START | 5-38 |

| 5.36    | STOP  | 5-39 |

| 5.37    | ΤΑΡΑ  | 5-40 |

| 5.38    | ТАРВ  | 5-41 |

| 5.39    | TAPD  | 5-42 |

| 5.40    | ΤΑΜ   | 5-43 |

| 5.41    | TAPRF | 5-44 |

| 5.42    | TAPSC | 5-45 |

| 5.43    | TASH  | 5-46 |

| 5.44    | TASL  | 5-47 |

| 5.45    | ΤΑΥ   | 5-48 |

| 5.46    | ΤΑΧ   | 5-49 |

| 5.47    | ТВА   | 5-50 |

| 5.48    | TBITA | 5-51 |

| 5.49    | твітм | 5-52 |

| 5.50    | тсх   | 5-53 |

| 5.51    | ΤΜΑ   | 5-54 |

| 5.52    | ΤΜΑΙΧ | 5-55 |

| 5.53    | TMEDA | 5-56 |

| 5.54    | ΤΡΑΑ  | 5-57 |

| 5.55    | TPAM  | 5-58 |

| 5.56    | TPCA  | 5-59 |

| 5.57    | TTMA  | 5-60 |

| 5.58    | ΤΧΑ   | 5-61 |

| 5.59    | ТХРА  | 5-62 |

| 5.60    | ТХТМ  | 5-63 |

| 5.61    | ХВХ   | 5-64 |

| 5 62    | XGEC  | 5-65 |

# **Contents (Concluded)**

| Section | Title                                             | Page |

|---------|---------------------------------------------------|------|

| 6       | Applications                                      | 6-1  |

| 6.1     | Synthesizer Control                               | 6-1  |

| 6.1.1   | Speech Coding and Decoding                        | 6-1  |

| 6.1.2   | RAM Usage                                         | 6-4  |

| 6.1.3   | ROM Usage                                         | 6-6  |

| 6.1.4   | Program Overview                                  | 6-7  |

| 6.1.5   | Calling the Synthesis Program                     | 6-8  |

| 6.1.6   | Synthesis Program Walkthrough                     | 6-11 |

| 6.2     | Arithmetic Modes                                  | 6-18 |

| 6.3     | Standby Mode                                      | 6-19 |

| 6.4     | Slave Option                                      | 6-20 |

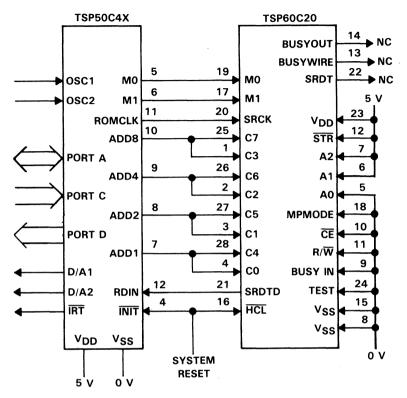

| 6.5     | TSP60CXX Interface                                | 6-22 |

| 6.5.1   | Initialization                                    | 6-23 |

| 6.5.2   | Using Internal and External Data Alternately      | 6-25 |

| 6.5.3   | TSP60CXX Power Down                               | 6-26 |

| 6.6     | Use of the TMEDA Instruction                      | 6-26 |

| 6.7     | Use of Timer, Prescaler, Interrupt and IRT Pin    | 6-27 |

| 6.8     | Use of the Stack                                  | 6-28 |

| 7       | Customer Information                              | 7-1  |

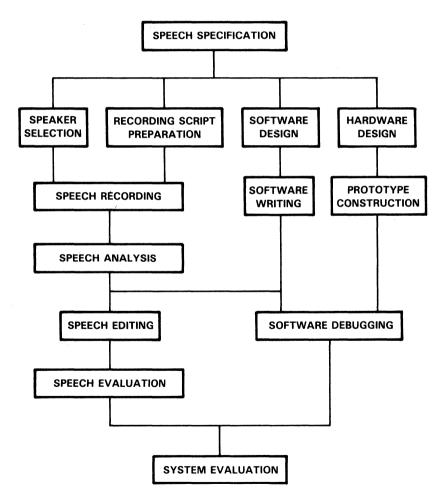

| 7.1     | Production Flow                                   | 7-1  |

| 7.2     | Summary of Speech Development/Production Sequence | 7-2  |

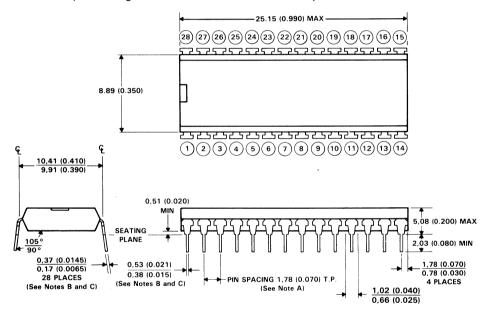

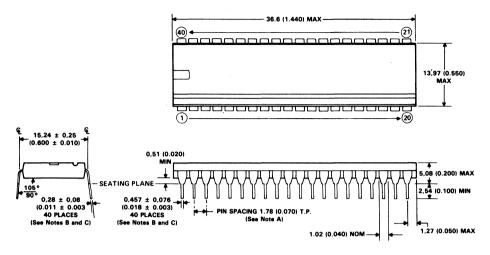

| 7.3     | Mechanical Data                                   | 7-3  |

| 7.4     | IC Sockets                                        | 7-6  |

| 7.5     | Ordering Information                              | 7-7  |

| 7.6     | New Product Release Forms                         | 7-8  |

| Α       | Script Preparation and Speech Development Tools   | A-1  |

| В       | TSP50C4X Synthesis Program                        | B-1  |

| С       | Program to Initialize the TSP60C20 Speech ROM     | C-1  |

# List of Illustrations

| Figure | Title                                      | Page |

|--------|--------------------------------------------|------|

| 1-1    | TSP50C4X Applications                      | 1-1  |

| 1-2    | Block Diagram                              | 1-2  |

| 1-3    | Pin Assignments                            | 1-5  |

| 1-4    | LPC-10 Vocal Tract Model                   | 1-12 |

| 2-1    | System Block Diagram                       | 2-1  |

| 2-2    | ROM Map                                    | 2-2  |

| 2-3    | I/O Data Bus (PA0-PA7)                     | 2-9  |

| 2-4    | RAM Map During Speech Generation           | 2-11 |

| 2-5    | Initialization Timing                      | 2-12 |

| 2-6    | Write Timing Diagram                       | 2-13 |

| 2-7    | Read Timing Diagram                        | 2-14 |

| 3-1    | Typical Phase Shift Oscillator Connections | 3-2  |

| 3-2    | Typical Direct Speaker Drive Connection    | 3-3  |

| 6-1    | TSP5220 Frame Decoding                     | 6-2  |

| 6-2    | Speech Parameter Unpacking and Decoding    | 6-3  |

| 6-3    | ALU Modes                                  | 6-19 |

| 6-4    | Read Operation                             | 6-21 |

| 6-5    | Write Operation                            | 6-22 |

| 6-6    | TSP50C4X/TSP60C19 Interface                | 6-23 |

| 6-7    | TSP50C4X/TSP60C20 Interface                | 6-24 |

| 7-1    | Speech Development Cycle                   | 7-1  |

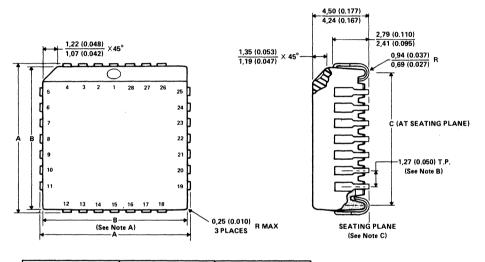

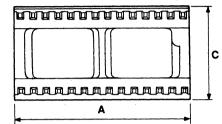

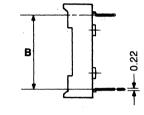

| 7-2    | 28-Pin N2 Plastic Package                  | 7-3  |

| 7-3    | 40-Pin N2 Plastic Package                  | 7-4  |

| 7-4    | 28-Pin FN PLCC                             | 7-5  |

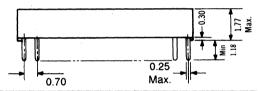

| 7-5    | Shrink Package                             | 7-6  |

# List of Tables

| Table | Title                                              | Page |

|-------|----------------------------------------------------|------|

| 1-1   | TSP50C4X Device Comparison                         | 1-3  |

| 1-2   | Pin Function Description of Port A for             |      |

|       | Three Mask Options                                 | 1-6  |

| 1-3   | Pin Function Description of Port B for External or |      |

|       | Internal ROM Modes                                 | 1-7  |

| 1-4   | Pin Function Description of Port C for             |      |

|       | Two Mask Options                                   | 1-8  |

| 1-5   | Pin Function Description of Port D                 | 1-9  |

| 1-6   | Pin Function Description of IRT (Several Options), |      |

|       | OSC and DA                                         | 1-10 |

| 2-1   | Initialization Timing                              | 2-12 |

| 2-2   | Timing Requirements                                | 2-12 |

| 2-3   | Write Timing Requirements                          | 2-13 |

| 2-4   | Read Timing Requirements                           | 2-14 |

| 4-1   | Switches and Options                               | 4-10 |

| 4-2   | Summary of Assembler Directives                    | 4-11 |

| 5-1   | TSP50C4X Instruction Set                           | 5-1  |

| 6-1   | Synthesizer RAM Addresses                          | 6-5  |

| 6-2   | Buffer and Control RAM Usage                       | 6-6  |

| 6-3   | ROM Usage                                          | 6-7  |

# 1 Introduction

The TSP50C4X family of speech synthesizers consists of the following four devices: TSP50C41, TSP50C42, TSP50C43, and TSP50C44. In each of these, an 8-bit microprocessor, a programmable speech synthesizer, and ROM are combined to provide a one-chip solution for many applications. The devices use Linear Predictive Coding (LPC) to generate speech at a low data rate. Mask options are also available to provide design flexibility.

This section consists of a brief overview of the TSP50C4X family. It begins with a summary of applications, key features, and a comparison of the devices, followed by a discussion on mask options and pin descriptions. Also included is an introduction to Linear Predictive Coding.

## 1.1 Applications

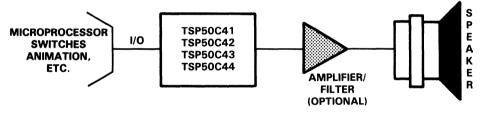

As illustrated in Figure 1-1, the TSP50C4X devices are versatile and can be used in many applications.

Figure 1-1. TSP50C4X Applications

Typical applications include:

Automotive Telecom PABX **Telephone Management** Security **Home Monitors** Navigation Aids Computer Tovs Analyzers Medical **Office Computers Personal Computers** Industrial **Inspection Controls** Inventory Controls Machine Controls Warehouse Systems

**Clock Systems** Warning Systems Consumer Appliances Mailboxes Equipment for the Handicapped Educational Learning Aids **Computer Aided** Instructions

#### 1.2 Description

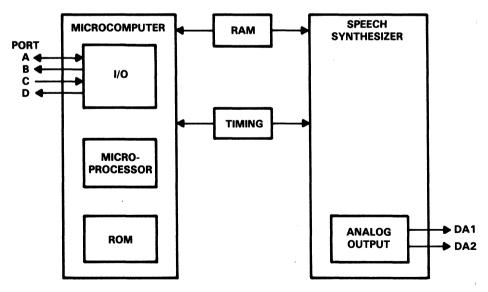

The TSP50C4X device can be divided into several functional blocks (Figure 1-2). The two main blocks are the microcomputer and the speech synthesizer, which share RAM and timing circuits.

Figure 1-2. Block Diagram

These devices implement an LPC-10 speech synthesis algorithm using a 10-pole lattice filter. The internal microprocessor accesses speech data from the internal or external ROM (TSP60CXX), decodes the speech data and sends the decoded data to the synthesizer. The output of the synthesizer can be used to drive a small speaker directly or, with an external filter and amplifier, to drive a large speaker.

## 1.3 Features

- Programmable LPC-10 Speech Synthesizer

- 8-Bit Microprocessor with 61 Instructions

- 128 Bytes plus 16 Nibbles of RAM

- 4-V to 6-V CMOS Technology for Low Power Dissipation

- High-Efficiency Push-Pull Pulse-Width-Modulated Digital-to-Analog Output that can Drive a Speaker Directly

- 10-kHz or 8-kHz Speech Sample Rate

- 8K Byte or 16K Byte ROM, 21- or 33-pin I/O

- Mask Options

- External Event Counter/Internal Timer

## 1.4 Device Comparison

| Table 1-1. | TSP50C4X | Device | Comparison |

|------------|----------|--------|------------|

|------------|----------|--------|------------|

|             | TSP50C41 | TSP50C42 | TSP50C43 | TSP50C44 |

|-------------|----------|----------|----------|----------|

| ROM (Bytes) | 8K       | 8K       | 16K      | 16K      |

| I/O pins*   | 21       | 33       | 21       | 33       |

| 8-bit ports | 2 1/2    | 4        | 2 1/2    | 4        |

| No. of pins | 28       | 40       | 28       | 40       |

<sup>\*</sup>I/O pins include the IRT pin.

# 1.5 Mask Options

The designer may choose from five basic mask options depending on the application. For instance, the master option is designed for single-chip applications in which the host is the internal microprocessor. The slave option is intended for use in multichip systems in which the host microprocessor is external as shown in Section 7. The mask options are as follows:

- 1. MASTER or SLAVE option

- a. MASTER option

Port A (PA1-PA8) is a general purpose input/output port.

b. SLAVE option

Port A can be controlled by an external processor.

Port C (PC0-PC3) pins are programmed to be interface control pins  $\overline{RDY}$ ,  $\overline{ENA1}$ ,  $\overline{ENA2}$  and  $R/\overline{W}$ .

### 2. IRT INPUT or OUTPUT option

a. IRT INPUT option

IRT is an input that can be software selected by a TTMA command to be a clock signal for the timer prescale register. The IRT pin is unused if the internal clock is selected by a RSECT software command.

b. IRT OUTPUT option

IRT is an output that indicates that the data output on port A is stable.

#### 3. KEYBOARD or NORMAL option

a. KEYBOARD option

Port A is split so that PA0-PA3 will be output pins and PA4-PA7 will be input pins. PC0 is not used and PC1-PC3 are tied low. This is referred to as the keyboard scan option since it is optimally configured for scanning a  $4 \times 4$  keyboard.

b. NORMAL option

Port A is configured as an 8-bit I/O port.

- 4. ROM 8K or ROM 4K option

- a. ROM 8K option

Allows the microprocessor software program to use 8K bytes of internal ROM for program instructions. Remaining ROM is available for other uses. Branches and calls must have even destination addresses (LSB = 0).

b. ROM 4K option

Limits the microprocessor program to the first 4K bytes of internal ROM for program instructions. Remaining ROM is available.

- 5. SETOFF DISABLED or ENABLED option

- a. SETOFF DISABLED

Disables the software "Setoff" command and causes it to act as a "NOP".

b. SETOFF ENABLED

Enables the "Setoff" command. The microprocessor puts the TSP50C4X device in the low-power standby by executing the "Setoff" command. The external circuitry takes the chip out of the standby option by driving the INIT pin to a low state and then back to a high state.

When the master option is selected, the NORMAL and IRT input options are pre-selected. When the slave option is selected, all of the remaining options are available.

The TSP50C4X devices have additional I/O mask options to minimize the system parts count. Each pin on Ports A and C can be individually programmed to have a pull-up resistor. Ports B and D can be programmed in blocks of 4 to have open-drain outputs, that is, the pull-up device can be disabled. The blocks are B0-3, B4-7, D0-3, and D4-7.

# 1.6 Pin Assignment and Description

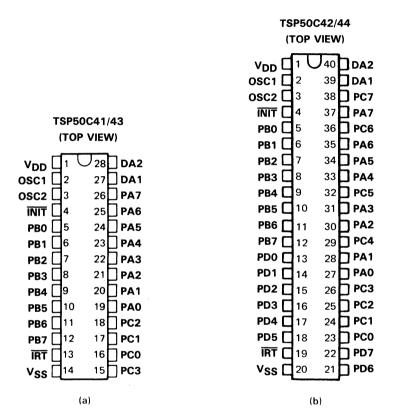

Figure 1-3 shows the pin assignments for the TSP50C41/43 and the TSP50C42/44. Tables 1-1 and 1-2 provide pin function descriptions.

Figure 1-3. Pin Assignments

|                       | PIN NO.          |                  |     |                                                                   |  |

|-----------------------|------------------|------------------|-----|-------------------------------------------------------------------|--|

| PIN NAME              | ′50C41<br>′50C43 | ′50C42<br>′50C44 | I/O | DESCRIPTION                                                       |  |

| [MASTER option]       |                  |                  |     | Port A is a general purpose bi-                                   |  |

| PAO (LSB)             | 19               | 27               | I/O | directional port that is controlled by                            |  |

| PA1                   | 20               | 28               | I/O | the internal microprocessor.                                      |  |

| PA2                   | 21               | 30               | I/O |                                                                   |  |

| PA3                   | 22               | 31               | I/O |                                                                   |  |

| PA4                   | 23               | 33               | I/O |                                                                   |  |

| PA5                   | 24               | 34               | I/O |                                                                   |  |

| PA6                   | 25               | 35               | I/O |                                                                   |  |

| PA7 (MSB)             | 26               | 37               | I/O |                                                                   |  |

| [SLAVE/NORMAL option] |                  |                  |     | Port A is an interface between the                                |  |

| PAO (LSB)             | 19               | 27               | I/O | internal and external microprocessor.                             |  |

| PA1                   | 20               | 28               | 1/0 | PCO-PC3 are configured as Ready.                                  |  |

| PA2                   | 21               | 30               | I/O | Enable and Read/Write control pins for                            |  |

| PA3                   | 22               | 31               | I/O | interface.                                                        |  |

| PA4                   | 23               | 33               | I/O | ·                                                                 |  |

| PA5                   | 24               | 34               | 1/0 |                                                                   |  |

| PA6                   | 25               | 35               | I/O |                                                                   |  |

| PA7 (MSB)             | 26               | 37               | I/O |                                                                   |  |

| [SLAVE/KEYBOARD opt]  |                  |                  |     | Port A is configured so that PAO-PA3                              |  |

| PAO (LSB)             | 19               | 27               | 0   | are outputs and pins PA4-PA7 are                                  |  |

| PA1                   | 20               | 28               | 0   | inputs. This configuration is optimal                             |  |

| PA2                   | 21               | 30               | 0   | for scanning a $4 \times 4$ keyboard. The                         |  |

| PA3                   | 22               | 31               | 0   | RDY signal is not used. The ENA1,                                 |  |

| PA4                   | 23               | 33               | 1   | $\overline{\text{ENA}2}$ and $R/\overline{W}$ should be tied low. |  |

| PA5                   | 24               | 34               | 1   |                                                                   |  |

| PA6                   | 25               | 35               | 1   |                                                                   |  |

| PA7 (MSB)             | 26               | 37               | I   |                                                                   |  |

Table 1-2. Pin Function Description of Port A for Three Mask Options

|                     | PIN NO.          |                  |     |                                         |  |  |  |

|---------------------|------------------|------------------|-----|-----------------------------------------|--|--|--|

| PIN NAME            | ′50C41<br>′50C43 | ′50C42<br>′50C44 | I/O | DESCRIPTION                             |  |  |  |

| [INTERNAL ROM mode] |                  |                  |     | The INTERNAL ROM mode is                |  |  |  |

| PBO (LSB)           | 5                | 5                | 0   | initiated by the INTRM software         |  |  |  |

| PB1                 | 6                | 6                | 0   | command. Port B is an output port       |  |  |  |

| PB2                 | 7                | 7                | 0   | controlled by the internal micro-       |  |  |  |

| PB3                 | 8                | 8                | 0   | processor. This port is put into the    |  |  |  |

| PB4                 | 9                | 9                | 0   | INTERNAL ROM mode on power-up           |  |  |  |

| PB5                 | 10               | 10               | 0   | and when the INIT pin is low.           |  |  |  |

| PB6                 | 11               | 11               | 0   | These two events also cause the         |  |  |  |

| PB7 (MSB)           | 12               | 12               | 0   | port's outputs to latch low.            |  |  |  |

| [EXTERNAL ROM mode] |                  |                  |     | The EXTERNAL ROM mode is initiated      |  |  |  |

|                     |                  |                  |     | by a EXTRM software command.            |  |  |  |

|                     |                  |                  |     | Port B is configured as an interface to |  |  |  |

|                     |                  |                  |     | a TSP60CXX vocabulary ROM.              |  |  |  |

| мо                  | 5                | 5                | 0   | Vocabulary ROM mode control             |  |  |  |

| M1                  | 6                | 6                | 0   | Vocabulary ROM mode control             |  |  |  |

| ADD1                | 7                | 7                | 0   | Vocabulary ROM address weight 1         |  |  |  |

| ADD2                | 8                | 8                | 0   | Vocabulary ROM address weight 2         |  |  |  |

| ADD4                | 9                | 9                | 0   | Vocabulary ROM address weight 4         |  |  |  |

| ADD8                | 10               | 10               | 0   | Vocabulary ROM address weight 8         |  |  |  |

| ROMCLK              | 11               | 11               | 0   | Clock output to the vocabulary ROM.     |  |  |  |

|                     |                  |                  |     | Oscillator divided by 16.               |  |  |  |

| RDIN                | 12               | 12               | I   | Vocabulary ROM data input               |  |  |  |

## Table 1-3. Pin Function Description of Port B for External and Internal ROM Modes

Table 1-4. Pin Function Description of Port C for Two Mask Options

|                                                     | PIN NO.              |                      |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-----------------------------------------------------|----------------------|----------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NAME                                            | ′50C41<br>′50C43     | ′50C42 I/<br>′50C44  |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| [SLAVE option]<br>RDY                               | 15                   | 23                   | ο | When active (low), Port A is ready to receive data fron an external microprocessor. $\overline{RDY}$ is set high when the $\overline{ENA2}$ pin is pulled low. If the external processor is not holding $\overline{ENA2}$ low, then an RSRDY software command will reset $\overline{RDY}$ low. Status of the pin can be evaluated by the TPCA* instruction.                                                                                                                                                                                                                                  |  |  |  |

| ENA1                                                | 16                   | 24                   | I | Enables the reading or writing of Port A data<br>PA0-PA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ENA2                                                | 17                   | 25                   | I | Read mode (R/W high)         ENA1:       Most significant nibble of Port A latch is put on the bus PA4-PA7 while ENA1 is low. When ENA1 goes low, IRT goes high.         ENA2:       Least significant nibble of Port A latch is put on the bus PA0-PA3 while ENA2 is low.         Write mode (R/W low)       ENA1:         ENA1:       Most significant nibble on the data bus PA4-PA7 is strobed in the Port A latch when ENA1 goes from low to high.         ENA2:       Least significant nibble on the data bus PA4-PA7 is strobed in the Port A latch when ENA1 goes from low to high. |  |  |  |

| R/₩                                                 | 18                   | 26                   | I | Determines the direction of the Port A data bus:<br>R/W = high; data in the Port A latch is<br>available to the external bus.<br>R/W = low; data on the external bus is<br>written into the Port A latch.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| [MASTER option]<br>PC0 (LSB)<br>PC1<br>PC2<br>PC3   | 16<br>17<br>18<br>15 | 23<br>24<br>25<br>26 | 1 | General-purpose input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| [MASTER or SLAVE]<br>PC4<br>PC5<br>PC6<br>PC7 (MSB) |                      | 29<br>32<br>36<br>38 | 1 | General-purpose input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

Note: If an external driving circuit is used, it should not be allowed to go into high impedance. \*Refer to Table 5-1 for more information.

|           | PIN NO.          |                  |     |                             |

|-----------|------------------|------------------|-----|-----------------------------|

| PIN NAME  | ′50C41<br>′50C43 | ′50C42<br>′50C44 | I/O | DESCRIPTION                 |

| PDO (LSB) |                  | 13               | 0   | General-purpose output port |

| PD1       |                  | 14               | 0   |                             |

| PD2       |                  | 15               | 0   |                             |

| PD3       |                  | 16               | 0   |                             |

| PD4       |                  | 17               | 0   |                             |

| PD5       |                  | 18               | 0   |                             |

| PD6       |                  | 21               | 0   |                             |

| PD7 (MSB) |                  | 22               | 0   |                             |

Table 1-5. Pin Function Description for Port D

|                               | PIN              | NO.              |     | DESCRIPTION                                                                                                                                                                                                                                                        |  |  |

|-------------------------------|------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN NAME                      | ′50C41<br>′50C43 | ′50C42<br>′50C44 | I/O |                                                                                                                                                                                                                                                                    |  |  |

| [MASTER/ĪRT IN OPTION]<br>ĪRT | 13               | 19               | I   | Interrupt input when programmed by<br>a TTMA software command to be an<br>input to the timer prescale register.                                                                                                                                                    |  |  |

| (SLAVE/IRT IN OPTION)<br>IRT  | 13               | 19               | Ι   | Interrupt input when programmed by<br>a TTMA software command to be an<br>input to the timer prescale register.                                                                                                                                                    |  |  |

| [SLAVE/IRT OUT OPTION]<br>IRT | 13               | 19               | 0   | Ready for data output. IRT goes high<br>when ENA1 is pulled low by externa<br>processor while pin R/W is high. IRT<br>goes low when data are put into<br>Port A with the TAPA* instruction<br>Software command TPCA can be<br>used to read the data on the IRT pin |  |  |

| DA1                           | 27               | 39               | 0   | Positive digital-to-analog converter output (PWM)                                                                                                                                                                                                                  |  |  |

| DA2                           | 28               | 40               | 0   | Negative digital-to-analog converter output (PWM)                                                                                                                                                                                                                  |  |  |

| ÎNÎT                          | 4                | 4                |     | Initialize input; when low, device is<br>initialized and goes into the low-power<br>mode, Port B and Port D outputs are<br>latched low. Port A is put into input<br>mode. When INIT goes from low to<br>high, the program counter is loaded<br>with zeroes.        |  |  |

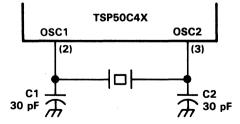

| OSC1                          | 2                | 2                | I   | Clock input. Crystal or ceramic<br>resonator between OSC1 and OSC2:<br>3.07-MHz crystal/ceramic resonator<br>for 8-kHz sampling rate<br>3.84-MHz crystal/ceramic resonator<br>for 10-kHz sampling rate                                                             |  |  |

| OSC2                          | 3                | 3                | 0   | Clock return                                                                                                                                                                                                                                                       |  |  |

| V <sub>DD</sub>               | 1                | 1                | 1   | 5-V nominal supply voltage                                                                                                                                                                                                                                         |  |  |

| V <sub>SS</sub>               | 14               | 20               | 1   | Ground                                                                                                                                                                                                                                                             |  |  |

Table 1-6. Pin Function Description of IRT (several options), INIT, OSC, and DA

\*Refer to Table 5-1 for more information.

# 1.7 Introduction to LPC

The LPC-10 system uses a mathematical model of the human vocal tract to enable efficient digital storage and the recreation of realistic speech. To understand LPC (Linear Predictive Coding), it is essential to understand how the vocal tract works . This introduction, therefore, begins with a short description of the vocal tract. The LPC model and data compression techniques are then addressed. A short discussion of the techniques and pitfalls of collecting, analyzing, and editing speech for LPC synthesis is included in Appendix A. For more information, contact your TI field sales representative or regional technology center.

### 1.7.1 The Vocal Tract

Speech is the result of the interaction between three elements in the vocal tract: air from the lungs, a restriction which converts the air flow to sound, and the vocal cavities that are positioned to resonate properly.

The air from the lungs is expelled through the vocal tract when the muscles of the chest and diaphragm are compressed. Pressure is used as a volume control, higher pressure for louder speech.

As air flows through the vocal tract, it makes very little sound if there is no restriction. The vocal cords are one type of restriction. They can be tightened across the vocal tract to stop the flow of air. Pressure builds up behind them and forces them open. This happens over and over, generating a series of pulses. The tension on the vocal cords can be varied to change the frequency of the pulses. Many speech sounds are produced by this type of restriction, for example, the "A" sound. This is called "voiced" speech.

A different type of restriction takes place in the mouth and causes a hissing sound called white noise. The "S" sound is a good example. This occurs when the tongue and some part of the mouth are in close contact or when the lips are pursed. This restriction causes high flow velocities which cause turbulence that produces white noise. This is called "unvoiced" speech.

The pulses from the vocal cords and the noise from the turbulence have fairly broad, flat spectral characteristics. In other words, they are really noise, not speech. The shape of the oral cavity changes noise into recognizable speech. The position of the tongue, the lips and the jaws change the resonance of the vocal tract, shaping the raw noise of restricted air flow into understandable sounds.

### 1.7.2 The LPC Model

The LPC model incorporates elements analogous to each of the elements of the vocal tract described above. It has an excitation function generator that models both types of restriction, a gain multiplication stage to model the possible levels of pressure from the lungs, and a digital filter to model the resonance in the oral and nasal cavities. Figure 1-4 shows the LPC model in schematic form. The excitation function generator accepts coded pitch information as an input and can generate a series of pulses similar to vocal cord pulses. It can also generate white noise. The waveform is then multiplied by an energy factor that corresponds to the pressure from the lungs. Finally, the signal is passed through a digital filter that models the shape of the oral cavity. In the TSP50C4X family, this filter has ten poles, so the synthesis is referred to as LPC-10.

Figure 1-4. LPC-10 Vocal Tract Model

### 1.7.3 LPC Data Compression

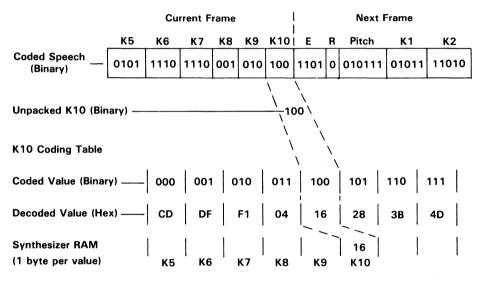

The data compression for LPC-10 takes advantage of other characteristics of speech. Speech changes fairly slowly, and the oral and nasal cavities tend to fall into certain areas of resonance more than others. The speech is analyzed in frames that are generally from 10 to 25 ms long. The inputs to the model are calculated as an average for the entire frame. The synthesizer smooths or interpolates the data during the frame, so there isn't an abrupt transition at the end of each frame. Often speech changes even more slowly than the frame. TI's LPC model allows for a repeat frame, where the only values changed are the pitch and the energy. The filter coefficients are kept constant from the previous frame. To take advantage of the recurrent nature of resonance in the oral cavity, all the coefficients are encoded, with anywhere from seven to three bits for each coefficient. The coding table is designed so that more coverage is given to the coefficient values that occur frequently.

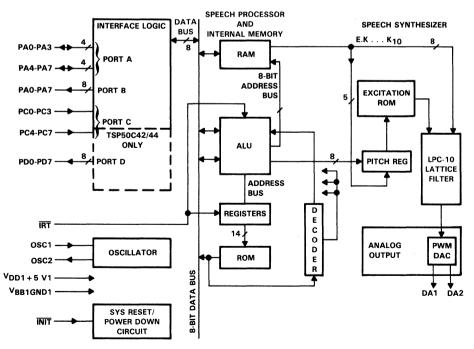

# 2 TSP50C4X Family Architecture

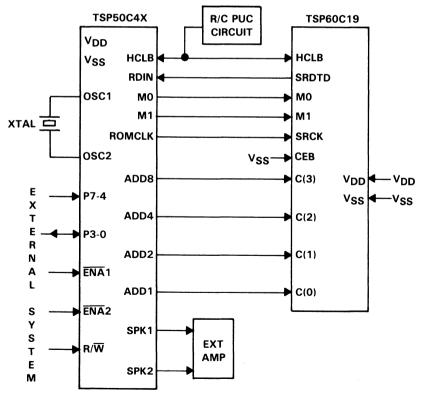

The major components of the TSP50C4X devices are a speech synthesizer, an 8-bit microprocessor, an internal 8K-byte (TSP50C41/42) or 16K-byte (TSP50C43/44) ROM and interface logic (I/O) as shown in Figure 2-1. Instructions are fetched by the microprocessor from the ROM approximately every 9  $\mu$ s (oscillator frequency divided by 32) and are used to control the algorithm sequences. To generate speech, the processor accesses speech data from either the internal 8K-byte ROM or an external speech ROM. Once the data has been read, the processor must unpack and decode the individual speech parameters and store the results in a dedicated section of the RAM.

The I/O consists of one 8-bit bidirectional port (Port A), two 8-bit output ports (Port B and Port D), one 8-bit input port (Port C) and an  $\overline{IRT}$  pin. These ports are under the control of the microprocessor and are configured by mask options.

The synthesizer shares access to the RAM and addresses the individual parameter locations as needed when generating speech. The speech synthesizer performs parameter smoothing and pitch period control as well as lattice filter computations.

Figure 2-1. System Block Diagram

## 2.1 ROM

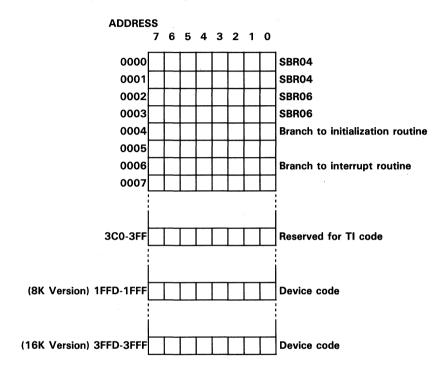

The ROM holds the control program, the speech data, and any other data required by the application. Certain locations in the ROM are reserved for specific purposes (Figure 2-2).

**NOTE:** All addresses in this manual are in hexadecimal unless otherwise noted. All other numbers are in decimal unless otherwise noted.

#### Figure 2-2. ROM Map

The ROM may be accessed in three ways:

- 1) The program counter is used to address processor instructions.

- 2) The GET\* instruction can be used to transfer 1 to 8-bits from anywhere in ROM to the A register. The GET counter is initialized by the LUSPS instruction. The SAR (Speech Address Register) points to the ROM location to be used.

- 3) The LUAA\* instruction can be used to transfer a byte from ROM locations 0-3FF into the A register.

\*Refer to Table 5-1 for more information.

## 2.2 Program Counter

The TSP50C4X devices are available with a 13-bit (TSP50C41/42) or 14-bit (TSP50C43/44) program counter. The program counter points to the next instruction to be executed. After the instruction is executed, it is normally incremented to point to the next instruction. Several instructions are used to change the value of the program counter. These are:

BR – branch

SBR - short branch

CALL - call subroutine

RETN - return from subroutine

RETI - return from interrupts

## 2.3 Program Counter Stack

The program counter stack has five levels. When a subroutine is called or an interrupt occurs, the contents of the program counter are pushed onto the stack. When a RETN (return from subroutine) or an RETI (return from interrupt) is executed, the contents of the top stack location are popped into the program counter. Certain instructions (LUSPS, GET, LUAA) push the contents of the program counter onto the stack and then pop it back during their execution. The POP\* instruction may be used to pop the top stack location.

## 2.4 Random Access Memory (RAM)

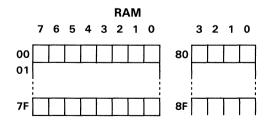

The RAM has 128 bytes plus 16 nibbles. Addresses 0 to 7F refer to bytes, and addresses 80 to 8F refer to nibbles. RAM locations 0 to 18 and 80 to 8F are used for communication with the synthesizer when speech is being generated. When not executing speech, the entire memory may be used for algorithm data storage.

\*Refer to Table 5-1 for more information.

# 2.5 Arithmetic Logic Unit (ALU)

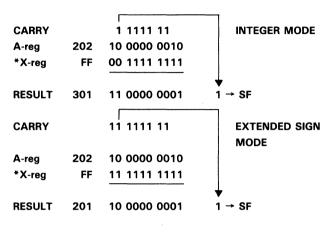

The ALU performs simple arithmetic, comparison, and logical functions for the central processor. The ALU is 10 bits in length and provides extra range for generating table look-up addresses. When transferring 8-bit data to the ALU, data is right justified. The input to the upper two bits may be either 0 (integer mode) or equal to the MSB of the 8-bit data (extended sign mode) depending on the set or reset condition of the mode latch (EXTSG and INTGR). All bit and comparison operations are performed on the lower 8 bits.

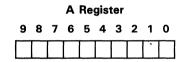

# 2.6 A Register

The A register or accumulator is the primary 10-bit register. Its contents can be transferred to or from ROM, RAM, and most of the other registers. It is used for arithmetic and logical operations. The contents are saved, in a dedicated storage register, during interrupts and restored by the RETI\* instruction.

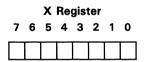

# 2.7 X Register

The X register is an 8-bit register used as a RAM index register. All RAM access instructions use the X register to point to a specific RAM location. The X register can also be used as a general purpose counter. The contents of the X register are saved during interrupts.

\*Refer to Table 5-1 for more detail.

## 2.8 B Register

The 8-bit B register is used for temporary storage. It is especially helpful for storing a RAM address, since it can be exchanged with the X register using the XBX\* instruction. The contents of the B register are not saved during interrupts.

## 2.9 Status Flag

The status flag is set or cleared by various instructions, depending on the result of the instruction. The BR, SBR, and CALL instructions are conditional. These instructions are executed only when the status flag is set. Refer to the individual descriptions of these instructions in Section 3 to find the status flag value.

# 2.10 Timer Register

The 8-bit timer register is used for generating interrupts and for counting events. It decrements once each time the timer prescale register goes from #00 to #FF. It can be loaded using the TXTM instruction and examined with the TTMA\* instruction. When it decrements from #00 to #FF an interrupt request will be generated. If interrupts are enabled, an immediate interrupt will occur; if not, the interrupt request will remain pending until interrupts are enabled. The timer will not start counting down again until it is reloaded by the TXTM instruction.

The timer register must be loaded with a fixed #1F (hex) during synthesis. It is used to generate interrupts for the synthesis software and as a time value for parameter interpolation.

\*Refer to Table 5-1 for more detail.

## 2.11 Timer Prescale Register

The 8-bit timer prescale register is used as a divider of the input to the timer register. When it decrements from #00 to #FF, the timer register is also decremented. The timer prescale register is then reloaded with the value in the preset latch, and the counting starts again.

The timer prescale register clock comes from an internal clock or from an external source on the  $\overline{IRT}$  pin. The internal clock runs at 1/48 the clock frequency of the chip. The TTMA\* instruction makes the clock source external, and the RSECT selects the internal clock.

### 2.12 Pitch Register

The 8-bit pitch register is really a synthesizer register, but it is mentioned here because it is the only one loaded explicitly by the processor. When the START instruction is executed, the pitch register is loaded with the current value in the accumulator. After that, the pitch register is loaded from a RAM location. See Section 6 for a detailed explanation.

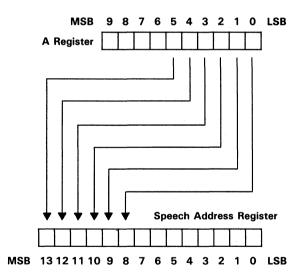

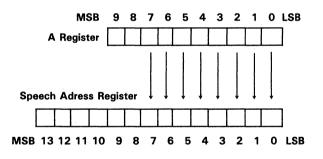

### 2.13 Speech Address Register

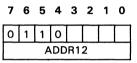

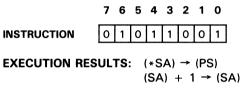

The speech address register is a 13-(TSP50C41/42) or 14-(TSP50C43/44) bit register that is used to point to data in the internal ROM. It is loaded with the TASH (Transfer Accumulator to Speech register High) and TASL (L is for Low) instructions. When a LUSPS or GET instruction is executed, the ROM value pointed to by the speech address register will be loaded into the parallel-to-serial register and the speech address register is incremented.

\*Refer to Table 5-1 for more information.

# 2.14 Parallel-to-Serial Register

#### Parallel-to-Serial Register

76543210

| -   |   | <br> | <br> |       |

|-----|---|------|------|-------|

|     |   |      |      |       |

|     |   |      |      |       |

|     |   |      |      |       |

| 1 1 |   |      |      |       |

|     | _ | <br> | <br> | <br>_ |

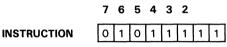

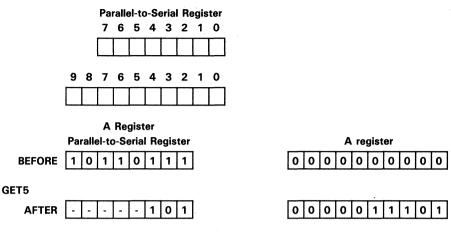

The 8-bit parallel-to-serial register is used to unpack speech. It can be loaded with eight bits of data from an external TSP60CXX speech ROM or from the internal ROM pointed to by the speech address register. The LUSPS instruction is used to initialize the parallel-to-serial register and zero its bit counter. GET instructions can then be used to transfer one to eight bits from the parallel-to-serial register is empty, it will automatically be reloaded. The INTRM instruction selects the internal ROM as the source for the parallel-to-serial register, while EXTRM selects external ROM.

## 2.15 Interface Logic

The TSP50C4X interface consists of four 8-bit ports. Port A (PA) is a bidirectional port, Ports B and D (PB and PD) are output ports. Port B can also be used as an interface to an external TSP60CXX serial ROM. Port C (PC) is either a general 8-bit input port (master option) or is split into a 4-bit input port and a 4-bit control port for Port A (slave option). In addition, an interrupt (IRT) pin and a hardware reset (INIT) pin are provided. The remaining six pins are used for power supply, oscillator, and analog outputs. The choice of master or slave operation for Port A is a mask-generation option that depends on the type of product to which the device will be applied. The master option is designed for single-chip applications or for applications in which the host is the internal microprocessor. The slave option is intended for use in multichip systems in which the host microprocessor is external.

## 2.16 Port A (MASTER Option)

Port A is a bidirectional port. The direction (input or output) of the port is determined by software control. If a TAPA\* instruction is executed, the contents of the lower eight bits of the accumulator are transfered to Port A, and it is used as an output port. If a TPAA\* instruction is executed, Port A is used as an input port and its contents are transferred to the A register. The TPAM\* instruction transfers the Port A values to the current RAM location.

If the port is switched from output to input mode with the TPAA or TPAM instructions, the data from the first transfer will be invalid. The instruction should be executed twice.

\*Refer to Table 5-1 for more information.

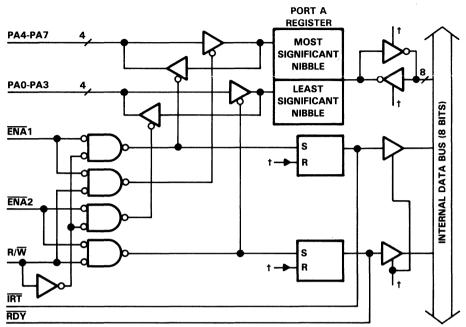

## 2.17 Port A (SLAVE Option)

In the slave option, the transfer of data to and from the 8-bit Port A is controlled by an external host through four pins of Port C. In the slave mode, pins PC3-PC0 have the function of read/write control, high nibble strobe, low nibble strobe, and ready flag for handshake interfacing. The high and low nibble strobe arrangement permits simple interfacing to 4-bit as well as 8-bit microprocessors. The ready pin is set to a not ready by a low nibble write and reset by the RSRDY instruction to acknowledge that the data written to Port A has been read by the internal microprocessor.

## 2.18 Port B

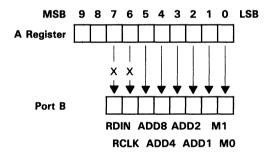

Port B can be either a general 8-bit output port or a specialized external speech ROM port. The configuration of this port is controlled by the EXTRM and INTRM instructions. If the microprocessor executes the EXTRM command, then the port is configured as a ROM port and the data source for GET instructions will be Port B. If the microprocessor executes the INTRM instruction, then Port B will be configured as a general 8-bit output port and all speech data will source from the internal ROM memory.

If the TSP60CXX external ROM is enabled and the INTRM instruction is executed, there will be a bus conflict. To avoid this, access a nonexistent TSP60CXX device before going to the INTRM mode. This will turn off the TSP60CXX so that it will not conflict when Port B becomes all outputs.

At power-up, Port B is low.

## 2.19 Port C

Port C has two possible configurations. If the master option is selected, Port C is a general input port. The data on the eight pins are transferred on command TPCA to the A Register.

In the slave option, the port is configured so that PC3-PC0 are used to control Port A through the functions ENA1, ENA2, R/W, and RDY. (See Applications, Section 6 for more details.)

### 2.20 Port D

Port D is a general output port. Data is transferred to this port from the internal microprocessor by executing the command TAPD. This is available only on the TSP50C42 and TSP50C44 devices.

At power-up, Port D is low.

<sup>†</sup>Processor Controlled Functions

Figure 2-3. I/O Data Bus (PAO-PA7)

# 2.21 IRT Pin

The interrupt pin is hardware configurable by mask option to be an eventcounter input pin (IRT = input) or an interrupt output (slave option, IRT = output). When selected as an event-counter input pin, a signal is used as the timer prescale register increment clock. The internal 80-kHz timing clock can be selected by executing RSECT. The external clock on the interrupt pin is selected by executing the command TTMA.

## 2.22 Speech Synthesizer

The task of generating synthetic speech is divided between the programmable microprocessor and the dedicated speech synthesizer.

The microprocessor controls speech synthesis by unpacking and decoding parameters as well as setting the update interval (frame rate). These aspects of speech tend to vary from application to application and are well suited to the microprocessor. The speech synthesizer, on the other hand, performs all of the synthetic speech functions that require intensive computations but do not change from application to application. These functions include the implementation of a 10-pole digital lattice filter, a pitch-controlled excitation generator, a parameter interpolator, and a digital-to-analog converter. Speech

parameter input is received from dedicated space in the microprocessor RAM, and speech samples are generated at 8 kHz or 10 kHz. Communication between the microprocessor and the speech synthesizer take place via a shared memory space in the microprocessor RAM. (Refer to the Applications section for more information.)

### 2.22.1 Use of RAM by the Synthesizer

The RAM consists of 1088 bits that are arranged as 128 8-bit words from address 00 to 7F and 16 4-bit words from 80-8F. The microprocessor can read or write to any word in the RAM. The synthesizer can only read from locations 00 to 17 and 80 to 8F, where the microprocessor stores the PRESENT and the NEW values for the frame parameters.

After the timer register generates an interrupt, the synthesizer will read only the PRESENT or both the PRESENT and NEW frame parameters. If interpolation is required, the INTE instruction is invoked for the current frame and the synthesizer uses both frame parameters. Otherwise, only the PRESENT parameter is used.

When interrupt occurs (see subsection 2.22.2), the context switch changes addresses for the PRESENT and NEW values. This is done so that the parameters put into NEW value RAM locations by the microprocessor become the PRESENT values for the current speech frame. This is a hardware function and it is transparent to the microprocessor.

If the INTE instruction is not invoked for the current frame, then interpolation will not be performed. The synthesizer will read the frame parameters for the PRESENT frame and put them into the LPC filter.

If the INTE instruction is invoked for the current frame, then the synthesizer will perform interpolation and the following sequence of events applies:

- 1. The interrupt will cause a context switch.

- 2. The microprocessor loads the next frame of data into the NEW value RAM location. The data for the current frame can be found in the PRESENT value RAM location.

- 3. The microprocessor invokes the INTE instruction, which will put the synthesizer into the interpolation mode.

- 4. Every pitch period the synthesizer will:

- a. Read the PRESENT and NEW value parameters.

- b. Read the timer register. This data defines the elapsed time from the start of the current frame (PRESENT data values) to the start of the next frame (NEW data values).

- c. The synthesizer uses the data from (a) and (b) to perform a straight line interpolation of the parameters for the current and next frame parameters.

- d. The computed parameters are put into the LPC filter.

# ADDRESS

COMMENTS

| DDRESS |                   | COMMENTS                              |

|--------|-------------------|---------------------------------------|

| 00     | NEW PITCH (11-4)  | 1                                     |

| 01     | OLD PITCH (11-4)  |                                       |

| 02     | NEW ENERGY (11-4) |                                       |

| 03     | OLD ENERGY (11-4) |                                       |

| 04     | NEW K1 (11-4)     |                                       |

| 05     | OLD K1 (11-4)     |                                       |

| 06     | NEW K2 (11-4)     | 8 MSBs (11-4) of both                 |

| 07     | OLD K2 (11-4)     | "new" and "old"                       |

| 08     | NEW K3 (11-4)     | speech parameters.                    |

| 09     | OLD K3 (11-4)     | This area is reserved                 |

| 0A     | NEW K4 (11-4)     | only during speech                    |

| •      | •                 | generation. Context                   |

| •      | •                 | address switch is                     |

| •      | •                 | operative only for                    |

| 14     | NEW K9 (11-4)     | speech.                               |

| 15     | OLD K9 (11-4)     |                                       |

| 16     | NEW K10 (11-4)    |                                       |

| 17     | OLD K10 (11-4)    | <b>±</b>                              |

| 18     |                   |                                       |

| •      | •                 | General memory. No                    |

| •      | •                 | context addressing mode.              |

| 7F     |                   | <u></u>                               |

| 80     | NEW PITCH (3-0)   | I T                                   |

| 81     | OLD PITCH (3-0)   |                                       |

| 82     | NEW ENERGY (3-0)  |                                       |

| 83     | OLD ENERGY (3-0)  |                                       |

| 84     | NEW K1 (3-0)      | 4 LSBs of speech                      |

| 85     | OLD K1 (3-0)      | parameters. K7-K10                    |

| 86     | NEW K2 (3-0)      | do not have memory                    |

| 87     | OLD K2 (3-0)      | assigned since 8 bit                  |

| 88     | NEW K3 (3-0)      | values are sufficient.                |

| 89     | OLD K3 (3-0)      | When not generating                   |

| 8A     | NEW K4 (3-0)      | speech the memory is                  |

| 8B     | OLD K4 (3-0)      | available. Context                    |

| 8C     | NEW K5 (3-0)      | addressing mode enabled               |

| 8D     | OLD K5 (3-0)      | during speech.                        |

| 8E     | NEW K6 (3-0)      | ⊥                                     |

| 8F     | OLD K6 (3-0)      | │▼                                    |

| 90     | NOT AVAILABLE     | Not available                         |

| •      |                   | · · · · · · · · · · · · · · · · · · · |

| FF     |                   | J                                     |

Figure 2-4. RAM Map During Speech Generation

# 2.22.2 Context Switch

The Context Switch is used to point to the parameter set just loaded as the NEW value and the previous set as the PRESENT value. Interpolation is then enabled between the two sets of parameter values. The INTE (Enable Timer Interrupt) instruction is used to control interpolation.

There are instances when interpolation should be disabled. The most common example is for voicing transitions or when going from zero to a nonzero value of energy. If no INTE instruction is executed, the Context Switch will change and interpolation will be disabled.

The context addressing mode is enabled for the dedicated speech data address space in RAM (addresses 00-17, 80-8F).

### 2.22.3 Interpolation

Interpolation takes place from the present values to the new values during the frame. If interpolation is not enabled, the present values are used for the entire frame. The programming task is made easier by the availability of the Context Switch.

# 2.22.4 Timing Requirements

#### Table 2-1. Initialization Timing

|    | CONDITION                                    | MIN | MAX | UNIT |

|----|----------------------------------------------|-----|-----|------|

| tw | TSP50C4X in the standby mode due to a 10     |     |     | ns   |

|    | INIT pulsed low while the TSP50C4X is active | *   |     |      |

\*One oscillator clock period.

Figure 2-5. Initialization Timing

#### Table 2-2. Timing Requirements

|                   | SAMPLE RATE |       |      |  |

|-------------------|-------------|-------|------|--|

|                   | 10 kHz      | 8 kHz | UNIT |  |

|                   | NOM         | NOM   |      |  |

| Sample period     | 100         | 125   | μs   |  |

| ROM clock rate    | 240         | 192   | kHz  |  |

| ROM clock period  | 4.17        | 5.20  | μS   |  |

| Oscillator rate   | 3.84        | 3.07  | MHz  |  |

| Oscillator period | 260         | 3.25  | ns   |  |

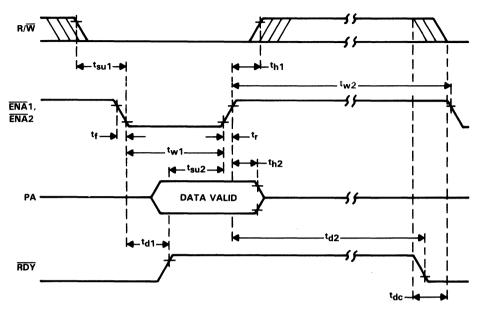

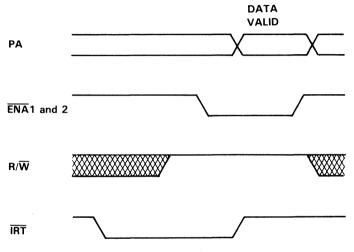

Figure 2-6. Write Timing Diagram

| Table 2-3. Write Timing Requirements (s | see Figure 2-6) |

|-----------------------------------------|-----------------|

|-----------------------------------------|-----------------|

|                  | PARAMETER                                                                            | MIN               | MAX | UNIT   |

|------------------|--------------------------------------------------------------------------------------|-------------------|-----|--------|

| t <sub>su1</sub> | Setup time, R/W before ENA1↓ or ENA2↓                                                | 80 n              |     | ns     |

| t <sub>su2</sub> | Setup time, data valid before $\overline{ENA}1\uparrow$ or $\overline{ENA}2\uparrow$ | 100               |     | ns     |

| t <sub>h1</sub>  | Hold time, R/W after $\overline{ENA}1\downarrow$ or $\overline{ENA}2\downarrow$      | 40                |     | ns     |

| <sup>t</sup> h2  | Hold time, data valid after $\overline{ENA}1\uparrow$ or $\overline{ENA}2\uparrow$   | 40 ns             |     | ns     |

| tw1              | Pulse duration, ENA1 or ENA2 low                                                     | 200               |     | ns     |

| +                | Cycle delay time                                                                     | 32                |     | CLK    |

| tdc              |                                                                                      | 52                |     | cycles |

| tr               | Rise time, ENA1 or ENA2                                                              | 50                |     | ns     |

| t <sub>f</sub>   | Fall time, ENA1 or ENA2                                                              |                   | 50  | ns     |

|                  | Delay time from ENA1 low or ENA2 low to                                              |                   | 250 |        |

| <sup>t</sup> d1  | RDY high                                                                             |                   | 250 | ns     |

| t                | Delay time from ENA1 high or ENA2 high to                                            | Brogrom Dependent |     | ondont |

| <sup>t</sup> d2  | RDY low                                                                              | Program Dependen  |     | enuent |

NOTE: ENA1 applies to PA4 through PA7, and ENA2 applies to PA0 through PA3.

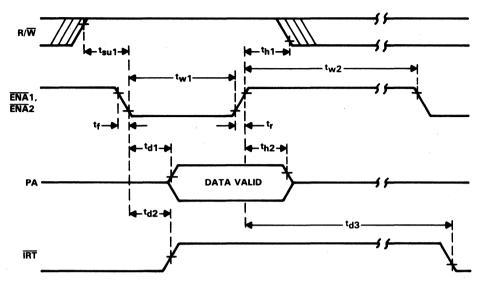

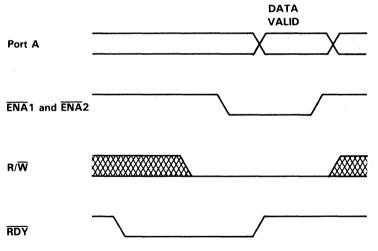

Figure 2-7. Read Timing Diagram

|  | Table 2-4. | Read Timing | Requirements | (see Figure 2-7) |

|--|------------|-------------|--------------|------------------|

|--|------------|-------------|--------------|------------------|

|                  | PARAMETER                                          | MIN  | MAX     | UNIT   |

|------------------|----------------------------------------------------|------|---------|--------|

| t <sub>su1</sub> | Setup time, R/W before ENA1↓ or ENA2↓              | 80   |         | ns     |

| th1              | Hold time, R/W after ENA11 or ENA21                | 40   |         | ns     |

| th2              | Hold time, data valid after ENA11 or ENA21         | 100  |         | ns     |

| tw1              | Pulse duration, ENA1 or ENA2 low                   | 200  |         | ns     |

| tw2              | Pulse duration, ENA1 or ENA2 high                  | 2    |         | μs     |

| t <sub>r</sub>   | Rise time, ENA1 or ENA2                            |      | 50      | ns     |

| t <sub>f</sub>   | Fall time, ENA1 or ENA2                            |      | 50      | ns     |

| <sup>t</sup> d1  | Delay time from ENA1 low or ENA2 low to data valid |      | 250     | ns     |

| <sup>t</sup> d2  | Delay time from ENA1 low or ENA2 low to IRT high   |      | 250     | ns     |

| td3              | Delay time from ENA1 high or ENA2 high to IRT low  | Prog | ram Dep | endent |

NOTE: ENA1 applies to PA4 through PA7, and ENA2 applies to PA0 through PA3.

# 2.22.5 Voicing Control

Voicing transitions refer to the change in the excitation source from voiced to unvoiced or from unvoiced to voiced. (See section 1.7.1 for a definition of voiced speech). The voicing status of a frame is encoded into the speech data and must be decoded by the unpacking algorithm. The voicing status is conveyed to the synthesizer by executing the TAV instruction (Transfer A Register to Voicing Register). A "1" on the LSB of the A Register will cause voiced excitation to be used while a "0" will indicate unvoiced excitation. A change in value of the voicing register will take effect on the next frame boundary. The actual voicing change in the synthesizer is synchronized by both timer overflow (next frame boundary) and parameter interpolation. This synchronization is hardware-controlled and is transparent to software control.

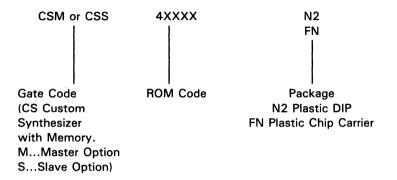

# 2.22.6 Frame Length Control