# UG0741 User Guide RTG4 FPGA I/O

а 🔨 Міскоснір company

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# Contents

| 1 | Revisi            | on His                                                                                                       | tory                                                                                                                                                             | 1                                                              |

|---|-------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|   | 1.1               | Revisio                                                                                                      | n 7.0                                                                                                                                                            | . 1                                                            |

|   | 1.2               | Revisio                                                                                                      | n 6.0                                                                                                                                                            | . 1                                                            |

|   | 1.3               | Revisio                                                                                                      | n 5.0                                                                                                                                                            | . 1                                                            |

|   | 1.4               |                                                                                                              | n 4.0                                                                                                                                                            |                                                                |

|   | 1.5               |                                                                                                              | n 3.0                                                                                                                                                            |                                                                |

|   | 1.6               |                                                                                                              | n 2.0                                                                                                                                                            |                                                                |

|   | 1.7               |                                                                                                              | n 1.0                                                                                                                                                            |                                                                |

| _ |                   |                                                                                                              |                                                                                                                                                                  |                                                                |

| 2 |                   |                                                                                                              | /                                                                                                                                                                |                                                                |

|   | 2.1               |                                                                                                              | nal Description                                                                                                                                                  |                                                                |

|   |                   | 2.1.1<br>2.1.2                                                                                               | MSIO, MSIOD, and DDRIO                                                                                                                                           |                                                                |

|   |                   | 2.1.2                                                                                                        | Receive Buffer                                                                                                                                                   |                                                                |

|   |                   | 2.1.4                                                                                                        | Input Programming Delay                                                                                                                                          |                                                                |

|   |                   | 2.1.5                                                                                                        | On-Die Termination                                                                                                                                               |                                                                |

|   | 2.2               | Radiatic                                                                                                     | on Hardening                                                                                                                                                     | . 7                                                            |

|   |                   | 2.2.1                                                                                                        | Built-in Radiation Mitigation for RTG4 I/Os                                                                                                                      | . 7                                                            |

|   | 2.3               | I/O Ban                                                                                                      | ks                                                                                                                                                               | . 7                                                            |

|   | 2.4               | Support                                                                                                      | ed I/O Standards                                                                                                                                                 | . 9                                                            |

|   |                   | 2.4.1                                                                                                        | Single-Ended Standards                                                                                                                                           |                                                                |

|   |                   | 2.4.2                                                                                                        | Voltage-Referenced Standards                                                                                                                                     |                                                                |

|   |                   | 2.4.3<br>2.4.4                                                                                               | Differential Standards                                                                                                                                           |                                                                |

|   |                   | 2.4.4                                                                                                        |                                                                                                                                                                  | 13                                                             |

| 3 | I/O Fe            |                                                                                                              |                                                                                                                                                                  |                                                                |

|   | 3.1               |                                                                                                              | grammable Features                                                                                                                                               |                                                                |

|   |                   | 3.1.1                                                                                                        | Programmable Input Delay                                                                                                                                         |                                                                |

|   |                   | 3.1.2<br>3.1.3                                                                                               | Pre-Emphasis                                                                                                                                                     |                                                                |

|   |                   | 3.1.3<br>3.1.4                                                                                               | Programmable Slew Rate Control Programmable Weak Pull-Up/Pull-Down                                                                                               |                                                                |

|   |                   | 3.1.5                                                                                                        | Programmable Schmitt-Trigger Input and Receiver                                                                                                                  |                                                                |

|   |                   | 3.1.6                                                                                                        | Programmable Output Drive Strength                                                                                                                               |                                                                |

|   |                   | 3.1.7                                                                                                        | Configuring ODT and Driver Impedance                                                                                                                             | 18                                                             |

|   | 3.2               | Cold Sp                                                                                                      |                                                                                                                                                                  |                                                                |

|   |                   | 3.2.1                                                                                                        | 5 V-Input Tolerance and Output Driving Compatibility (only MSIO)                                                                                                 | 24                                                             |

|   |                   |                                                                                                              |                                                                                                                                                                  |                                                                |

|   |                   | 3.2.2                                                                                                        | Temperature Sensing                                                                                                                                              |                                                                |

|   | 3.3               | I/Os Sha                                                                                                     | ared By Fabric and FDDR                                                                                                                                          | 26                                                             |

|   | 3.3               | I/Os Sha<br>3.3.1                                                                                            | ared By Fabric and FDDR                                                                                                                                          | 26<br>26                                                       |

|   | 3.3               | I/Os Sha<br>3.3.1<br>3.3.2                                                                                   | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric                                                                                                  | 26<br>26<br>26                                                 |

|   |                   | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3                                                                          | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric                                                                        | 26<br>26<br>26<br>26                                           |

|   | 3.4               | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3<br>JTAG I/                                                               | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric<br>Os                                                                  | 26<br>26<br>26<br>26<br>26                                     |

|   |                   | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3<br>JTAG I/                                                               | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric<br>Os                                                                  | 26<br>26<br>26<br>26<br>26<br>28                               |

|   | 3.4               | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3<br>JTAG I/<br>Dedicate                                                   | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric<br>Os                                                                  | 26<br>26<br>26<br>26<br>26<br>28<br>28                         |

|   | 3.4               | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3<br>JTAG I/<br>Dedicate<br>3.5.1<br>3.5.2                                 | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric<br>Os<br>ed I/Os<br>Device Reset I/Os                                  | 26<br>26<br>26<br>26<br>28<br>28<br>28                         |

|   | 3.4<br>3.5        | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3<br>JTAG I/<br>Dedicate<br>3.5.1<br>3.5.2                                 | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric<br>Os<br>ed I/Os<br>Device Reset I/Os<br>SerDes I/Os                   | 26<br>26<br>26<br>26<br>28<br>28<br>28<br>28<br>28             |

|   | 3.4<br>3.5        | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3<br>JTAG I/<br>Dedicate<br>3.5.1<br>3.5.2<br>Dedicate<br>3.6.1            | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric<br>Os<br>ed I/Os<br>Device Reset I/Os<br>SerDes I/Os<br>ed Global I/Os | 26<br>26<br>26<br>26<br>28<br>28<br>28<br>28<br>28<br>29<br>29 |

|   | 3.4<br>3.5<br>3.6 | I/Os Sha<br>3.3.1<br>3.3.2<br>3.3.3<br>JTAG I/<br>Dedicate<br>3.5.1<br>3.5.2<br>Dedicate<br>3.6.1<br>I/O Reg | ared By Fabric and FDDR<br>DDRIO with FDDR<br>DDRIO with Fabric<br>MSIO/MSIOD with Fabric<br>Os<br>ed I/Os<br>Device Reset I/Os<br>SerDes I/Os<br>ed Global I/Os | 26<br>26<br>26<br>28<br>28<br>28<br>28<br>29<br>29<br>35       |

# **Figures**

| Figure 1  | I/O Interconnection                               | . 4 |

|-----------|---------------------------------------------------|-----|

| Figure 2  | IOA Architecture                                  | . 6 |

| Figure 3  | RT4G-CG1657 I/O Bank Locations                    | . 8 |

| Figure 4  | RT4G-CQ352 I/O Bank Locations                     | . 8 |

| Figure 5  | Cold Sparing                                      | 23  |

| Figure 6  | 5 V Input Tolerance–Solution 1                    | 25  |

| Figure 7  | 5 V Input Tolerance–Solution 2                    | 25  |

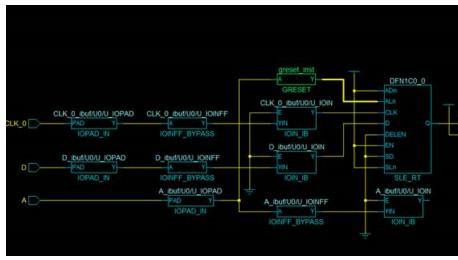

| Figure 8  | Chip Level Resets From Device Reset I/Os          | 28  |

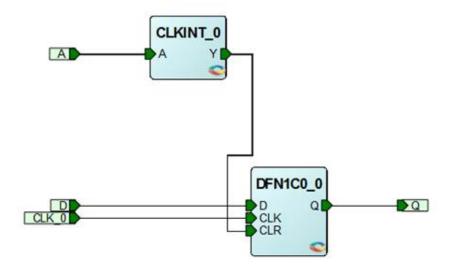

| Figure 9  | Asynchronous Reset/Set                            | 30  |

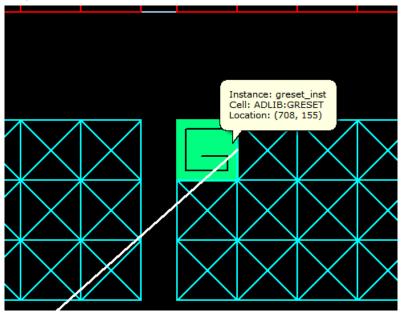

| Figure 10 | GRESET I/O Chip Layout                            | 30  |

| Figure 11 | Dedicated GRESET I/O                              | 30  |

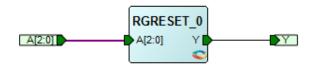

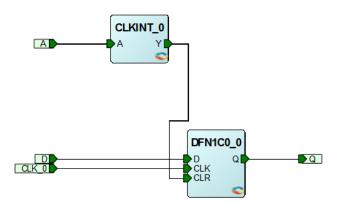

| Figure 12 | Software Netlist Viewer Optimized View            | 31  |

| Figure 13 | GRESET Output – Case 1                            | 31  |

| Figure 14 | ARST_N Signal                                     | 32  |

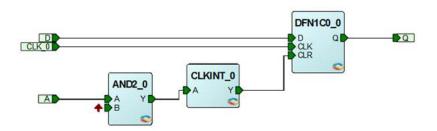

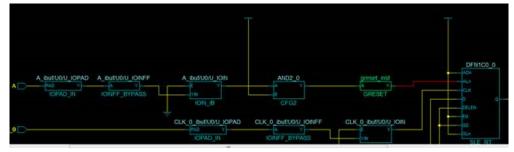

| Figure 15 | Regular I/O Pad – Case 2                          |     |

| Figure 16 | GRESET Output – Case 2                            |     |

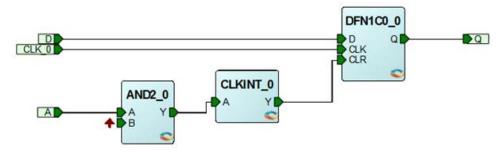

| Figure 17 | Regular I/O Pad – Case 3                          | 33  |

| Figure 18 | GRESET Output – Case 3                            | 33  |

| Figure 19 | Regular I/O Pad – Case 4                          | 34  |

| Figure 20 | GRESET Output– Case 4                             | 34  |

| Figure 21 | Regular I/O Pad – Case 5                          | 34  |

| Figure 22 | GRESET Output– Case 5                             | 35  |

| Figure 23 | Netlist Attributes                                | 36  |

| Figure 24 | LVDS Failsafe Mode                                | 37  |

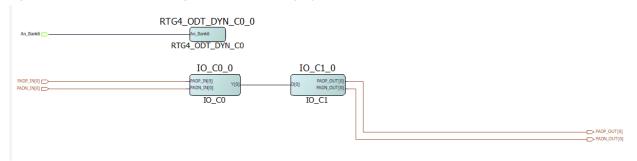

| Figure 25 | ODT Control for Fail-Safe Operation               | 37  |

| Figure 26 | Simple SmartDesign for Failsafe using Dynamic ODT | 38  |

| Figure 27 | IOEditor Example with Failsafe Settings           | 38  |

# **Tables**

| Table 1  | RTG4 Device I/O Banks                                    |  |

|----------|----------------------------------------------------------|--|

| Table 2  | Supported Voltage Standards                              |  |

| Table 3  | IOA Pair Design Rules                                    |  |

| Table 4  | Status of the V <sub>REF</sub> Pin Assigned Rule for IOA |  |

| Table 5  | RTG4 I/O Features                                        |  |

| Table 6  | Weak Pull-Up/Pull-Down Support                           |  |

| Table 7  | Schmitt Receiver Support                                 |  |

| Table 8  | Recommended Output Drive Strengths                       |  |

| Table 9  | Calibrated ODT Impedance                                 |  |

| Table 10 | Calibrated Driver/Transmitter Impedance                  |  |

| Table 11 | Recommended PCODE and NCODE Values                       |  |

| Table 12 | ODT Values                                               |  |

| Table 13 | Supported ODT Values                                     |  |

| Table 14 | Supported Termination Schemes                            |  |

| Table 15 | Cold Sparing Board Tie-Off                               |  |

| Table 16 | JTAG Pin Description                                     |  |

| Table 17 | Recommended Tie-Off Values for the TCK and TRST Pins     |  |

| Table 18 | Device Reset I/O Pin Details                             |  |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 7.0

The following is a summary of the changes made in this revision.

- Information about SSTL Termination, page 12 was added.

- Information about Schmitt receiver was updated. See Table 5, page 14.

- Information about Pre-Emphasis, page 15 was updated.

- Information about Programmable Schmitt-Trigger Input and Receiver, page 17 was updated.

- Information about Failsafe Mode for Differential Receivers, page 36 was updated.

- Information about Failsafe LVDS using Dynamic ODT, page 37 was added.

- Information about Calibrating ODT/Driver Impedance Using Fixed Calibration Codes, page 20 was updated.

# 1.2 Revision 6.0

The following is a summary of the changes made in this revision.

- Added the ODT behavior during power-down, POR (DEVRST), and user-reset scenarios in On-Die Termination, page 6.

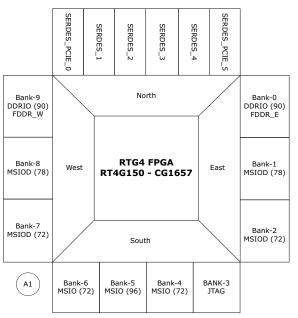

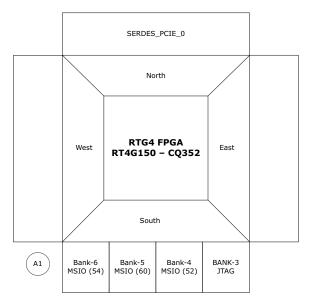

- Updated the I/O Banks, page 7 section to include information about the CQ352 package.

- Added Figure 4, page 8 to show the I/O Bank locations on the CQ352 package.

- Added I/O Bank details of CQ532 package in Table 1, page 9.

- Updated Table 2, page 9 to show that:

- HSTL18I standard is supported for MSIO, MSIOD and DDRIO Banks.

- HSTL1 standard is supported for MSIO and MSIOD Banks.

- LVCMOS25 does not support programmable slew rate, updated the Programmable Slew Rate Control, page 16 section accordingly.

- Added a footnote in Table 5, page 14 directing the user to see page 148 of the Libero Design Constraints User Guide for more information about I/O types and Banks that supports ODT.

- Added the I/O Register Combining, page 35 section.

- Added information about the support for failsafe mode, see Failsafe Mode for Differential Receivers, page 36.

- Added DEVRST\_N behavior during POR, see Device Reset I/Os, page 28.

# 1.3 Revision 5.0

The following is a summary of changes made in this revision.

- Added the guidelines for making MSIOD complaint with LVCMOS 3.3V, see 5 V-Input Tolerance and Output Driving Compatibility (only MSIO), page 24.

- Added information about ODT timing during power-up and power-down, see On-Die Termination, page 6.

# 1.4 Revision 4.0

The following is a summary of changes made in this revision.

- Information about programmable output drive strength was updated. See Table 8, page 17.

- Information about SSTL18 I/O standard was updated. See Table 2, page 9.

# 1.5 **Revision 3.0**

Added the Status of the V<sub>REF</sub> Pin Assigned Rule for IOA table (see Table 4, page 11).

# 1.6 Revision 2.0

The following is a summary of changes made in this revision.

- Added more information about bi-directional buffers in the Radiation Hardening section. For more information, see Radiation Hardening, page 7.

- · Added information about pre-emphasis. For more information, see Pre-Emphasis, page 15.

- Added a new table for ODT I/O standards that support ODT ON. For more information, see Table 13, page 22.

- Re-arranged the I/O bank positions as required. For more information, see Figure 3, page 8.

- Added notes for HCSL, Mini LVDS, Bus LVDS, and MLVDS. For more information, see Table 2, page 9.

- Restructured the content as required and updated the diagram. For more information, see 5 V-Input Tolerance and Output Driving Compatibility (only MSIO), page 24.

# 1.7 **Revision 1.0**

The first publication of this document.

# 2 I/O Overview

RTG4<sup>™</sup> FPGAs have several types of I/Os such as MSIO, MSIOD, double-data-rate I/O (DDRIO), and dedicated I/Os for various functions. For more information about I/O naming conventions and I/O descriptions, see *DS0130: RTG4 FPGA Pin Descriptions*.

MSIO, MSIOD, and DDRIO provide programmable I/O features such as drive strength, slew rate, input delay, weak pull-up, and weak pull-down for several voltages. The programmable I/O features are explained in detail in the I/O Programmable Features, page 14.

DDRIO is an MSIO optimized for LPDDR/DDR2/DDR3 performance. In RTG4 devices, a DDR subsystem is used to control an external DDR memory called FDDR. DDRIOs can be connected to the respective DDR subsystem PHYs or can be used as user I/Os. For more information about DDR subsystem, see *UG0567: RTG4 FPGA High Speed Serial Interfaces User Guide*.

MSIO, MSIOD, and DDRIO can be configured as fabric I/Os, whereas dedicated I/Os can be used for a single purpose such as serializer/deserializer (SerDes), device reset, or for clock functions. Dedicated I/Os cannot be used by any other circuits.

Using the Libero<sup>®</sup> SoC, MSIO, MSIOD, and DDRIO are automatically configured at power-up by fabric-related flash bits, which initialize the register blocks.

# 2.1 Functional Description

RTG4 I/Os are classified into the following three categories depending on their functional usage:

- MSIO, MSIOD, and DDRIO

- JTAG I/O

- Dedicated I/Os

# 2.1.1 MSIO, MSIOD, and DDRIO

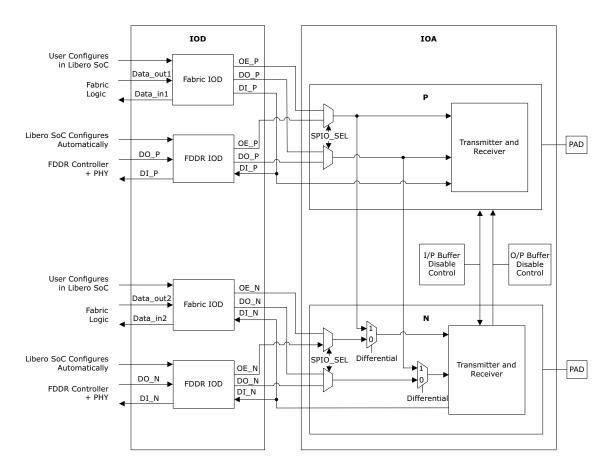

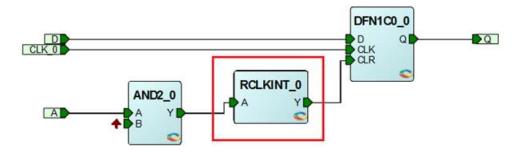

DDRIOs are shared between the fabric logic and FDDR. When the FDDR controller is used, Libero SoC automatically assigns and configures the FDDR controller signals to the respective DDRIOs. The SPIO\_SEL signal (as shown in the following figure) determines whether the fabric logic or the FDDR peripheral must be connected to the corresponding I/Os. The I/Os are set automatically selected by Libero SoC during programming. When the FDDR controller is not used, the respective DDRIOs are available to the fabric logic as shown in the following figure.

MSIO and MSIOD are directly connected to the fabric logic. For the fabric logic, each I/O port of the design must be individually assigned to I/Os in the Libero SoC.

#### Figure 1 • I/O Interconnection

The following figure shows the top-level view of I/O interconnections between the fabric logic and FDDR.

Each I/O has a highly-featured bi-directional I/O buffer. The I/O has the following two main parts, as shown in Figure 1, page 4:

- Digital IO (IOD) (includes fabric and FDDR)

- Analog IO (IOA)

IOD generates output enable (OE), data out (DO), and data in (DIN) signals for both P and N. For more information about IOD, see UG0574: RTG4 FPGA Fabric User Guide.

Each pair of P and N cells in an IOA block forms a differential pair as shown in Figure 2, page 6. Each differential pair supports differential and pseudo-differential modes of operations. It is composed of a true and complement IOA. The true IOA is called P, with positive polarity relative to the DO/DIN data signals of the P cell. The complement IOA is called N, with negative polarity relative to the DO/DIN data signals of the N cell.

IOA blocks form a ring around the periphery of the device, excluding the SerDes channel edge. The top and bottom edges of the IOA device order start with P on the left and N on the right. The left and right edges use N on the top and P on the bottom. There is one IOD for each pair of IOAs.

To support a variety of differential standards, RTG4 devices use a pair of regular P and N I/O cells. The P and N I/O cells of MSIO, MSIOD, and DDRIO can be configured as separate single-ended I/Os or as one differential I/O pair. In differential output mode, the output data signal is driven out on both the P and N cells as a differential pair, where the true signal is on the P pad and the complement signal is on the N pad.

The P and N output signals are complementary as required by the DDR1, DDR2, and DDR3 standards for CK and DQS signals. The P and N cells have to be laid out next to each other, as a pair, in order to minimize the skew rate between the two output signals of the differential pair.

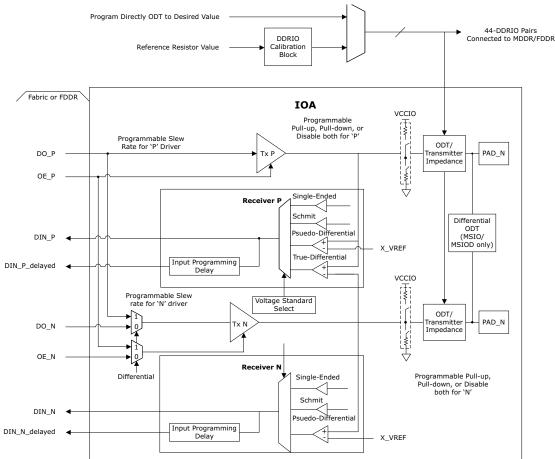

The IOA part has transmitter and receiver buffers for the P and N pair. The main circuits in the IOA are transmit and receive buffers (shown in the following figure), which support various I/O standards and contain the following modules:

- Transmit buffer

- Receive buffer

- Input programming delay

- On-die termination (ODT)

# 2.1.2 Transmit Buffer

Transmit and receive buffers transfer signals between the FPGA fabric and the IOA and also transfer signals between FDDR and the IOA.

The OE\_P and OE\_N pins control the direction of I/O buffers, as shown in the following figure. When an I/O is operated as a single-ended I/O, the OE\_P and OE\_N pins individually control the P and N I/O buffers. When an I/O is operated as a differential I/O, OE\_P controls both the P and N I/O buffers.

Depending on the current status of an output buffer, the dynamic OE enables or disables the buffer for all the standards.

## 2.1.3 Receive Buffer

Enabling and disabling of the input buffer are controlled automatically by Libero SoC.

The I/O receiver can operate in four different modes, as shown in the following figure. These modes are selected based on the flash configuration bits, which are configured during programming or after power-on. The four modes of the receiver are:

- True differential

- Pseudo-differential

- Single-ended

- Schmitt trigger

In true differential mode, the P and N pad inputs are fed to the comparator, whereas in pseudo-differential mode, each pad's input is compared to an external reference voltage. The following figure shows the detailed IOA structure of an I/O.

The I/O input can be configured as a Schmitt trigger receiver or a single-ended receiver. When Schmitt trigger inputs are selected, the input buffers present hysteresis, which filters the noise at the receiver and prevents double glitching caused by noisy input edges.

## 2.1.4 Input Programming Delay

Input delays can be used to improve the hold time of the input register by increasing input pin to input register delay. For more information about input programming delay, see I/O Programmable Features, page 14.

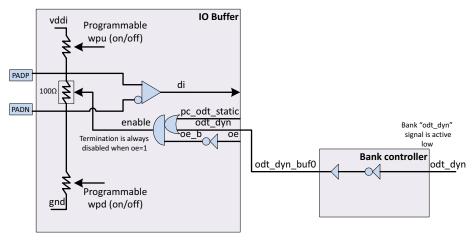

# 2.1.5 On-Die Termination

ODT improves the signaling environment by reducing the electrical discontinuities introduced with off-die termination; thus, it enables reliable operation at higher signaling rates.

The following points summarize the ODT behavior during power-down, POR (DEVRST), and user-reset scenarios:

- During power-up, ODT activation is same as inbuf timing.

- During power-down, the ODT behavior is determined by the brown-out condition. RTG4 devices do not support brown-out detection and brown-out detection varies die to die. The

- brown-out point is mentioned in AC439. Once device hits brown-out voltage on VDD, the fabric is not

functional and all the I/O configurations driven by PC bits are lost. Hence, any ODT set using PC bits

will not be available at that time.

- If the RTG4 device is held in reset using DEVRST, I/Os are tristated and hence ODT is not available.

- During user reset there is no impact on ODT because user reset is only for registers and not for I/O configurations.

For more information about the programmed ODT values for DDRIO, MSIO, and MSIOD, see the I/O Programmable Features, page 14.

#### Figure 2 • IOA Architecture

**Note:** The DIN\_P and DIN\_N pins provide the DIN\_P\_delayed and DIN\_N\_delayed input signals. The input programmable delay is provided using the I/O Constraints Editor in Libero SoC.

During the power-up cycle, ODT activation occurs at the time of activation input buffers. During the power-down cycle, the time of ODT deactivation is determined by the brown-out condition. The time at which ODT is deactivated varies from die to die because brown-out detection is absent in RTG4. The brown-out point is mentioned in *AC439: Board Design Guidelines for RTG4 FPGAs Application Note*.

Once the device hits the brown-out voltage on VDD, the fabric is not functional and the I/O configuration driven by flash bits is not available including ODT.

If the device is held in reset using DEVRST\_N, IOs are tristated. As a result, ODT is not available. A design reset has no impact on ODT because design reset is for registers and not for the I/O configuration.

# 2.2 Radiation Hardening

Radiation hardening is the act of making systems resistant to damage or malfunctioning caused by ionization radiation such as particle radiation and high-energy electromagnetic radiation, which are encountered in space, high-altitude flights, and so on. The term *hardened*, in context of FPGAs, refers to radiation hardened.

RTG4 devices have hardened input buffers for receiving clock inputs or other critical signals. There are 24 primary clock inputs on an RTG4 device. Hardening is available only on MSIO and MSIOD receivers. The DDRIO receivers are not hardened, meaning they are susceptible to radiation.

Each hardened receiver uses the triple modular redundancy (TMR) logic, that is, each receiver block is composed of three receivers with wired or connection at the output. Each hardened receiver in MSIO and MSIOD supports the following modes of operations:

- · Single-ended ratio receiver mode (LVTTL/LVCMOS) that can be programmed ON or OFF

- Reference receiver mode (SSTL/HSTL)

- Differential input mode (LVDS/RSDS)

In RTG4 devices, hardening is used only when an I/O is configured as a receiver. Therefore, when an I/O is configured as bi-directional, it is not hardened. Bi-directional buffers contain both outbuf and inbuf. Only inbuf is hardened, but not outbuf. As Bidirectional Buffer (BIBUF) contains both, on the whole it is not considered as hardened. The hardened input has a programmable on-die termination and programmable weak pull-up/pull-down (ON/OFF) per pad.

# 2.2.1 Built-in Radiation Mitigation for RTG4 I/Os

In RTG4 FPGAs, SEL mitigation is done by design in all components of the device, including I/Os. SET mitigation is built in for all MSIO and MSIOD input buffers except the input buffer of bi-directional I/Os.

- Mitigation on inputs is done by the TMR logic where three input buffers are processed in parallel. The buffer TMR is built in and made transparent when the I/O is configured as an input.

- Clock and global signals have a dedicated radiation mitigated route on the device to the global clock routing and/or CCC blocks. If the global clock routing and/or CCC blocks are not used for these hardened clock or global signals, their inputs can be routed to the fabric like any other I/Os. For nonclock and non-global inputs, the routing on-chip is not radiation hardened and thus they must use SET mitigated flip-flops in the fabric or I/O input flip-flops for any cones of logic from those inputs. Mitigation is only done on MSIO and MSIOD input buffers because of performance-power trade-off.

DDRIO requires high performance and uses twice as many buffers so the DDR input buffers are not triplicated. SEL and SET mitigations are built in for the 24 global clocks/resets as driven by MSIO or MSIOD input buffers. SET mitigation is done by triplicating global buffers and global clock tree, including any connections to/from the CCC blocks found in the corners of the device. SEU and SET mitigations are built-in for all I/O registers because they are the same as the fabric registers.

# 2.3 I/O Banks

I/Os are grouped into banks on the basis of I/O voltage standards. Each I/O bank has a dedicated I/O supply and ground voltages and uses standards compatible with the voltage supplied to the bank. There are 10 I/O banks as shown in the following figure. Every I/O bank has input and output buffers to support a wide range of standards, which require different VDD and reference voltages ( $V_{REF}$ ) for voltage-referenced standards. These voltages are externally supplied and are connected to device pins, which serve the I/O banks.

This section provides I/O Bank details of the RT4G150 device for the CG1657 and CQ352 packages.

The CG1657 package includes 10 banks— three MSIO banks, four MSIOD banks, two DDRIO banks, and one JTAG bank.

• The CQ352 package includes four banks—three MSIO banks and one JTAG bank.

Figure 3 and Figure 4 show I/O Bank locations and number of I/Os in CG1657 and CQ352 packages. For more information about RTG4 FPGA pin descriptions, supply pins, unused conditions, and packaging details, see the *DS0130: RTG4 FPGA Pin Descriptions*.

#### Figure 3 • RT4G-CG1657 I/O Bank Locations

Figure 4 • RT4G-CQ352 I/O Bank Locations

MSIOs are divided into banks, each of which may be configured to support one of the standards listed in Table 2, page 9. RTG4-CQ352 package does not include MSIOD or DDRIO pins.

The following table shows the organization of I/O banks in the RTG4 devices.

| C        | G1657 Package            | CQ35     | 2 Package       |

|----------|--------------------------|----------|-----------------|

| I/O Bank | Function                 | I/O Bank | Function        |

| Bank 0   | DDRIO for FDDR or fabric | Bank 3   | MSIO for JTAG   |

| Bank 1   | MSIOD for fabric         | Bank 4   | MSIO for fabric |

| Bank 2   | MSIOD for fabric         | Bank 5   | MSIO for fabric |

| Bank 3   | MSIO for JTAG            | Bank 6   | MSIO for fabric |

| Bank 4   | MSIO for fabric          | -        | -               |

| Bank 5   | MSIO for fabric          | -        | -               |

| Bank 6   | MSIO for fabric          | -        | -               |

| Bank 7   | MSIOD for fabric         | -        | -               |

| Bank 8   | MSIOD for fabric         | -        | -               |

| Bank 9   | DDRIO for FDDR or fabric | -        | -               |

| Bank 9   | DDRIO for FDDR or fabric | -        | -               |

| Table 1 • R | G4 Device | I/O | Banks |

|-------------|-----------|-----|-------|

|-------------|-----------|-----|-------|

# 2.4 Supported I/O Standards

The following table shows the supported voltage standards for various I/O types.

#### Table 2 • Supported Voltage Standards

| I/O Standard                                     | Single-Ended | Differential | MSIO (Max 3.3 V) | MSIOD (Max 2.5 V) | DDRIO (Max 2.5 V) |

|--------------------------------------------------|--------------|--------------|------------------|-------------------|-------------------|

| LVTTL                                            | Yes          |              | Yes              |                   |                   |

| PCI                                              | Yes          |              | Yes              |                   |                   |

| LVPECL (input<br>only)                           |              | Yes          | Yes              |                   |                   |

| LVCMOS33                                         | Yes          |              | Yes              |                   |                   |

| LVCMOS25                                         | Yes          |              | Yes              | Yes               | Yes               |

| LVCMOS18                                         | Yes          |              | Yes              | Yes               | Yes               |

| LVCMOS15                                         | Yes          |              | Yes              | Yes               | Yes               |

| LVCMOS12                                         | Yes          |              | Yes              | Yes               | Yes               |

| SSTL2I                                           | Yes          | Yes          | Yes              | Yes               | Yes (DDR1)        |

| SSTL2II                                          | Yes          | Yes          | Yes              |                   | Yes (DDR1)        |

| SSTL18I                                          | Yes          | Yes          | Yes              | Yes               | Yes (DDR2)        |

| SSTL18II                                         | Yes          | Yes          | Yes              | Yes               | Yes (DDR2)        |

| SSTL15I (only for<br>I/Os used by<br>MDDR/FDDR)  | Yes          | Yes          |                  |                   | Yes (DDR3)        |

| SSTL15II (only for<br>I/Os used by<br>MDDR/FDDR) | Yes          | Yes          |                  |                   | Yes (DDR3)        |

| LPDDRI                                           | Yes          | Yes          |                  |                   | Yes               |

| LPDDRII                                          | Yes          | Yes          |                  |                   | Yes               |

| HSTLI                                            | Yes          | Yes          | Yes              | Yes               | Yes               |

| I/O Standard          | Single-Ended | Differential | MSIO (Max 3.3 V) | MSIOD (Max 2.5 V) | DDRIO (Max 2.5 V) |

|-----------------------|--------------|--------------|------------------|-------------------|-------------------|

| HSTLII                | Yes          | Yes          |                  |                   | Yes               |

| HSTL18I               | Yes          | Yes          | Yes              | Yes               | Yes               |

| LVDS25 <sup>1</sup>   |              | Yes          | Yes              | Yes               |                   |

| LVDS33 <sup>2</sup>   |              |              | Yes              |                   |                   |

| HCSL <sup>1</sup>     |              | Yes          | Yes              | Yes               |                   |

| RSDS <sup>1</sup>     |              | Yes          | Yes              | Yes               |                   |

| MINILVDS <sup>1</sup> |              | Yes          | Yes              | Yes               |                   |

| BUSLVDS               |              | Yes          | Yes              | Yes (Only Input)  |                   |

| MLVDS                 |              | Yes          | Yes              | Yes (Only Input)  |                   |

#### Table 2 • Supported Voltage Standards (continued)

1. When VICM > 1.5 V, an external differential termination of  $100 \Omega$  (typical) or  $200 \Omega$  (typical) is required to meet the minimum input differential voltage specification of 200 mV. A  $200 \Omega$  differential termination effectively doubles the differential voltage for a given drive current compared to a  $100 \Omega$  on-die termination (ODT). For example, a 2.5 mA current produces 500 mV of differential voltage across the  $200 \Omega$  termination, whereas it produces only 250 mV across a  $100 \Omega$  termination. When using external termination, ensure ODT is disabled in Libero SoC software.

2. An external differential termination of 200 Ω (typical) is required to meet the minimum input differential voltage specification of 500 mV since the LVDS33 receiver no longer supports ODT. Libero SoC v11.8 SP1 software disables ODT for LVDS33 I/O standards. When a design with ODT-enabled LVDS33 I/Os is first opened in Libero SoC v11.8 SP1 software, the Generate Programming step is invalidated. To continue designing in this software release, disable ODT for all impacted I/O standards. If a design contains ODT-enabled LVDS33 I/Os for high-speed serial interfaces (for example, SERDES REFCLK is ODT-enabled LVDS33 I/O), these configurations with ODT-enabled are no longer supported in this software release. To continue designing in Libero SoC v11.8 SP1 software release. To continue designing in Libero SoC v11.8 SP1 software release.

For more information about I/O pin naming and assignments to specific banks, see the DS0130: RTG4 FPGA Pin Descriptions.

# 2.4.1 Single-Ended Standards

Single-ended I/O standards use a push-pull CMOS output stage with a voltage referenced to the system ground. The input buffer configuration, output drive, and I/O supply voltage (VDDI) vary among I/O standards. The advantage of these standards is that a common ground can be used for multiple I/Os. This simplifies board layout and reduces system cost. The reduced slew rate of these I/O standards minimizes electromagnetic interference (EMI) on the board.

## 2.4.1.1 Low-Voltage Transceiver Transistor Logic (LVTTL)

This is a general-purpose standard (EIA/JESD8-B) for 3.3 V applications. It uses an LVTTL input buffer and a push-pull output buffer. The LVTTL output buffer can have up to eight different programmable drive strengths.

### 2.4.1.2 Low Voltage CMOS (LVCMOS)

RTG4 devices provide five different kinds of LVCMOS:

- LVCMOS 3.3 V—an extension of the LVCMOS standard (JESD8-B compliant) used in MSIO for general-purpose 3.3 V applications.

- LVCMOS 2.5 V—an extension of the LVCMOS standard (JESD8-5-compliant) used for general-purpose 2.5 V applications.

- LVCMOS 1.8 V—an extension of the LVCMOS standard (JESD8-7-compliant) used for general-purpose 1.8 V applications.

- LVCMOS 1.5 V—an extension of the LVCMOS standard (JESD8-11-compliant) used for general-purpose 1.5 V applications.

- LVCMOS 1.2 V

The VDDI values for these standards are 3.3 V, 2.5 V, 1.8 V, 1.5 V, and 1.2 V, respectively. For MSIOs, all the versions use a 3.3 V-tolerant CMOS input buffer and a push-pull output buffer. Similar to LVTTL, the output buffer has up to eight different programmable drive strengths.

# 2.4.1.3 3.3 V Peripheral Component Interface (PCI)

This standard specifies support for both 33 MHz and 66 MHz PCI bus applications. It uses an LVTTL input buffer and a push-pull output buffer. With the aid of an external resistor, this I/O standard can be 5 V-compliant.

# 2.4.2 Voltage-Referenced Standards

I/Os are referenced to an external reference voltage (V<sub>REF</sub>).

### 2.4.2.1 Input Reference Voltage

Each I/O bank supports a reference voltage (V<sub>REF</sub>). For MSIO or MSIOD banks, any I/O in a bank can be configured as the input-reference voltage pin to be used in conjunction with voltage reference input and bi-directional buffers. A V<sub>REF</sub> pin is a regular MSIO/MSIOD that is configured as a reference voltage input in the design. MSIO/MSIOD allow any pin to be a V<sub>REF</sub> pin, but DDRIOs have dedicated V<sub>REF</sub> pins. To support SSTL and HSTL inputs, the reference voltage is typically powered with a voltage of one-half that of the bank's VDDI level.

In general, mixing of a single-ended voltage-referenced I/O with a non-referenced I/O is permitted in MSIO and MSIOD banks. The mixing of signals allows the combinations of LVCMOS, HSTL, and SSTL I/O types as long as they share the same VDDI level. However, I/O type mixing within a bank must follow the placement I/O pair restrictions between the positive differential I/O pin (IOP) and negative differential pin (ION) within an IOA block.

The following table lists the valid and invalid pairs that can be created in IOA block pins.

| IOP       | ION              | Valid/Invalid |

|-----------|------------------|---------------|

| HSTL/SSTL | Unused           | Valid         |

| HSTL/SSTL | HSTL/SSTL        | Valid         |

| HSTL/SSTL | LVCMOS/LVTTL/PCI | Invalid       |

Table 3 •IOA Pair Design Rules

- The rules mentioned in this section apply only to MSIO/MSIOD I/O types.

- The rules apply to all HSTL/SSTL Class I or Class II input, output, or bi-directional I/O.

- According to JEDEC standards, HSTL/SSTL outputs and bi-directional pins must be terminated to VTT, and inputs referenced to VTT.

- Lack of SSTL/HSTL termination or use of a non-HSTL/SSTL combination results in excessive V<sub>REF</sub> leakage. Such leakage can reduce the V<sub>REF</sub> voltage level on the board and affect the reliability of the device.

- Input V<sub>REF</sub> leakage is specified in the device datasheet.

The following table lists the assignment of ION signal, when IOP signal is assigned for  $V_{\sf REF}$  pin of MSIO/MSIOD banks.

| IOP              | ION                   | Status  |  |

|------------------|-----------------------|---------|--|

| V <sub>REF</sub> | Output                | Invalid |  |

|                  | Tristate              | Invalid |  |

|                  | <b>Bi-directional</b> | Invalid |  |

|                  | Input                 | Valid   |  |

Table 4 • Status of the V<sub>REF</sub> Pin Assigned Rule for IOA

## 2.4.2.2 High-Speed Transceiver Logic (HSTL) Class I

HSTL I is a general-purpose, high-speed 1.5 V bus standard (EIA/JESD8-6) for signaling between integrated circuits. The signaling range is 0 V to 1.5 V, and signals can be either single-ended or differential. HSTL requires a differential amplifier input buffer and a push-pull output buffer. This standard is used in the memory bus interface, with a data-switching capability of up to 400 MHz. Other advantages

of this standard are low power and fewer EMI concerns. HSTL has four classes, of which RTG4 devices support Class I. The reference voltage ( $V_{REF}$ ) for this standard is 0.75 V.

## 2.4.2.3 Stub-Series Terminated Logic 2.5 V (SSTL2) Class I and II

SSTL2 Class I and II are general-purpose 2.5 V memory bus standards (JESD8-9) designed specifically for driving the DDR SDRAM modules used in computer memory. The SSTL2 requires a differential amplifier input buffer and a push-pull output buffer. The V<sub>REF</sub> for these standards is 1.25 V.

## 2.4.2.4 Stub-Series Terminated Logic 1.8 V (SSTL18) Class I and II

SSTL18 Class I and II are general-purpose 1.8 V memory bus standards (JESD8-15), designed specifically for driving the DDR2 SDRAM modules used in computer memory. SSTL18 requires a differential amplifier input buffer and a push-pull output buffer. The V<sub>REF</sub> for these standards is 0.9 V.

### 2.4.2.5 SSTL Termination

SSTL2/SSTL18 FPGA circuitry incorporates a calibrated termination which no longer require external "stub" resistors. This implementation saves cost and board space. The circuitry provides JEDEC compliant signaling and maintains accurate signal integrity.

## 2.4.3 Differential Standards

Differential standards require two I/Os per signal, called a signal pair. Logic values are determined by the potential difference between the lines, not with respect to ground. This is why differential drivers and receivers have much better noise immunity than single-ended standards. Differential standards offer higher performance and lower power consumption than their single-ended counterparts. Two I/O pins are used for each data transfer channel; resistor termination is required on both the I/Os.

## 2.4.3.1 Low-Voltage Positive Emitter Coupled Logic (LVPECL)

When the power supply is +3.3 V, it is commonly referred to as LVPECL. LVPECL requires that one data bit is carried through two signal lines; thus two pins are needed per input. The voltage swing between the two signal lines is approximately 850 mV.

### 2.4.3.2 Low-Voltage Differential Signaling (LVDS)

LVDS is a differential I/O standard. As with all differential signaling standards, LVDS requires that one data bit is carried through two signal lines, and it has inherent noise immunity over single-ended I/O standards. The voltage swing between two signal lines is approximately 350 mV. External  $V_{\text{REF}}$  or board termination voltage (VTT) is not required. LVDS requires the use of two pins per input or output.

### 2.4.3.3 Reduced Swing Differential Signaling

Reduced swing differential signaling (RSDS) is a signaling standard that defines the output characteristics of a transmitter and input characteristics of a receiver along with the protocol for a chip-to-chip interface between flat-panel timing controllers and column drivers.

### 2.4.3.4 B-LVDS/M-LVDS

Bus LVDS (B-LVDS) refers to bus interface circuits based on LVDS technology. Multi-point LVDS (M-LVDS) specifications extend the LVDS standard to high-performance multi-point bus applications. Multi-drop and multi-point bus configurations may contain any combination of drivers, receivers, and transceivers. The LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the bus load.

The driver requires series terminations to improve signal quality and to control the voltage swing. Termination is also required at both ends of the bus because the driver can be located anywhere on the bus. The RTG4 MSIOD has an internal circuit isolation, and when using M-LVDS, the bus isolation must be implemented in the design external to the FPGA.

### 2.4.3.5 Mini-LVDS

Mini-LVDS is a serial, intra-flat panel solution that serves as an interface between the timing control function and an LCD source driver.

# 2.4.3.6 HCSL

HCSL is for PCI Express (PCIe) reference clock inputs, and is also available for many industry standard clock-generation devices.

# 2.4.4 Checking the Constraint Flow

The following section describes a constraint flow that is followed for RTG4 devices.

## 2.4.4.1 SSTL/HSTL

The design combines SSTL/HSTL I/O types with non-SSTL/HSTL I/O types such as LVCMOS, LVTTL, or PCI in a single MSIO or MSIOD bank. In an I/O pair, an SSTL/HSTL input or SSTL/HSTL bi-directional I/O is placed on PADP and a non-SSTL/HSTL I/O on PADN.

When an existing RT4G150 project created with a release prior to Libero SoC 11.7 SP1.1 is opened in the current release, a placement check on the SSTL/HSTL I/Os is triggered.

- If the design fails to the SSTL/HSTL I/O check, the design is reverted to the pre-synthesis state for an enhanced constraint flow or to the pre-compile state for the classic constraint flow.

- To continue with the design flow after the check fails, change the I/O standards or package pin assignment to remove the violation and rerun the design flow.

- **Note:** For new projects created with the current release, the SSTL/HSTL I/O check is implemented as part of the design flow.

In MSIO or MSIOD banks, the design uses SSTL/HSTL I/O inputs or SSTL/HSTL bi-directional pins without ODT or on-board terminations.

- If on-board termination is not in place, the ODT I/O attribute must be enabled in the Constraint Manager.

- The board has MSIO or MSIOD banks with unterminated pins, which can be driven completely low tied to the VSS (0 V) rail or hard tied to VSS. The pins are paired with SSTL/HSTL I/O inputs on PADN or SSTL/HSTL bi-directional pins on PADP. It is recommended to revise the board design to eliminate this condition and avoid any leakage current. For more information about board design guidelines, see AC439: Board Design Guidelines for RTG4 FPGAs Application Note.

# 3 I/O Features

This chapter describes the following I/O features that are supported in the RTG4 FPGA:

- I/O Programmable Features

- Cold Sparing

- I/Os Shared By Fabric and FDDR

- JTAG I/Os

- Dedicated I/Os

- Dedicated Global I/Os

- I/O Register Combining

- Failsafe Mode for Differential Receivers

# 3.1 I/O Programmable Features

RTG4 devices support different I/O programmable features for MSIO, MSIOD, and DDRIO. Each I/O pair (P and N) supports the following programmable features:

- Programmable input delay

- Pre-emphasis

- Programmable slew rate control

- Programmable output drive strength

- Programmable weak pull-up/pull-down

- Programmable Schmitt trigger input and receiver

- Configurable ODT and driver impedance

These features can be configured using Libero SoC or in a PDC file. For more information about I/O programmable features, see the *Libero SoC User Guide*.

The following table lists the features supported for single-ended and differential I/Os.

#### Table 5 • RTG4 I/O Features

| I/O Features                                                       | MSIO | MSIOD | DDRIO |

|--------------------------------------------------------------------|------|-------|-------|

| Single-Ended Transmitter                                           |      |       |       |

| Programmable drive strength                                        | Yes  | Yes   | Yes   |

| Programmable weak pull-up and pull-down                            | Yes  | Yes   | Yes   |

| Configurable ODT <sup>1</sup>                                      | Yes  | Yes   | Yes   |

| LVTTL/LVCMOS 3.3 V outputs compatible with external 5 V TTL inputs | Yes  |       |       |

| Pre-emphasis capability                                            |      | Yes   |       |

| Programmable slew rate                                             |      |       | Yes   |

| Single-Ended Receiver                                              |      |       |       |

| 5 V-tolerant with minimal use of external circuitry                | Yes  | Yes   |       |

| Schmitt receiver                                                   | Yes  | Yes   | Yes   |

| Programmable input delay                                           | Yes  | Yes   | Yes   |

| Differential Transmitter                                           |      |       |       |

| Programmable weak pull-up and pull-down                            | Yes  | Yes   | Yes   |

| Configurable ODT                                                   | Yes  | Yes   | Yes   |

| Programmable slew rate                                             |      |       | Yes   |

#### Table 5 • RTG4 I/O Features (continued)

| I/O Features                  | MSIO | MSIOD | DDRIO |

|-------------------------------|------|-------|-------|

| Differential Receiver         |      |       |       |

| 100 $\Omega$ differential ODT | Yes  | Yes   |       |

| Schmitt receiver              | No   | No    | No    |

| Programmable input delay      | Yes  | Yes   | Yes   |

| Programmable Slew rate        |      |       | Yes   |

1. ODT is not supported for LVCMOS18 in any Bank. See the table on page 148 of the *Libero Design Constraints User Guide* for more information about I/O types and Banks that supports ODT.

# 3.1.1 Programmable Input Delay

When configured as an input, each I/O can be programmed with different input delays. The input delay is calculated using the following equation:

$Delay = D + N \times 0.1 ns$

where N ranges from 0 to 63.

D is the intrinsic delay or circuit delay of an input (without additional delay), when N is 0. The total delay range is between D ns to D + 6.3 ns. The intrinsic delay varies depending on the slew rates—SLOW (SS), MEDIUM (TT), and FAST (FF).

Therefore, there are 65 input delay values that can be selected and configured using the I/O Constraints Editor in Libero SoC for MSIO, MSIOD, and DDRIO.

**Note:** Input delays can be used to improve the hold time of the input register by increasing the input pin to match with the input register delay.

## 3.1.2 Pre-Emphasis

Pre-emphasis is supported in transmitting high-speed signal through long cable connection. When a serial of data is transmitted through long cables, there are chances of losing the original data at the receiver end. Therefore, the serial data rate is increased by reducing losses in copper interconnect or long cables. Pre-emphasis is supported in LVDS of MSIOD banks.

Pre-emphasis is only supported in the MSIOD User IO Bank.

Pre-emphasis is used to temporarily boost the differential drive during a transition of signal from low to high or high to low. This is a temporary boost of the drive strength. The boost strength (amplitude) is programmable in multiples of the base drive strength. The boost length (width) is delay based and not PVT compensated.

The base driver of the RTG4 is 1.25 mA. Based on the legal combinations, the "required" LVDS Tx drive strength is 2.5 mA (called 2x mode). There are three options for LVDS IO type modes:

- 2x drive mode (no pre-emphasis)"= IO constraint NONE"

- 3x drive mode (2x base drive + additional 1x pre-emphasis)"= IO constraint MIN"

- 4x drive mode (2x base drive + additional 2x pre-emphasis) "=IO constraint MAX"

The base RSDS Tx drive strength is 1.25 mA (called 1x mode). There are four options for RSDS IO type modes:

- 1x drive mode (no pre-emphasis)"= IO constraint NONE"

- 2x drive mode (1x base drive + additional 1x pre-emphasis)"=IO constraint MIN"

- 3x drive mode (1x base drive + additional 2x pre-emphasis)"=IO constraint MED"

- 4x drive mode (1x base drive + additional 3x pre-emphasis)'=IO constraint MAX".

**Note:** In MSIOD, pre-emphasis is supported only on the differential output.

# 3.1.3 **Programmable Slew Rate Control**

MSIO and MSIOD do not support a user programmable slew rate, although, the MSIO and MSIOD output drive slew rate is managed, to some extent, with staggered output pre-drive stages. Each output buffer has multiple transistors connected in parallel and driven by corresponding pre-driver circuits. Delay circuit is introduced to stagger the pre-driver turn-on times and control overshooting of the switching current.

DDRIO has two bits of programmable slew control on the non-differential drive outputs. LVCMOS18, LVCMOS15, and LVCMOS12 support the minimum, medium, and maximum slew controls.

The DDRIO output drive slew rate is also managed through staggered-output pre-drive stages and by use of an impedance matched output driver.

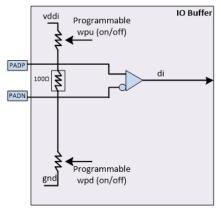

# 3.1.4 Programmable Weak Pull-Up/Pull-Down

All I/O standards support the weak pull-up, weak pull-down, and none state. The default configuration is none. These states can be configured using the I/O Constraints Editor in the Libero SoC. The weak pull-up and weak pull-down are mutually exclusive and weakly hold the output to VDDI or VSS through a 10 K  $\alpha$  resistor.

The following table lists the weak pull-up and weak pull-down support for various I/O standards.

| I/O Standard | MSIO | MSIOD | DDRIO |

|--------------|------|-------|-------|

| LVTTL33      | None |       |       |

|              | Down |       |       |

|              | Up   |       |       |

| LVCMOS33     | None |       |       |

|              | Down |       |       |

|              | Up   |       |       |

| PCI          | None |       |       |

|              | Down |       |       |

|              | Up   |       |       |

| LVCMOS12     | None | None  | None  |

|              | Down | Down  | Down  |

|              | Up   | Up    | Up    |

| LVCMOS15     | None | None  | None  |

|              | Down | Down  | Down  |

|              | Up   | Up    | Up    |

| LVCMOS18     | None | None  | None  |

|              | Down | Down  | Down  |

|              | Up   | Up    | Up    |

| LVCMOS25     | None | None  | None  |

|              | Down | Down  | Down  |

|              | Up   | Up    | Up    |

Table 6 • Weak Pull-Up/Pull-Down Support

# 3.1.5 Programmable Schmitt-Trigger Input and Receiver

The MSIO, MSIOD, and DDRIO inputs can be configured as a Schmitt-trigger receiver. Schmitt Triggers are supported for only CMOS/LVTTL Type single-ended standards. When the Schmitt trigger inputs are enabled, the input buffers present a hysteresis, filter out the noise at the receiver, and prevent double glitching caused by noise at input edges. This feature can be enabled or disabled using a physical design constraints (PDC) command or using the I/O Constraints Editor in Libero SoC. The Schmitt-trigger receiver is disabled by default.

The following table lists standards that support the Schmitt receiver feature.

| I/O Standard | MSIO | MSIOD | DDRIO |

|--------------|------|-------|-------|

| LVTTL33      | Off  |       |       |

|              | On   |       |       |

| LVCMOS33     | Off  |       |       |

|              | On   |       |       |

| PCI          | Off  |       |       |

|              | On   |       |       |

| LVCMOS12     | Off  | Off   | Off   |

|              | On   | On    | On    |

| LVCMOS15     | Off  | Off   | Off   |

|              | On   | On    | On    |

| LVCMOS18     | Off  | Off   | Off   |

|              | On   | On    | On    |

| LVCMOS25     | Off  | Off   | Off   |

|              | On   | On    | On    |

#### Table 7 • Schmitt Receiver Support

# 3.1.6 **Programmable Output Drive Strength**

The programmable current drive output buffers can be programmed to select current drive capabilities ranging from 2 mA to 16 mA. Programmable values are available only for LVTTL and LVCMOS standards, as listed in the following table. These values can be programmed for the selected I/O standards using the I/O Constraints Editor in Libero SoC.

| I/O Standard | MSIO (mA) | MSIOD (mA) | DDRIO (mA) |

|--------------|-----------|------------|------------|

| LVTTL        | 2         |            |            |

|              | 4         |            |            |

|              | 8         |            |            |

|              | 12        |            |            |

|              | 16        |            |            |

| VCMOS33 2 |    |    |

|-----------|----|----|

|           |    |    |

| 4         |    |    |

| 8         |    |    |

| 12        |    |    |

| 16        |    |    |

| VCMOS12 2 | 2  | 2  |

| 4         | 4  | 4  |

|           |    | 6  |

| VCMOS15 2 | 2  | 2  |

| 4         | 4  | 4  |

| 6         | 6  | 6  |

| 8         |    | 8  |

|           |    | 10 |

|           |    | 12 |

| VCMOS18 2 | 2  | 2  |

| 4         | 4  | 4  |

| 6         | 6  | 6  |

| 8         | 8  | 8  |

| 10        | 10 | 10 |

| 12        |    | 12 |

|           |    | 16 |

| VCMOS25 2 | 2  | 2  |

| 4         | 4  | 4  |

| 6         | 6  | 6  |

| 8         | 8  | 8  |

| 12        | 12 | 12 |

| 16        |    | 16 |

Table 8 • Recommended Output Drive Strengths (continued)

# 3.1.7 Configuring ODT and Driver Impedance

MSIO, MSIOD, and DDRIO have the ODT or transmitter impedance feature, which is calibrated depending on the I/O standard used. Only DDRIO supports calibrated ODT and driver impedance. If the impedance feature is enabled, DDRIO ODT and driver impedance can be programmed to the desired value in three ways:

- Using calibration block

- Using fixed calibration codes

- Statically and directly to desired value

There are two DDRIO calibration blocks in each RTG4 device, one of which is in the FDDR. Each calibration block calibrates ODT/driver impedance for all 44 DDRIO pairs (P and N). Table 2, page 9 shows the impedance configuration for DDRIO.

# 3.1.7.1 Calibrating the DDRIO ODT/Driver Impedance Using Calibration Block

The I/O calibration block automatically calibrates the I/O drivers to an external resistor. The impedance controller identifies the digital values, PCODE<5:0> and NCODE<5:0>. These values are fed to the soft enter pull-up/pull-down reference network to match the impedance values with external resistor values. After matching the PCODE and NCODE register values with the external resister values, they are latched and sent to the drivers.

The calibrated impedance value can be configured statically by enabling ODT\_STATIC, or dynamically by enabling ODT\_DYN. ODT\_STATIC selects the ODT value set in the flash configuration bits programmed during power-on, whereas ODT\_DYN selects the ODT value provided at run time. For more information about how to enable the calibration block, see *UG0573: RTG4 FPGA High Speed DDR Interfaces User Guide*.

The following table lists ODT impedance calibrated for the various I/O standards.

| Driver Mode               | Reference<br>Resistor (Ω) | Calibrated<br>Impedance |

|---------------------------|---------------------------|-------------------------|

| ODT, DDR3/SSTL 1.5, 1.5 V | 240                       | 120                     |

|                           |                           | 60                      |

|                           |                           | 40                      |

|                           |                           | 30                      |

|                           |                           | 20                      |

| ODT, DDR2/SSTL 1.8, 1.8 V | 150                       | 150                     |

|                           |                           | 75                      |

|                           |                           | 50                      |

| ODT, HSTL                 | 191                       | 47.8                    |

|                           |                           |                         |

#### Table 9 • Calibrated ODT Impedance

To calibrate a driver or a transmitter impedance for an I/O, configure it to the calibrated impedance according to the flash configuration bits for the appropriate I/O standard. The recommended reference resistor values listed in Table 9, page 19 are used for calibration.

The following table lists the driver and transmitter impedance values calibrated for various standards.

Table 10 • Calibrated Driver/Transmitter Impedance

| Driver Mode                   | Reference<br>Resistor (Ω) | Calibrated Impedance |

|-------------------------------|---------------------------|----------------------|

| Transmitter, DDR3 SSTL 1.5 V  | 240                       | 34                   |

|                               |                           | 40                   |

| Transmitter, DDR2 SSTL 1.8 V  | 150                       | 20                   |

|                               |                           | 42                   |

| Transmitter, DDR1 SSTL 2.5 V  | 150                       | 20                   |

|                               |                           | 42                   |

| Transmitter, LPDDR SSTL 1.8 V | 150                       | 20                   |

|                               |                           | 42                   |

| Transmitter, HSTL 1.5 V       | 191                       | 25.5                 |

|                               |                           | 47.8                 |

| Driver Mode            | Reference<br>Resistor (Ω) | Calibrated Impedance |

|------------------------|---------------------------|----------------------|

| LVCMOS 1.2 V and 1.5 V | 300                       | 75                   |

|                        |                           | 66.7                 |

|                        |                           | 50                   |

| LVCMOS 1.8 V           | 150                       | 75                   |

|                        |                           | 50                   |

|                        |                           | 33                   |

|                        |                           | 25                   |

| LVCMOS 2.5 V           | 150                       | 75                   |

|                        |                           | 50                   |

|                        |                           | 33                   |

|                        |                           | 25                   |

|                        |                           |                      |

#### Table 10 • Calibrated Driver/Transmitter Impedance (continued)

## 3.1.7.2 Calibrating ODT/Driver Impedance Using Fixed Calibration Codes

DDRIO can use fixed impedance calibration for different drive strengths, and these values can be programmed using the I/O Constraints Editor in the Libero SoC for the selected I/O standards. For more information about I/O Constraints Editor, see *Libero SoC User Guide*.

The following table lists the recommended DDRIO output drive strength values. PCODE and NCODE values are used to define internally calibrated impedance and drive strengths of the IO. Libero SoC generally programs the required PCODE/NCODE values but these values can be modified when necessary. The PCODE<5:0> and NCODE<5:0> registers are accessible through the dedicated APB configuration interface.

| I/O Standard              | NCODE | PCODE |

|---------------------------|-------|-------|

| DDR1 Full Drive/SSTL2 II  | 42    | 44    |

| DDR1 Half Drive/SSTL2 I   | 42    | 44    |

| DDR2 Full Drive/SSTL18 II | 58    | 61    |

| DDR2 Half Drive/SSTL18 I  | 58    | 61    |

| LPDDR Full Drive          | 58    | 61    |

| LPDDR Half Drive          | 58    | 61    |

| HSTL II                   | 53    | 56    |

| HSTLI                     | 53    | 56    |

| LVCMOS25 16 mA            | 42    | 44    |

| LVCMOS25 12 mA            | 42    | 44    |

| LVCMOS25 8 mA             | 42    | 44    |

| LVCMOS25 6 mA             | 42    | 44    |

| LVCMOS25 4 mA             | 42    | 44    |

| LVCMOS25 2 mA             | 42    | 44    |

| LVCMOS18 16 mA            | 58    | 61    |

| LVCMOS18 12 mA            | 58    | 61    |

|                           |       |       |

#### Table 11 • Recommended PCODE and NCODE Values

| I/O Standard   | NCODE | PCODE |

|----------------|-------|-------|

| LVCMOS18 10 mA | 58    | 61    |

| LVCMOS18 8 mA  | 58    | 61    |

| LVCMOS18 6 mA  | 58    | 61    |

| LVCMOS18 4 mA  | 58    | 61    |

| LVCMOS18 2 mA  | 58    | 61    |

| LVCMOS15 12 mA | 53    | 56    |

| LVCMOS15 10 mA | 53    | 56    |

| LVCMOS15 8 mA  | 53    | 56    |

| LVCMOS15 6 mA  | 53    | 56    |

| LVCMOS15 4 mA  | 53    | 56    |

| LVCMOS15 2 mA  | 53    | 56    |

| LVCMOS12 6 mA  | 40    | 42    |

| LVCMOS12 4 mA  | 40    | 42    |

| LVCMOS12 2 mA  | 40    | 42    |

Table 11 • Recommended PCODE and NCODE Values (continued)

## 3.1.7.3 Configuring ODT/Driver Impedance Statically to Desired Value Directly

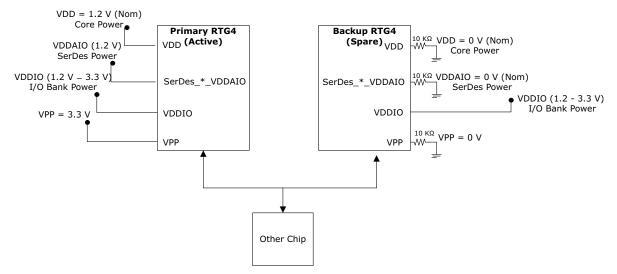

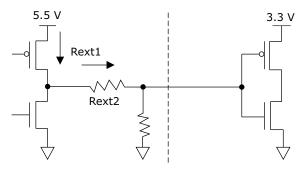

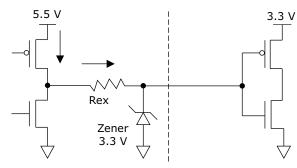

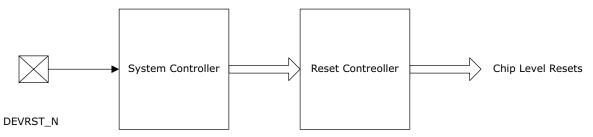

ODT/drivers can directly be calibrated to a desired value by providing PCODE<5:0> and NCODE<5:0> values through the dedicated APB configuration interface—FIC2. When this is done, the values are overwritten with the existing values. For more information about how to configure the PCODE and NCODE values, see the FDDR I/O Calibration Control register of the System Register Block in the UG0573: RTG4 FPGA High Speed DDR Interfaces User Guide.