# **ReadTheDocs-Breathe Documentation**

Release 1.0.0

**Thomas Edvalson**

# Contents

| 1                            | Goin                                              | g to 11: | Amping           | Up the Programming-Language Run-Time Foundation                                    | 3  |

|------------------------------|---------------------------------------------------|----------|------------------|------------------------------------------------------------------------------------|----|

| 2                            | Solid Compilation Foundation and Language Support |          |                  | 5                                                                                  |    |

|                              | 2.1                                               | Quick    | uick Start Guide |                                                                                    |    |

|                              |                                                   | 2.1.1    | Current          | t Release Notes                                                                    | 5  |

|                              |                                                   | 2.1.2    | Installa         | tion Guide                                                                         | 5  |

|                              |                                                   | 2.1.3    | Prograi          | mming Guide                                                                        | 6  |

|                              |                                                   | 2.1.4    | _                | GPU Tunning Guides                                                                 | 7  |

|                              |                                                   | 2.1.5    |                  | SA Manuals                                                                         | 7  |

|                              |                                                   | 2.1.6    |                  | API References                                                                     | 7  |

|                              |                                                   | 2.1.7    | ROCm             | Tools                                                                              | 8  |

|                              |                                                   | 2.1.8    |                  | Libraries                                                                          | 9  |

|                              |                                                   | 2.1.9    |                  | Compiler SDK                                                                       | 10 |

|                              |                                                   | 2.1.10   |                  | System Management                                                                  | 10 |

|                              |                                                   | 2.1.11   |                  | Virtualization & Containers                                                        | 10 |

|                              |                                                   | 2.1.12   |                  | e Device Programming                                                               | 11 |

| 2.1.13 Deep Learning on ROCm |                                                   |          | 11               |                                                                                    |    |

| 2.1.14 System Level Debug    |                                                   | 11       |                  |                                                                                    |    |

|                              |                                                   | 2.1.15   | -                | 1                                                                                  | 11 |

|                              |                                                   | 2.1.16   |                  | Glossary                                                                           | 12 |

|                              | 2.2                                               | Currer   |                  | Notes                                                                              | 12 |

|                              |                                                   | 2.2.1    |                  | atures and enhancements in ROCm 2.1                                                | 12 |

|                              |                                                   |          | 2.2.1.1          | RocTracer v1.0 preview release – 'rocprof' HSA runtime tracing and statistics sup- |    |

|                              |                                                   |          |                  | port                                                                               | 12 |

|                              |                                                   |          | 2.2.1.2          | Improvements to ROCM-SMI tool                                                      | 12 |

|                              |                                                   |          | 2.2.1.3          | DGEMM Optimizations                                                                | 12 |

|                              |                                                   | 2.2.2    | New fe           | atures and enhancements in ROCm 2.0                                                | 12 |

|                              |                                                   |          | 2.2.2.1          | Adds support for RHEL 7.6 / CentOS 7.6 and Ubuntu 18.04.1                          | 12 |

|                              |                                                   |          | 2.2.2.2          | Adds support for Vega 7nm, Polaris 12 GPUs                                         | 12 |

|                              |                                                   |          | 2.2.2.3          | Introduces MIVisionX                                                               | 12 |

|                              |                                                   |          | 2.2.2.4          | Improvements to ROCm Libraries                                                     | 12 |

|                              |                                                   |          | 2.2.2.5          | MIOpen                                                                             | 12 |

|                              |                                                   |          | 2.2.2.6          | Tensorflow multi-gpu and Tensorflow FP16 support for Vega 7nm                      | 13 |

|                              |                                                   |          | 2.2.2.7          | PyTorch/Caffe2 with Vega 7nm Support                                               | 13 |

|                              |                                                   |          | 2.2.2.8          | Improvements to ROCProfiler tool                                                   | 13 |

|                              |                                                   |          | 2.2.2.9          | Support for hipStreamCreateWithPriority                                            | 13 |

|                              |                                                   |          |                  | ** *                                                                               |    |

|     |       | 2.2.2.11<br>2.2.2.12 | Improve<br>Kuberne | 2.0 support                                                        | 13<br>13 |

|-----|-------|----------------------|--------------------|--------------------------------------------------------------------|----------|

|     |       |                      |                    | d features                                                         | 13       |

|     | 2.2.3 |                      |                    | enhancements in ROCm 1.9.2                                         | 13       |

|     |       | 2.2.3.1              |                    | MPI) support on Vega 7nm                                           | 13       |

|     |       | 2.2.3.2              |                    | ments to HCC                                                       | 14       |

|     |       | 2.2.3.3              |                    | ments to ROCProfiler tool                                          | 14       |

|     | 2.2.4 | 2.2.3.4              | Critical           | bug fixes                                                          | 14       |

|     | 2.2.4 |                      |                    | enhancements in ROCm 1.9.1                                         | 14       |

|     |       | 2.2.4.1              | Added L            | PPM support to Vega 7nm                                            | 14       |

|     |       | 2.2.4.2              |                    | 'ROCm profiling' "Version mismatch between HSA runtime and libhsa- | 1.4      |

|     | 225   | NI C                 |                    | tools64.so.1" error                                                | 14       |

|     | 2.2.5 |                      |                    | enhancements in ROCm 1.9.0                                         | 14       |

|     |       | 2.2.5.1              |                    | for Vega 7nm                                                       | 14       |

|     |       | 2.2.5.2              |                    | Management Interface                                               | 14       |

|     |       | 2.2.5.3              |                    | ments to HIP/HCC                                                   | 14       |

|     |       | 2.2.5.4              |                    | for rocprof Profiling Tool                                         | 14       |

|     |       | 2.2.5.5              |                    | for rocr Debug Agent rocr_debug_agent                              | 15       |

|     |       | 2.2.5.6              |                    | tribution support                                                  | 15       |

| 2.2 | DOG   | 2.2.5.7              |                    | .9 is ABI compatible with KFD in upstream Linux kernels            | 15       |

| 2.3 |       |                      |                    |                                                                    | 15       |

|     | 2.3.1 |                      |                    | Yersion: 2.1                                                       | 15       |

|     | 2.3.2 |                      |                    | t                                                                  | 15       |

|     |       | 2.3.2.1              |                    | ed GPUs                                                            | 15       |

|     |       | 2.3.2.2              |                    | ed CPUs                                                            | 16       |

|     |       | 2.3.2.3              |                    | ported or limited support under ROCm                               | 17       |

|     |       |                      | .3.2.3.1           | Limited support                                                    | 17       |

|     |       |                      | .3.2.3.2           | Not supported                                                      | 17       |

|     | 2.3.3 |                      |                    | platform - ROCm 2.1                                                | 18       |

|     |       | 2.3.3.1              |                    | ed Operating Systems - New operating systems available             | 19       |

|     |       | 2.3.3.2              |                    | upport in upstream Linux kernels                                   | 19       |

|     | 2.3.4 |                      |                    | MD ROCm repositories                                               | 20       |

|     |       | 2.3.4.1              |                    | Binary Package Structure                                           | 20       |

|     |       | 2.3.4.2              |                    | Support - installing from a Debian repository                      | 22       |

|     |       |                      | .3.4.2.1           | First make sure your system is up to date                          | 22       |

|     |       |                      | .3.4.2.2           | Add the ROCm apt repository                                        | 22       |

|     |       |                      |                    | Install                                                            | 23       |

|     |       |                      | .3.4.2.4           | Next set your permissions                                          | 23       |

|     |       |                      | .3.4.2.5           | Test basic ROCm installation                                       | 23       |

|     |       |                      | .3.4.2.6           | Performing an OpenCL-only Installation of ROCm                     | 23       |

|     |       |                      | .3.4.2.7           | How to uninstall from Ubuntu 16.04 or Ubuntu 18.04                 | 24       |

|     |       |                      | .3.4.2.8           | Installing development packages for cross compilation              | 24       |

|     |       |                      | .3.4.2.9           | Using Debian-based ROCm with upstream kernel drivers               | 24       |

|     |       | 2.3.4.3              |                    | RHEL 7 (7.4, 7.5, 7.6) Support                                     | 24       |

|     |       |                      | .3.4.3.1           | Preparing RHEL 7 (7.4, 7.5, 7.6) for installation                  | 24       |

|     |       |                      | .3.4.3.2           | Install and setup Devtoolset-7                                     | 25       |

|     |       |                      | .3.4.3.3           | Prepare CentOS/RHEL (7.4, 7.5, 7.6) for DKMS Install               | 25       |

|     |       |                      | .3.4.3.4           | Installing ROCm on the system                                      | 25       |

|     |       |                      | .3.4.3.5           | Set up permissions                                                 | 25       |

|     |       |                      | .3.4.3.6           | Compiling applications using HCC, HIP, and other ROCm software     | 26       |

|     |       |                      | .3.4.3.7           | How to uninstall ROCm from CentOS/RHEL 7.4, 7.5 and 7.6            | 26       |

|     |       |                      | .3.4.3.8           | Installing development packages for cross compilation              | 26       |

|     |       | 2.                   | .3.4.3.9           | Using ROCm with upstream kernel drivers                            | 27       |

|     | 2.3.5 | Known 2.3.5.1 2.3.5.2 |                                                                                | 27<br>27 |

|-----|-------|-----------------------|--------------------------------------------------------------------------------|----------|

|     |       |                       | rsmi_dev_power_profile_set() will not work for all but the first gpu in multi- |          |

|     |       |                       |                                                                                | 27       |

|     | 2.3.6 |                       | <u>.</u>                                                                       | 27       |

|     | 2.3.7 | _                     |                                                                                | 27       |

|     |       | 2.3.7.1               |                                                                                | 27       |

|     |       |                       |                                                                                | 28       |

|     | 2 2 0 |                       |                                                                                | 28       |

| 2 1 | 2.3.8 |                       |                                                                                | 28       |

| 2.4 |       |                       |                                                                                | 28       |

|     | 2.4.1 |                       |                                                                                | 28       |

|     |       | 2.4.1.1               |                                                                                | 28       |

|     |       | 2.4.1.2               |                                                                                | 28       |

|     |       | 2.4.1.3               |                                                                                | 29       |

|     |       | 2.4.1.4               |                                                                                | 29       |

|     |       | 2.4.1.5               |                                                                                | 29       |

|     |       | 2.4.1.6               |                                                                                | 29       |

|     |       | 2.4.1.7               | 1                                                                              | 30       |

|     |       | 2.4.1.8               |                                                                                | 30       |

|     |       | 2.4.1.9               |                                                                                | 30       |

|     |       | 2.4.1.10              |                                                                                | 30       |

|     |       | 2.4.1.11<br>2.4.1.12  | 1 1                                                                            | 30<br>32 |

|     |       |                       |                                                                                | 33       |

|     | 2.4.2 |                       |                                                                                | 33       |

|     | 2.4.2 | 2.4.2.1               |                                                                                | 33       |

|     |       | 2.4.2.1               | 1                                                                              | 34       |

|     |       | 2.4.2.3               | 1                                                                              | 34       |

|     |       | 2.4.2.4               |                                                                                | 34       |

|     |       | 2.4.2.5               |                                                                                | 34       |

|     |       | 2.4.2.6               |                                                                                | 35       |

|     |       | 2.4.2.7               |                                                                                | 36       |

|     |       | 2.4.2.8               |                                                                                | 36       |

|     |       | 2.4.2.9               | 1                                                                              | 37       |

|     | 2.4.3 |                       | , 66                                                                           | 37       |

|     | 2.1.5 | 2.4.3.1               |                                                                                | 38       |

|     |       | 2.4.3.2               |                                                                                | 38       |

|     |       | 2.4.3.3               | *                                                                              | 39       |

|     |       | 2.4.3.4               |                                                                                | 10       |

|     |       |                       |                                                                                | 10       |

|     |       | 2.                    |                                                                                | 11       |

|     |       | 2.                    |                                                                                | 12       |

|     |       | 2.                    | 4.3.4.4 Overhead                                                               | 13       |

|     |       | 2.                    |                                                                                | 13       |

|     |       | 2.4.3.5               | API documentation                                                              | 13       |

|     | 2.4.4 | HIP Pro               | graming Guide                                                                  | 13       |

|     | 2.4.5 | HIP Bes               | st Practices                                                                   | 14       |

|     | 2.4.6 |                       |                                                                                | 14       |

|     | 2.4.7 | OpenCL                | Best Practices                                                                 | 14       |

| 2.5 |       |                       | e                                                                              | 14       |

|     | 2.5.1 |                       |                                                                                | 14       |

|     | 2.5.2 | GFX8 T                | Suning Guide                                                                   | 14       |

|     | 2.5.3 Vega  | Tuning Guide                                                        |

|-----|-------------|---------------------------------------------------------------------|

| 2.6 | GCN ISA Mar | nuals                                                               |

|     | 2.6.1 GCN   | 1.1                                                                 |

|     | 2.6.2 GCN   | 2.0                                                                 |

|     | 2.6.3 Vega  |                                                                     |

|     |             | GCN ISA Assembly Guide                                              |

|     | 2.6.4.1     | The Art of AMDGCN Assembly: How to Bend the Machine to Your Will 45 |

|     | 2.6.4.2     | DS Permute Instructions                                             |

|     | 2.6.4.3     | Passing Parameters to a Kernel                                      |

|     | 2.6.4.4     | The GPR Counting                                                    |

|     | 2.6.4.5     | Compiling GCN ASM Kernel Into Hsaco                                 |

| 2.7 |             | ferences                                                            |

| 2.1 |             | System Runtime API                                                  |

|     |             | Language Runtime API                                                |

|     |             |                                                                     |

|     |             |                                                                     |

|     |             | Math API         49                                                 |

|     |             | t API Documentation                                                 |

|     |             | Library API's                                                       |

|     |             | Learning API's                                                      |

| 2.8 |             |                                                                     |

|     |             |                                                                     |

|     | 2.8.1.1     | Download HCC                                                        |

|     | 2.8.1.2     | Build HCC from source                                               |

|     | 2.8.1.3     | Use HCC                                                             |

|     | 2.8.1.4     | Multiple ISA                                                        |

|     | 2.8.1.5     | CodeXL Activity Logger                                              |

|     | 2.8.1.6     | HCC with ThinLTO Linking                                            |

|     | 2.8.2 GCN   | Assembler and Disassembler                                          |

|     | 2.8.3 GCN   | Assembler Tools                                                     |

|     | 2.8.4 ROC   | Profiler                                                            |

|     | 2.8.4.1     | Download                                                            |

|     | 2.8.4.2     | Build                                                               |

|     | 2.8.4.3     | Profiling Tool 'rocprof' Usage                                      |

|     |             | Debug Agent                                                         |

|     |             | n-GDB                                                               |

|     |             | n-Profiler                                                          |

|     |             | XL                                                                  |

|     |             | Motivation                                                          |

|     | 2.8.8.2     | Installation and Build                                              |

|     | 2.8.8.3     | Contributors                                                        |

|     |             |                                                                     |

|     | 2.8.8.4     | License                                                             |

|     | 2.8.8.5     | Attribution and Copyrights                                          |

|     | 1           | perfAPI                                                             |

|     | 2.8.9.1     | Major Features                                                      |

|     | 2.8.9.2     | What's New                                                          |

|     | 2.8.9.3     | System Requirements                                                 |

|     | 2.8.9.4     | Cloning the Repository                                              |

|     | 2.8.9.5     | Source Code Directory Layout                                        |

|     | 2.8.9.6     | Public" vs "Internal" Versions                                      |

|     | 2.8.9.7     | Known Issues                                                        |

|     |             | n Binary Utilities                                                  |

|     |             | $\operatorname{sion} X$                                             |

|     | 2.8.11.1    | I AMD OpenVX (amd_openvx)                                           |

|     |             | 2.8.11.1.1 Features                                                 |

| 2.8.11.1.2                      | Pre-requisites:                                                            |    |

|---------------------------------|----------------------------------------------------------------------------|----|

| 2.8.11.1.3                      | Build Instructions                                                         | 1  |

| 2.8.11.1.4                      | Build using Visual Studio Professional 2013 on 64-bit Windows 10/8.1/7 . 7 | 1  |

| 2.8.11.1.5                      | Build using CMake                                                          | 1  |

| 2.8.11.2 AMD C                  | OpenVX Extensions (amd_openvx_extensions)                                  | 2  |

| 2.8.11.2.1                      | Radeon Loom Stitching Library (vx_loomsl)                                  | 2  |

| 2.8.11.2.2                      | OpenVX Neural Network Extension Library (vx_nn)                            | 4  |

| 2.8.11.2.3                      |                                                                            | 5  |

| 2.8.11                          | 1.2.3.1 Build Instructions                                                 | 6  |

| 2.8.11.3 Applica                | tions                                                                      | 6  |

| 2.8.11.3.1                      |                                                                            |    |

| 2.8.11.3.2                      | Convert Neural Net models into AMD NNIR and OpenVX Code 7                  |    |

| 2.8.11.3.3                      | ±                                                                          |    |

|                                 | s                                                                          |    |

| 2.8.11.4.1                      |                                                                            |    |

|                                 | onX Toolkit                                                                |    |

|                                 | 8                                                                          |    |

|                                 |                                                                            |    |

| 2.8.11.7 Fie-iequ<br>2.8.11.7.1 |                                                                            |    |

| 2.8.11.7.2                      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                    |    |

|                                 |                                                                            |    |

|                                 | MVisionX                                                                   |    |

| 2.8.11.8.1                      | 8 (                                                                        |    |

| 2.8.11.8.2                      | 11 8                                                                       | .3 |

| 2.8.11.8.3                      |                                                                            |    |

|                                 | Windows 10/8.1/7                                                           |    |

|                                 | 8                                                                          |    |

| 2.8.11.9.1                      |                                                                            |    |

| 2.8.11.9.2                      | 1                                                                          |    |

| 2.8.11.9.3                      |                                                                            |    |

|                                 | Notes                                                                      |    |

|                                 | 1 Supported Neural Net Layers                                              |    |

|                                 | 2 Known issues                                                             |    |

|                                 | 3 Tested configurations                                                    | 5  |

| 2.9 ROCm Libraries              | 8                                                                          | 5  |

| 2.9.1 rocFFT                    | 8                                                                          | 5  |

| 2.9.1.1 API des                 | sign                                                                       | 5  |

| 2.9.1.2 Installin               | ng pre-built packages                                                      | 5  |

| 2.9.1.3 Quickst                 | art rocFFT build                                                           | 5  |

| 2.9.1.4 Exampl                  | e                                                                          | 6  |

| 2.9.2 rocBLAS                   |                                                                            | 7  |

| 2.9.2.1 Installin               | ng pre-built packages                                                      | 7  |

|                                 | art rocBLAS build                                                          | 7  |

| _                               | build (all supported platforms)                                            | 7  |

|                                 | AS interface examples                                                      |    |

| 2.9.2.5 GEMV                    |                                                                            |    |

|                                 | l and strided GEMM API                                                     |    |

|                                 | ronous API                                                                 |    |

| 2.9.2.8 API                     |                                                                            |    |

| 2.9.2.8 ATT 2.9.2.8.1           | Types                                                                      |    |

| 2.9.2.6.1                       | *1                                                                         |    |

| 2.9.2.                          |                                                                            |    |

| 2.9.2.                          | <del>-</del>                                                               |    |

|                                 | _ 6                                                                        |    |

| 2.9.2.                          | 1                                                                          |    |

| 2.9.2.                          | 8.1.5 rocblas_double_complex                                               | y  |

| 2.9.2.8.1.6                  | rocblas_half                                     |

|------------------------------|--------------------------------------------------|

| 2.9.2.8.1.7                  | rocblas_half_complex                             |

| 2.9.2.8.1.8                  | rocblas_handle                                   |

| 2.9.2.8.1.9                  | Enums                                            |

| 2.9.2.8.1.10                 | rocblas_operation                                |

| 2.9.2.8.1.11                 | rocblas_fill                                     |

| 2.9.2.8.1.12                 | rocblas_diagonal                                 |

| 2.9.2.8.1.13                 | rocblas_side                                     |

| 2.9.2.8.1.14                 | rocblas_status                                   |

| 2.9.2.8.1.15                 | rocblas_datatype                                 |

| 2.9.2.8.1.16                 | rocblas_pointer_mode                             |

| 2.9.2.8.1.17                 | rocblas_layer_mode                               |

| 2.9.2.8.1.18                 | rocblas_gemm_algo                                |

|                              | tions                                            |

| 2.9.2.8.2.1                  | Level 1 BLAS                                     |

| 2.9.2.8.2.2                  | rocblas_ <type>scal()</type>                     |

|                              |                                                  |

| 2.9.2.8.2.3                  | rocblas_ <type>copy()</type>                     |

| 2.9.2.8.2.4                  | rocblas_ <type>dot()</type>                      |

| 2.9.2.8.2.5                  | rocblas_ <type>swap()</type>                     |

| 2.9.2.8.2.6                  | rocblas_ <type>axpy()</type>                     |

| 2.9.2.8.2.7                  | rocblas_ <type>asum()</type>                     |

| 2.9.2.8.2.8                  | rocblas_ <type>nrm2()</type>                     |

| 2.9.2.8.2.9                  | rocblas_i <type>amax()</type>                    |

| 2.9.2.8.2.10                 | rocblas_i <type>amin()</type>                    |

| 2.9.2.8.2.11                 | Level 2 BLAS                                     |

| 2.9.2.8.2.12                 | rocblas_ <type>gemv()</type>                     |

| 2.9.2.8.2.13                 | rocblas_ <type>ger()</type>                      |

| 2.9.2.8.2.14                 | rocblas_ <type>syr()</type>                      |

| 2.9.2.8.2.15                 | Level 3 BLAS                                     |

| 2.9.2.8.2.16                 | rocblas_ <type>trtri_batched()</type>            |

| 2.9.2.8.2.17                 | rocblas_ <type>trsm()</type>                     |

| 2.9.2.8.2.18                 | rocblas_ <type>gemm()</type>                     |

| 2.9.2.8.2.19                 | rocblas_ <type>gemm_strided_batched() 100</type> |

| 2.9.2.8.2.20                 | rocblas_ <type>gemm_kernel_name() 100</type>     |

| 2.9.2.8.2.21                 | rocblas_ <type>geam()</type>                     |

| 2.9.2.8.2.22                 | BLAS Extensions                                  |

| 2.9.2.8.2.23                 | rocblas_gemm_ex()                                |

| 2.9.2.8.2.24                 | rocblas_gemm_strided_batched_ex()                |

| 2.9.2.8.2.25                 | Build Information                                |

| 2.9.2.8.2.26                 | rocblas_get_version_string()                     |

| 2.9.2.8.2.27                 | Auxiliary                                        |

| 2.9.2.8.2.28                 | rocblas_pointer_to_mode()                        |

| 2.9.2.8.2.29                 | rocblas_create_handle()                          |

| 2.9.2.8.2.30                 | rocblas_destroy_handle()                         |

| 2.9.2.8.2.31                 | rocblas_add_stream()                             |

| 2.9.2.8.2.32                 | rocblas_set_stream()                             |

| 2.9.2.8.2.33                 | rocblas_get_stream()                             |

| 2.9.2.8.2.34                 | rocblas_set_pointer_mode()                       |

| 2.9.2.8.2.35                 | rocblas_get_pointer_mode()                       |

| 2.9.2.8.2.36                 |                                                  |

|                              |                                                  |

| 2.9.2.8.2.37<br>2.9.2.8.2.38 | rocblas_get_vector()                             |

|                              |                                                  |

| 2.9.2.8.2.39                 | rocblas_get_matrix()                             |

| 2.9.3 hipBLAS                |                                                  |

|        | 2.9.3.1   | Installing pre-built packages         | )5 |

|--------|-----------|---------------------------------------|----|

|        | 2.9.3.2   | Quickstart hipBLAS build              | )5 |

|        | 2.9.3.3   | hipBLAS interface examples            | )5 |

|        | 2.9.3.4   | GEMV API                              |    |

|        | 2.9.3.5   | Batched and strided GEMM API          |    |

| 2.9.4  | hcRNG     |                                       |    |

|        | 2.9.4.1   | Introduction                          |    |

|        | 2.9.4.2   | Examples                              |    |

|        | 2.9.4.3   | Installation                          |    |

|        | 2.9.4.4   | Key Features                          |    |

|        | 2.9.4.5   | Tested Environments                   |    |

|        | 2.9.4.6   | Unit testing                          |    |

| 2.9.5  |           | 11                                    |    |

| 2.9.3  |           |                                       |    |

|        | 2.9.5.1   | Installation instructions for ROCm    |    |

|        | 2.9.5.2   | Installing from AMD ROCm repositories |    |

|        | 2.9.5.3   | Installation instructions for Eigen   |    |

|        | 2.9.5.4   | Build and Run hipeigen direct tests   |    |

| 2.9.6  |           |                                       |    |

|        | 2.9.6.1   | Introduction to clFFT                 |    |

|        | 2.9.6.2   | clFFT library user documentation      |    |

|        | 2.9.6.3   | API semantic versioning               |    |

|        | 2.9.6.4   | clFFT Wiki                            | 13 |

|        | 2.9.6.5   | Contributing code                     | 3  |

|        | 2.9.6.6   | License                               | 13 |

|        | 2.9.6.7   | Example                               | 13 |

|        | 2.9.6.8   | Build dependencies                    |    |

|        | 2.9.6.9   | Performance infrastructure            |    |

| 2.9.7  | clBLAS    |                                       |    |

|        | 2.9.7.1   | clBLAS library user documentation     |    |

|        | 2.9.7.2   | License                               |    |

|        | 2.9.7.3   | Example                               |    |

|        | 2.9.7.4   | Build dependencies                    |    |

|        | 2.9.7.5   | Performance infrastructure            |    |

| 2.9.8  |           | SE                                    |    |

| 2.7.0  | 2.9.8.1   | What's new in clSPARSE v0.10.1        |    |

|        | 2.9.8.2   | clSPARSE features                     |    |

|        | 2.9.8.3   | API semantic versioning               |    |

|        |           | License                               |    |

| 200    | 2.7.0.1   |                                       |    |

| 2.9.9  |           |                                       |    |

|        | 2.9.9.1   | What's New                            |    |

|        | 2.9.9.2   | Building                              |    |

|        | 2.9.9.3   | Example Instructions for Linux        |    |

|        | 2.9.9.4   | Building the documentation manually   |    |

| 2.9.10 | hcFFT     |                                       |    |

|        | 2.9.10.1  | Installation                          |    |

|        | 2.9.10.2  | Introduction                          |    |

|        | 2.9.10.3  | KeyFeature                            |    |

|        | 2.9.10.4  | Examples                              | 27 |

|        | 2.9.10.5  | Tested Environments                   | 28 |

| 2.9.11 | Tensile . |                                       | 28 |

|        | 2.9.11.1  | Benchmark Config                      | 29 |

|        | 2.9.11.2  | Benchmark Protocol                    | 32 |

|        | 2.9.11.3  | Dependencies                          | 34 |

|        | 2.9.11.4  | Kernel Parameters                     |    |

|      | 2.9.11.5 Languages                                                         | 136 |

|------|----------------------------------------------------------------------------|-----|

|      | 2.9.11.6 Problem Nomenclature                                              |     |

|      | 2.9.11.7 Tensile.lib                                                       | 138 |

|      | 2.9.12 rocALUTION                                                          | 139 |

|      | 2.9.12.1 Introduction                                                      | 139 |

|      | 2.9.12.2 Overview                                                          | 139 |

|      | 2.9.12.3 Building and Installing                                           |     |

|      | 2.9.12.4 Installing from AMD ROCm repositories                             |     |

|      | 2.9.12.5 Building rocALUTION from Open-Source repository                   |     |

|      | 2.9.12.6 Download rocALUTION                                               |     |

|      | 2.9.12.7 Using <i>install.sh</i> to build dependencies + library           |     |

|      | 2.9.12.8 Using <i>install.sh</i> to build dependencies + library + client  |     |

|      | 2.9.12.9 Using individual commands to build rocALUTION                     |     |

|      | 2.9.12.10 Common build problems                                            |     |

|      | 2.9.12.11 Simple Test                                                      |     |

|      |                                                                            |     |

|      | 2.9.13 rocSPARSE                                                           |     |

|      | 2.9.13.1 Introduction                                                      |     |

|      | 2.9.13.2 Device and Stream Management                                      |     |

|      | 2.9.13.3 Asynchronous Execution                                            |     |

|      | 2.9.13.4 HIP Device Management                                             |     |

|      | 2.9.13.5 HIP Stream Management                                             |     |

|      | 2.9.13.6 Multiple Streams and Multiple Devices                             |     |

|      | 2.9.13.7 Building and Installing                                           |     |

|      | 2.9.13.8 Installing from AMD ROCm repositories                             |     |

|      | 2.9.13.9 Building rocSPARSE from Open-Source repository                    |     |

|      | 2.9.13.10 Download rocSPARSE                                               |     |

|      | 2.9.13.11 Using <i>install.sh</i> to build dependencies + library          |     |

|      | 2.9.13.12 Using <i>install.sh</i> to build dependencies + library + client |     |

|      | 2.9.13.13 Using individual commands to build rocSPARSE                     | 145 |

|      | 2.9.13.14 Common build problems                                            | 146 |

| 2.10 | ROCm Compiler SDK                                                          | 147 |

|      | 2.10.1 GCN Native ISA LLVM Code Generator                                  | 147 |

|      | 2.10.2 ROCm Code Object Format                                             | 147 |

|      | 2.10.3 ROCm Device Library                                                 | 147 |

|      | 2.10.3.1 OVERVIEW                                                          | 147 |

|      | 2.10.3.2 BUILDING                                                          | 147 |

|      | 2.10.3.3 USING BITCODE LIBRARIES                                           |     |

|      | 2.10.3.4 TESTING                                                           |     |

|      | 2.10.4 ROCr Runtime                                                        |     |

|      | 2.10.4.1 HSA Runtime API and runtime for ROCm                              |     |

|      | 2.10.4.2 Source code                                                       |     |

|      | 2.10.4.3 Binaries for Ubuntu & Fedora and installation instructions        |     |

|      | 2.10.4.4 Infrastructure                                                    |     |

|      | 2.10.4.5 Sample                                                            |     |

|      | 2.10.4.6 Known issues                                                      |     |

| 2.11 |                                                                            |     |

| 2.11 | 2.11.1 ROCm-SMI                                                            |     |

|      |                                                                            |     |

|      | 2.11.1.1 Programing ROCm-SMI                                               |     |

|      | 2.11.2 SYSFS Interface                                                     |     |

|      | 2.11.2.1 Naming and data format standards for sysfs files                  |     |

|      | 2.11.2.1.1 Global attributes                                               |     |

|      | 2.11.2.1.2 Voltages                                                        |     |

|      | 2.11.2.1.3 Fans                                                            |     |

|      | 2.11.2.1.4 PWM                                                             | 163 |

|      | 2.11.2.1.5 Temperatures                                                              |

|------|--------------------------------------------------------------------------------------|

|      | 2.11.2.1.6 Currents                                                                  |

|      | 2.11.2.1.7 Power                                                                     |

|      | 2.11.2.1.8 Energy                                                                    |

|      | 2.11.2.1.9 Humidity                                                                  |

|      | 2.11.2.1.10 Alarms                                                                   |

|      | 2.11.2.1.11 Intrusion detection                                                      |

|      | 2.11.2.1.111 Initiation detection 2.11.2.1.111 sysfs attribute writes interpretation |

|      | 2.11.2.1.12 Performance                                                              |

|      | 2.11.2 Topology                                                                      |

|      | 2.11.3 KFD Topology                                                                  |

|      |                                                                                      |

|      | 2.11.3.2 Node Information                                                            |

|      | 2.11.3.3 Memory                                                                      |

|      | 2.11.3.4 Cache                                                                       |

|      | 2.11.3.5 IO-LINKS                                                                    |

|      | 2.11.3.6 How to use topology information                                             |

| 2.12 | ROCm Virtualization & Containers                                                     |

|      | 2.12.1 PCIe Passthrough on KVM                                                       |

|      | 2.12.1.1 Ubuntu 16.04                                                                |

|      | 2.12.1.2 Fedora 27 or CentOS 7 (1708)                                                |

|      | 2.12.2 ROCm-Docker                                                                   |

|      | 2.12.2.1 Docker Hub                                                                  |

|      | 2.12.2.2 ROCm-docker set up guide                                                    |

|      | 2.12.2.3 Details                                                                     |

|      | 2.12.2.4 Building images                                                             |

|      | 2.12.2.5 Docker compose                                                              |

| 2.13 | Remote Device Programming                                                            |

|      | 2.13.1 ROCnRDMA                                                                      |

|      | 2.13.1.1 Restrictions and limitations                                                |

|      | 2.13.1.2 ROCmRDMA interface specification                                            |

|      | 2.13.1.3 Data structures                                                             |

|      | 2.13.1.4 The function to query ROCmRDMA interface                                    |

|      | 2.13.1.5 The function to query ROCmRDMA interface                                    |

|      | 2.13.1.6 ROCmRDMA interface functions description                                    |

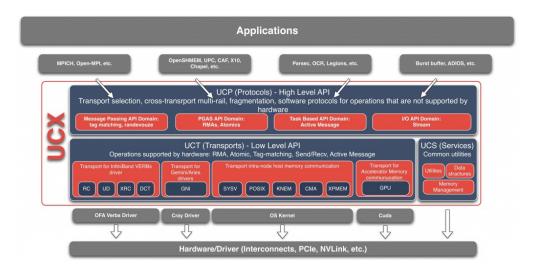

|      | 2.13.2 UCX                                                                           |

|      | 2.13.2.1 Introduction                                                                |

|      | 2.13.2.2 UCX Quick start                                                             |

|      | 2.13.2.3 UCX API usage examples                                                      |

|      | 2.13.2.4 Running UCX                                                                 |

|      | 2.13.2.4 Running OCX                                                                 |

|      | 1                                                                                    |

|      | 2.13.2.4.2 OpenMPI and OpenSHMEM with UCX                                            |

|      | 2.13.2.5 Interface to ROCm                                                           |

|      | 2.13.2.6 Documentation                                                               |

|      | 2.13.2.6.1 High Level Design                                                         |

|      | 2.13.2.6.2 Infrastructure and Tools                                                  |

|      | 2.13.2.7 FAQ                                                                         |

|      | 2.13.3 MPI                                                                           |

|      | 2.13.4 IPC                                                                           |

|      | 2.13.4.1 Introduction                                                                |

| 2.14 | Deep Learning on ROCm                                                                |

|      | 2.14.1 ROCm Tensorflow v1.12 Release                                                 |

|      | 2.14.2         Tensorflow Installation         199                                   |

|      | 2.14.3 Tensorflow More Resources                                                     |

|      | 2.14.4 ROCm MIOpen v1.6 Release                                                      |

|      | 2.14.5 Port       | ng from cuDNN to MIOpen                                           |

|------|-------------------|-------------------------------------------------------------------|

|      | 2.14.6 The        | ROCm 2.0 has prebuilt packages for MIOpen                         |

|      |                   | ding PyTorch for ROCm                                             |

|      | 2.14.8 Reco       | ommended:Install using published PyTorch ROCm docker image:       |

|      | 2.14.9 Opti       | on 2: Install using PyTorch upstream docker file                  |

|      | 2.14.10 Opti      | on 3: Install using minimal ROCm docker file                      |

|      | 2.14.11 Try       | PyTorch examples                                                  |

|      | 2.14.12 Buil      | ding Caffe2 for ROCm                                              |

|      | 2.14.13 Opti      | on 1: Docker image with Caffe2 installed:                         |

|      | 2.14.14 Opti      | on 2: Install using Caffe2 ROCm docker image:                     |

|      | 2.14.15 Test      | the Caffe2 Installation                                           |

|      | 2.14.16 Deep      | Dearning Framework support for ROCm                               |

|      | 2.14.17 Tuto      | rials                                                             |

| 2.15 | System Level      | Debug                                                             |

|      |                   | Em Language & System Level Debug, Flags and Environment Variables |

|      | 2.15.1            | .1 ROCr Error Code                                                |

|      | 2.15.1            | .2 Command to dump firmware version and get Linux Kernel version  |

|      | 2.15.1            | .3 Debug Flags                                                    |

|      | 2.15.1            | .4 ROCr level env variable for debug                              |

|      |                   | .5 Turn Off Page Retry on GFX9/Vega devices                       |

|      | 2.15.1            | .6 HCC Debug Environment Varibles                                 |

|      | 2.15.1            | .7 HIP Environment Varibles                                       |

|      | 2.15.1            | .8 OpenCL Debug Flags                                             |

|      | 2.15.1            | .9 PCIe-Debug                                                     |

| 2.16 | Tutorial          | 211                                                               |

| 2.17 | <b>ROCm Gloss</b> | ary                                                               |

We are excited to present ROCm, the first open-source HPC/Hyperscale-class platform for GPU computing that's also programming-language independent. We are bringing the UNIX philosophy of choice, minimalism and modular software development to GPU computing. The new ROCm foundation lets you choose or even develop tools and a language run time for your application.

**ROCm is built for scale**; it supports multi-GPU computing in and out of server-node communication through RDMA. It also simplifies the stack when the driver directly incorporates RDMA peer-sync support.

**ROCm has a rich system run time** with the critical features that large-scale application, compiler and language-runtime development requires.

Contents 1

2 Contents

# CHAPTER 1

# Going to 11: Amping Up the Programming-Language Run-Time Foundation

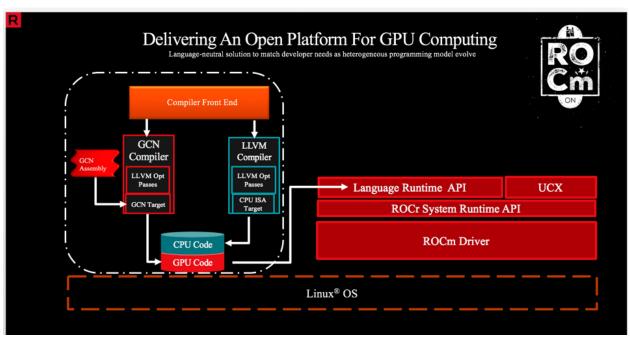

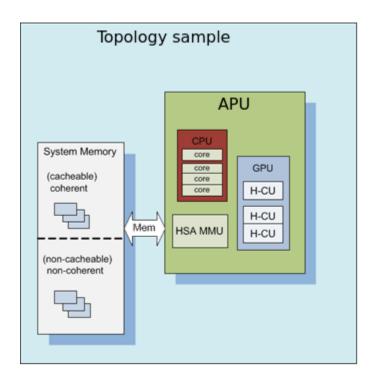

The ROCr System Runtime is language independent and makes heavy use of the Heterogeneous System Architecture (HSA) Runtime API. This approach provides a rich foundation to execute programming languages such as HCC C++ and HIP, the Khronos Group's OpenCL, and Continuum's Anaconda Python.

Important features include the following:

- Multi-GPU coarse-grain shared virtual memory

- Process concurrency and preemption

- · Large memory allocations

- HSA signals and atomics

- · User-mode queues and DMA

- · Standardized loader and code-object format

- Dynamic and offline-compilation support

- Peer-to-peer multi-GPU operation with RDMA support

- · Profiler trace and event-collection API

- Systems-management API and tools

# Solid Compilation Foundation and Language Support

- LLVM compiler foundation

- HCC C++ and HIP for application portability

- · GCN assembler and disassembler

The frontiers of what you can accomplish with ROCm are vast and uncharted. We look forward to working with you to improve the platform so you can use it more effectively in your own projects. Our efforts have opened the door to unique heterogeneous-computing applications that explore what this growing technology can do.

# 2.1 Quick Start Guide

# 2.1.1 Current Release Notes

# Release Notes

The Release Notes for the ROCm Latest version.

# 2.1.2 Installation Guide

# Installing from AMD ROCm repositories

This guide discusses how to install and check for correct operation of ROCm using AMD ROCm Repository.

# Installing from a Debian repository

This guide discusses how to install and check for correct operation of ROCm using Debian repository on Ubuntu.

# Installing from an yum repository

This guide describes how to install and check for correct operation of ROCm using yum on RHEL and CentOS 7.5.

#### Getting ROCm source code

This guide discusses how to modifying the open source code base and rebuilding the components of ROCm latest version.

# Installing ROCk-Kernel only

This guide discusses how to install ROCm Kernel into the system.

#### FAO on Installation

This section provides answers for various frequently asked questions regarding the installation steps and issues that can be faced during installation.

# 2.1.3 Programming Guide

This guide provides a detailed discussion of the ROCm programming model and programming interface. It then describes the hardware implementation and provides guidance on how to achieve maximum performance.

The appendices include a list of all ROCm-enabled devices, detailed description of all extensions to the C language, listings of supported mathematical functions, C++ features supported in host and device code, technical specifications of various devices, and concludes by introducing the low-level driver API.

#### **ROCm Languages**

This guide provides information on different ROCm languages. ROCm stack offers multiple programming-language choices which can be found in this section.

#### HC Programing Guide

This guide provides a detailed discussion of The Heterogeneous Compute programming installation requirements methods to install on various platfroms and How to build it from source

#### **HC Best Practices**

This section deals with detailed working with HCC, build the program, Build-in Macros, HCC Profiler mode and API Documentaion.

#### HIP Programing Guide

This guide provides a detailed discussion of The HIP programming, installation requirements methods to install on various platfroms and How to build it from source

#### **HIP Best Practices**

This section Provides details regarding variou concepts of HIP Poring, Debugging, Bugs, FAQ and other aspects of the HIP.

# OpenCL Programing Guide

This guide provides a detailed discussion of The OpenCL Architecture, AMD Implementation, Profiling, and other aspects of Opencl.

# OpenCL Best Practices

This section provides information on Perfromance and optimization for various device types such as GCN devices.

# 2.1.4 ROCm GPU Tunning Guides

# GFX7 Tuning Guide

- In-Progress

# **GFX8** Tuning Guide

- In-Progress

# Vega Tuning Guide

- In-Progress

# 2.1.5 GCN ISA Manuals

#### GCN 1.1

This Section Gives Information on ISA Manual for Hawaii (Sea Islands Series Instruction Set Architecture)

# GCN 2.0

This Section Gives Information on ISA Manual for Fiji and Polaris (AMD Accelerated Parallel Processing technology)

# Vega

This section provides "Vega" Instruction Set Architecture, Program Organization, Mode register and more details.

# Inline GCN ISA Assembly Guide

This section covers various concepts of AMDGCN Assembly, DS Permute Instructions, Parameters to a Kernel, GPR Counting.

# 2.1.6 ROCm API References

Here API References are listed out for users

# **ROCr System Runtime API**

ROCr System Runtime API Details are listed here

# HCC Language Runtime API

HCC Language Runtime APIDetails are listed here

# HIP Language Runtime API

HIP Language Runtime API Details are listed here

2.1. Quick Start Guide 7

#### HIP Math API

Here HIP Math API are listed with sample working classes

#### Thrust API Documentation

Here you can find all the Details on installation and working of Thrust Library and Thrust API List

# Math Library API's

HIP MAth API with hcRNG, clBLAS, clSPARSE API's.

# Deep Learning API's

Here we have MIOpen API and MIOpenGEMM API listed.

# 2.1.7 ROCm Tools

#### **HCC**

Complete description of Heterogeneous Compute Compiler has been listed and documented.

# GCN Assembler and Disassembler

This Section provieds details regarding GCN in-detail.

#### **GCN** Assembler Tools

In this Section there are useful items related to AMDGPU ISA assembler has been documented.

#### ROCm-GDB

Complete Documentaion of ROCm-GDB tool has been Documented here.Installtion, Build steps and working of Debugger and API related to it has been documented.

#### ROCm-Profiler

This section gives Details on Radeon Compute Profiler is a performance analysis tool, here we have details on how to clone and use it.

## CodeXL

This section provides details on CodeXL, a comprehensive tool suite. here Documentaion of Installation and builds and other details related to Codexl is done.

# **GPUperfAPI**

This section provieds details related to GPU Performance API. Content related to how to clone, system requiments and source code directory layout can be found.

# **ROCm Binary Utilities**

In-progess

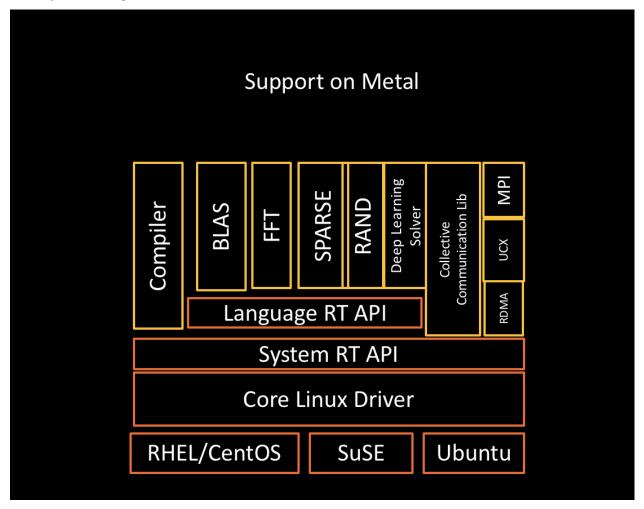

# 2.1.8 ROCm Libraries

#### rocFFT

This section provides details on rocFFT, it is a AMD's software library and also be compiled with the CUDA compiler using HIP tools for running on Nvidia GPU devices.

lrocBLAS | This section provieds details on rocBLAS, It is a library for BLAS on ROCm.rocBLAS is implemented in the HIP programming language and optimized for AMD's latest discrete GPUs.

# hipBLAS

This section provides details on hipBLAS,It is a BLAS marshalling library, with multiple supported backends.hipBLAS exports an interface that does not require the client to change.Currently,it supports :ref:'rocblas'and cuBLAS as backends.

#### hcRNG

This section provieds details on hcRNG.It is a software library ,where uniform random number generators targeting the AMD heterogeneous hardware via HCC compiler runtime is implemented..

# hipeigen

This section provieds details on Eigen.It is a C++ template library which provides linear algebra for matrices, vectors, numerical solvers, and related algorithms.

#### clFFT

This section provieds details on clFFT.It is a software library which contains FFT functions written in OpenCL, and clFFt also supports running on CPU devices to facilitate debugging and heterogeneous programming.

#### clBLAS

This section provieds details on clBLAS.It makes easier for developers to utilize the inherent performance and power efficiency benefits of heterogeneous computing.

# clSPARSE

This section provides details on cISPARSE,It is an OpenCL library which implements Sparse linear algebra routines.

# clRNG

This section provides details on cIRNG, This is a library for uniform random number generation in OpenCL..

#### hcFFT

This section provides details on hcFFT,It hosts the HCC based FFT Library and targets GPU acceleration of FFT routines on AMD devices.

# Tensile

2.1. Quick Start Guide 9

This section provieds details on Tensile.It is a tool for creating a benchmark-driven backend library for GEMMs,N-dimensional tensor contractions and multiplies two multi-dimensional objects together on a GPU..

# 2.1.9 ROCm Compiler SDK

#### GCN Native ISA LLVM Code Generator

This section provide complete description on LLVM such as introduction, Code Object, Code conventions, Source languages, etc.,

# ROCm Code Object Format

This section describes about application binary interface (ABI) provided by the AMD, implementation of the HSA runtime. it also provides details on Kernel, AMD Queue and Signals.

#### **ROCm Device Library**

Here we have instruction related to ROCm Device Library overview, Building and Testing related information with respect to Device Library.

#### **ROCr Runtime**

This section refers the user-mode API interfaces and libraries necessary for host applications to launch compute kernels to available HSA ROCm kernel agents. we can find installation details and Infrastructure details related to ROCr.

# 2.1.10 ROCm System Management

#### ROCm-SMI

ROCm System Management Interface a complete guide to use and work with rocm-smi tool.

#### **SYSFS** Interface

This section provides information on sysfs file structure where all detailes related to file structure related to system are captured in sysfs.

#### KFD Topology

KFD Kernel Topology is the system file structure wich describes about AMD GPU related information such as nodes, Memory, Cache and IO-links.

# 2.1.11 ROCm Virtualization & Containers

# PCIe Passthrough on KVM

Here PCIe Passthrough on KVM is described. A KVM-based instructions assume a headless host with an input/output memory management unit (IOMMU) to pass peripheral devices such as a GPU to guest virtual machines, more information can be found on the same here.

# ROCm-Docker

A framework for building the software layers defined in the Radeon Open Compute Platform into portable docker images. Detailed Information related to ROCm-Docker can be found.

# 2.1.12 Remote Device Programming

# **ROCnRDMA**

ROCmRDMA is the solution designed to allow third-party kernel drivers to utilize DMA access to the GPU memory. Complete indoemation related to ROCmRDMA is Documented here.

# **UCX**

This section gives information related to UCX, How to install, Running UCX and much more

#### **MPI**

This section gives information related to MPI.

# **IPC**

This section gives information related to IPC.

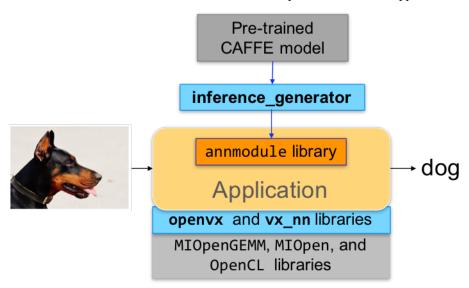

# 2.1.13 Deep Learning on ROCm

This section provides details on ROCm Deep Learning concepts.

# Porting from cuDNN to MIOpen

The porting guide highlights the key differences between the current cuDNN and MIOpen APIs.

# Deep Learning Framework support for ROCm

This section provides detailed chart of Frameworks supported by ROCm and repository details.

#### **Tutorials**

Here Tutorials on different DeepLearning Frameworks are documented.

# 2.1.14 System Level Debug

# ROCm Language & System Level Debug, Flags and Environment Variables

Here in this section we have details regardinf various system related debugs and commands for isssues faced while using ROCm.

# 2.1.15 Tutorial

This section Provide details related to few Concepts of HIP and other sections.

2.1. Quick Start Guide 11

# 2.1.16 ROCm Glossary

ROCm Glossary gives highlight concept and their main concept of how they work.

# 2.2 Current Release Notes

# 2.2.1 New features and enhancements in ROCm 2.1

# 2.2.1.1 RocTracer v1.0 preview release - 'rocprof' HSA runtime tracing and statistics support -

Supports HSA API tracing and HSA asynchronous GPU activity including kernels execution and memory copy

# 2.2.1.2 Improvements to ROCM-SMI tool -

Added support to show real-time PCIe bandwidth usage via the -b/-showbw flag

# 2.2.1.3 DGEMM Optimizations -

Improved DGEMM performance for large square and reduced matrix sizes (k=384, k=256)

# 2.2.2 New features and enhancements in ROCm 2.0

Features and enhancements introduced in previous versions of ROCm can be found in version\_history.md

# 2.2.2.1 Adds support for RHEL 7.6 / CentOS 7.6 and Ubuntu 18.04.1

# 2.2.2.2 Adds support for Vega 7nm, Polaris 12 GPUs

# 2.2.2.3 Introduces MIVisionX

A comprehensive computer vision and machine intelligence libraries, utilities and applications bundled into a single toolkit.

# 2.2.2.4 Improvements to ROCm Libraries

- rocSPARSE & hipSPARSE

- rocBLAS with improved DGEMM efficiency on Vega 7nm

# 2.2.2.5 MIOpen

- This release contains general bug fixes and an updated performance database

- Group convolutions backwards weights performance has been improved

- RNNs now support fp16

# 2.2.2.6 Tensorflow multi-gpu and Tensorflow FP16 support for Vega 7nm

• TensorFlow v1.12 is enabled with fp16 support

# 2.2.2.7 PyTorch/Caffe2 with Vega 7nm Support

- fp16 support is enabled

- Several bug fixes and performance enhancements

- Known Issue: breaking changes are introduced in ROCm 2.0 which are not addressed upstream yet. Meanwhile, please continue to use ROCm fork at https://github.com/ROCmSoftwarePlatform/pytorch

# 2.2.2.8 Improvements to ROCProfiler tool

• Support for Vega 7nm

# 2.2.2.9 Support for hipStreamCreateWithPriority

Creates a stream with the specified priority. It creates a stream on which enqueued kernels have a different

priority for execution compared to kernels enqueued on normal priority streams. The priority could be higher or

lower than normal priority streams.

# 2.2.2.10 OpenCL 2.0 support

• ROCm 2.0 introduces full support for kernels written in the OpenCL 2.0 C language on certain devices and systems. Applications can detect this support by calling the "clGetDeviceInfo" query function with "parame\_name" argument set to "CL\_DEVICE\_OPENCL\_C\_VERSION". In order to make use of OpenCL 2.0 C language features, the application must include the option "-cl-std=CL2.0" in options passed to the runtime API calls responsible for compiling or building device programs. The complete specification for the OpenCL 2.0 C language can be obtained using the following link: https://www.khronos.org/registry/OpenCL/specs/opencl-2.0-openclc.pdf

# 2.2.2.11 Improved Virtual Addressing (48 bit VA) management for Vega 10 and later GPUs

- Fixes Clang AddressSanitizer and potentially other 3rd-party memory debugging tools with ROCm

- Small performance improvement on workloads that do a lot of memory management

- Removes virtual address space limitations on systems with more VRAM than system memory

# 2.2.2.12 Kubernetes support

# 2.2.2.13 Removed features

HCC: removed support for C++AMP

#### 2.2.3 New features and enhancements in ROCm 1.9.2

# 2.2.3.1 RDMA(MPI) support on Vega 7nm

• Support ROCnRDMA based on Mellanox InfiniBand.

# 2.2.3.2 Improvements to HCC

• Improved link time optimization.

# 2.2.3.3 Improvements to ROCProfiler tool

• General bug fixes and implemented versioning APIs.

# 2.2.3.4 Critical bug fixes

#### 2.2.4 New features and enhancements in ROCm 1.9.1

# 2.2.4.1 Added DPM support to Vega 7nm

Dynamic Power Management feature is enabled on Vega 7nm.

# 2.2.4.2 Fix for 'ROCm profiling' "Version mismatch between HSA runtime and libhsa-runtime-tools64.so.1" error

# 2.2.5 New features and enhancements in ROCm 1.9.0

# 2.2.5.1 Preview for Vega 7nm

• Enables developer preview support for Vega 7nm

# 2.2.5.2 System Management Interface

• Adds support for the ROCm SMI (System Management Interface) library, which provides monitoring and management capabilities for AMD GPUs.

# 2.2.5.3 Improvements to HIP/HCC

- Support for gfx906

- Added deprecation warning for C++AMP. This will be the last version of HCC supporting C++AMP.

- Improved optimization for global address space pointers passing into a GPU kernel

- Fixed several race conditions in the HCC runtime

- Performance tuning to the unpinned copy engine

- Several codegen enhancement fixes in the compiler backend

# 2.2.5.4 Preview for rocprof Profiling Tool

Developer preview (alpha) of profiling tool 'rpl\_run.sh', cmd-line front-end for rocProfiler, enables: \* Cmd-line tool for dumping public per kernel perf-counters/metrics and kernel timestamps \* Input file with counters list and kernels selecting parameters \* Multiple counters groups and app runs supported \* Output results in CSV format The tool location is: /opt/rocm/bin/rpl\_run.sh

# 2.2.5.5 Preview for rocr Debug Agent rocr\_debug\_agent

The ROCr Debug Agent is a library that can be loaded by ROCm Platform Runtime to provide the following functionality: \* Print the state for wavefronts that report memory violation or upon executing a "s\_trap 2" instruction. \* Allows SIGINT (ctrl c) or SIGTERM (kill -15) to print wavefront state of aborted GPU dispatches. \* It is enabled on Vegal0 GPUs on ROCm1.9. The ROCm1.9 release will install the ROCr Debug Agent library at /opt/rocm/lib/librocr debug agent64.so

# 2.2.5.6 New distribution support

Binary package support for Ubuntu 18.04

# 2.2.5.7 ROCm 1.9 is ABI compatible with KFD in upstream Linux kernels.

Upstream Linux kernels support the following GPUs in these releases: 4.17: Fiji, Polaris 10, Polaris 11 4.18: Fiji, Polaris 10, Polaris 11, Vega10

Some ROCm features are not available in the upstream KFD: \* More system memory available to ROCm applications \* Interoperability between graphics and compute \* RDMA \* IPC

To try ROCm with an upstream kernel, install ROCm as normal, but do not install the rock-dkms package. Also add a udev rule to control /dev/kfd permissions:

```

echo 'SUBSYSTEM=="kfd", KERNEL=="kfd", TAG+="uaccess", GROUP="video"' | sudo tee /etc/

→udev/rules.d/70-kfd.rules

```

# 2.3 ROCm Installation Guide

#### 2.3.1 Current ROCm Version: 2.1

# 2.3.2 Hardware Support

ROCm is focused on using AMD GPUs to accelerate computational tasks such as machine learning, engineering workloads, and scientific computing. In order to focus our development efforts on these domains of interest, ROCm supports a targeted set of hardware configurations which are detailed further in this section.

# 2.3.2.1 Supported GPUs

Because the ROCm Platform has a focus on particular computational domains, we offer official support for a selection of AMD GPUs that are designed to offer good performance and price in these domains.

ROCm officially supports AMD GPUs that use following chips:

- · GFX8 GPUs

- "Fiji" chips, such as on the AMD Radeon R9 Fury X and Radeon Instinct MI8

- "Polaris 10" chips, such as on the AMD Radeon RX 580 and Radeon Instinct MI6

- "Polaris 11" chips, such as on the AMD Radeon RX 570 and Radeon Pro WX 4100