**UCC28056**

SLUSD37E -OCTOBER 2017-REVISED NOVEMBER 2019

# UCC28056 6-Pin Single-Phase Transition-Mode PFC Controller

#### **Features**

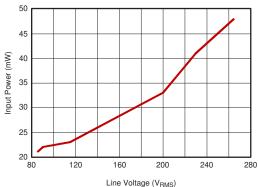

- Ultra-low no-load input power enables < 80-mW standby power at 230 V<sub>AC</sub> in PFC+LLC system

- Excellent light load efficiency and high efficiency over wide range of load due to multi-mode TM and DCM control

- Enables low system cost through FET drain valley synchronized turn-on which eliminates need for second winding on the boost inductor

- Enables compliance to green power standards without disabling PFC

- EuP Lot 6 Tier 2, CoC Ver. 5 Tier 2, Energy Star Ver. 6.1, DoE Level VI

- Burst mode with soft-entry and soft-exit periods enables ultra-low audible noise output

- Enhanced error amplifier, responds rapidly to load steps without degrading input current distortion

- User adjustable valley delay ensures valley switching

- Low start-up current consumption (<46 µA)

- Wide VCC range 8.5 V to 34 V

- Cycle-by-cycle current limit

- Second independent output over-voltage protection

- Integrated over-temperature protection

- Create a custom design using the UCC28056 device with the WEBENCH® Power Designer

# Applications

- Desktop computing and digital TV

- Gaming, set top box and AC adapter front end

- LED drivers and luminaries

- Industrial and medical power supplies, e-bike chargers, power tools chargers

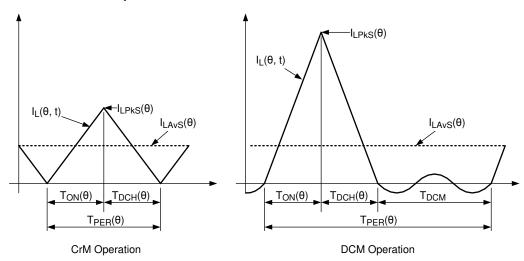

# 3 Description

The UCC28056 device drives PFC boost stages based on an innovative mixed mode method that operates in transition mode (TM) at full load and transitions seamlessly into discontinuous conduction mode (DCM) at reduced load, automatically reducing switching frequency. This device incorporates burst mode operation to further improve light load performance, enabling systems to meet challenging energy standards while eliminating the need to switch off the PFC. UCC28056 can drive a PFC power stage up to 300 W, ensuring sinusoidal line input current with low distortion, close to unity power factor. When used with the LLC controller UCC256403/4, and dual synchronous rectifier controller UCC24624 less than 80 mW system standby power can be achieved, enabling PFC always on architecture and eliminating the need for an auxiliary converter. This with FET Drain valley turn-on with simple boost inductor allows fewest component count and reduced system cost.

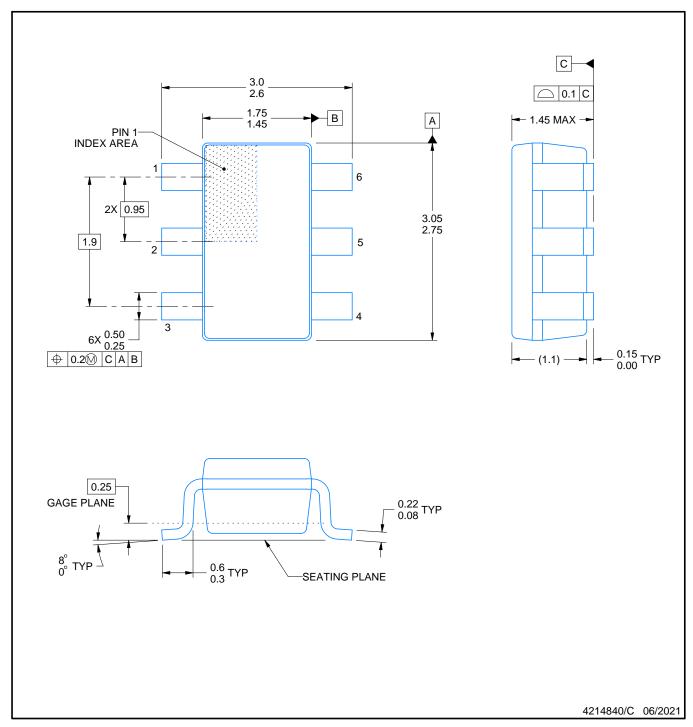

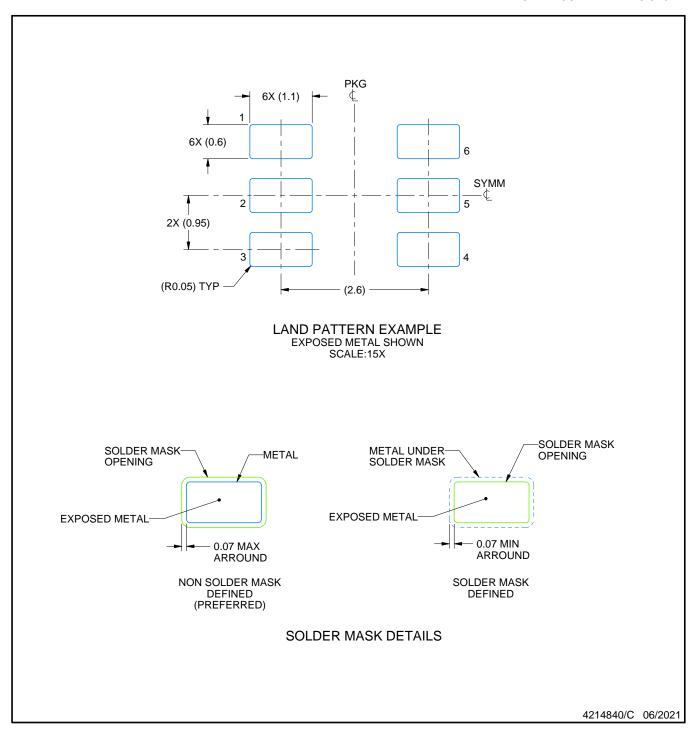

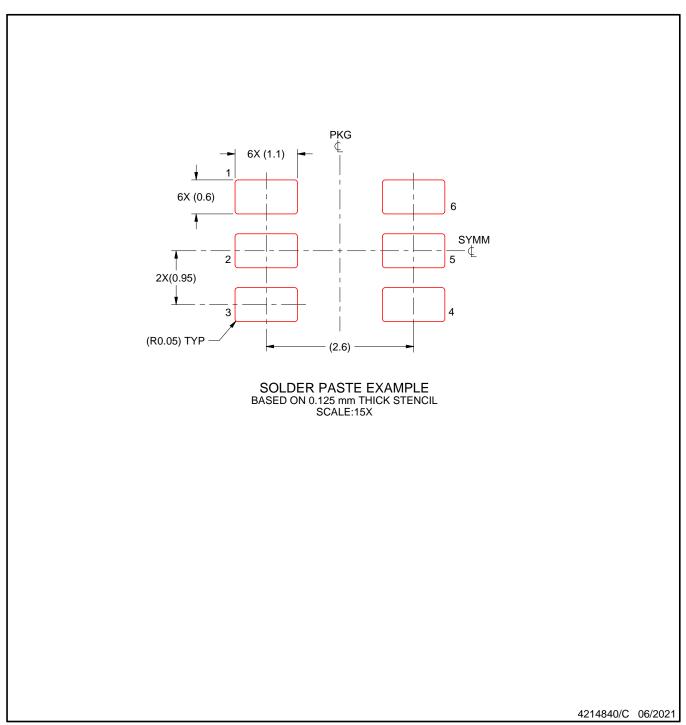

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)  |

|-------------|-----------|------------------|

| UCC28056    | SOT-23(6) | 2.90 mm x 1.6 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# No Load Power

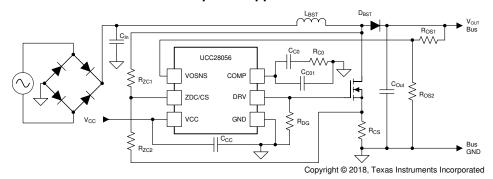

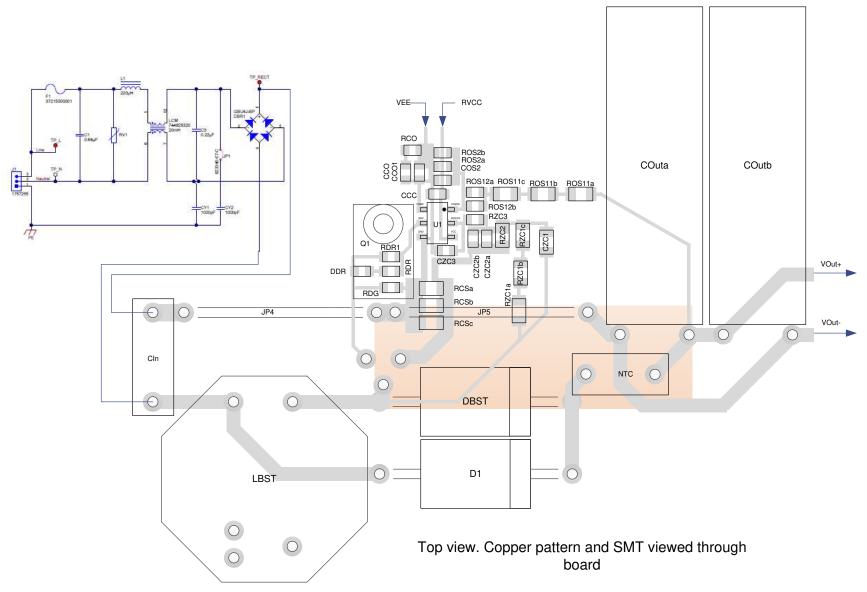

# Simplified Application

# **Table of Contents**

| Features 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.4 Controller Functional Modes2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9 Application and Implementation 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.2 Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 Power Supply Recommendations 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 Layout 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11.1 Layout Guidelines 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11.2 Layout Example4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| S Contract of the contract of | 12 Device and Documentation Support 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.1 Custom Design With WEBENCH® Tools 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.2 Receiving Notification of Documentation Updates 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.3 Community Resources4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.4 Trademarks 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.5 Electrostatic Discharge Caution 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12.6 Glossary4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

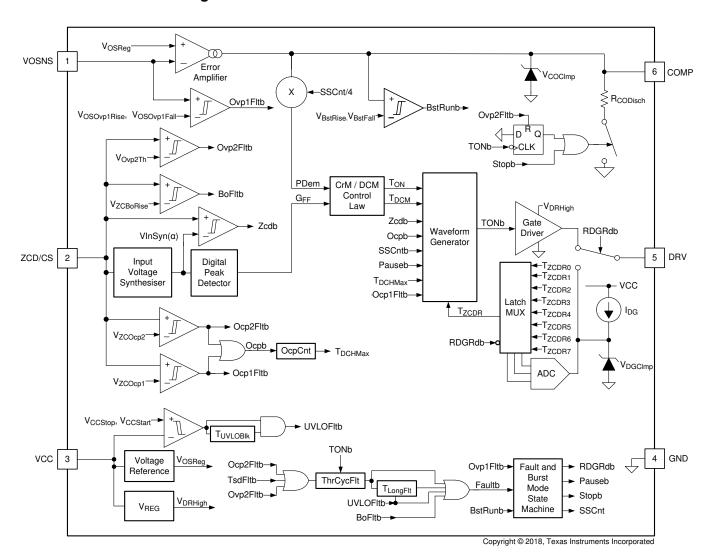

| 8.2 Functional Block Diagram       15         8.3 Feature Description       16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 Mechanical, Packaging, and Orderable Information4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Applications       1         Description       1         Revision History       2         Device Comparison Tables       4         Pin Configuration and Functions       5         Specifications       6         7.1 Absolute Maximum Ratings       6         7.2 ESD Ratings       6         7.3 Recommended Operating Conditions       6         7.4 Thermal Information       6         7.5 Electrical Characteristics       7         7.6 Typical Characteristics       11         Detailed Description       14         8.1 Overview       14         8.2 Functional Block Diagram       15 |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision D (April, 2019) to Revision E   | Page |

|-------------------------------------------------------|------|

| Added target market applications.                     | 4    |

| Added explanation for ZCD noise immunity.             | 4    |

| Changed new variant of LLC controller                 | 14   |

| Added burst mode modified                             | 14   |

| Added burst mode levels for versions.                 | 25   |

| Added burst modes for different versions              | 25   |

| Changed boost inductance calculation.                 | 30   |

| Changed inductor requirements.                        | 31   |

| Changes from Revision C (February 2018) to Revision D | Page |

| ٠. | inaligue from Novicion & (i. estata) 2016, to Novicion 2      | . 490 |

|----|---------------------------------------------------------------|-------|

| •  | Added Link to UCC256403/4 LLC controller                      | 1     |

| •  | Added Link to UCC24624 synchronous rectifier controller       | 1     |

| •  | Updated Description section                                   | 1     |

| •  | Updated Description section                                   | 1     |

| •  | Added Device Comparison Table                                 | 4     |

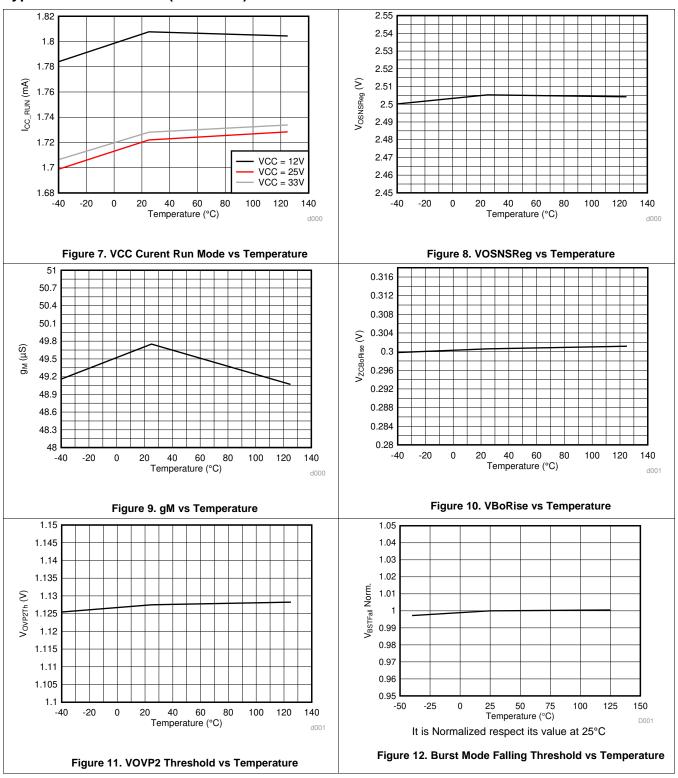

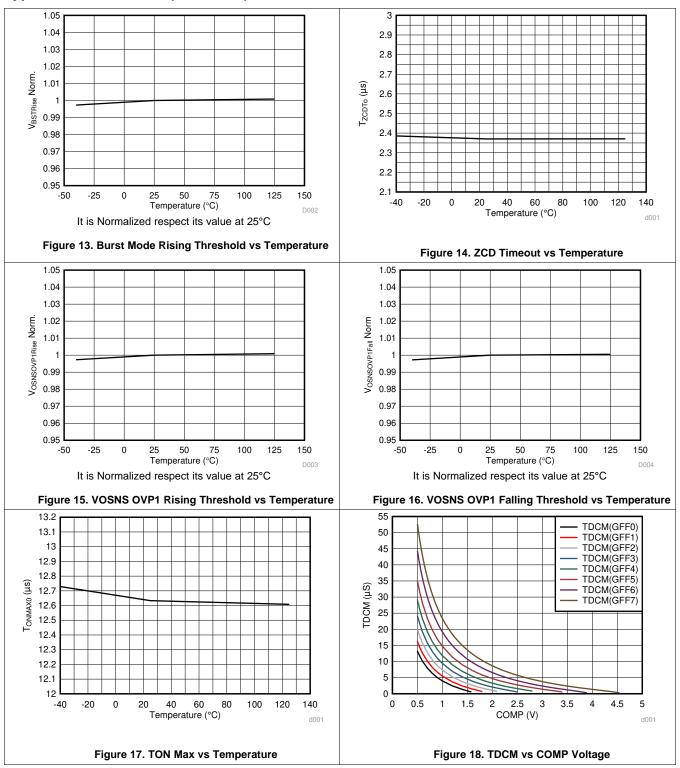

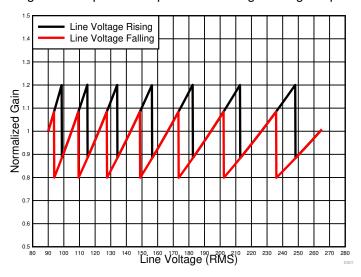

| •  | Changed V <sub>BSTFall</sub> graph into normalized graph.     | 12    |

| •  | Changed V <sub>BSTRise</sub> graph into normalized graph      | 12    |

| •  | Changed V <sub>OSNSOVP1Rise</sub> graph into normalized graph | 13    |

| •  | Changed V <sub>OSNSOVP1Fall</sub> graph into normalized graph | 13    |

|    |                                                               |       |

| C | Changes from Revision B (January 2018) to Revision C |   |  |  |

|---|------------------------------------------------------|---|--|--|

| • | Updated Description section                          | 1 |  |  |

| Changes from Revision A (November 2017) to Revision B               |      |  |

|---------------------------------------------------------------------|------|--|

| Updated Simplified Application                                      | 1    |  |

| Changed document status from Advance Information to Production Data | 1    |  |

| Changes from Original (October 2017) to Revision A                  | Page |  |

| Added WEBENCH links to data sheet                                   | 1    |  |

# 5 Device Comparison Tables

| DEVICE                | UCC28056                       | UCC28056A               | UCC28056B                          | UCC28056C                        |

|-----------------------|--------------------------------|-------------------------|------------------------------------|----------------------------------|

| Target Applications   | Not recommended for new design | PFC Bus output >400VDC  | Improved audible noise performance | Drop in replacement for UCC28056 |

| OVP2 FEATURE INCLUDED | YES                            | NO                      | YES                                | YES                              |

| OVP1 THRESHOLD        | 110% Vout                      | 108% Vout               | 110% Vout                          | 110% Vout                        |

| BURST MODE THRESHOLD  | < 10% Load                     | < 15% Load              | < 15% Load                         | < 10% Load                       |

| ZCD NOISE IMMUNITY    | Basic noise immunity           | Improved noise immunity | Improved noise immunity            | Improved noise immunity          |

The enhanced noise immunity of UCC28056A, UCC28056B, and UCC28056C provides system robustness advantages and less sensitivity to PCB layout than the UCC28056. For more information on the system level benefits that UCC28056A, UCC28056B and UCC28056C provide, please see UCC28056X Selection Guide SLUA974.

| PARAMETER               | l                                                                                                          | DEVICE    | MIN            | TYP   | MAX   | UNIT |

|-------------------------|------------------------------------------------------------------------------------------------------------|-----------|----------------|-------|-------|------|

| Output Over             | Voltage Protection                                                                                         |           |                | •     | •     |      |

|                         |                                                                                                            | UCC28056A | 2.64           | 2.7   | 2.76  |      |

| \ /                     | VOSNS over-voltage threshold, rising,                                                                      | UCC28056  |                |       |       | .,   |

| V <sub>OSOvp1Rise</sub> | VCC = 12 V                                                                                                 | UCC28056B | 2.69           | 2.75  | 2.81  | V    |

|                         |                                                                                                            | UCC28056C |                |       |       |      |

| -                       |                                                                                                            | UCC28056A | 2.55           | 2.625 | 2.68  |      |

| .,                      | VOSNS over-voltage threshold, falling,                                                                     | UCC28056  |                |       |       | .,   |

| V <sub>OSOvp1Fall</sub> | VCC = 12 V                                                                                                 | UCC28056B | 2.60           | 2.675 | 2.73  | V    |

|                         |                                                                                                            | UCC28056C |                |       |       |      |

| V <sub>OSOvp1Hyst</sub> | VOSOovp1Rise - VOSOovp1Fall                                                                                | All       | 0.072          |       |       | V    |

|                         |                                                                                                            | UCC28056A | Not Applicable | 9     | '     | •    |

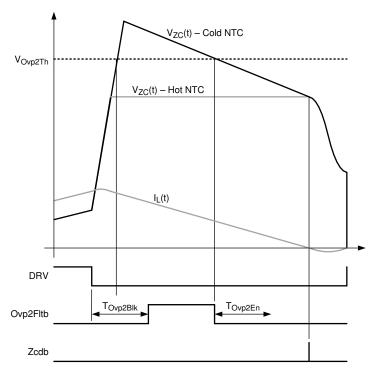

| _                       | Ovp2 Comparator output is blanked for                                                                      | UCC28056  |                |       | 720   |      |

| $T_{Ovp2Blk}$           | this period after falling edge of DRV                                                                      | UCC28056B | 520            | 620   |       | ns   |

|                         |                                                                                                            | UCC28056C |                |       |       |      |

|                         |                                                                                                            | UCC28056A | Not Applicable |       |       |      |

| <b>-</b>                | Ovp2b fault is detected if ZCD is detected during this period after falling edge of Ovp2 Comparator output | UCC28056  | 620            | 720   | 820   |      |

| $T_{Ovp2bEn}$           |                                                                                                            | UCC28056B |                |       |       | ns   |

|                         |                                                                                                            | UCC28056C |                |       |       |      |

|                         |                                                                                                            | UCC28056A | Not Applicable | Э     |       |      |

| \ /                     | Second level output over-voltage fault                                                                     | UCC28056  |                |       | 1.148 |      |

| $V_{Ovp2Th}$            | Threshold                                                                                                  | UCC28056B | 1.102          | 1.125 |       | ns   |

|                         |                                                                                                            | UCC28056C |                |       |       |      |

| Burst Mode (            | Operation                                                                                                  |           |                |       |       |      |

|                         |                                                                                                            | UCC28056  |                | 0.5   |       |      |

| V <sub>BSTFall</sub>    | VCOMP Burst Threshold Falling                                                                              | UCC28056C |                | 0.5   |       |      |

|                         |                                                                                                            | UCC28056A |                | 0.75  |       |      |

|                         |                                                                                                            | UCC28056B |                | 0.75  |       |      |

|                         |                                                                                                            | UCC28056  |                | 0.625 |       | V    |

| V                       | VCOMB Burst Threshold Bisins                                                                               | UCC28056C |                | 0.025 |       |      |

| $V_{BSTRise}$           | VCOMP Burst Threshold Rising                                                                               | UCC28056A |                | 0.875 |       |      |

|                         |                                                                                                            | UCC28056B |                | 0.675 |       |      |

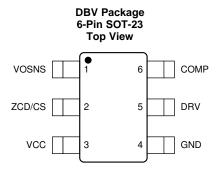

# 6 Pin Configuration and Functions

## **Pin Functions**

| PI     | PIN |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|--------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

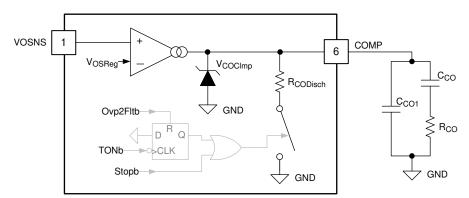

| СОМР   | 6   | I/O | Output of the internal transconductance error amplifier and power demand input. To achieve compensation of the voltage loop, connect a suitable RC network from this pin to GND. The error amplifier output is internally limited to V <sub>COCImp</sub> . An internal resistor, R <sub>CODisch</sub> , discharges the external compensation network when the controller is in its Stopb state or when the Ovp2 comparator is tripped. Switching stops, and the controller enters a low-power state (BstOffb), when the voltage on the COMP pin drops below V <sub>BSTFall</sub> . Switching resumes when the COMP pin voltage exceeds V <sub>BSTRise</sub> .                     |  |  |

| DRV    | 5   | I/O | GATE connection to drive the main power MOSFET. This output is internally limited to V <sub>DRHigh</sub> . This is done to reduce power dissipation in the internal driver and allow controller operation from high VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| GND    | 4   | G   | Controller Ground reference pin. Connect to the power stage at the lower terminal of the current sense resistor, $R_{CS}$ , only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| VCC    | 3   | Р   | Positive supply voltage. Switching operation can start once VCC exceeds $V_{CCStart}$ . Switching operation ceases if VCC drops below $V_{CCStop}$ for longer than $T_{UVLOBIk}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| ZCD/CS | 2   | I   | This pin is fed by a potential divider connected across the Drain & Source pins of the power MOSFET switch. While the DRV pin is high this pin monitors the voltage across the current sense resistor, R <sub>CS</sub> . This pin implement over-current protection functions. While the DRV pin in low this pin monitors the Drain voltage waveform. Input voltage applied to the power stage can be obtained by filtering the Drain waveform. Input voltage provides Line voltage feed - forward and Line Brown - In features. Drain voltage waveform is also used to provide ZCD detection, valley synchronization and second level output over - voltage protection features. |  |  |

| VOSNS  | 1   | I   | Voltage error amplifier inverting input. The error amplifier non - inverting input connects to internal reference voltage V <sub>OSReg</sub> . Error amplifier gain increases with error magnitude to improve transient response without compromising Line current distortion. Output over-voltage protection is implemented on this pin. Switching operation halts if the voltage on this pin exceeds V <sub>Ovp1Rise</sub> and resumes when it drops below V <sub>Ovp1Fall</sub> .                                                                                                                                                                                              |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                   | 1 0 (                | MIN  | MAX | UNIT |

|---------------------------------------------------|----------------------|------|-----|------|

|                                                   | VCC                  | -0.5 | 36  |      |

| Input voltage                                     | ZCD/CS               | -0.5 | 7   | V    |

|                                                   | VOSNS                | -0.5 | 7   |      |

| Output valtage                                    | COMP                 | -0.5 | 7   | V    |

| Output voltage                                    | DRV                  | -0.3 | 20  | V    |

| Junction<br>temperature<br>range                  | T <sub>J</sub>       | -40  | 150 |      |

| Storage<br>temperature<br>range, T <sub>stg</sub> | T <sub>stg</sub>     | -65  | 150 | °C   |

| Lead temperature                                  | Soldering, 10 second |      | 300 |      |

| Leau temperature                                  | Reflow               |      | 260 |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                                | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>                    | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per<br>JEDEC specification JESD22-C101, all<br>pins <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                               | MIN | NOM | MAX | UNIT |

|----------------|-------------------------------|-----|-----|-----|------|

| VCC            | Input voltage                 |     | 12  |     | V    |

| T <sub>A</sub> | Operating ambient temperature | -40 |     | 125 | °C   |

## 7.4 Thermal Information

|                      |                                              | UCC28056 |      |

|----------------------|----------------------------------------------|----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | SOT23-6  | UNIT |

|                      |                                              | 6 PINS   |      |

| $R_{\Theta JA}$      | Junction-to-ambient thermal resistance       | 116.4    | °C/W |

| $R_{\Theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 74.9     | °C/W |

| $R_{\Theta JB}$      | Junction-to-board thermal resistance         | 36.1     | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 18.8     | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 36.0     | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

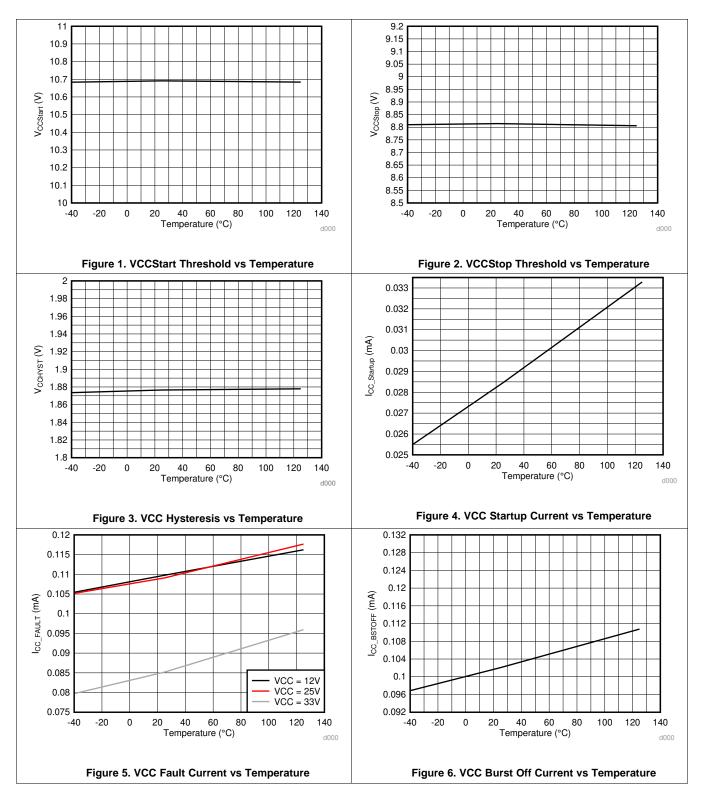

| SUPPLY VOL<br>V <sub>CCStart</sub><br>V <sub>CCStop</sub> | Turn-on threshold                                                                      |                                                                     |       |       |       |    |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------|-------|-------|----|

| V <sub>CCStop</sub>                                       | Turn-on threshold                                                                      |                                                                     |       |       |       |    |

|                                                           |                                                                                        | VCC Rising                                                          |       | 10.65 | 11    | V  |

|                                                           | Turn-off threshold                                                                     | VCC Falling                                                         | 8.5   | 8.85  | 9.2   | V  |

| $V_{CCHyst}$                                              | UVLO Hysteresis (V <sub>CCStart</sub> - V <sub>CCStop</sub> ) (1)                      |                                                                     | 1.5   |       |       | V  |

| T <sub>UVLOBIk</sub>                                      | Turn-OFF Blanking Time                                                                 |                                                                     | 27    | 35    | 42    | μs |

| SUPPLY CUR                                                | RRENT                                                                                  |                                                                     |       |       |       | -  |

| CC_Startup                                                | Current consumption before startup                                                     | VCC = V <sub>CCStart</sub> -200mV, T <sub>A</sub> < 110°C           |       |       | 46    | μA |

| I <sub>CC_FAULT</sub>                                     | Current consumption during fault condition                                             | VCC = 12V                                                           |       |       | 130   | μA |

| CC_BSTOFF                                                 | Current consumption during Burst OFF period                                            | VCC = 12V                                                           |       |       | 132   | μΑ |

| I <sub>CC_RUN</sub>                                       | Operating current with DRV pin unloaded                                                | VCC = 12V                                                           |       | 1.8   | 2.2   | mA |

| GATE DRIVE                                                |                                                                                        |                                                                     |       |       |       |    |

| $V_{DRLow}$                                               | DRV output low voltage                                                                 | I <sub>DR</sub> = 100mA                                             |       |       | 0.9   | V  |

| $V_{DRHigh}$                                              | DRV output voltage high level, limited                                                 | VCC = 25V, I <sub>DR</sub> = -10mA                                  | 10    | 13.7  | 15    | V  |

| $V_{DRHighMin}$                                           | DRV minimum high voltage level                                                         | VCC = V <sub>CCStop</sub> + 200 mV, I <sub>DR</sub> = -8mA          | 8     |       |       | V  |

| R <sub>DRH</sub>                                          | DRV, Pull-up resistance                                                                | T <sub>A</sub> = -40°C to 125°C, I <sub>DR</sub> = -8mA,<br>VCC=12V |       | 9.7   | 16    | Ω  |

| R <sub>DRL</sub>                                          | DRV, Pull-down resistance                                                              | T <sub>A</sub> = -40°C to 125°C, I <sub>DR</sub> = 100mA            | 2.0   | 4.6   | 9     | Ω  |

| t <sub>R</sub>                                            | Rise Time                                                                              | CLOAD=1nF, DRV=1V to 6V, VCC=12V                                    | 10    | 34    | 61    | ns |

| t <sub>F</sub>                                            | Fall Time                                                                              | CLOAD=1nF, DRV=6V to 1V,<br>VCC=12V                                 | 4     | 15    | 40    | ns |

| Isource                                                   | Source peak current on DRV Pin (1)                                                     |                                                                     |       | -0.7  |       | Α  |

| Isink                                                     | Sink peak current on DRV Pin (1)                                                       |                                                                     |       | 1     |       | Α  |

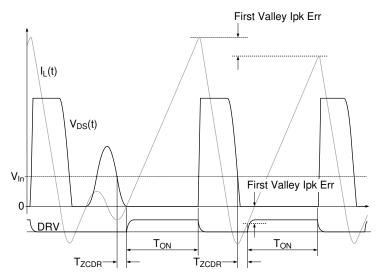

| R <sub>DG0</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR0</sub> <sup>(1)</sup>                |                                                                     | 130   | 200   |       | kΩ |

| R <sub>DG1</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR1</sub> <sup>(1)</sup>                |                                                                     | 81.18 | 82    | 82.82 | kΩ |

| R <sub>DG2</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR2</sub> <sup>(1)</sup>                |                                                                     | 61.38 | 62    | 62.62 | kΩ |

| R <sub>DG3</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR3</sub> <sup>(1)</sup>                |                                                                     | 42.57 | 43    | 43.43 | kΩ |

| R <sub>DG4</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR4</sub> <sup>(1)</sup>                |                                                                     | 26.73 | 27    | 27.27 | kΩ |

| R <sub>DG5</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR5</sub> <sup>(1)</sup>                |                                                                     | 17.82 | 18    | 18.18 | kΩ |

| R <sub>DG6</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR6</sub> <sup>(1)</sup>                |                                                                     | 12.87 | 13    | 13.13 | kΩ |

| R <sub>DG7</sub>                                          | DRV to GND resistance value to select T <sub>ZCDR7</sub> <sup>(1)</sup>                | _                                                                   | 9     | 9.1   | 9.2   | kΩ |

| T <sub>DGSmpl</sub>                                       | Time needed to detect R <sub>DG</sub> value.                                           | T <sub>A</sub> < 85°C                                               | 3.95  | 4.4   | 4.95  | ms |

| $V_{DGCImp}$                                              | Maximum voltage that will be applied on DRV pin while detecting R <sub>DG</sub> value. |                                                                     | 1     | 1.05  | 1.1   | V  |

| Error Amplifi                                             | er                                                                                     |                                                                     |       | ·     |       |    |

| V <sub>OSReg</sub>                                        | Feedback voltage reference                                                             |                                                                     | 2.45  | 2.5   | 2.55  | V  |

|                                                           | ISNS pin bias current                                                                  | V <sub>OS</sub> = V <sub>OSReg</sub>                                | -100  |       | 100   | nA |

| I <sub>OSBias</sub>                                       |                                                                                        |                                                                     |       |       |       |    |

## (1) Not tested in production. Ensured by design.

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                                       | TEST CONDITIONS                                                       | MIN   | TYP   | MAX   | UNIT      |

|----------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|-----------|

| g <sub>MNL</sub>     | Error Amplifier Transconductance<br>Gain for large error                                        | V <sub>OS</sub> -V <sub>OSReg</sub>   > DSuThs                        |       | 300   |       | μS        |

| DSuThs               | Non-Linear Gain Threshold                                                                       |                                                                       | 67    |       |       | mV        |

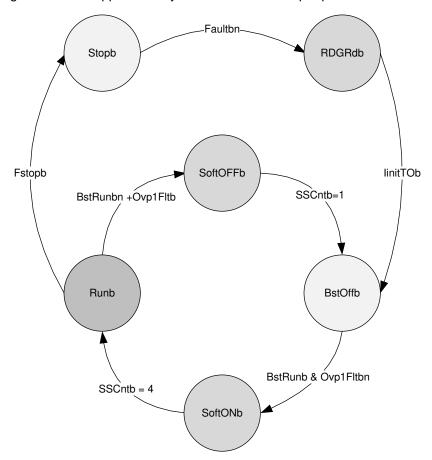

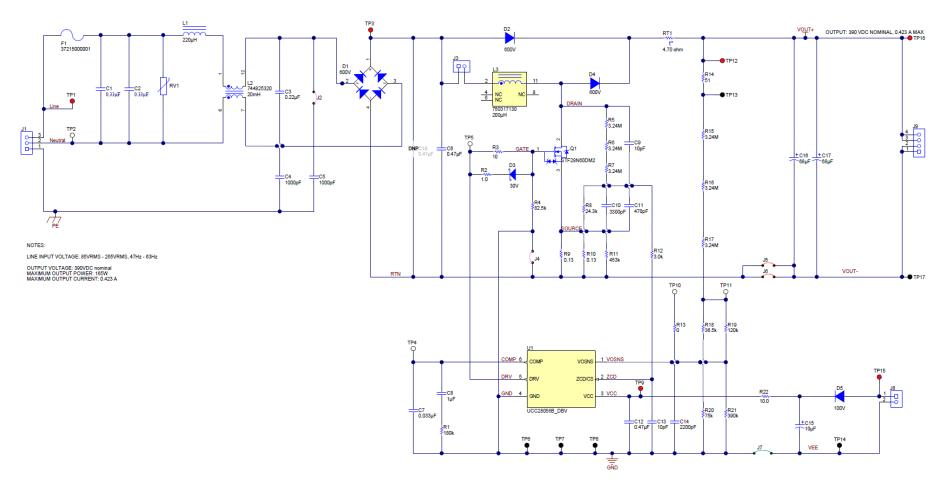

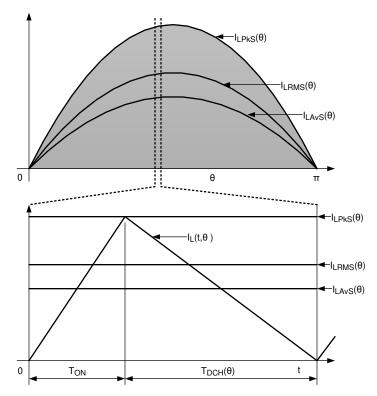

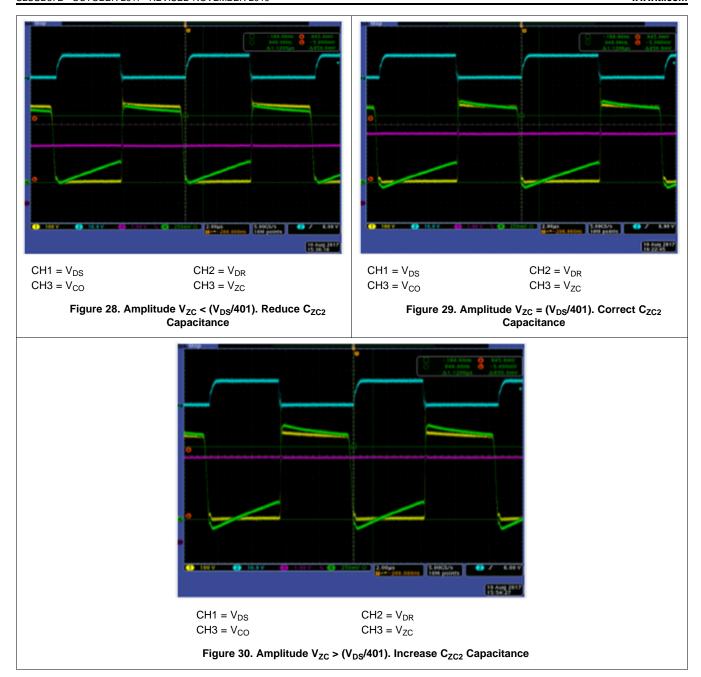

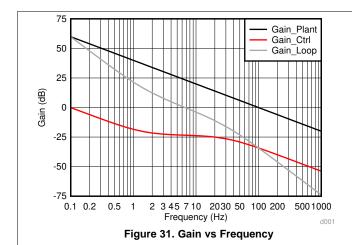

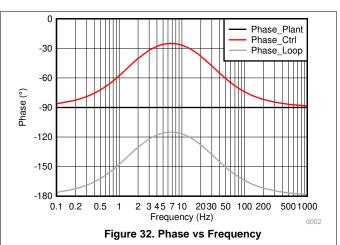

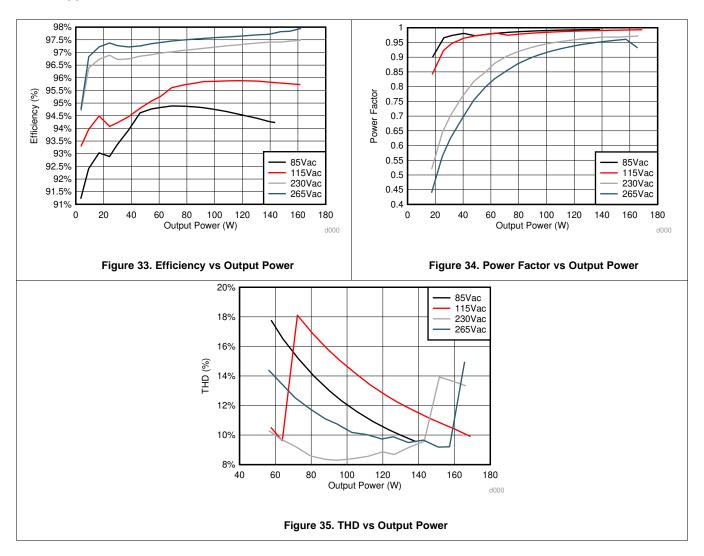

| R <sub>CODisch</sub> | Internal COMP to GND resistance when in STOPb state.                                            |                                                                       | 4.3   | 5     | 5.7   | $k\Omega$ |