• Replacements for ADI, PMI and LTC OP27 Series

Features of OP27A and OP27C:

- Maximum Equivalent Input Noise Voltage: 3.8 nV/\Hz at 1 kHz 5.5 nV/\Hz at 10 kHz

- Very Low Peak-to-Peak Noise Voltage at 0.1 Hz to 10 Hz ... 80 nV Typ

- Low Input Offset Voltage OP27A . . . 25 μV Max OP27C . . . 100 μV Max

- High Voltage Amplification OP27A ... 1 V/μV Min OP27C ... 0.7 V/μV Min

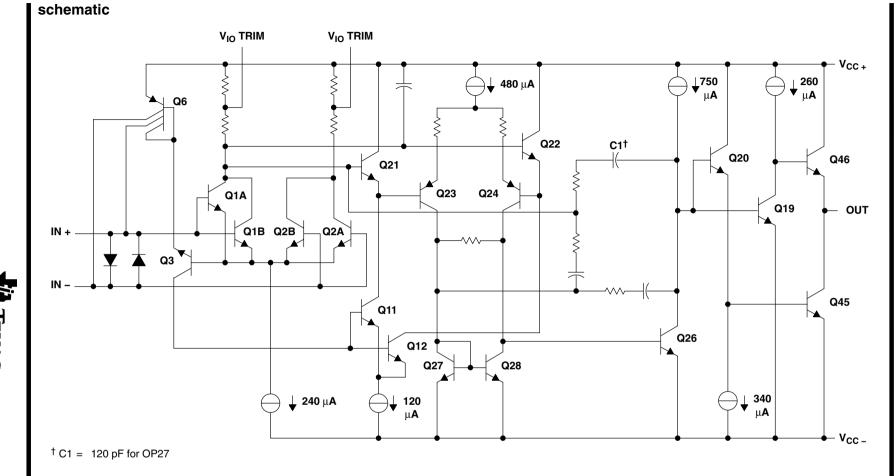

#### description

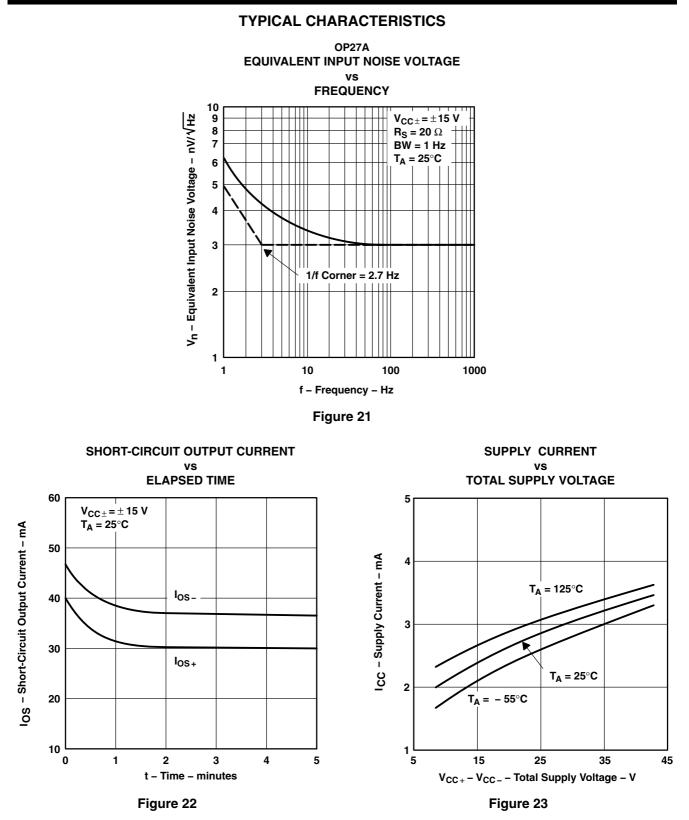

The OP27 operational amplifiers combine outstanding noise performance with excellent precision and high-speed specifications. The wideband noise is only 3 nV/ $\sqrt{Hz}$  and with the 1/f noise corner at 2.7 Hz, low noise is maintained for all low-frequency applications.

The outstanding characteristics of the OP27 make these devices excellent choices for low-noise amplifier applications requiring precision performance and reliability.

The OP27 series is compensated for unity gain.

The OP27A and OP27C are characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C.

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

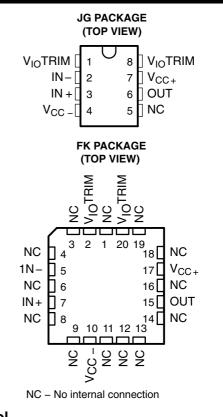

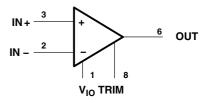

symbol

Pin numbers are for the JG packages.

# AVAILABLE OPTIONS

| T <sub>A</sub> | M man                          |                | PACKAGE             |                      |  |  |  |

|----------------|--------------------------------|----------------|---------------------|----------------------|--|--|--|

|                | V <sub>IO</sub> max<br>AT 25°C | STABLE<br>GAIN | CERAMIC DIP<br>(JG) | CHIP CARRIER<br>(FK) |  |  |  |

| –55°C to 125°C | 25 μV                          | 1              | OP27AJG             | OP27AFK              |  |  |  |

|                | 100 μV                         | 1              | OP27CJG             | —                    |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2010, Texas Instruments Incorporated

Template Release Date: 7–11–94 האיזא האיזא

# OP27A, OP27C LOW-NOISE HIGH-SPEED PRECISION OPERATIONAL-AMPLIFIER

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

N

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC+</sub> (see Note 1)<br>Supply voltage, V <sub>CC-</sub> (see Note 1) | 22 V                           |

|------------------------------------------------------------------------------------------------|--------------------------------|

| Input voltage, V <sub>I</sub>                                                                  | $\dots$ $V_{CC\pm}$            |

| Duration of output short circuit                                                               | unlimited                      |

| Differential input current (see Note 2)                                                        | ±25 mA                         |

| Continuous power dissipation                                                                   | . See Dissipation Rating Table |

| Operating free-air temperature range: OP27A, OP27C                                             | –55°C to 125°C                 |

| Storage temperature range                                                                      |                                |

| Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds: JG or FK pa                      | ckage 300°C                    |

NOTES: 1. All voltage values are with respect to the midpoint between V<sub>CC+</sub> and V<sub>CC-</sub> unless otherwise noted.

The inputs are protected by back-to-back diodes. Current-limiting resistors are not used in order to achieve low noise. Excessive

input current will flow if a differential input voltage in excess of approximately ±0.7 V is applied between the inputs unless some

limiting resistance is used.

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|------------------------------------------------|---------------------------------------|----------------------------------------|

| JG      | 1050 mW                               | 8.4 mW/°C                                      | 546 mW                                | 210 mW                                 |

| FK      | 1375 mW                               | 11.0 mW/°C                                     | 715 mW                                | 275 mW                                 |

#### **DISSIPATION RATING TABLE**

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### recommended operating conditions

|                                       |                                                                                    | OP27A |     |     | OP27C |     |     |      |

|---------------------------------------|------------------------------------------------------------------------------------|-------|-----|-----|-------|-----|-----|------|

|                                       |                                                                                    | MIN   | NOM | MAX | MIN   | NOM | MAX | UNIT |

| Supply voltage, V <sub>CC+</sub>      | 4                                                                                  | 15    | 22  | 4   | 15    | 22  | V   |      |

| Supply voltage, $V_{CC-}$             | -4                                                                                 | -15   | -22 | -4  | -15   | -22 | V   |      |

| Common-mode input voltage, $V_{IC}$   | $V_{CC\pm}=\pm15~V,~T_A=25^\circ C$                                                | ± 11  |     |     | ±11   |     |     | v    |

|                                       | $V_{CC\pm} = \pm 15 \text{ V},  T_A = -55^{\circ}\text{C to } 125^{\circ}\text{C}$ | ±10.3 |     |     | ±10.2 |     |     | v    |

| Operating free-air temperature, $T_A$ | -55                                                                                |       | 125 | -55 |       | 125 | °C  |      |

# electrical characteristics at specified free-air temperature, $V_{CC\pm} = \pm 15$ V (unless otherwise noted)

|                    |                                                               |                                                                                | OP27A                         |                  |                     | OP27C |     |                     | T     |      |       |

|--------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------|------------------|---------------------|-------|-----|---------------------|-------|------|-------|

|                    | PARAMETER                                                     | TEST CO                                                                        | ONDITIONS                     | T <sub>A</sub> † | MIN                 | TYP   | MAX | MIN                 | TYP   | МАХ  | UNIT  |

|                    | Input offset voltage                                          | V <sub>O</sub> = 0,                                                            | $V_{IC} = 0$                  | 25°C             |                     | 10    | 25  |                     | 30    | 100  |       |

| V <sub>IO</sub>    |                                                               | $R_{\rm S} = 50 \ \Omega,$                                                     |                               | Full range       |                     |       | 60  |                     |       | 300  | μV    |

| ανιο               | Average temperature<br>coefficient of input<br>offset voltage |                                                                                |                               | Full range       |                     | 0.2   | 0.6 |                     | 0.4   | 1.8  | μV/°C |

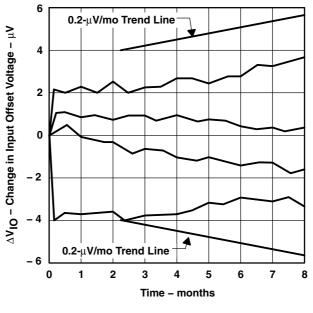

|                    | Long-term drift of input offset voltage                       | See Note 4                                                                     |                               |                  |                     | 0.2   | 1   |                     | 0.4   | 2    | μV/mo |

|                    | Input offect ourrent                                          | V 0                                                                            | V O                           | 25°C             |                     | 7     | 35  |                     | 12    | 75   | - 1   |

| I <sub>IO</sub>    | Input offset current                                          | V <sub>O</sub> = 0,                                                            | $V_{IC} = 0$                  | Full range       |                     |       | 50  |                     |       | 135  | nA    |

|                    | Innut higg gurrant                                            | V 0                                                                            | V 0                           | 25°C             |                     | ±10   | ±40 |                     | ±15   | ±80  | - 1   |

| I <sub>IB</sub>    | Input bias current                                            | V <sub>O</sub> = 0,                                                            | V <sub>IC</sub> = 0           | Full range       |                     |       | ±60 |                     |       | ±150 | nA    |

| V <sub>ICR</sub>   | Common-mode input<br>voltage range                            |                                                                                |                               | 25°C             | 11<br>to<br>-11     |       |     | 11<br>to<br>-11     |       |      | v     |

|                    |                                                               |                                                                                |                               | Full range       | 10.3<br>to<br>-10.3 |       |     | 10.5<br>to<br>-10.5 |       |      | v     |

|                    | Peak output voltage swing                                     | $R_L \geq 2 \ k\Omega$                                                         |                               |                  | ±12                 | ±13.8 |     | ±11.5               | ±13.5 |      |       |

| V <sub>OM</sub>    |                                                               | $R_L \ge 0.6 \ k\Omega$                                                        |                               |                  | ±10                 | ±11.5 |     | ±10                 | ±11.5 |      | V     |

|                    |                                                               | $R_L \geq 2 \ k\Omega$                                                         |                               | Full range       | ±11.5               |       |     | 10.5                |       |      |       |

|                    |                                                               |                                                                                | $V_{O} = \pm 10 V$            |                  | 1000                | 1800  |     | 700                 | 1500  |      |       |

|                    | Large signal differential                                     | $R_L \ge 1 \ k\Omega$ ,                                                        | $V_{O} = \pm 10 V$            |                  | 800                 | 1500  |     |                     | 1500  |      |       |

| A <sub>VD</sub>    | Large-signal differential voltage amplification               | $\begin{array}{l} R_L \geq 0.6 \ k\Omega \\ V_{CC\pm} = \ \pm \ 4 \end{array}$ | , V <sub>O</sub> = ±1 V,<br>V |                  | 250                 | 700   |     | 200                 | 500   |      | V/mV  |

|                    |                                                               | $R_L \ge 2 \ k\Omega$ ,                                                        | $V_{O} = \pm 10 V$            | Full range       | 600                 |       |     | 300                 |       |      |       |

| r <sub>i(CM)</sub> | Common-mode input resistance                                  |                                                                                |                               |                  |                     | 3     |     |                     | 2     |      | GΩ    |

| r <sub>o</sub>     | Output resistance                                             | $V_{O} = 0,$                                                                   | l <sub>O</sub> = 0            | 25°C             |                     | 70    |     |                     | 70    |      | Ω     |

| CMRR               | Common-mode rejection                                         | $V_{IC} = \pm 11 V$                                                            |                               | 25°C             | 114                 | 126   |     | 100                 | 120   |      | -10   |

|                    | ratio                                                         | $V_{IC} = \pm 10 V$                                                            | 1                             | Full range       | 110                 |       |     | 94                  |       |      | dB    |

| Kour               | Supply voltage rejection                                      | $V_{CC\pm} = \pm 4$                                                            | V to ±18 V                    | 25°C             | 100                 | 120   |     | 94                  | 118   |      | dB    |

| k <sub>SVR</sub>   | ratio                                                         | $V_{CC\pm} = \pm 4.5$                                                          | 5 V to ±18 V                  | Full range       | 96                  |       |     | 86                  |       |      | uВ    |

<sup>†</sup> Full range is  $-55^{\circ}$ C to  $125^{\circ}$ C.

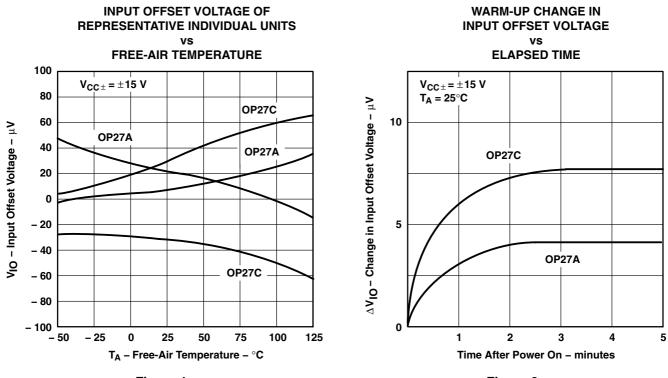

NOTES: 3. Input offset voltage measurements are performed by automatic test equipment approximately 0.5 seconds after applying power. 4. Long-term drift of input offset voltage refers to the average trend line of offset voltage versus time over extended periods after the

first 30 days of operation. Excluding the initial hour of operation, changes in  $V_{IO}$  during the first 30 days are typically 2.5  $\mu$ V (see Figure 3).

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### OP27C OP27A PARAMETER **TEST CONDITIONS** UNIT MAX MIN TYP MAX MIN TYP SR Slew rate $A_{VD} \geq 1,$ $R_L \ge 2 \ k\Omega$ 1.7 2.8 1.7 2.8 V/µs $f=0.1~Hz~to~10~Hz,~~R_S=20~\Omega,$ Peak-to-peak equivalent $V_{N(PP)}$ 0.225 0.375 0.225 0.375 μV See Figure 26 input noise voltage f = 10 Hz, ${\sf R}_{\sf S}$ = 20 $\Omega$ 3.5 8 3.8 8 Vn Equivalent input noise voltage nV/√Hz f = 1 kHz, $R_S = 20 \Omega$ 3 4 3.2 4 f = 10 Hz, See Figure 27 5 25 5 25 Equivalent input noise current pA/√Hz I<sub>n</sub> f = 1 kHz,See Figure 27 0.7 2.5 0.7 2.5 Gain-bandwidth product f = 100 kHz 5 8 5 8 MHz

# OP27 operating characteristics, V<sub>CC $\pm$ </sub> = ±15 V, T<sub>A</sub> = 25°C

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

### **TYPICAL CHARACTERISTICS**

#### **Table of Graphs**

|                    |                                     |                                                                                             | FIGURE                     |

|--------------------|-------------------------------------|---------------------------------------------------------------------------------------------|----------------------------|

| V <sub>IO</sub>    | Input offset voltage                | vs Temperature                                                                              | 1                          |

| $\Delta V_{IO}$    | Change in input offset voltage      | vs Time after power on<br>vs Time (long-term drift)                                         | 2<br>3                     |

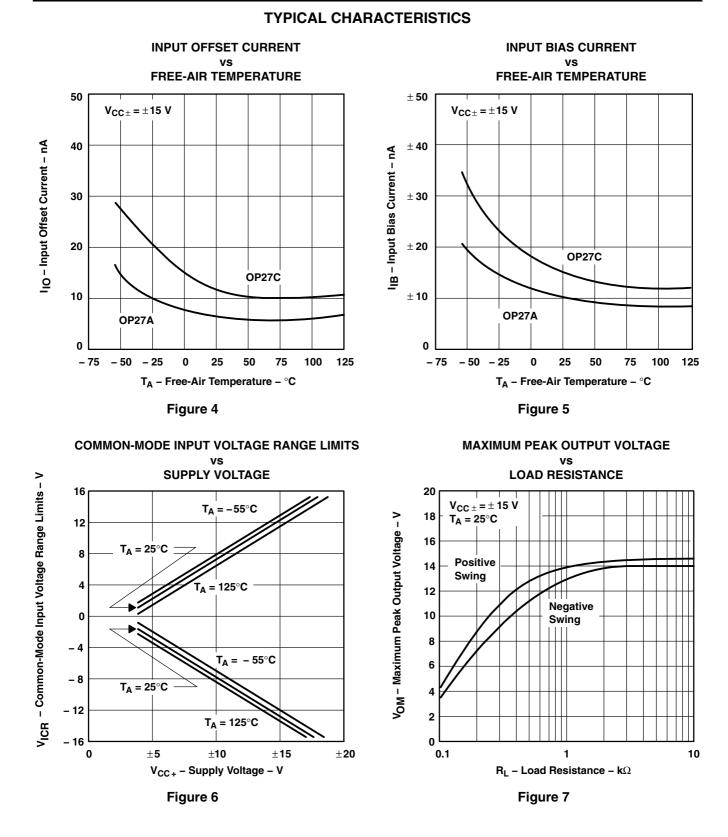

| I <sub>IO</sub>    | Input offset current                | vs Temperature                                                                              | 4                          |

| I <sub>IB</sub>    | Input bias current                  | vs Temperature                                                                              | 5                          |

| V <sub>ICR</sub>   | Common-mode input voltage range     | vs Supply voltage                                                                           | 6                          |

| V <sub>OM</sub>    | Maximum peak output voltage         | vs Load resistance                                                                          | 7                          |

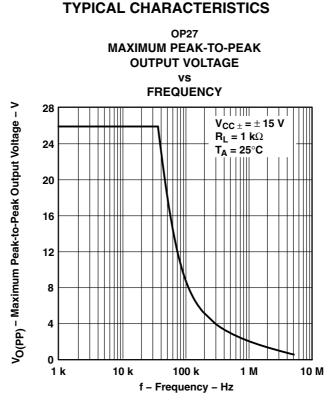

| V <sub>O(PP)</sub> | Maximum peak-to-peak output voltage | vs Frequency                                                                                | 8                          |

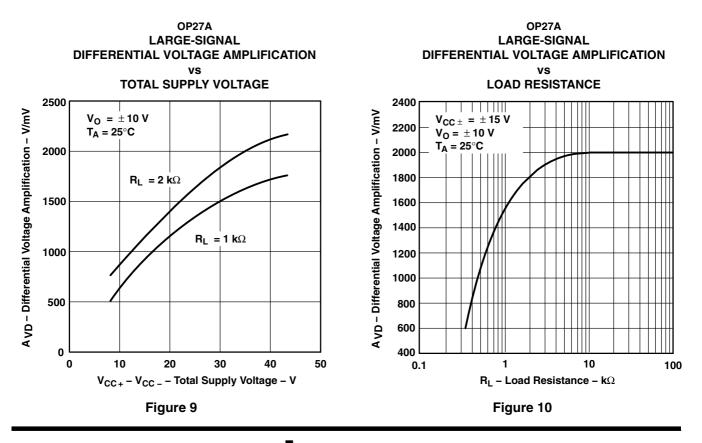

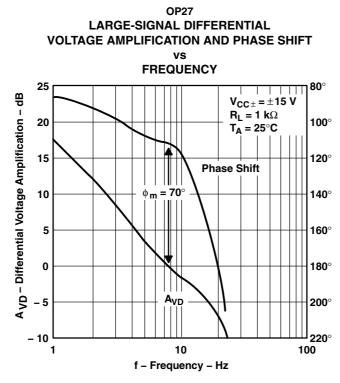

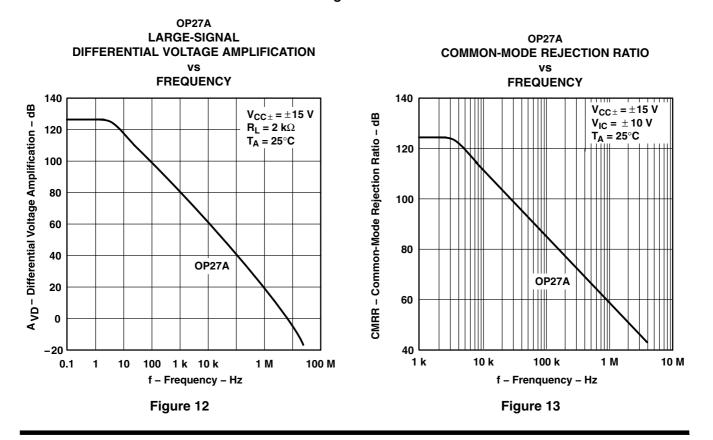

| A <sub>VD</sub>    | Differential voltage amplification  | vs Supply voltage<br>vs Load resistance<br>vs Frequency                                     | 9<br>10<br>11, 12          |

| CMRR               | Common-mode rejection ratio         | vs Frequency                                                                                | 13                         |

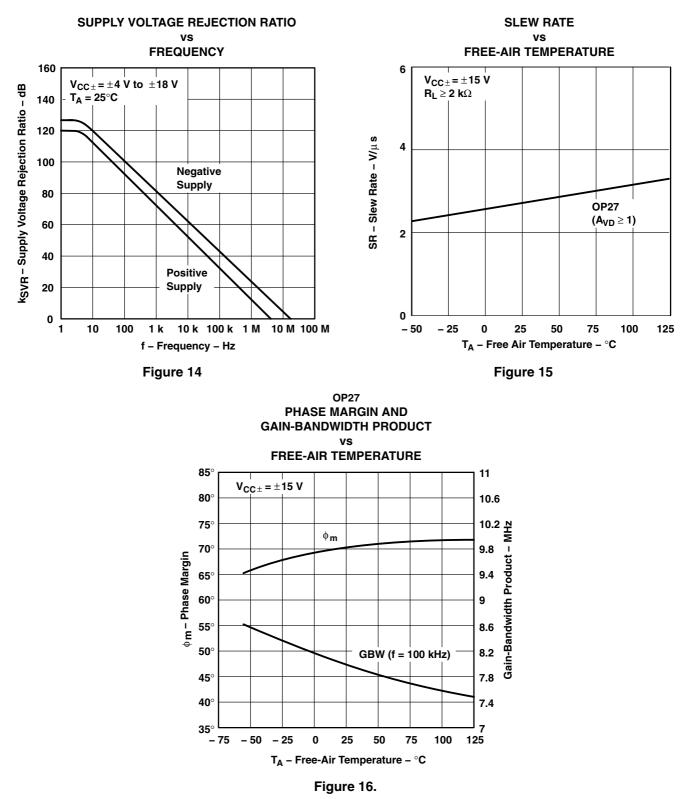

| k <sub>SVR</sub>   | Supply voltage rejection ratio      | vs Frequency                                                                                | 14                         |

| SR                 | Slew rate                           | vs Temperature                                                                              | 15                         |

| φ <sub>m</sub>     | Phase margin                        | vs Temperature                                                                              | 16                         |

| ¢                  | Phase shift                         | vs Frequency                                                                                | 11                         |

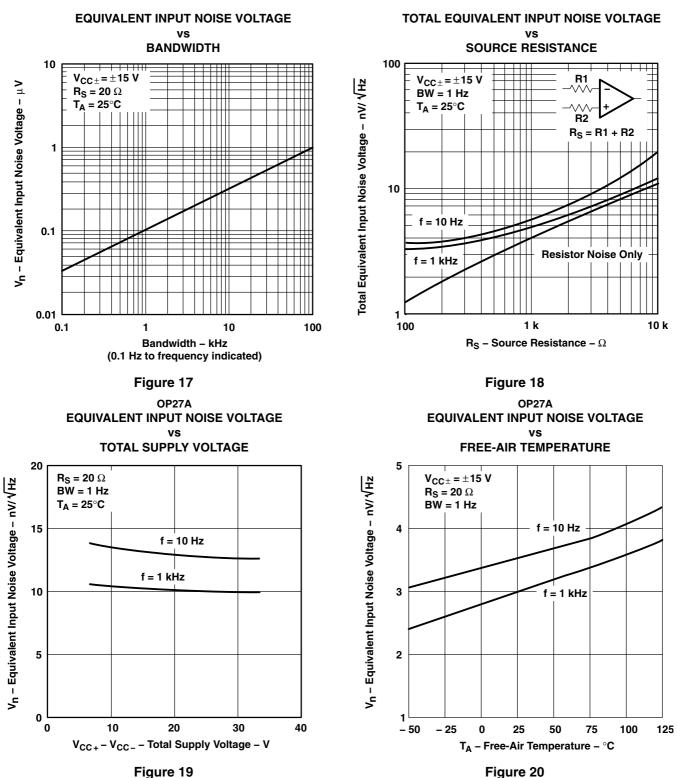

| V <sub>n</sub>     | Equivalent input noise voltage      | vs Bandwidth<br>vs Source resistance<br>vs Supply voltage<br>vs Temperature<br>vs Frequency | 17<br>18<br>19<br>20<br>21 |

|                    | Gain-bandwidth product              | vs Temperature                                                                              | 16                         |

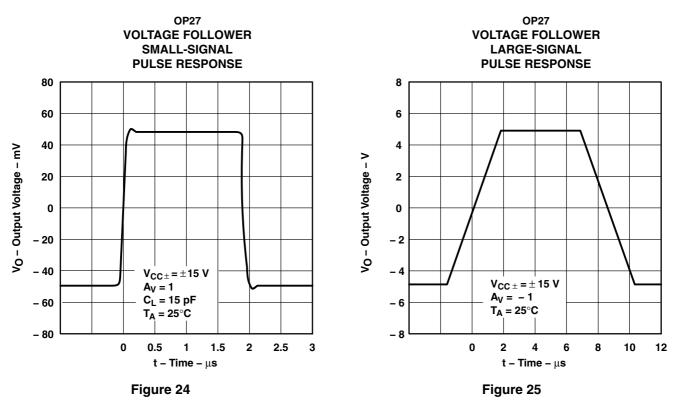

| l <sub>os</sub>    | Short-circuit output current        | vs Time                                                                                     | 22                         |

| I <sub>CC</sub>    | Supply current                      | vs Supply voltage                                                                           | 23                         |

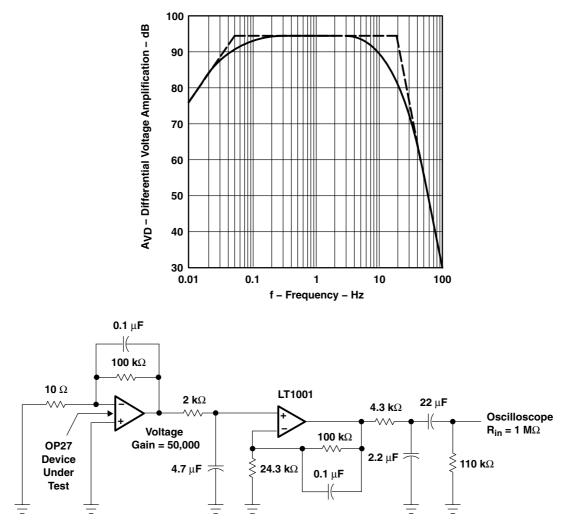

|                    | Pulse response                      | Small signal<br>Large signal                                                                | 24<br>25                   |

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### **TYPICAL CHARACTERISTICS**

LONG-TERM DRIFT OF INPUT OFFSET VOLTAGE OF REPRESENTATIVE INDIVIDUAL UNITS

Figure 3

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

# POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

8

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

**TYPICAL CHARACTERISTICS**

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

**TYPICAL CHARACTERISTICS**

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### **TYPICAL CHARACTERISTICS**

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### **TYPICAL CHARACTERISTICS**

#### general

The OP27 series devices can be inserted directly onto OP07, OP05,  $\mu$ A725, and SE5534 sockets with or without removing external compensation or nulling components. In addition, the OP27 can be fitted to  $\mu$ A741 sockets by removing or modifying external nulling components.

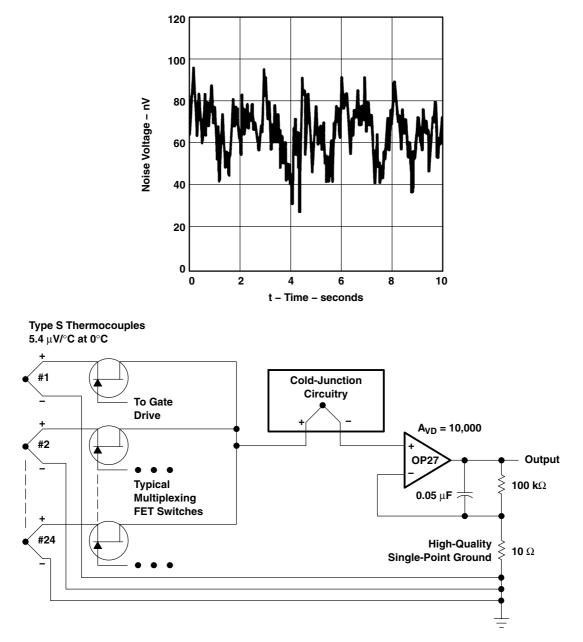

#### noise testing

Figure 26 shows a test circuit for 0.1-Hz to 10-Hz peak-to-peak noise measurement of the OP27. The frequency response of this noise tester indicates that the 0.1-Hz corner is defined by only one zero. Because the time limit acts as an additional zero to eliminate noise contributions from the frequency band below 0.1 Hz, the test time to measure 0.1-Hz to 10-Hz noise should not exceed 10 seconds.

Measuring the typical 80-nV peak-to-peak noise performance of the OP27 requires the following special test precautions:

#### **APPLICATION INFORMATION**

#### noise testing (continued)

- The device should be warmed up for at least five minutes. As the operational amplifier warms up, the

offset voltage typically changes 4 μV due to the chip temperature increasing from 10°C to 20°C starting

from the moment the power supplies are turned on. In the 10-s measurement interval, these

temperature-induced effects can easily exceed tens of nanovolts.

- 2. For similar reasons, the device should be well shielded from air currents to eliminate the possibility of thermoelectric effects in excess of a few nanovolts, which would invalidate the measurements.

- 3. Sudden motion in the vicinity of the device should be avoided, as it produces a feedthrough effect that increases observed noise.

NOTE: All capacitor values are for nonpolarized capacitors only.

Figure 26. 0.1-Hz to 10-Hz Peak-to-Peak Noise Test Circuit and Frequency Response

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### **APPLICATION INFORMATION**

#### noise testing (continued)

When measuring noise on a large number of units, a noise-voltage density test is recommended. A 10-Hz noise-voltage density measurement correlates well with a 0.1-Hz to 10-Hz peak-to-peak noise reading since both results are determined by the white noise and the location of the 1/f corner frequency.

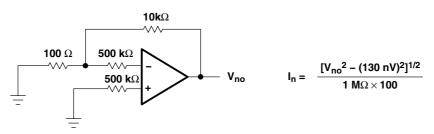

Figure 27 shows a circuit measuring current noise and the formula for calculating current noise.

Figure 27. Current Noise Test Circuit and Formula

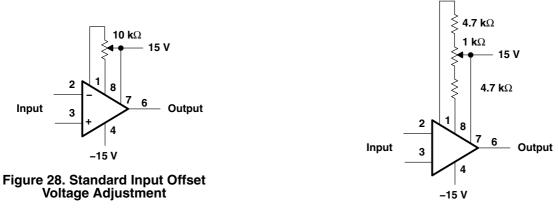

#### offset voltage adjustment

The input offset voltage and temperature coefficient of the OP27 are permanently trimmed to a low level at wafer testing. However, if further adjustment of V<sub>IO</sub> is necessary, using a 10-k $\Omega$  nulling potentiometer as shown in Figure 28 does not degrade the temperature coefficient  $\alpha_{VIO}$ . Trimming to a value other than zero creates an  $\alpha_{VIO}$  of V<sub>IO</sub>/300  $\mu$ V/°C. For example, if V<sub>IO</sub> is adjusted to 300  $\mu$ V, the change in  $\alpha_{VIO}$  is 1  $\mu$ V/°C.

The adjustment range with a 10-k $\Omega$  potentiometer is approximately ±2.5 mV. If a smaller adjustment range is needed, the sensitivity and resolution of the nulling can be improved by using a smaller potentiometer in conjunction with fixed resistors. The example in Figure 29 has an approximate null range of ±200  $\mu$ V.

Figure 29. Input Offset Voltage Adjustment With Improved Sensitivity

#### offset voltage and drift

Unless proper care is exercised, thermoelectric effects caused by temperature gradients across dissimilar metals at the contacts to the input terminals can exceed the inherent temperature coefficient  $\propto V_{IO}$  of the amplifier. Air currents should be minimized, package leads should be short, and the two input leads should be close together and at the same temperature.

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### **APPLICATION INFORMATION**

#### offset voltage and drift (continued)

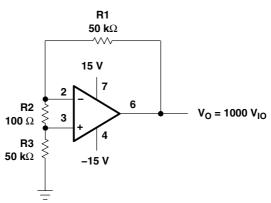

The circuit shown in Figure 30 measures offset voltage. This circuit can also be used as the burn-in configuration for the OP27 with the supply voltage increased to 20 V, R1 = R3 = 10 k $\Omega$ , R2 = 200  $\Omega$ , and A<sub>VD</sub> = 100.

NOTE A: Resistors must have low thermoelectric potential.

#### Figure 30. Test Circuit for Offset Voltage and Offset Voltage Temperature Coefficient

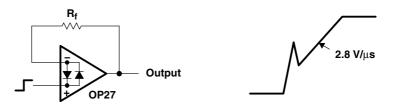

#### unity gain buffer applications

The resulting output waveform, when  $R_f \le 100 \Omega$  and the input is driven with a fast large-signal pulse (>1 V), is shown in the pulsed-operation diagram in Figure 31.

Figure 31. Pulsed Operation

During the initial (fast-feedthrough-like) portion of the output waveform, the input protection diodes effectively short the output to the input, and a current, limited only by the output short-circuit protection, is drawn by the signal generator. When  $R_f \ge 500 \Omega$ , the output is capable of handling the current requirements (load current  $\le 20 \text{ mA}$  at 10 V), the amplifier stays in its active mode, and a smooth transition occurs. When  $R_f \ge 2 k\Omega$ , a pole is created with  $R_f$  and the amplifier's input capacitance, creating additional phase shift and reducing the phase margin. A small capacitor (20 pF to 50 pF) in parallel with  $R_f$  eliminates this problem.

SLOS100E - FEBRUARY 1989 - REVISED FEBRUARY 2010

#### **APPLICATION INFORMATION**

#### unity gain buffer applications (continued)

NOTE A: If 24 channels are multiplexed per second and the output is required to settle to 0.1 % accuracy, the amplifier's bandwidth cannot be limited to less than 30 Hz. The peak-to-peak noise contribution of the OP27 will still be only 0.11 µV, which is equivalent to an error of only 0.02°C.

Figure 32. Low-Noise, Multiplexed Thermocouple Amplifier and 0.1-Hz to 10-Hz Peak-to-Peak Noise Voltage

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)     | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|---------------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| JM38510/13506BPA | ACTIVE        | CDIP         | JG                 | 8    | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | JM38510<br>/13506BPA    | Samples |

| M38510/13506BPA  | ACTIVE        | CDIP         | JG                 | 8    | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   | -55 to 125   | JM38510<br>/13506BPA    | Samples |

| OP27AFKB         | ACTIVE        | LCCC         | FK                 | 20   | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   |              | OP27AFKB                | Samples |

| OP27AJGB         | ACTIVE        | CDIP         | JG                 | 8    | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   |              | OP27AJGB                | Samples |

| OP27CJGB         | ACTIVE        | CDIP         | JG                 | 8    | 1              | Non-RoHS<br>& Green | SNPB                                 | N / A for Pkg Type   |              | OP27CJGB                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

www.ti.com

9-Mar-2021

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

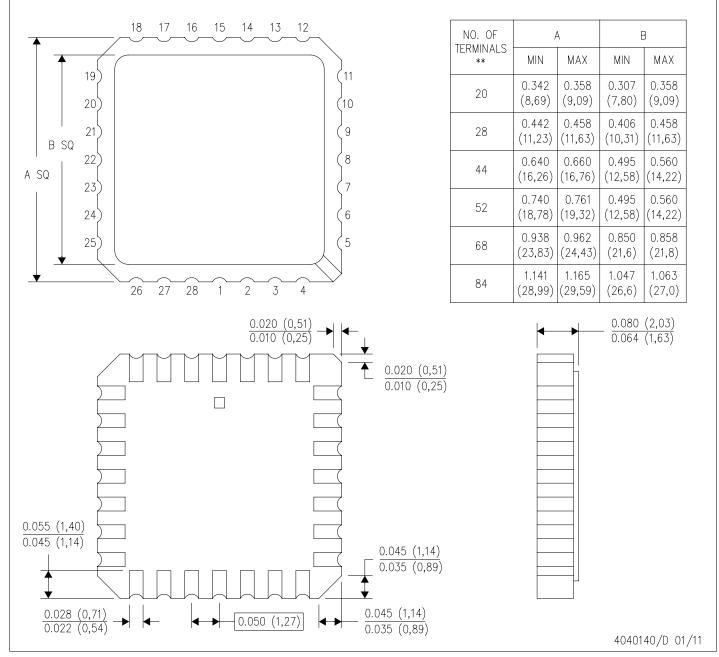

LEADLESS CERAMIC CHIP CARRIER

FK (S-CQCC-N\*\*) 28 TERMINAL SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. Falls within JEDEC MS-004

# **MECHANICAL DATA**

MCER001A - JANUARY 1995 - REVISED JANUARY 1997

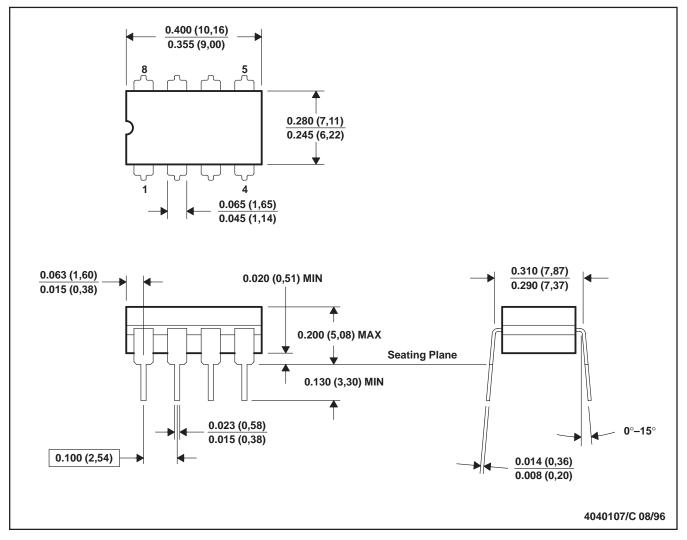

#### **CERAMIC DUAL-IN-LINE**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification.

- E. Falls within MIL STD 1835 GDIP1-T8

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated