# SIGNETICS INSTRUCTOR 50 USERS' GUIDE

a subsidiary of U.S. Philips Corporation

Signetics Corporation P.O. Box 9052 811 East Argues Avenue Sunnyvale, California 94086 Telephone 408/739-7700 Signetics reserves the right to make changes in the products contained in this manual in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement. Reproduction of any portion hereof without the prior written consent of Signetics is prohibited.

Copyright June 1978, Signetics Corporation

#### PREFACE

This manual provides tutorial and reference information on the Signetics INSTRUCTOR 50--a complete, fully assembled and low cost microcomputer system. The INSTRUCTOR 50's computing power is enhanced by the Signetics 2650 microprocessor which is described in detail in Chapter 9.

INSTRUCTOR 50 is designed to assist you in learning programming and in writing, debugging, and testing the programs you develop. There is enough information here to get you started, whether or not you have ever written a program before. The only prerequisite is a familiarity with the 2650 microprocessor. Readers who are not familiar with the 2650's hardware structure and instruction set should read Chapter 9 prior to using the INSTRUCTOR 50.

The microprocessor has brought with it a host of terms which experienced users bandy back and forth with the greatest of ease. For the novice, this "language within a language" can be an obstacle of no small proportions. For the benefit of these people, Chapter 1 is devoted exclusively to microcomputer basics. To further assist you, we've put a glossary in the back to summarize some of the more frequently used buzz words.

### CONTENTS

|     |                                                    | Page       |

|-----|----------------------------------------------------|------------|

| PRE | FACE                                               | iii        |

| 1.  | MICROCOMPUTER BASICS                               | 1-1        |

|     | A Micro Defined                                    | 1-1        |

|     | Word/Byte/Nibble                                   | 1-1        |

|     | Binary Notation                                    | 1-2        |

|     | Hexadecimal Notation                               | 1-2        |

|     | Architecture                                       | 1-3        |

|     | Program Counter (Jumps, Subroutines and the Stack) | 1-4        |

|     | Instruction Register and Decoder                   | 1-6        |

|     | Address Register(s)                                | 1-6<br>1-6 |

|     | Addressing Modes                                   | 1-8        |

|     | Extended/Non-Extended I/OSoftware                  | 1-0        |

|     | Machine Language                                   | 1-10       |

|     | Assembly Language                                  | 1-10       |

|     | Higher-Level Languages                             | 1-10       |

| •   | Other Software                                     | 1-10       |

| 2.  | GETTING STARTED                                    | 2-1        |

|     | Introduction                                       | 2-1        |

|     | Power On and Initial Display                       | 2-1        |

|     | Operating Modes                                    | 2-1        |

|     | Keying in and Entering Values                      | 2-2        |

|     | Correcting Entry Errors                            | 2-2        |

|     | The Prompt Light                                   | 2-3        |

|     | Entering and Executing a Simple Program            | 2-3        |

|     | Example 2: The Billboard Program                   | 2-6        |

|     | Example 3: The Clock Program                       | 2-12       |

| 3.  | SYSTEM OVERVIEW                                    | 3-1        |

|     | Introduction                                       | 3-1        |

|     | 2650 Microprocessor                                | 3-1        |

|     | 2656 System Memory Interface                       | 3-3        |

|     | Keyboards                                          | 3-3        |

|     | Display Panel                                      | 3-3        |

|     | Audio Cassette Interface                           | 3-3        |

|     | S100-Compatible Expansion Bus                      | 3-3        |

|     | Monitor Firmware                                   | 3-5        |

|     | Debugging Aids                                     | 3-5        |

|     | On-Board User I/O                                  | 3-5<br>3-7 |

|     | Forced Jump Logic                                  | 3-7        |

|     | Memory and I/O Organization                        | 3-7<br>3-7 |

|     | Internal Power Supply                              | 3-7        |

|     |                                                    |            |

## **CONTENTS (cont.)**

|    |                                                           | Page       |

|----|-----------------------------------------------------------|------------|

| 4. | CONTROLS AND INDICATORS                                   | 4-1        |

|    | Introduction                                              | 4-1        |

|    | Function Control Keyboard                                 | 4-1<br>4-3 |

|    | Hexadecimal Keyboard                                      | 4-4        |

|    | Eight-Digit Hex Display Panel<br>Port Data Input Switches | 4-4        |

|    | Port Data Indicators                                      | 4-4        |

|    | Direct/Indirect Interrupt Switch                          | 4-4        |

|    | Port Address Select Switch                                | 4-4        |

|    | FLAG Indicator                                            | 4-4        |

|    | RUN Indicator                                             | 4-4        |

| 5. | COMMAND DESCRIPTIONS                                      | 5-1        |

|    |                                                           | <b>г</b> 1 |

|    | Introduction                                              | 5-1<br>5-2 |

|    | Display and Alter Registers                               | 5-4        |

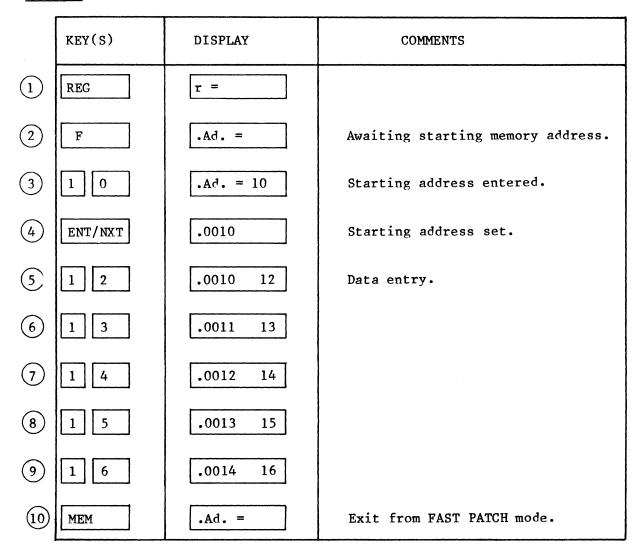

|    | Display and Alter Memory<br>Fast Patch                    | 5-4<br>5-6 |

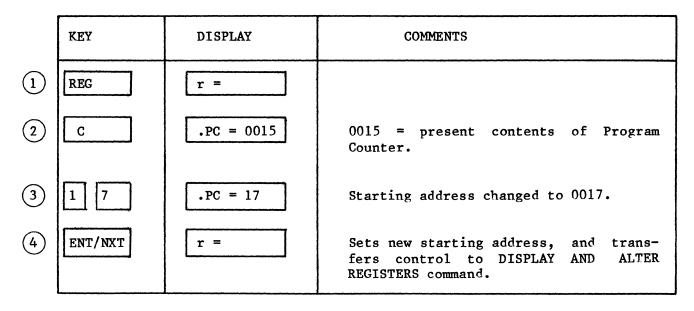

|    | Display and Alter Program Counter                         | 5-8        |

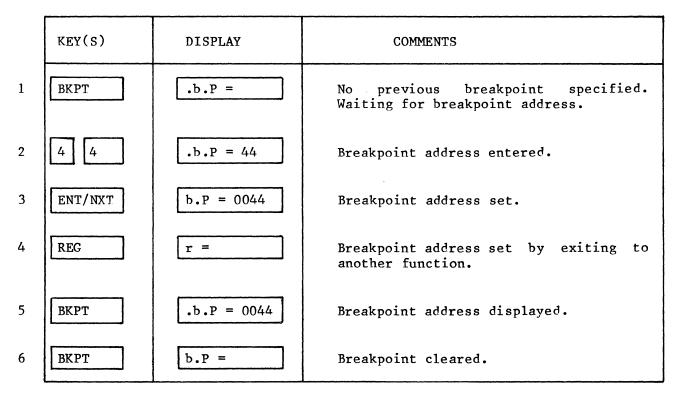

|    | Breakpoint                                                | 5-10       |

|    | Step                                                      | 5-12       |

|    | Write Cassette                                            | 5-14       |

|    | Adjust Cassette                                           | 5-17       |

|    | Read Cassette                                             | 5-19       |

|    | Run                                                       | 5-21       |

|    | Reset                                                     | 5-22       |

|    | Error Messages                                            | 5-23       |

| 6. | USING THE INSTUCTOR 50                                    | 6-1        |

|    | Restrictions on Using the 2650 Instruction Set            | 6-1        |

|    | Using Interrupts                                          | 6-1        |

|    | Using the I/O Switches and Lights                         | 6-5        |

|    | FLAG and SENSE I/O                                        | 6-5        |

|    | Non-Extended I/0                                          | 6-5        |

|    | Extended I/O                                              | 6-6<br>6-6 |

|    | Memory Mapped I/O                                         | 6-6        |

|    | Calling Monitor Subroutines<br>MOVE Subroutine            | 6-8        |

|    | DISPLAY Subroutine                                        | 6-10       |

|    | USER DISPLAY Subroutine                                   | 6-12       |

|    | NIBBLE Subroutine                                         | 6-14       |

|    | INPUT DATA Subroutine                                     | 6-16       |

|    | MODIFY DATA Subroutine                                    | 6-19       |

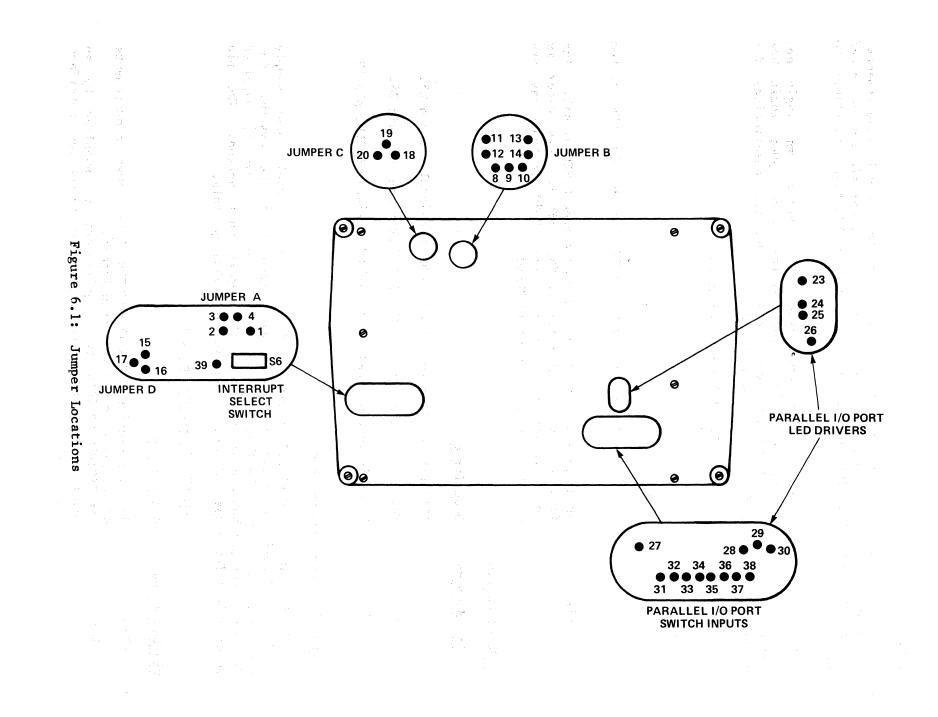

|    | Jumper Options                                            | 6-22       |

|    | Jumper A - Interrupt Selection                            | 6-22       |

|    | Jumper B - S100 Clock Select                              | 6-24       |

|    | Jumper C - Power Source Select                            | 6-24       |

|    | Jumper D - Cassette Output Selection                      | 6-25       |

## **CONTENTS (cont.)**

| 7.       SYSTEM EXPANSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 8. THEORY OF OPERATION.       8-1         Introduction.       8-1         Basic Concept.       8-1         Detailed Block Diagram Description.       8-3         The Microcomputer.       8-3         INSTRUCTOR 50 Memory Allocation.       8-5         Parallel I/O Port.       8-8         Keyboard and Display Logic.       8-8         Bit Assignments for Keyboard and Display Ports.       8-11         The Cassette Interface.       8-12         Interrupt Logic.       8-12         Forced Jump Logic.       8-14         Breakpoint Detection.       8-14         Single Step.       8-15         Sil00 Bus Interface.       8-15         System Power.       8-16         9. THE 2650 MICROPROCESSOR.       9-1         Interdaces.       9-2         Wide Range of Applications.       9-2         2650 Microprocessor Characteristics.       9-2         Interfaces.       9-3         Program Status Word.       9-5         Sense (S).       9-5         Interrupt Inhibit (II).       9-6         Condition Code (CC).       9-6         Interdigit Carry (IDC).       9-7         With/Without Carry (WC).       9-7 </td <td>7.</td> <td>SYSTEM EXPANSION</td> <td>7-1</td> | 7. | SYSTEM EXPANSION                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-1                                                                                                                                             |

| Introduction.       8-1         Basic Concept.       8-1         Detailed Block Diagram Description.       8-3         The Microcomputer.       8-3         INSTRUCTOR 50 Memory Allocation.       8-5         Parallel I/O Port.       8-8         Keyboard and Display Logic.       8-8         Bit Assignments for Keyboard and Display Ports.       8-11         The Cassette Interface       8-12         Forced Jump Logic.       8-12         Forced Jump Logic.       8-14         Single Step.       8-15         SlOB Bus Interface.       8-15         System Power.       8-15         System Power.       8-15         System Power.       8-16         9.       THE 2650 MICROPROCESSOR.       9-1         Introduction.       9-1         Ease of Use       9-2         Wide Range of Applications.       9-2         Qeneral.       9-2         Interfaces.       9-2         Interfaces.       9-2         Interfaces.       9-2         Mid Range of Applications.       9-2         Interfaces.       9-2         Interfaces.       9-2         Interfaces.       9-3 <td></td> <td>Introduction</td> <td>7-1</td>                                                          |    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-1                                                                                                                                             |

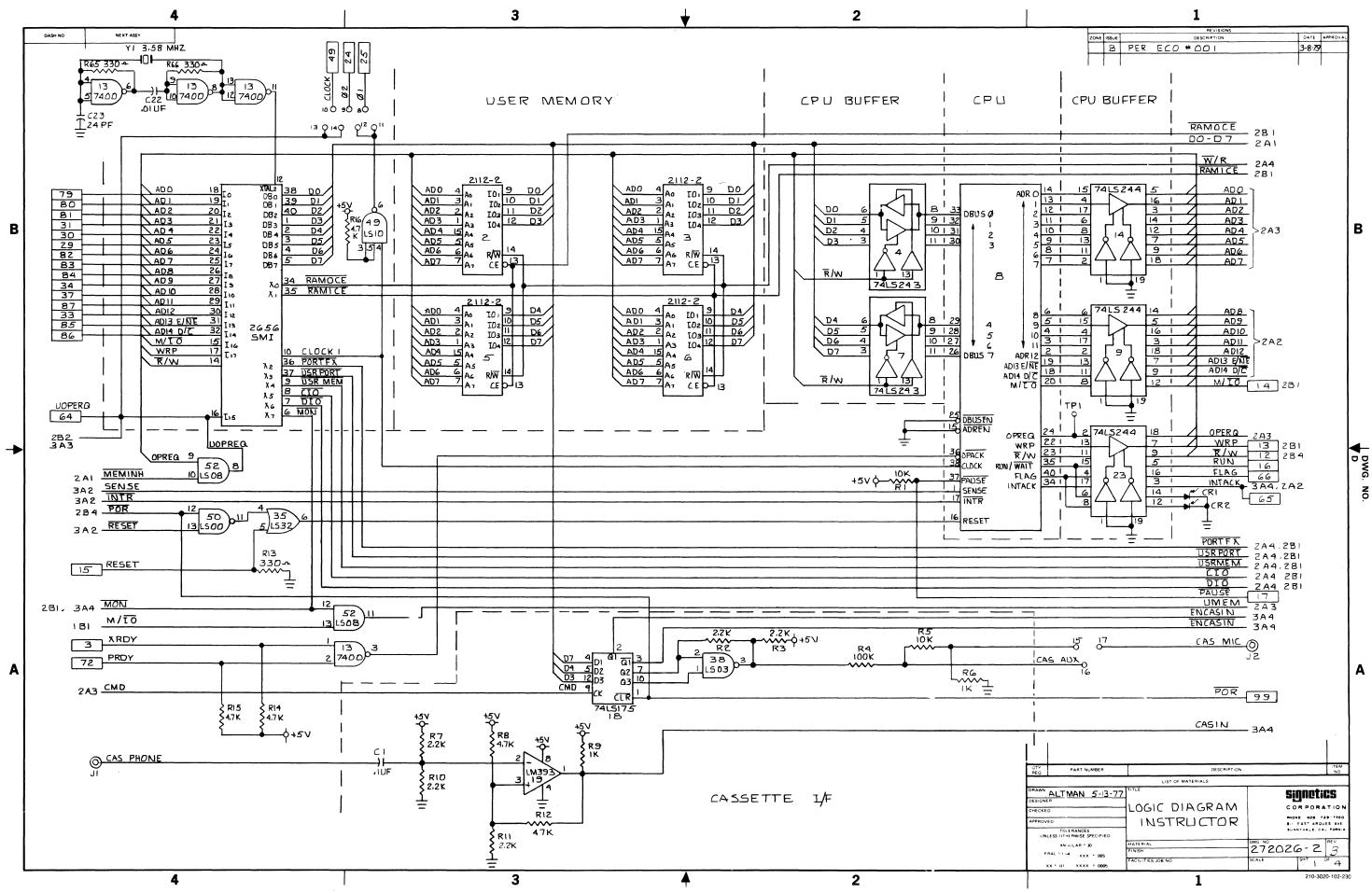

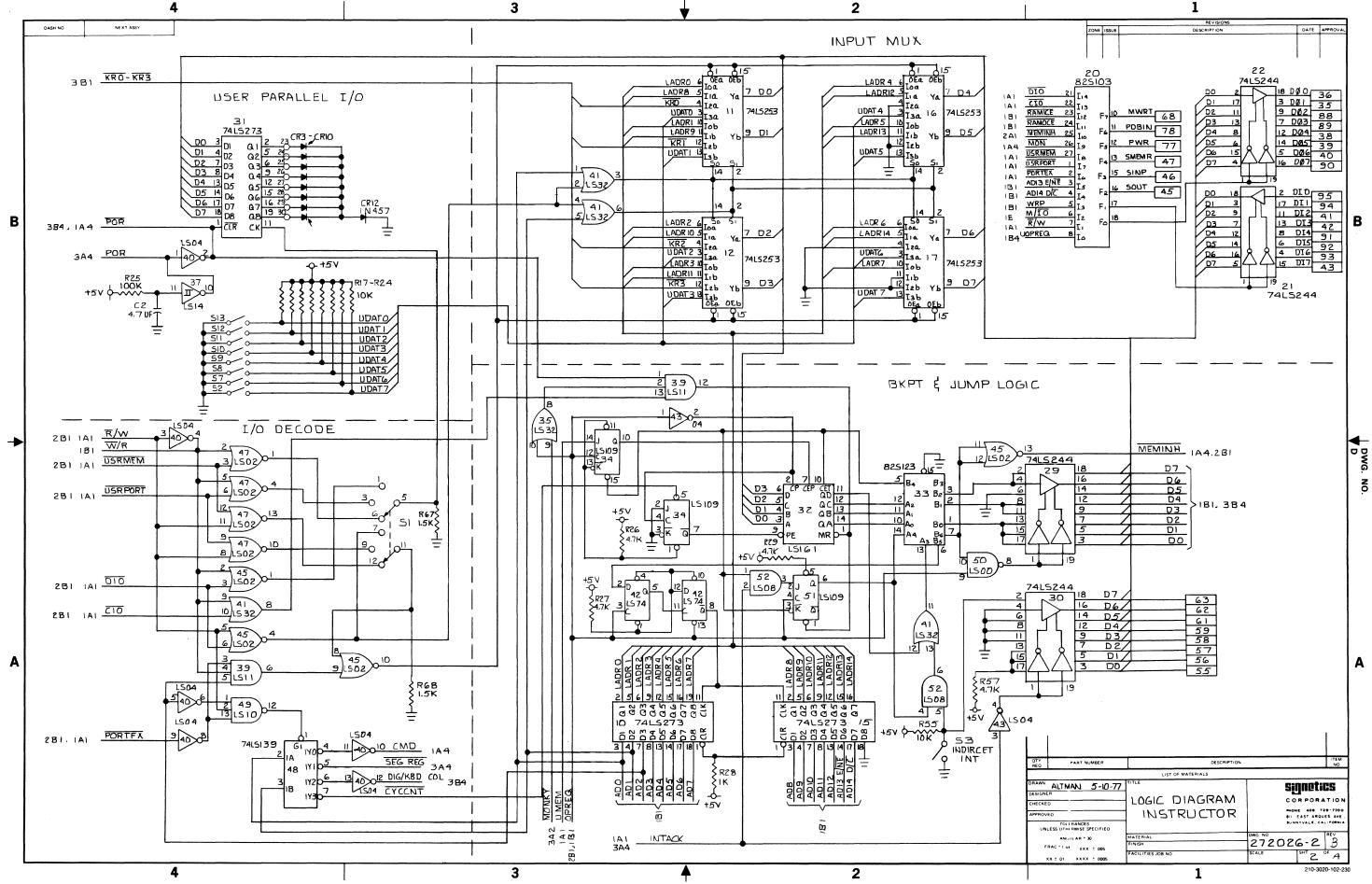

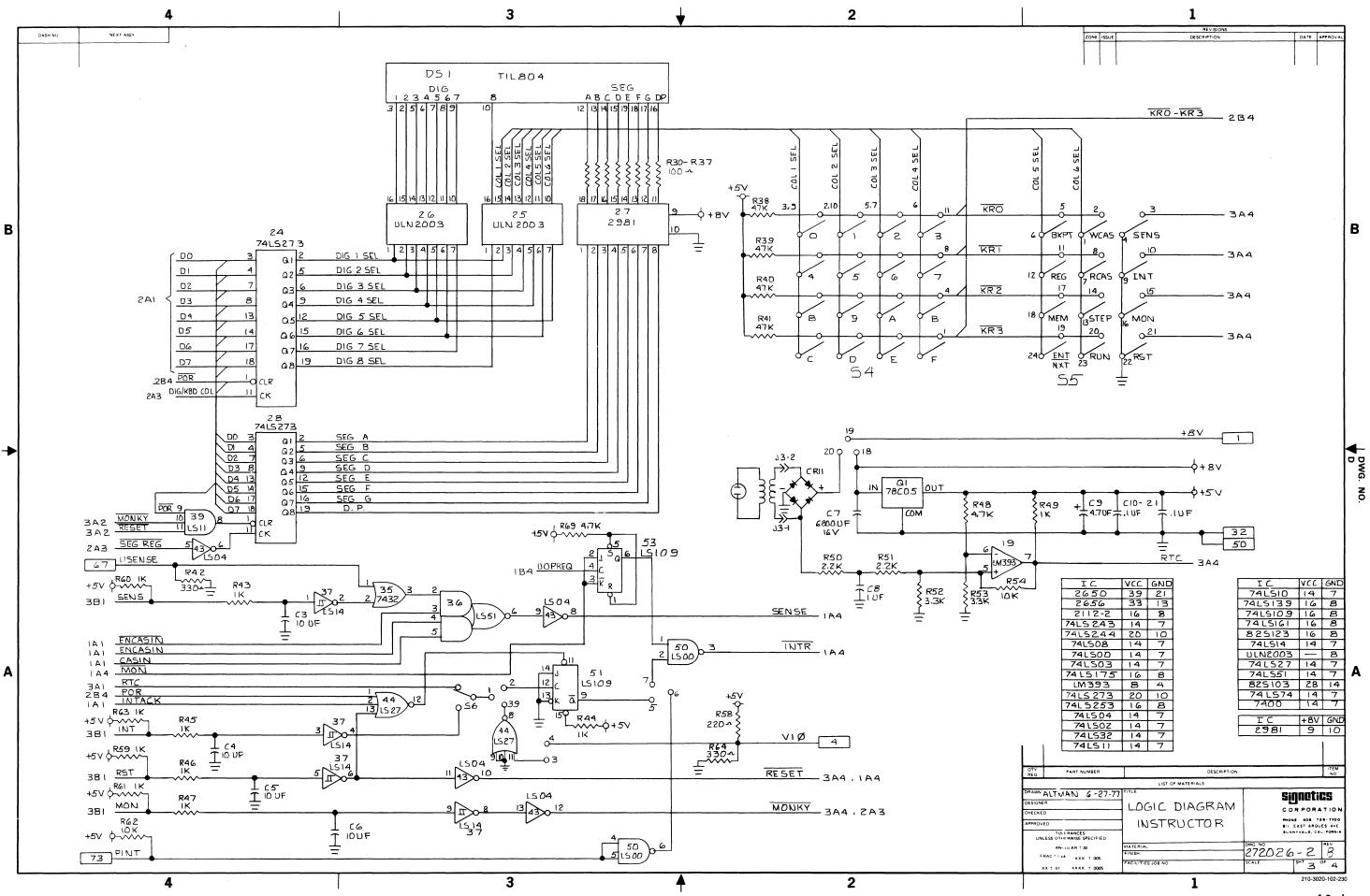

| Basic Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8. | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-1                                                                                                                                             |

| Introduction.       9-1         Features.       9-1         Low System Cost.       9-1         Ease of Use.       9-1         Ease of Use.       9-2         Wide Range of Applications.       9-2         2650 Microprocessor Characteristics.       9-2         General.       9-2         Interfaces.       9-2         Architecture.       9-2         Instruction Set.       9-2         Internal Organization.       9-3         Program Status Word.       9-5         Sense (S).       9-5         Flag (F).       9-5         Interrupt Inhibit (II).       9-6         Stack Pointer (SP).       9-6         Condition Code (CC).       9-6         Interdigit Carry (IDC).       9-7         Register Select (RS).       9-7         With/Without Carry (WC).       9-7         Compare (COM).       9-8         Carry (C).       9-8                                                                                                                                                                                                                                                                                                                                               |    | Basic Concept<br>Detailed Block Diagram Description.<br>The Microcomputer<br>INSTRUCTOR 50 Memory Allocation.<br>Parallel I/O Port.<br>Keyboard and Display Logic.<br>Bit Assignments for Keyboard and Display Ports.<br>The Cassette Interface.<br>Interrupt Logic.<br>Forced Jump Logic.<br>Power On (POR) or MON Key Depression.<br>Breakpoint Detection.<br>Single Step.<br>Sl00 Bus Interface.<br>System Power.                                                           | 8-1<br>8-3<br>8-5<br>8-8<br>8-8<br>8-11<br>8-12<br>8-12<br>8-12<br>8-12<br>8-14<br>8-14<br>8-14<br>8-15<br>8-15<br>8-15                         |

| Features.       9-1         Low System Cost.       9-1         Ease of Use.       9-2         Wide Range of Applications.       9-2         2650 Microprocessor Characteristics.       9-2         General.       9-2         Interfaces.       9-2         Architecture.       9-2         Instruction Set.       9-3         Internal Organization.       9-3         Program Status Word.       9-5         Sense (S).       9-5         Interrupt Inhibit (II).       9-6         Stack Pointer (SP).       9-6         Condition Code (CC).       9-6         Interdigit Carry (IDC).       9-7         Register Select (RS).       9-7         With/Without Carry (WC).       9-7         Compare (COM).       9-8         Carry (C).       9-8                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9. | THE 2650 MICROPROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-1                                                                                                                                             |

| Overflow (OVF) 9-9<br>Memory Organization 9-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | Features.<br>Low System Cost.<br>Ease of Use.<br>Wide Range of Applications.<br>2650 Microprocessor Characteristics.<br>General.<br>Interfaces.<br>Architecture.<br>Instruction Set.<br>Internal Organization.<br>Program Status Word.<br>Sense (S).<br>Flag (F).<br>Interrupt Inhibit (II).<br>Stack Pointer (SP).<br>Condition Code (CC).<br>Interdigit Carry (IDC).<br>Register Select (RS).<br>With/Without Carry (WC).<br>Compare (COM).<br>Carry (C).<br>Overflow (OVF). | 9-1<br>9-2<br>9-2<br>9-2<br>9-2<br>9-2<br>9-2<br>9-3<br>9-3<br>9-5<br>9-5<br>9-5<br>9-6<br>9-6<br>9-7<br>9-7<br>9-7<br>9-7<br>9-8<br>9-8<br>9-9 |

### CONTENTS (cont.)

#### Interface..... 9-11 Pin Configuration..... 9 - 11Signal Descriptions..... 9-11 Signal Timing..... 9-17 Memory Read..... 9-18 Memory Write..... 9-18 I/O Device Read..... 9-19 I/O Device Write..... 9-19 A Minimal System Example..... 9 - 19Input/Output Facilities..... 9-21 Flag and Sense I/O..... 9-21 Non-Extended I/O..... 9-21 Extended I/O..... 9-22 Memory 1/0..... 9-22 Interrupt Mechanism..... 9-24 Subroutine Linkage..... 9-26 Condition Code Usage..... 9-27 Start-Up Procedure..... 9-27 Instructions..... 9 - 27Addressing Modes..... 9-27 Register Addressing..... 9-28 Immediate Addressing..... 9-28 Relative Addressing..... 9-29 Absolute Addressing for Non-Branch Instructions..... 9-29 Absolute Addressing for Branch Instructions...... 9-30 Indirect Addressing..... 9-31 Instruction Format Exceptions..... 9-32 Detailed Processor Instructions..... 9-35 Introduction...... 9-35 Symbols and Abbreviations Used..... 9-35 Calculating Effective Addresses..... 9-36 Instruction Descriptions..... 9-37 INSTRUCTOR 50 SYSTEM SCHEMATICS..... 10. 10 - 1USE PROGRAM LISTINGS..... 11. 11-1 CONVERSION TABLES..... 12. 12 - 1ASCII Conversion Table..... 12 - 1Decimal to Hex Conversion Table..... 12 - 2GLOSSARY..... 13. 13-1

### LIST OF ILLUSTRATIONS

<u>Title</u>

Figure No.

#### Page

| 1-1  | Basic Elements of Computers                       | 1-4  |

|------|---------------------------------------------------|------|

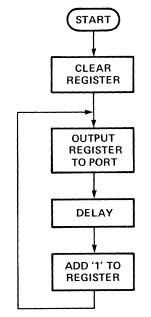

| 2-1  | Flowchart for Binary'Counter Program              | 2-3  |

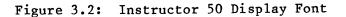

| 2-2  | Flowchart for Billboard Program                   | 2-9  |

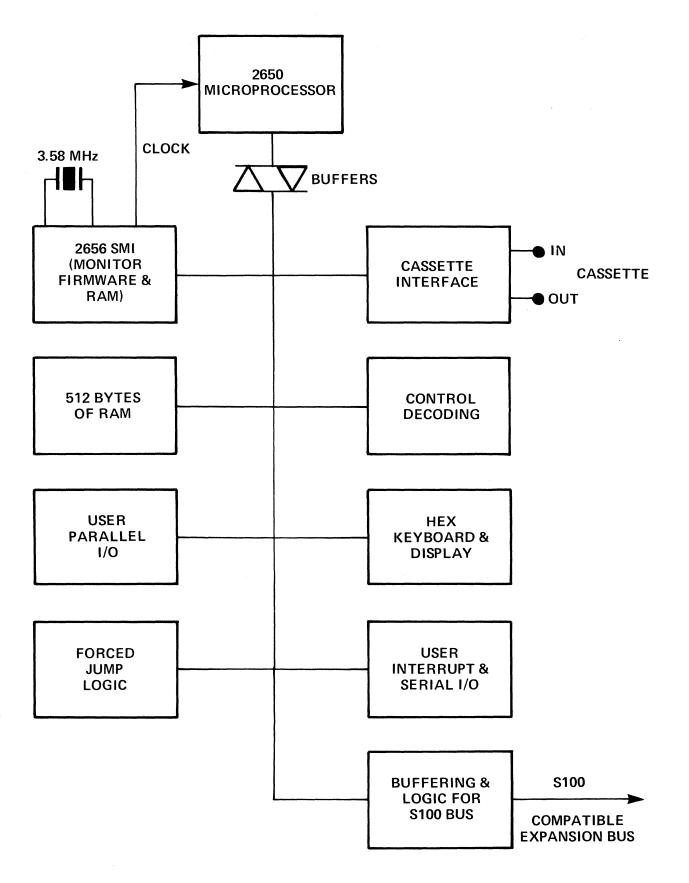

| 3-1  | INSTRUCTOR 50 Basic Block Diagram                 | 3-2  |

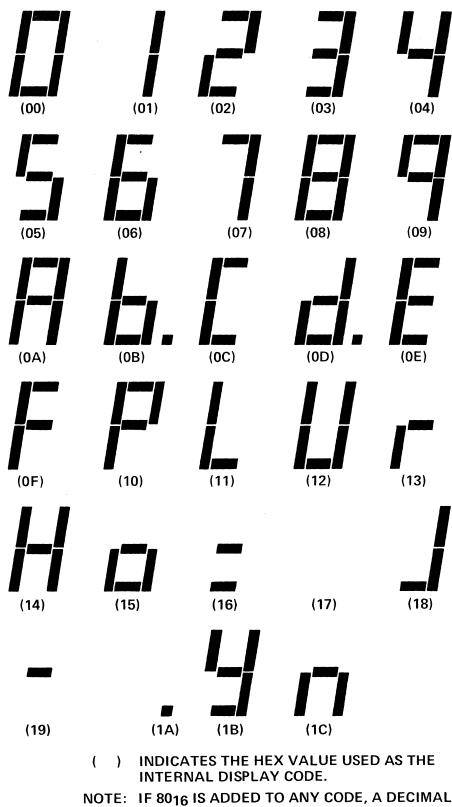

| 3-2  | INSTRUCTOR 50 Display Font                        | 3-4  |

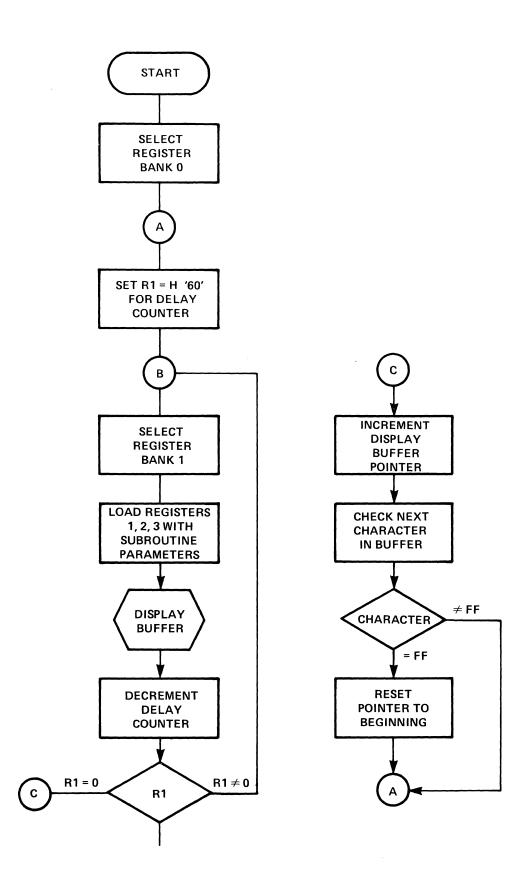

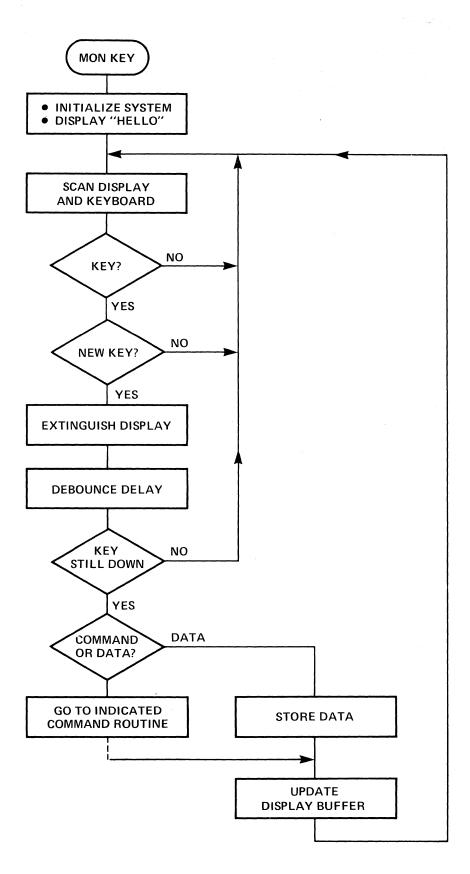

| 3-3  | Basic USE Monitor Flowchart                       | 3-6  |

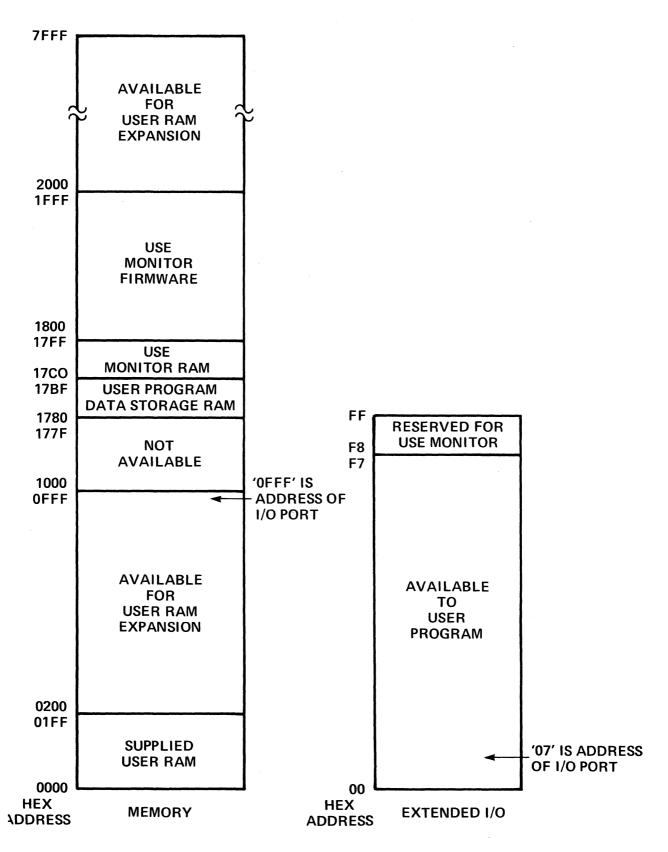

| 3-4  | Memory and I/O Organization                       | 3-8  |

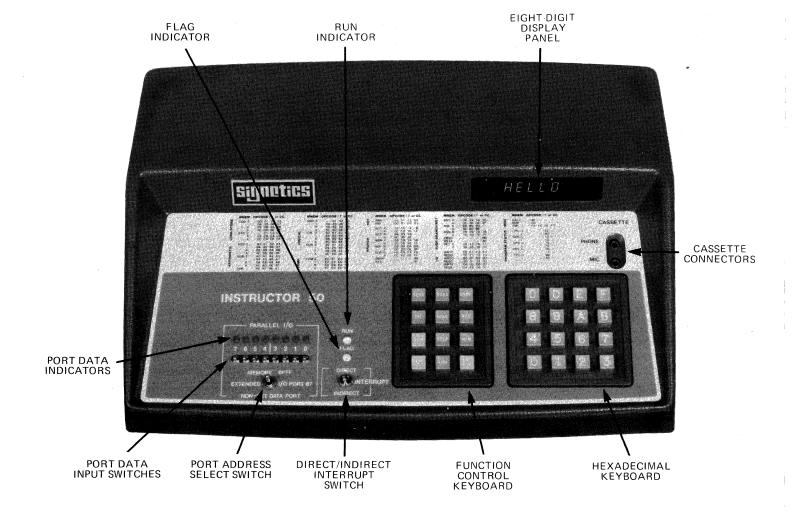

| 4-1  | Controls and Indicators                           | 4-2  |

| 6-1  | Jumper Locations                                  | 6-23 |

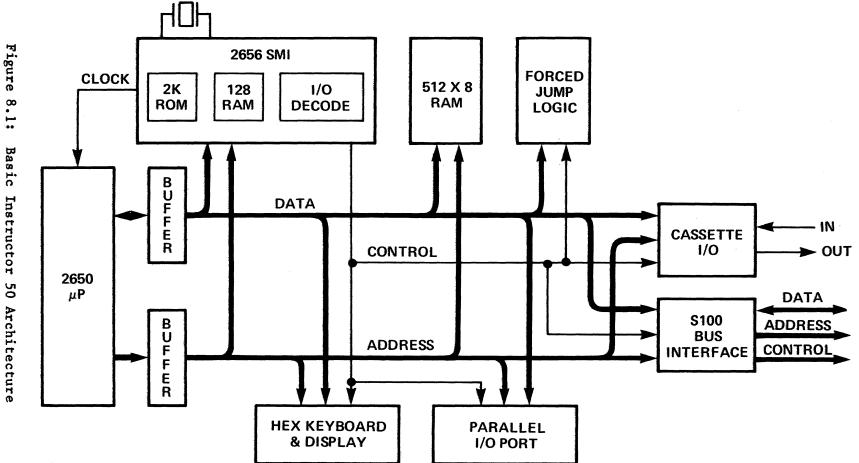

| 8-1  | Basic INSTRUCTOR 50 Architecture                  | 8-2  |

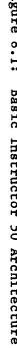

| 8-2  | INSTRUCTOR 50 Detailed Block Diagram              | 8-4  |

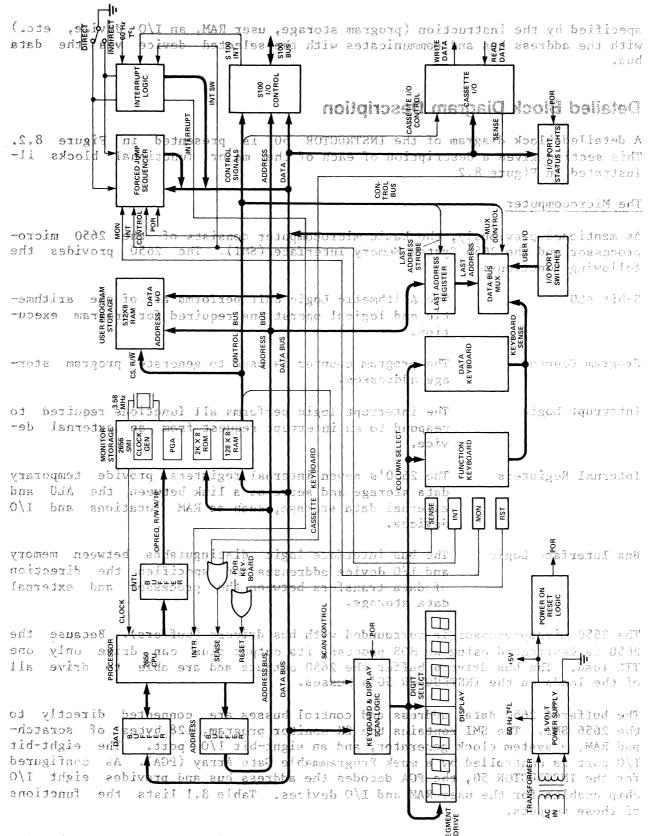

| 8-3  | Memory and I/O Organization                       | 8-7  |

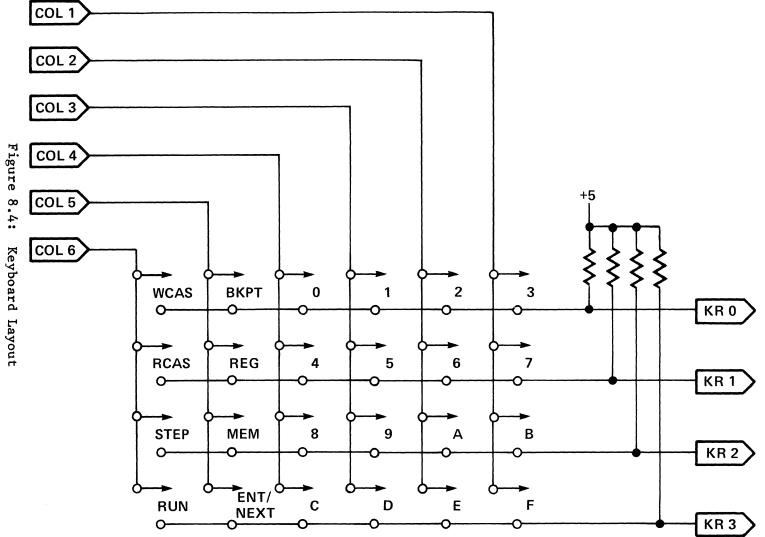

| 8-4  | Keyboard Layout                                   | 8-10 |

| 8-5  | Bit Assignments for Keyboard & Display Ports      | 8-11 |

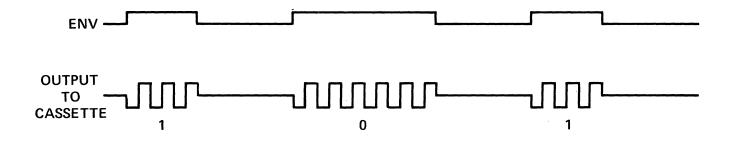

| 8-6  | Cassette Record Waveforms                         | 8-13 |

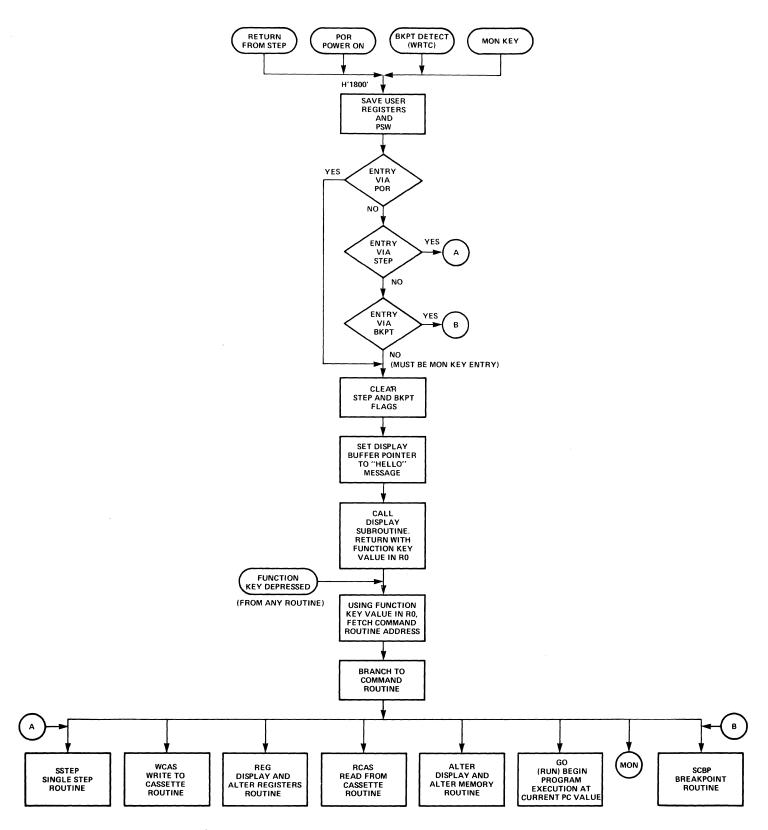

| 8-7  | USE Command and Routine Executive                 | 8-17 |

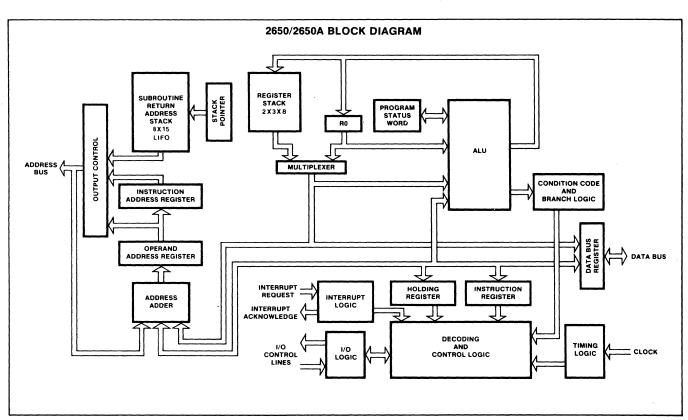

| 9-1  | 2650/2650A Block Diagram                          | 9-4  |

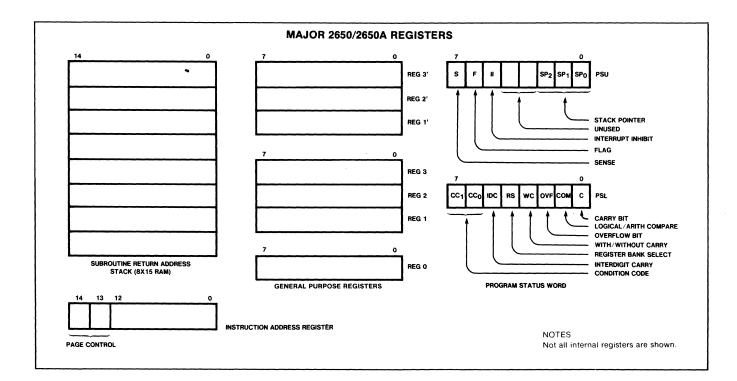

| 9-2  | Major 2650/2650A Registers                        | 9-4  |

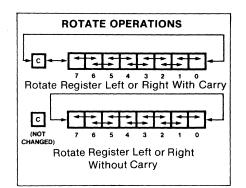

| 9-3  | Rotate Operations                                 | 9-8  |

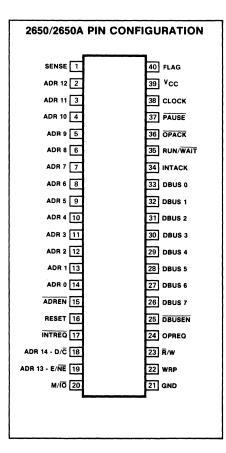

| 9-4  | 2650/2650A Pin Configuration                      | 9-12 |

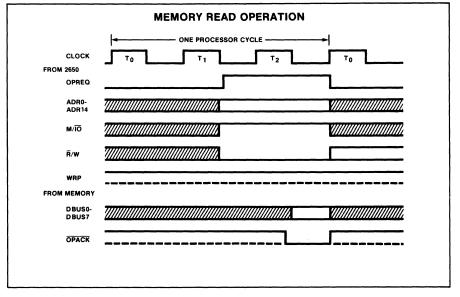

| 9-5  | Memory Read Operation                             | 9-18 |

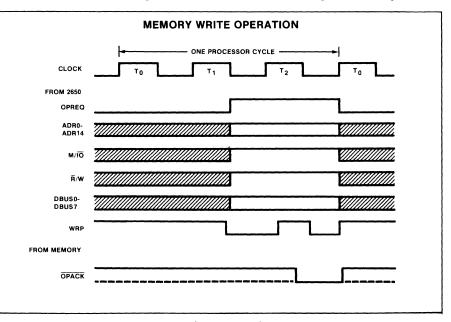

| 9-6  | Memory Write Operation                            | 9-19 |

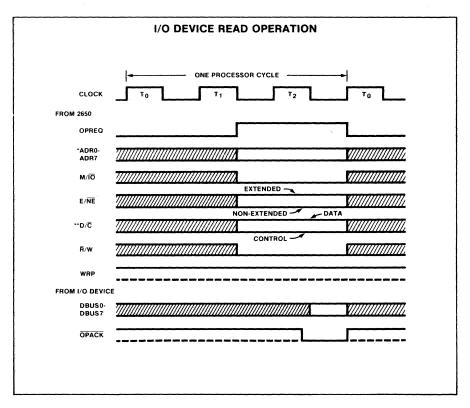

| 9-7  | I/O Device Read Operation                         | 9-20 |

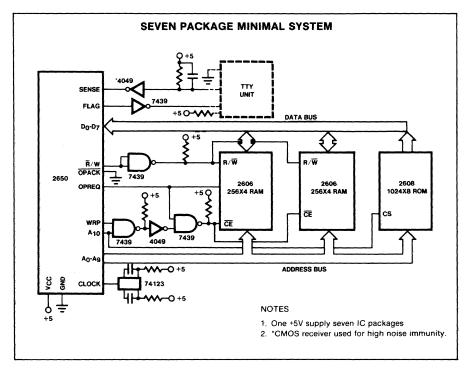

| 9-8  | Seven Package Minimal System                      | 9-20 |

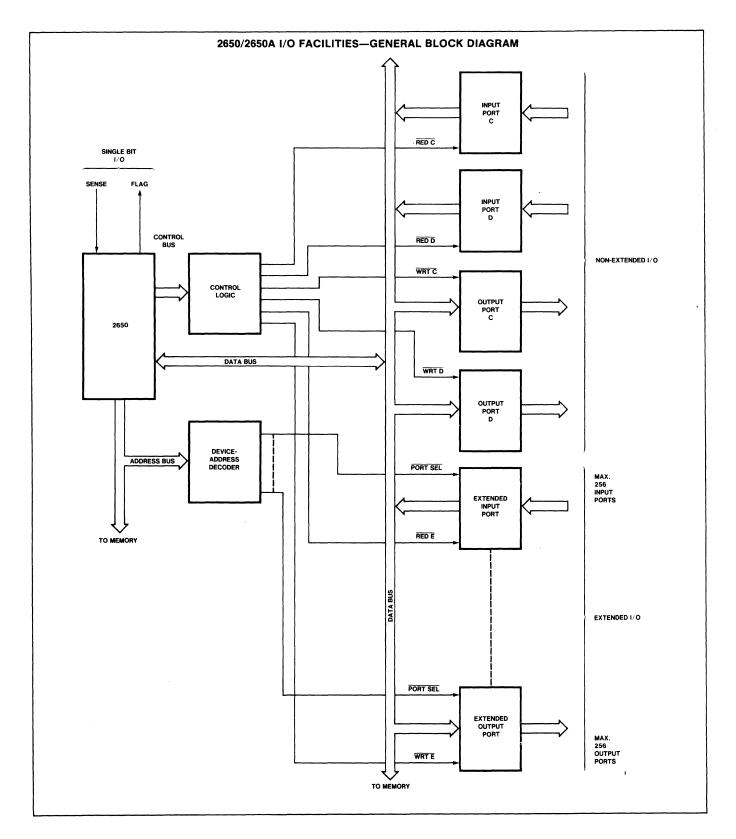

| 9-9  | 2650/2650A I/O Facilities - General Block Diagram | 9-23 |

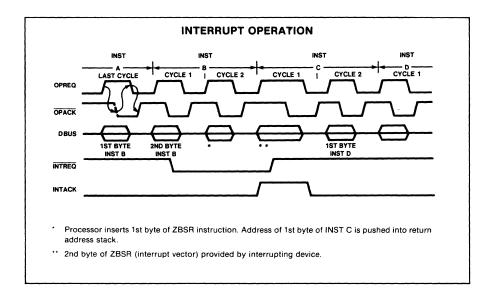

| 9-10 | Interrupt Operation                               | 9-25 |

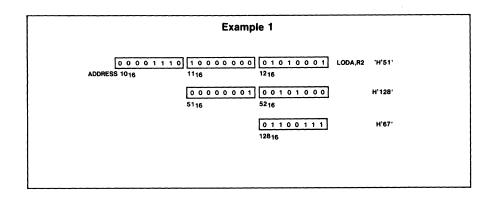

| 9-11 | Example 1 - Indirect Addressing                   | 9-31 |

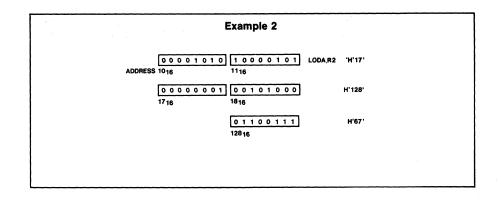

| 9-12 | Example 2 - Indirect Addressing                   | 9-32 |

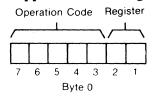

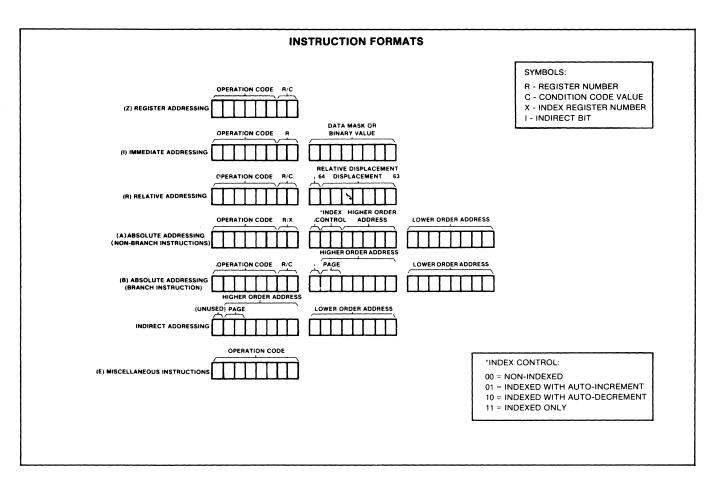

| 9-13 | Instruction Formats                               | 9-33 |

|      |                                                   |      |

ę

### **1. MICROCOMPUTER BASICS**

This chapter introduces certain basic computer concepts. It provides background information and definitions which will be useful in later chapters of this manual. Those already familiar with computers may skip this material.

Before we begin, note that we are using two words: <u>microprocessor</u> and <u>micro-computer</u>. The microprocessor is a device which performs arithmetic, control, and logical operations. The microcomputer, in turn, is a collection of demovices that includes a microprocessor, memory, and associated interface circuits to communicate with the "outside" world. Because it has its own micro-processor (the Signetics 2650), memory, latches, counters, buffers, power supriply, an operator keyboard and display panel, and a cassette input/output inmitterface, the INSTRUCTOR 50 is a complete and fully operational microcomputer system housed in one single package.

#### A MICRO DEFINED

Since the microprocessor is a miniaturized, coventional digital computer in integrated circuit (IC) form, a good place to start is with computers. Simply put, A computer is a device capable of automatically carrying out a sequence of operations on data expressed in descrete (digital) or continuous (analog) form. Its purpose is to solve a problem or class of problems; it may be one of control, analysis, or a combination of the two. In digital computers, numbers are represented by the presence of voltage levels or pulses on given lines. A single line defines one bit. A bit is the smallest unit of information in a binary system of notation. It is the choice between two possible states, usually designated one (1) and zero (0). A group of lines considered together is called a "word"; a word may represent a computational quantity (operand) or it may be an instruction specifying how the machine is to operate on computational quantities.

and and an and

#### Word/Byte/Nibble

These terms are often misused in describing microprocessor data. For a specific microprocessor, a word is the number of bits associated with the instruction or data length. This can be 4, 8, 16 bits, etc., depending on the machine. A byte commonly refers to an 8-bit word; a byte can be manipulated by a 4, 8, or 16-bit microprocessor. For example, instructions are often provided to deal with byte data in 4 or 16-bit processors. This is called byte handling, and is independent of the natural word size of the machine.

"你你这边你们还没有你的你,你……"

A nibble is 4 bits, and it is rather humorous to consider that it takes two nibbles to make a byte. Nibble (or 4 bit) control can be found on many 8-bit word machines as well as on some 16-bit machines. Four-bit operations are usually associated with Hexadecimal (Hex) or Binary Coded Decimal (BCD) operations. Applications that have a man/machine interface, such as a control keyboard or a numeric display, are good candidates for nibble control.

- edana (sertosbared deluya) est os yau 1 (...) alter decidado ....) reseva

to bette

#### **Binary Notation**

经差销地支持

One of the problems in communicating with a computer is language. How does an electronic instrument handle and manipulate numbers? The answer is suggested by the nature of all electrical devices: a light bulb is either on or off, a switch is either open or closed, a magnet has a field in one direction or the opposite. For the purpose of understanding computer language, one can think of the "on" condition as being equal to 1 and the "off" state as 0. So the computer, which is made up of literally millions of electronic components, has two numbers it can work with. These numbers, 1 and 0, form all the elements needed in the binary system of notation.

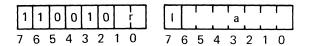

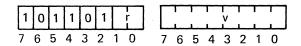

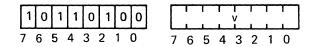

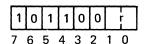

In our more familiar decimal system, the right-hand column of a figure counts numbers up to 9; the column to the left of that registers the number of 10s; the column next to the left registers hundreds--then thousands, millions, and so on. In binary notation, the columns starting at the right register powers of 2 instead of 10. Take the binary number 10110, with successive powers of 2 noted above each column:

|           | 16 | 8 | 4 | 2 | 1 |

|-----------|----|---|---|---|---|

| A TARA ST | 1  | 0 | 1 | 1 | 0 |

Adding together the powers of 2 turned "on" in this binary number--16, 4 and 2-we arrive at its decimal equivalent--22. The first eight decimal numbers translated into the binary system look like this:

| - 400 (J. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | = | 1   | 5 | =  | 101  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|----|------|

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | = | 10  | 6 | =  | 110  |

| - 141 + 5 (m) - 1 (m) 1 <b>3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | = | 11  | 7 | =  | 111  |

| harablana sa4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | = | 100 | 8 | =. | 1000 |

| $(1-\varepsilon^2) = S^{(1)} + (1-\varepsilon^2) - S^{(2)} + (1-\varepsilon$ |   |     |   |    |      |

| Constant of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |     |   |    |      |

#### **Hexadecimal Notation**

To deal with large binary numbers, certain simplifications are extremely helpful. To this end, hexadecimal notation is often used. The term "hexadecimal", or hex for short, refers to a shorthand method of expressing a group of four consecutive binary bits by a single digit. Valid digits range from 0 through F, where F represents the highest decimal value (15). See Table 1.1.

Two hexadecimal digits can be used to specify a byte. Hexadecimal notation is very convenient for microprocessors since it gives good counting densities and works very well with the multiples-of-four binary words usually encountered in a microprocessor.

医静脉 美国大学 网络

To understand hex notation, take a decimal number like  $107_{10}$ . In binary notation, this becomes  $1101011_2$ . Breaking this number into 4-bit nibbles (half-bytes), you get  $0110_2$  and  $1011_2$ . The first and most-significant nibble is equal to  $6_{16}$ , while the second and least-significant nibble is equal to  $B_{16}$ . Thus, in hexadecimal notation,  $107_{10}$  becomes  $6B_{16}$ . One way to distinguish hexadecimal numbers from numbers written in other number systems (e.g., decimal, octal, etc.) is to enclose the hex number in single

| Decimal | <u>Hexadecimal</u> | <u>Binary</u> |

|---------|--------------------|---------------|

| 0       | 0                  | 0000          |

| 1       | 1                  | 0001          |

| 2       | 2                  | 0010          |

| 3       | 3                  | 0011          |

| 4       | 4                  | 0100          |

| 5       | 5                  | 0101          |

| 6       | 6                  | 0110          |

| 7       | 7                  | 0111          |

| 8       | 8                  | 1000          |

| 9       | 9                  | 1001          |

| 10      | A                  | 1010          |

| 11      | В                  | 1011          |

| 12      | С                  | 1100          |

| 13      | D                  | 1101          |

| 14      | E                  | 1110          |

| 15      | F                  | 1111          |

Table 1.1: Relationship among decimal, hexadecimal, and binary systems.

quotation marks and precede it by the letter H. Hence, in hex notation  $6B_{16}$  would appear as H'6B'. To convert from decimal to hexadecimal, or vice versa, you must first convert the number into binary and then into hexadecimal as previously illustrated.

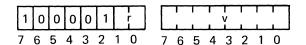

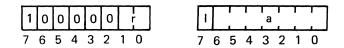

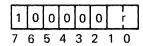

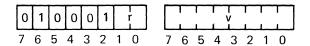

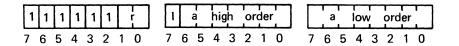

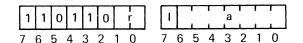

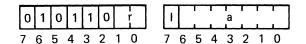

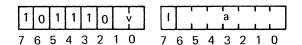

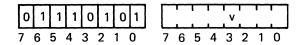

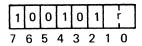

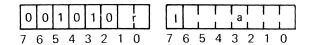

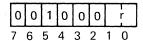

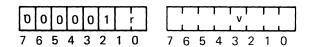

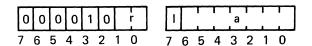

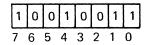

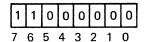

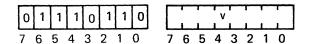

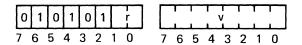

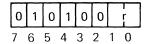

The INSTRUCTOR 50 uses the hexadecimal number system for entering values. Since the INSTRUCTOR 50 uses 8-bit bytes, two hexadecimal digits can be used to specify a byte. The smallest hexadecimal number is H'00' (000000002) and the largest is H'FF' (111111112). The INSTRUCTOR 50 still reads only binary numbers; hexadecimal is the user's shorthand, not the microcomputers.

#### Architecture

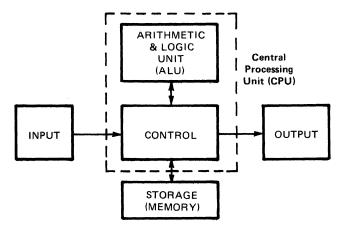

A microcomputer looks, architecturally, like any other computer (Figure 1.1). What distinguishes a micro from other computers is the intrinsic power inside each of the five functional boxes. What large-scale computers used to do, minis now handle. Similarly, micros have begun to supplant minicomputers in many applications. Advances in semiconductor technology have made this possible.

The four basic elements of all programmable computers emerge:

• <u>Memory</u> -- A storage unit. In modern computers, memories are implemented with semiconductor or magnetic core systems. Memories can be read only (ROM), for program or data constant storage, or read/write random access (RAM) for program, operand or temporary storage. Data is usually stored in binary notation. The memory is composed of storage space for a large number of words, with each storage space identified by a unique address. The word stored at a given address might be either computational data (operands) or an instruction (such as add, read from memory, etc.). • <u>Arithmetic & Logic Unit (ALU)</u> -- Performs the arithmetic and/or logical operations on operands or provides partial results within the computer. The simplest ALU consists of a parallel adder and an accumulator. The adder adds (or performs similar logical operations, e.g., OR) two inputs, A and B, and produces the output. The accumulator holds intermediate results of a computation or numbers for a pending computation. The accumulator serves as a temporary storage device.

• <u>Control unit</u> -- Referred to as the brain of any computer because it coordinates all units of the computer in a timed, logical sequence. The control unit generates clock pulses to control and maintain the proper sequence of operations within the microprocessor. It also responds to external signals such as an interrupt request. In fixed-instruction computers, this unit receives instructions from the program memory. These instructions are in sequences, called programs. The control unit is closely synchronized to the memory cycle speed, and the execution time of each fixed instruction is often a multiple of the memory speed.

• <u>Input/Output</u> -- The means by which the computer communicates with a wide variety of devices, referred to as peripherals. They include audio cassette recorders, switches, indicator lamps, teletypewriters, CRT terminals, paper tape units, line printers, A/D or D/A converters, card readers and punches, communication modems, etc. The I/O lines can be connected to intermediate storage devices for use with mass memories, including magnetic discs and large-scale RAM systems.

#### **Program Counter (Jumps, Subroutines, and the Stack)**

The instructions that make up a program are stored in the system's memory. The central processor references the contents of memory in order to determine what action is appropriate. This means that the processor must know which location contains the next instruction.

Each of the locations in memory is numbered to distinguish it from all other locations in memory. The number which identifies a memory location is called its Address.

Figure 1.1

The processor maintains a counter which contains the address of the next program instruction. This is called a <u>Program Counter (PC)</u>. The processor updates the program counter by adding to the counter each time it fetches an instruction, so that the program counter is always current (pointing to the next instruction). If an instruction takes several words in memory, the PC is incremented by the proper number so that it is always pointing to the first word of the next instruction.

The programmer therefore stores his instructions in numerically adjacent addresses, so that the lower addresses contain the first instructions to be executed and the higher addresses contain later instructions. The only time the programmer may violate this sequential rule is when an instruction in one section of memory is a jump instruction to another section of memory.

A jump instruction contains the address of the instruction which is to follow it. The next instruction may be stored in any memory location, as long as the programmed jump specifies the correct address. During execution of a jump instruction, the processor replaces the contents of its program counter with the address embodied in the jump. Thus, the logical continuity of the program is maintained.

A special kind of program jump occurs when the stored program <u>calls</u> a subroutine. In this kind of jump, the processor is required to "remember" the contents of the program counter at the time that the jump occurs. This enables the processor to resume execution of the main program when it is finished with the last instruction of the subroutine.

A <u>subroutine</u> is a program within a program. Usually it is a general-purpose set of instructions that must be executed repeatedly in the course of a main program. Routines which calculate the square, the sine, or the logarithm of a program variable are good examples of functions often written as subroutines. Other examples might be programs designed for inputting or outputting data to a particular peripheral device.

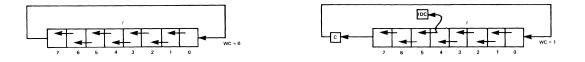

The processor has a special way of handling subroutines, in order to insure an orderly return to the main program. When the processor receives a call instruction, it increments the Program Counter and stores the counter's contents in a reserved memory area known as the <u>stack</u>. The stack thus saves the address of the instruction to be executed after the subroutine is completed. Then the processor loads the address specified in the call into its Program Counter. The next instruction fetched will therefore be the first step of the subroutine.

The last instruction in any subroutine is a <u>return</u>. Such an instruction need specify no address. When the processor fetches a return instruction, it simply replaces the current contents of the Program Counter with the address on the top of the stack. This causes the processor to resume execution of the calling program at the point immediately following the original call instruction.

Subroutines are often <u>nested</u>; that is, one subroutine will sometimes call a second subroutine. The second may call a third, and so on. This is perfectly acceptable, as long as the processor has enough stack capacity to store the necessary return addresses, and the logical provision for doing so. In other words, the maximum depth of nesting is determined by the depth of the stack itself. If the stack has space for storing three return addresses, then three levels of subroutines may be accommodated.

Processors have different ways of maintaining stacks. For example, some, like the Signetics 2650, have facilities for the storage and return addresses built into the processor itself. Other processors use a reserved area of external memory as the stack and simply maintain a <u>pointer</u> register which contains the address of the most recent stack entry. The external stack allows virtually unlimited subroutine nesting.

#### **Instruction Register and Decoder**

Each operation that the processor can perform is identified by a unique byte of data known as an <u>Instruction Code</u> or <u>Operation Code</u>. An eight-bit word used as an instruction code can distinguish between 256 alternative actions, more that adequate for most processors.

The processor fetches an instruction in two distinct operations. First, the processor transmits the address in its Program Counter to the memory. Then the memory returns tha addressed byte to the processor. The CPU stores this instruction byte in a register known as the <u>Instruction Register</u>, and uses it to direct activities during the remainder of the instruction execution.

An eight-bit instruction code is often sufficient to specify a particular processing action. There are times, however, when execution of the instruction requires more information than eight bits can convey.

One example of this is when the instruction references a memory location. The basic instruction code identifies the operation to be performed, but cannot specify the operand address as well. In a case like this, a twoor three-byte instruction must be used. Successive instruction bytes are stored in sequentially adjacent memory locations, and the processor performs two or three fetches in succession to obtain the full instruction. The first byte retrieved from memory is placed in the processor's instruction register, and subsequent bytes are placed in temporary storage; the processor then proceeds with the execution phase. Such an instruction is referred to as variable length.

#### Address Register(s)

A CPU may use a register pair to hold the address of a memory location that is to be accessed for data. If the address register is programmable (i.e., if there are instructions that allow the programmer to alter the contents of the register), the program can "build" an address in the address register prior to executing a memory reference instruction (i.e., an instruction that reads data from memory, writes data to memory or operates on data stored in memory).

#### Addressing Modes

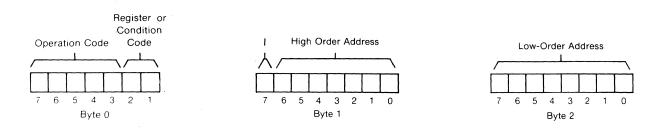

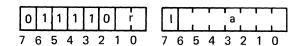

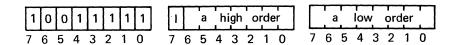

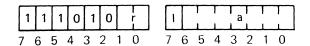

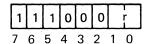

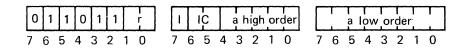

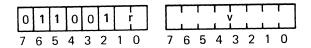

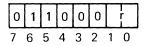

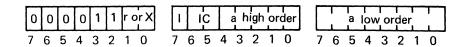

An instruction word must convey the operation to be performed (operation code) and the address of the memory location or registers containing the data on which the operation is to be performed (operand). An n-bit instruction may be divided into three basic parts: 1) an operations code, 2) an address mode, and 3) an operand address. The number of bits in each of these parts varies from microprocessor to microprocessor.

The instruction length depends on the machine and the operation being performed. An 8-bit instruction format would allow only  $2^8 = 256$  possible combinations of operations and addresses. This is obviously inadequate if a reasonable-size memory is to be accessed. For this reason 2 and 3-byte instructions are frequently used for memory access. Such an instruction is 16 or 24 bits long. In most cases, one byte is used to represent the operations code and address mode portions of an instruction. The number of bits used for each of these and their relative locations within the byte vary from processor to pro-The address mode and operand part of the instruction combine to indicessor. cate the location in which the operand is stored. There are numerous modes of addressing the operand. The most important for microprocessors include direct (or absolute), indirect, relative, indexed, and immediate addressing. The address mode portion of the instruction specifies how the address is to be interpreted. These addressing modes are defined as follows:

- <u>Direct Addressing</u>. With direct addressing, the address of the operand is specified directly in the instruction. This is a common form of addressing used in microcomputers. Direct addressing usually requires multiword instructions in 4 or 8-bit microprocessors.

- <u>Indirect Addressing</u>. In this mode, the instruction provides the address at which the address of the operand is to be found. In microprocessors, a form of addressing called <u>register</u> indirect addressing is commonly used. The address is stored in one or more registers within the CPU. In most cases, this architecture allows any location in memory to be addressed with a single-word instruction. Indirect addressing allows modification of the operand address during execution of the program.

- <u>Relative Addressing</u>. In relative addressing, the address is specified by its relation to the program counter. In this mode the address specified in the instruction is added to the number in the program counter to obtain the address of the operand. For example, if the address in the instruction is 11 and the program counter contains 124, then the address of the operand will be 11 + 124 = 135. The use of relative addressing simplifies the transfer of programs to different areas of memory.

Microcomputer memory is frequently structured into pages. A page may consist of 256 words of memory and is frequently located on a single IC. A page structure divides the memory into small blocks. The use of paging reduces the necessity for multiword memory reference instructions. In conjunction with a memory page structure, a form of relative addressing called page relative addressing is frequently used. In page relative addressing, an operand address given in the instruction is interpreted as a location on the same page of memory addressed by the program counter. In page-0 relative addressing, the operand address refers to a location on page 0 of the memory, regardless of the program counter contents.

• Indexed Addressing. This mode is similar to relative addressing. The address specified in the instruction, however, is relative to a prespecified register other than the program counter. This register is called the index. The address given in the instruction is added to the contents of the index register to determine the address of the operand. Indexed addressing is valuable in programs involving tables or arrays of numbers. The address of the first element of the table may be stored in the index register, and all other elements in the table may be addressed in relation to the first element.

• <u>Immediate Addressing</u>. In this mode, the operand is given in the instruction itself. In a microprocessor with only an 8-bit word length this may not be possible. In this case, the memory location immediately following the instruction is often used to store the immediate data.

The Signetics 2650 microprocessor can develop addresses in eight ways:

- Register addressing.

- Immediate addressing.

- Relative addressing.

- Relative, indirect addressing.

- Absolute addressing.

- Absolute, indirect addressing.

- Absolute, indexed addressing.

- Absolute, indirect, indexed addressing.

However, of these eight addressing modes, only four of them are basic. The others are variations due to indexing and indirection. Chapter 9 describes how effective addresses are developed by the 2650 microprocessor.

#### Extended/Non-Extended I/O

One of the major tasks performed by the CPU portion of a microcomputer is the transfer of data between the CPU and an I/O device. This, of course, is the method used by the computer to communicate with the outside world; e.g., reading data into the processor from a keyboard, cassette tape unit, paper tape reader, etc. or writing data into a CRT display, paper tape punch, cassette recorder, etc.

In most microprocessor-based system, there is essentially only one way that these I/O data transfers take place; i.e., by placing the "address" or identification code of a specific I/O device on the address bus and the data to be written on the data bus. (If its a read operation, the I/O device will place the data to be read on the data bus.) With this arrangement, some mechanism must be provided to examine the address bus during an I/O transfer to determine which specific I/O device is being accessed. This operation requires some type of decoder which can look at up to 8-bits of address data and from this information, generate a signal on a single line which will open a path from the data bus to the individual I/O device specified by the data on the address bus.

This can be a rather complex task and, in fact, is often implemented by a special LSI chip designated specifically for this purpose. In addition to the hardware required, this approach to I/O data transfer also consumes memory space for storing this I/O address. For example, the 2650 requires two eightbit memory words to implement this type of I/O transfer. One word specifies the operation (Read or Write) and the other specifies the I/O device. In the 2650, this is referred to as an Extended I/O operation.

In addition to the Extended Mode of parallel I/O data transfer, the 2650 can also operate in what is referred to as a <u>Non-Extended</u> mode. In this mode, two different I/O devices can be addressed by a single pin called Data/Control (D/C). This is an output from the 2650 that responds to a specific instruction calling for a Non-Extended I/O operation. This pin and the memory mapped I/O (see Chapter 6) are the only two pins that need be decoded to use this simple form of I/O. When the D/C output is high, it connects the "D" output device to the data bus; when it is low, it connects the "C" output device. Thus, simple SSI gates are the only interface required to enable the 2650 to communicate with I/O devices in the Non-Extended Mode.

In addition to saving hardware, the Non-Extended I/O mode also saves software (or program memory). Each Non-Extended instruction is a single word instruction which contains enough information to specify two different operations (Read or Write) to two different ports (D or C).

One additional benefit in having both Extended and Non-Extended I/O modes is the fact that one can "mix" modes in any given system. For example, assume that a typical system has 20 I/O channels, two of which are used substantially more that the other eighteen. In this system, one could specify the two frequently used channels as Non-Extended channels and address these with singlebyte instructions. The other, less frequently used channels would be addressed with Extended instructions.

Another example would be in those situations where a single I/O device has two separate ports for information flow. Quite often, one of these ports is used to handle Control or status information; for example, "start a motor" or "start the timer," etc. The other channel is used for the actual data transfer. In this case, the basic I/O device can be addressed in the Extended Mode with a two-byte instruction and the actual information transferred in a Non-Extended Mode with a single-byte instruction. (In fact, the Data/Control aspects of this dual-port situation is what prompted the nomenclature for the D/C pin.)

#### SOFTWARE

Software is a term used to describe the programs that make a computer do a specific task. In fact, when used in the context of computers, the word software can be interchanged with the word program. In general, a program is a series of sequential steps (instructions) that accomplish an objective. Even though the specific set of instructions it can use is fixed by its design, a computer is general purpose because it can execute a list of these instructions (a program) to perform some functions, execute another list of instructions to perform some other function, and so on.

In discussions about software and programming, a great deal is often said about programming in some language or another. This is because the way we command the machine is very much like the way we communicate in a written language. We have rules about how we start and end sentences and paragraphs and how we spell words. The way we communicate with a computer is through a programming language, which also has rules of spelling and punctuation, but these rules are much more strictly enforced. If you misspell a few words, your reader will probably understand you anyway. A computer language is not that forgiving and will not produce the desired result if its rules are broken.

#### Machine Language

There are a number of levels of programming languages. The most basic level is that of the actual machine language. Each instruction is uniquely defined by a binary code (pattern) of ones and zeros. The central processing unit (CPU) examines each instruction code and performs the exact sequence of events to produce the operation defined by that instruction. After an operation has been performed and a problem solved, the computer must then reverse its opening procedure. It must retranslate its machine language and display the answer in a form the person who presented the problem can understand.

The use of machine language is a perfectly reasonable way to program when the application is not too complex and the effort is on a low budget. The IN-STRUCTOR 50 is a machine-language microcomputer; making it support assembly language would have considerably raised its cost. The main advantages of machine language programming are that it can be completed without the aid of another program, and it allows the programmer to keep track of and control every detail of the machine operation.

#### Assembly Language

To make programming easier, assemblers have been developed. An assembler is a computer program that accepts coded instructions or mnemonics that are more meaningful to use and translates them into binary machine code for execution by a computer. The mnemonics used for each instruction are much easier to remember, and they make a listing of the program much easier to read. Assembly language programming allows the programmer to retain complete control over the important details of the computer operation, but takes care of all the drudgery of the binary coding, address calculations, and the like.

#### **Higher-Level Languages**

A third category of software is the higher-level languages, such as BASIC and FORTRAN, which come the closest to natural human languages. They are problemoriented and contain familiar words and expressions; however, they have a very strictly defined structure and syntax. There are two types of support programs associated with higher-level languages: compilers and interpreters. Both types take the higher-level language program the programmer writes and turn it into machine language the computer can use.

#### Other Software

Other software associated with microprocessors include monitor programs, debug programs, simulators, editors, I/O handlers, diagnostic programs, and loaders. Brief definitions of these programs are provided in the glossary (Chapter 13).

### 2. GETTING STARTED

#### Introduction

Welcome aboard the INSTRUCTOR 50--a unique and powerful training tool designed to introduce you to the world of microcomputers in the shortest possible time.

INSTRUCTOR 50 is for computer hobbyists, students, engineers or anyone who wants to learn how to use a microcomputer the easy way, without having to face the drudgery of a long and tedious training program.

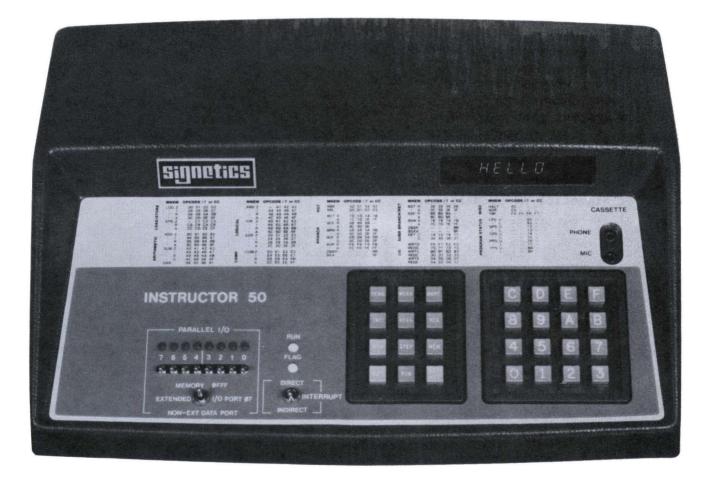

INSTRUCTOR 50 is a stand-alone microcomputer based on the Signetics 2650 microprocessor. It includes everything that you need to write, run, and debug machine-language programs. A 12-key Function Control Keyboard and a 16-key Hexadecimal Keyboard are used to enter data and perform various system functions associated with the INSTRUCTOR 50. The INSTRUCTOR 50 User System Executive (USE) monitor program guides you in the use of the system by displaying prompting messages and responses on an eight-digit LED display. All facilities required for program development are built into INSTRUCTOR 50 -- you don't need anything else to start.

Before getting into the details of what makes the INSTRUCTOR 50 tick, let's first take a short shakedown cruise and write a few simple programs. Detailed information on each 2650 instruction is provided in Chapter 9.

#### **Power On and Initial Display**

To apply power to the INSTRUCTOR 50, connect the power cord into the rear panel receptacle, and insert the power pack into any standard 115 VAC domestic wall socket. The INSTRUCTOR 50 does not have a power ON/OFF switch. The initial display is the message HELLO, indicating that the INSTRUCTOR 50 is in the monitor mode and ready for use. If the HELLO message does not appear, depress the MON key to initialize the INSTRUCTOR 50. Unplug the power pack to turn the INSTRUCTOR 50 off.

#### **Operating Modes**

The INSTRUCTOR 50 has two basic modes of operation, the MONITOR mode and the EXECUTION mode. The MONITOR mode is entered automatically on power up or by depressing the MON key on the function control keyboard. The monitor responds by displaying HELLO. While in the MONITOR mode, you may:

- Enter and alter a program.

- Read in a previously saved program from audio cassette tape.

- Display and alter the contents of the microcomputer's general-purpose working registers and/or Program Status Word (PSW).

- Examine and alter the contents of memory locations.

- Examine and alter the contents of the Program Counter.

- Specify and examine a program breakpoint.

- Step through a program one instruction at a time.

- Save a program on cassette tape.

The EXECUTION mode is entered by depressing the RUN key, the STEP key, or the RESET (RST) key on the function control keyboard. Depressing the RUN key terminates the MONITOR mode and causes program execution to begin at the address specified in the Program Counter. Depressing the STEP key causes the IN-STRUCTOR 50 to execute a single instruction and return to the MONITOR mode. When the RST key is depressed, current INSTRUCTOR 50 activity is terminated, and the processor begins program execution at address zero or, in hex notation, H'0000'.

#### Keying in and Entering Values

Address and data parameters are entered into the INSTRUCTOR 50 via the hexadecimal keyboard using the hex notation described in Chapter 1. When entering an address, you may enter as many as four hex digits starting with the mostsignificant digit of the address. Leading zeroes need not be entered; if less that four digits are entered, the leading digits are automatically zeroed. Data values consist of one or two hex digits, with the most-significant digit entered first. If only one digit is entered, the most-significant digit is automatically zeroed.

#### **Correcting Entry Errors**

The numbers keyed in appear in the address or data display field and can be edited prior to depression of a funciton key by simply keying in the correct characters. The display shifts to the left each time a new character is entered, and characters shifted out of the field are disregarded. Only the last digits entered are retained, so that an error in entry can be corrected by entering the correct data.\*

For example, if you were entering an address and you depressed 121 instead of the correct value of 120, the display would read:

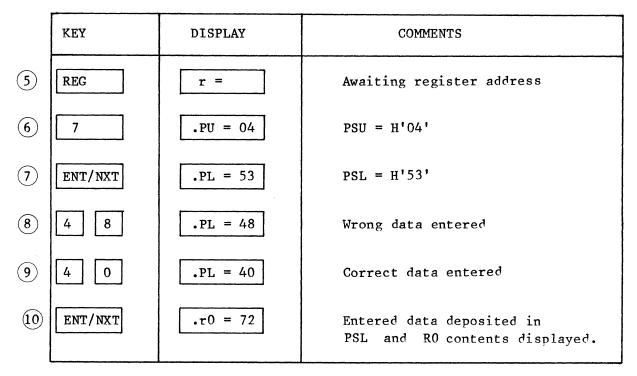

.Ad. = 121