# Safety Manual for TMS570LC4x Hercules ARM Safety MCUs

# **User's Guide**

Literature Number: SPNU540A May 2014—Revised September 2016

# **Contents**

| 1 | Introduc | ction                                                                                             | . 8 |

|---|----------|---------------------------------------------------------------------------------------------------|-----|

| 2 | Hercule  | s TMS570LC4x Product Overview                                                                     | 10  |

|   | 2.1      | Targeted Applications                                                                             | 11  |

|   | 2.2      | Product Safety Constraints                                                                        | 12  |

| 3 | Hercule  | s Development Process for Management of Systematic Faults                                         | 13  |

|   | 3.1      | TI Standard MCU Automotive Development Process                                                    | 14  |

|   | 3.2      | TI MCU Automotive Legacy IEC 61508 Development Process                                            | 15  |

|   | 3.3      | Yogitech fRMethodology Development Process                                                        | 15  |

|   | 3.4      | Hercules Enhanced Safety Development Process                                                      | 15  |

| 4 | Hercule  | s Product Architecture for Management of Random Faults                                            | 18  |

|   | 4.1      | Safe Island Philosophy and Architecture Partition to Support Safety Analysis (FMEA/FMEDA)         | 18  |

|   | 4.2      | Identification of Parts/Elements                                                                  | 19  |

|   | 4.3      | Management of Family Variants                                                                     | 20  |

|   | 4.4      | Operating States                                                                                  | 20  |

|   | 4.5      | Management of Errors                                                                              | 22  |

| 5 | System   | Integrator Recommendations                                                                        | 23  |

|   | 5.1      | System Integrator Activities                                                                      | 23  |

|   | 5.2      | Hints for Performing Dependent/Common Cause Failure Analysis Including the Hercules MCU           | 25  |

|   | 5.3      | Hints for Improving Independence of Function/Co-Existence of Function When Using the Hercules MCU | 25  |

|   | 5.4      | Support for System Integrator Activities                                                          | 25  |

| 6 | Brief De | escription of Elements                                                                            | 26  |

|   | 6.1      | Power Supply                                                                                      | 26  |

|   | 6.2      | Power Management Module (PMM)                                                                     | 26  |

|   | 6.3      | Clocks                                                                                            | 27  |

|   | 6.4      | Reset                                                                                             | 27  |

|   | 6.5      | System Control Module                                                                             | 28  |

|   | 6.6      | Error Signaling Module (ESM)                                                                      | 29  |

|   | 6.7      | CPU Subsystem                                                                                     | 29  |

|   | 6.8      | Primary Embedded Flash                                                                            | 31  |

|   | 6.9      | Flash EEPROM Emulation (FEE)                                                                      | 32  |

|   | 6.10     | Primary Embedded SRAM                                                                             |     |

|   | 6.11     | CPU Interconnect Subsystem                                                                        | 34  |

|   | 6.12     | Peripheral Interconnect Subsystem                                                                 |     |

|   | 6.13     | Peripheral Central Resource 1 (PCR1)                                                              |     |

|   | 6.14     | Peripheral Central Resource 2 (PCR2)                                                              |     |

|   | 6.15     | Peripheral Central Resource 3 (PCR3)                                                              |     |

|   | 6.16     | EFuse Static Configuration                                                                        |     |

|   | 6.17     | OTP Static Configuration                                                                          |     |

|   | 6.18     | I/O Multiplexing Module (IOMM)                                                                    |     |

|   | 6.19     | Vectored Interrupt Module (VIM)                                                                   |     |

|   | 6.20     | Real Time Interrupt (RTI)                                                                         | 39  |

#### www.ti.com

|   | 6.21     | Direct Memory Access (DMA)                                 | 40 |

|---|----------|------------------------------------------------------------|----|

|   | 6.22     | High-End Timer (N2HET), HET Transfer Unit (HTU)            | 40 |

|   | 6.23     | Multi-Buffered Analog-to-Digital Converter (MibADC)        | 42 |

|   | 6.24     | Enhanced Pulse Width Modulators (ePWM)                     | 42 |

|   | 6.25     | Enhanced Capture (eCAP)                                    | 43 |

|   | 6.26     | Enhanced Quadrature Encoder Pulse (eQEP)                   | 44 |

|   | 6.27     | Multi Buffered Serial Peripheral Interface (MibSPI)        | 44 |

|   | 6.28     | Inter-Integrated Circuit (I2C)                             | 45 |

|   | 6.29     | Serial Communication Interface (SCI)                       | 46 |

|   | 6.30     | Local Interconnect Network (LIN)                           | 46 |

|   | 6.31     | Controller Area Network (DCAN)                             | 47 |

|   | 6.32     | FlexRay, FlexRay Transfer Unit (FTU)                       | 48 |

|   | 6.33     | General-Purpose Input/Output (GIO)                         | 49 |

|   | 6.34     | Ethernet                                                   | 50 |

|   | 6.35     | External Memory Interface (EMIF)                           | 50 |

|   | 6.36     | JTAG Debug, Trace, Calibration, and Test Access            | 51 |

|   | 6.37     | Cortex-R5F Central Processing Unit (CPU) Debug and Trace   | 51 |

|   | 6.38     | Data Modification Module (DMM)                             | 52 |

|   | 6.39     | RAM Trace Port Interface (RTP)                             |    |

|   | 6.40     | Parameter Overlay Module (POM)                             |    |

|   | 6.41     | Error Profiling Controller (EPC)                           |    |

|   | 6.42     | Temperature Sensor                                         | 53 |

| 7 | Brief De | escription of Diagnostics                                  |    |

|   | 7.1      | 1002 Software Voting Using Secondary Free Running Counter  | 54 |

|   | 7.2      | Bit Error Detection                                        |    |

|   | 7.3      | Bit Multiplexing in FEE Memory Array                       |    |

|   | 7.4      | Bit Multiplexing in Flash Memory Array                     |    |

|   | 7.5      | Bit Multiplexing in Primary SRAM Memory Array              |    |

|   | 7.6      | Bit Multiplexing in Peripheral SRAM Memory Array           |    |

|   | 7.7      | CPU Illegal Operation and Instruction Trapping             |    |

|   | 7.8      | Logic Built In Self-Test (LBIST)                           |    |

|   | 7.9      | Logic Built In Self-Test (LBIST) Auto-Coverage             |    |

|   | 7.10     | CPU Lockstep Compare                                       |    |

|   | 7.11     | VIM Lockstep Compare                                       |    |

|   | 7.12     | Lockstep Comparator Self-Test                              |    |

|   | 7.13     | CPU Online Profiling Using the Performance Monitoring Unit |    |

|   | 7.14     | CPU Memory Protection Unit (MPU)                           |    |

|   | 7.15     | CRC Auto-coverage                                          |    |

|   | 7.16     | CRC in Message                                             |    |

|   | 7.17     | DCAN Acknowledge Error Detection                           |    |

|   | 7.18     | DCAN Form Error Detection                                  |    |

|   | 7.19     | DCAN Stuff Error Detection                                 |    |

|   | 7.20     | DCAN Protocol CRC in Message.                              |    |

|   | 7.21     | Disable the DMM Pin Interface                              |    |

|   | 7.22     | Disable the RTP Pin Interface                              |    |

|   | 7.23     | Dual Clock Comparator (DCC)                                |    |

|   | 7.24     | Autoload Self-Test                                         |    |

|   | 7.25     | Efuse Autoload Self-Test Auto-Coverage                     |    |

|   | 7.26     | EFuse ECC                                                  | 58 |

Copyright © 2014–2016, Texas Instruments Incorporated

| 7.27         | EFuse ECC Logic Self-Test                                                        | 58 |

|--------------|----------------------------------------------------------------------------------|----|

| 7.28         | eQEP Quadrature Watchdog                                                         | 58 |

| 7.29         | eQEP Software Test of Quadrature Watchdog Functionality                          | 59 |

| 7.30         | Error Trapping - IOMM                                                            | 59 |

| 7.31         | Error Trapping (including Peripheral Slave Error Trapping) - L2/L3 Interconnect  | 59 |

| 7.32         | Ethernet Alignment Error Detection                                               |    |

| 7.33         | Ethernet Physical Layer Fault                                                    | 59 |

| 7.34         | External Monitoring of Warm Reset (nRST)                                         | 59 |

| 7.35         | External Monitoring via ECLK                                                     |    |

| 7.36         | External Voltage Supervisor                                                      | 60 |

| 7.37         | External Watchdog                                                                |    |

| 7.38         | FEE Contents Check by Hardware CRC                                               | 60 |

| 7.39         | FEE Data ECC                                                                     |    |

| 7.40         | FEE Sector Protection                                                            | 60 |

| 7.41         | Flash Address and Control Bus Parity                                             | 61 |

| 7.42         | Flash Contents Check by Hardware CRC                                             |    |

| 7.43         | Flash ECC                                                                        |    |

| 7.44         | Flash Hard Error Cache and Livelock                                              |    |

| 7.45         | Flash Sector Protection                                                          |    |

| 7.46         | Flash Wrapper Address ECC                                                        |    |

| 7.47         | Flash Wrapper Diag Mode 5 Test                                                   |    |

| 7.48         | Flash Wrapper Diag Mode 7 Test                                                   |    |

| 7.49         | FlexRay 1002 Voting Using Both FlexRay Channels                                  |    |

| 7.50         | FlexRay CCF Clock Correction Failure Detection                                   |    |

| 7.51         | FlexRay EDA / EDB Error Detection                                                |    |

| 7.52         | FlexRay FIFO Overrun Detection                                                   |    |

| 7.53         | FlexRay Message Handler Error Detection                                          |    |

| 7.54         | FlexRay Sync Frames Below Minimum / Sync Frame Overflow                          |    |

| 7.55         | FlexRay Transmission Across Boundary Error Detection                             |    |

| 7.56         | Glitch Filtering on nRST and nPORRST                                             |    |

| 7.57         | Hardware CRC Check of External Memory                                            |    |

| 7.58         | Hardware CRC Check of OTP Contents                                               |    |

| 7.59         | Hardware Disable of JTAG Port                                                    |    |

| 7.60         | Information Redundancy Techniques                                                |    |

| 7.61         | Information Redundancy Techniques - CPU Specific                                 |    |

| 7.62         | Information Redundancy Techniques - DCAN Specific                                |    |

| 7.63         | Information Redundancy Techniques - DMA Specific                                 |    |

| 7.64         | Information Redundancy Techniques Including End-to-End Safing - FlexRay Specific |    |

| 7.65         | Information Redundancy Techniques - N2HET Specific                               |    |

| 7.66         | Internal Voltage Monitor (VMON)                                                  |    |

| 7.67         | Internal Watchdog                                                                |    |

| 7.68         | IOMM Master ID Filtering                                                         |    |

|              | LIN Checksum Error Detection                                                     |    |

| 7.69<br>7.70 | LIN No-Response Error Detection                                                  |    |

| 7.70<br>7.71 | LIN Physical Bus Error Detection                                                 |    |

| 7.71         | LIN / SCI Bit Error Detection                                                    |    |

| 7.72         | LIN / SCI Frame Error Detection                                                  |    |

| 7.73<br>7.74 | LIN / SCI Overrun Error Detection                                                |    |

| 1.14         | LINY / OOI OVEITUIT LITUI DEIEGUIUIT                                             | OO |

#### www.ti.com

| 7.75  | Locking Mechanism for Control Registers                                          | 66         |

|-------|----------------------------------------------------------------------------------|------------|

| 7.76  | Lockout of JTAG Access Using AJSM                                                | 66         |

| 7.77  | Low Power Oscillator Clock Detector (LPOCLKDET)                                  | 66         |

| 7.78  | Memory Protection Unit (MPU) for Non-CPU Bus Masters                             | 66         |

| 7.79  | MibADC Calibration                                                               | 67         |

| 7.80  | MibADC Information Redundancy Techniques                                         | 67         |

| 7.81  | MibADC Input Self-Test                                                           | 67         |

| 7.82  | MibSPI/SPI Data Length Error Detection                                           | 67         |

| 7.83  | MibSPI/SPI Data Overrun Detection                                                | 67         |

| 7.84  | MibSPI/SPI Slave Desync Detection                                                | 67         |

| 7.85  | MibSPI/SPI Slave Timeout Detection                                               | 67         |

| 7.86  | Monitoring by Second N2HET                                                       | 68         |

| 7.87  | Monitoring by eCAP or N2HET                                                      | 68         |

| 7.88  | Non-Privileged Bus Master Access                                                 | 68         |

| 7.89  | OTP Autoload ECC                                                                 | 68         |

| 7.90  | Parity in Message                                                                | 68         |

| 7.91  | Periodic Hardware CRC Check of OTP Contents                                      | 68         |

| 7.92  | PCR Access Management: Protection Mode and MasterID Filtering                    | 68         |

| 7.93  | Periodic Hardware CRC Check of SRAM Contents                                     | 69         |

| 7.94  | Periodic Software Read Back of Static Configuration Registers                    | 69         |

| 7.95  | Peripheral SRAM Parity                                                           | 69         |

| 7.96  | Peripheral Memory ECC                                                            | 69         |

| 7.97  | PLL Slip Detector                                                                | 69         |

| 7.98  | Primary SRAM Address and Control Bus Parity                                      | 69         |

| 7.99  | Primary SRAM Data and ECC Storage in Multiple Physical Banks per Logical Address | 70         |

| 7.100 | Primary SRAM Correctable ECC Profiling                                           | <b>7</b> 0 |

| 7.101 | ECC on Cache RAM                                                                 | 70         |

| 7.102 | Primary SRAM Data ECC                                                            | 70         |

| 7.103 | Primary SRAM Wrapper Redundant Address Decode                                    | 70         |

| 7.104 | Primary SRAM Hard Error Cache and Livelock                                       | 71         |

| 7.105 | Privileged Mode Access and Multi-Bit Enable Keys for Control Registers           | 71         |

| 7.106 | PBIST Check of Primary or Module SRAM                                            | 71         |

| 7.107 | PBIST Auto-coverage                                                              | 72         |

| 7.108 | Power Domain Inactivity Monitor                                                  | 72         |

| 7.109 | PBIST Test of Parity Bit Memory                                                  | 72         |

| 7.110 | PBIST Test of ECC Bit Memory                                                     | 72         |

| 7.111 | Lockstep PSCON                                                                   |            |

| 7.112 | Redundant Address Decode Self-Test                                               | 72         |

| 7.113 | Redundant Temperature Sensors                                                    |            |

| 7.114 | Scrubbing of SRAM to Correct Detected Single Bit Errors                          |            |

| 7.115 | Shadow Registers                                                                 |            |

| 7.116 | Software Check of Cause of Last Reset                                            |            |

| 7.117 | Software Read Back of CPU Registers                                              |            |

| 7.118 | Software Read Back of Written Configuration                                      |            |

| 7.119 | Software Test of DCC Functionality                                               |            |

| 7.120 | Software Test of DWD Functionality                                               |            |

| 7.121 | Software Test of DWWD Functionality                                              |            |

| 7.122 | Software Test of ECC Profiler (EPC)                                              |            |

| 7.123 | Software Test of Error Path Reporting                                            | 73         |

| 7.124      | Software Test of Flash Sector Protection Logic                                 | . 73         |

|------------|--------------------------------------------------------------------------------|--------------|

| 7.125      | Software Test of Function Including Error Tests                                | . 74         |

| 7.126      | Software Test of Function Using I/O Loopback                                   | . 74         |

| 7.127      | Software Test of Function Using I/O Checking In GIO Mode                       | . 74         |

| 7.128      | Software Test of Function Using I/O Loopback in Transceiver/PHY                | . 74         |

| 7.129      | Software Test of Function Using I/O Loopback in Transceiver / PHY - FlexRay    | . 74         |

| 7.130      | Software Test of Function Using I/O Loopback Including Error Tests - IOMM Only | . 74         |

| 7.131      | Software Test of Hardware CRC                                                  | . 75         |

| 7.132      | Software Test of MPU Functionality                                             | . 75         |

| 7.133      | Software Test of Parity Logic                                                  | . 75         |

| 7.134      | Software Test of PBIST                                                         | 75           |

| 7.135      | Software Test of SRAM Wrapper Address Decode Diagnostic and ECC                | . 75         |

| 7.136      | Software Test for Reset                                                        | . 75         |

| 7.137      | Software Warm Reset Generation                                                 | . 75         |

| 7.138      |                                                                                |              |

| 7.139      | Use of CoreSight Debug Logic Key Enable Scheme                                 | . 75         |

| 7.140      | Use of DCC as Program Sequence Watchdog                                        | . <b>7</b> 6 |

| 7.141      | Use of MPUs to Block Access to Memory Mapped Debug                             | . <b>7</b> 6 |

| 7.142      |                                                                                |              |

| 7.143      |                                                                                |              |

| 7.144      | 3                                                                              |              |

| 7.145      | Transaction ECC (Data Lines)                                                   | . <b>76</b>  |

| 7.146      |                                                                                |              |

| 7.147      | Peripheral Interconnect New Memory Protection Unit (NMPU)                      | . 77         |

| 7.148      | Software Test of The New Memory Protection Unit (NMPU) Functionality           | . 77         |

| 7.149      | Software Test of ECC Logic                                                     | . 77         |

| 7.150      | 3 · · · · · · · · · · · · · · · · · · ·                                        |              |

| 8 Next St  | eps in Your Safety Development                                                 | <b>78</b>    |

| Appendix A | Summary of Safety Feature Usage                                                | <b>79</b>    |

| Appendix B | Development Interface Agreement                                                | 130          |

| B.1        | Appointment of Safety Managers                                                 | 130          |

| B.2        | Tailoring of the Safety Lifecycle                                              | 130          |

| B.3        | Activities Performed by TI                                                     | 132          |

| B.4        | Information to be Exchanged                                                    | 133          |

| B.5        | Parties Responsible for Safety Activities                                      | 133          |

| B.6        | Communication of Target Values                                                 | 134          |

| B.7        | Supporting Processes and Tools                                                 | 134          |

| B.8        |                                                                                | 134          |

| B.9        | Creation of Functional Safety Concept                                          | 134          |

| Appendix C | Revision History                                                               | 135          |

#### www.ti.com

# **List of Figures**

| 1 | Device Revision Code Identification                                        |    |

|---|----------------------------------------------------------------------------|----|

| 2 | Hercules Product Architecture Overview                                     | 10 |

| 3 | TI Standard MCU Automotive QM Development Process                          | 14 |

| 4 | Hercules Enhanced Functional Safety Development Process                    | 17 |

| 5 | Partition of Hercules MCU for Safety Analysis                              | 18 |

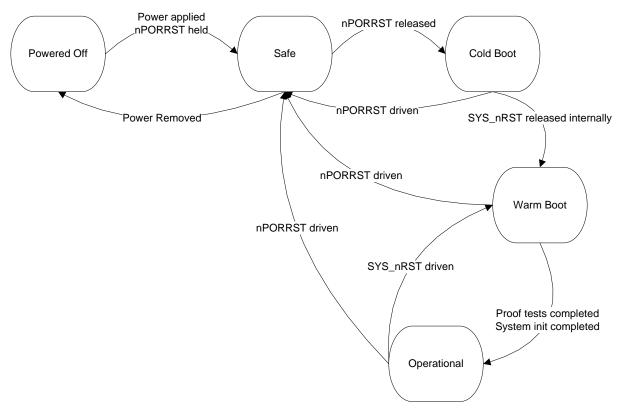

| 6 | Operating States of the Hercules MCU                                       | 21 |

| 7 | Lockstep Temporal Diversity                                                | 30 |

| 8 | Hercules Tailoring of Safety Lifecycle1                                    | 31 |

|   |                                                                            |    |

|   | List of Tables                                                             |    |

| 1 | Identification of Parts/Elements                                           | 19 |

| 2 | Summary of ESM Error Indication                                            | 22 |

| 3 | Key to Summary of Safety Features and Diagnostics                          | 79 |

| 4 | Summary of Safety Features and Diagnostics                                 | 80 |

| 5 | Activities Performed by TI vs. Performed by SEooC Customer                 | 32 |

| 6 | Product Safety Documentation                                               | 33 |

| 7 | Product Functional Documentation to be Considered in Safety-Related Design | 33 |

| 8 | Product Safety Documentation Tools and Formats                             |    |

| ^ | CDNII F 40 A Pavisions                                                     | ^- |

# Safety Manual for TMS570LC4x Hercules ARM Safety MCUs

#### 1 Introduction

You, a system and equipment manufacturer or designer, are responsible to ensure that your systems (and any TI hardware or software components incorporated in your systems) meet all applicable safety, regulatory, and system-level performance requirements. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested TI products, and other materials) is provided for reference only. You understand and agree that your use of TI components in safety critical applications is entirely at your risk, and that you (as buyer) agree to defend, indemnify, and hold harmless TI from any and all damages, claims, suits, or expense resulting from such use.

This document is a safety manual for the Texas Instruments Hercules safety critical microcontroller product family. The product family utilizes a common safety architecture that is implemented in multiple application focused products. Product configurations supported by this safety manual include silicon revisions A and B of the following products: (Note that the part numbers listed below are for revision B; other revisions are slightly different. The device revision can be determined by the symbols marked on the top of the device as seen in Figure 1 below this list).

- TMS570LS Safety Critical Microcontrollers

- TMS570LC4357-ZWT (Orderable Part #: TMS5704357BZWTQQ1)

- TMS570LC4357-ZWT (Orderable Part #: TMS5704357BZWTQQ1R)

- TMS570LC4355-ZWT (Orderable Part #: TMS5704355BZWTQQ1)

- TMS570LC4355-ZWT (Orderable Part #: TMS5704355BZWTQQ1R)

- TMS570LC4355-ZWT (Orderable Part #: TMS5704355BZWTSQ1)

- TMS570LC4355-ZWT (Orderable Part #: TMS5704355BZWTSQ1R)

- TMS570LC4343-ZWT (Orderable Part #: TMS5704343BZWTQQ1)

- TMS570LC4343-ZWT (Orderable Part #: TMS5704343BZWTQQ1R)

- TMS570LC4343-ZWT (Orderable Part #: TMS5704343BZWTSQ1)

- TMS570LC4343-ZWT (Orderable Part #: TMS5704343BZWTSQ1R)

SafeTI is a trademark of Texas Instruments.

ARM, Cortex are registered trademarks of ARM Limited.

Adobe is a trademark of Adobe Systems Incorporated in the United States, and/or other countries.

IBM, DOORS are registered trademarks of International Business Machines Corporation, registered in many jurisdictions worldwide. Microsoft, Excel are registered trademarks of Microsoft Corporation in the United States and/or other countries, or both. All other trademarks are the property of their respective owners.

www.ti.com Introduction

Figure 1. Device Revision Code Identification

This Safety Manual provides information needed by system developers to assist in the creation of a safety critical system using a supported Hercules microcontroller. This document contains:

- An overview of the superset product architecture

- An overview of the development process utilized to reduce systematic failures

- An overview of the safety architecture for management of random failures

- · The details of architecture partitions, implemented safety mechanisms

The following information is documented in the Safety Analysis Report Summary for TMS570LC4x ARM®-Based Safety Critical Microcontrollers (SPNU541) and is not repeated in this document:

- Summary of failure rates of the MCU estimated at the chip level

- Assumptions of use utilized in calculation of safety metrics

- Summary of targeted standard (IEC 61508, ISO 26262, and so forth) safety metrics at the chip level

The following information is documented in the *Detailed Safety Analysis Report for TMS570LC4x ARM®-Based Safety Critical Microcontrollers* (SPNU542) and is not repeated in this document:

- Fault model used to estimate device failure rates suitable to enable calculation of customized failure rates

- Quantitative FMEA (also known as FMEDA, Failure Modes, Effects, and Diagnostics Analysis) with detail to the sub-module level of the device, suitable to enable calculation based on customized application of diagnostics

The following information is documented in the Safety Report, and will not be repeated in this document:

· Results of assessments of compliance to targeted standards

The user of this document should have a general familiarity with the Hercules product families. For more information, see <a href="http://www.ti.com/hercules">http://www.ti.com/hercules</a>. This document is intended to be used in conjunction with the pertinent data sheets, technical reference manuals, and other documentation for the products under development.

For information which is beyond the scope of the listed deliverables, please contact your TI sales representative or <a href="http://www.ti.com">http://www.ti.com</a>.

#### 2 Hercules TMS570LC4x Product Overview

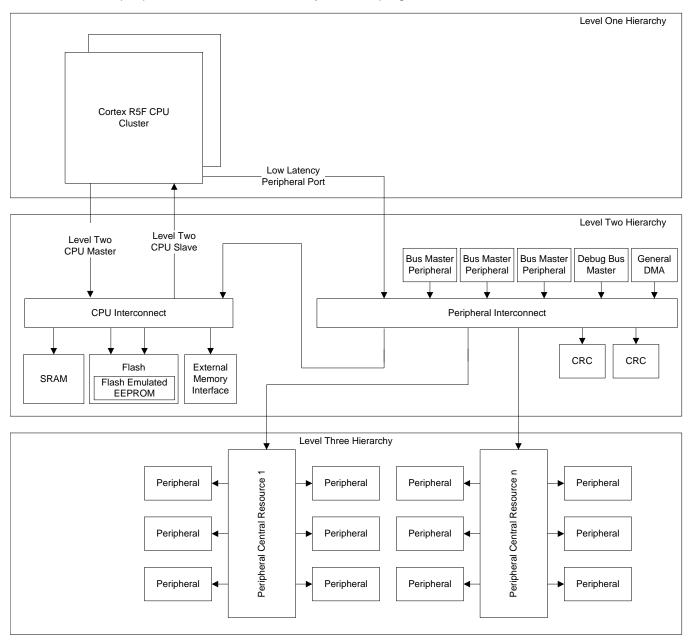

The TMS570LC4x 65 nm Hercules product family is an evolution of the proven TMS570LS Hercules products in the 65 nm manufacturing process. A simplified graphical view of the product superset architecture can be seen in Figure 2. This is a basic representation of the architecture and is not all inclusive. For example, products in the family may scale based on the number of peripherals, number of bus master peripherals, or amount of memory - but the programmer's model remains consistent.

Figure 2. Hercules Product Architecture Overview

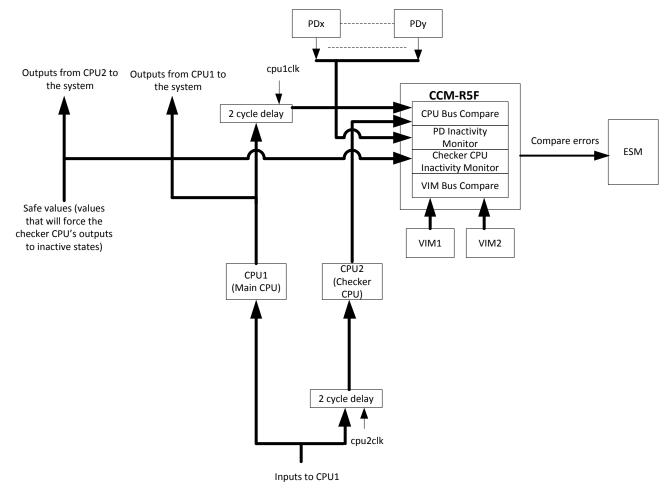

The Hercules product architecture utilizes the ARM Cortex®-R5F CPU in a cached memory configuration with both instruction and data caches. The Cortex-R5F CPU is implemented with a checker Cortex-R5F CPU in a lockstep configuration. This provides cycle by cycle checking of correct CPU operation while keeping a simple, easy to use, single core programmer's model. The Cortex R5F CPU has a multi-threaded level two bus master interface, which provides access to the level two memory hierarchy, supporting up to seven concurrent CPU accesses in flight. A level two slave interface allows bus masters access to the level one cache memories for test, debug, and fault insertion purposes. A separate low latency peripheral port provides access to peripherals. In addition, a Snoop Control Unit (SCU) module is present to snoop non-CPU bus master accesses for the purpose of I/O cache coherency.

The level two device hierarchy is dominated by two switched central resource interconnect modules (also known as bus matrices or crossbars): CPU Interconnect Subsystem and Peripheral Interconnect Subsystem. These device level interconnect modules allow multiple bus masters to access multiple bus slaves. Prioritization, routing, decode, and arbitration functions are provided. Access to the memory subsystem (Flash, FEE, SRAM, and EMIF) is provided via the CPU Interconnect Subsystem. Peripherals are accessed via the Peripheral Interconnect Subsystem and multiple level three peripheral interconnect segments (PCR1, PCR2, and PCR3). Bus masters to the level two device hierarchy include CPUs, bus master peripherals, debug bus masters, and general purpose direct memory access (DMA) controllers. Bus slaves on the level two hierarchy include the primary Flash memory, primary SRAM, Flash EEPROM emulation memory, and external memory interface (EMIF), one or more peripheral bus segments (PCRs), and Cortex-R5F slave port access.

The level three hierarchy is primarily composed of peripherals. Peripherals are grouped into one or more peripheral bus segments (PCRs), managed by a peripheral central resource. The peripheral central resource provides address decode functionality for bus transactions targeting peripherals.

# 2.1 Targeted Applications

The Hercules MCU family is targeted at general purpose safety applications. Multiple safety applications were analyzed during the concept phase in order to support Safety Element out of Context (SEooC) development according to ISO 26262-10:2012. Example target applications include:

- Automotive braking systems, including anti-lock braking (ABS), anti-lock braking with traction control (ABS+ TC), and electronic stability control (ESC)

- Motor control systems, particularly electronic power steering (EPS) systems and electric vehicle (EV) power train

- General purpose safety computation, such as integrated sensor cluster processing and vehicle strategy generation in an active safety system

- Industrial automation such as programmable logic controllers (PLCs) and programmable automation controllers (PACs) for safety critical process control

In the case of overlapping requirements between target systems, TI has attempted to design the device respecting the most stringent requirements. For example, the fault tolerant time intervals for timer logic in an ESC application are typically on the order of 100 ms. In an EPS application, the fault tolerant time interval is typically on the order of 10 ms. In such case, TI has performed timer subsystem analysis respecting <10 ms fault tolerant time interval.

While TI considered certain applications during the development of these devices, this should not restrict a customer who wishes to implement other systems. With all safety critical components, rationalization of the component safety concept to the system safety concept should be executed by the system integrator.

### 2.2 Product Safety Constraints

This device is a Type B device, as defined in IEC 61508:2010

This device claims no hardware fault tolerance (HFT = 0), as defined in IEC 61508:2010

For safety components developed according to many safety standards, it is expected that the component safety manual will provide a list of product safety constraints. For a simple component, or more complex components developed for a single application, this is a reasonable response. However, the Hercules product family is both a complex design and is not developed targeting a single, specific application. Therefore, a single set of product safety constraints cannot govern all viable uses of the product. The Detailed Safety Analysis Report for TM570LC4x ARM®-Based Safety Critical Microcontrollers (SPNU542) provides a reference implementation of the Hercules product in a common system with relevant product safety constraints.

### 3 Hercules Development Process for Management of Systematic Faults

For a safety critical development, it is necessary to manage both systematic and random faults. Texas Instruments has created a unique development process for safety critical semiconductors that greatly reduces probability of systematic failure. This process builds on a standard Quality Managed (QM) development process as the foundation for safety critical development. This process is then augmented by a second layer of development activities that are specific to safety critical developments targeting IEC 61508 and ISO 26262.

In 2007, TI first saw the need to augment this standard development process in order to develop products according to IEC 61508. TI engaged with safety industry leader exida consulting to ensure the development was compliant to the standard. During 2008, a process for safety critical development according to IEC 61508 1st edition was implemented. This process has been executed on multiple microcontroller developments that are currently shipping into safety critical systems. The Hercules family product and safety architectures described in this document began development under the IEC 61508 development flow.

By mid 2009, it became clear that the emerging IEC 61508 2nd edition and ISO 26262 functional safety standards would require enhanced process flow capabilities. Due to the lack of maturity of these draft standards, it was not possible to implement a development process that ensured compliance before final drafts were available.

TI joined the ISO 26262 working group in mid 2009 as a way to better understand and influence the standard with respect to microcontroller hardware component development. As part of the US Technical Advisory Group (TAG) and international working group for ISO 26262, TI has notable contributions to:

- ISO 26262-5; Annex D informative section describing failure modes and recommended diagnostics for hardware components, enhanced by TI's detailed knowledge of silicon failure modes and effectiveness of diagnostic methods

- ISO 26262-10; Clause 9 informative section describing development of safety elements out of context, a technique that legitimizes and enables the use of Commercial Off The Shelf (COTS) safety critical components

- ISO 26262-10; Annex A informative section describing how to apply ISO 26262 to microcontrollers, influenced by TI's lessons learned in application of IEC 61508 to microcontroller development

In mid 2010, TI started development of a process flow compliant to IEC 61508 2nd edition and ISO 26262 draft baseline 18. TI worked in detail with Yogitech in the ISO 26262 international working group and found that the companies have complementary capabilities. A partnership was established for engineering services and safety consulting services to accelerate new safety-related product development. Yogitech's existing fRMethodology development process and Tl's IEC 61508 development process were merged and enhanced to create a new process addressing both ISO 26262 and IEC 61508 2nd edition. This process has gone through a process of continual improvement as ISO 26262 standards development continues. The process applied to the Hercules silicon covered by this document incorporates all changes through ISO 26262:2012 international standard release for part 10 and the ISO 26262:2011 international standard release for parts 1-9.

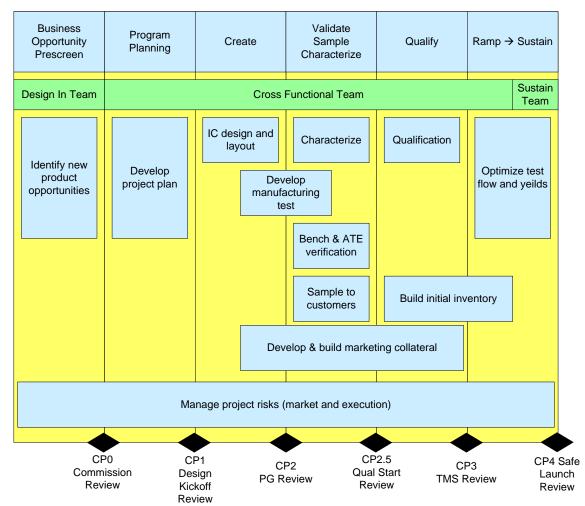

### 3.1 TI Standard MCU Automotive Development Process

Texas Instruments has been developing automotive microcontrollers for safety critical and non-safety critical automotive applications for over twenty years. Automotive markets have strong requirements on quality management and high reliability of product. Though not explicitly developed for compliance to a functional safety standard, the TI standard MCU Automotive development process already features many elements necessary to manage systematic faults. This development process can be considered to be Quality Managed (QM), but does not achieve an IEC 61058 Safety Integrity Level (SIL) or ISO 26262 Automotive Safety Integrity Level (ASIL). For up-to-date information on TI quality process certifications, see <a href="http://www.ti.com/quality">http://www.ti.com/quality</a>.

The standard process breaks development into phases:

- Business opportunity pre-screen

- Program planning

- Create

- · Validate, sample, and characterize

- Qualify

- · Ramp to production and sustaining production

The standard process is illustrated in Figure 3.

Figure 3. TI Standard MCU Automotive QM Development Process

### 3.2 TI MCU Automotive Legacy IEC 61508 Development Process

Texas Instruments developed an initial process for developing safety critical automotive microcontrollers in 2008. This process was developed targeting the IEC 61508 1st edition standard, as augmented with available committee drafts of the 2nd edition. The process is developed as an additional layer of activities that should be carried out in addition to the standard MCU Automotive QM development process. This process as applied on the TMS570LS20216S product development has been assessed suitable for use in IEC 61508 SIL 3 applications by exida Certification S.A. (certificate TI 071227 C001). In July 2012 the development process and the TMS570LS20x/10x product family was assessed to the IEC 61508:2010 standard and certified suitable for use in IEC 61508 SIL 3 applications by exida Certification Services (certificate TI 1204073 C001).

Key new activities in this process included:

- Nomination of a safety manager with ownership of all safety related activities

- Development of a safety plan to track safety related activities

- · Generation, application, and validation of safety requirements

- Execution of qualitative (FMEA) and quantitative (FMEDA) safety analysis

- · Authoring of safety manual and safety analysis report to support customer development

# 3.3 Yogitech fRMethodology Development Process

fRMethodology is the "white-box" approach for safety design exploration proprietary of YOGITECH, including:

- fRFMEA, a methodology to perform the FMEA of an integrated circuit in accordance to IEC 61508 and ISO 26262

- fRFI, a tool to perform fault injection of an integrated circuit based on inputs derived from fRFMEA

YOGITECH's fRMethodology is in line with ISO 26262-10; Annex A. It mainly consists of:

- Splitting the component or system in elementary parts ("sensitive zones")

- · Computing their failure rates

- Using those failure rates to compute safety metrics

- · Validating the results with fault injection

- Allowing sensitivity analyses of those metrics by changing architectural or technological parameters

- Delivering to the customer numbers to compare different architectures

# 3.4 Hercules Enhanced Safety Development Process

The Hercules enhanced safety development process is a merger of the existing TI and Yogitech flows for functional safety development. The goal of the process development is to take the best aspects of each flow and collaborate, resulting in the best in class capabilities to reduce systematic faults.

The process flow is targeted for compliance to IEC 61508 and ISO 26262, and is under a process of continuous improvement to incorporate new features of emerging functional safety standards. These functional safety standards are targeted because TI and Yogitech believe they best represent the state of the art in functional safety development for semiconductors. While not directly targeted at other functional safety standards, it is expected that products developed to industry state-of-the-art can be readily utilized in other functional safety systems.

The resulting flow was subsequently assessed by TUEV SUED for compliance to IEC 61508 and ISO 26262 and further enhanced based on technical findings. The development flow is certified by TUEV SUED under certificate Q4B 13 03 84071 001.

Key elements of the combined process flow are:

- Assumptions on system level design, safety concept, and requirements based on TI's expertise in safety critical systems development

- Combined qualitative and quantitative or similar safety analysis techniques comprehending the sum of silicon failure modes and diagnostic techniques known to both TI and Yogitech

- · Fault estimation based on multiple industry standards as well as TI manufacturing data

- Application of Yogitech's state-of-the-art fault injection techniques for validation of claimed diagnostic coverage

- Integration of lessons learned by both companies through multiple safety critical developments to IEC 61508 and participation in the ISO 26262 international working group

The Figure 4 is shown below in a simplified graphic.

| Phase 0<br>Business<br>Opportunity                                              | Phase 1 Program Planning                                                        | Phase 2<br>Create                                      | Phase 2.5<br>Validate, Sample,<br>and | Phase 3<br>Qualify                        | Phase 4<br>Ramp/Sustain                             |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------|-------------------------------------------|-----------------------------------------------------|

| Prescreen                                                                       |                                                                                 |                                                        | Characterize                          | <b>,</b>                                  | ,                                                   |

| Determine if safety<br>process execution is<br>necessary                        | Define SIL/ASIL capability                                                      | Execute safety design                                  | Validate safety design in silicon     | Qualification of safety design            | Implement plans to support operation and production |

| Execute development interface agreement (DIA) with lead customers and suppliers | Generate safety plan                                                            | Qualitative analysis of<br>design (FMEA and<br>FTA)    | Release safety<br>manual              | Release safety case report                | Update safety case report (if needed)               |

|                                                                                 | Initiate safety case                                                            | Incorporate findings into safety design                | Release safety<br>analysis report     | Update safety manual<br>(if needed)       | Periodic confirmation measure reviews               |

|                                                                                 | Analyze system to generate system level safety assumptions and requirements     | Develop safety product preview                         | Characterization of safety design     | Update safety analysis report (if needed) |                                                     |

|                                                                                 | Develop component<br>level safety<br>requirements                               | Validation of safety<br>design at RTL level            | Confirmation measure review           | Confirmation measure review               |                                                     |

|                                                                                 | Validate component<br>safety requirements<br>meet system safety<br>requirements | Quantitative analysis of design (FMEDA)                |                                       |                                           |                                                     |

|                                                                                 | Implement safety requirements in design specification                           | Incorporate findings into safety design                |                                       |                                           |                                                     |

|                                                                                 | Validate design<br>specification meets<br>component safety<br>requirements      | Validation of safety<br>design at gate/layout<br>level |                                       |                                           |                                                     |

|                                                                                 | Confirmation measure review                                                     | Confirmation measure review                            |                                       |                                           |                                                     |

Figure 4. Hercules Enhanced Functional Safety Development Process

### 4 Hercules Product Architecture for Management of Random Faults

For a safety critical development it is necessary to manage both systematic and random faults. The Hercules product architecture includes many safety mechanisms, which can detect and respond to random faults when used correctly. This section of the document describes the architectural safety concept for the MCU.

# 4.1 Safe Island Philosophy and Architecture Partition to Support Safety Analysis (FMEA/FMEDA)

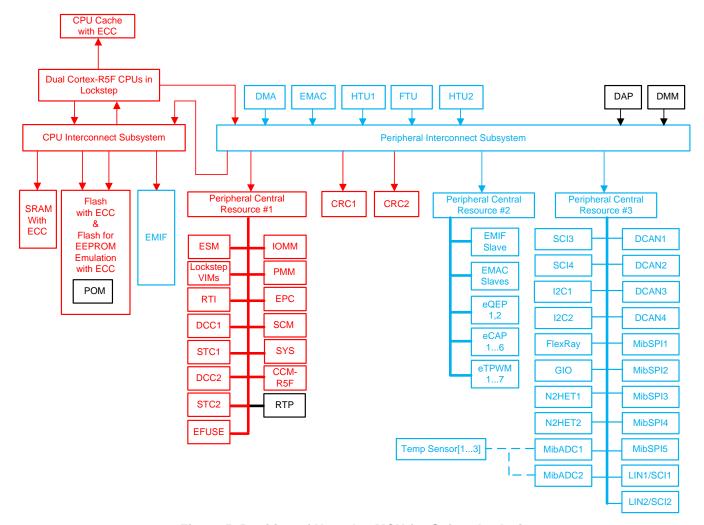

The TMS570 Hercules processors share a common safety architecture concept called a "safe island" philosophy. The basic concept involves a balance between application of hardware diagnostics and software diagnostics to manage functional safety, while balancing cost concerns. In the "safe island" approach, a core set of elements are allocated continuously operating hardware safety mechanisms. This core set of elements, including power and clock and reset, CPU, Flash memory, SRAM and associated interconnect to Flash and SRAM, is needed to assure any functionally correct execution of software. Once correct operation of these elements is confirmed, software can be executed on these elements in order to provide software-based diagnostics on other device elements, such as peripherals. This concept has been proven viable through multiple generations of safety-critical products in the automotive passenger vehicle space.

Figure 5 illustrates the safe island approach overlaid to a superset configuration of the Hercules product architecture.

Figure 5. Partition of Hercules MCU for Safety Analysis

Figure 5 illustrates three architectural partitions:

- "Safe Island Layer" (RED) This is the region of logic that is needed for all processing operations. This

logic is protected heavily by on board hardware diagnostics and specific assumptions of use to assure

a high level of confidence in safe operation. Once this region is safed, it can be used to provide

comprehensive software diagnostics on other design elements.

- "Blended Layer" (BLUE) This is the region of logic that includes most safety critical peripherals. This

region has less reliance on hardware diagnostics. Software diagnostics and application protocols are

overlaid to provide the remainder of needed diagnostic coverage.

- "Offline Layer" (BLACK) This region of logic has minimal or no integrated hardware diagnostics.

Many features in this layer are used only for debug, test, and calibration functions; they are not active during safety critical operation. Logic in this region could be utilized for safety critical operation assuming appropriate software diagnostics or system level measures are added by the system integrator.

#### 4.2 Identification of Parts/Elements

For the purposes of a safety analysis, each module on this device can be considered to be a part or element. Each part or element has been assigned a three letter unique identifier, which is used uniformly in the Safety Manual, Safety Analysis Report, and FMEDA Documents to identify the element and it's diagnostics. Table 1 lists each element present on this device and the unique identifier for this element. The overall IEC 61508 systematic capability of the MCU is SC3. TI does not make claims of systematic capability for specific IP modules on the device.

Table 1. Identification of Parts/Elements

| Part / Element Name                                                | Unique Identifier |

|--------------------------------------------------------------------|-------------------|

| Clock                                                              | CLK               |

| Cortex-R5F Central Processing Unit (CPU)                           | CPU               |

| Controller Area Network (DCAN)                                     | CAN               |

| Cortex-R5F Central Processing Unit (CPU) Debug and Trace           | DBG               |

| CPU Interconnect Subsystem                                         | MEM               |

| Data Modification Unit                                             | DMM               |

| Direct Memory Access (DMA)                                         | DMA               |

| Enhanced Capture (eCAP)                                            | CAP               |

| EFuse Static Configuration                                         | EFU               |

| External Memory Interface (EMIF)                                   | EMF               |

| Enhanced Pulse Width Modulators (ePWM)                             | PWM               |

| Enhanced Quadrature Encoder Pulse (eQEP)                           | QEP               |

| Error Profiling Controller                                         | EPC               |

| Error Signaling Module (ESM)                                       | ESM               |

| Ethernet                                                           | ETH               |

| Flash EEPROM Emulation (FEE)                                       | FEE               |

| Primary Flash                                                      | FLA               |

| FlexRay Including FlexRay Transfer Unit (FTU)                      | FRY               |

| General Purpose Input/Output (GIO)                                 | GIO               |

| Inter-Integrated Circuit (I2C)                                     | IIC               |

| Input/Output (I/O) Multiplexing Module (IOMM)                      | IOM               |

| Joint Technical Action Group (JTAG) Debug/Trace/Calibration Access | JTG               |

| Local Interconnect Network (LIN)                                   | LIN               |

| Multi-Buffered Analog to Digital Converter (MibADC)                | ADC               |

| Multi-Buffered Serial Peripheral Interface (MibSPI)                | MSP               |

| High-End Timer (N2HET) Including HET Transfer Unit (HTU)           | HET               |

| One Time Programmable (OTP) Flash Static Configuration             | ОТР               |

Table 1. Identification of Parts/Elements (continued)

| Part / Element Name                              | Unique Identifier |

|--------------------------------------------------|-------------------|

| Peripheral Interconnect Subsystem                | PER               |

| Peripheral Central Resource 1                    | P1T               |

| Peripheral Central Resource 2                    | P2T               |

| Peripheral Central Resource 3                    | P3T               |

| Power Management Module (PMM)                    | PMM               |

| Parameter Overlay Module                         | POM               |

| Power Supply                                     | PWR               |

| RAM Trace Port                                   | RTP               |

| Reset                                            | RST               |

| Real Time Interrupt (RTI) Operating System Timer | RTI               |

| Serial Communications Interface (SCI)            | SCI               |

| SRAM                                             | RAM               |

| System Control Module                            | SYS               |

| Temperature Sensors                              | TSN               |

| Vectored Interrupt Module (VIM)                  | VIM               |

NOTE: The terms "element" and "part" may have specific meaning and imply specific requirements dependent on the targeted functional safety standard. The terms are used here in a general sense.

TheHercules Architecture Brief Description of Elements section contains a brief description of the elements listed above. For a full functional description of any of these modules, see the device-specific technical reference manual.

#### 4.3 Management of Family Variants

The Hercules family architecture supports multiple product variants. These products could be implemented as unique silicon designs or they can be shared silicon designs that have elements disabled or not assured by specification, even if present in silicon. Only the elements of the superset architecture that are specifically detailed in the device-specific data sheet and technical reference manual are assured to be present and operate. When developing for the Hercules platform, it is recommended that the safety concept be based on the superset product architecture to enable maximum scalability across family variants. The superset architecture shown in the previous section is valid for all device part numbers noted in the introduction of the safety manual.

#### 4.4 Operating States

The Hercules MCU products have a common architectural definition of operating states. These operating states should be observed by the system developer in their software and system level design concepts. The operating states state machine is shown in Figure 6 and described below.

Figure 6. Operating States of the Hercules MCU

- "Powered Off" This is the initial operating state of the Hercules MCU. No power is applied to either

core or I/O power supply and the device is non-functional. This state can only transition to the safe

state, and can only be reached from the safe state.

- "Safe" In the safe state, the Hercules MCU is powered but non-operational. The nPORRST (power-on reset, also known as cold reset) is asserted by the system but is not released until power supplies have ramped to a stable state. The internal voltage monitor (VMON) safety mechanism also continues to assert the nPORRST internal to the device if power supplies are not within a minimum operational range. When the product is in the safe state, the CPU and peripherals are non-functional. Output drivers are tri-stated and input/output pins are kept in an input only state.

- "Cold Boot" In the cold boot state, key analog elements, digital control logic, and debug logic are

initialized for future use. The CPU remains powered but non-operational. When the cold boot process

is completed, the SYS\_nRST signal is internally released, leading to the warm boot stage. The

SYS\_nRST signal transition change can be monitored externally on the SYS\_nRST I/O pin.

- "Warm Boot" The warm boot mode resets digital logic and enables the CPU. The CPU begins executing software from Flash memory and software initialization of the device can begin. There is no hardware interlock to say that warm boot is completed; this is a software decision.

- "Operational" During the operational mode, the device is capable of supporting safety critical functionality.

### 4.5 Management of Errors

When a diagnostic detects a fault, the error must be indicated. The Hercules product architecture provides aggregation of fault indication from internal safety mechanisms using a peripheral logic known as the error signaling module (ESM). The ESM provides mechanisms to classify errors by severity and to provide programmable error response. The ESM does not, in and of itself, impact the overall function of the device and serves the limited purpose of fault aggregation and classification. The error classifications in the ESM are summarized in Table 2.

**Table 2. Summary of ESM Error Indication**

| Error Group | r Group Interrupt Response Error Pin Respo                 |                       | Notes                                                              |

|-------------|------------------------------------------------------------|-----------------------|--------------------------------------------------------------------|

| 1           | Programmable interrupt and programmable interrupt priority | Programmable response | For errors that are generally not of critical severity             |

| 2           | Non maskable interrupt generated                           | Error pin activated   | For errors that are generally of critical severity                 |

| 3           | No interrupt response                                      | Error pin activated   | For critical errors that are seen by diagnostic implemented in CPU |

The error response is action that is taken by the MCU or system when an error is indicated. There are multiple potential of error response possible for the Hercules product. The system integrator is responsible to determine what error response should be taken and to ensure that this is consistent with the system safety concept.

- CPU abort This response is implemented directly in the CPU, for diagnostics implemented in the CPU. During an abort, the program sequence transfers context to an abort handler and software has an opportunity to manage the fault.

- CPU interrupt This response can be implemented for diagnostics outside the CPU. An interrupt allows events external to the CPU to generate a program sequence context transfer to an interrupt handler where software has an opportunity to manage the fault.

- Generation of SYS\_nRST This response allows the device to change states to warm boot from

operational state. The SYS\_nRST could be generated from an external monitor or internally by the

software reset or watchdog. Re-entry to the warm reset state allows possibility for software recovery

when recovery in the operational state was not possible.

- Generation of nPORRST This response allows the device to change state to safe state from cold boot, warm boot, or operational states. From this state, it is possible to re-enter cold boot to attempt recovery when recovery via warm boot is not possible. It is also possible to move to the powered-down state, if desired, to implement a system level safe state. This response can be generated from the internal voltage monitor, but is primarily driven by monitors external to the MCU.

The ESM provides multiple registers that can be read by the CPU to determine the current status of diagnostics and the state of the nERROR pin. For the severe group 2 errors, a shadow register is provided that is not reset by SYS\_nRST. This allows the possibility of warm reset reinitialization to identify that a group 2 error initiated the external reset.

It is possible for the CPU to trigger the nERROR pin response manually to test system behavior or to notify external logic of an internal fault not automatically indicated to ESM. The CPU is responsible to clear indicated errors in the ESM, including clearing of the nERROR pin response.

The EPC is used as a complement to the ESM for error profiling. The primary goal of this module is to provide a unified correctable ECC error (single bit ECC fault) profiling capability and error address cache on ECC failures in system bus memory slaves like Flash, FEE, and SRAM. The secondary goal of this module is to provide an ECC error reporting capability for bus masters, which do not natively have ECC logic built in like the DMA and TUs. The ECC generation and evaluation logic for bus masters such as DMA and the TUs are built into the CPU Interconnect Subsystem.

System level management of the external error response can be simplified through the use of a TI TPS6538x power supply and safety companion device developed for use with the Hercules family.

### 5 System Integrator Recommendations

You, as a system and equipment manufacturer or designer, are responsible to ensure that your systems (and any TI hardware or software components incorporated in your systems) meet all applicable safety, regulatory, and system-level performance requirements. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested TI products, and other materials) is provided for reference only. You understand and agree that your use of TI components in safety critical applications is entirely at your risk, and that you (as buyer) agree to defend, indemnify, and hold TI harmless from any and all damages, claims, suits, or expense resulting from such use.

A brief description of each element on this device and the general assumptions of use are provided in Section 6.

A list of diagnostic mechanisms for this device and a brief description for each diagnostic are provided in Section 7.

The effectiveness of the hardware safety mechanisms is noted in the *Detailed Safety Analysis Report for TM570LC4x ARM®-Based Safety Critical Microcontrollers* (SPNU542).

This information should be used to determine the strategy for utilizing safety mechanisms. The details of each safety mechanism can be found in the device-specific technical reference manual.

Depending on the safety standard and end equipment targeted, it may be necessary to manage not only single point faults, but also latent faults. Per ISO 26262, a latent fault occurs when a fault capable of violating a safety goal occurs simultaneously to a fault in the diagnostic mechanism that would normally provide diagnostic coverage for that fault. Latent fault testing does not need to occur during the fault tolerant time interval, but can be performed at boot time, at shut down, or periodically as determined by the system developer. Many of the safety mechanisms described in this section can be used as primary diagnostics, diagnostics for latent fault, or both. When considering system design for management of latent faults, take care to include failure of execution resources when considering latent faults with software diagnostics, such as failure of CPU and memories.

# 5.1 System Integrator Activities

The system integrator is responsible for carrying out a number of product development activities. These activities carried out may include but are not limited to the following:

- Operational and Environmental Constraints

- Verify that the implementation of the TI component in the system design is compliant to requirements in TI documentation. This includes but is not limited to the requirements found in technical reference manuals, data sheets, errata documents, safety manuals, and safety analysis reports

- Verify that the system operational lifetime (power-on hours) does not exceed lifetime specifications for the TI component, as specified in the device data sheet. If the operational lifetime (power-on hours) is not specified in the data sheet, the use case does not match published conditions, or there are questions regarding device lifetime, please contact a TI quality/reliability engineering representative or <a href="http://www.ti.com">http://www.ti.com</a>.

- Define system maintenance requirements. The Hercules MCU does not require maintenance.

- Define system repair requirements. The Hercules MCU is non-repairable with respect to permanent faults. A power-on reset of the Hercules MCU may be considered a repair activity for transient faults per some definitions of system repair requirements.

- Define system decommissioning requirements. The Hercules MCU has no specific decommisioning requirements.

- Define system disposal requirements. The Hercules MCU has no specific disposal requirements.

- Avoidance of Systematic Errors

- Verify the application of appropriate best practices at all stages of hardware and system development (including development of hardware and system diagnostics external to the MCU) to avoid systematic failure and to control random failures. This may include but is not limited to compliance to the requirements documented in IEC61508-2;Annex A Tables A.15 through A.18, as well as Annex B Tables B.1 through B.6

- Verify that any software implemented (including software diagnostics) is developed with an

appropriate set of measures to avoid systematic errors

#### Safety Concept Definition

- Define the supported safety functions and verify that the microcontroller behaves properly to support execution of the defined safety function. This microcontroller is a generic product, which is capable of supporting a variety of safety functions but does not have fixed support for any specific safety function.

- Define the system-level safe state concept considering safe-state entry, maintenance of safe state, and safe-state exit as appropriate to the application and verify correct implementation

- Define the system-level error-handling concept and verify correct implementation.

- Define appropriate overall timing requirements for safety metrics to be calculated for the application

- Define appropriate safety metric targets for the application

# Safety Concept Implementation

- Select and implement an appropriate set of diagnostics and safety mechanisms from the MCU safety manual as necessary to satisfy the requirements of the targeted standards and the high level safety concept. Dependent on the results of the system level safety analysis, it may not be necessary to implement all diagnostic measures which TI has identified.

- For the device diagnostics listed as "system" in Table 4, implement the diagnostic in a manner that meets functional safety requirements of the system, particularly monitoring of the external clock, monitoring of voltage, and MCU state monitoring via external watchdog logic. Tl's recommendations are based on analysis of what faults might be detected external to the MCU when considering fault models/failure modes described in IEC 61508 -2 Annex A as to be considered for any claims of high diagnostic coverage, including both permanent and transient failure modes.

- Implement appropriate mechanisms to detect shorts between pins on the device. Tests may include

I/O loopback tests, information redundancy, or system-level mechanisms designed to detect shorts.

- Any end-to-end communications diagnostics implemented should consider the failure modes and potential mitigating safety measures described in IEC 61784-3:2010 and summarized in IEC 61784-3:2010 in Table 1.

- Ensure that any additional system level hardware or software diagnostics created or implemented by the system integrator are developed with an appropriate process to avoid systematic errors.

- Define an appropriate diagnostic test interval per diagnostic to be implemented.

- Verification of Safety Concept including Safety Metric Calculation

- Verify the behavior of the MCU outputs in the system when the MCU is in a faulted condition.

- Evaluate the system design for specific failure modes of functional logic and diagnostic logic which

are detectable based on the specific application usage and the specific diagnostics applied. Tl's

safety analysis for the MCU considers all fault models noted in IEC 61508-2 Annex A as to be

considered for any claims of high diagnostic coverage, including both permanent and transient

failure modes. Refer to the Safety Analysis Report for more details.

- Evaluate the system design for specific failure modes of functional logic and diagnostic logic which are not detectable based on the specific application usage and the specific diagnostics applied. TI's safety analysis for the MCU considers all fault models noted in IEC 61508-2 Annex A as to be considered for any claims of high diagnostic coverage, including both permanent and transient failure modes. Refer to the Safety Analysis Report for more details and ensure that the system design considers system level diagnostics recommended by TI, such as external voltage supervision, external watchdog, and so forth.

- Verify that the implemented diagnostics meet the target diagnostic test interval per diagnostic.

- Estimate failure rates and diagnostic coverage per failure mode with respect to specific application usage. TI provides tools to support this activity in the Safety Analysis Report (SAR).

- Verify that environmental and operational constraints are properly modeled in the FMEDA to provide failure rate estimates.

- Verify that appropriate on-chip design elements are selected in the FMEDA for the specific safety function under analysis.

- Verify that targeted safety metrics are calculated and achieved

- Verify the diagnostic coverage achieved by the implemented system and software based

diagnostics.

- Verify that the safety analysis considers MCU elements which are necessary to support the primary function, such as clock, power, OTP configuration, and similar. Many times the focus of analysis is the functional datapath but the elements necessary to support proper operation should also be considered.

- Execute a co-existence/freedom from interference analysis per the targeted standard to confirm that implemented functionality can co-exist without interference.

- Execute a dependent failure/common cause analysis to consider possible dependent/common cause failures on the sub-elements of the MCU, including pin level connections.

# 5.2 Hints for Performing Dependent/Common Cause Failure Analysis Including the Hercules MCU

The following steps may be useful for performing dependent/common cause failure analysis when using the Hercules MCU:

- Consider a relevant list of dependent fault/common cause fault initiators, such as the lists found in the draft ISO/PAS 19451 document, "Application of ISO 26262 to Semiconductors"

- Verify that the dependent failure analysis considers the impact of the software tasks running on the MCU, including hardware and software interactions and task/operating system interactions.

- Verify that the dependent failure analysis considers the impact of pin/ball level interactions on the MCU package, including aspects related to the selected I/O multiplexing

# 5.3 Hints for Improving Independence of Function/Co-Existence of Function When Using the Hercules MCU

The following steps may be useful for improving independence of function when using the Hercules MCU:

- Verify that unused interrupt channels are disabled in the VIM

- Verify that unused interrupt sources are disabled in the source peripherals

- Hold peripheral chip selects in reset with the PCR if the peripherals are unused

- Leave peripherals in default reset state if not controlled via PCR

- Power down power domains if all logic in power domain is not used

- Disable event triggers if unused

- Power down the ADC cores if MibADCs are unused

- Utilize peripheral bus master memory protection units (MPUs) to only allow access to needed transmit and receive buffers

- Utilize the CPU MPU to support isolation of separate software tasks running on the CPU

- Utilize privileged access modes as a secondary level of task isolation

- Utilize bus master ID filtering when available to limit allocation of peripherals to bus masters

- When possible, separate critical I/O functions by using non adjacent I/O pins/balls. Consider using the pin muxing logic to support such separation.

- Power down unused clock sources.

- · Disable unused clock domains.

- · Power down the flash pump logic if flash memory is not used after boot.

# 5.4 Support for System Integrator Activities

If you have any questions regarding usage of the TI documentation for system integration, or if you have questions regarding MCU level functional safety standard work products not provided as part of the TI documentation package, please contact TI support. The preferred and fastest method to contact TI support is via the E2E forum at <a href="http://e2e.ti.com/support/microcontrollers/hercules/default.aspx">http://e2e.ti.com/support/microcontrollers/hercules/default.aspx</a>.

### 6 Brief Description of Elements