### **About this document**

### **Scope and purpose**

This is a design guide to help customers design a 65 W USB-PD adaptor with Infineon's latest ZVS digital controller **XDPS21081**. It provides guidelines for power stage design, IC parameter settings, PCB layout and .dp Vision GUI usage.

### **Intended audience**

This document is intended for power supply engineers who need to design adaptors with Infineon's digital control ZVS IC, XDPS21081. It also provides an insight into making a highly efficient transformer design with understanding of the loss mechanism.

## **Table of contents**

| Abou  | t this documentt                           | 1  |

|-------|--------------------------------------------|----|

| Table | of contents                                | 1  |

| 1     | Abstract                                   | 3  |

| 2     | Introduction                               | 4  |

| 2.1   | IC introduction                            | 4  |

| 2.2   | Pin configuration and description          | 4  |

| 2.3   | Product highlights                         | 5  |

| 2.4   | Simplified application diagram             | 6  |

| 2.5   | ZVS principles                             | 6  |

| 3     | Flyback power stage design                 | 8  |

| 3.1   | 65 W adaptor system specifications         | 8  |

| 3.2   | Bulk capacitor selection                   | 8  |

| 3.3   | Transformer design                         | 9  |

| 3.4   | Output capacitor selection                 |    |

| 3.5   | MOSFET selection                           |    |

| 3.5.1 | Primary MOSFET                             |    |

| 3.5.2 | ZVS MOSFET                                 |    |

| 3.5.3 | SR MOSFET                                  |    |

| 3.5.4 | SR IC selection                            |    |

| 3.6   | Snubber circuit design                     | 14 |

| 4     | Control diagram                            | 17 |

| 5     | IC parameter settings                      |    |

| 5.1   | HV pin-related parameters and functions    |    |

| 5.2   | ZCD pin-related settings and functions     |    |

| 5.2.1 | Output OVP function                        |    |

| 5.2.2 | $V_{cs}$ offset based on $V_{zcD}$         |    |

| 5.3   | Gate driver related settings and functions |    |

| 5.4   | MFIO pin-related parameters                |    |

| 5.5   | V <sub>cc</sub> pin-related parameters     |    |

| 5.6   | CS pin-related parameters                  | 21 |

### **Abstract**

| 6    | Burst mode operation              | 23 |

|------|-----------------------------------|----|

| 7    | Tips on PCB layout                | 24 |

| 8    | Usage of .dp Vision               | 25 |

| 8.1  | Installation of .dp Vision        |    |

| 8.2  | Parameter setting with .dp Vision |    |

| 9    | References                        | 30 |

| Revi | ision history                     | 31 |

### **Abstract**

#### 1 **Abstract**

Infineon's digital controller XDPS21081 is a multiple-mode zero voltage switching (ZVS) controller for a flyback converter, QR operation for low-line input, forced quasi-resonant (FQR) ZVS operation for high-line input. This design guide provides information on the ZVS principle of the flyback converter as well as related parameter settings. It gives a step-by-step design for power stage components with given specifications of a typical 65 W USB-PD adaptor design. The design equation can also be extended to other power ratings. Installation and usage of a graphical user interface (GUI) – .dp Vision – are covered, and customers will learn how to set IC parameters through the digital interface.

### Introduction

#### Introduction 2

#### **IC** introduction 2.1

The XDPS21081 [1] is a ZVS flyback current mode controller with built-in HV start-up cell. The start-up cell makes the IC power supply much more efficient and flexible during no-load operation. The DSP in the controller is like the brain of the chip, making the controller much smarter than a conventional mixed-signal hardware chip. The IC selects the most efficient operation mode depending on line input. For low-line input, it enables QR mode, and natural quasi-ZVS is achieved without current injection, reducing power loss. For highline input, it transfers to FQR ZVS mode, implemented by self-generated resonant oscillation. With medium or light load, it enables frequency reduction mode and configurable burst mode power to get the best efficiency across line and load regulation. In addition, a one-time programmable (OTP) unit is integrated to provide a wide set of programmable parameters to ease the design-in phase.

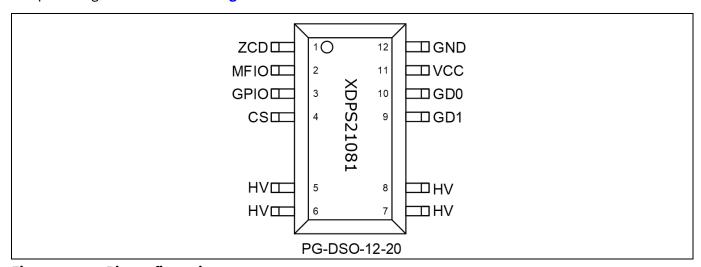

#### Pin configuration and description 2.2

The pin configuration is shown in Figure 1 and Table 1.

Figure 1 Pin configuration

### Introduction

Pin definitions and functions Table 1

| Symbol          | Pin        | Туре | Function                                                                                   |

|-----------------|------------|------|--------------------------------------------------------------------------------------------|

| ZCD             | 1          | 1    | Zero crossing detection                                                                    |

| 200             |            |      | The ZCD pin is connected to an auxiliary winding for zero crossing detection,              |

|                 |            |      | positive pin voltage measurement and also to insert V <sub>cs</sub> offset based on output |

|                 |            |      | voltage.                                                                                   |

| MFIO            | 2          | 1    | Multifunctional input output                                                               |

| IVII IO         |            |      | The MFIO pin is connected to an optocoupler that provides an amplified error               |

|                 |            |      | signal for PWM mode operation.                                                             |

| GPIO            | 3          | 10   | Digital general-purpose input output                                                       |

|                 |            |      | The GPIO pin provides a UART interface until brown-in. It is switched to weak              |

|                 |            |      | pull-down mode, and UART function is disabled during normal operation.                     |

| CS              | 4          | 1    | Current sense                                                                              |

|                 |            |      | The CS pin is connected via a resistor in series to an external shunt resistor and         |

|                 |            |      | the source of the power MOSFET.                                                            |

| HV              | 5, 6, 7, 8 | 1    | High voltage input                                                                         |

|                 |            |      | The HV pin is connected to the rectified bulk voltage. An internally connected             |

|                 |            |      | 600 V HV start-up cell is used for initial V <sub>CC</sub> charge. Brown-in and brown-out  |

|                 |            |      | detection are also provided.                                                               |

| GD1             | 9          | 1    | FQR ZVS signal gate driver output                                                          |

|                 |            |      | The GD1 pin provides a gate driver pulse signal to initiate FQR ZVS mode                   |

|                 |            |      | operation.                                                                                 |

| GD0             | 10         | 0    | Gate driver output                                                                         |

|                 |            |      | Output for directly driving the main power MOSFET.                                         |

| V <sub>cc</sub> | 11         | 1    | Positive voltage supply                                                                    |

|                 |            |      | IC power supply.                                                                           |

| GND             | 12         | 0    | Power and signal ground                                                                    |

#### **Product highlights** 2.3

- Integrated 600 V start-up cell for fast start-up and direct bus voltage sensing

- Adaptive CS compensation for USB-PD

- FFR mode

- High-precision line and load regulation

- Primary-side output overvoltage protection (OVP)

- Supports lowest no-load standby power

- One-pin UART interface for configuration

### Introduction

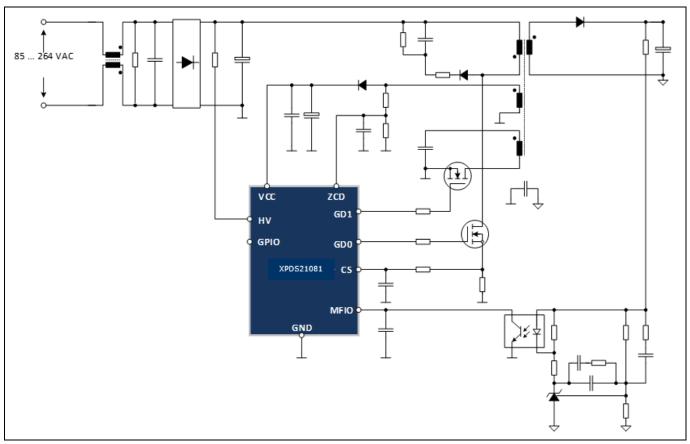

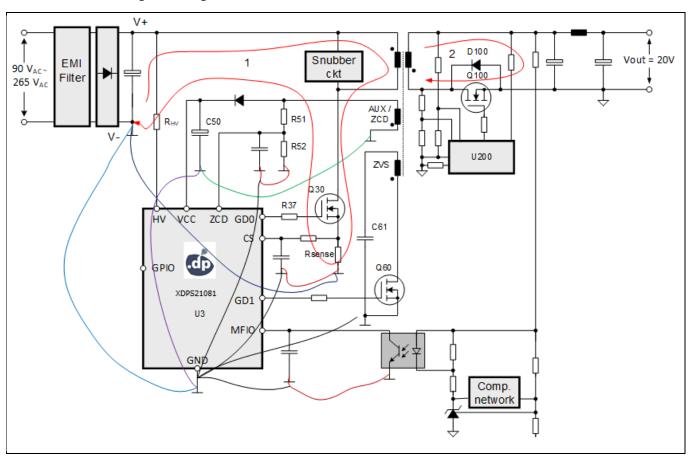

## 2.4 Simplified application diagram

Figure 2 Simplified application diagram

# 2.5 ZVS principles

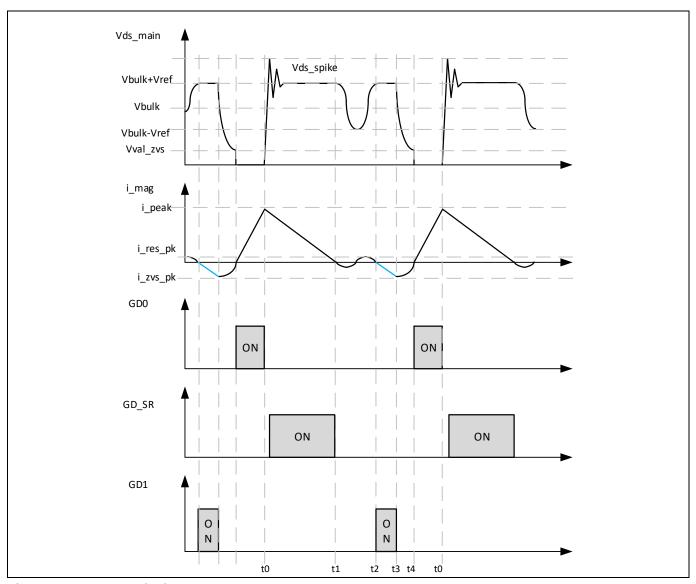

Figure 3 shows the typical PWM sequences and related key waveforms for the ZVS flyback.

After the primary MOSFET turns off at  $t_0$ , the synchronous rectifier (SR) MOSFET will turn-on, delayed by a short blanking time. At  $t_1$ , the SR MOSFET turns off when the demagnetizing current ideally goes to zero, then the magnetizing inductance  $L_p$  and  $C_{eqv}$  will oscillate. The voltage of the primary MOSFET will oscillate from  $V_{bulk+Vref}$  to  $V_{bulk-Vref}$ . If the auxiliary MOSFET is turned on at  $t_2$ , the resonant peak of the primary MOSFET will mean the magnetizing current is zero, then the  $i_{mag}$  will build up as negative. During this controlled ZVS on-time, the  $V_{DS}$  of the primary MOSFET is clamped to  $V_{bulk+Vref}$ . Once the peak current reaches  $i_{zvs\_pk}$ , the aux MOSFET is turned off, and because this current is stored in the magnetizing inductance and in the reverse direction, it will continue to flow in this direction and discharge the energy stored in  $C_{eqv}$ . This time duration in the IC is controlled by the  $t_{zvs\_dead}$  parameter, which is configurable. So at  $t_4$ , the drain voltage of the primary MOSFET reaches its minimum, and turns on the primary MOSFET, which reduces the turn-on losses significantly, which is almost ZVS. As seen in the diagram, the energy is proportional to  $V_{bulk}$ , and so is the ZVS on-time.

ZVS pulse insertion is based on nano-DSP core and memory info. The IC knows the next switching cycle period and ZVS dead-time and ZVS pulse on-time, so the switching period minus these two parts will decide the ZVS pulse starting point, assuming the IC main gate turn-on time is also fixed. When the CS signal reaches the current command, the main gate off-point can also be decided.

## Introduction

Figure 3 ZVS principles

### Flyback power stage design

#### Flyback power stage design 3

#### 3.1 65 W adaptor system specifications

Table 2 shows the simplified system specs for the nominal 65 W adaptor. Only the key specs are included here to dimension the power train components such as the bulk capacitor, transformer and MOSFETs.

Table 2 65 W adaptor system specifications

| Descriptions          | Symbol              | Value        | Unit | Test conditions                              |

|-----------------------|---------------------|--------------|------|----------------------------------------------|

| Input AC voltage      | V AC                | 90 to 264    | V AC |                                              |

| Input AC frequency    | f <sub>line</sub>   | 50/60        | Hz   |                                              |

| Output voltage        | V <sub>out</sub>    | 5/9/12/15/20 | V    |                                              |

| Output voltage ripple | $\Delta V_{out}$    | 150          | mV   | From 5 V to 20 V under steady-<br>state load |

| Nominal output        | I <sub>outnom</sub> | 3            | Α    | 3 A for voltage below 20 V                   |

| current               |                     | 3.25         | Α    | 3.25 A for 20 V output                       |

#### 3.2 **Bulk capacitor selection**

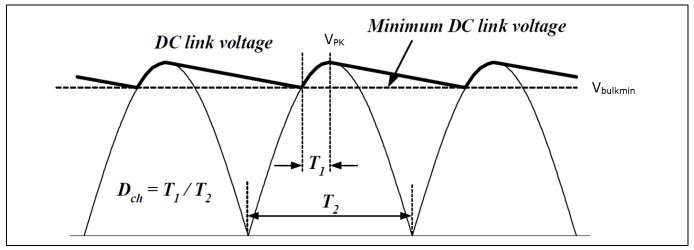

Figure 4 shows the typical waveforms after the rectification bridge with a large bulk capacitor. T1 is the conduction period of the rectifier bridge diode. During this timeframe, input AC voltage will charge the bulk capacitor, and the rest of the time is the discharging of the bulk capacitor. The difference between the energy stored in the bulk capacitor is equal to the output power times (T2 to T1).

The conducting period can be calculated using the following equation:

$$T_1 = T_2 \times \frac{\frac{\pi}{2} - sin^{-1} \frac{V_{bulkmin}}{V_{pk}}}{\pi}$$

(1)

Where T2 is the period of the rectified sine waveform, i.e. T<sub>line</sub>/2, V<sub>pk</sub> is the AC peak input voltage, and V<sub>bulkmin</sub> is the minimum voltage of the bulk capacitor.

The energy discharged from the bulk capacitor during the rectifier off-period is:

$$C_{energy} = 0.5 \times C_{bulk} (V_{nk}^2 - V_{bulkmin}^2) \tag{2}$$

This energy should be equal to the input power times of the off-period, so we get the following equation:

$$P_{out} \div \eta \times (T_2 - T_1) = C_{energy} \tag{3}$$

Using equations (1), (2)(1) and (3), with given line frequency and AC input voltage, either the value of the bulk capacitor or the minimum bulk voltage can be calculated once one variable is fixed.

Here we choose  $C_{\text{bulk}}$  120  $\mu F$  as an example, with the given power requirement in **Table 2**, giving the minimum bulk voltage shown in Table 3.

### Flyback power stage design

Figure 4 Bulk capacitor voltage after rectification

Table 3 V<sub>bulk</sub> minimum voltage at max. load

| V <sub>in</sub> (V AC) | Freq. (Hz) | V <sub>out</sub> (DC) | I <sub>out</sub> (A) | P <sub>out</sub> (W) | Eff. η | V <sub>bulkmin</sub> (DC) |

|------------------------|------------|-----------------------|----------------------|----------------------|--------|---------------------------|

| 90                     | 47         | 20                    | 3.25                 | 65                   | 0.94   | 85                        |

Using 120 μF for the bulk capacitor value, the minimum V<sub>bulk</sub> 85 V appears at 90 V AC/47 Hz with 3.25 A loading.

#### 3.3 Transformer design

Now, with the minimum bulk capacitor voltage information at different AC-line/frequency and output power, we will be able to design the transformer of the flyback converter. According to the XDPS21081 operation scheme, the system will operate at QR/boundary mode at low-line (90 V AC/47 Hz) at maximum 65 W. Since the gate drive signal is only available when zero crossing (ZC) is detected, during overload condition, the on-time will be increased and also the off-time, so switching frequency will be reduced. The transformer design will need to guarantee that flux density B<sub>max</sub> is below saturation level while the wire size only caters for nominal power to handle the thermal issue.

Reference [2] shows how to design the inductance in critical mode operation. The relevant equations are (4) and (5).

$$L_p \cdot i_{pk} \left( \frac{1}{V_{bulk}} + \frac{1}{V_{refl}} \right) + 0.5 \cdot T_r = \frac{1}{f_{sw}}$$

$$\tag{4}$$

$$0.5 \cdot L_p \cdot i_{pk}^2 \cdot f_{sw} \cdot \eta = P_{out} \tag{5}$$

**Table 4** shows the calculated inductance will be 200  $\mu$ H, and primary-side peak current is 3.05 A at 20 V/3.25 A output.

Calculated inductance and peak current Table 4

| F <sub>sw</sub> (kHz) | T <sub>r</sub> (μs) | V <sub>ref</sub> (V DC) | V <sub>bulk</sub> (V DC) | P <sub>out</sub> (W) | η    | L <sub>ρ</sub> (μΗ) | I <sub>pk</sub> (A) |

|-----------------------|---------------------|-------------------------|--------------------------|----------------------|------|---------------------|---------------------|

| 75                    | 1.6                 | 112                     | 85                       | 65                   | 0.94 | 200                 | 3.05                |

### Flyback power stage design

The next thing to do is decide the transformer turns based on the selected core shape/material,  $B_{\text{max}}$ . Core loss and copper loss are the main considerations here.

$$B_{max} = \frac{L_p \cdot i_{pk}}{N \cdot A_e} \tag{6}$$

Equation (6) shows the delta flux density or peak flux in DCM, where N is the primary turns of the transformer, and  $A_e$  is the effective flux area of the core.

**Table 5** shows the peak current and maximum flux density under maximum load based on the selected PQ20/16 core.

Table 5 Peak current and B<sub>max</sub> under different output voltages

| V <sub>in</sub> (AC) | P <sub>out</sub> (W) | V <sub>out</sub> (V) | V <sub>bulk</sub> (V DC) | I <sub>pk</sub> (A) | L <sub>թ</sub> (μΗ) | Np | A <sub>e</sub> (mm <sup>2</sup> ) | B <sub>max</sub> (T) |

|----------------------|----------------------|----------------------|--------------------------|---------------------|---------------------|----|-----------------------------------|----------------------|

| 90                   | 65                   | 20                   | 85                       | 3.05                | 200                 | 28 | 62                                | 0.34                 |

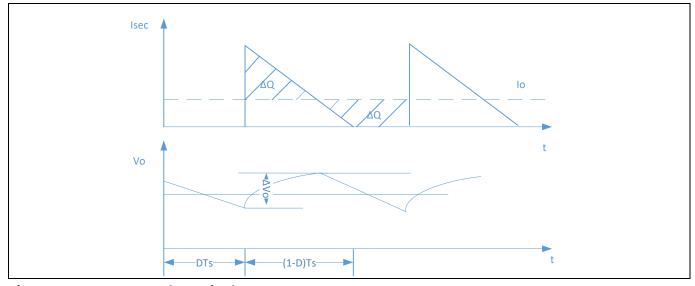

## 3.4 Output capacitor selection

One consideration when selecting the output capacitor value is based on the ripple requirement. The required ripple is 150 mV. The ripple has two parts: one is the current charge to the output capacitor; the other is dominated by the ESR of the capacitor. **Figure 5** shows the current charge output capacitor for the flyback converter.

Part 1 voltage ripple is calculated using the following equation:

$$\Delta V_{o_{-1}} = \frac{\Delta Q}{C} = \frac{(Ipk_{sec} - I_o)^2 * I_o * T_{sw}}{Ipk\_sec^2 * C}$$

(7)

Part 2 voltage ripple is calculated using the following equation:

$$\Delta V_{o\_2} = esr \cdot I_{ac} = esr \cdot \sqrt{i_{pk}^2 - i_o^2}$$

(8)

Total output voltage ripple is the sum of  $\Delta V_{o_1} + \Delta V_{o_2}$ .

Figure 5 Output voltage ripple

### Flyback power stage design

Output ripple calculation under 20 V/3.25 A Table 6

| $\Delta V_{o\_spec}$ (mV) | I <sub>pk_sec</sub> (A) | T <sub>sw</sub><br>(μS) | C<br>(μF) | $\Delta V_{o_{-1}}$ (mV) | ESR<br>(mΩ) | I <sub>out</sub><br>(A) | I AC<br>(A) | $\Delta V_{o\_2}$ (mV) |

|---------------------------|-------------------------|-------------------------|-----------|--------------------------|-------------|-------------------------|-------------|------------------------|

| 150                       | 3.05 x 5.6              | 13.33                   | 1222      | 23                       | More than 5 | 3.25                    | 16.77       | More than 84           |

**Table 6** shows the total ripple is (23 + 84) = 107 mV, which meets the requirements. The selected output capacitors are polymer capacitors plus multiple-layer ceramic capacitors, two 470 μF/25 V polymer capacitors and six 47  $\mu$ F/25 V multiple-layer ceramic capacitors.

#### 3.5 **MOSFET selection**

#### 3.5.1 **Primary MOSFET**

The superjunction MOSFET is the popular, HV discrete component used nowadays in AC-DC conversion. The latest CoolMOS™ P7 [3] technology shows the best Q<sub>G</sub> x R<sub>DS(on)</sub> figure-of-merit (FOM), and fast turn-off speed, which reduces the turn-off losses, so it is best suited to this design.

Based on the transformer design, the turns ratio is 5.6, so we can estimate the maximum voltage stress of the primary MOSFET based on the following equation. Derating is the most important consideration when selecting MOSFETs.

$$V_{ds} = V_{in} + V_{clamp}$$

So the maximum voltage rating during steady-state happens with maximum input RMS AC voltage, i.e. 264 V AC.

$V_{DS} = 264 \times 1.414 + V_{clamp}$ , with a 600 V MOSFET; the  $V_{clamp}$  should be kept below 227 V DC. This means properly dimensioning the snubber circuit is important, because the ZVS topology shown here will still have a turn-off spike caused by the energy in the leakage inductance.

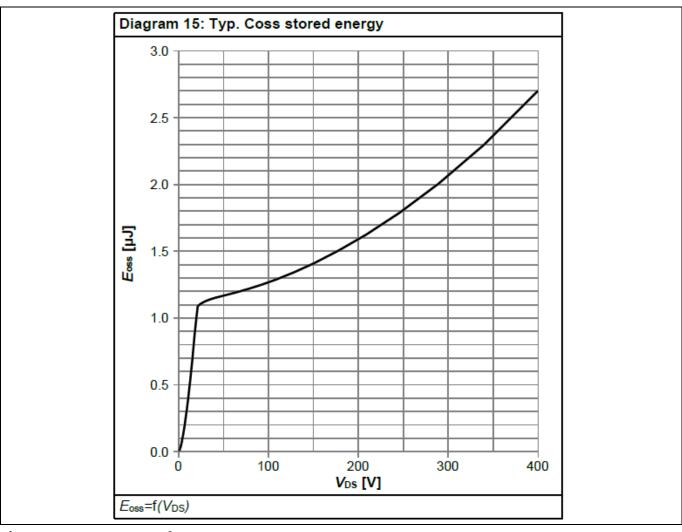

The other selection consideration for the primary MOSFET is its R<sub>DS(on)</sub> value; usually conduction loss is the main concern at low-line, which is the worst case. A low R<sub>DS(on)</sub> MOSFET is preferred, but this means greater C<sub>oss</sub>, and it also means more turn-on losses at high-line for conventional hard-switching or even QR flyback. With ZVS technology, we now can choose a low R<sub>DS(on)</sub> MOSFET to optimize the conduction losses while maintaining low losses at high-line.

As already known, different MOSFETs have different RDS(on) and Qoss combinations, and Qoss will need certain energy from the auxiliary winding to discharge it. Again, it is a trade-off between the losses gained and dissipated in term of system optimization.

Let us estimate the losses stored in the MOSFET junction capacitor at 230 V AC, considering the reflection voltage 112 V DC; the plateau of the primary MOSFET V<sub>DS</sub> will be 230 x 1.414 + 112 = 437 V DC, while from the IPL60R185C7 datasheet  $C_{oss}$  curve, we find that from 400 V DC to 40 V DC, the  $E_{oss}$  change is  $(2.7 - 1.1) \mu J$ , with 120 kHz switching frequency, which means power loss is  $E_{oss}$  x  $F_{sw}$  = 1.6 x 120 = 192 mW. We notice that from 40 V DC to zero, the  $E_{oss}$  is around 1.1  $\mu$ J, which means 132 mW is needed to discharge from 40 V to zero. So when considering efficiency, the optimum turn-on point for the primary MOSFET is not really zero voltage; it should be around 40~50 V DC for CoolMOS™.

### Flyback power stage design

E<sub>oss</sub> curve of IPL60R185C7 Figure 6

Based on these considerations, **IPL60R185C7** is chosen.

The conduction losses of the primary MOSFET at 20 V output and 3.25 A loading at 100°C junction temperature

$$\mathsf{P}_{\mathsf{cond}} = i_{rms}^2 \cdot R_{dson} = \left( \sqrt{D/3} \cdot i_{pk} \right)^2 \cdot R_{dson} = \left( \sqrt{0.53/3} \cdot 3.05 \right)^2 \cdot 0.25 = 0.414W$$

#### 3.5.2 **ZVS MOSFET**

The transformer has one additional winding at the primary. This winding provides the energy to discharge the primary MOSFET's equivalent Coss by controlling the on-time of the ZVS MOSFET. The designed transformer has  $N_{DZ} = N_D$ :  $N_{ZVS} = 28:2$  turns ratio, so similarly the  $V_{DS}$  stress of this MOSFET can be calculated with  $V_{inmax}/N_{DZ} + V_{ZVS} =$ 374 V/14 + 8 V = 34.7 V. Considering the voltage spike, the voltage rating should be at least 60 V. Because this MOSFET only handles low energy, a small-signal MOSFET can be chosen. Here we choose **BSL606SN**.

### Flyback power stage design

#### 3.5.3 **SR MOSFET**

The secondary-side SR MOSFET selected is the OptiMOS™ 5 series, considering the best FOMgd and FOMoss.

Based on the turns ratio  $N_{ps}$  = 28:5, the MOSFET rating will be 374 V/5.6 + 20 = 86.8 V. Due to the ZVS turns on the primary side, hardly any spike is seen at the output SR MOSFET in ZVS mode. So 100 V rating is chosen. Here we choose BSC0802LS.

The RMS current in the secondary SR MOSFET is:

$$i_{rms} = \sqrt{D_{off}/3} \cdot i_{pksec} = \sqrt{\frac{0.41}{3}} \cdot 3.05 \cdot 5.6 = 6.31A$$

The conduction loss of the SR MOSFET is:  $i_{rms}^2 R_{DS(on)} = 6.31^2 0.0032 \Omega = 0.127 W$

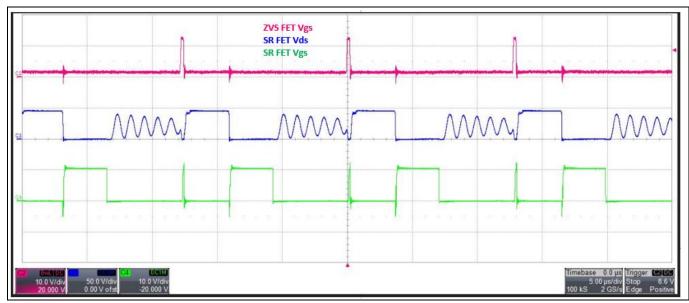

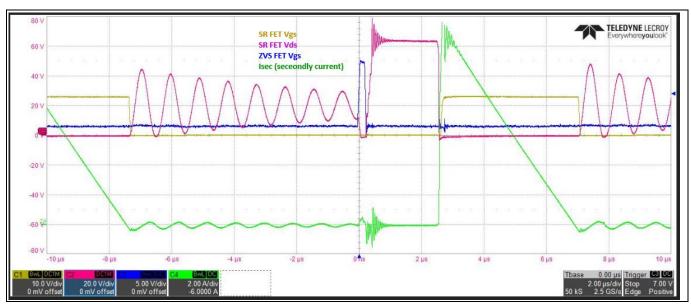

#### 3.5.4 **SR IC selection**

When the ZVS pulse is turned on, the SR V<sub>DS</sub> will also drop below zero voltage. It will tend to mistrigger the V<sub>DS</sub> direct sensing SR IC, as shown in Figure 7. While using the voltage balance SR IC as shown in Figure 8, due to the SR arming function, there is no mis-triggering of the SR gate. For SR IC with direct sensing without arming function, the minimum on-time needs to be set to minimum, e.g., 50 ns, and the minimum on-time should be shorter than the primary ZVS on-time, otherwise shoot-through between primary and secondary will happen as soon as the primary main MOS turns on, then the primary MOS could be damaged. Here, it is worth mentioning CYPD3184, which is V<sub>DS</sub> direct sensing SR IC plus PD protocol. Each time CYPD3184 drives the SR MOS, it will calculate the product of V<sub>DS</sub>\*T<sub>off</sub> first, and it drives the SR MOS only if the calculated V<sub>DS</sub>\*T<sub>off</sub> exceeds the setting threshold, so it can avoid mis-triggering the SR gate. Any other SR IC feature with calculation of V<sub>DS</sub>\*T<sub>off</sub> is highly recommended.

Figure 7 SR gate signal witds direct sensing SR controller

### Flyback power stage design

SR gate signal with voltage-second balance SR controller Figure 8

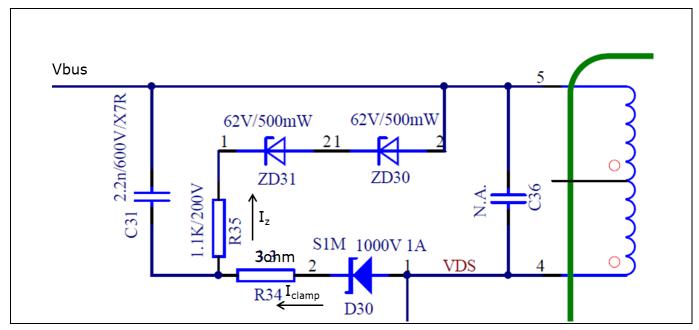

#### **Snubber circuit design** 3.6

When the primary MOSFET turns off, the energy stored in leakage inductance will cause significant ringing at the drain node. This ringing must be clamped to keep the MOSFET within a safe operating range. A Zener clamp circuit as shown in Figure 9 is chosen, as it has high efficiency at light load since the Zener clamp will never conduct, so there is no residual resistor loss compared to an RCD snubber. This is the snubber circuit used in the 65 W demo board. In general, the energy that goes into the snubber circuit is leakage inductance stored energy. Depending on the D1 type, the losses will be different. Due to the reverse recovery characteristic, the current entering the clamp capacitor can return to the output side, and part of the energy is recovered to the input or output.

Figure 9 **Snubber circuit**

### Flyback power stage design

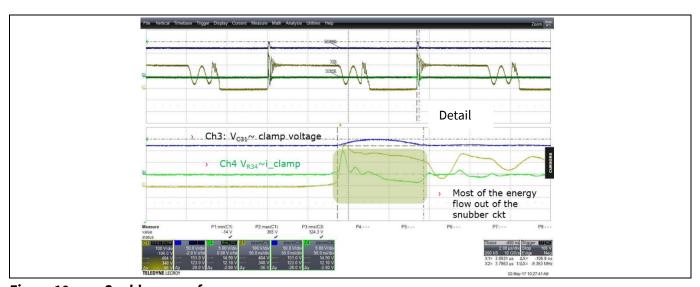

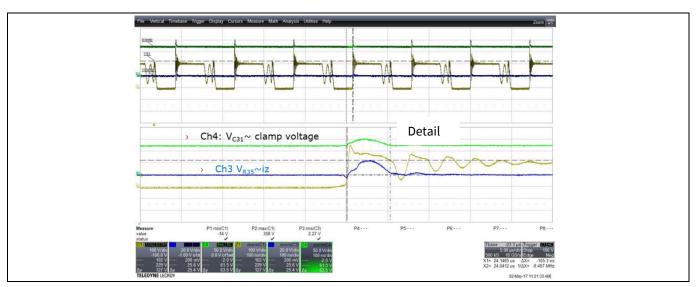

Figure 10 and Figure 11 show the snubber current and clamp voltage waveforms when the MOSFET turns off.

In reality, there is reverse recovery of the snubber diode, as shown in **Figure 10**, which means not all the current into the snubber capacitors is lost; the longer the recovery, the lower the losses that can be achieved.

Table 7 shows the calculation results of energy entering the snubber tank during turn-off, which is around 1.16 W. Figure 10 also clearly shows that after the snubber diode current goes in the negative direction, the clamp voltage begins to decay.

This means not all the energy into the tank is lost, and the clamp voltage returns to the steady-state. Because the current returns to negative, the only way for this current path is to flow out of the dot terminal of the secondary-side transformer and partially to the output. So this energy is not fully dissipated.

**Table 8** shows the losses in the Zener clamp, based on the measured waveforms. The power loss is calculated using 0.5 x I<sub>z</sub> x V<sub>Zener clamp</sub> x duration x F<sub>sw</sub>. It shows only 21 mW is dissipated in the Zener diode.

Table 7 **Energy entering the snubber tank**

| V <sub>clamp_bottom</sub> (V) | V <sub>clamp_peak</sub> (V) | C <sub>clamp</sub> (nF) | F <sub>sw</sub> (kHz) | P <sub>enter_snubber</sub> (W) |

|-------------------------------|-----------------------------|-------------------------|-----------------------|--------------------------------|

| 123                           | 151                         | 2.2                     | 137                   | 1.16                           |

Power loss in the Zener diode Table 8

| I <sub>Zener</sub> (mA) | V <sub>Zener_clamp</sub> (V) | Time (ns) | F <sub>sw</sub> (kHz) | P <sub>Zener_dissipate</sub> (mW) |

|-------------------------|------------------------------|-----------|-----------------------|-----------------------------------|

| 23                      | 130                          | 105       | 137                   | 21                                |

Figure 10 **Snubber waveforms**

# Flyback power stage design

Figure 11 **Snubber waveforms**

### **Control diagram**

#### **Control diagram** 4

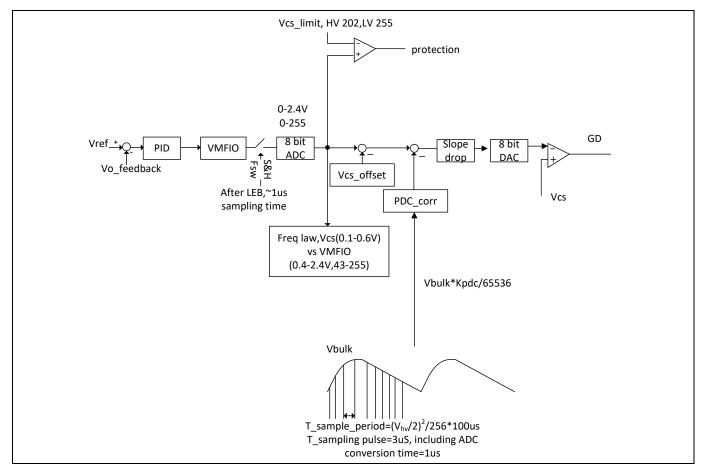

Figure 12 shows the control diagram of XDPS21081.

The secondary-side control feedback signal feeds into the MFIO pin through the optocoupler, and this signal is sampled after leading-edge blanking (LEB) time every switching cycle and converted into a digital number by an 8-bit ADC, which takes around 1 µs. Based on this MFIO value, frequency and peak current will be picked up from the frequency law reference table. This value will be compared to the CS limit to see if maximum power is reached. If yes, after 31.3 ms blanking time, the IC will enter overload protection (OLP).

If not, the digital CS signal will be taken away from the V<sub>cs</sub> offset, PDC correction, and feed into the 8-bit DAC to convert back to an analog signal. It compares with the CS shunt resistor to form the classical current mode control.

The V<sub>cs</sub> offset value is calculated based on output voltage, which means the maximum usable current command will be different for variable output voltage, and therefore it will have different output power. For calculation details please refer to 5.2.2.

The propagation delay correction is to compensate for propagation delay influenced by the slew rate of the CS signal. For example, PDC =  $V_{in}/L_p$  x  $T_{delay}$ , where  $V_{bulk}$  is the bulk capacitor voltage,  $L_p$  is main inductance, and  $T_{delay}$ includes both IC internal (~100 ns) and external MOSFET turn-off delay. The detailed calculation can be found in 5.6.

Overall control diagram Figure 12

### IC parameter settings

# 5 IC parameter settings

## 5.1 HV pin-related parameters and functions

The HV pin provides the start-up and bulk capacitor voltage sensing. The sensed voltage information will provide input power estimation and ZVS on-time adjustment. The brown-in/out function is also based on the HV pin, but on the current level.

The internal 600 V depletion start-up cell provides the charging current to the V<sub>CC</sub> pin.

The charging current is calculated as  $i_{hv}(t) = \frac{V_{bulk} - V_{cc}(t)}{R_{hv}}$ , so it can be seen with a fixed HV pin external resistor, and the charging current will change proportionally with input AC-line voltage.

The start-up delay time needed is the time spent charging the  $V_{CC}$  capacitor before reaching the  $V_{CCon}$  threshold 20.5 V.  $t_{delay} = C_{vcc} \cdot \frac{vcc_{on}}{i_{hv}-i_{lk}}$ ,  $i_{lk}$  is the HV pin leakage current before power-up, stated in the datasheet specifications, typically ~10  $\mu$ A.

When the  $V_{CC}$  is above 9 V, if the current flowing into the HV pin is greater than 1.156 mA, the IC starts switching. If the current is below 0.443 mA, the IC will stop switching after 1.06 ms.

So based on this current limit and the 100 k $\Omega$  HV pin resistor, we will see the brown-in voltage is  $V_{brownin} = I_{hvbi} x$   $R_{hv} + I_{hvbi} x 1.49 = 1.156$  mA x  $(100 \text{ k}\Omega + 1.49 \text{ k}\Omega) = 117.32$  V DC.

The brown-out voltage is  $V_{brownout} = I_{hvbo} \times R_{hv} + I_{hvbo} \times 0.99 = 0.443 \text{ mA} \times (100 \text{ k}\Omega + 0.99 \text{ k}\Omega) = 44.7 \text{ V DC}$ .

The other functions of V<sub>bulk</sub> are used to tune the ZVS on-time and input power estimation. The current flow into the HV pin is not enough to get the voltage information, as it is also decided by the external HV pin resistor.

# 5.2 ZCD pin-related settings and functions

# 5.2.1 Output OVP function

The ZCD pin provides zero crossing detection in DCM and output voltage sensing during off-time. This pin's negative voltage is clamped to -0.2 V during the primary MOSFET's on-time.

$$V_{zcd} = \frac{N_{aux}}{N_s} \cdot \frac{R_l}{R_h + R_l} \cdot V_o < Vo_{ovpthr}$$

(9)

$$i_{zcd} = \frac{-0.2 + \frac{N_{aux}}{N_p} v_{bulkmax}}{R_h} \le 3.5 mA$$

(10)

$R_h$  determines the current flowing out of the ZCD pin, based on designed  $N_{aux}$  and  $N_s$ .  $R_h$  will be selected first based on the current limit of the ZCD pin. Once  $R_h$  is chosen, based on the OVP requirement and  $V_{ZCD}$  OVP threshold,  $R_l$  can be calculated.

Based on  $N_{aux}$  = 5,  $N_p$  = 28,  $V_{bulkmax}$  = 374 V, from equation (10),  $R_h$  is greater than or equal to 19.02 k $\Omega$ , and here we choose 39 k $\Omega$ .

The next thing is to decide the value of  $R_l$  based on equation (9) and the OVP requirement,  $N_s = 5$ ,  $R_h = 39 \text{ k}\Omega$ ,  $V_{\text{outovpthr}} = 2.75 \text{ V}$ ,  $V_{\text{outovp}} = 21.7 \text{ V}$ ,  $R_l = 5.6 \text{ k}\Omega$ .

To filter noise at the ZCD pin, a small capacitor such as 10 pF can be paralleled to the low-side resistor.

### IC parameter settings

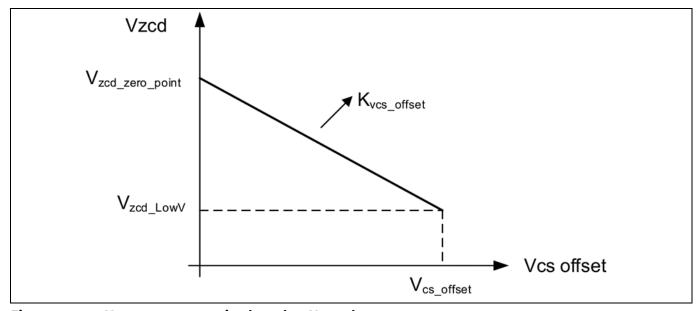

### 5.2.2 $V_{CS}$ offset based on $V_{ZCD}$

**Figure 13** shows the  $V_{CS}$  offset based on  $V_{ZCD}$ , while the ZCD voltage corresponds to the output voltage. The purpose of this compensation is to reduce the current command for different output voltages, so the maximum allowed power can be reduced. This feature is especially important for variable-output voltage applications when the system is dimensioned at full power at the highest voltage. So the power can be reduced at lower output voltages to meet limited power supply (LPS) requirements.

ZCD pin voltage is from 1.2 V to 2.8 V, with the gain 1.5; this voltage is converted to the digital value internally with an 8-bit ADC.

The calculation procedure is to decide the zero point of V<sub>ZCD</sub>; above this threshold, there is no compensation.

Second, based on the targeted compensation value, calculate K<sub>vcs\_offset</sub>.

The output voltage:

$$Vzcd_{zeropoint} = \frac{Rl}{Rl + Rh} * \frac{Naux}{Ns} * Vo\_zero\_point$$

(11)

Here we choose  $V_{o\_zero\_point} = 13.5 \text{ V}$ , with known  $R_l = 5.6 \text{ k}\Omega$ ,  $R_h = 39 \text{ k}\Omega$ ,  $N_{aux} = 5$ ,  $N_s = 5$ ,  $V_{ZCDzeropoint} = 1.7 \text{ V}$ .

The digital number  $V_{ZCD\_dig\_zeropoint} = (V_{ZCD\_zeropoint} - 1.2) \times 1.5/2.4 \times 255 = 79$ ; this parameter can be set in the .dp Vision GUI.

Next is to decide the target compensation value, e.g., 53 mV at  $V_{ZCD}$  = 1.2 V, so the compensated digital value of  $V_{CS\_dig}$  = 53 mV/0.4 V x 255 = 34, then  $K_{vcs\_offset}$  =  $V_{CS\_dig}$ /(0- $V_{ZCDzeropoint}$ ) x 65535 = 28240, and this slew rate is also a configurable parameter in the .dp Vision GUI.

Figure 13  $V_{CS\_offset}$  compensation based on  $V_{ZCD}$  voltage

# 5.3 Gate driver related settings and functions

The two gate drivers are double-loop controlled, with external current loop and internal voltage loop. The default sourcing current is 35 mA (GD0), 118 mA (GD1) and 10.5 V clamp. The sink capability of the internal discharge path is limited by internal equivalent resistance less than or equal to 6.5  $\Omega$ , so the maximum sink current is 10.5 V/6.5  $\Omega$  = 1.6 A if there is no external serial resistor adopted.

### IC parameter settings

Unlike the conventional voltage source-based driver, only one gate resistor is needed to limit the sink current. Generally a 10  $\Omega$  or lower gate resistor is used, and this should be tuned based on switch-off losses versus turnoff speed.

GD0 is the gate driver for the primary main MOSFET. GD1 is for the ZVS MOSFET.

There are two configurable parameters that can tune ZVS MOSFET on-time. Tuning this parameter is necessary since the parasitic capacitor varies with different Coss of the primary MOSFET, SR MOSFET and parasitic coupling capacitor of the transformer.

$$t_{GD1on} = \left(V_{bulk} * \frac{K_{zvson}}{65535} \frac{1}{V} + 2\right) * 15.8ns + (2.34V - V_{zcd}) * \frac{K_{zvson_{vout}}}{65535} * \frac{1}{V} * 15.8ns$$

(12)

V<sub>bulk</sub> is measured through the HV pin and reflects bulk input voltage. V<sub>zcd</sub> reflects power supply output voltage V<sub>out</sub> and is proportional to V<sub>out</sub>. According to equation (12), ZVS MOS on-time t<sub>GD1on</sub> is proportional to V<sub>bulk</sub> and reverse proportional to V<sub>out</sub>.

The energy stored in the magnetizing inductance needed to discharge the equivalent capacitor energy of the primary MOSFET is like this:

$$0.5 \cdot L_p \cdot i_{neg}^2 > 0.5 \cdot C_{eqv} \cdot V_{ds}^2 \tag{13}$$

$$i_{zvs\_pk} = \frac{N_p}{N_{zvs}} \cdot \frac{V_{zvs}}{L_p} \cdot t_{GD1on} \tag{14}$$

Required dead-time is:

$$t_{ZVSdead} = \frac{Q_{oss}}{i_{zvs\ pk}} \tag{15}$$

There is also a configurable parameter t<sub>ZVSdead</sub> that can be tuned for required dead-times based on system parameters.

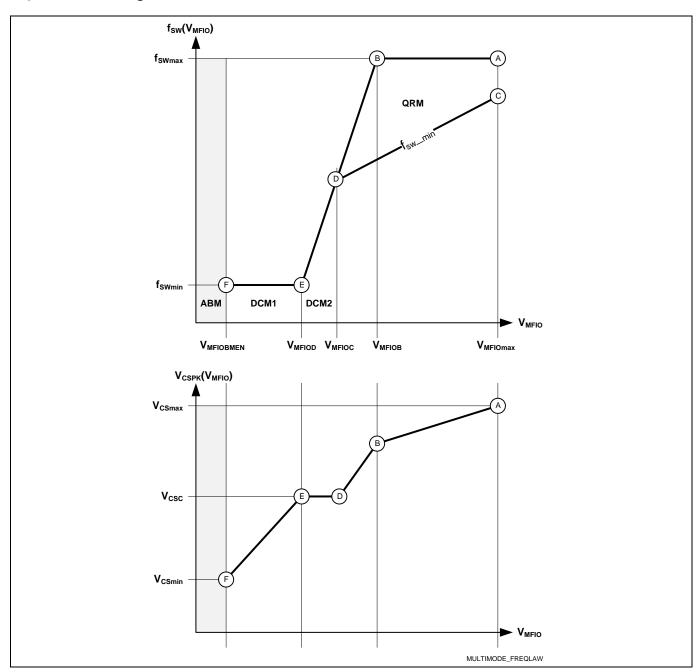

#### 5.4 MFIO pin-related parameters

The MFIO pin provides the feedback information for the IC. Based on the voltage measured at the MFIO pin, the IC will check the reference table to get the desired frequency or frequency band and current limit command. The MFIO pin represents the loading directly, so the IC can also choose the operation mode (QR/FQR ZVS, DCM, burst mode) based on the MFIO voltage level.

### **IC parameter settings**

Figure 14 Frequency law configuration

#### **Vcc pin-related parameters** 5.5

V<sub>CC</sub> provides the operating voltage of the IC and also has undervoltage lockout (UVLO) protection when V<sub>CC</sub> drops below 7.2 V. Brown-in is activated when V<sub>CC</sub> is above 9 V.

V<sub>cc</sub> also has a V<sub>cc</sub> OVP function, 21.8 V (typ.).

#### 5.6 **CS pin-related parameters**

The CS pin's main functions are current mode control and overcurrent protection (OCP). For the current command, it is influenced by propagation delay compensation (PDC), V<sub>CS\_offset</sub>, and these parameters can be tuned according to different system dimensions.

### IC parameter settings

The current command is given by equation(16):

$$CS\_OCP1LVL = (Ipk) - PDC\_Correction - Vcsoffset$$

(16)

$$PDC\_Correction = INT(2^{-16} * PDC_{FACTOR} * Vbulk + PDCOFFSET)$$

(17)

Where PDC<sub>FACTOR</sub> and PDC<sub>OFFSET</sub> are two configurable parameters using .dp Vision – propagation delay-related parameters.

$$PDC_{FACTOR} = \frac{R_{CS} \cdot t_{PD}}{L_p \cdot V_{CSlsb8}} \cdot (2^{16} - 1)$$

$$\tag{18}$$

$$\mathsf{PDC}_{\mathsf{FACTOR}} = \frac{R_{\mathit{CS}} \cdot t_{\mathit{PD}}}{L_p \cdot V_{\mathit{CSlsb8}}} \cdot (2^{16} - 1) = \frac{0.135 ohm \cdot 352 ns}{200 \mu H \cdot 2.34 mV} \cdot 65535 = 6654$$

Actually, the default PDC<sub>FACTOR</sub> for XDPS21081 is 9000, default PDC<sub>OFFSET</sub> is 0, so PDC\_correction = 9000 x 85 V/65535 + 0 = 9 bits, each bit is 2.34 mV, so PDC-induced  $V_{CS}$  reduction is 2.34 mV x 9 = 21 mV.

Where R<sub>CS</sub> is the current sense resistor, t<sub>pd</sub> is the propagation delay, which includes internal comparator delay and external turn-off delay, Lp is the main inductance value, and Vcsisb8 is the DAC lsb of the CS signal.

As maximum  $V_{CS}$  at low-line is 0.4 V, so  $R_{CS} = (400 \text{ mV} - 21 \text{ mV})/I_{pk} = 0.232 \text{ V}/3.05 \text{ A} = 0.125 \Omega$ . As we see in the calculation procedure, the PDC calculation is influenced by Rcs, which is unknown before we get the final R<sub>CS</sub> value, and also the propagation delay needs to be calibrated. And peak current calculations are also influenced by the efficiency assumption, etc., so R<sub>CS</sub> would be tuned slightly to tailor it to a real design based on real test results. In the 65 W reference board,  $R_{CS} = 0.135 \Omega$  is chosen.

### **Burst mode operation**

#### **Burst mode operation** 6

To maintain efficiency at light load, the IC needs to keep the system working in burst mode. XPDS21081 will stop the core engine and reduce power consumption depending on feedback voltage, which reflects load signal. Table 9 shows the burst mode entry level. Different MFIO voltage means different peak current based on frequency.

Table 9 Burst mode entry level per V<sub>ZCD</sub>

| Burst mode entry | Symbol                | Min.  | Тур.  | Max.  | Unit |

|------------------|-----------------------|-------|-------|-------|------|

| threshold        | V <sub>MFIOBMEN</sub> | 0.175 | 0.209 | 0.242 | V    |

Burst mode operation power is defined as follows:

$$P_{bst} = 0.5 * L_p * I_{pk}^2 * F_{bst}$$

(19)

Based on default  $V_{CS}$  in burst mode 78 mV, the peak current is 78 mV/0.135  $\Omega$  = 0.578 A,  $f_{bst}$  = 23 kHz. With known inductance, the burst mode power can be calculated.

**Tips on PCB layout**

### **Tips on PCB layout** 7

In principle, there are two key switching loops, which need to be as small as possible. One is from bulk capacitor V+ to transformer winding to Q30 to R<sub>sense</sub> to bulk capacitor V-. The other is the secondary-side rectification loop from the secondary transformer winding to the output filter capacitor and Q100 SR MOSFET.

For XDPS21081 ground connection, star ground to bulk capacitor negative V- is necessary. The ZCD winding's ground should connect to filtering capacitor C50 first, then all other pins' grounds should tie to this IC's ground first before connecting to C50's ground.

Figure 15 System layout recommendation

infineon

**Usage of .dp Vision**

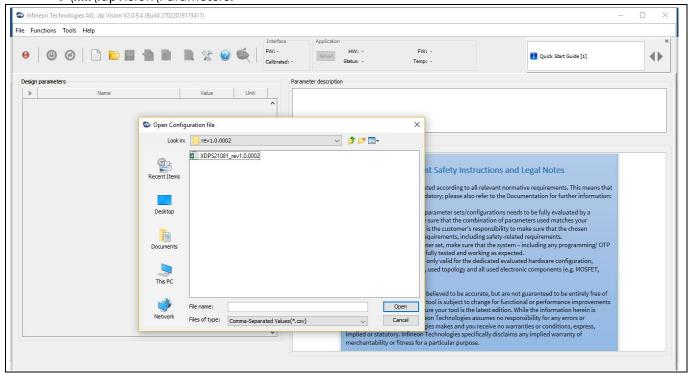

# 8 Usage of .dp Vision

# 8.1 Installation of .dp Vision

Customers can install the user interface .dp Vision on their own computer, following the installation instructions.

- 1) Install the latest .dp Vision\_2.0.9.4 from the folder (double-click "dpVision\_2.0.9.4.msi").

- 2) Connect the IFX IDP21081 sample to the **dpIFGen2** interface board using V<sub>CC</sub>, UART and GND pins.

Figure 16 dpIFGen2 interface board (side view)

3) Connect the **dpIFGen2** interface board using the USB cable provided to the laptop USB port and open the .dp Vision GUI by double-clicking on "dpVision.exe" or the icon shown below.

Figure 17 .dp Vision icon

### **Usage of .dp Vision**

4) Open "XDPS21081\_with\_assistant\_trials\_rev1.07.csv" using menu → File → Open → browse to folder →\.....\.dpVision\Parameters.

Power device on/off button and device status Figure 18

5) Press the power device on/off button  $\rightarrow$  device status should turn green.

Power device on/off button and device status

6) Press the "Test Configuration Set" button and the parameter values are loaded in the XDPS21081 sample and the application firmware starts running.

# Usage of .dp Vision

7) Change the parameters under the "Value" field.

| Hardware Configuration   | _ |              |         |

|--------------------------|---|--------------|---------|

| P_EFF                    |   | 90           | %       |

| R_CS                     |   | 0.120        | ohm     |

| Control Feature          |   |              |         |

| k_PDC                    |   | 9000         |         |

| k_PDC_OFFSET             |   | 0            |         |

| t_CSLEB                  |   | 283          | ns      |

| t_ZVSdead                |   | 236          | ns      |

| k_ZVSon                  |   | 3600         |         |

| k_ZVSon_Vout             |   | 9000         |         |

| t_ZVS_turnOn             |   | 204          | ns      |

| I_GD0_Drive              |   | 31           | mA      |

| V_BULK_ZVS_ON            |   | 250          | VDC     |

| t_MAX_OnTime             |   | 14000        | ns      |

| Protection               |   |              |         |

| т_јотр                   |   | 130          | degreeC |

| t_OCP2                   |   | 600          | ns      |

| t_PeakPower              |   | 30           | ms      |

| EN_PeakPower             |   | Enabled      |         |

| Response_OVP             |   | Auto-Restart |         |

| Burst Configuration      |   |              |         |

| Vcs_Burst                |   | 0.078        | V       |

| Freq_Burst               |   | 50.4         | KHz     |

| v_Burst_Pause            |   | 0.20         | V       |

| v_Burst_Exit             |   | 0.26         | ٧       |

| v_Burst_Wakeup           |   | 0.26         | ٧       |

| t_ReEntry_Burst          |   | 0            | ms      |

| Adaptive Vcs offset      |   |              |         |

| k_Vcs_offset             |   | 20000        |         |

| Vcs_offset_Vzcdzeropoint |   | 79           |         |

| EN_Vcs_offset            |   | Enabled      |         |

Figure 20 Value field

### **Usage of .dp Vision**

8) Changing the parameters will activate the "Save Configuration Set" button. Save the configuration and again press the power on/off button and click on "Test Configuration Set", which will load the new configuration set into the chip's RAM area. Click on "Functions/Burn Configuration Set", which will burn the new configuration set into OTP memory.

Figure 21 "Save Configuration Set" button

For details of setting parameters with .dp Vision, please press "Help" for the.dp Vision user manual.

"Help" button Figure 22

#### Parameter setting with .dp Vision 8.2

Table 10 lists all the parameters configurable by customers through .dp Vision. The setting of the major parameters has been explained in detail in this design guide. The description of each parameter together with an explanatory image will be displayed by clicking on each parameter name. In addition, a user manual can be obtained via the "Help" button.

# Usage of .dp Vision

Table 10 **Configurable parameters**

| Feature                                              | Parameter                          | Default         | Description                                                                                           |

|------------------------------------------------------|------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------|

| Propagation                                          | k_PDC                              | 9000 d          | Propagation delay compensation factor                                                                 |

| delay<br>compensation<br>for peak<br>current control | k_PDC_OFFSET                       | 0 d             | Propagation delay compensation offset                                                                 |

| LEB                                                  | tcsleb                             | 283 ns          | Blanking filter at CS pin to avoid erroneous turn-off of GD0 due to leading-edge spike at GD0 turn-on |

| ZVS dead-time                                        | $t_{\sf ZVSdead}$                  | 236 ns          | Dead-time between end of ZVS pulse at GD1 and start of GD0                                            |

| ZVS pulse<br>length factor                           | $k_{ZVSon}$                        | 3600            | ZVS pulse length factor per bulk voltage                                                              |

|                                                      | $k_{\sf ZVSon\_vout}$              | 9000            | ZVS pulse length factor per output voltage                                                            |

| ZVS gate turn-<br>on point                           | T <sub>zvs_turnon</sub>            | 204 ns          | Turn-on of the ZVS gate after zero crossing detected                                                  |

| Gate driver<br>capability                            | $I_{\_GD0\_drive}$                 | 35 mA           | Sourcing current of gate driver 0                                                                     |

| ZVS enable<br>voltage                                | V <sub>BULK_ZVS_ON</sub>           | 250 V DC        | Above this voltage, ZVS gate is allowed to turn-on                                                    |

|                                                      | t <sub>MAX_OnTime</sub>            | 140000<br>ns    |                                                                                                       |

| Protections                                          | $T_{JOTP}$                         | 130°C           | Internal overtemperature detection level                                                              |

|                                                      | $t_{ m ocp2}$                      | 600 ns          | Blanking time for OCP2 of V <sub>cs</sub> signal                                                      |

|                                                      | $t_{{	extit{peakpower}}}$          | 30 ms           | Blanking time for OLP                                                                                 |

|                                                      | En_OLP                             | Enabled         | To enable or disable OLP                                                                              |

|                                                      | Response_OVP                       | Auto<br>restart | Protection mode for OVP, configurable for AR or latch                                                 |

| Burst mode parameters                                | Vcs_bst                            | 0.078 V         | Burst mode current limit                                                                              |

|                                                      | Freq_bst                           | 50.4 kHz        | Burst mode frequency                                                                                  |

|                                                      | V_bst_pause                        | 0.2 V           | Pause threshold at MFIO pin during on-phase in burst mode operation                                   |

|                                                      | V_bst_exit                         | 0.26 V          | Burst mode exit voltage at MFIO pin                                                                   |

|                                                      | V_bst_wakeup                       | 0.26 V          | Burst mode wake-up voltage at MFIO pin                                                                |

|                                                      | T_reentry_bst                      | 0 ms            | Minimum time to re-enter burst mode                                                                   |

| Adaptive V <sub>cs</sub> offset                      | K_V <sub>CS_offset</sub>           | 20000           | Gradient for compensation curve                                                                       |

|                                                      | $V_{CS\_offset\_}V_{zcdzeropoint}$ | 79              | ZCD voltage level (digital value) without V <sub>cs</sub> offset                                      |

|                                                      | En_V <sub>CS_offset</sub>          | Enabled         | To enable or disable V <sub>CS_offset</sub> compensation                                              |

### References

# 9 References

- [1] XDPS21081 1.0 datasheet

- [2] Design tips for flyback converters using the quasi-resonant PWM controller ICE2QS01, <a href="http://www.infineon.com/dgdl/ANPS0005-ICE2QS01-V11-14122011.pdf?fileId=db3a30432f91014f012fb9a251d750c4">http://www.infineon.com/dgdl/ANPS0005-ICE2QS01-V11-14122011.pdf?fileId=db3a30432f91014f012fb9a251d750c4</a>

- [3] Robert W. Erickson, Fundamentals of Power Electronics, second edition, Springer, 2001

**Revision history**

# **Revision history**

| Document version | Date of release | Description of changes |  |

|------------------|-----------------|------------------------|--|

| V 1.0            | 14-10-2020      | First release          |  |

|                  |                 |                        |  |

|                  |                 |                        |  |

### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-10-14 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference DG\_2010\_PL21\_2010\_034005

### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.