# **MCUXDWQS**

## **Quick Start Guide for MCUXpresso Config Tools**

Rev. 1 — 04/2019 User's Guide

## 1 Introduction

**MCUXpresso Config Tools** is a set of tools for configuration of NXP Cortex-M processors. In order to showcase some of its abilities, a simplified version of its **Pins** and **Clocks** tools is available online, at <a href="http://mcuxpresso.nxp.com">http://mcuxpresso.nxp.com</a>:

- Pins tool allows you to configure pins routing and electrical properties,

- Clocks tool allows you to configure system clocks.

You can use the tools to evaluate chip features and capabilities and generate initialization code.

## 2 Start MCUXpresso Config Tools

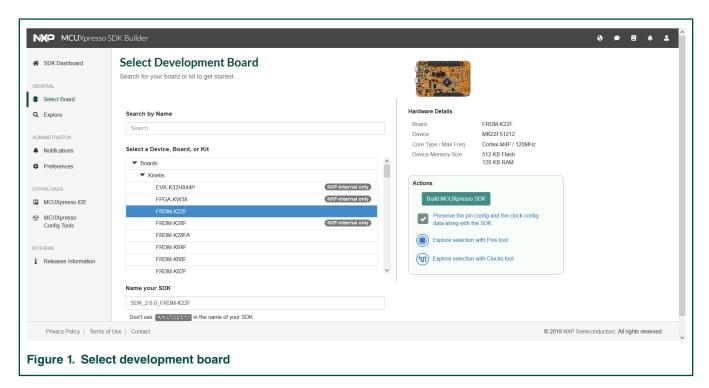

You can inspect device configuration in the online version of **Pins** and **Clocks** tools once you have selected a device, board, or a kit

- Visit mcuxpresso.nxp.com.

- Select Select Development Board and log in.

- Select the device of your choice from the Select a Device, Board, or Kit dropdown list or filter by name in the Search by Name field.

- Once device is selected, select the **Explore selection with Pins tool** to open the device configuration in **Pins** tool, or **Explore selection with Clocks tool** to open it in the **Clocks** tool.

NOTE

You can always switch between the tools

| 1 Introduction                  | 1 |

|---------------------------------|---|

| 2 Start MCUXpresso Config Tools | 1 |

| 3 Pins Tool                     | 2 |

| 4 Clocks Tool                   | 3 |

| 5 Generate Code                 | 4 |

NOTE

All the tool settings are stored within the configuration.

## 3 Pins Tool

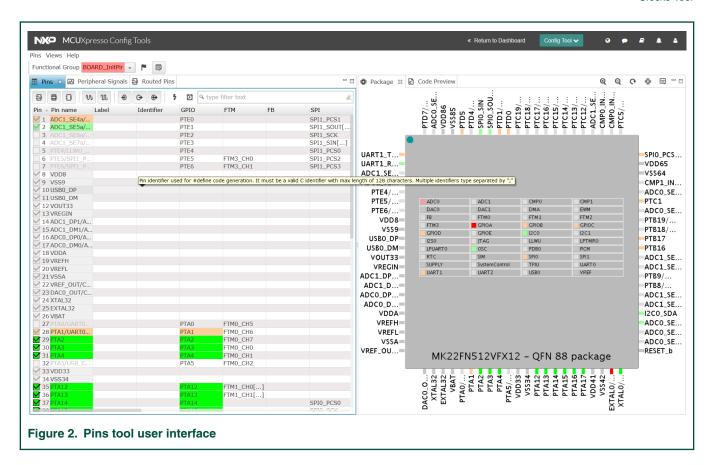

In the **Pins** tool, you can display and configure the pins of the processor. Basic configuration can be done in **Pins**, **Peripheral Signals**, or **Package** views.

More advanced settings (pin electrical features) can be adjusted in the Routed Pins view.

### 4 Clocks Tool

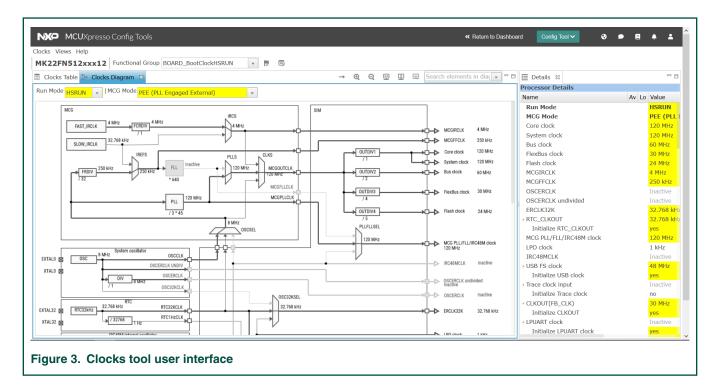

In the **Clocks** tool, you can display and modify clock sources and outputs settings in the **Clocks Table** view. Advanced settings can be adjusted in the **Clocks Diagram** and **Details** views. Global settings of the clocking environment such as run modes, MCG modes and SCG modes can be modified in **Clocks Table**, **Clocks Diagram**, and **Details** views..

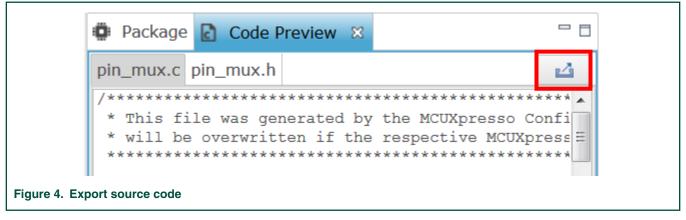

#### 5 Generate Code

To see generated code, open **Code Preview** view by selecting **Views** > **Code Preview** from the **Main Menu**. The source code is updated automatically after every change. It is possible to copy-paste generated code or download a ZIP file with the **Export** button in **Code Preview** view.

The generated code uses MCUXpresso SDK for peripheral initialization, so it is necessary to download device specific SDK package to build it. Supported toolchains are:

- MCUXpresso IDE

- IAR Embedded Workbench

- Keil μVision

- Arm GCC

- · Kinetis Design Studio

How To Reach Us :

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFIRE, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET. TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro,  $\mu$ Vision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2017-2019.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 04/2019

Document identifier: MCUXDWQS