Hands-On Workshop: Configuring and Optimizing Built-In Self Tests with MPC5777M and MPC57XX

FTF-ACC-F1258

Andrew Turner | Automotive MCU Applications Engineer

J U N E . 2 0 1 5

### **Session Introduction**

- Built-In Self-Testing (BIST) is a mechanism provided on Freescale MPC57XX devices to detect the accumulation of latent faults, a requirement of the ISO26262 standard

- This session demonstrates how to configure the BIST tests on MPC5777M using the Self-Test Control Unit

- The safety coverage aspects of the BIST tests will be briefly explained

- This session will work though examples of BIST execution during runtime (on-line) and boot (off-line)

- The examples will detail how to configure Memory BIST (MBIST) and digital Logic BIST (LBIST)

# Agenda

- MPC5777M Overview and Architecture

- BIST Overview

- BIST and Functional Safety

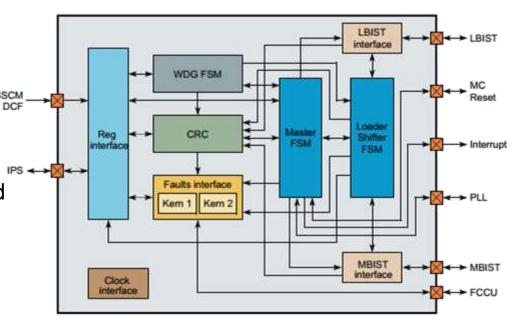

- STCU2 Description

- Lab Examples and Tools Introduction

- Walk-Through of Examples

- Summary

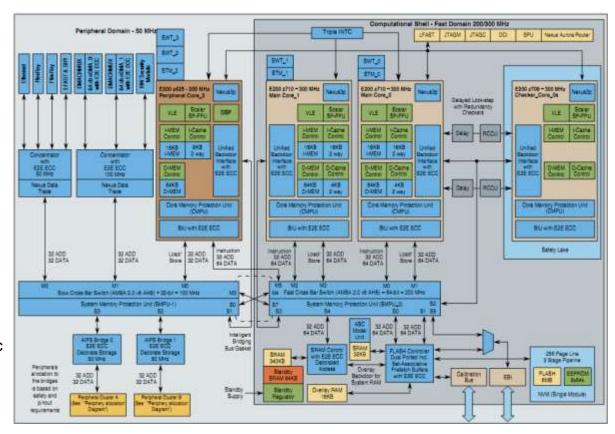

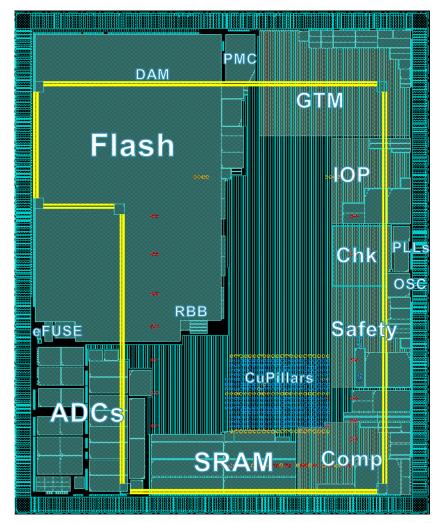

### MPC5777M Overview

#### **Key Functional Characteristics**

- Two independent 300 MHz Power Architecture z7 computational cores

- Single 300 MHz Power Architecture z7 core in delayed lockstep for ASIL-D safety

- Single I/O 200 MHz Power Architecture z4 core

- Hardware Security Module (HSM)

- Dual PLL with freq modulation

- eDMA controller 128 channels

- 8M Flash with ECC

- 596k total SRAM with ECC

- 404k of system RAM (incls. 64k standby)

- 192k of tightly coupled data RAM

- 10 ΣΔ Converters 16-bit

- 12 SAR converters 12-bit

- Ethernet (MII/RMII)

- DSPI 8 channels (3 supporting μSec ch.)

- LINFlex 6 channels (3 supporting μSec ch.)

- MCAN / TTCAN 4x modules/1x module

- 2 x PSI5 Controllers

- GTM 104

Generic Timer Module

- External Bus Interface (EBI)

- · 2 x FlexRay controllers

- Built In Self Test capability

# BIST Overview

### Overview of Built-In Self-Test

- The term Built-In Self-Test (BIST) is used to describe the on-chip hardware mechanisms that can be used to detect latent faults within the MCU

- The BIST allows the MCU to conduct periodic self-tests to identify faults.

- The results of these self-tests can then be used by the MCU to handle the faults and ensure that the device remains in a safe state

- On MPC5777M the BIST provides the ability to meet the latent fault detection requirements defined by the ISO26262 ASIL-D functional safety standard

### **MBIST and LBIST Overview**

- Two different types of BIST are implemented on the MPC5777M: Memory Built-In Self-Test (MBIST) for memory and Logic Built-In Self-Test (LBIST) for digital logic. MBIST is implemented for each of the RAM and peripheral memories on the MPC5777M.

- For MBIST testing purposes each of the memories is segmented into individual MBIST partitions. Each memory is broken down into multiple partitions providing flexibility to test selected address ranges only.

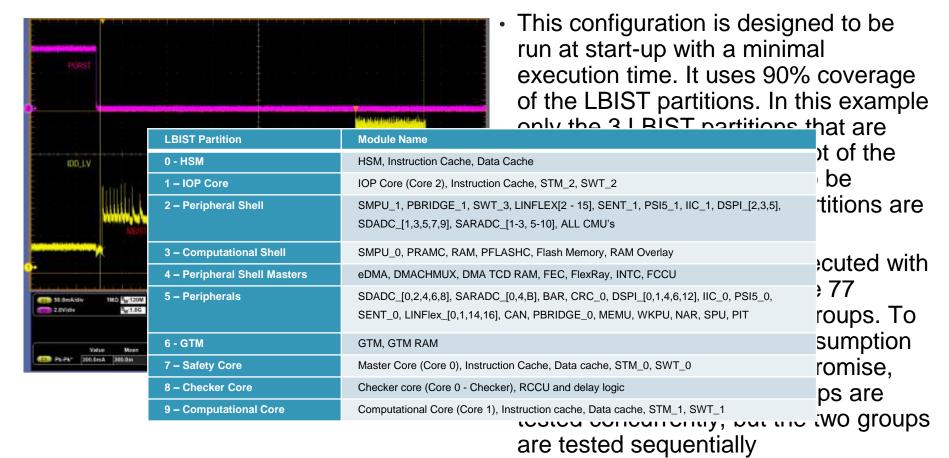

- LBIST tests operate on the digital logic of the device and use scan test techniques to provide high coverage defect detection. The logic is divided up into multiple partitions, with each partition containing multiple user recognizable logic modules (CPU, XBAR, MCAN etc).

# **LBIST & MBIST for functional safety**

- LBIST and MBIST are safety mechanisms to detect permanent die faults during start-up (at time 0) or within the Latent-FTTI (at shutdown for example).

- The failure rate of permanent die faults is very low

- Much less than 10 FIT for the MCU according to IEC TR 62380

- Whereas transient faults are much greater than 1000 FIT for the MCU.

- The majority of MCU safety mechanisms are to address transient faults during application runtime – e2eECC, Lock-Step

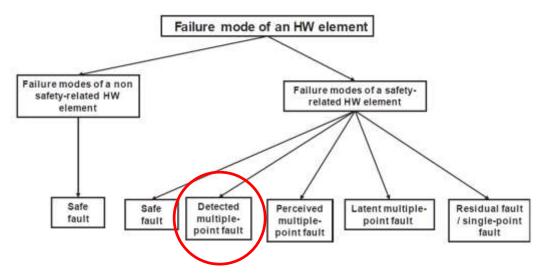

- The LBIST and MBIST tests on MPC5777M do not distinguish between Safe Faults, Single-Point Faults or Latent Faults, they focus on finding faults in the digital logic or SRAM logic, no matter what their categorization.

- From ISO 26262 FMEDA perspective, the LBIST is used to detect Latent Faults.

- LBIST contributes to the Latent Fault Metric calculated in the FMEDA and is required by ISO

26262 to be >90% for the MCU to achieve ASIL D in the context of the safety system.

### **Application Context for LBIST & MBIST**

- Expected that each product will have 2 standard configurations for LBIST & MBIST

- Start-up test as much as possible within the start-up time constraints OFF-LINE

- Shutdown / diagnostic maximize test coverage, no time constraints ON-LINE

#### Start-up

- During start-up the execution time is critical.

- Ideally LBIST & MBIST execution time needs to be in the range of 10 ms 30 ms dependent on application

- In order to achieve the time of 10 30 ms, power and test coverage are tailored

- More power consumed, test time is shorter

- More test coverage, test time is longer

- Power budget is part of MCU spec, so application independent and can be optimized by Freescale through standard LBIST & MBIST configuration

- Test coverage is dependent on ASIL, ranging from 60 90%

# ISO 26262 – Latent Fault Metric (LFM)

- The requirements from ISO 26262-5 for Latent Fault Metric are as shown in the table below

- Freescale use this as guideline for LBIST / MBIST target fault coverage

- The FMEDA uses the LBIST and MBIST as Latent Fault Safety Mechanisms in order to quantify if the ISO 26262 target metrics are met for the MCU

Table 5 — Possible source for the derivation of the target "latent-fault metric" value

|                     | ASIL B | ASIL C | ASIL D |

|---------------------|--------|--------|--------|

| Latent-fault metric | ≥60 %  | ≥80 %  | ≥90 %  |

LBIST & MBIST Latent Fault Coverage

# **LBIST Standard Configurations for MPC57XX Products**

#### Start-up

- ASIL C & D: If time permits, 90% stuck-at coverage, otherwise reduce test to most critical partitions only as defined by safety concept & module classification (maintain 90% stuck-at coverage on partitions tested)

- ASIL B: 60% stuck-at coverage

### Shutdown / diagnostic

- ASIL C & D: 90% stuck-at coverage & 60% transition-delay coverage

- ASIL B: 60% stuck-at coverage

Note: Not all ASIL B products require LBIST & MBIST

# **MBIST Standard Configurations for MPC57XX Products**

- Three types of MBIST March tests are available, with different coverage and execution time

- Auto Test (18N)

- Reduced RunBIST

- Full RunBIST

- Start-up

- ASIL C & D: If time permits, Full RunBIST, otherwise Auto Test (18N)

- ASIL B: Auto Test (18N)

- Shutdown / diagnostic

- ASIL C & D: Full RunBIST

- ASIL B: Auto Test (18N)

|                                                             | Mode bit setting |                 |                    | ng                |

|-------------------------------------------------------------|------------------|-----------------|--------------------|-------------------|

| STCU_CF                                                     | G.MBU            | 0               | 0                  | 1                 |

| STCU_CFG.PM                                                 | IOSEN            | 1               | 0                  | X                 |

|                                                             |                  |                 |                    |                   |

|                                                             |                  | Diagnostic      | Coverage of I      | MBIST mode        |

|                                                             | MBU?             | RunBIST<br>Mode | Reduced<br>RunBIST | Auto Test<br>Mode |

| Fault Model                                                 |                  | (full test)     | Mode               | (18N algo)        |

| Stuck at faults                                             |                  | high            | high               | high              |

| Stuck open faults                                           |                  | high            | high               | Low               |

| Transition faults                                           |                  | high            | high               | high              |

| Write destructive faults                                    |                  | high            | high               | Low               |

| Read destructive fault                                      |                  | high            | high               | high              |

| Deceptive read destructive fault                            |                  | high            | high               | Low               |

| Read deceptive coupling fault                               |                  | high            | high               | Low               |

| Deceptive read disturb faults triggered by several read     |                  | high            | high               | Low               |

| Data retention fault                                        |                  | high            | high               | Low               |

| Coupling faults                                             |                  | high            | high               | Low               |

| Realistic linked coupling faults                            |                  | high            | high               | Low               |

| Weak pull-up PMOS transistor of bitcell                     |                  | high            | Low                | Low               |

| SNPSF (static)                                              |                  | high            | high               | Partial           |

| PNPSF (passive) & ANPSF (active) partially covered          |                  | Partial         | Partial (*)        | Partial (**)      |

| Address Decoder faults                                      | MBU              | high            | high               | high              |

| Address decoder Activation                                  | MBU              | high            | high               | high              |

| Address decoder Deactivation                                | MBU              | high            | Low                | Low               |

| Slow Sense amplifier faults                                 | MBU              | high            | high               | high              |

| Slow Write drivers faults                                   | MBU              | high            | high               | high              |

| Slow precharge circuit faults                               | MBU              | high            | high               | high              |

| Bit line imbalance faults                                   | MBU              | high            | high               | high              |

| Coupling Faults between Global bitlines with local bitlines |                  | high            | high               | Low               |

| CSN and Mask pins test                                      |                  | high            | high               | Low               |

| IO coupling faults                                          |                  | high            | high               | Low               |

# **Application Usage**

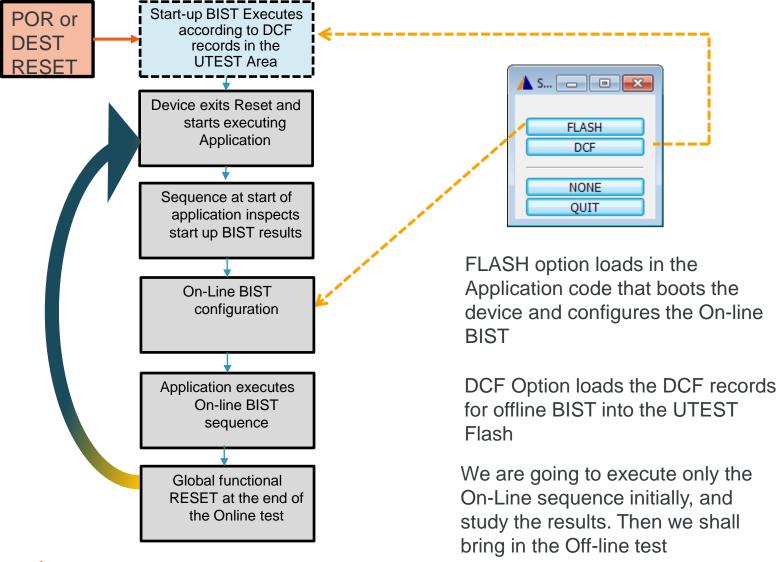

# MPC57XX Start-up/Off-Line BIST implementation

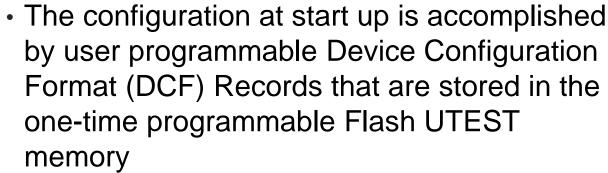

- Off-line, or start-up BISTS are configured to execute every time the MCU boots or performs a destructive reset.

- This procedure is performed while the MCU is powered and held in reset.

# On-Line (Shut-down/Diagnostic) BIST Overview

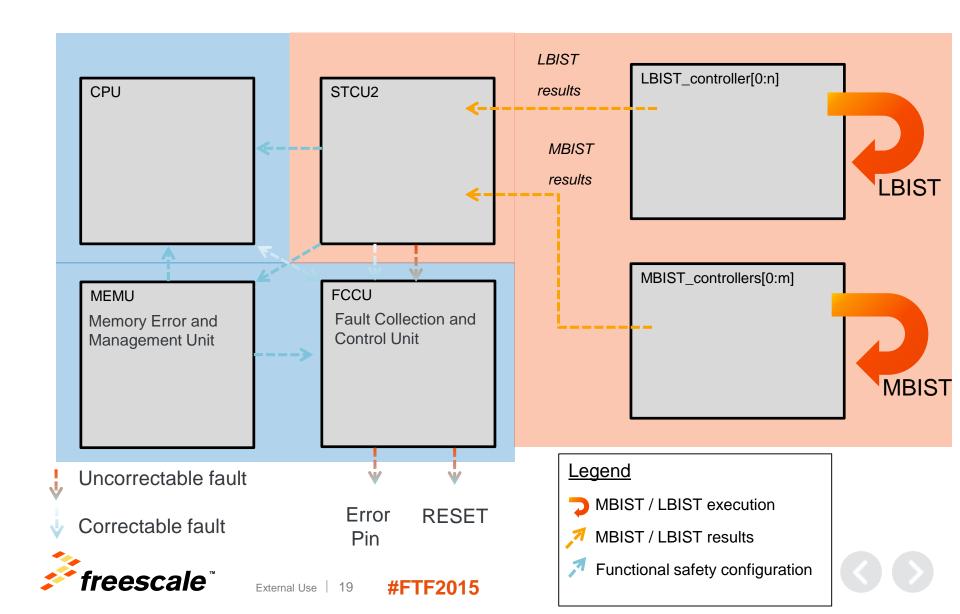

- In addition to being able to run at start-up under control of the STCU2, the MCU allows software to write to the STCU2 during runtime to configure and trigger the execution of MBIST or LBIST. This is known as online testing

- Online testing is mainly intended for a full BIST of the MCU, typically performed prior to shutdown of the ECU, when execution time is not as critical. The online mode can also be used for failure diagnostics and quality control within a manufacturing environment

# **Example Configurations for MPC5777M**

| Self Test<br>Level | Applicati<br>on Mode       | Clock             | STCU2<br>Config.                                | Allocated<br>Time             | LBIST coverage                        | MBIST Algo,           |

|--------------------|----------------------------|-------------------|-------------------------------------------------|-------------------------------|---------------------------------------|-----------------------|

| Ultra-Short        | KEY ON<br>(STARTUP)        | PLL0<br>50MHz     | Loaded from Flash by SSCM                       | 7.5ms<br>(1.2ms LB, 6.3ms MB) | 80% of 3 partitions (1ms/partition)   | Autotest (4 ms)       |

| Short              | KEY ON<br>(STARTUP)        | PLL0<br>50MHz     | Loaded from Flash by SSCM                       | 15ms<br>(8.7ms LB, 6.3ms MB)  | 90% of 3partition s (6ms/partition)   | Autotest (4 ms)       |

| Medium             | KEY OFF<br>(SHUTDOW<br>N)  | PLL1<br>Full Freq | IOP using<br>IPS I/F                            | 48ms<br>(29ms LB, 19ms MB)    | 90% of all partitions (6ms/partition) | Full w/o PMOS<br>open |

| Diagnostic         | Board-level<br>Diagnostics | PLL0<br>Full Freq | IOP using<br>IPS I/F<br>or<br>NEXUS JTAG<br>I/F | 680ms<br>(660ms LB, 20ms MB)  | 94% of all partitions                 | Full set              |

Ultra-Short Short Medium Diagnostic

# **BIST Hardware**

# **Self Test Control Unit summary**

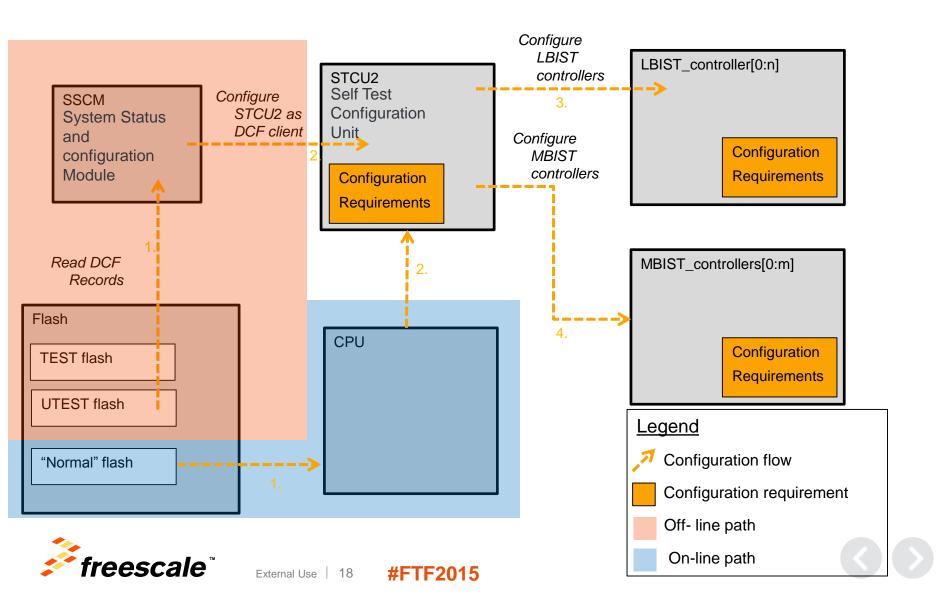

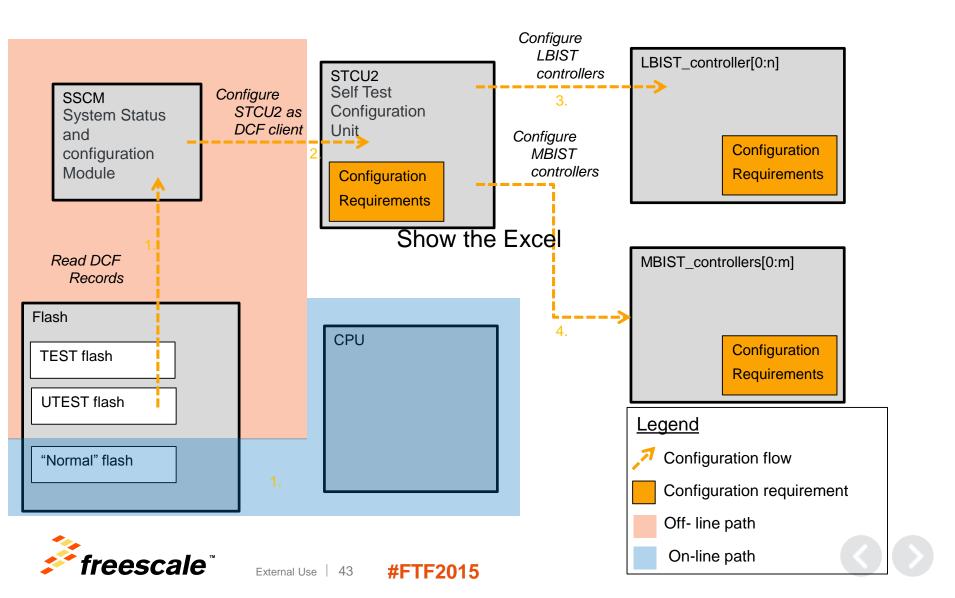

The STCU2 is a programmable hardware module that controls the selftest sequence applied both during the offline and/or online conditions. It is able to manage by hardware the device's LBIST and MBIST blocks

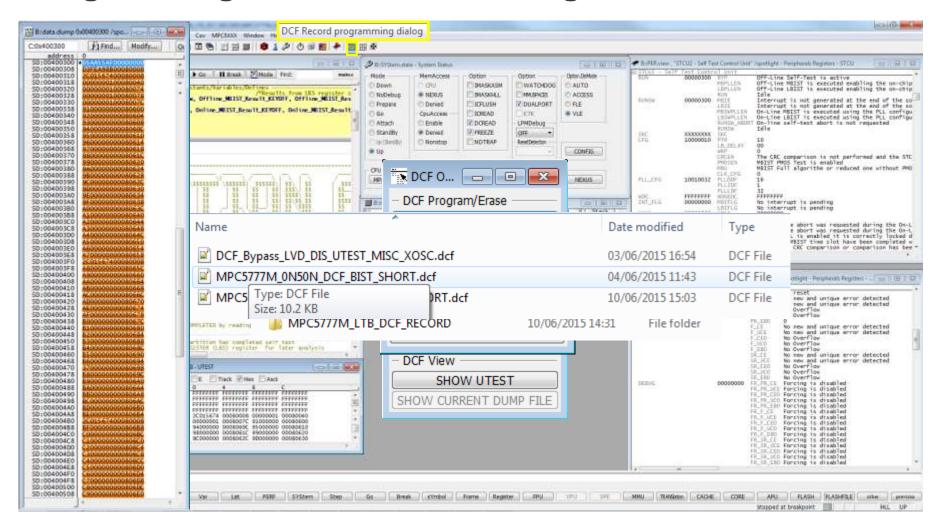

Off-line: The STCU2 uses the System Status and Configuration Module (SSCM) module which has a Device Configuration Format (DCF) bus to load the Self-test parameters from flash memory during the Off-Line Self-Test phase. This interface is able only to write the configuration parameters and start the Self-Test execution once after the STCU2 global reset has been applied

On-line: The STCU2 register access by software is granted by a bus interface with the purpose to check the results of the Off-Line Self-Test but also to load/check the execution of the On-Line Self-Test

STCU2: Self Test Configuration Unit SSCM: System Status and Configuration Module

# FCCU:Fault Collection and Control Unit MEMU:Memory Error Management Unit

# Lab Exercise Project

### **Lab Exercises**

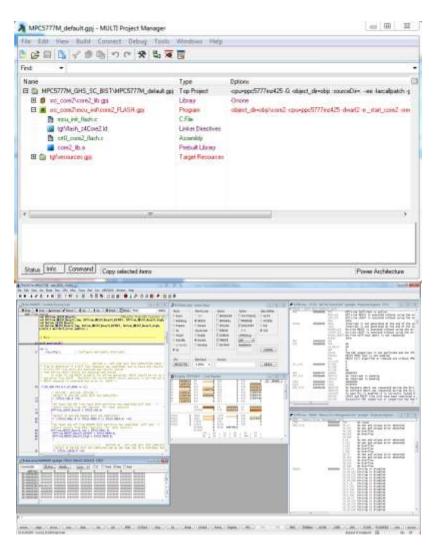

- The provided project contains 2 offline and 2 online BIST configurations

- We will step through the operation of one online BIST, then work through a lab question to create a new On-line BIST configuration

- The project uses the Green Hills software MULTI IDE to compile and assemble the code, and the Lauterbach TRACE 32 debugger to run and step through the code

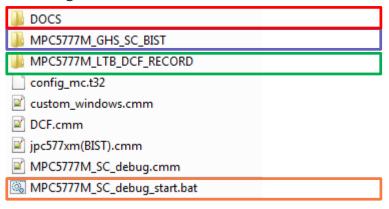

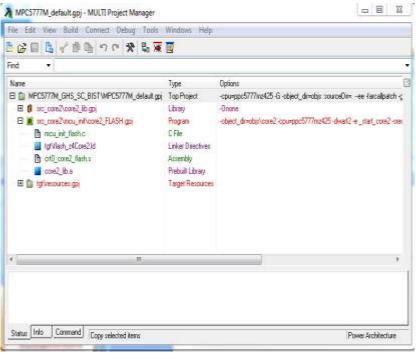

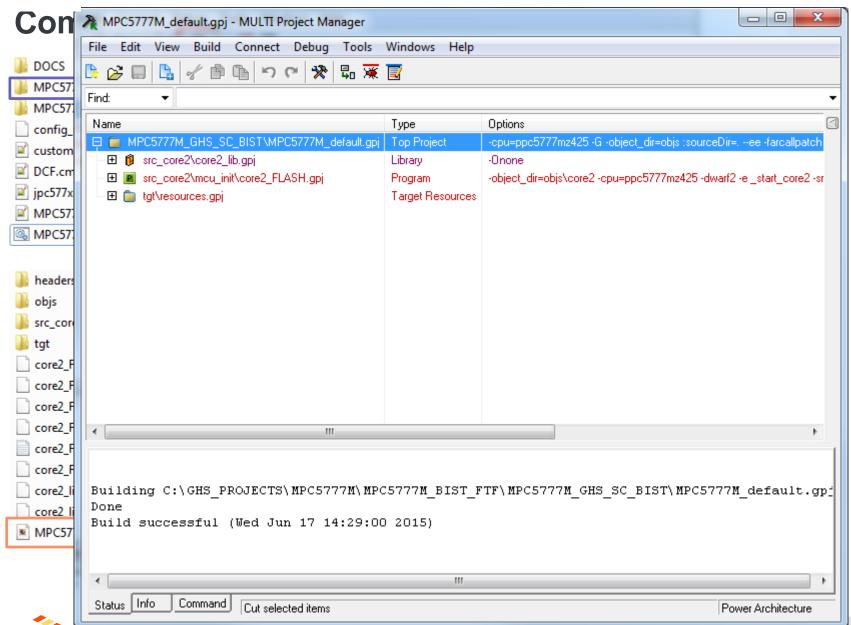

# **Project Structure**

- Batch file launches custom Lauterbach TRACE scripts

- MPC5777M\_GHS\_SC\_BIST contains the Green Hills MULTI project

- MPC5777M\_LTB\_DCF\_REC ORDS contains the flash programming scripts to configure offline BIST

- Docs contains the reference manual, Safety manual, and BIST pertinent documents we will access during the demo

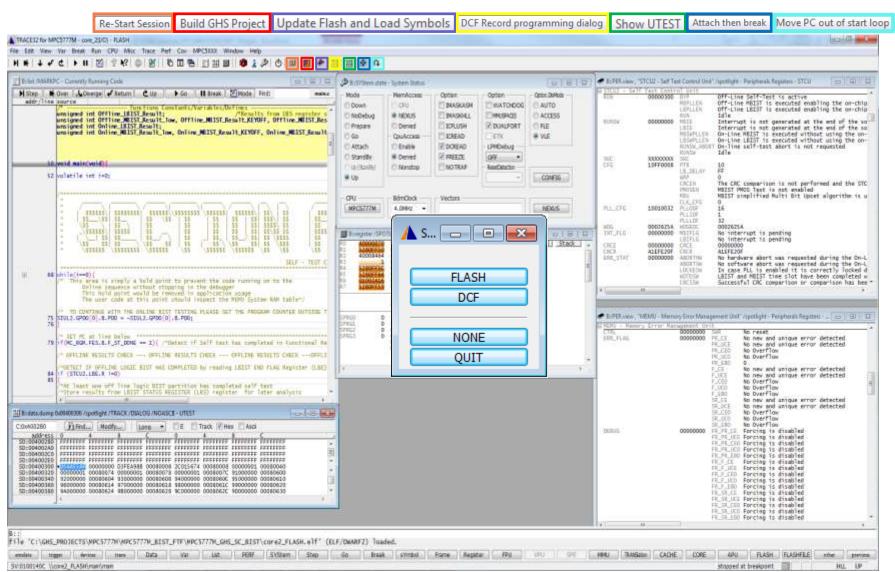

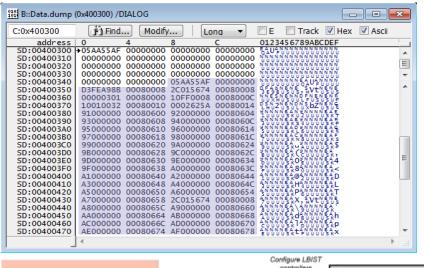

# **TRACE 32 Customized Debugging Window**

## Self-test sequence in the demonstration project

# On-Line BIST "Key Off Example" step through

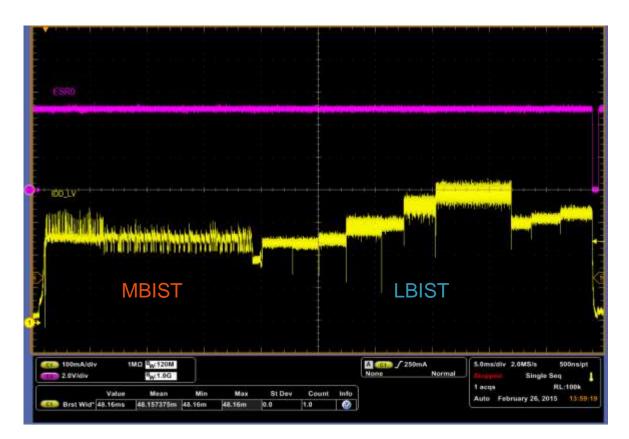

- This is an example configuration for a Key-off or MCU shutdown BIST. This BIST routine is intended to be run at the end of the application prior to shutting down the ECU. In this configuration all LBIST and MBIST partitions are tested as it is anticipated that there will be sufficient time to accommodate this at application Key-off

- This mode change stops all cores other than core 2 (which is the boot core on MPC5777M), configures the systems clock dividers and configures the PLL to support the BIST execution. The MBIST is configured to run at 200MHz and the LBIST is configured to execute at 50MHz. These are the maximum frequencies allowable.

- In this test all LBIST partitions are tested with 90% coverage. All MBIST partitions are tested with the full MBIST algorithm but without the PMOSEN test which provides additional coverage of decoders.

# **On-Line BIST Step Through Sequence**

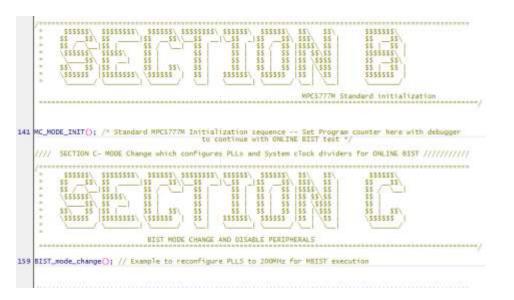

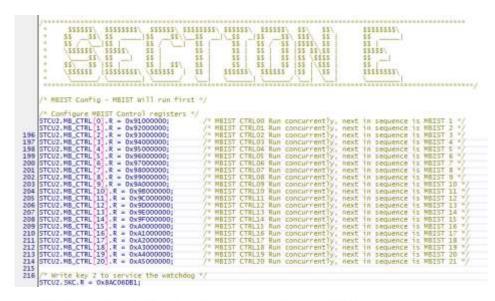

- The code is broken down into sections A through G

- A : Self test Completion check

- B: Device Init

- C: BIST Mode change

- D: STCU2 Unlock

- E: MBIST CONFIGURATION

- F: MBIST ERROR configuration

- G: LBIST Configuration

- H: LBIST Error handling

- I: Final config and Watchdog setting

- J: Start test

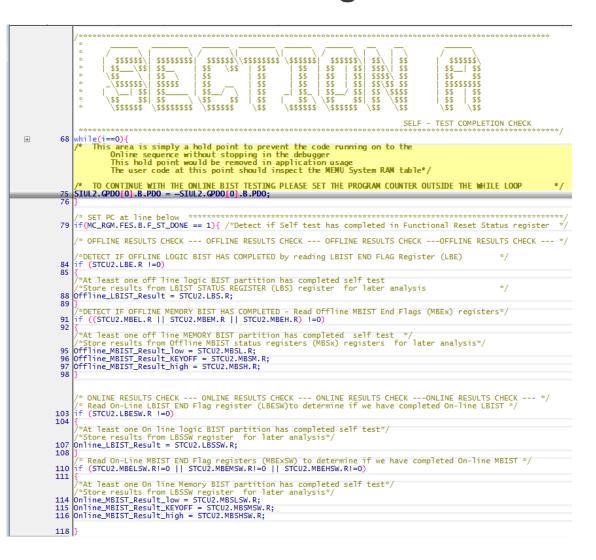

# Section A – Checking for Results of Previous Tests

- Sequence is intended to hold the program

- STCU2 registers are tested to check for completion of any BIST tests and the results are stored for later analysis

- Set the program counter to line 79 (using the "out of loop" button" to move the program out of the while hold loop.

### Section B and Section C

- Section B is the standard MPC5777M device initialization sequence – All clocks configured, PLL's enabled, Progressive clock switching configured, Peripherals and other cores configured

- Section C reconfigures the MPC5777M to the highest frequency for Online BIST(200MHz)

- Section C also disables the auxiliary clocks and disables the peripherals

# **Section D Unlock Sequence**

```

/* Write key 2 to service the watchdog */

219 STCU2.SKC.R = 0x8AC06DB1;

```

- There are three different watchdogs that should not be confused!!!!

- 1) Initialization watchdog Hardcoded timeout that detects faults in the initialization phase preventing the self-test running or being bypassed. Nothing required from user side

- 2) Execution of BIST tests- If the tests do not complete within user defined time the watchdog will time out and Reset the device if configured to do so

- 3) Register write access timeout Access to the STCU2 registers during the configuration phase is unlocked via a set of keys to prevent unintentional access. After a predetermined amount of cycles the access rights will time out unless the second part of the key is written

- The STCU2\_SKC register implements the security key code mechanism needed to begin the write sequence to the other STCU2 registers.

- Depending on the off/on-line test step, the two keys will be different. Byte write operation is not allowed since the full key has to be recognized as one unit.

# **Section E Configuring MBIST partitions**

The STCU2\_MB\_CTRL register defines the control setting of MBIST controller.

The R/W fields in this register are readable at any time. You can write to these fields when either of the following conditions is true:

- · Off-line Self-Test phase is active

- On-line Self-Test phase is active and STCU2\_CFG[WRP] = 0

The offset of this register is a function of NMCUT.

Notes:

The reset value is chip-specific; see the chapter that describes how modules are configured and connected.x = Undefined at reset.

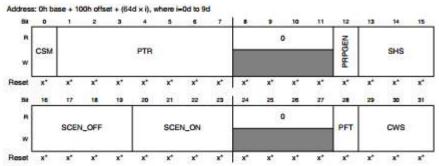

- CSM determines whether the partitions are tested concurrently or sequentially

- PTR defines the logical pointer to the next LBIST or MBIST partition

- 0h to (LBIST-1) = LBIST

- 10h to (MBIST-1) = MBIST

- 7Fh = pointer to Nil CSM must be set to sequential in this instance

- To reduce current consumption our example runs two sequential blocks of concurrent partitions

Please open MBIST\_Partitions.xlsx in the docs folder!

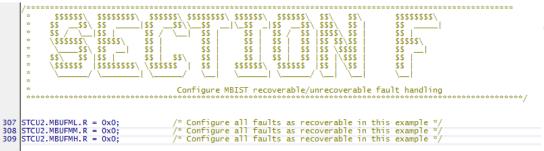

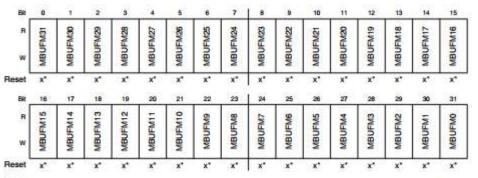

# **Section F MBIST Fault Mapping Configuration**

#### \* Notes:

#### STCU2\_MBUFML field descriptions

| Field        | Description                            |  |  |  |  |

|--------------|----------------------------------------|--|--|--|--|

| 0<br>MBUFM31 | MBIST Unrecoverable Fault Mapping      |  |  |  |  |

|              | Recoverable Fault mapping              |  |  |  |  |

|              | 1 Unrecoverable Fault mapping          |  |  |  |  |

| - 27         | LIBERT III was a sold for this sold of |  |  |  |  |

- The MBUFML/M/H

registers allow the user to

configure whether a fault in

a particular MBIST partition

is recoverable or

unrecoverable.

- This consequently determines whether the STCU2 recoverable or STCU2 unrecoverable flag is set in the Fault control and Configuration Unit (FCCU)

The reset value is chip-specific; see the chapter that describes how modules are configured and connected.x = Undefined at reset.

# **Section G Configuring Online LBIST Partitions**

```

$$$$$$\ $$$$$$$\ $$$$$$\ $$$$$$\ $$$$$$\

$$

$$ |$$$$\

\$$$$$$\

$$$$$\

$$

$$

$$

$$

$$

|$$ $$\$$

\_$$

$$\ $$

$$

$$

$$

$$

$$

155

$$

$$ | $$

$$

$$

$$

$$

|$$

\$$$

$$

$$

$$$$$$

\$$$$$$ |$$$$$$$$\ \$$$$$$

$$

$$$$$$\

\$$

\$$$$$$

On-line LBIST partition configuration

/* Configure Online LBIST partition coverage

/* Configure LBIST for 90% coverage using KEYOFF #define

/*Configure LBIST for 94% coverage using DIAGNOSTIC #define

/* LBISTO HSM Config */

#ifdef KEYOFF

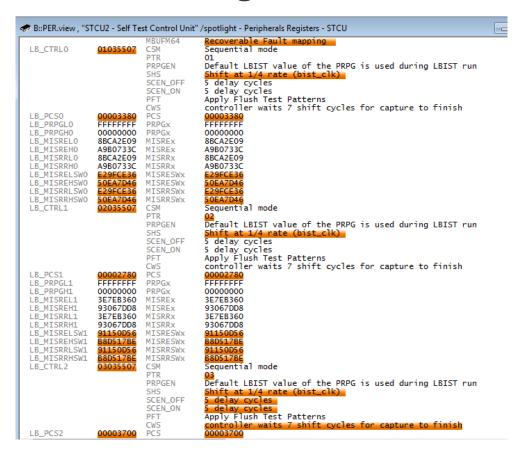

337 STCU2.LB[0].LB_CTRL.R = 0x01035507;

* LBIST CTRLO Run concurrently, next in sequence is LBIST 1 */

338 STCU2.LB[0].LB_PCS.R = 0x00000580;

/* LBIST 0 pattern count */

/* LBIST MISREL Expected Low

STCU2.LB[0].LB_MISRELSW.R = 0xC600B837

/* LBIST MISREH Expected High */

340 STCU2.LB[0].LB_MISREHSW.R = 0x9CC36E3F:

#endif

#ifdef DIAGNOSTIC

STCU2.LB[0].LB\_CTRL.R = 0x01035507;

/* LBIST CTRLO Run concurrently, next in sequence is LBIST 1 */

/* LBIST 0 pattern count */

STCU2.LB[0].LB PCS.R = 0x00003380:

STCU2.LB[0].LB_MISRELSW.R = 0xE29FCE36;

/* LBIST MISREL Expected Low */

STCU2.LB[0].LB_MISREHSW.R = 0x50EA7D46;

/* LBIST MISREH Expected High */

#endif

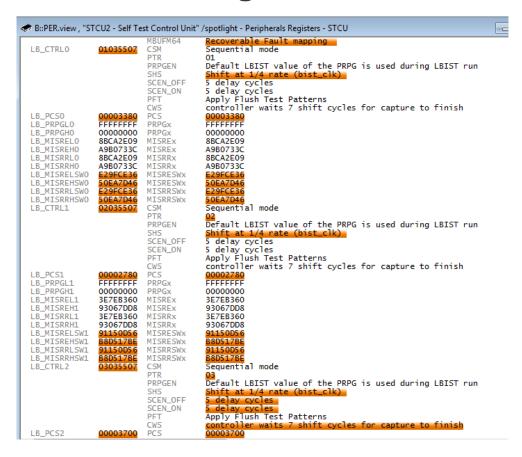

```

- \* Notes

- The reset value is chip-specific; see the chapter that describes how modules are configured and connected.x = Undefined at reset.

- LB\_CTRL register is similar to the MBIST\_CTRL register as it configures concurrent /sequential partition mode, and sets the next partition to be tested.

- LB\_CTRL also contains fields for LBIST shift speed, SCAN ENABLE OFF delay, SCAN ENABLE ON delay, Past Flush test, Capture window size and PPGEN.

- The values for the LB\_CTRL fields are provided my Freescale, in the Excel table accompanying this exercise.

# Section G Configuring Online LBIST partitions cont'd

| Partition                            | STOURES            | KEYON (OFFLINE) Mode<br>ULTRA-SHORT | KEYON (OFFLINE) Mode<br>SHORT | KEYOFF (ORLINE) Mode | DEBUG Mode |

|--------------------------------------|--------------------|-------------------------------------|-------------------------------|----------------------|------------|

| Misc. STCV Configuration<br>Settigns | STOU PIL CFG       | 08010019                            | \$6010019                     |                      |            |

|                                      | 87DU_VO6           | FFFFFFF                             | EFFFFFF                       | FFFFFFF              | FFFFFFF    |

|                                      | STOU_LBRMSV        | 000003FF                            | 888603FF                      | 000003FF             | .000003FF  |

| perition 8                           | COVERNOE           | 81.94%                              | 90.05%                        | 90.05%               | 94.00%     |

|                                      | SHFT SPEED (MH)    | 50                                  | 50                            | 50                   | 50         |

|                                      | CAPTURE SPEED      | SLOW SPEED                          | SLOW SPEED                    | FUNC, SPEED          | FUNC SPEED |

|                                      | TEST TIME (ma)     | 0.37                                | 2.70                          | 2.37                 | 22.15      |

|                                      | STOULB CTRL 0      | 00005507                            | 00005507                      | 00035507             | 00035507   |

|                                      | STOULB PCS I       | 00000000                            | 00000580                      | 00000580             | 00003386   |

|                                      | STOJ LB PRPIL 0    | FFFFFFF                             | FFFFFFF                       | FFFFFFF              | ERFFERE    |

|                                      | STOU LB PRPG4 6    | 10                                  |                               |                      |            |

|                                      | STOU LB MISRO, 0   | EDADSCED                            | 8BCA2E09                      |                      |            |

|                                      | STOU LB_MISREH_U   | D8E388A1                            | A980733C                      | The second second    |            |

|                                      | STOU_LB_MISRELSV_I |                                     | 200000                        | CH21B637             | E29FCE36   |

|                                      | STOULE MISRIEHRY I | 6                                   | 23                            | 9CCMESF              | 50EA7D46   |

```

STCU2.LB[0].LB\_CTRL.R = 0x01035507;

/* LBIST CTRLO Run concurrently, next in sequence is LBIST 1

/* LBIST O pattern count */

/* LBIST MISREL Expected Low

338 STCU2.LB[0].LB_PCS.R = 0 \times 000000580;

339 STCU2.LB[0].LB_MISRELSW.R = 0xC600B837;

STCU2.LB[0].LB_MISREHSW.R = 0x9CC36E3F

/* LBIST MISREH Expected High */

#ifdef DIAGNOSTIC

STCU2.LB[0].LB\_CTRL.R = 0x01035507;

* LBIST CTRLO Run concurrently, next in sequence is LBIST 1 *,

STCU2.LB[0].LB_PCS.R = 0x00003380;

/* LBIST 0 pattern count */

STCU2.LB[0].LB_MISRELSW.R = 0xE29FCE36;

/* LBIST MISREL Expected Low */

STCU2.LB[0].LB_MISREHSW.R = 0x50EA7D46;

/* LBIST MISREH Expected High */

```

- The Excel document contains the pertinent settings for each of the LBIST partitions for Offline and Online mode

- PCS register = Pattern counter stop

- MISRFI SW and MISRFHSW registers are populated with the expected MISR values that will be returned by the LBIST unit.

- MISR In BIST it is not possible to store all the circuit outputs, but the circuit output can be compressed to form a signature that can later be compared to the known "golden" signature. The Multiple – Input Signature Register is a type of Linear feedback Signature register. Each state of the MISR relies on the previous states rather than just the current state, so the MISR will always generate the same correct output sequence from the same input sequence

- The expected MISR signatures are provided by Freescale

- All 10 partitions are configured.

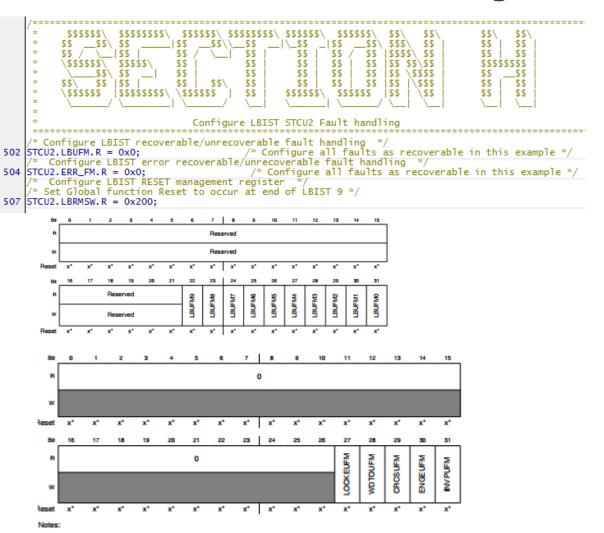

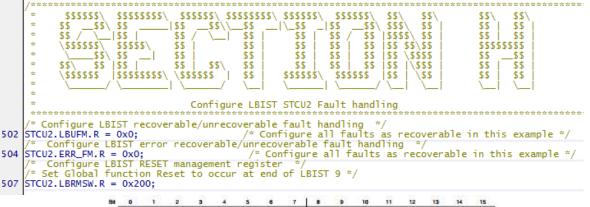

# Section H LBIST fault handling and Global Reset

- The LBUFM register is used to configure whether each LBIST partition generates an un-recoverable fault.

- The Error FM configuration determines whether the other STCU2 faults generate a recoverable or unrecoverable fault

#### Section H Global Reset

#### \* Notes:

#### STCU2\_LBRMSW field descriptions

| Field            | Description                                                                                                                                            |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0-21<br>Reserved | This field is reserved. This read-only field is reserved and always has the value 0.                                                                   |  |  |  |  |

| 22<br>LBRMSW9    | On-Line LBIST Reset Management  NOTE: In case one of the selected LBIST has this bit set to '1', then only the Global functional reset will be pulsed. |  |  |  |  |

|                  | Reserved     Global functional reset is pulsed at the end of LBIST run                                                                                 |  |  |  |  |

In our example as

LBIST partition 9 is the

last partition to be

tested, we configure

LBMSRW such that a

Global functional Reset

is generated when

LBIST 9 completes its

test.

The reset value is chip-specific; see the chapter that describes how modules are configured and connected.x = Undefined at reset.

#### **Section I Configure Watchdog and MBIST PMOS Test**

|     | * Configure Watchdog Time out and PMOS MBIST test                                                                                                                                                   |    |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|     | /* Set Watchdog timeout Config */ STCU2.WDG.R = 0xFFFFFFFF; /* Watchdog time out to Max value */                                                                                                    |    |  |  |  |  |

|     | /* Configure pointer to point to first MBIST partition and configure PMOST Test #ifdef DIAGNOSTIC STCU2.CFG.R = 0x10000010; /*MBIST PMOS TEST is enabled for The Full online test sequence*/ #endif | */ |  |  |  |  |

| 531 | <pre>#ifdef KEYOFF STCU2.CFG.R = 0x10000000;</pre>                                                                                                                                                  |    |  |  |  |  |

| MBIST<br>Type   | STCU2_<br>CFG[PM<br>OSEN] | STCU2_<br>CFG[MB<br>U] | MBIST Algorithm                                                                    | Internal Nodes/<br>Circuits Additionally<br>Covered by Test                              | Usecase                                                                                                            | Test Cycle                                |

|-----------------|---------------------------|------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Full Test       | 1                         | o                      | Test memory using all<br>built in algorithms.<br>Open PMOS algorithm<br>included   | Address Decoder and<br>Bitcell as well as<br>resistive defects in the<br>address decoder | Used by FSL<br>production test.<br>Recommended to use<br>in the field for MBIST<br>online self-test.               | About 3 to 4x<br>more than Auto<br>Test   |

| Reduced<br>Test | 0                         | 0                      | Test memory using all<br>built in algorithms<br>except the open<br>PMOS algorithm. | Address Decoder and<br>Bitcell                                                           | Recommended to use<br>in the field for MBIST<br>online self-test if the<br>Full Test takes too<br>long.            | About 10% less<br>than Full Test          |

| Auto Test       | x                         | 1                      | A smaller set of<br>algorithms which<br>target latent defect<br>mechanisms.        | Latent defects such as<br>NBTI of the PMOS<br>transistors in the<br>bitcells             | Recommended to use<br>for MBIST offline self-<br>test as an optimum<br>balance of test time<br>vs. fault coverage. | About 3 to 4x<br>faster than Full<br>Test |

- For our example we have configured the watchdog timeout value to be the maximum. This watchdog value defines the timeout of the execution run

- The CFG PTR file is configured to point to the first MBIST partition in our example.

- The PMOSEN field is set to provide either the full or reduced test (Auto is used by the off-line BIST)

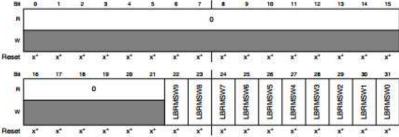

#### Section J Start the Test

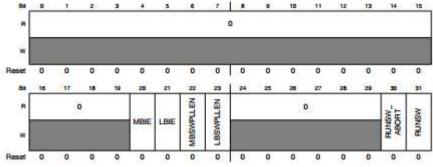

STCU2\_RUNSW field descriptions

| 22<br>MBSWPLLEN | On-Line MBIST with PLL Enabled                                                                                                                                                              |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 | On-Line MBIST is executed without using the on-chip PLL.                                                                                                                                    |  |  |

|                 | 1 On-Line MBIST is executed using the PLL configuration provided by software. STCU2 does not take<br>the PLL control but monitors the PLL look signal to check if PLL is working correctly. |  |  |

- The MBIST and LBIST tests are configured to be executed using the on-chip PLL

- The RUNSW bit field is set to start the Online -self test procedure

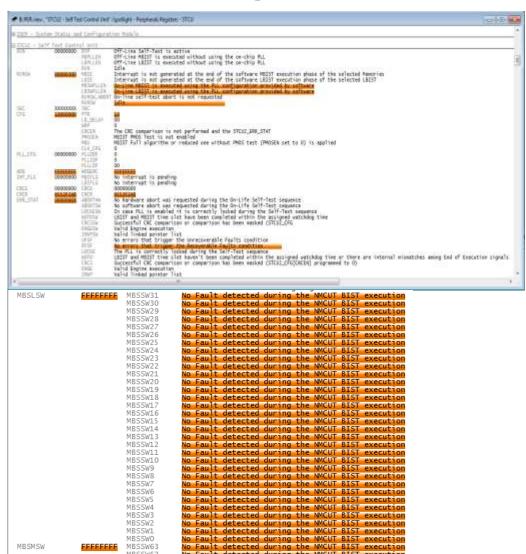

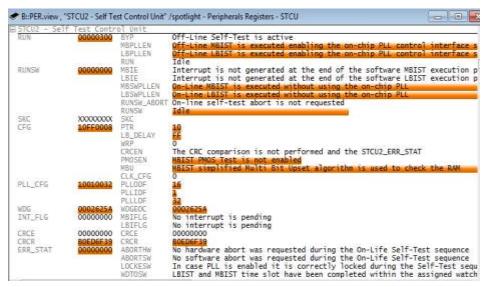

### **Result Checking**

- Press the attach then break button

- Observation of the STCU2 registers will display the results of the BIST tests

- ERR\_STAT displays the status flags for internal fault conditions that occurred during configuration or Self-Testing

- LBSSW Register shows the Successfully executed LBIST tests

- LBESW shows which LBIST tests have completed

- MBS[L/M/H]SW display the offline MBIST results.

MBE[L/M/H]SW show the completion status

# **MISR Matching**

Scroll down to the LB\_CTRL registers. We can see here that the returned MISR values match the expected MISR values

- Change Test to full diagnostic sequence using pre-processor directive

- Set MBIST sequence to be fully concurrent. See MBIST CTRL Register on RM page 4564)

- Change the LB\_MISRELSW, and LB\_MISREHSW values to be 0x0 for LBIST Partition 9 – Lines 485 and 486 of main.c

- Recompile

- Execute test

STCU2: Self Test Configuration Unit

SSCM: System Status and Configuration Module

#### STCU2 DCF Configuration for Off-Line BIST

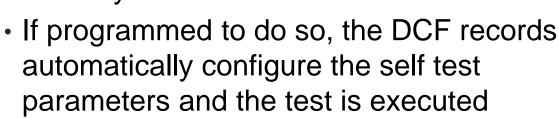

- The Device Configuration Format (DCF) is a mechanism to configure specific registers during system boot and to set up an initial configuration for the device after reset or start up

- In order to configure the self-test to run at start-up a DCF configuration must be written and programmed into the UTEST memory. The DCF records will be processed by the SSCM at start-up and written to the STCU2. The STCU2 will then execute the configured selftest

- A DCF record is 64-bit wide data field in TEST or UTEST Flash that contains 32-bit data that is written to DCF clients, address information and check bits

- A DCF client is a module whose registers can be written by DCF record

- Each write to the STCU2 has a corresponding DCF record entry

#### **Programming Off-line STCU2 Configuration to UTEST**

# **Off-Line DCF Short Example**

LBIST: Partitions 0, 1 and 3 are tested sequentially with 90% coverage

#### **Offline Result Checking**

- Press the attach then break button

- Observation of the STCU2 registers will display the results of the BIST tests

- ERR\_STAT displays the status flags for internal fault conditions that occurred during configuration or Self-Testing

- LBS Register shows the Successfully executed LBIST tests

- LBE shows which LBIST tests have completed

- MBSL/M/H display the off-line MBIST results. MBEL/M/H the completion status

# **MISR Matching**

- Scroll down to the LB\_CTRL registers. We can see here that the returned MISR values match the expected MISR values

- Not required to check this in application

- Built-In Self-Testing (BIST) is a mechanism provided on Freescale MPC57XX devices in order to detect the accumulation of latent faults, a requirement of the ISO26262 standard which defines functional safety for automotive equipment.

- MPC5777M can be configured to carry out Self Test of both memory and logic at either start up or during run time.

- Freescale provides example configurations with Specific ASIL coverage for MPC5777M.

- Other MPC5777x devices will be provided with a standard offline configuration programmed into the UTEST memory, and an application note detailing the configurations available for On-line BIST

www.Freescale.com