#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### Cautions

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# I<sup>2</sup>C Bus Interface

Application Note Renesas Single-Chip Microcomputer

Renesas Electronics www.renesas.com

Rev.2.0 2001.11

#### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

#### Contents

| Secti | on 1    | Overview of the I <sup>2</sup> C Bus                                                       | 1  |

|-------|---------|--------------------------------------------------------------------------------------------|----|

| 1.1   | Overvi  | ew of the I <sup>2</sup> C Bus                                                             | 1  |

|       | 1.1.1   | Features of the I <sup>2</sup> C Bus                                                       | 1  |

|       | 1.1.2   | Differences with the Serial Communications Interface (SCI)                                 | 1  |

|       | 1.1.3   | Connection Type of the I <sup>2</sup> C bus Interface                                      | 2  |

| 1.2   | Method  | l of Data Transfer over an I <sup>2</sup> C Bus                                            | 3  |

|       | 1.2.1   | Basic Concepts and Elements of Data Transfer over an I <sup>2</sup> C Bus                  | 3  |

|       | 1.2.2   | Procedure for Data Transfer (Example: master transmission, slave reception)                | 6  |

| 1.3   | The Sir | ngle-Master and Multi-Master Configurations                                                | 8  |

|       | 1.3.1   | Single-Master                                                                              | 8  |

|       | 1.3.2   | Multi-Master                                                                               | 8  |

| 1.4   | Proced  | ure for Adjusting Communications                                                           | 9  |

| Secti | on 2    | Explanation of the Interface Functions of the I <sup>2</sup> C Bus                         | 11 |

| 2.1   | Lineup  | of Products that Incorporate the I <sup>2</sup> C Bus Interface                            | 11 |

| 2.2   | Specifi | cations of the I <sup>2</sup> C Bus Interfaces Incorporated in H8/300 Series and           |    |

|       | H8/300  | DL Series Products [H8 Series]                                                             | 13 |

|       | 2.2.1   | Specifications of the I <sup>2</sup> C Bus Interfaces Incorporated in H8/300 Series        |    |

|       |         | and H8/300L Series Products                                                                | 13 |

|       | 2.2.2   | Configuration of the I <sup>2</sup> C Bus Interfaces Incorporated in H8/300 Series         |    |

|       |         | and H8/300L Series Products                                                                | 14 |

|       | 2.2.3   | Data Transfer Format of the I <sup>2</sup> C Bus Interfaces Incorporated in H8/300 Series  |    |

|       |         | and H8/300L Series Products                                                                | 15 |

|       | 2.2.4   | Explanation of Functions of the Registers of the I <sup>2</sup> C Bus Interfaces           |    |

|       |         | Incorporated in H8/300 Series and H8/300L Series Products                                  | 17 |

| 2.3   | Specifi | cations of the I <sup>2</sup> C Bus Interfaces Incorporated in H8S Series Products         | 19 |

|       | 2.3.1   | Features of the I <sup>2</sup> C Bus Interfaces Incorporated in H8S Series Products        | 19 |

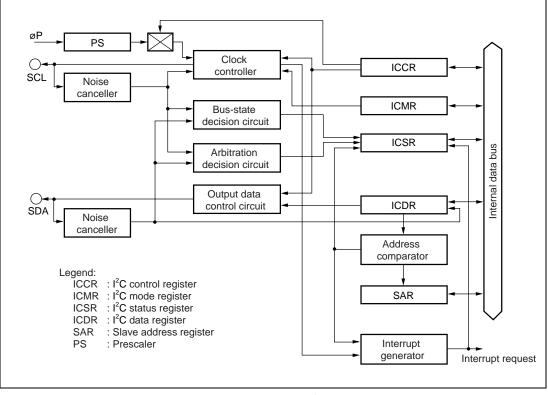

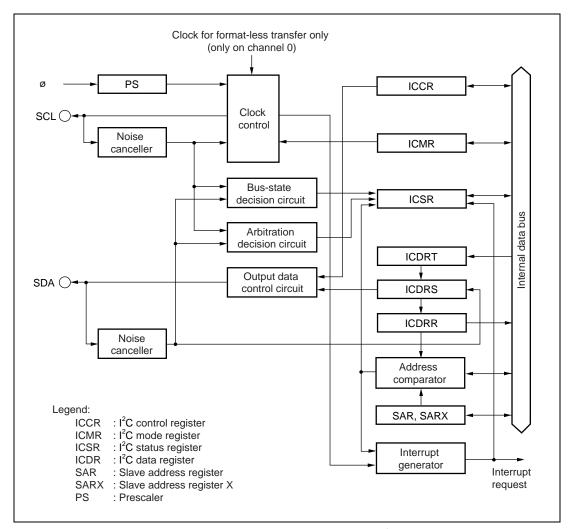

|       | 2.3.2   | Internal Block Configuration of the H8S Series I <sup>2</sup> C Bus Interface              | 21 |

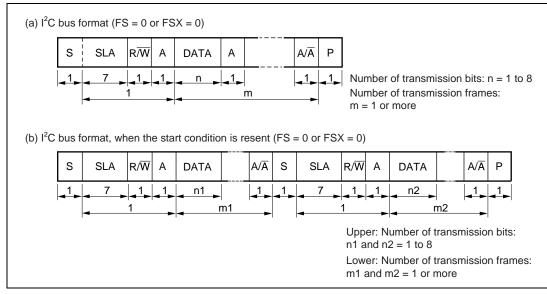

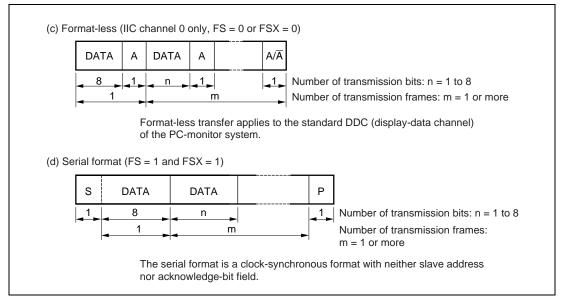

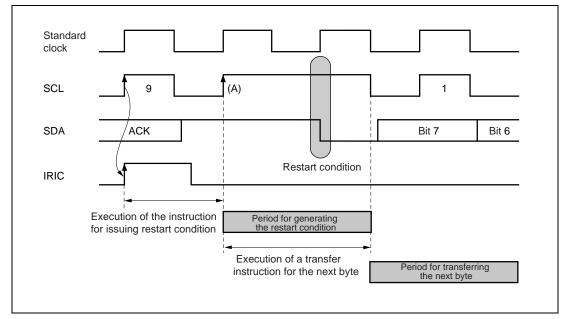

|       | 2.3.3   | Data Format for the H8S Series I <sup>2</sup> C Bus                                        | 22 |

|       | 2.3.4   | Description of Functions of the H8S Series I <sup>2</sup> C Bus Interface Incorporated     |    |

|       |         | Registers                                                                                  | 24 |

|       | 2.3.5   | Relationship between Flags of On-chip I <sup>2</sup> C Bus Interface and Transfer State in |    |

|       |         | H8S Series (H8S/2138 Series)                                                               | 42 |

| 2.4   | Descrip | otion of I <sup>2</sup> C Bus Interface Usage                                              | 43 |

| 2.5   | Synchr  | onization of the I <sup>2</sup> C Bus Communication                                        | 54 |

| 2.6   | Descrip | otion of Data Transfer in H8/300 and H8/300L Series [H8 Series]                            | 56 |

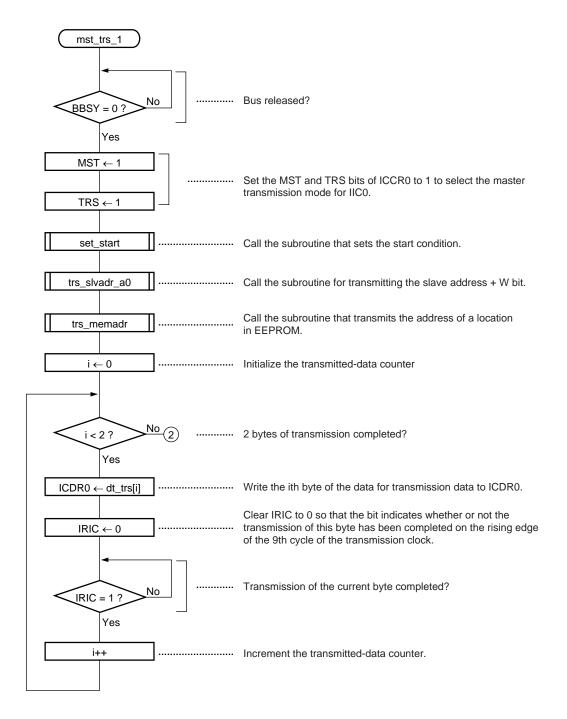

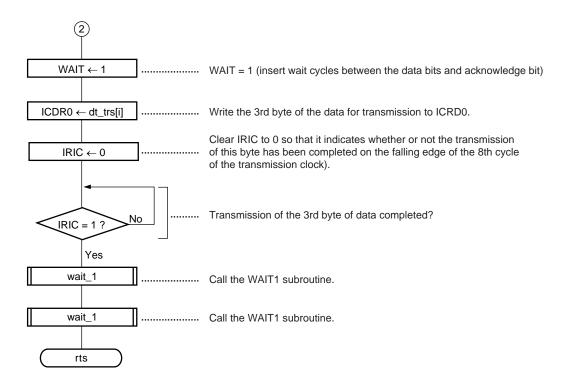

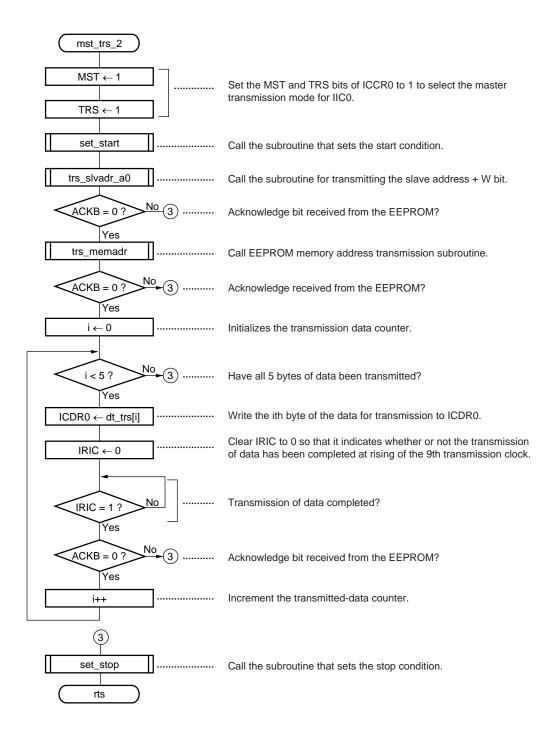

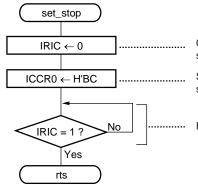

|       | 2.6.1   | Master transmission                                                                        | 56 |

|       | 2.6.2   | Master Reception                                                                           | 58 |

|       | 2.6.3   | Slave Reception                                                                            | 60 |

|            | 2.6.4                                                                                                                 | Slave Transmission                                                                                                                                                                                                                                                                                                                                                           | 63                                                                                                                                                                                  |

|------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

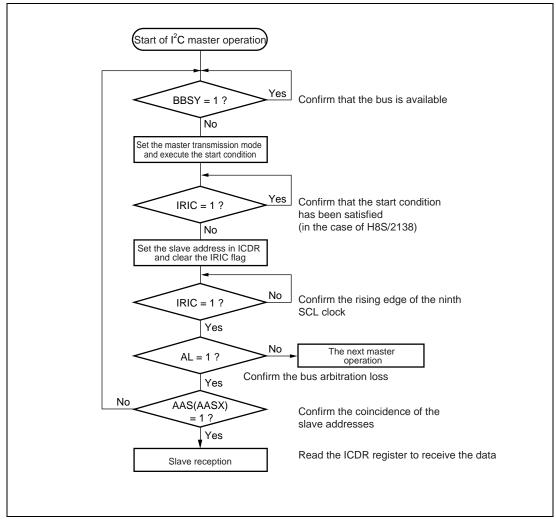

| 2.7        | Descrip                                                                                                               | ption of Data Transfer in H8S Series (H8/2138 Series) [H8S Series]                                                                                                                                                                                                                                                                                                           | 65                                                                                                                                                                                  |

|            | 2.7.1                                                                                                                 | Master Transmission                                                                                                                                                                                                                                                                                                                                                          | 65                                                                                                                                                                                  |

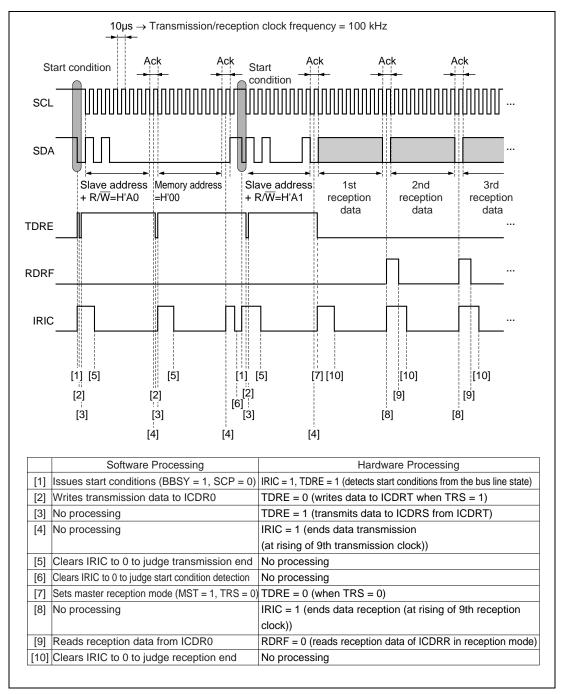

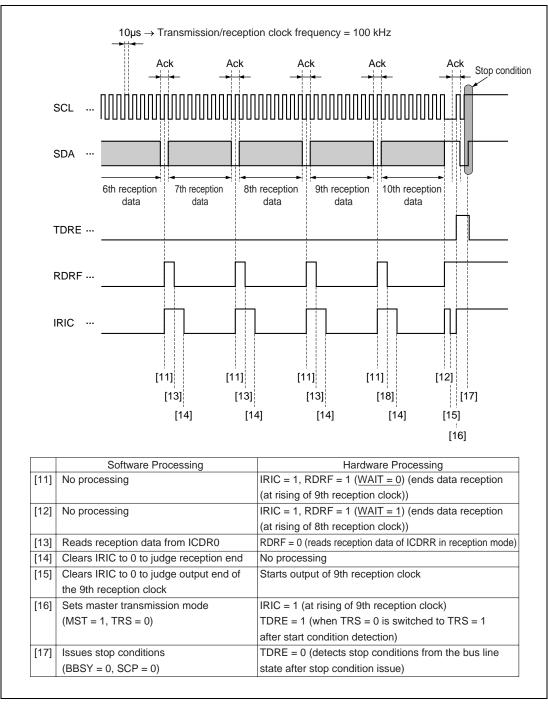

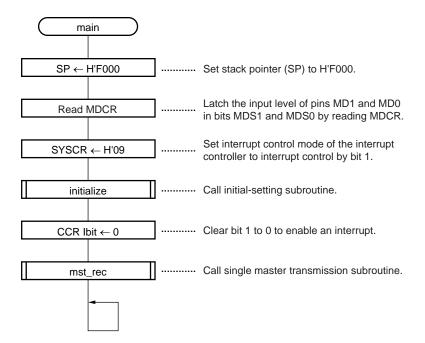

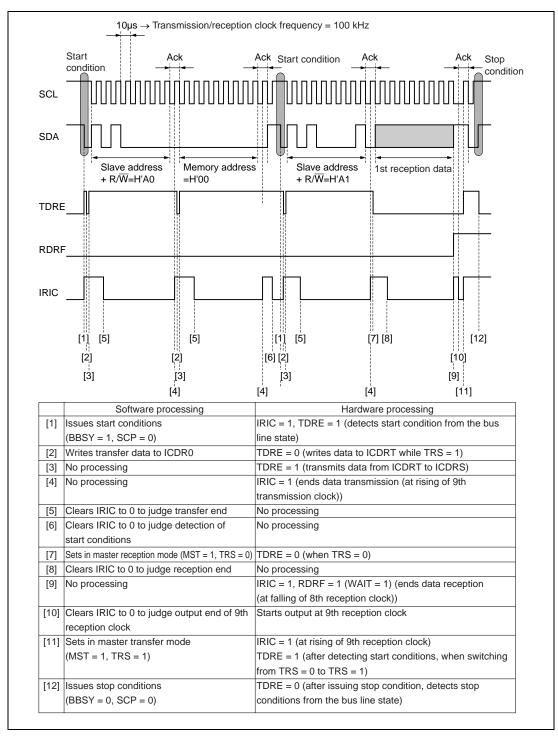

|            | 2.7.2                                                                                                                 | Master Reception                                                                                                                                                                                                                                                                                                                                                             | 70                                                                                                                                                                                  |

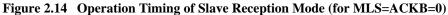

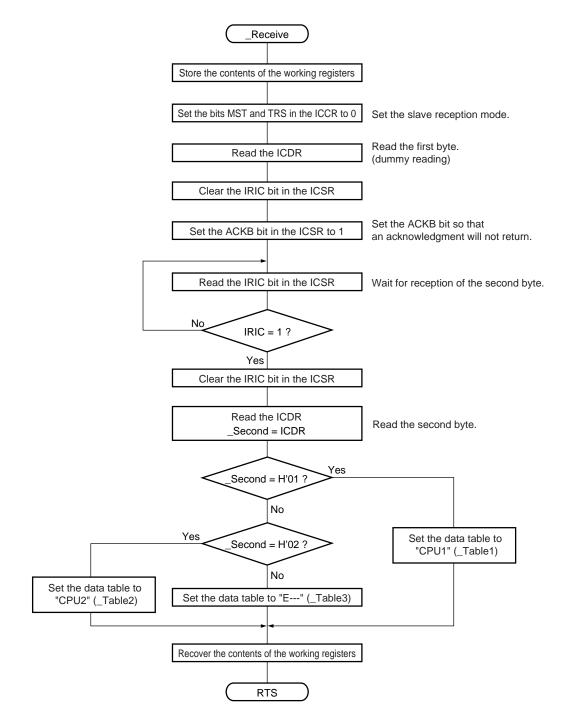

|            | 2.7.3                                                                                                                 | Slave Reception                                                                                                                                                                                                                                                                                                                                                              | 75                                                                                                                                                                                  |

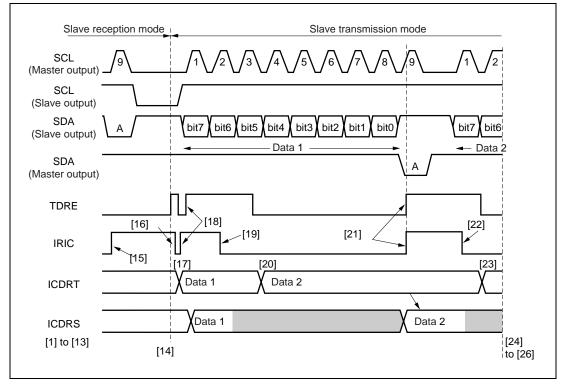

|            | 2.7.4                                                                                                                 | Slave Transmission                                                                                                                                                                                                                                                                                                                                                           | 78                                                                                                                                                                                  |

| Secti      | ion 3                                                                                                                 | Examples of Application to the H8/300 and H8/300L Series                                                                                                                                                                                                                                                                                                                     | 83                                                                                                                                                                                  |

| 3.1        | System                                                                                                                | a Specifications                                                                                                                                                                                                                                                                                                                                                             | 83                                                                                                                                                                                  |

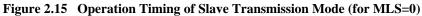

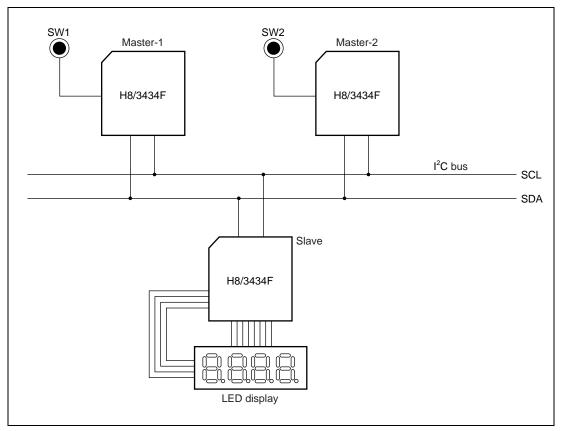

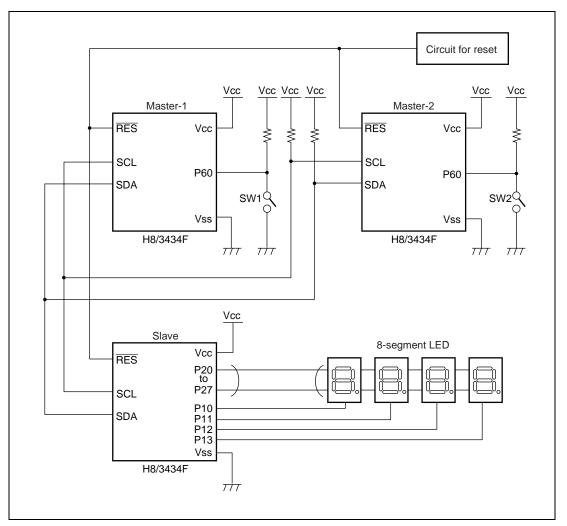

| 3.2        | Circuit                                                                                                               | for Multi-Master Evaluation System                                                                                                                                                                                                                                                                                                                                           | 87                                                                                                                                                                                  |

| 3.3        | Design                                                                                                                | of Software                                                                                                                                                                                                                                                                                                                                                                  | 88                                                                                                                                                                                  |

|            | 3.3.1                                                                                                                 | Description of Modules                                                                                                                                                                                                                                                                                                                                                       | 88                                                                                                                                                                                  |

|            | 3.3.2                                                                                                                 | Master                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                     |

|            | 3.3.3                                                                                                                 | Slave                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     |

| 3.4        | Flowch                                                                                                                | narts                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     |

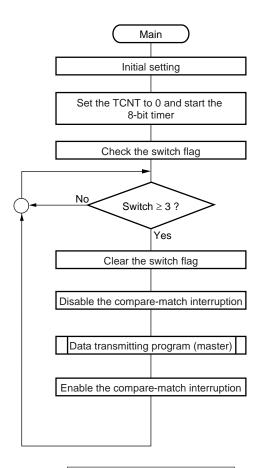

|            | 3.4.1                                                                                                                 | Master Program                                                                                                                                                                                                                                                                                                                                                               | 92                                                                                                                                                                                  |

|            | 3.4.2                                                                                                                 | Slave Program                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

| 3.5        | Program                                                                                                               | m Listings                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                     |

|            | 3.5.1                                                                                                                 | Master Program                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                     |

|            | 3.5.2                                                                                                                 | Slave Program                                                                                                                                                                                                                                                                                                                                                                | 105                                                                                                                                                                                 |

|            |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

|            |                                                                                                                       | Example Applications for the H8S Series                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                     |

| 4.1        | Usage                                                                                                                 | Guide to the Example Applications for the H8S Series                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |

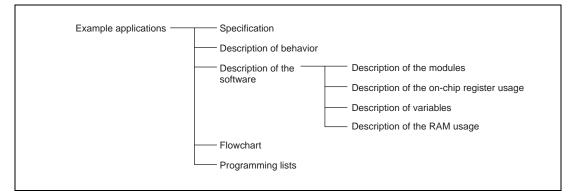

|            | 4.1.1                                                                                                                 | The Structure of the Example Applications for the H8S Series                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

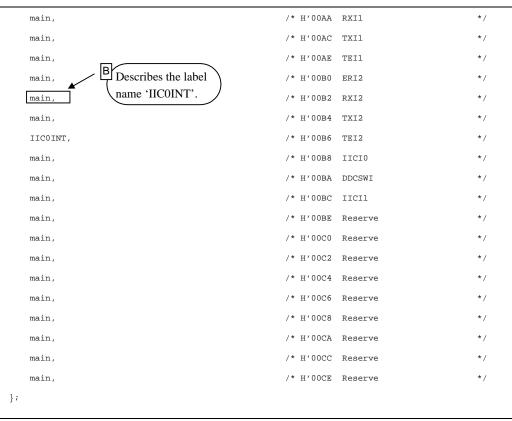

|            | 4.1.2                                                                                                                 | Description of the Definition File for the Vector Table                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                     |

|            | 4.1.3                                                                                                                 | Description of the Definition File for the Registers                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |

|            | 4.1.4                                                                                                                 | Description of the Inclusion of Assembler Files in C Language Programs                                                                                                                                                                                                                                                                                                       | 1/0                                                                                                                                                                                 |

|            | 4.1.5                                                                                                                 | Description of the inclusion of rissenfold rifes in C Lungauge riograms                                                                                                                                                                                                                                                                                                      | 140                                                                                                                                                                                 |

|            |                                                                                                                       | Description of the Linkage of Files                                                                                                                                                                                                                                                                                                                                          | 149                                                                                                                                                                                 |

| 4.2        |                                                                                                                       | Description of the Linkage of Files<br>Master Transmission                                                                                                                                                                                                                                                                                                                   | 149<br>150                                                                                                                                                                          |

| 4.2        |                                                                                                                       | Description of the Linkage of Files                                                                                                                                                                                                                                                                                                                                          | 149<br>150                                                                                                                                                                          |

| 4.2        | Single-                                                                                                               | Description of the Linkage of Files<br>Master Transmission                                                                                                                                                                                                                                                                                                                   | 149<br>150<br>150                                                                                                                                                                   |

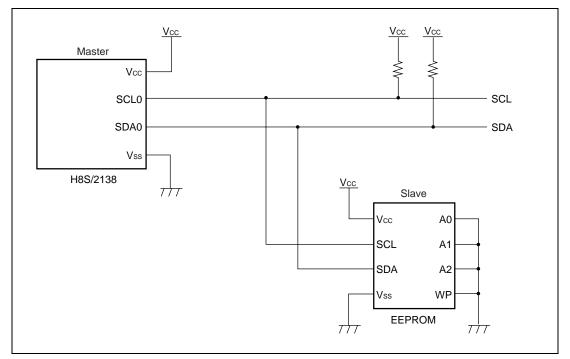

| 4.2        | Single-<br>4.2.1                                                                                                      | Description of the Linkage of Files<br>Master Transmission<br>Specification                                                                                                                                                                                                                                                                                                  | 149<br>150<br>150<br>152                                                                                                                                                            |

| 4.2        | Single-<br>4.2.1<br>4.2.2                                                                                             | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation                                                                                                                                                                                                                                                                  | 149<br>150<br>150<br>152<br>153                                                                                                                                                     |

| 4.2        | Single-<br>4.2.1<br>4.2.2<br>4.2.3                                                                                    | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation<br>Description of the Software                                                                                                                                                                                                                                   | 149<br>150<br>150<br>152<br>153<br>157                                                                                                                                              |

| 4.2<br>4.3 | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                                                  | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation<br>Description of the Software<br>Flowchart<br>Program List                                                                                                                                                                                                      | 149<br>150<br>150<br>152<br>153<br>157                                                                                                                                              |

|            | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                                                  | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation<br>Description of the Software<br>Flowchart<br>Program List                                                                                                                                                                                                      | 149<br>150<br>150<br>152<br>153<br>157<br>162<br>167                                                                                                                                |

|            | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Single-                                                       | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation<br>Description of the Software<br>Flowchart<br>Program List                                                                                                                                                                                                      | 149<br>150<br>152<br>153<br>157<br>162<br>167<br>167                                                                                                                                |

|            | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Single-<br>4.3.1                                              | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation<br>Description of the Software<br>Flowchart<br>Program List<br>Master Reception<br>Specifications                                                                                                                                                                | 149<br>150<br>152<br>153<br>157<br>162<br>167<br>167<br>169                                                                                                                         |

|            | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Single-<br>4.3.1<br>4.3.2                                     | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation<br>Description of the Software<br>Flowchart<br>Program List<br>Master Reception<br>Specifications<br>Operation Descriptions                                                                                                                                      | 149<br>150<br>152<br>153<br>157<br>162<br>167<br>167<br>169<br>172                                                                                                                  |

|            | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Single-<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5          | Description of the Linkage of Files                                                                                                                                                                                                                                                                                                                                          | <ul> <li>149</li> <li>150</li> <li>150</li> <li>152</li> <li>153</li> <li>157</li> <li>162</li> <li>167</li> <li>167</li> <li>169</li> <li>172</li> <li>175</li> <li>183</li> </ul> |

|            | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Single-<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>One-B | Description of the Linkage of Files<br>Master Transmission<br>Specification<br>Description of the Operation<br>Description of the Software<br>Flowchart<br>Program List<br>Master Reception<br>Specifications<br>Operation Descriptions<br>Software Descriptions<br>Flowchart<br>Program List<br>Software Descriptions<br>Software Descriptions<br>Flowchart<br>Program List | 149<br>150<br>152<br>153<br>157<br>162<br>167<br>167<br>169<br>172<br>175<br>183<br>189                                                                                             |

| 4.3        | Single-<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Single-<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5          | Description of the Linkage of Files                                                                                                                                                                                                                                                                                                                                          | 149<br>150<br>152<br>153<br>157<br>162<br>167<br>167<br>169<br>172<br>175<br>183<br>189<br>189                                                                                      |

|      | 4.4.3   | Software Descriptions                        |     |

|------|---------|----------------------------------------------|-----|

|      | 4.4.4   | Flowchart                                    | 195 |

|      | 4.4.5   | Program List                                 | 200 |

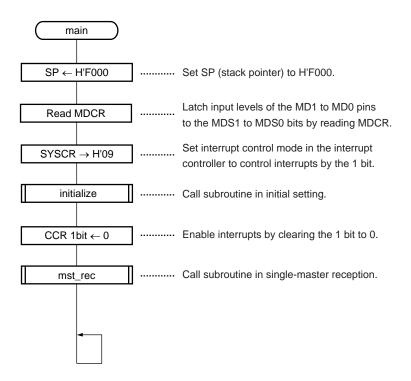

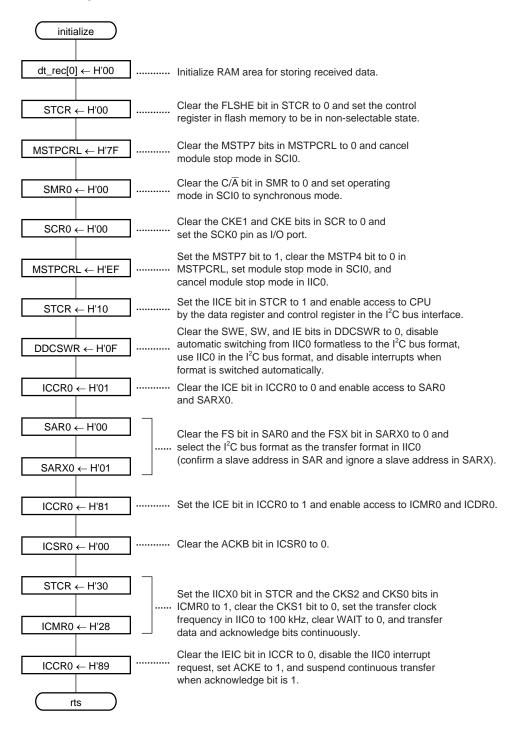

| 4.5  | One-By  | te Data Reception by Single-Master Reception | 204 |

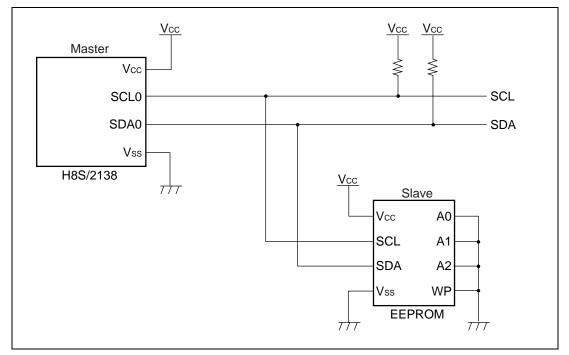

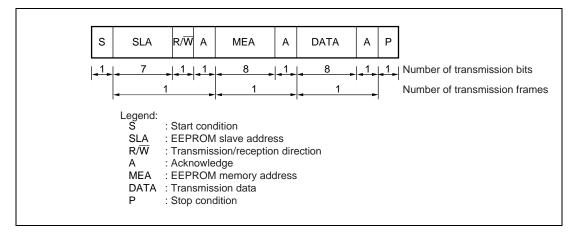

|      | 4.5.1   | Specifications                               | 204 |

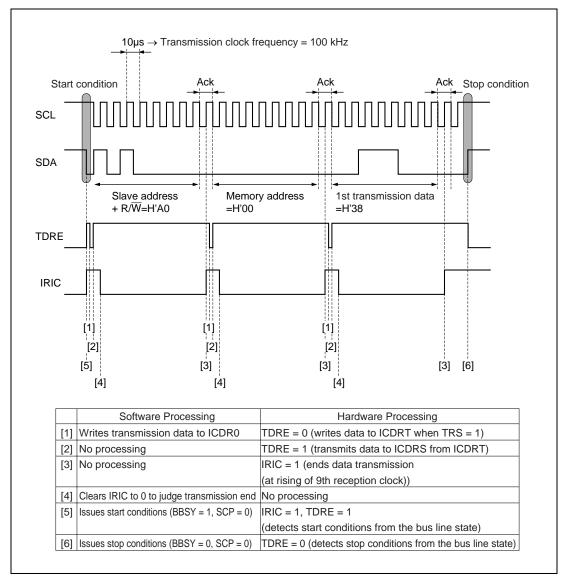

|      | 4.5.2   | Operation Description                        | 205 |

|      | 4.5.3   | Software Description                         | 207 |

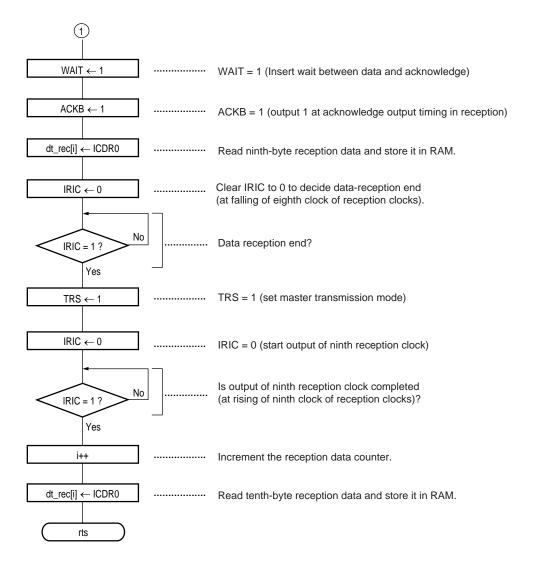

|      | 4.5.4   | Flowchart                                    | 210 |

|      | 4.5.5   | Program List                                 | 217 |

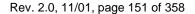

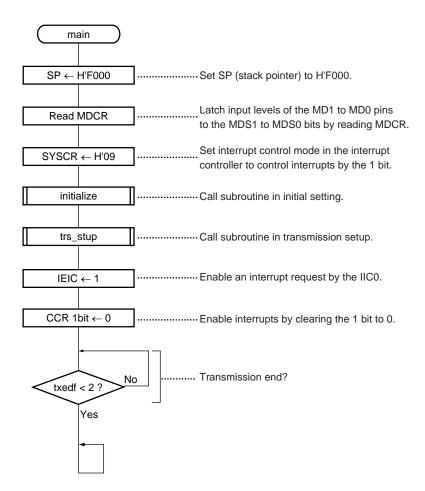

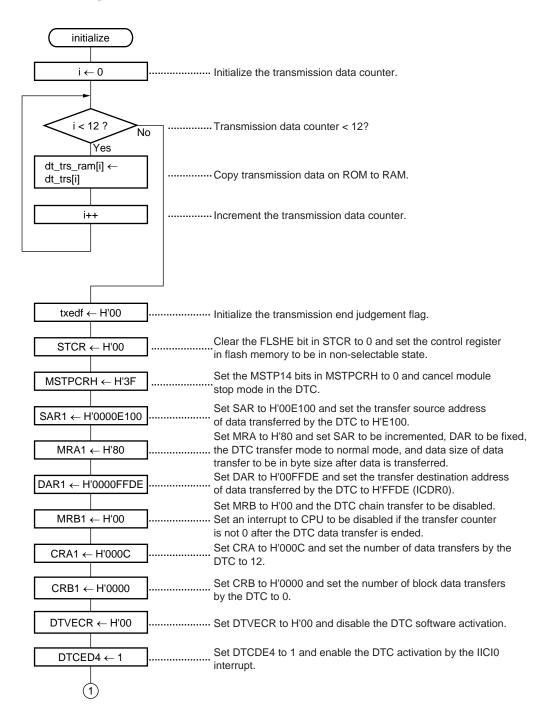

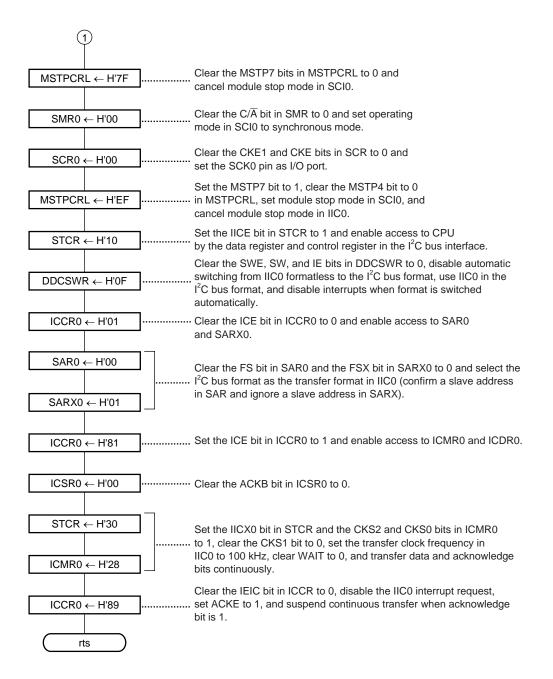

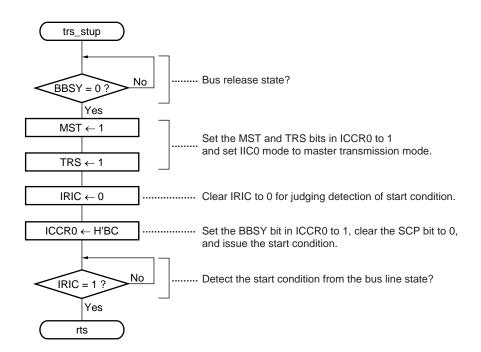

| 4.6  | Single- | Master Transmission by DTC                   | 222 |

|      | 4.6.1   | Specifications                               | 222 |

|      | 4.6.2   | Operation Description                        | 229 |

|      | 4.6.3   | Software Description                         | 229 |

|      | 4.6.4   | Flowchart                                    | 235 |

|      | 4.6.5   | Program List                                 | 240 |

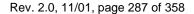

| 4.7  | Single- | Master Reception by DTC                      | 245 |

|      | 4.7.1   | Specifications                               | 245 |

|      | 4.7.2   | Description of Operation                     | 252 |

|      | 4.7.3   | Description of Software                      | 253 |

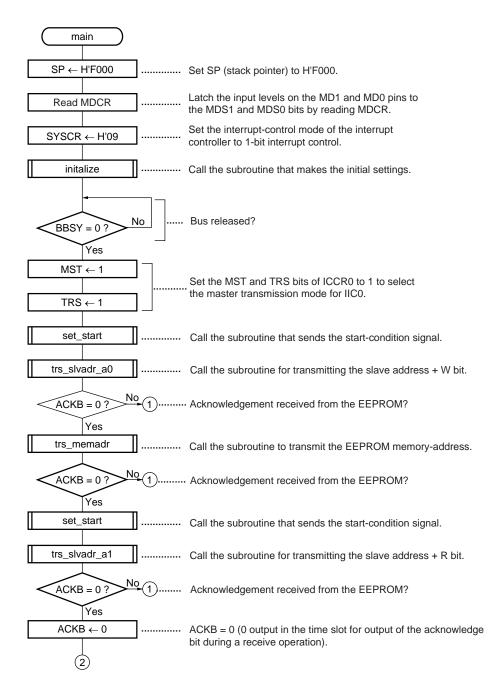

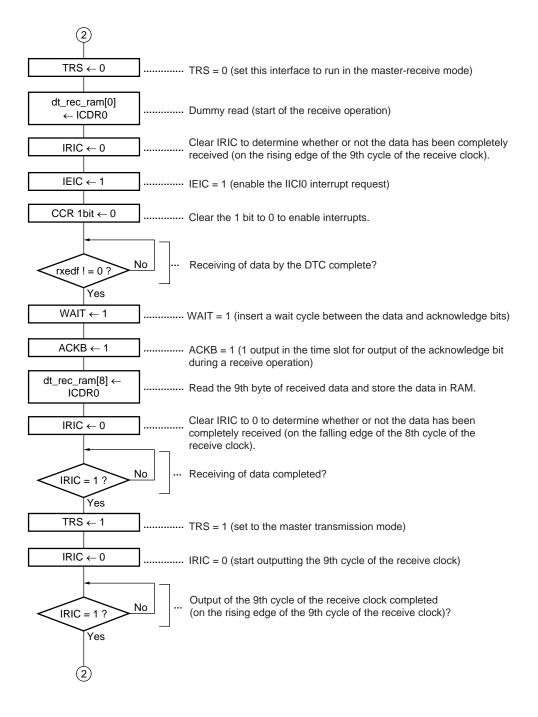

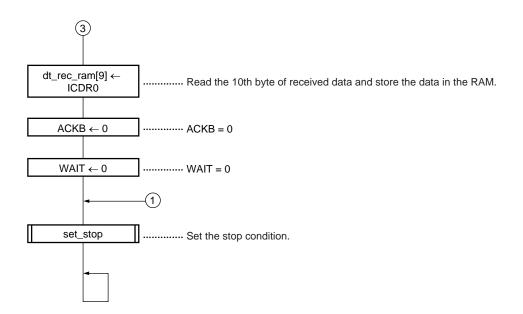

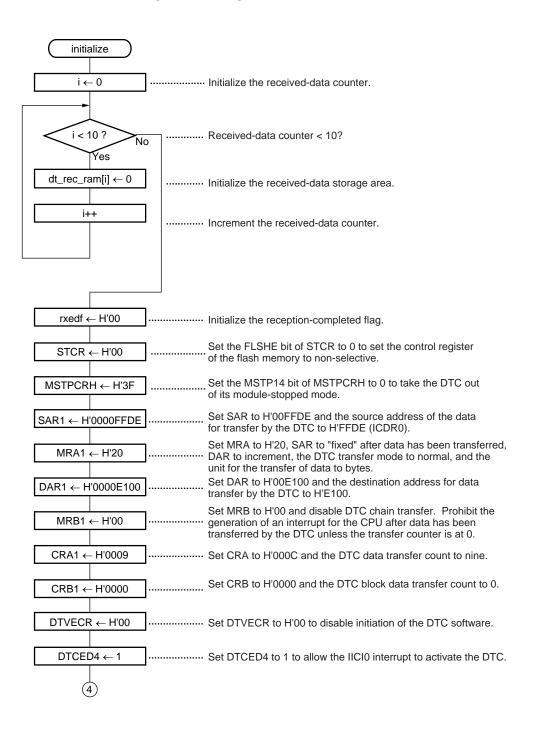

|      | 4.7.4   | Flowchart                                    | 258 |

|      | 4.7.5   | Program List                                 | 266 |

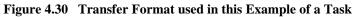

| 4.8  | Slave ' | Fransmission                                 | 272 |

|      | 4.8.1   | Specifications                               | 272 |

|      | 4.8.2   | Description of Operation                     | 273 |

|      | 4.8.3   | Description of Software                      | 275 |

|      | 4.8.4   | Flowcharts                                   | 279 |

|      | 4.8.5   | Program List                                 | 282 |

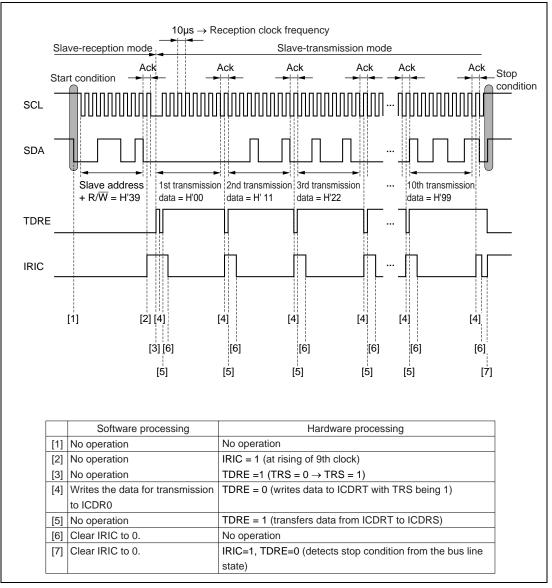

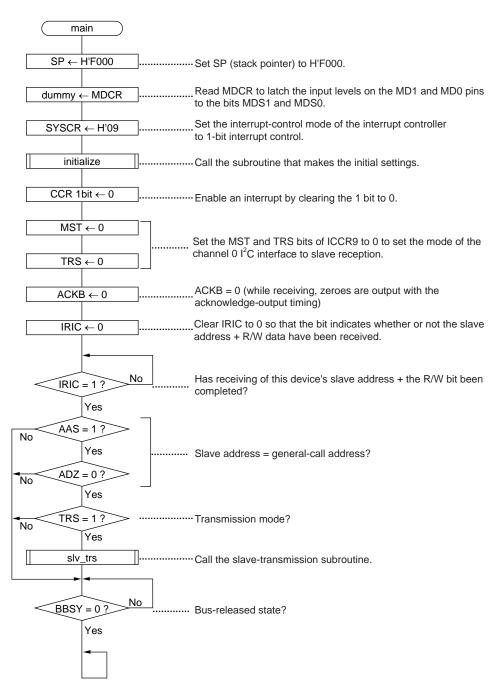

| 4.9  | Slave F | Reception                                    | 286 |

|      | 4.9.1   | Specifications                               | 286 |

|      | 4.9.2   | Description of Operation                     | 288 |

|      | 4.9.3   | Description of Software                      | 289 |

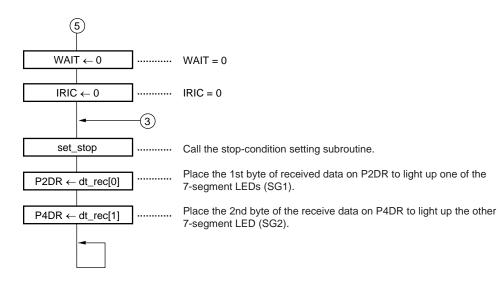

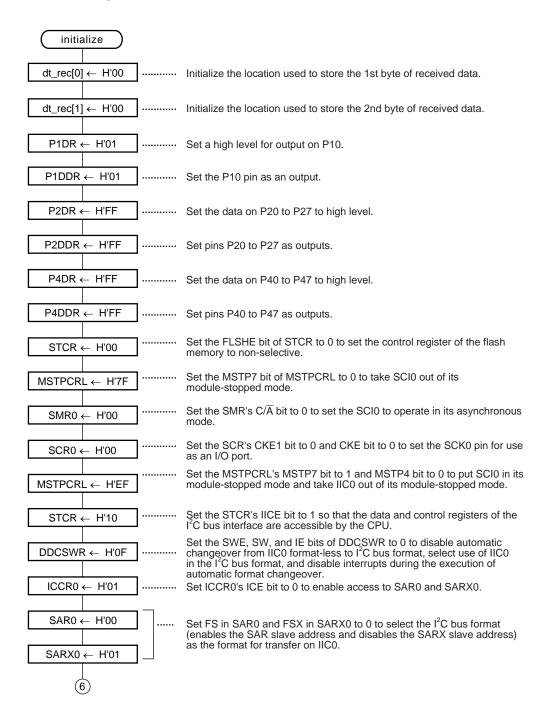

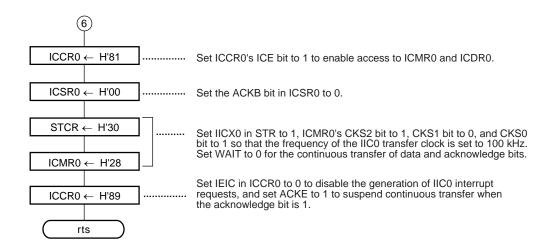

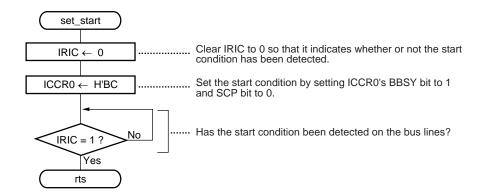

|      | 4.9.4   | Flowcharts                                   | 293 |

|      | 4.9.5   | Program List                                 | 297 |

| 4.10 | Examp   | le of Processing Bus Disconnection           | 301 |

|      | 4.10.1  | Specification                                | 301 |

|      | 4.10.2  | Description of Operation                     | 303 |

|      |         | Description of Software                      |     |

|      | 4.10.4  | Flowcharts                                   | 308 |

|      | 4.10.5  | Program List                                 | 317 |

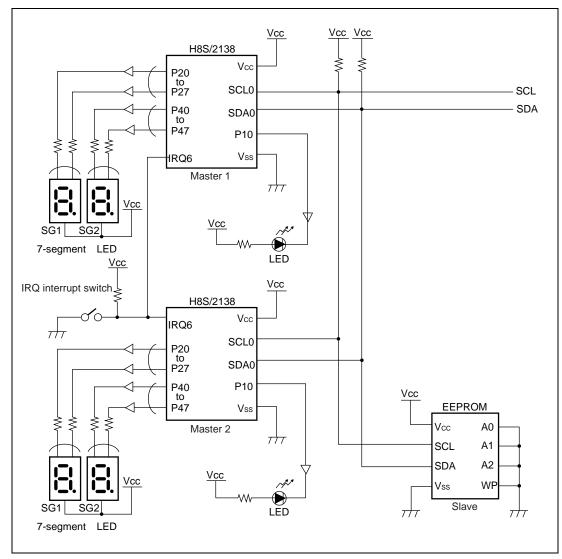

| 4.11 | Bus Co  | nflict                                       | 324 |

|      | 4.11.1  | Specifications                               | 324 |

|      | 4.11.2  | Operation Description                        | 330 |

|      | 4.11.3  | Description of Software                      | 331 |

|      |         |                                              |     |

| 4.11.4 | Flowchart             | 335 |

|--------|-----------------------|-----|

| 4.11.5 | Master-1 program List | 344 |

| 4.11.6 | Master-2 program List | 351 |

#### Introduction

In recent times, the peripheral interfaces for all fields of application have been being unified and standardized because of the need for lower costs and greater utility. The I<sup>2</sup>C bus<sup>\*</sup> interface covered by this application note is one such standardized interface. It is for use as an interface with the control ICs of home appliances, and in controlling the battery packs of notebook-sized PCs, PC monitors, etc.

The I<sup>2</sup>C bus is the standardized form of a bi-directional serial bus system which was developed by Philips in the Netherlands. In products based on this standard, two wires (a clock line and data line) are used to carry mutual data communications among multiple peripheral ICs.

The I<sup>2</sup>C bus interfaces incorporated in Hitachi's 8-bit/16-bit H8/300-series, H8/300L-series, and H8S-series single-chip microcomputers are an implementation of a sub-set of the standard functions and conform to the I<sup>2</sup>C bus interface method proposed by Philips, Ltd. (that is, note that some specifications of the I<sup>2</sup>C bus interface are not completely implemented depending on the condition used).

In sections 1 and 2 of this application note, an outline of the  $I^2C$  bus is given and the specifications and functions of our  $I^2C$  bus-interface module are described. Examples of systems in multi-master configurations are introduced in section 3 and examples of the application of the  $I^2C$  bus interface with H8S-series products are given in section 4.

The operation of the examples of hardware and software described in this application note has been confirmed. However, when they are actually used, be sure to base this usage on a confirmation of their operation.

Note: \*  $I^2C$  Bus: Inter-IC Bus

Rev. 2.0, 11/01, page vi of vi

#### Section 1 Overview of the I<sup>2</sup>C Bus

#### **1.1** Overview of the I<sup>2</sup>C Bus

#### 1.1.1 Features of the I<sup>2</sup>C Bus

Features of the I<sup>2</sup>C bus are shown below.

- An I<sup>2</sup>C bus is made up of two bus lines; a serial data line (SDA) and a serial clock line (SCL). It is easy to extend an I<sup>2</sup>C bus so that it serves more devices.

- In the I<sup>2</sup>C bus, the master-slave relationships among devices is always set up and each device has a particular address. Specifying the particular address of the object of the communication forms a path along which data communications is enabled.

- Any device is able to act as a master (i.e., construction of a multi-master system is possible). A system to avoid competition for bus rights and thus prevent the loss of data has thus been defined for the I<sup>2</sup>C bus interface.

- The maximum data transfer rates are 100 kbps in normal mode and 400 kbps in high-speed mode (up to 3.4 Mbps is defined in version 2.0 of the I<sup>2</sup>C bus specification).

- The limit on the attachment of devices to an I<sup>2</sup>C bus system is defined as 400 pF, which is the upper limit of the bus-load capacity of the system.

- Examples of the standard's application are the SMBus<sup>\*1</sup> and Access.bus<sup>\*2</sup>.

Notes: \*1 SMBus is a form of serial bus devised by Duracell and Intel.

\*2 ACCESS.bus is a form of serial bus devised by Digital Equipment.

#### 1.1.2 Differences with the Serial Communications Interface (SCI)

Hitachi's serial interface is referred to as the serial communications interface (SCI). The differences between this interface and the standard  $I^2C$  interface are listed in the table below.

As listed in table 1.1, an SCI is connected to two data lines, one for transmission and one for reception. Data communications is generally on a one-to-one basis.

On the other hand, communications on an  $I^2C$  bus are bi-directional over a single data line by the equipment to a master. An object is selected for a communication by specifying that object's particular address. This allows the transmission and reception of data between any pair among multiple connected devices. The mechanism for avoiding conflicts over bus access that has been defined for the  $I^2C$  bus means that the bus supports the operation of multi-master systems, in which any device is able to act as the master. The maximum transfer rates are 100 kbps in normal mode and 400 kbps in high-speed mode.

#### Rev. 2.0, 11/01, page 1 of 358

|                             | SCI                      | l²C bus                                       |                                            |  |

|-----------------------------|--------------------------|-----------------------------------------------|--------------------------------------------|--|

|                             | Clock synchronous        | Asynchronous                                  | -                                          |  |

| Used pins                   | Three-line method        | Two-line method                               | Two-line method                            |  |

|                             | Transmission data output | Transmission data output                      | Transmission/reception data (input/output) |  |

|                             | Reception data input     | Reception data input                          | -                                          |  |

|                             | Serial clock             | Serial clock (when an external clock is used) | Serial clock                               |  |

| Transfer rate               | 100 bps to 4 Mbps        | 110 bps to 38.4 kpbs                          | 100 kbps (normal mode)                     |  |

|                             |                          |                                               | 400 kbps (high-speed<br>mode)*             |  |

| Transmission/re             | ec Impossible            | Impossible                                    | Possible;                                  |  |

| eption with<br>multiple ICs |                          |                                               | slave devices have<br>individual addresses |  |

#### Table 1.1Differences from SCI

Note: \* Hs mode (maximum transfer speed: 3.4 Mbps) which is defined in the I<sup>2</sup>C Bus Specifications Ver. 2.0 is not supported.

#### **1.1.3** Connection Type of the I<sup>2</sup>C bus Interface

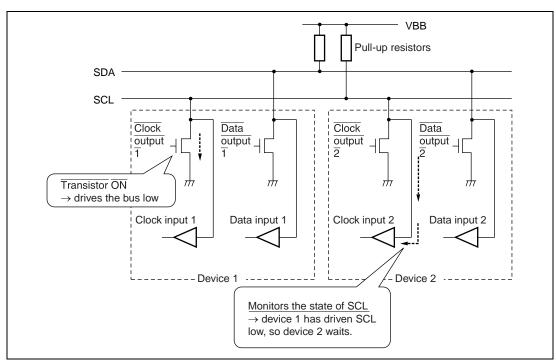

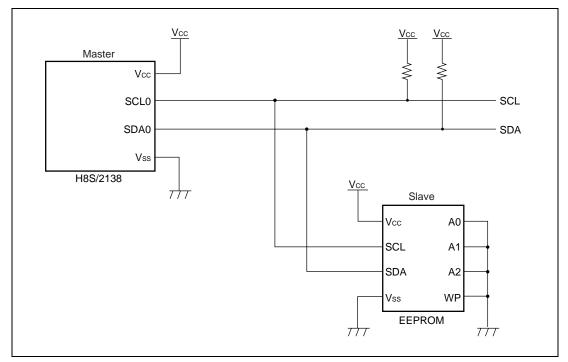

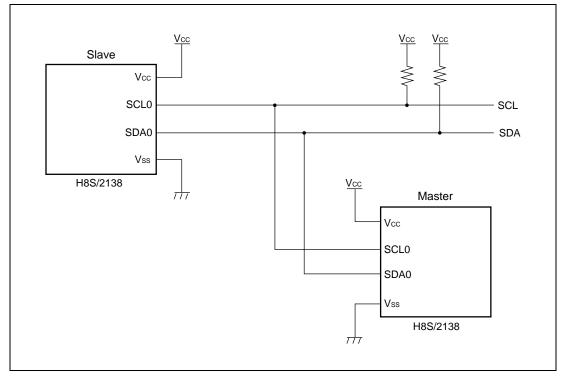

Figure 1.1 shows the form of a connection between  $I^2C$  bus interfaces. As shown in the drawing, the  $I^2C$  bus is made up of clock line SCL and data line SDA, and they are connected to the power source of the bus, VBB, via pull-up resistors. The SCL and SDA pins of devices 1 and 2 have wired-AND connections with the SCL and SDA lines, respectively.

In the figure, device 2 has been monitoring the state of the SCL line and thus confirms that another device is using the bus when device 1 drives the SCL line low. Furthermore, even while device 1 is using the bus and thus driving the SCL line, device 2 is able to drive SCL low and place the device 1 in its wait state, in terms of communications operations (for details, see the I<sup>2</sup>C bus specification).

Figure 1.1 Form of a Connection between I<sup>2</sup>C Bus Interfaces (when device 1 initiates the connection by driving SCL low)

#### **1.2** Method of Data Transfer over an I<sup>2</sup>C Bus

#### 1.2.1 Basic Concepts and Elements of Data Transfer over an I<sup>2</sup>C Bus

To start with, the basic concepts and elements of data transfer over an I<sup>2</sup>C bus are given below.

#### (1) Master device

The master device generates the clock signals that synchronize data communications and sets the start and stop conditions that indicate the beginning and end of each data communication.

#### (2) Slave device

The slave device is a device other than a master device which is on the  $I^2C$  bus.

#### (3) Transmission device

The transmission device is a device which is transmitting data. It may be a master device or a slave device.

#### (4) Reception device

#### Rev. 2.0, 11/01, page 3 of 358

The reception device is a device which is receiving data. It may be a master device or a slave device.

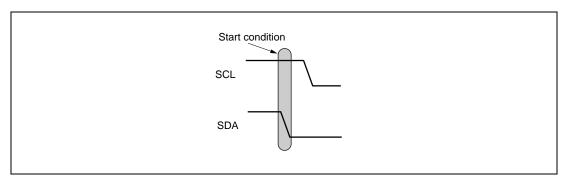

#### (5) Start condition

The start condition is set by changing the level on the SDA line from high to low while the SCL line is high. This is shown in figure 1.2. A data communication is initiated by this operation. The start condition is set by the master device.

Figure 1.2 Start Condition

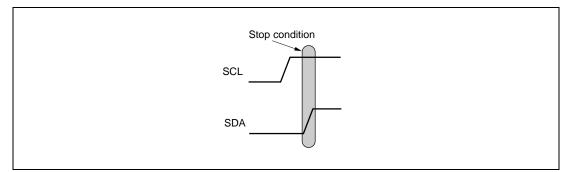

#### (6) Stop condition

The stop condition is set by changing the level on the SDA line from low to high while the SCL line is high. This is shown in figure 1.3. A data communication is stopped by this operation. The stop condition is set by the master device.

Figure 1.3 Stop Condition

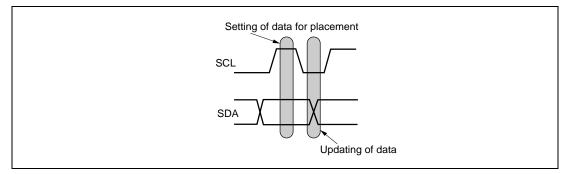

#### (7) Output timing of the data

Figure 1.4 shows the timing of data output. The data on the SDA line is updated while the SCL line is low and the data on the SDA line is settled for placement on the SDA line while the SCL line is high. The signal on the SDA line only changes while the SCL line is high, that is, only from the setting of the start condition to the setting of the stop condition.

Rev. 2.0, 11/01, page 4 of 358

Figure 1.4 Timing of Data Output

#### (8) Master transmission

Master transmission is the activity when a master device is a transmission device. This is the activity when a slave address is transmitted after the start condition has been issued or a command is transmitted to the slave device, etc.

#### (9) Master reception

Master reception is the activity when a master device is a reception device.

#### (10) Slave transmission

Slave transmission is the activity when a slave device is a transmission device.

#### (11) Slave reception

Slave reception is the activity when a slave device is a reception device. A master device transmits a slave address after the start condition is in place to initiate slave-reception activity in the selected slave device.

#### (12) Bus-released state

This is the state in which no  $I^2C$  bus devices are in communication. While this state applies, both the SCL and SDA lines stay at the logic-high level.

#### (13) Bus-occupied state

This is the state in which something is communicated over the  $I^2C$  bus device. The system returns to the bus-released state after the transmission master device has set a stop condition.

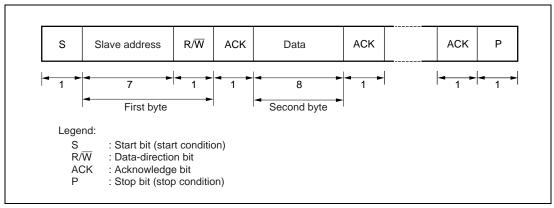

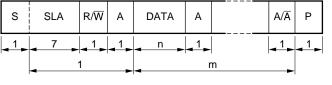

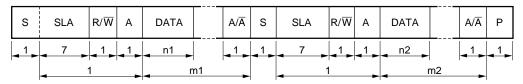

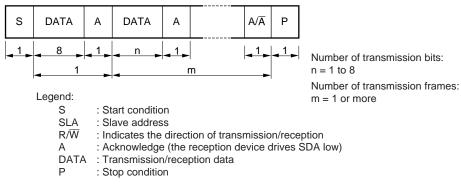

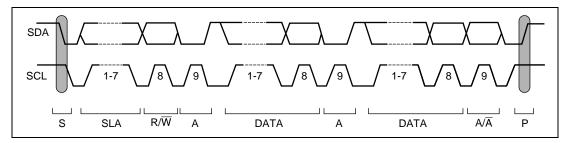

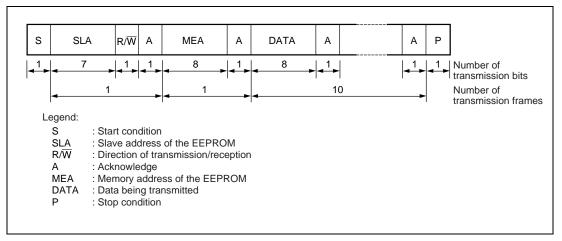

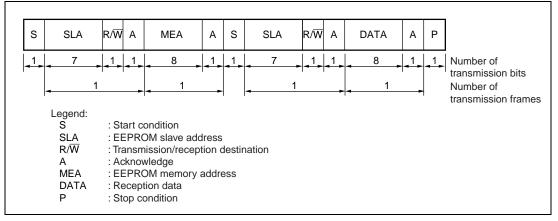

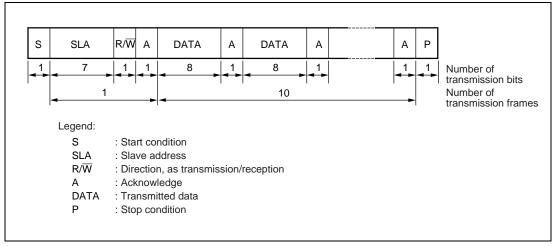

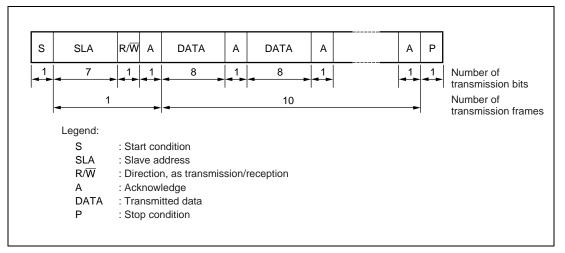

#### (14) Format for data transfer

Figure 1.5 shows the format for the transfer of data over the  $I^2C$  bus. The start and stop condition signals and the SCL clock are generated by the master device. The first data after the start

Rev. 2.0, 11/01, page 5 of 358

#### Renesas

condition carry the slave address. The eighth bit indicates the direction of communication. A zero value for this bit indicates that the subsequent data is transmitted from a master device while a one indicates that the communication after the second byte is for reception by a master device. The slave address is defined by 7 bits<sup>\*1</sup>, and is set between B'0000000 and H'1111111 by the user. However, address B'0000000 (referred to as the general call address) and certain other addresses are reserved.

Data is transferred in 1-byte (8-bit) units. The ninth bit is an acknowledge bit from the reception device. For example, when a slave address is transmitted from the master device, the corresponding slave device drives SDA low on the ninth clock cycle to return an acknowledgement to the master.

There is no limit on the number of bytes of data that can be transferred between the setting of a start condition and of the corresponding stop condition. A communication is completed when the stop condition is set.

Notes: \*1 The I<sup>2</sup>C bus specification describes 10-bit addresses. Hitachi's I<sup>2</sup>C bus interface module does not support this 10-bit address specification.

\*2 The general call address, B'0000000, is used to specify all slave addresses that are connected to the bus.

Figure 1.5 Format for Data Transfer

#### **1.2.2** Procedure for Data Transfer (Example: master transmission, slave reception)

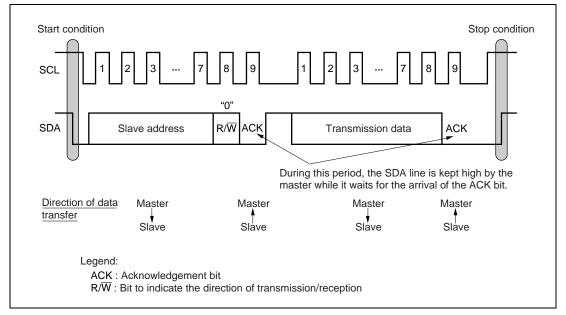

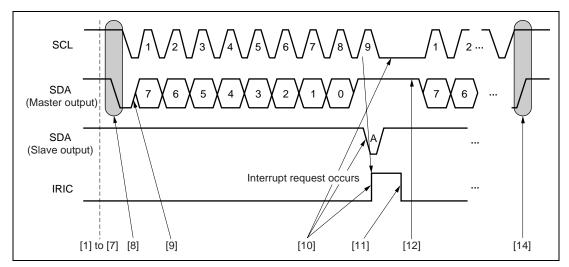

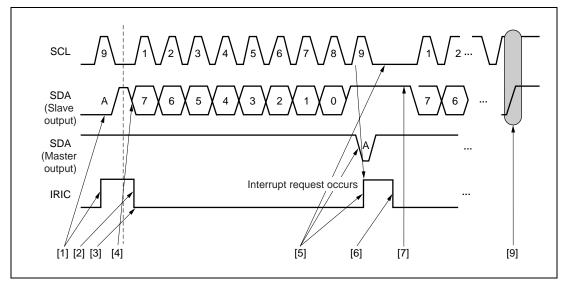

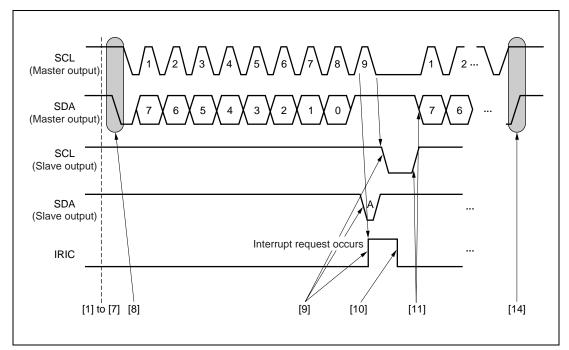

Figure 1.6 shows an example when the master device transmits 1 byte of data to the slave device.

In the first place, the master device sets the start condition by changing the level on the SDA line from high to low while the SCL line is high. Next, the master outputs a clock signal on the SCL line and outputs, on the SDA line, the address of the slave that will be the target of this communication. The address of the slave is defined by 7 bits. A bit to indicate the direction of the communication is added as an eighth bit.

Rev. 2.0, 11/01, page 6 of 358

The master device releases the SDA line in the ninth clock cycle so that it is able to receive an acknowledgement of selection from the slave device. The selected slave device drives the SDA line low during this clock cycle to return the acknowledgement.

The master device receives the acknowledgement from the slave at the specified address and keeps the SCL line low until the first byte of data is ready for transmission. When the first byte is ready, the master device outputs the data on the SDA line while outputting a clock signal on the SCL line. In the same way as for the slave address, the selected slave device returns an acknowledgement to the master device in the ninth clock cycle. This signal acknowledges that the slave device has received the data without problems.

The master device keeps the SCL line low while receiving this acknowledgement from the slave device. To set the stop condition, the level on the SDA line is then changed from low to high while the SCL line is high.

During the transmission of data, the slave device may become unable to receive the data because it is busy with some other processing. In this case, the slave device keeps the SCL line at its low level so that the master device stays in its wait state. The timing with which the slave device is able to drive SCL low is at the same time as the master device is driving SCL low.

Figure 1.6 Format for Data Transfer (Master Transmission, Slave Reception)

#### **1.3** The Single-Master and Multi-Master Configurations

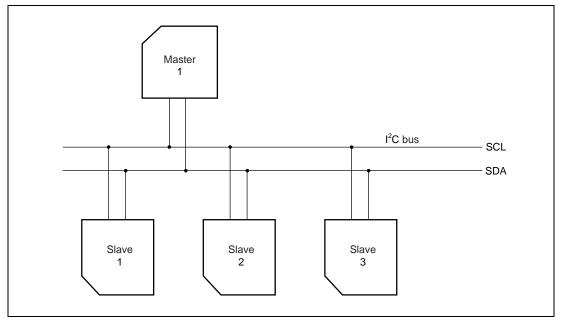

#### 1.3.1 Single-Master

The master device sets start and stop conditions to control data communications. It also outputs the synchronizing clock signal on the SCL line and slave addresses so that data can be transmitted and received. The system configuration shown in figure 1.7, in which a set device is always the master, is a single-master configuration.

Figure 1.7 A Single-Master Configuration

#### 1.3.2 Multi-Master

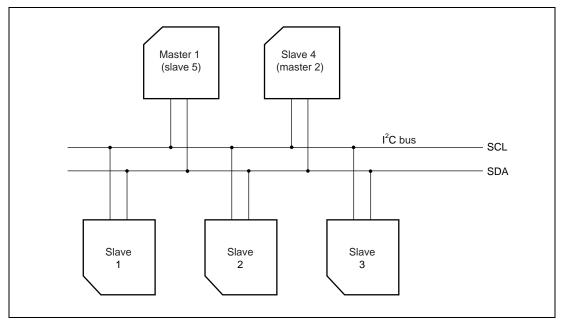

A configuration in which two or more devices are included as masters in one system is called a multi-master configuration.

The master device is only able to start the transfer of data after the bus has been released. However, in the multi-master configuration, multiple master devices may simultaneously attempt to start to transfer data. There is then a conflict over bus rights. The specifications of the  $I^2C$  bus thus include a procedure for adjusting communications when there is a conflict over bus rights. For details, see 1.4, Procedure for Adjusting Communications.

Figure 1.8 A Multi-Master Configuration

#### 1.4 Procedure for Adjusting Communications

The specification of the I<sup>2</sup>C bus interface includes a procedure for adjusting communications to prevent conflicts over bus rights. This supports systems in multi-task configurations.

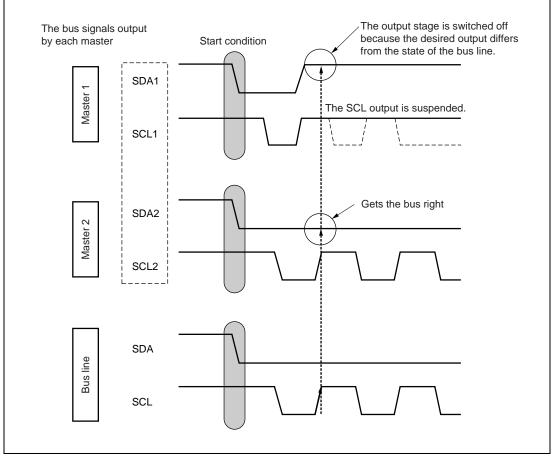

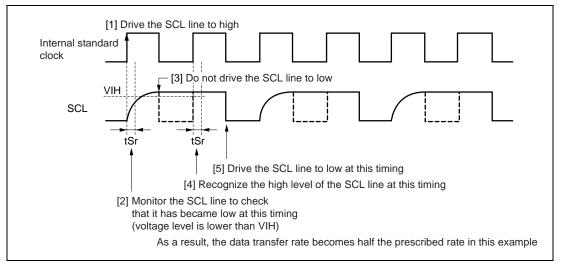

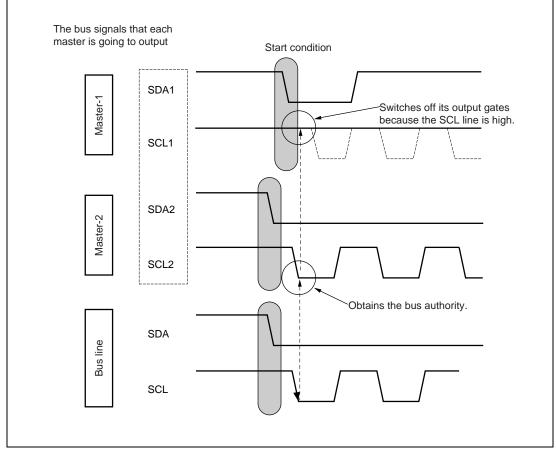

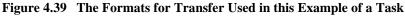

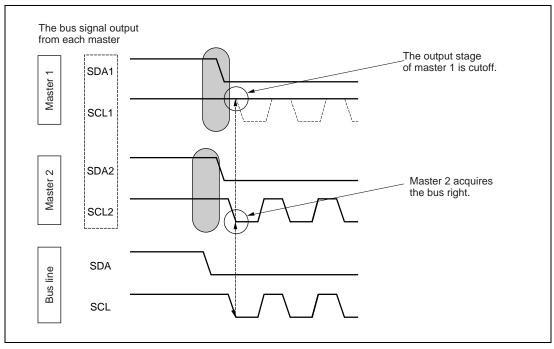

Master devices monitor the bus line to confirm that the bus has been released before they set the start condition. When the bus is released, multiple master devices may attempt to set the start condition. A single valid master device is thus defined by the procedure shown in figure 1.9.

In the I<sup>2</sup>C bus, the data is settled for placement on the SDA line while the SCL line is at its high level. Therefore, each device monitors for the rising edge of the SCL line after the start condition has been set and compares the state of the SDA line with the bit of data that each device is attempting to send (this initial data will be the slave address). If device 1 is driving SDA high while device 2 is driving SDA low, the actual SDA line will be low because of the wired-AND connection, so device 1 confirms that this differs from the bit which is attempting to output. Device 1 then switches the data output stage off. In this example, device 2 continues its operation as a master device (see figure 1.9). When all masters are trying to specify the address of the same slave device, the operation will proceed to the next step and the first bit of data will be compared, and so on.

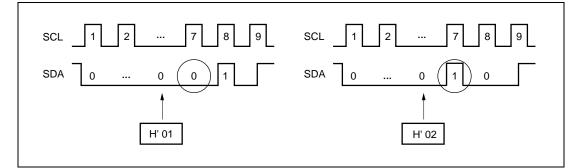

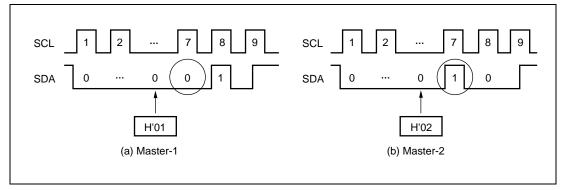

For example, when the data to be transferred transfer data are H'01 and H'02 as shown in figure 1.10, the datum H'01 is low over a longer period, and its transmission thus continues to be enabled. In the same way, the general call address (H'00) has the highest priority.

Rev. 2.0, 11/01, page 9 of 358

Figure 1.9 Procedure for Adjusting Communications (Detection of the Loss of Bus Arbitration)

Figure 1.10 A Specific Example of the Adjustment of Communications

# Section 2 Explanation of the Interface Functions of the $I^2C$ Bus

#### 2.1 Lineup of Products that Incorporate the I<sup>2</sup>C Bus Interface

Our I<sup>2</sup>C bus interface modules may be roughly classified into two groups.

- (1) H8 family: The models which feature the first I<sup>2</sup>C bus interface module to have been manufactured by Hitachi.

- (2) H8S family: An enhanced version of the H8 family.

Table 2.1 lists Hitachi's products that incorporate the  $I^2C$  bus interface and the types of the  $I^2C$  bus interface modules.

| Series |         | Product name | Numbe<br>of pins |     | el MASK* <sup>1</sup> | F-ZTA | T™ ZTAT® | l²C<br>module |

|--------|---------|--------------|------------------|-----|-----------------------|-------|----------|---------------|

| H8/300 | H8/3217 | H8/3217      | 64, 80           | 2ch | 0                     | _     | 0        | H8 series     |

| series | series  | H8/3216      |                  | 2ch | 0                     | _     | _        | _             |

|        |         | H8/3214      |                  | 2ch | 0                     | _     | 0        | _             |

|        |         | H8/3212      | _                | 2ch | 0                     | _     | _        | _             |

|        |         | H8/3202      | _                | 1ch | 0                     | _     | _        | _             |

|        | H8/3337 | H8/3337Y     | 80, 84           | 1ch | 0                     | _     | 0        | _             |

|        | series  | H8/3337YF    |                  | 1ch | _                     | 0     | _        | _             |

|        |         | H8/3337SF    | _                | 1ch | _                     | 0     | _        | _             |

|        |         | H8/3336Y     | _                | 1ch | 0                     | _     | _        | _             |

|        |         | H8/3334Y     | _                | 1ch | 0                     | _     | 0        | _             |

|        |         | H8/3334YF    | _                | 1ch | _                     | 0     | _        | _             |

|        | H8/3437 | H8/3437      | 100              | 1ch | 0                     | _     | 0        | _             |

|        | series  | H8/3437YF    | _                | 1ch | _                     | 0     | _        | _             |

|        |         | H8/3437SF    | _                | 1ch | _                     | 0     | _        | _             |

|        |         | H8/3436      | _                | 1ch | 0                     | _     | _        | _             |

|        |         | H8/3434      | _                | 1ch | 0                     |       | 0        | _             |

|        |         | H8/3434F     | _                | 1ch | —                     | 0     | —        | _             |

Table 2.1

Products that Incorporate the I<sup>2</sup>C Bus Interface

| Series       |                     | Product<br>name | Numbe<br>of pins | r Chann | el MASK* <sup>1</sup> | F-ZTAT <sup>™</sup> | ' ZTAT® | l²C<br>module |

|--------------|---------------------|-----------------|------------------|---------|-----------------------|---------------------|---------|---------------|

| H8/300       | H8/3567             | H8/3567         | 42, 44           | 2ch     | 0                     | _                   | 0       | H8S           |

| series       | series              | H8/3564         | -                | 2ch     | 0                     | _                   | _       | series        |

|              |                     | H8/3561         | -                | 2ch     | 0                     | _                   | _       | _             |

|              |                     | H8/3567U        | -                | 2ch     | 0                     | _                   | 0       | _             |

|              |                     | H8/3564U        | -                | 2ch     | 0                     | _                   | _       | _             |

|              | H8/3577             | H8/3577         | 64               | 2ch     | 0                     | _                   | 0       | _             |

|              | series              | H8/3574         | -                | 2ch     | 0                     | 0                   | _       | _             |

| H8/300L      | H8/3947             | H8/3947         | 100              | 2ch     | 0                     | _                   | 0       | H8 series     |

| series       | series              | H8/3946         | -                | 2ch     | 0                     | _                   | _       | _             |

|              |                     | H8/3945         | -                | 2ch     | 0                     | _                   | _       | _             |

| H8/300H      | H8/3664             | H8/3664         | 42, 64           | 1ch     | 0                     | 0                   | _       | H8S           |

| Tiny series* | <sup>2</sup> series |                 |                  |         |                       |                     |         | series        |

| H8S series   | H8S/2100            | H8S/2127        | 64, 80           | 2ch     | 0                     | _                   | _       | H8S           |

|              | series              | H8S/2126        | -                | 2ch     | 0                     | _                   | _       | series        |

|              |                     | H8S/2128F       | -                | 2ch     | _                     | 0                   | _       | _             |

|              |                     | H8S/2138        | 80               | 2ch     | 0                     | _                   | _       | _             |

|              |                     | H8S/2137        | -                | 2ch     | 0                     | _                   | _       | _             |

|              |                     | H8S/2138F       | -                | 2ch     | _                     | 0                   | _       | _             |

|              |                     | H8S/2148        | 100              | 2ch     | 0                     | _                   | _       | _             |

|              |                     | H8S/2147        | -                | 2ch     | 0                     | _                   | _       | _             |

|              |                     | H8S/2148F       | -                | 2ch     | _                     | 0                   | _       | _             |

|              |                     | H8S/2147NF      |                  | 2ch     | _                     | 0                   | _       | _             |

|              |                     | H8S/2149YV<br>F | ,                | 2ch     | _                     | 0                   | _       | _             |

|              |                     | H8S/2169YV<br>F | ' 144            | 2ch     |                       | 0                   | —       |               |

|              |                     | H8S/2194        | 112              | 1ch     | 0                     | —                   | _       | _             |

|              |                     | H8S/2193        | -                | 1ch     | 0                     | _                   |         |               |

|              |                     | H8S/2192        | -                | 1ch     | 0                     | _                   |         |               |

|              |                     | H8S/2191        | -                | 1ch     | 0                     | _                   | _       |               |

|              |                     | H8S/2194F       | _                | 1ch     | _                     | 0                   | _       | _             |

#### Table 2.1 Products that Incorporate the I<sup>2</sup>C Bus Interface (continued)

| Series     |          | Product<br>name | Number<br>of pins | Channel | MASK*1                  | F-ZTAT <sup>™</sup>     | <b>ZTAT</b> <sup>®</sup> | l²C<br>module |

|------------|----------|-----------------|-------------------|---------|-------------------------|-------------------------|--------------------------|---------------|

|            |          | H8S/2199        |                   | 2ch     | 0                       | _                       | _                        |               |

|            |          | H8S/2198        | _                 | 2ch     | 0                       | _                       | _                        | _             |

|            |          | H8S/2197        | -                 | 2ch     | 0                       | _                       | _                        | _             |

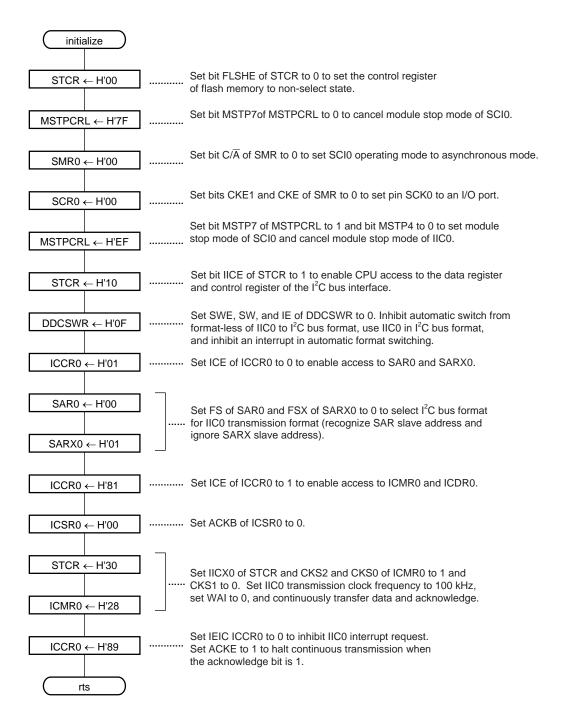

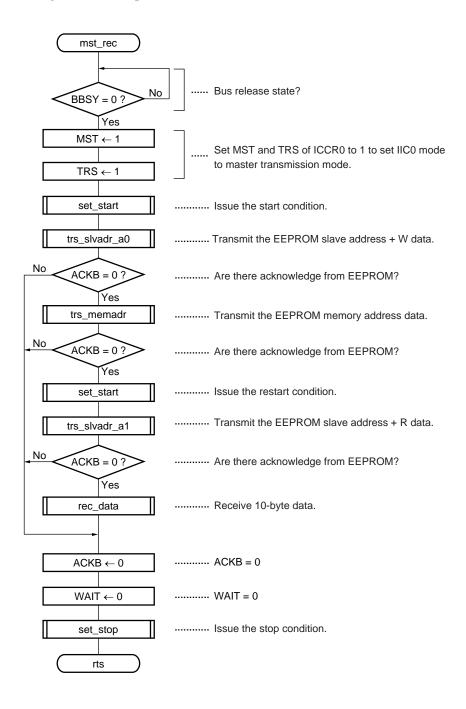

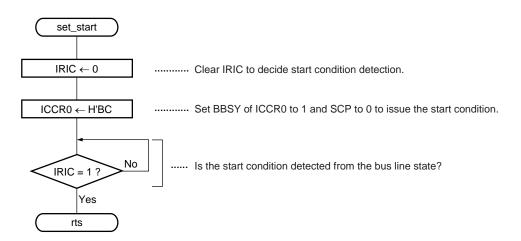

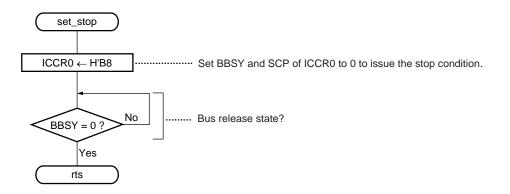

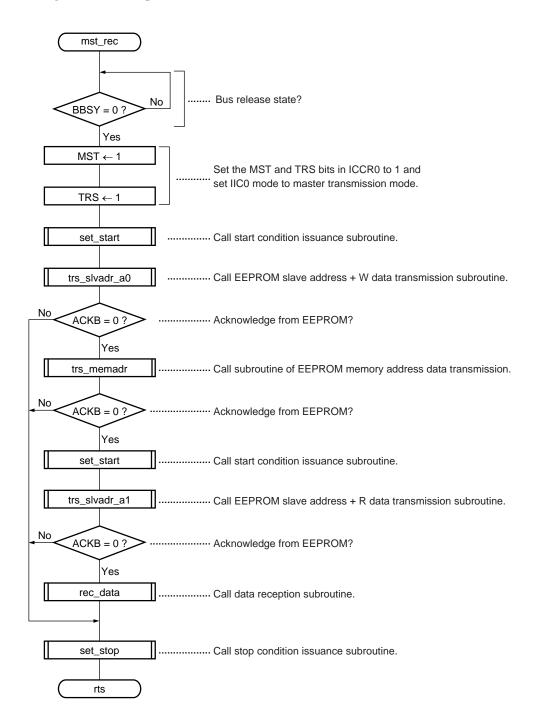

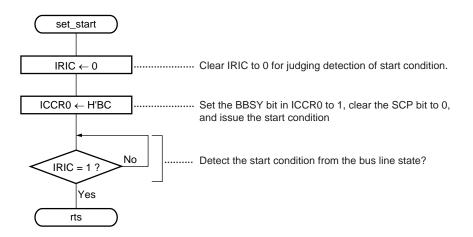

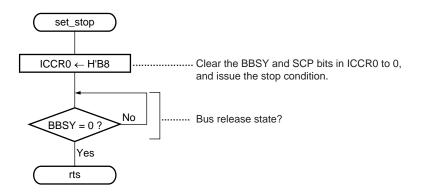

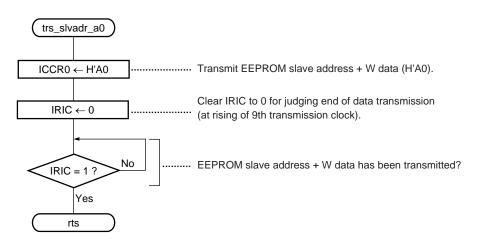

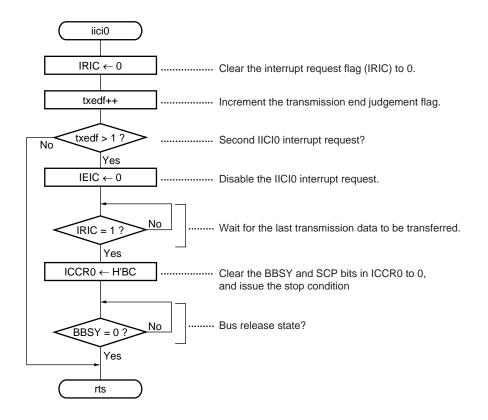

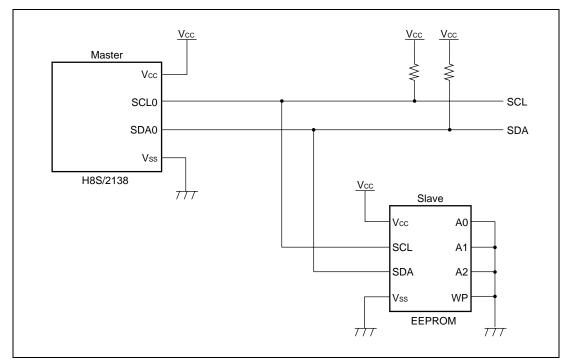

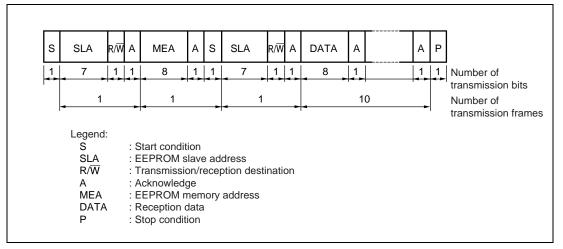

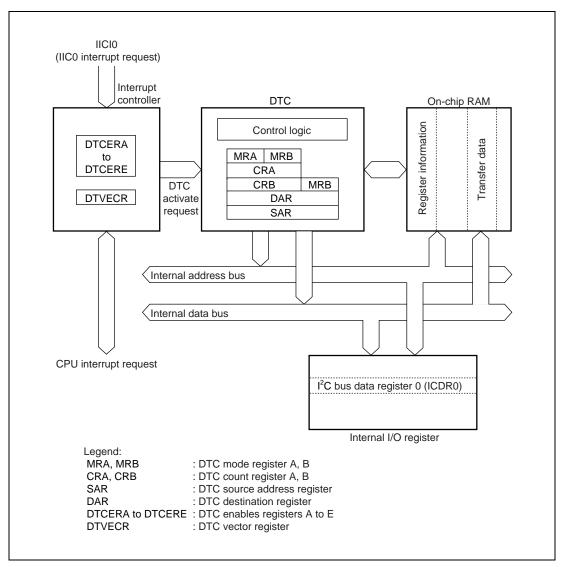

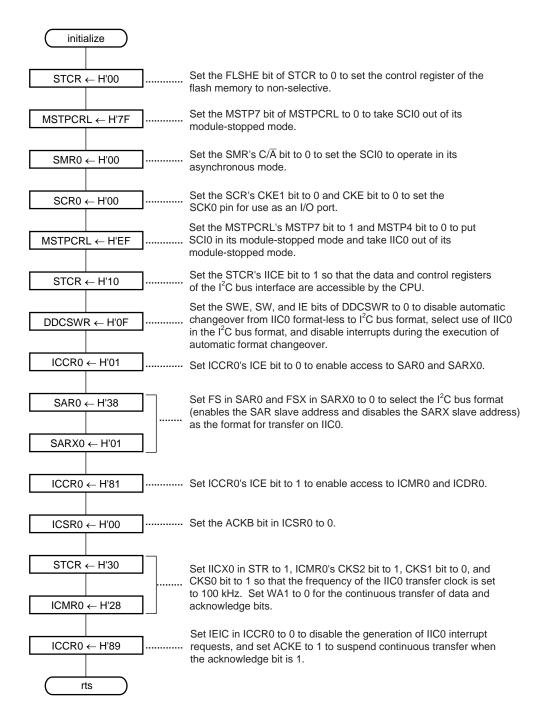

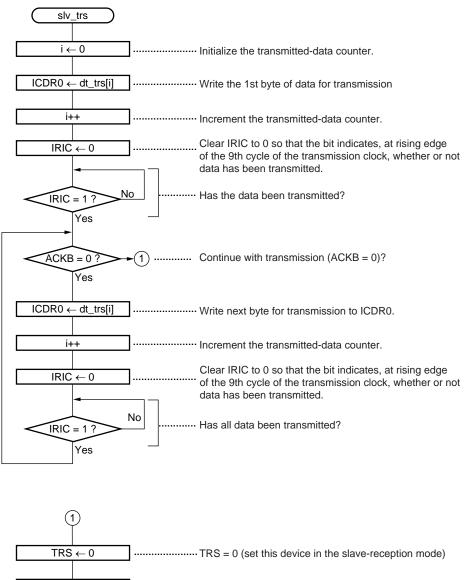

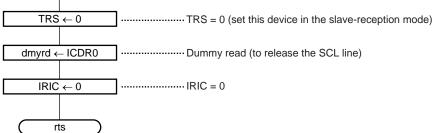

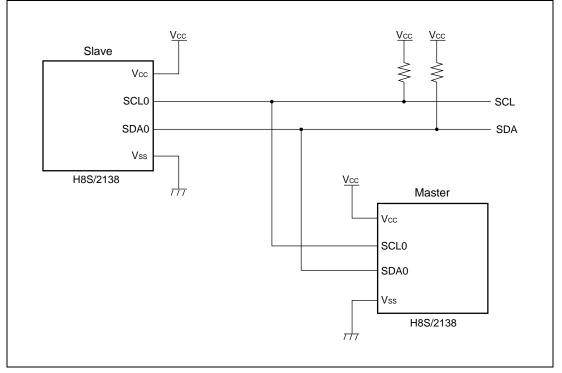

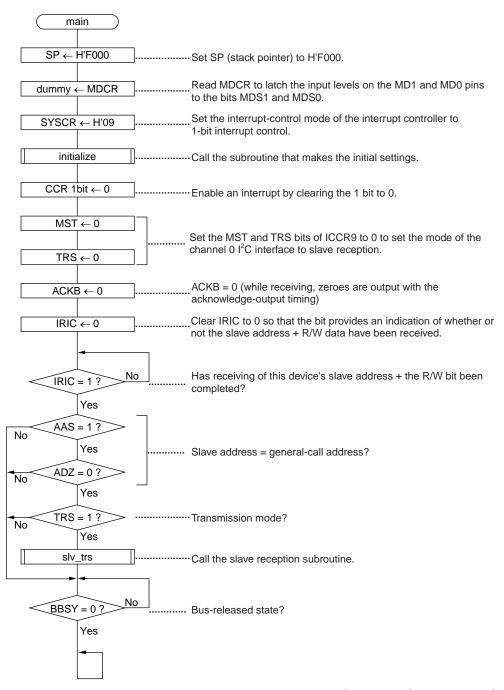

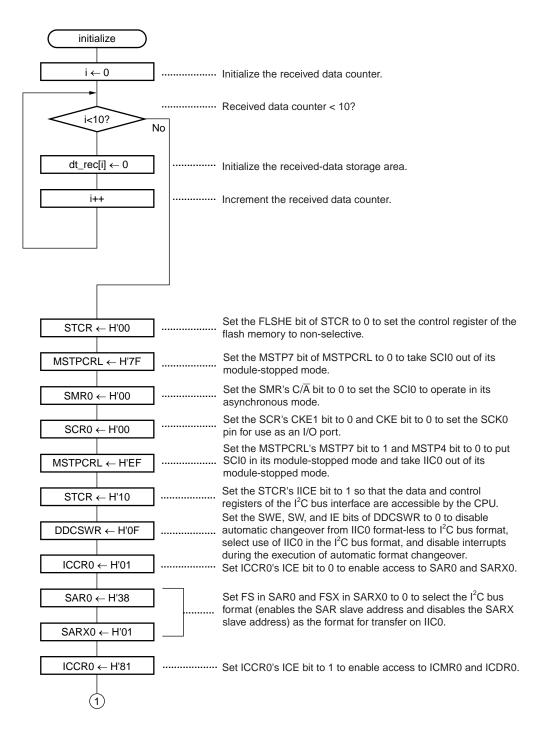

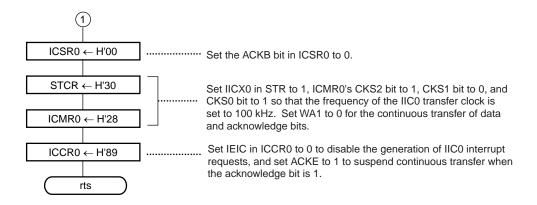

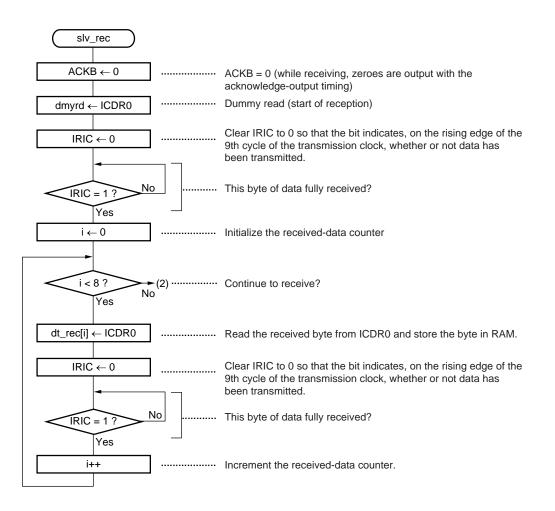

|            |          | H8S/2196        | _                 | 2ch     | 0                       | _                       | _                        | _             |