# TI Designs Analog Input, Output, and Relay Drive Output Module for Smart Grid IEDs

# Texas Instruments

# **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help *you* accelerate your time to market.

# **Design Resources**

| TIDA-00310 | Tool Folder Containing Design Files |

|------------|-------------------------------------|

| ADS8684    | Product Folder                      |

| DAC8760    | Product Folder                      |

| OPA188     | Product Folder                      |

| TCA6408A   | Product Folder                      |

| TPL7407L   | Product Folder                      |

| TPS7A1650  | Product Folder                      |

| TPS7A1633  | Product Folder                      |

|            |                                     |

TI E2E<sup>TM</sup> Community

ASK Our E2E Experts WEBENCH® Calculator Tools

#### **Design Features**

- DC Analog Input Design Based on ADS8684

4-Channel 16-Bit ADC

- Provision to Measure Two Current Inputs and Two Voltage Inputs

- Accuracy of < ±0.2% of Full Scale at 25°C</li>

- DC Analog Output Design Based on DAC8760 Single-Channel 16-Bit Digital Analog Converter (DAC)

- Provision for Two Output Channels (Each Channel Configurable as Either Voltage or Current Output)

- Uses SPI With Daisy Chain With Two DAC8760s

- Accuracy < ±0.2% Full Scale Value At 25°C</li>

- TPL7407L Low-Side Driver Configured to Drive Six Relay Outputs

- Relay-Drive Output Supports Coil Voltage Rating of 12-, 15-, and 24-V DC

- TCA6408A I/O Expander With I2C Interface to Provide Inputs to TPL7407L for Relay Control

#### **Featured Applications**

- Multifunction Protection Relay

- Power Quality Meters

- Substation Automation Products and Remote Terminal Units (RTUs)

- I/O Expansion Modules

All trademarks are the property of their respective owners.

#### System Description

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

Protection relays are commonly found along the entire grid infrastructure pathway from generation to transmission and distribution. Protection relays allow operators to monitor and control the grid at different points. The two main functionalities of a protection relay are measurement and protection. In modern protection relays, communication is also an integral part of the solution, enabling operators to remotely monitor and operate the grid infrastructure. The protection relay typically functions as the local intelligence that signals to a circuit breaker to open or close. The basic purpose of a protection relay is to protect the grid (further downstream) in the event of a malfunction. The protection relay protects the grid by monitoring the current and voltage on specific lines on the grid. The circuit breaker sits on the line. The inputs into a protection relay are typically the current and voltage from a sensor on the line, plus any communication from other related auxiliary equipment or sensor on the grid communication network, for example, health information of the transformer from temperature and pressure sensors. The output consists of signals to a circuit breaker (to turn open or close) and communication to the grid network. In situations where the protection relay detects a fault, the relay commands a breaker to open the line, thus protecting everything down the line from the protection relay.

Remote terminal units are also used in entire smart grid infrastructures to record parameter information related to the health of equipment like generators, motors, or transformers.

The accurate measurement of the voltage, current, or other parameters like temperature pressure or the vibration of power system equipment are prerequisites to any form of control, ranging from automatic closed-loop control to the recording of data for statistical purposes. There are a variety of ways to measure these parameters, including the use of direct-reading instruments and electrical measuring transducers.

# 1.1 Instrumentation in Smart Grid

#### 1.1.1 Analog Inputs

Transducers produce an accurate DC analogue output (usually a current) that corresponds to the parameter being measured (the measured). Outputs from transducers may be used in many ways, from the simple presentation of measured values for an operator, to utilization by a network automation scheme to determine the control strategy. There are two types of transducers:

- 1. Analog transducers where output is a function of time

- 2. Digital transducers which use analog transducers along with digital processing

Analog transducers are used for the following measurements in power systems:

- Voltage and current measurement

- Vibration measurement

- · Temperature and pressure measurement of oil in the transformer

- · Status signal for breaker health

- Tap changer status signal

CT and VT are normally preferred to measure voltage and current. For other parameters, transducers with the following outputs are used:

- (a) Voltage outputs ranging from

- (a) ±10-V DC

- (b) 0- to 10-V DC

- (c) 0- to 5-V DC

2

- 2. Current outputs ranging from

- (a) ±20 mA

- (b) 0 to 20 mA

- (c) 0 to 24 mA

- (d) 4 to 20 mA

Protection relays and RTUs use the analog input module for interfacing with such transducers. This interfacing uses analog front end (AFE), which comprises ADC, programmable gain array, the signal-conditioning chain, and other filter circuits.

The TI portfolio includes devices which contain the AFE for the measurement of 4-8 channels in a single chip.

#### 1.1.2 Analog Outputs

Multifunction protection relays and RTUs also include analog outputs that can transfer any parameters such as energy to an RTU or protection relay. These analog outputs also provide the required input supply for an analog instrumentation system.

The analog output can either be a voltage output or a current output.

Voltage output can be

- 0- to 10-V DC

- 0- to 5-V DC

- ±10-V DC

whereas current output can be

- ±20 mA

- 0 to 20 mA

- 0 to 24 mA

- 4 to 20 mA

Analog outputs use DAC which can be 12- to 16-bit. The TI portfolio includes several DAC devices that can be configured to provide either voltage or current outputs.

#### 1.1.3 Relay Drive Outputs

Multifunction protection relays and RTUs also include relay outputs. This relay output uses electromechanical relay switching to convey the status of particular incidents, especially for the interlocking of protection relays and the circuit breaker system.

Relay outputs can also provide power to the auxiliary equipment. The electromechanical relay used to provide power to auxiliary equipment are power relays with ratings from 8 A to 12 A at 240-V AC. Such relay outputs are also known as wet contacts.

The basic solution to drive electromechanical relays utilizes a discrete bipolar junction transistor (BJT) or metal-oxide semiconductor field-effect transistor (MOSFET). This solution requires more PCB space and is also unreliable because of stress occurrences due to the switching of inductive loads. This solution is also prone to malfunction due to the effect of electromagnetic interference (EMI). The number of ports required for driving the relays rises with an increase in the number of relays.

The TI portfolio includes a single-chip solution, which can be used to drive seven electromechanical relays with high current ratings simultaneously. The TI portfolio also includes an I2C to parallel-bus expander, which can be used to drive the relay driver, reducing the number of interfaces or driving ports from the MCU.

System Description

#### 1.2 TI Design

The TI Designs Reference Design Library is a robust reference design library spanning across analog, embedded processor, and connectivity products. All TI designs include schematics, block diagrams, BOMs, and design files.

This reference TI design provides details for the design and development of an analog input module, analog output module, and relay output-driver module, which can be directly used in a protection relay and RTU system.

This TI design also includes an external protection circuit that has been tested and verified to be compliant with the IEC61000-4 standard for electrostatic discharge (ESD).

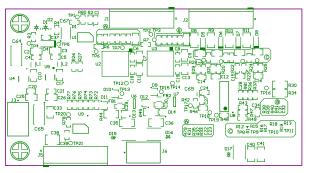

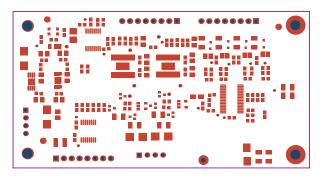

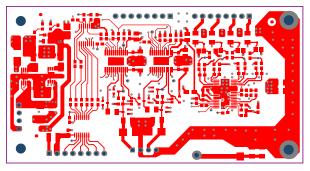

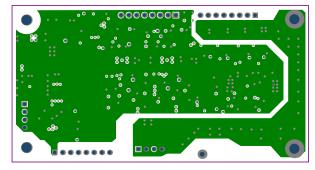

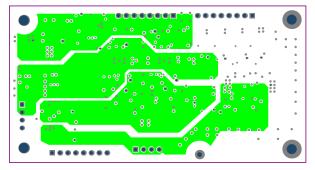

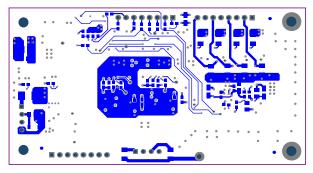

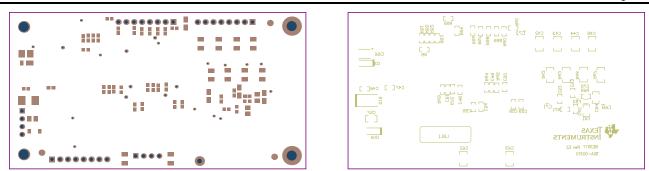

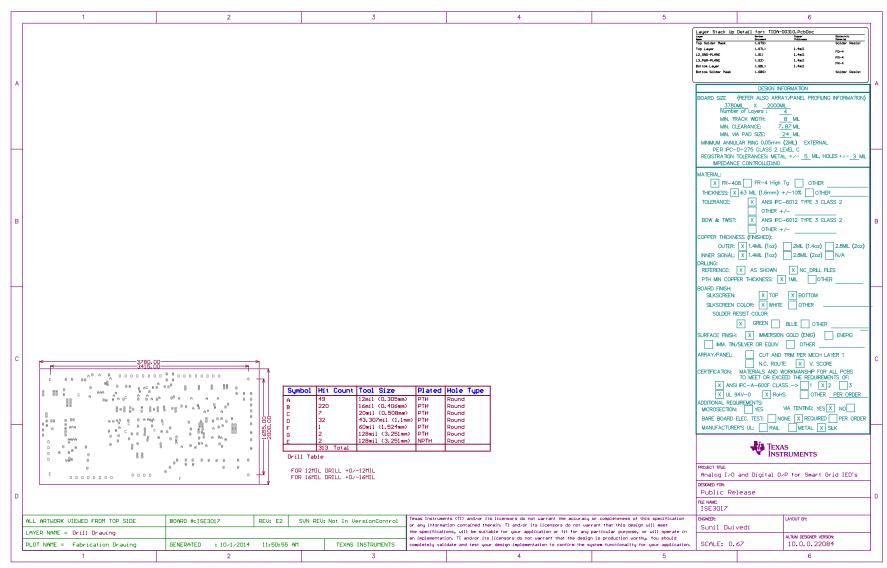

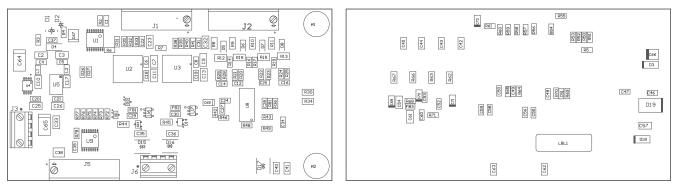

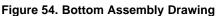

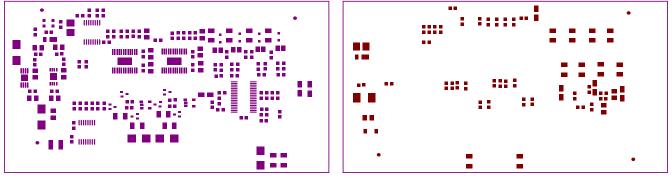

This user sheet provides all of the relevant design files for users to evaluate this reference design in Section 8 such as schematics, BOM, PCB layouts, and Gerber files.

#### 2 Design Features

This TI design has the following specifications.

|                      | ANALOG INPUTS                                     |                                                                          |

|----------------------|---------------------------------------------------|--------------------------------------------------------------------------|

|                      | ADC resolution                                    | 16 Bit                                                                   |

| ADC Details          | ADC type and speed                                | Successive approximation (SAR)                                           |

|                      | Maximum sampling rate                             | 500 kSPS                                                                 |

|                      |                                                   | 0- to 10-V DC                                                            |

| Veltege Input        | DC voltage Inputs                                 | 0- to 5-V DC                                                             |

| Voltage Input        | Number of voltage input channels                  | 2                                                                        |

|                      | Input impedance for voltage channel               | > 1 MΩ                                                                   |

|                      |                                                   | 4 to 20 mA                                                               |

|                      | DC current inputs                                 | 0 to 20 mA                                                               |

| Current Input        |                                                   | 0 to 24 mA                                                               |

|                      | Input impedance                                   | < 300 Ω                                                                  |

|                      | Number of current input channels                  | 2                                                                        |

| Accuracy             | % of full scale value at 25°C                     | < ±0.2 %                                                                 |

| Interface            | Interface with host controller                    | SPI                                                                      |

| EMC                  | ESD immunity IEC61000-4-2                         | ± 4 kV Contact discharge                                                 |

| Connector            | 8-Pin 2.54-mm pitch screw type                    |                                                                          |

|                      | ANALOG OUTPUTS                                    |                                                                          |

| DAC Details          | DAC resolution                                    | 16 Bit                                                                   |

| DAC Details          | DAC type                                          | Resistor string monotonic                                                |

|                      | Number of analog output channels                  | 2                                                                        |

|                      |                                                   | 0- to 5-V DC                                                             |

| Output Configuration |                                                   | 0- to 10-V DC                                                            |

| Output Configuration | Voltage and current output <sup>(1)</sup>         | 4- to 20-mA DC                                                           |

|                      |                                                   | 0- to 20-mA DC                                                           |

|                      |                                                   | 0- to 24-mA DC                                                           |

| Accuracy             | % of full scale value at 25°C < ±0.2 %            |                                                                          |

| Load                 | Output load                                       | For V_{OUT}: R_L = 1 k\Omega, C_L= 200 pF; for I_{OUT}: R_L = 300 \Omega |

| Interface            | Interface with host controller SPI                |                                                                          |

| EMC                  | ESD immunity IEC61000-4-2 ±4 kV Contact discharge |                                                                          |

| Connector            | 4-Pin 2.54-mm pitch screw type                    |                                                                          |

#### Table 1. Design Features

<sup>(1)</sup> Either voltage or current output is available.

# TEXAS INSTRUMENTS

www.ti.com

Design Features

| RELAY DRIVE OUTPUTS          |                                                     |                                             |  |  |

|------------------------------|-----------------------------------------------------|---------------------------------------------|--|--|

| Number of Outputs            |                                                     | 6                                           |  |  |

| Type of Outputs              |                                                     | Open drain                                  |  |  |

| Voltage Rating               | Rated coil voltage                                  | 12-, 15-, and 24-V DC                       |  |  |

| Interface to Host Controller | I2C                                                 |                                             |  |  |

| Interface to Host Controller | Using I2C to parallel port expander                 | 8-Bit parallel port                         |  |  |

| Connector                    | 8-Pin 2.54-mm pitch screw type                      |                                             |  |  |

|                              | POWER SUPPLY                                        |                                             |  |  |

|                              |                                                     | +15-V DC                                    |  |  |

|                              | Analog supply for DAC                               | -15-V DC                                    |  |  |

| On-Board Power Supply        |                                                     | Ground                                      |  |  |

| On-Board Fower Suppry        | Digital power supply for ADC, DAC, and I2C expander | 3.3 V                                       |  |  |

|                              | Analog power supply for ADC                         | 5-V DC                                      |  |  |

|                              | External power supply                               | 12- , 15-, and 24-V DC                      |  |  |

| Relay Drive Power Supply     | Connector                                           | Common with relay drive output<br>connector |  |  |

5

#### Block Diagram

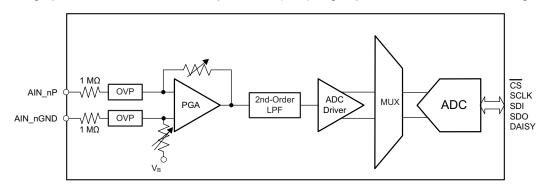

#### 3 Block Diagram

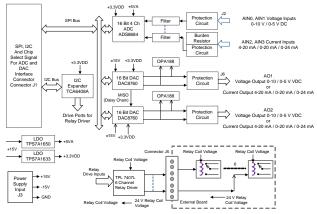

Figure 1. Block Diagram of TIDA-00310

# 3.1 Analog Input Section

#### 3.1.1 ADC

The analog input section has a provision for four inputs. This design uses the ADS8684 device (16-bit, 4-channel, SAR ADC) with an on-chip programmable gain amplifier (PGA) and reference. The ADC provides a high-input impedance (typically 1 M $\Omega$ ). The ADC interfaces with the host controller through the use of SPI. The on-chip 4.096-V ultra-low drift voltage reference is used as the reference for the ADC.

#### 3.1.2 Input Type and Range Supported

Analog inputs AIN0 and AIN1 are configured as voltage inputs; AIN2 and AIN3 are configured as current inputs.

This design supports the following input ranges:

- 0- to 5-V DC and 0- to 10-V DC for voltage channels.

- 0- to 20-mA DC, 0- to 24-mA DC, and 4- to 20-mA DC for current channel.

#### 3.1.3 Power Supply

This analog input module requires a 3.3-V digital power supply and a 5-V analog power supply.

Analog Input, Output, and Relay Drive Output Module for Smart Grid IEDs

6

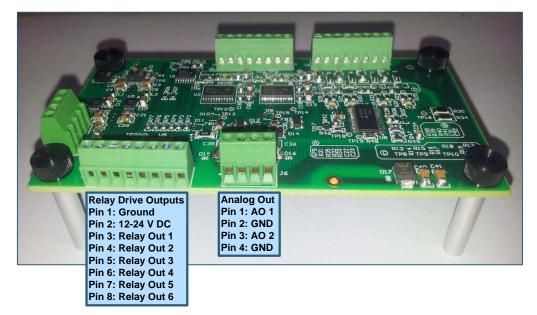

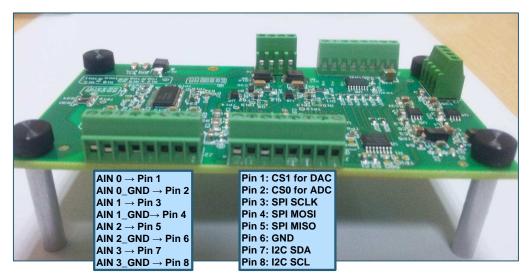

#### 3.1.4 Connector Details

An 8-pin screw-type connector J2 is used for analog inputs with two pins for each analog channel. The input applied is single-ended.

# 3.2 Analog Ouput

# 3.2.1 DAC

This design uses a 16-bit resolution DAC8760 device. Each DAC provides one output for either voltage or current . This design uses two DACs to meet the two AO requirements.

The DAC8760 is a low-cost, precision, fully-integrated, 16-bit DAC.

Users can program the DAC8760 device as a:

- current output with a range of 4- to 20- mA, 0- to 20- mA, or 0- to 24- mA.

- voltage output with a range of 0- to 5- V, 0- to 10- V, ±5 V, or ±10 V, with a 10% over-range.

(0- to 5.5- V, 0- to 11- V, ±5.5 V, or ±11 V).

The DAC interfaces with the host controller through the use of SPI communication. This DAC has a feature that allows a daisy-chain SPI.

# 3.2.2 Output Type and Range Supported

The DAC outputs can be configured as either voltage output or current output. Both AO support the following ranges:

- 0- to 5-V DC and 0- to 10-V DC

- 0- to 20-mA DC, 0- to 24-mA DC, and 4- to 20-mA DC

- For  $V_{OUT}$ :  $R_L = 1 \text{ k}\Omega$ ,  $C_L = 200 \text{ pF}$ ; for  $I_{OUT}$ :  $R_L = 300 \Omega$

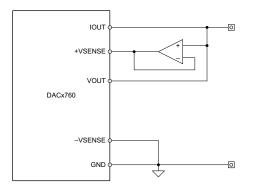

# 3.2.3 Output Voltage Sense Buffering

$+V_{\text{SENSE}}$  and  $-V_{\text{SENSE}}$  enable the sensing of a load. Ideally the load is connected to  $V_{\text{OUT}}$  at the terminals. As  $V_{\text{OUT}}$  and  $I_{\text{OUT}}$  are tied together, and when used as a current output, there is a gain error due to the current leakage of the  $+V_{\text{SENSE}}$  pin. This current leakage introduces a gain error of -0.36%. This error can be minimized by using a high input impedance, low-input bias current op-amp. In the current design the  $+V_{\text{SENSE}}$  connects to  $V_{\text{OUT}}$  through the buffer implemented using TI's op-amp OPA188, which has a typical input bias current of 160 pA.

# 3.2.4 Power Supply

This DAC requires 3.3 V and ±15.0 V.

#### 3.2.5 Connector

The 4-pin screw type connector J6 is used for analog outputs with two pins for each analog output.

# 3.3 Relay Drive Output

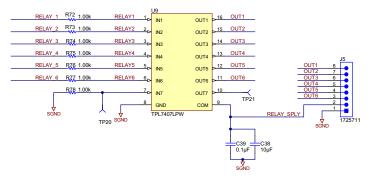

#### 3.3.1 Relay Driver

The relay drive output module provides six low-side drive outputs for driving electromagnetic relays. This design uses the TPL7407L device, which is a high-voltage, high-current n-channel MOS (NMOS) transistor array. This device consists of seven NMOS transistors that feature high-voltage outputs with common-cathode clamp diodes for the purpose of switching inductive loads. The maximum drain-current rating for a single NMOS channel is 600 mA.

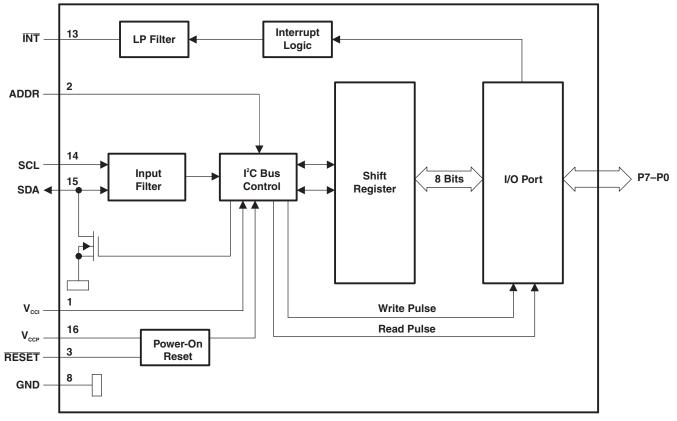

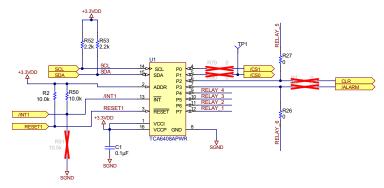

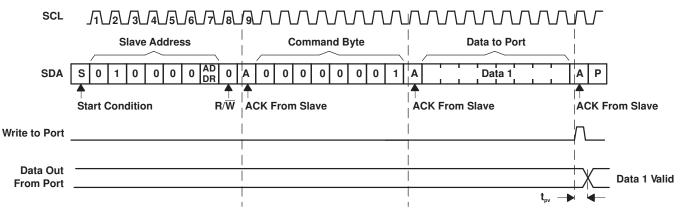

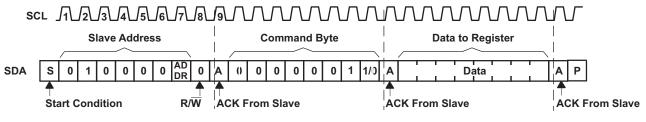

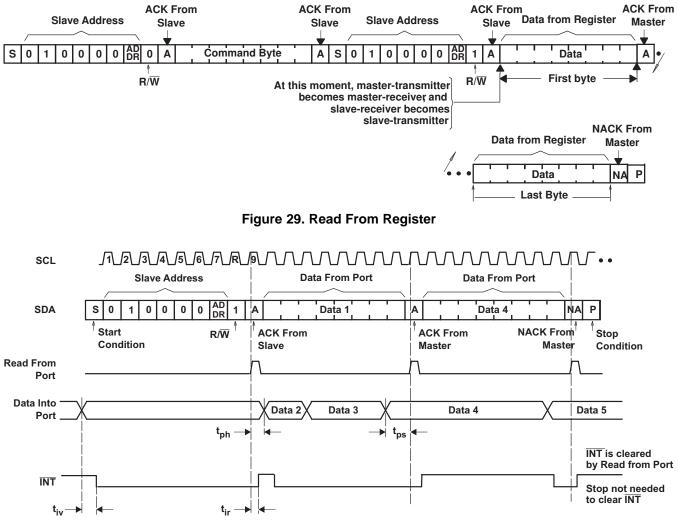

#### 3.3.2 I2C I/0 Expander

The digital input required for the relay driver is provided by the I2C I/O expander. The TCA6408A device provides a drive signal to the TPL7407L device. This 8-bit I/O expander interfaces with the host controller through the I2C interface (serial clock (SCL) and serial data (SDA)). The major benefit of the I2C I/O expander is a wide VCC range. The device can operate from 1.65 V to 5.5 V on the P-port side as well as the SDA and SCL sides. Pull-up resistors are provided in the design.

#### 3.3.3 Power Supply

This module requires a 3.3-V digital power supply. This module requires an external power supply of 12- to 24-V DC that can be applied to two pins of connector J5. Refer to the schematics in Section 4.1.4 and the test setup details in Section 6 for connection purposes.

#### 3.3.4 Connector

The relay drive outputs use an 8-pin screw type connector, J5.

#### 3.4 Power Supply

#### 3.4.1 Input Supply

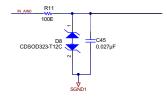

This TI design requires a ±15-V DC input voltage to be connected to connector J3.

#### 3.4.2 On-Board Supply

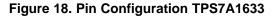

The ADS8684 ADC requires 5 V for the analog supply, which is derived from 15 V using the low-dropout (LDO) TPS7A1650 device that can provide a 100-mA output current.

The ADS8684 and DAC8760 devices require a 3.3-V supply for digital power supply VDD, which is derived from the 15 V using an LDO TPS7A1633.

The TPS7A16 family of ultra-low power, LDO voltage regulators offers benefits such as an ultra-low, quiescent current around 5  $\mu$ A; a 60-V high input voltage; and miniaturized, high thermal-performance packaging that can source a 100-mA load.

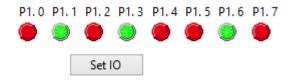

#### 3.5 Interface to Host Controller

This TI design can interface to a host controller through the connector J1.

J1 is an 8-pin, 2.54-mm pitch connector and has chip select signals (CS0 and CS1) for ADC and DAC, SPI standard signal, ground, and I2C standard signals.

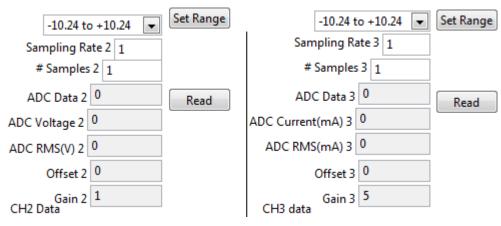

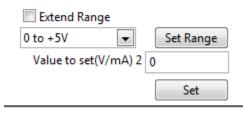

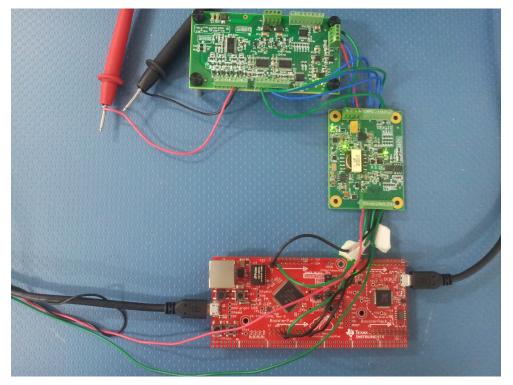

For testing purposes the TM4C1294XL device TIVA<sup>™</sup> C-series LaunchPad<sup>™</sup> is used as a host controller. Use the following signals on the LaunchPad to interface:

- SPI Clock ---- PA2

- SPI MOSI ---- PA4

- SPI MISO ---- PA5

- SPI Chip Select for ADC ---- PA3

- SPI Chip Select for DAC ---- PK3

- I2C Clock(SCLK) ---- PB2

- I2C Data(SDATA) ---- PB3

- Ground

8

#### 4 **Circuit Design and Component Selection**

#### 4.1 Analog Input

#### 4.1.1 ADC Description

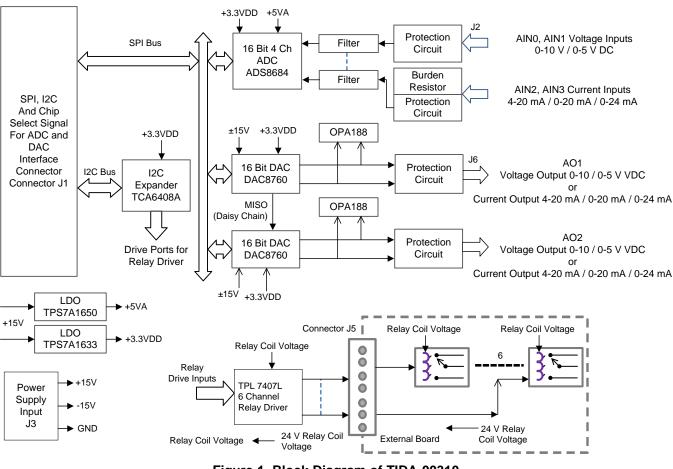

The 4-channel analog input design is based on the ADS8684 16-bit SAR ADC device. The ADS8684 is a 4-channel integrated data acquisition systems based on a 16-bit SAR ADC. The device features integrated AFE circuitry for each input channel with over-voltage protection up to ±20 V, a 4-channel multiplexer with automatic and manual scanning modes, and an on-chip 4.096-V reference with extremely low drift. Operating on a single analog supply of 5 V, each input channel on the devices can support true bipolar input ranges of ±10.24 V, ±5.12 V, and ±2.56 V; as well as unipolar input ranges of 0 to 10.24 V and 0 to 5.12 V. The input range selection is done by software programming of the device internal registers and is independent for each channel. The ADS8684 offers a 1-MΩ constant, resistive-input impedance regardless of the selected input range.

Figure 2. Internal Block Diagram of ADS8684

9

The ADS8684 ADC has the following features:

- A 16-bit ADC with an integrated AFE

- A 4-channel multiplexor (MUX) with auto and manual scan

- Software programmable inputs per channel

- Bipolar ranges: ±10.24 V, ±5.12 V, and ±2.56 V

- Unipolar ranges: 0 to 10.24 V and 0 to 5.12 V

- A 5-V analog supply; 1.65- to 5-V I/O supply

- Excellent performance:

- 500-kSPS Aggregate throughput

- INL: ±2.5 LSB

- SNR: 91 dB

- Low power: 70 mW

- An SPI<sup>™</sup>-compatible interface

The ADS8684 device offers a simple SPI-compatible serial interface to the host. The digital supply operates from 1.65 V to 5.25 V, enabling direct interface to a wide range of host controllers.

The device also offers integrated front end signal processing including a multiplexer, second-order anti-aliasing filter, ADC driver amplifier, and an extended industrial temperature range, which all make the ADS8684 ideal for any standard industrial analog input measurement.

In the design, analog input channels AIN0 and AIN1 are used for voltage input. The voltage input has the following possible input ranges:

- 0- to 10-V DC

- 0- to 5-V DC

- Accuracy < ±0.2% full scale at 25°C

- Input impendence > 1 MΩ

Analog Input channels AIN2 and AIN3 are used for current input. The current input has the following possible input ranges:

- 0- to 20-mA, 0- to 24-mA, and 4- to 20-mA DC input current ranges

- Accuracy < ±0.2% full scale at 25°C

- Input impendence < 300  $\Omega$

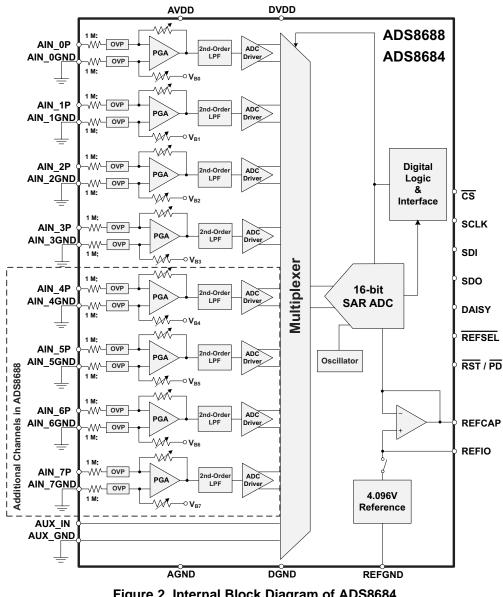

# 4.1.1.1 Analog Input AIN0-AIN3

The ADS8684 device has four analog input channels; the positive inputs,  $AIN_nP$  (n = 0 to 3), are the single-ended analog inputs and the negative inputs,  $AIN_nGND$ , are tied to GND.

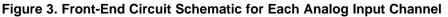

Figure 3 shows the simplified circuit schematic for each analog input channel, including the input overvoltage protection circuit, PGA, low-pass filter (LPF), high-speed ADC driver, and analog multiplexer.

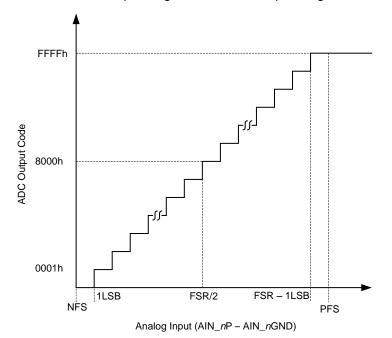

#### 4.1.1.2 Input Section

The devices support multiple unipolar or bipolar, single-ended input voltage ranges based on the configuration of the program registers. The input voltage range for each analog channel can be configured to bipolar  $\pm 2.5 \times V_{REF}$ ,  $\pm 1.25 \times V_{REF}$ , and  $\pm 0.625 \times V_{REF}$ ; or unipolar 0 to  $2.5 \times V_{REF}$  and 0 to  $1.25 \times V_{REF}$ . With the internal or external reference voltage set to 4.096 V, the input ranges of the device can be configured to bipolar ranges of  $\pm 10.24$  V,  $\pm 5.12$  V, and  $\pm 2.56$  V or unipolar ranges of 0.0 V to 10.24 V and 0.0 V to 5.12 V.

Any of these input ranges can be assigned to any analog input channel of the device. The device samples the voltage difference (AIN\_nP – AIN\_nGND) between the selected analog input channel and the AIN\_nGND pin. TI recommends running separate wires from the AIN\_nGND pin of the device to the sensor or signal conditioning ground.

Each analog input channel in the device presents a constant resistive impedance of 1 M $\Omega$ . The input impedance is independent of either the ADC sampling frequency, the input signal frequency, or range. The primary advantage of such high-impedance inputs is the ease of driving the ADC inputs without requiring driving amplifiers with low output impedance.

To maintain the DC accuracy of the system, matching the external source impedance on the AIN\_nP input pin with an equivalent resistance on the AIN\_nGND pin is recommended. This matching helps to cancel any additional offset error contributed by the external resistance.

# 4.1.1.3 PGA

The AD8684 ADC offers a PGA at each individual analog input channel, which convert the original singleended input signal into a fully-differential signal to drive the internal 16-bit ADC. The PGA also adjusts the common-mode level of the input signal before being fed into the ADC to ensure maximum usage of the ADC input dynamic range. Depending on the range of the input signal, the PGA gain can adjust accordingly by setting the Range\_CHn[2:0] (n = 0 to 3) bits in the program register. The default or poweron state for the Range\_CHn[2:0] bits is 000, which corresponds to an input signal range of  $\pm 2.5 \times V_{REF}$  as Table 2 shows.

| ANALOG INPUT RANGE           | Range_CH <i>n</i> [2:0] |       |       |  |

|------------------------------|-------------------------|-------|-------|--|

| ANALOG INFOT KANGE           | BIT 2                   | BIT 1 | BIT 0 |  |

| $\pm 2.5 \times V_{REF}$     | 0                       | 0     | 0     |  |

| $\pm 1.25 \times V_{REF}$    | 0                       | 0     | 1     |  |

| $\pm 0.625 \times V_{REF}$   | 0                       | 1     | 0     |  |

| 0 to 2.5 × V <sub>REF</sub>  | 1                       | 0     | 1     |  |

| 0 to 1.25 × V <sub>REF</sub> | 1                       | 1     | 0     |  |

#### Table 2. Input Range Selection Bits Configuration

# 4.1.1.4 Multiplexer (MUX)

The ADS8684 device features an integrated 4-channel analog multiplexer. For each analog input channel, the voltage difference between the positive analog input AIN\_nP and the negative ground input AIN\_nGND is conditioned by the AFE circuitry before being fed into the multiplexer. The ADC directly samples the output of the multiplexer. The multiplexer in the device can scan analog inputs in either manual or auto-scan mode. In manual mode (MAN\_Ch\_n), the channel is selected for every sample through a register write; in auto-scan mode (AUTO\_RST), the channel number is incremented automatically on every CS falling edge after the present channel is sampled. The analog inputs can be selected for an auto scan with register settings.

The devices automatically scan only the selected analog inputs and in ascending order. The maximum overall throughput for ADS8684 is specified at 500 kSPS across all of the channels. The per-channel throughput value depends on the number of channels selected in the multiplexer scanning sequence. For example, the throughput per channel is equal to 250 kSPS only if two channels are selected; but, the throughput per channel is equal to 125 kSPS per channel if four channels are selected.

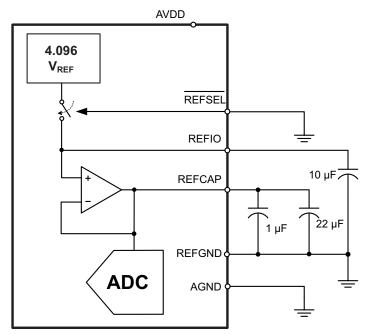

#### 4.1.1.5 Reference

The ADS8684 device can operate with either an internal voltage reference or an external voltage reference using the internal buffer. The internal or external reference selection is defined by an external REFSEL pin biasing. The device has a built-in buffer amplifier to drive the actual reference input of the internal ADC core to maximize performance. The ADS8684 has an internal 4.096-V (nominal value) reference. In order to select the internal reference, the REFSEL pin must be tied low or connected to AGND. When using the internal reference option, the REFIO (pin 5) becomes an output pin with the internal reference value. TI recommends placing a 10- $\mu$ F (minimum) decoupling capacitor between the REFIO pin and the REFGND (pin 6), as shown in Figure 4. Place the capacitor as close to the REFIO pin as possible.

Figure 4. Device Connections for Using an Internal 4.096-V Reference

The internal reference is also temperature compensated to provide excellent temperature drift over an extended industrial temperature range of –40°C to 125°C.

#### 4.1.1.6 Power Supply Recommendations

The device uses two separate power supplies: AVDD and DVDD. The internal circuits of the device operate on AVDD, while DVDD is used for the digital interface. AVDD and DVDD can be independently set to any value within the permissible range.

The AVDD supply pins must be decoupled with AGND by using a minimum  $10-\mu$ F and  $1-\mu$ F capacitor on each supply. Place the  $1-\mu$ F capacitor as close to the supply pins as possible. Place a minimum  $10-\mu$ F decoupling capacitor very close to the DVDD supply to provide the high-frequency digital switching current. The effect of using the decoupling capacitor is illustrated in the difference between the power-supply rejection ratio (PSRR) performance of the device.

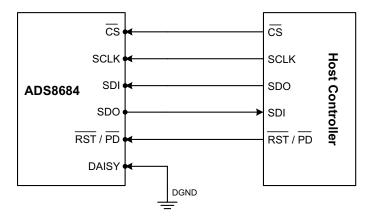

Figure 5. ADS8684 Digital Interface

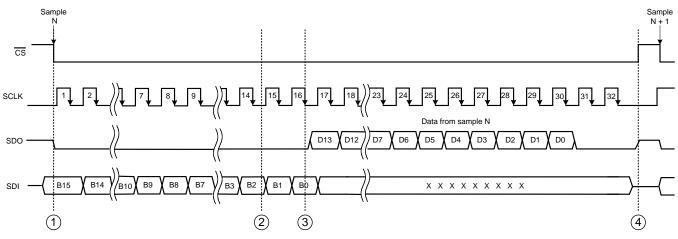

# CS (Input)

$\overline{CS}$  is an active-low, chip-select signal. CS is also used as a control signal to trigger a conversion on the falling edge. Each data frame begins with the falling edge of the  $\overline{CS}$  signal. The analog input channel to be converted during a particular frame is selected in the previous frame. On the  $\overline{CS}$  falling edge, the devices sample the input signal from the selected channel and a conversion is initiated using the internal clock. The device settings for the next data frame can be input during this conversion process. When the  $\overline{CS}$  signal is high, the ADC is considered to be in an idle state.

# SCLK (Input)

This pin is the clock input for the data interface. All synchronous accesses to the device are timed with respect to the falling edges of the SCLK signal.

# SDI (Input)

SDI is the data input line. SDI is used by the host processor to program the internal device registers for device configuration. At the beginning of each data frame, the CS signal goes low and the data on the SDI line are read by the device at every falling edge of the SCLK signal for the next 16 SCLK cycles. Any changes made to the device configuration in a particular data frame are applied to the device on the subsequent falling edge of the  $\overline{CS}$  signal.

# SDO (Input)

SDO is the data output line. SDO is used by the device to output conversion data. The size of the data output frame varies depending on the register setting for the SDO format. A low level on  $\overline{CS}$  releases the SDO pin from the Hi-Z state. SDO is kept low for the first 15 SCLK falling edges. The MSB of the output data stream is clocked out on SDO on the 16th SCLK falling edge, followed by the subsequent data bits on every falling edge thereafter. The SDO line goes low after the entire data frame is output and goes to a Hi-Z state when  $\overline{CS}$  goes high.

Circuit Design and Component Selection

www.ti.com

#### 4.1.2 Input Range Supported

This TI design supports the following input ranges.

| VOLTAGE INPUT                             |                     |  |  |

|-------------------------------------------|---------------------|--|--|

| DC Veltare                                | 0- to 10-V DC       |  |  |

| DC Voltage                                | 0- to 5-V DC        |  |  |

| Number of Voltage Input Channels          | 2                   |  |  |

| Input Impedance for Voltage Channels      | > 1 MΩ              |  |  |

| Connector Details                         | AIN0 -> J2.1 - J2.2 |  |  |

| Connector Details                         | AIN1 -> J2.3 - J2.4 |  |  |

| CURRENT IN                                | NPUT                |  |  |

|                                           | 0- to 20-mA DC      |  |  |

| DC Current                                | 0- to 24-mA DC      |  |  |

|                                           | 4- to 20-mA DC      |  |  |

| Input Impedance for Current Input Channel | < 300 Ω             |  |  |

| Number of Current Inputs                  | 2                   |  |  |

| Connector Details                         | AIN3 -> J2.5 - J2.6 |  |  |

| Connector Details                         | AIN4 -> J2.7- J2.8  |  |  |

| ACCURACY                                  |                     |  |  |

| For Both Current and Voltage Inputs       | < 0.2% Full scale   |  |  |

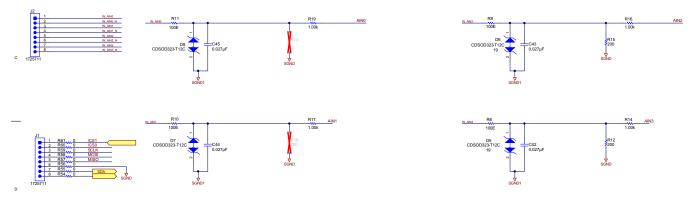

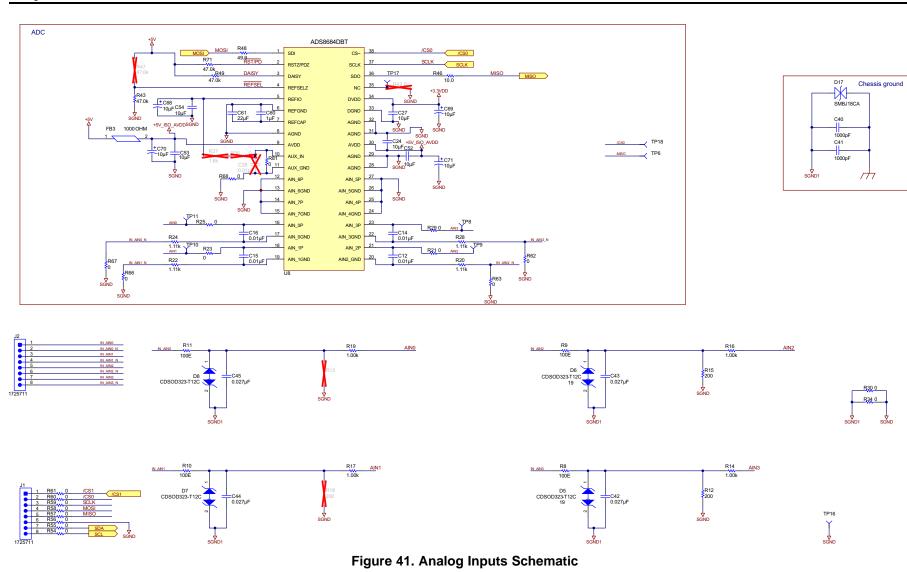

On the AINx line  $100-\Omega$  resistors are used to protect the input Zener (CSDO323) from high current due to EMI. A 1-K resistor is also used for overvoltage protection. To create balance, a 1.11-K resistor is used in the return line AIN\_xGND. After these balancing resistors, AIN\_xGND is connected to signal ground through the 0- $\Omega$  resistor.

#### 4.1.3 Power Supply Requirement

| VOLTAGE        | VOLTAGE – V | I – mA  |

|----------------|-------------|---------|

| Analog supply  | 5           | 11.5 mA |

| Digital supply | 3.3         | 1       |

The analog power supply of 5.0 V derives from a 15-V supply using an LDO TPS7A1650.

The digital power supply of 3.3 V derives from a 15-V supply using an LDO TPS7A1633. View further details about the power supply of this design in Section 4.2.3.

+5∨ ₽

R22

1.11k

R66

0

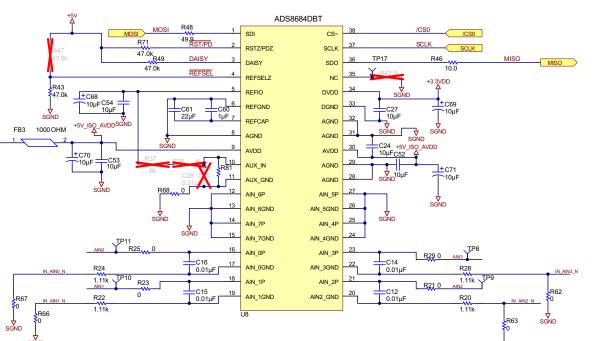

#### 4.1.4 **Schematics**

AIN2\_GND

AIN\_1GND

ັບ

Figure 7. Analog I/P Front End

R20

1.11k

**č**0

. ↓ SGND

R63

Circuit Design and Component Selection

# 4.2 Analog Output

#### 4.2.1 DAC Description

This design uses the DAC8760 device. DAC8760s are low-cost, precision, fully-integrated, 16-bit DACs designed to meet the requirements of smart grid process-control applications. The DAC8760 device has the following features:

- DC current output: 4 to 20 mA, 0 to 20 mA, and 0 to 24 mA

- DC voltage output: 0 to 5 V, 0 to 10 V,  $\pm$ 5 V,  $\pm$ 10 V, 0 to 5.5 V, 0 to 11 V,  $\pm$ 5.5 V, and  $\pm$ 11 V

- ±0.1% Full-scale reading (FSR) total unadjusted error (TUE) max

- DNL: ±1 LSB max

- Simultaneous voltage and current output

- Internal 5-V reference (10 ppm/°C, max)

- Internal 4.6-V power supply output

- Reliability features:

- CRC check and watchdog timer

- Thermal alarm

- Open alarm, short current limit

- Wide temperature range: -40°C to +125°C

- Devices can superimpose an external HART® signal on the current output and can operate with either a single 10- to 36-V supply, or dual supplies of up to ±18 V

AO1 and AO2 can be configured for either voltage output or for current output. Both AO1 and AO2 support the following ranges:

- 1. 0- to 5-V DC, 0- to 10-V DC

- 2. 0- to 20-mA DC, 0- to 24-mA DC, and 4- to 20-mA DC

- 3. For  $V_{OUT}$ :  $R_L$  = 1 k $\Omega$ ,  $C_L$ = 200 pF; for  $I_{OUT}$ :  $R_L$  = 300  $\Omega$

#### 4.2.1.1 DAC Architecture

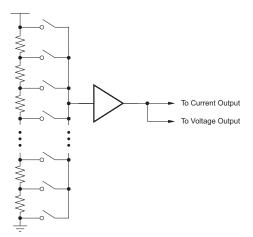

The DAC8760 consists of a resistor-string DAC followed by a buffer amplifier. The output of the buffer drives the current output and the voltage output. The resistor-string section is simply a string of resistors, each of value R, from REF to GND. This type of architecture ensures the DAC is monotonic.

The current-output stage converts the voltage output from the string to current. The voltage output provides a buffered output of the programmed range to the external load. When the current output or the voltage output is disabled, the analog output is in a high impedance (Hi-Z) state. After power-on, both output stages are disabled.

Figure 8. DAC Structure: Resistor String of DAC8760

Circuit Design and Component Selection

#### www.ti.com

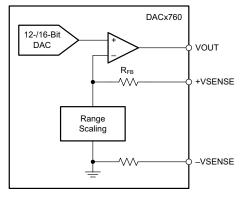

#### 4.2.1.2 Voltage Output Stage

The voltage output stage as shown in Figure 9 provides the voltage output according to the DAC code and output range setting. The output range can be programmed as 0 V to 5 V or 0 V to 10 V for unipolar output mode and  $\pm$ 5 V or  $\pm$ 10 V for bipolar output mode. In addition, an option is available to increase the output voltage range by 10%. The output current drive can be up to 10 mA. The output stage has short-circuit current protection that limits the output current to 30 mA. The voltage output is able to drive a capacitive load up to 1  $\mu$ F. For loads greater than 20 nF, an external compensation capacitor can be connected between CMP and VOUT to keep the output voltage stable at the expense of reduced bandwidth and increased settling time.

Figure 9. Voltage Output

The +VSENSE pin is provided to enable sensing of the load by connecting to points electrically closer to the load. This configuration allows the internal output amplifier to make sure that the correct voltage is applied across the load, as long as headroom is available on the power supply. Ideally, this pin is used to correct for resistive drops on the system board and is connected to VOUT at the terminals. In some cases, both VOUT and +VSENSE are brought out as terminals and, through separate lines, connected remotely together at the load. In such cases, if the +VSENSE line is cut, the amplifier loop is broken; use an optional 5-k $\Omega$  resistor between VOUT and +VSENSE to prevent this from occurring. The –VSENSE pin, on the other hand, is provided as a GND sense reference output from the internal VOUT amplifier. The output swing of the VOUT amplifier is relative to the voltage seen at this pin. The actual voltage difference between the –VSENSE pin and the device GND pins is not expected to be more than a few 100  $\mu$ V. The internal resistor shown in Figure 9 between the device internal GND and the –VSENSE pin is typically 2 k $\Omega$ .

After power on, the power-on-reset circuit confirms that all registers are at default values. The voltage output buffer is in a Hi-Z state; however, the +VSENSE pin connects to the amplifier inputs through an internal 60-k $\Omega$  feedback resistor (R<sub>FB</sub> in Figure 9). If the VOUT and +VSENSE pins are connected together, the VOUT pin is also connected to the same node through the feedback resistor. This node is protected by internal circuitry and settles to a value between GND and the reference input.

#### Circuit Design and Component Selection

The output voltage (VOUT) can be expressed as Equation 1 and Equation 2.

For unipolar output mode:

$$VOUT = VREF \times GAIN \times \frac{CODE}{2^N}$$

For bipolar output mode:

$$VOUT = VREF \times GAIN \times \frac{CODE}{2^N} - GAIN \times \frac{VREF}{2}$$

where

- CODE is the decimal equivalent of the code loaded to the DAC.

- N is the bits of resolution; 16 for DAC8760 and 12 for DAC7760.

- VREF is the reference voltage; for internal reference, VREF = +5.0 V.

- GAIN is automatically selected for a desired voltage output range as shown in Table 3.

# Table 3. Voltage Output Range vs Gain Setting

| VOLTAGE OUTPUT RANGE | GAIN |

|----------------------|------|

| 0- to 5-V            | 1    |

| 0- to 10-V           | 2    |

| ±5 V                 | 2    |

| ±10 V                | 4    |

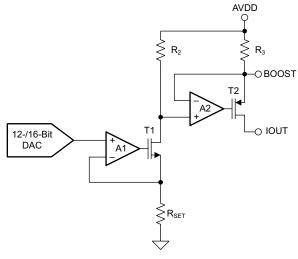

# 4.2.1.3 Current Output Stage

The current output stage consists of a pre-conditioner and a current source as shown in Figure 10. This stage provides a current output according to the DAC code. The output range can be programmed as 0 to 20 mA, 0 to 24 mA, or 4 to 20 mA. An external boost transistor can be used to reduce the power dissipation of the device. The maximum compliance voltage on pin IOUT equals (AVDD – 2 V). In single power supply mode, the maximum AVDD is 36 V and the maximum compliance voltage is 34 V. After power-on, the IOUT pin is in a Hi-Z state.

Figure 10. Current Output

Resistor  $R_{SET}$  (used to convert the DAC voltage to current) determines the stability of the output current over temperature. If desired, an external, low-drift, precision 15-k $\Omega$  resistor can be connected to the ISET-R pin and used instead of the internal  $R_{SET}$  resistor.

RUMENTS

EXAS

(2)

(1)

For a 5-V reference, the output can be expressed as Equation 3, Equation 4, and Equation 5.

$$IOUT = 20 \text{ mA} \times \frac{\text{CODE}}{2^{N}}$$

For a 0- to 20-mA output range:

$$IOUT = 24 \text{ mA} \times \frac{\text{CODE}}{2^{N}}$$

For a 4- to 20-mA output range:

(4)

$$IOUT = 16 \text{ mA} \times \frac{CODE}{2^N} + 4 \text{ mA}$$

where

- CODE is the decimal equivalent of the code loaded to the DAC. ٠

- N is the bits of resolution; 16 for DAC8760.

(5)

#### 4.2.1.4 DAC Clear

The DAC has an asynchronous clear function through the CLR pin which is active high and allows the voltage output to be cleared to either zero-scale code or midscale code. This action is user selectable through the CLR-SEL pin or the CLRSEL bit. The CLR-SEL pin and CLRSET register are ORed together. The current output clears to the bottom of its preprogrammed range. When the CLR signal returns to low, the output remains at the cleared value. The pre-clear value can be restored by pulsing the LATCH signal without clocking any data. A new value cannot be programmed until the CLR pin returns to low.

In addition to defining the output value for a clear operation, the CLRSEL bit and CLR-SEL pin also define the default output value. During the selection of a new voltage range, the output value corresponds to the definitions given in Table 4.

#### **Table 4. CLR-SEL Options**

| CLR-SEL | OUTPUT VALUE                               |                     |  |

|---------|--------------------------------------------|---------------------|--|

| CLR-SEL | UNIPOLAR OUTPUT RANGE BIPOLAR OUTPUT RANGE |                     |  |

| 0       | 0 V                                        | 0 V                 |  |

| 1       | Midscale                                   | Negative full-scale |  |

The CLR-SEL pin is shorted to ground for both DACs.

#### 4.2.2 **Range Supported**

#### Table 5. Analog Output Range

| NUMBER OF OUTPUTS                | 2 Channels     |

|----------------------------------|----------------|

|                                  | 0- to 5-V DC   |

| VOLTAGE OUTFUT AND               | 0- to 10-V DC  |

|                                  | 4- to 20-mA DC |

| CURRENT OUTPUT <sup>(1)(2)</sup> | 0- to 20-mA DC |

|                                  | 0- to 24-mA DC |

Either current or voltage output mode is configurable.

$^{(2)}$   $\;$  For  $V_{OUT}\!\!:R_L$  = 1 k0,  $C_L\!\!=$  200 pF; for  $I_{OUT}\!\!:R_L$  = 300  $\Omega.$

#### 4.2.3 Power Supply

This design uses +15 V as AVDD and -15 V for AVSS. These inputs are directly applied from an external DC digital power supply, 3.3 V is derived from a 15-V supply using an LDO TPS7A1633. Further details concerning power supply are given in Section 4.2.3.2 and Section 4.2.3.3.

#### 4.2.3.1 Internal Reference

The DAC8760 includes an integrated 5-V reference with a buffered output (REFOUT) capable of driving up to 5 mA (source or sink) with an initial accuracy of ±5 mV maximum and a temperature drift coefficient of 10 ppm/°C maximum.

#### 4.2.3.2 Digital Power Supply

An internally generated 4.6-V supply capable of driving up to 10 mA can be output on DVDD by leaving the DVD-EN pin unconnected. The supply eases the system supply design especially when isolation barriers must be crossed to generate the digital supply. If an external supply is preferred, the DVDD pin can be made into an input by tying DVDD-EN to GND.

#### 4.2.3.3 Power Supply Sequence

The DAC8760 has internal power-on reset (POR) circuitry for both the digital DVDD and analog AVDD supplies. This circuitry ensures that the internal logic and power-on state of the DAC power up to the proper state independent of the supply sequence. While there is no required supply power-on sequence, the recommendation is to first have the digital DVDD supply come up, followed by the analog supplies, AVDD and AVSS. AVSS is powered assuming a negative supply is being used; otherwise, AVSS is tied to GND.

#### 4.2.4 SPI

The device is controlled over a versatile four-wire serial interface (SDI, SDO, SCLK, and LATCH) that operates at clock rates of up to 30 MHz and is compatible with SPI, QSPI<sup>™</sup>, Microwire, and digital signal processing (DSP) standards.

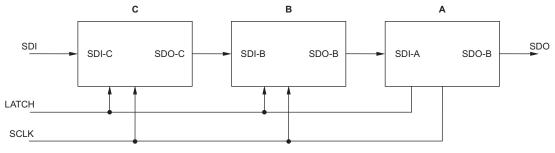

#### 4.2.4.1 Daisy Chain Operation

For systems that contain multiple DAC8760s, the SDO pin is used to daisy-chain in the SPI. This mode is useful in reducing the number of serial interface lines in applications that use multiple SPI devices. Daisy-chain mode is enabled by setting the DCEN bit of the control register to '1'. By connecting the SDO of the first device to the SDI input of the next device in the chain, a multiple-device interface is constructed, as Figure 11 shows.

Figure 11. DAC8760 in Daisy-Chain Mode

Like stand-alone operation, the SPI daisy-chain write operation requires one frame, and the read requires two frames. The rising edge of SCLK that clocks in the most significant bit (MSB) of the input frame marks the beginning of the write cycle. When the serial transfer to all devices is complete, LATCH is taken high. This action transfers the data from the SPI shift registers to the device internal register of each DAC8760 in the daisy-chain. However, the number of clocks in each frame in this case depends on the number of devices in the daisy chain. For two devices, each frame is 48 clocks; the first 24 clocks are for the second

DAC and the next 24 bits are for the first DAC. For a readback, the data are read from the two DACs in the following 48-bit frame; the first 24 clocks are for the second DAC and the next 24 clocks are for the first DAC. The input data to the DACs during the second frame can be another command or NOP. Similar to the two-device case described, for N devices, each frame is  $N \times 24$  clocks, where *N* is the total number of the DAC8760s in the chain.

The serial clock can be a continuous or gated clock. A continuous SCLK source can only be used if LATCH is taken high after the correct number of clock cycles. In gated clock mode, a burst clock containing the exact number of clock cycles must be used and LATCH must be taken high after the final clock to latch the data.

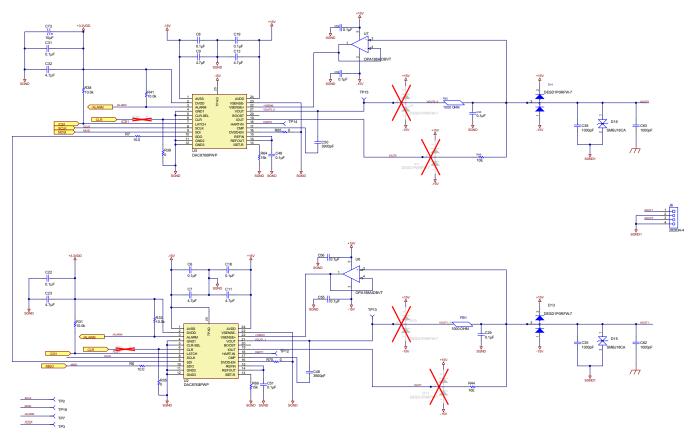

#### 4.2.5 Buffering

In this design, VOUT and IOUT are tied together and never simultaneously enabled.

Special consideration must be paid to the +VSENSE pin in this case. When VOUT is disabled, the +VSENSE pin is connected to the internal amplifier input through an internal 60-k $\Omega$  resistor. This internal node has diode clamps to REFIN and GND. Setting bit 6 of the configuration resistor forces this internal node to be tied to GND via a 10-k $\Omega$  resistor—in effect, the +VSENSE pin is tied to GND through a 70-k $\Omega$  power-down resistor.

Whether the APD bit is set or not set, the current output in this case incurs a gain error because the internal resistor acts as a parallel load in addition to the external load. If this gain error is undesirable, it can be corrected through use of the application circuit as shown in Figure 12.

Figure 12. VOUT and IOUT Tied Together to One Terminal

The buffer amplifier prevents leakage through the internal 60-k $\Omega$  resistor in current output mode and does not allow it to be seen as a parallel load. The VOUT pin is in high impedance mode in this case and will allow minimal leakage current. Note that the offset of the external amplifier will add to the overall VOUT offset error and any potential phase shift from the external amplifier can cause VOUT stability issues.

#### Circuit Design and Component Selection

www.ti.com

#### 4.2.6 Schematics

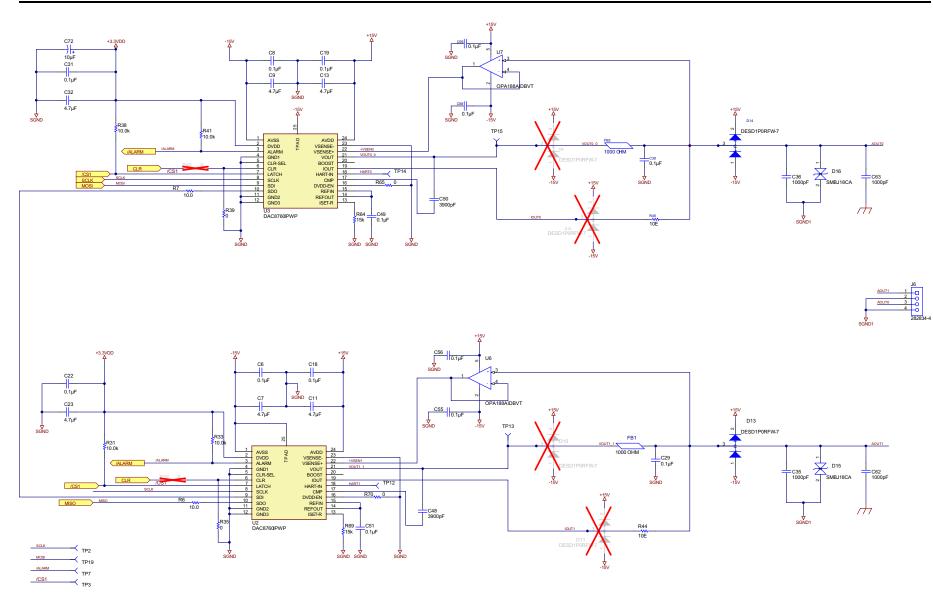

Figure 13. Analog Output

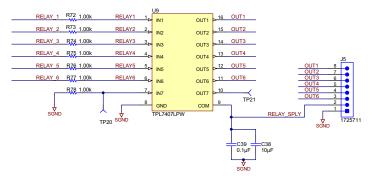

# 4.3 Relay Drive Outputs

This TI design provides six high-current relay driver outputs.

# 4.3.1 Low Side Relay Driver

The TPL7407L is a high-voltage, high-current NMOS transistor array. This device consists of seven NMOS transistors that feature high-voltage outputs with common-cathode clamp diodes for switching inductive loads. The maximum drain-current rating of a single NMOS channel is 600 mA.

The key benefit of the TPL7407L is its improved power efficiency and lower leakage than a Bipolar Darlington Implementation. The TPL7407L device features the following:

- 600-mA rated drain current (per channel)

- Power efficient (very low V<sub>OL</sub>)

- Less than 4 times lower  $V_{OL}$  at 100 mA than Darlington array

- Very low output leakage < 10 nA per channel

- Compatible with 1.8-V to 5.0-V microcontrollers and logic interface

- Internal free-wheeling diodes for inductive kick-back protection

- · Input RC-snubber to eliminate spurious operation in noisy environments

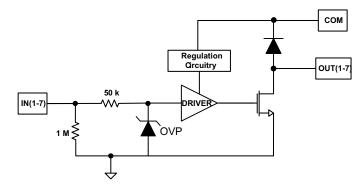

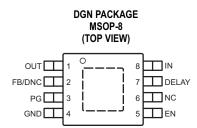

#### 4.3.1.1 TPL7407L Functional Block Diagram

Figure 14. TPL7407L Functional Block Diagram

The TPL7407L comprises seven high voltage, high current NMOS transistors tied to a common ground driven by internal level shifting and gate drive circuitry. The TPL7407L offers solutions to many interface needs, including solenoids, relays, lamps, small motors, and LEDs. Applications requiring sink currents beyond the capability of a single output may be accommodated by paralleling the outputs.

Each channel of TPL7407L consists of high power, low-side NMOS transistors driven by level shifting and gate driving circuitry. The gate drivers allow for high output current drive with a very low input voltage, essentially equating to operability with low general purpose input and output (GPIO) voltages.

In order to enable floating inputs, a 1-M $\Omega$  pull-down resistor exists on each channel. Another 50-k $\Omega$  resistor exists between the input and gate-driving circuitry. This resistor exists to limit the input current whenever there is an overvoltage and the internal Zener clamps. The resistor also interacts with the inherent capacitance of the gate driving circuitry to behave as an RC snubber to help prevent spurious switching in a noisy environment.

In order to power the gate driving circuitry an LDO exists. The diodes connected between the output and COM pin are used to suppress kick-back voltage from an inductive load that is excited when the NMOS drivers are turned off (stop sinking) and the stored energy in the coils causes a reverse current to flow into the coil supply.

# 4.3.1.2 TTL and Other Logic Inputs

TPL7407L input interface is specified for the standard 1.8-V through 5-V complementary metal oxide semiconductor (CMOS) logic interface and can tolerate up to 30 V. At any input voltage, the output drivers are driven at the maximum when  $V_{COM}$  is greater than or equal to 8.5 V.

# 4.3.1.3 Input RC Snubber

TPL7407L features an input RC snubber that helps prevent spurious switching in noisy environments. Connect an external 1-k $\Omega$  to 5-k $\Omega$  resistor in series with the input to further enhance the TPL7407Ls noise tolerance.

# 4.3.1.4 High-Impedance Input Driver

TPL7407L features a 1-M $\Omega$  input pull-down resistor. The presence of this resistor allows the input drivers to be tri-stated. When a high-impedance driver is connected to a channel input, the TPL7407L device detects the channel input as a low-level input and remains in the OFF position. The input RC snubber helps improve noise tolerance when input drivers are in the high-impedance state.

# 4.3.1.5 Drive Current

The coil current is determined by the coil voltage ( $V_{SUP}$ ), coil resistance, and output low voltage ( $V_{OL}$ ).

$I_{\text{COIL}} = (V_{\text{SUP}} - V_{\text{OL}}) / R_{\text{COIL}}$

#### Circuit Design and Component Selection

www.ti.com

The output low voltage (VOL) is the drain to source (VDS) voltage of the output NMOS transistors when the input is driven high and the transistor is sinking current.

#### 4.3.1.6 Thermal Considerations

The number of coils driven is dependent on the coil current and on-chip power dissipation.

For a more accurate determination of number of coils possible, use Equation 6 to calculate TPL7407Ls on-chip power dissipation  $P_D$ :

$$\mathsf{P}_\mathsf{D} = \sum_{i=1}^\mathsf{N} \mathsf{V}_\mathsf{OLi} \times \mathsf{I}_\mathsf{Li}$$

where

- N is the number of channels active together.

- V<sub>OLi</sub> is the OUT<sub>i</sub> pin voltage for the load current I<sub>Li</sub>. This is the same as V<sub>CE(SAT)</sub>.

In order to guarantee reliability of TPL7407L and the system, the on-chip power dissipation must be lower than or equal to the maximum allowable power dissipation ( $P_{D(MAX)}$ ) dictated by Equation 7.

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \frac{(\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}})}{\theta_{\mathsf{J}\mathsf{A}}}$$

where

- $T_{J(MAX)}$  is the target maximum junction temperature.

- T<sub>A</sub> is the operating ambient temperature.

- $\theta_{JA}$  is the package junction to ambient thermal resistance.

(7)

(6)

TI recommends to limit TPL7407L ICs die junction temperature to less than 125°C. The IC junction temperature is directly proportional to the on-chip power dissipation.

#### 4.3.1.7 Power Supply Recommendation

The COM pin is the power supply pin of this device to power the gate drive circuitry. This design ensures full drive potential with any GPIO above 1.5 V. The gate drive circuitry is based on low voltage CMOS transistors that can only handle a max gate voltage of 7 V. An integrated LDO reduces the COM voltage of 8.5 V to 40 V to a regulated voltage of 7 V. Though 8.5 V minimum is recommended for  $V_{COM}$ , the part still functions with a reduced COM voltage, with a reduced gate drive voltage, and a resulting higher Rds(on).

To prevent overvoltage on the internal LDO output due to a line transient on the COM pin, the COM pin must be limited to below 3.5 V/µs. Faster slew-rate (or hot-plug) may cause damage to the internal gate driving circuitry due to the LDOs inability to clamp a fast-input transient fast enough. Because most modern power supplies are loaded by capacitors > 10 µF, this inability to clamp should not be of any concern. TI recommends to use a bypass capacitor that limits the slew rate to below 0.5 V/µs.

In summary, whenever the COM pin experiences a slew rate greater than 0.5 V/ $\mu$ s, a capacitor must be added to limit the slew to < 0.5 V/ $\mu$ s.

# 4.3.1.8 Layout Recommendation

Thin traces can be used on the input due to the low current logic that is typically used to drive the TPL7407L device. Care must be taken to separate the input channels as much as possible, as to eliminate cross-talk. Thick traces are recommended for the output to drive whatever high currents that may be needed. Determine the wire thickness by the current density and desired drive current of the trace material.

Because all of the channels currents return to a common ground, the best method is to size that trace width to be very wide—some applications require up to 2 A.

Because the COM pin only draws up to 25  $\mu$ A, thick traces are not necessary.

#### 4.3.2 I2C I/O Expander

This TI design uses an I2C I/O expander to provide digital inputs for driving the relay driver inputs. The TCA6408A is a low voltage 8-bit I2C I/O expander. The device is compliant to a 400-KHz fast I2C bus.

The bidirectional voltage-level translation in the TCA6408A is provided through  $V_{CCI}$ . The  $V_{CCI}$  is to be connected to the  $V_{CC}$  of the external SCL/SDA lines. This connection indicates the  $V_{CC}$  level of the I2C bus to the TCA6408A device. The voltage level on the P-port of the TCA6408A is determined by  $V_{CCP}$ .

The TCA6408A consists of one 8-bit configuration (input or output selection), input, output, and polarity inversion (active high) register. At power on, the I/Os are configured as inputs. However, the system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each input or output is kept in the corresponding input or output register. The polarity of the input port register can be inverted with the polarity inversion register. The system master can read all registers.

The system master can reset the TCA6408A in the event of a timeout or other improper operation by asserting a low in the RESET input. The power-on reset puts the registers in their default state and initializes the I2C state machine. The RESET pin causes the same reset and initialization to occur without depowering the part.

The TCA6408A open-drain interrupt (INT) output activates when any input state differs from its corresponding input port register state and is used to indicate to the system master that an input state has changed.

INT can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate through the I2C bus. Thus, the TCA6408A can remain a simple slave device.

The device P-port outputs have high-current sink capabilities for directly driving LEDs while consuming low device current.

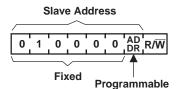

As shown in Table 6, one hardware pin (ADDR) can be used to program the I2C address to allow two devices to share the same I2C bus.

| ADDRESS | I2C BUS SLAVE ADDRESS          |

|---------|--------------------------------|

| L       | 32 (decimal), 20 (hexadecimal) |

| Н       | 33 (decimal), 21 (hexadecimal) |

#### **Table 6. Address Reference**

A All pin numbers shown are for the PW package. B. All I/Os are set to inputs at reset.

Figure 15. TCA6408 I2C to Parallel Bus Expander Block

| TERMINAL      |            |           |                  |                                                                                                                                                              |

|---------------|------------|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER        |            |           | DESCRIPTION      |                                                                                                                                                              |

| TSSOP<br>(PW) | µQFN (RSV) | QFN (RGT) | NAME             |                                                                                                                                                              |

| 1             | 15         | 15        | V <sub>CCI</sub> | Supply voltage of I <sup>2</sup> C bus. Connect directly to the V <sub>CC</sub> of the external I <sup>2</sup> C master. Provides voltage level translation. |

| 2             | 16         | 16        | ADDR             | Address input. Connect directly to $V_{CCP}$ or ground.                                                                                                      |

| 3             | 1          | 1         | RESET            | Active-low reset input. Connect to V <sub>CCI</sub> through a pull-up resistor, if no active connection is used.                                             |

| 4             | 2          | 2         | P0               | P-port input/output (push-pull design structure). At power on,<br>P0 is configured as an input.                                                              |

| 5             | 3          | 3         | P1               | P-port input/output (push-pull design structure). At power on,<br>P1 is configured as an input.                                                              |

| 6             | 4          | 4         | P2               | P-port input/output (push-pull design structure). At power on,<br>P2 is configured as an input.                                                              |

| 7             | 5          | 5         | P3               | P-port input/output (push-pull design structure). At power on,<br>P3 is configured as an input.                                                              |

| 8             | 6          | 6         | GND              | Ground.                                                                                                                                                      |

| 9             | 7          | 7         | P4               | P-port input/output (push-pull design structure). At power on,<br>P4 is configured as an input.                                                              |

| 10            | 8          | 8         | P5               | P-port input/output (push-pull design structure). At power on,<br>P5 is configured as an input.                                                              |

| 11            | 9          | 9         | P6               | P-port input/output (push-pull design structure). At power on,<br>P6 is configured as an input.                                                              |

#### **Table 7. Terminal Functions**

26 Analog Input, Output, and Relay Drive Output Module for Smart Grid IEDs

| 12 | 10 | 10 | P7               | P-port input/output (push-pull design structure). At power on,<br>P7 is configured as an input. |

|----|----|----|------------------|-------------------------------------------------------------------------------------------------|

| 13 | 11 | 11 | INT              | Interrupt output. Connect to $V_{CCI}$ through a pull-up resistor.                              |

| 14 | 12 | 12 | SCL              | Serial clock bus. Connect to VCCI through a pull-up resistor.                                   |

| 15 | 13 | 13 | SDA              | Serial data bus. Connect to VCCI through a pull-up resistor.                                    |

| 16 | 14 | 14 | V <sub>CCP</sub> | Supply voltage of TCA6408A for P-port.                                                          |

#### Table 7. Terminal Functions (continued)

#### 4.3.3 Schematics

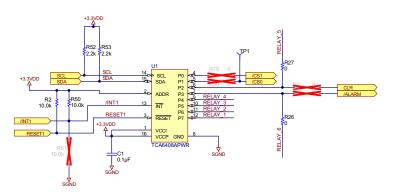

# Figure 16. I2C I/O Expander

Figure 17. Digital Output Relay Driver

# 4.4 Power Supply

This TI design requires the following power supplies.

- 1. 15-V DAC analog supply

- 2. -15-V DAC analog supply

- 3. 3.3-V Digital power supply

- 4. 5.0-V Analog power supply

#### 4.4.1 Supply Input

This design has the following power supply inputs.

- 15 V

- -15 V

- Ground

#### 4.4.2 Analog Power Supply for DAC

A  $\pm$ 15-V supply is directly used for DAC analog supply in the analog output module. Both  $\pm$ 15 V are properly decoupled at the input connector and at the analog power supply of DAC8760. A  $\pm$ 15-V supply is also used for generating 3.3-V and 5.0-V supplies.

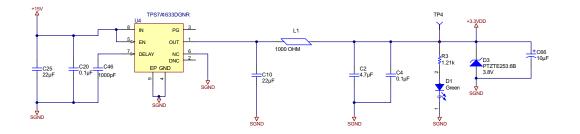

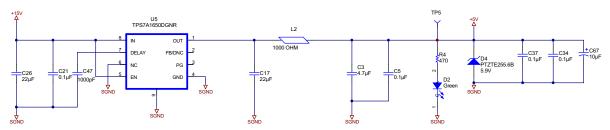

#### 4.4.3 Digital Power Supply +3.3 V and Analog Power Supply +5.0 V (For ADC)

For generating a 3.3-V digital power supply, this TI design uses a TPS7A1633 LDO. For generating a 5.0-V analog power supply for ADC, this TI design uses a TPS7A16450 LDO. The TPS7A16 family of ultra-low power, LDO voltage regulators offers the benefits of an ultra -low quiescent current, high input voltage, and miniaturized, high thermal-performance packaging. The TPS7A16 family is designed for continuous or sporadic (power backup) battery-powered applications where ultra-low quiescent current is critical to extending system battery life. The following are features of the TPS7A series LDO.

- Wide input voltage range: 3 V to 60 V

- Ultra-low quiescent current: 5 µA

- Quiescent current at shutdown: 1 µA

- Output current: 100 mA

- Low dropout voltage: 60 mV at 20 mA

- Accuracy: 2% power good with programmable delay

- Current-limit and thermal shutdown

- Stable with ceramic output capacitors: ≥ 2.2 µF

#### 4.4.4 Schematics

Figure 19. Digital Power Supply 3.3 V and Analog Power Supply 5.0-V Regulators

Figure 20. Front End Power Supply Connector and Filter

# 4.5 Host Controller Interface

#### 4.5.1 Host Controller Details

The testing for this TI design uses the TM4C1294 LaunchPad Evaluation Board. The Tiva<sup>™</sup> C-Series TM4C1294 Connected LaunchPad Evaluation Board (EK-TM4C1294XL) is a low-cost evaluation platform for ARM® Cortex<sup>™</sup>-M4F-based microcontrollers. The Connected LaunchPad design highlights the TM4C1294NCPDT microcontroller with its on-chip 10/100 Ethernet MAC and PHY, USB 2.0, hibernation module, motion control pulse-width modulation, and a multitude of simultaneous serial connectivity.

#### 4.5.2 Host Controller

The following lines are used for the interfacing with the TI design board from the LaunchPad.

- SPI Clock ---- PA2

- SPI MOSI ---- PA4

- SPI MISO ---- PA5

- SPI Chip Select for ADC -- PA3

- I2C Clock(SCLK) -- PB2

- I2C Data(SDATA) -- PB3

- SPI Chip select for DAC: PK3

- Ground

# 4.5.3 SPI and I2C Communication

The TIVA controller used in the LaunchPad kit has an SPI peripheral module with an SPI clock that can reach up to 30 MHz. To get the 500-kSPS sampling rate of the ADS8684 device, set the SPI clock rate to 17 MHz; and for the DAC8760 device, set the SPI clock rate to 4 MHz.

TIVA has an I2C peripheral module to support standard, fast, and high-speed modes of I2C communication. This module can be used to communicate with the I/O expander at the standard mode (100 KHz).

# 4.5.4 Connector

J1 is an 8-pin, 2.54-mm pitch connector that has chip select signals (CS0 and CS1) for ADC and DAC, the SPI standard signal, ground, and the I2C standard signal.

# 4.5.5 Schematic

# Figure 21. J1 Connector

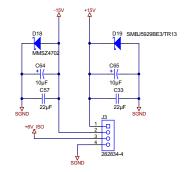

# 4.6 Protection

# 4.6.1 Analog Input

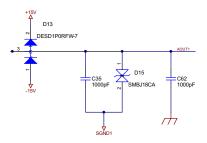

The goal of electromagnetic compatibility (EMC)-protected circuitry is to shunt any sort of external transient to earth ground with low impedance and protect the analog input module from damage. The 100R pulse withstanding resistors protect each analog input line against overcurrent occurrences due to high voltage EMI phenomenon. The RC filter, comprised by a 100- $\Omega$  resistor and a 0.027-µF capacitor, filters out all high-frequency disturbances. The bidirectional transient voltage suppressor (CDSOD323-T12C) protects each analog input line from ESD.

Figure 22. Analog Input EMC Protection

#### Circuit Design and Component Selection

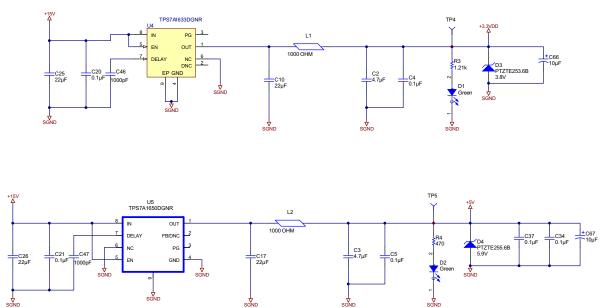

#### 4.6.2 Analog Output

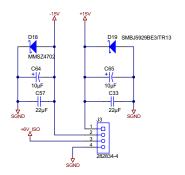

The output stage is designed to withstand ±4-kV of contact discharge. The TVS SMBJ18CA protects every channel. This circuit clamps overvoltage inputs to approximately 25 V. The ESD protection diodes also protect against overvoltage inputs. Layout guidelines must be followed to ensure compliance to EMC standards. The selected protection devices are chosen to dissipate the required energy. There are also Y-capacitors connected across the analog output and earth for filtering out all high frequency disturbances. There are overvoltage clamping diodes connected on each output line.

Figure 23. Analog Output EMC Protection

#### 5 Software Description

For software description and code examples for TIDA-00310, please see <u>TIDU577</u>: <u>Software Code</u> <u>Examples for TIDA-00310</u>.

#### 5.1 Analog Inputs

#### 5.1.1 Range Select Register

The 4-analog input channels of ADS8684 can be configured to a given voltage range by configuring the range select register.

- Channel 0 range selector register address is 05h

- Channel 1 range selector register address is 06h

- Channel 2 range selector register address is 07hW

- Channel 3 range selector register address is 08h

#### Table 8. Channel n Input Range Registers

| 7 | 6 | 5 | 4 | 3 | 2   | 1                       | 0   |

|---|---|---|---|---|-----|-------------------------|-----|

| 0 | 0 | 0 | 0 | 0 |     | Range_CH <i>n</i> [2:0] |     |

| R | R | R | R | R | R/W | R/W                     | R/W |

#### Table 9. Channel n Input Range Registers Field Descriptions

| BIT | FIELD                   | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | 0                       | R    | 0h    | Must always be set to 0                                                                                                                                                                                                                                                                                                                                             |

| 2:0 | Range_CH <i>n</i> [2:0] | R/W  | 0h    | Input range selection bits for channel n (n = 0 to 3 for ADS8684)<br>000 = Input range is set to $\pm 2.5 \times V_{REF}$<br>001 = Input range is set to $\pm 1.25 \times V_{REF}$<br>010 = Input range is set to $\pm 0.625 \times V_{REF}$<br>101 = Input range is set to 0 to 2.5 x V <sub>REF</sub><br>110 = Input range is set to 0 to 1.25 x V <sub>REF</sub> |

# 5.1.2 ADC Gain Control — Programmable Gain Amplifier

The devices offer a PGA at each individual analog input channel, which converts the original single-ended input signal into a fully-differential signal to drive the internal 16-bit ADC. The PGA also adjusts the common-mode level of the input signal before being fed into the ADC to ensure maximum usage of the ADC input dynamic range. Depending on the range of the input signal, the PGA gain can be accordingly adjusted by setting the Range\_CHn[2:0] (n = 0 to 3) bits in the program register. The default or power-on state for the Range\_CHn[2:0] bits is 000, which corresponds to an input signal range of  $\pm 2.5 \times VREF$ . Table 10 lists the various configurations of the Range\_CHn[2:0] bits for the different analog input voltage ranges. The PGA uses a very highly-matched network of resistors for multiple gain configurations. Matching between these resistors and the amplifiers across all channels is accurately trimmed to keep the overall gain error low across all channels and input ranges.

#### Table 10. PGA of ADS8684

| ANALOG INPUT RANGE           | Range_CH <i>n</i> [2:0]                                                                                               |       |       |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|-------|--|--|--|

| ANALOG INFOT KANGE           | BIT 2         Control           0         0         0           0         0         0           1         1         1 | BIT 1 | BIT 0 |  |  |  |

| $\pm 2.5 \times V_{REF}$     | 0                                                                                                                     | 0     | 0     |  |  |  |

| ±1.25 × V <sub>REF</sub>     | 0                                                                                                                     | 0     | 1     |  |  |  |

| ±0.625 × V <sub>REF</sub>    | 0                                                                                                                     | 1     | 0     |  |  |  |

| 0 to 2.5 × V <sub>REF</sub>  | 1                                                                                                                     | 0     | 1     |  |  |  |

| 0 to 1.25 × V <sub>REF</sub> | 1                                                                                                                     | 1     | 0     |  |  |  |

#### 5.1.3 ADC Sampling — Auto Scan Sequencing Control Register

In AUTO\_RST mode, the device automatically scans the preselected channels in ascending order with a new channel selected for every conversion. Each individual channel can be selectively included in the auto channel sequencing. For the channels that are not selected for auto sequencing, the AFE circuitry can be individually powered down.

#### **Command Register Description**

The command register is a 16-bit, write-only register that is used to set the operating modes of ADS8684. The settings in this register are used to select the channel sequencing mode (AUTO\_RST or MAN\_Ch\_n), configure the device in standby (STDBY) or power-down (PWR\_DN) mode, and reset (RST) the program registers to their default values. All command settings for this register are listed in Table 11. During power-up or reset, the default content of the command register is all 0s and the device waits for a command to be written before being placed into any mode of operation The device executes the command at the end of this particular data frame when the CS signal goes high.

| REGISTER                                   | MSB BYTE |     |     |     |     |     |    |    | LSB BYTE  | COMMAND | OPERATION IN NEXT FRAME              |  |

|--------------------------------------------|----------|-----|-----|-----|-----|-----|----|----|-----------|---------|--------------------------------------|--|

| REGISTER                                   | B15      | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B[7:0]    | (Hex)   |                                      |  |

| Continued Operation<br>(NO_OP)             | 0        | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | 0000h   | Continue operation in previous mode  |  |

| Standby<br>(STDBY)                         | 1        | 0   | 0   | 0   | 0   | 0   | 1  | 0  | 0000 0000 | 8200h   | Device is placed into standby mode   |  |

| Power Down<br>(PWR_DN)                     | 1        | 0   | 0   | 0   | 0   | 0   | 1  | 1  | 0000 0000 | 8300h   | Device is powered down               |  |

| Reset Program Registers<br>(RST)           | 1        | 0   | 0   | 0   | 0   | 1   | 0  | 1  | 0000 0000 | 8500h   | Program register is reset to default |  |

| Auto Ch. Sequence with Reset<br>(AUTO_RST) | 1        | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | A000h   | Auto mode enabled following a reset  |  |

| Manual Ch 0 Selection<br>(MAN_Ch_0)        | 1        | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | C000h   | Channel 0 input is selected          |  |

| Manual Ch 1 Selection<br>(MAN_Ch_1)        | 1        | 1   | 0   | 0   | 0   | 1   | 0  | 0  | 0000 0000 | C400h   | Channel 1 input is selected          |  |

| Manual Ch 2 Selection<br>(MAN_Ch_2)        | 1        | 1   | 0   | 0   | 1   | 0   | 0  | 0  | 0000 0000 | C800h   | Channel 2 input is selected          |  |

| Manual Ch 3 Selection<br>(MAN_Ch_3)        | 1        | 1   | 0   | 0   | 1   | 1   | 0  | 0  | 0000 0000 | CC00h   | Channel 3 input is selected          |  |

| Manual AUX Selection<br>(MAN_AUX)          | 1        | 1   | 1   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | E000h   | AUX channel input is selected        |  |

Table 11. Command Register Description of ADS8684

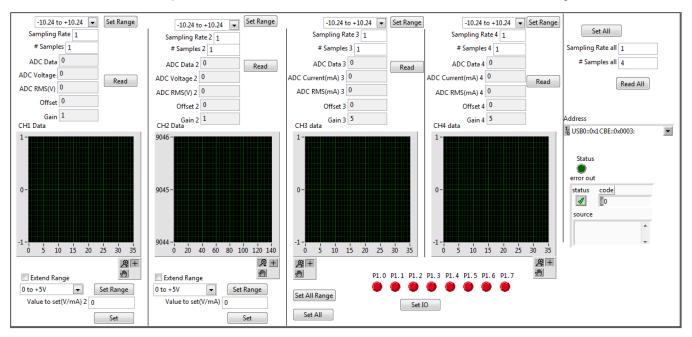

# 5.1.4 Auto-Scan Sequence Enable Register (Address = 01h)