# FAIRCHILD SEMICONDUCTOR

# THE VOLTAGE REGULATOR APPLICATIONS HANDBOOK

**MARCH 1974**

# THE VOLTAGE REGULATOR APPLICATIONS HANDBOOK

#### Prepared by

Linear Applications Staff Fairchild Semiconductor

### 464 Ellis Street, Mountain View, California 94042

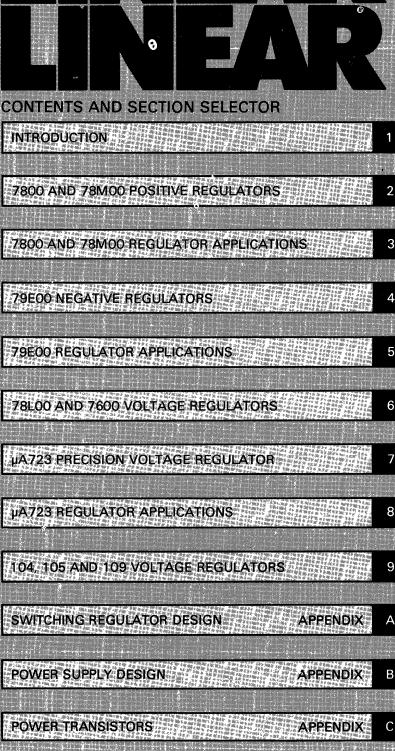

# **CONTENTS**

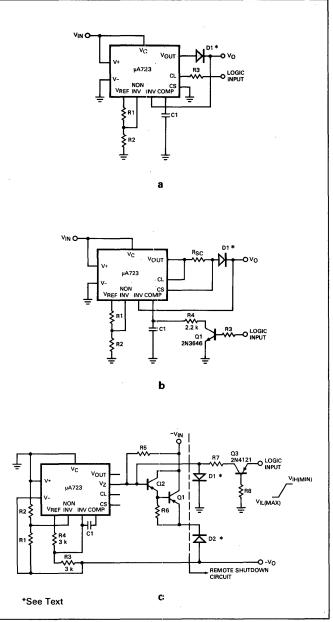

# CHAPTER 1

| INTRODUCTION                  | PAGE |

|-------------------------------|------|

| INTRODUCTION                  |      |

| SPECIFICATIONS AND PARAMETERS |      |

| SELECTION GUIDE               |      |

# CHAPTER 2

# 7800/78M00 POSITIVE, 3-TERMINAL VOLTAGE REGULATORS

| INTRODUCTION                       |      |

|------------------------------------|------|

| VOLTAGE REFERENCE                  |      |

| ERROR AMPLIFIER                    |      |

| THERMAL OVERLOAD PROTECTION        |      |

| FUNCTIONAL DESCRIPTION             |      |

| TESTING PHILOSOPHY                 |      |

| CONDENSED SPECIFICATIONS           |      |

| TYPICAL PERFORMANCE CURVES         |      |

| TYPICAL ELECTRICAL CHARACTERISTICS |      |

| PACKAGING AND CONNECTION DIAGRAMS  | 2-11 |

| ORDERING INFORMATION               | 2-12 |

# CHAPTER 3

| 7800/78M00 POSITIVE, 3-TERMINAL VOLTAGE REGULATOR APPLICATIONS |     |

|----------------------------------------------------------------|-----|

| BYPASSING                                                      | 3-3 |

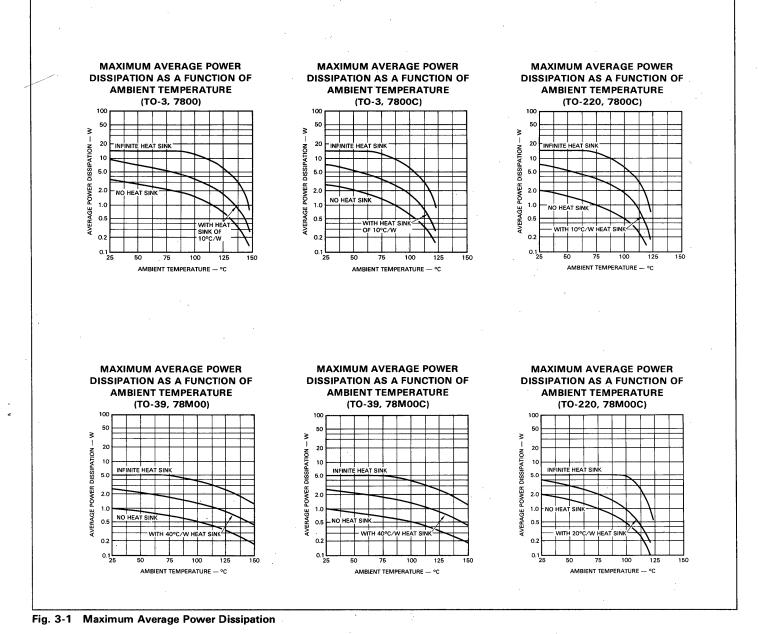

| THERMAL CONSIDERATIONS                                         |     |

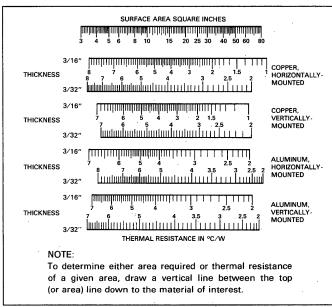

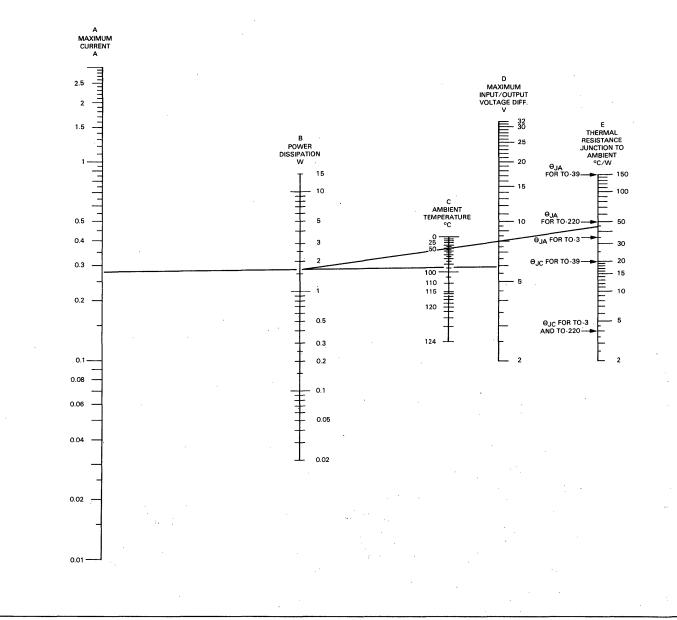

| Heat Sink Selection                                            | 3-4 |

| Package/Heat Sink Nomograph                                    | 3-5 |

| TYPICAL APPLICATIONS                                           |     |

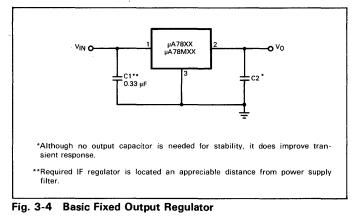

| Fixed Output Regulator                                         | 3-6 |

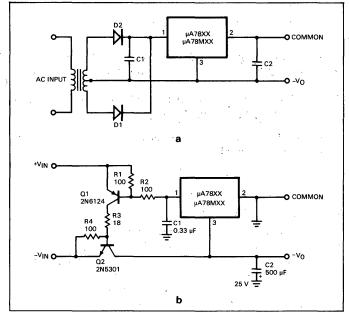

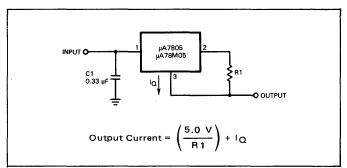

| Negative Output Voltage Regulators                             |     |

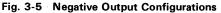

| Current Regulator                                              | 3-6 |

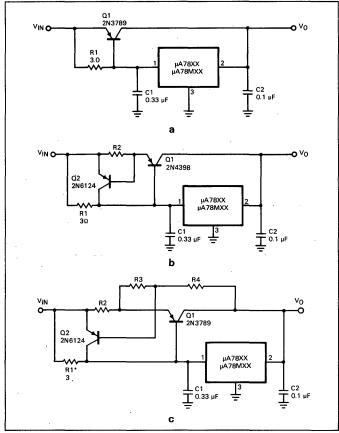

| High Current Voltage Regulators                                | 3-6 |

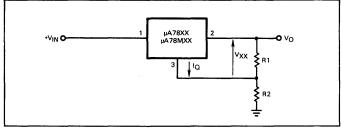

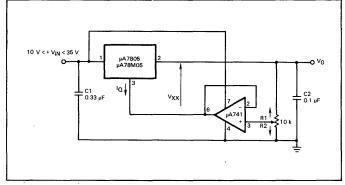

| Variable Output Voltage Regulators                             | 3-7 |

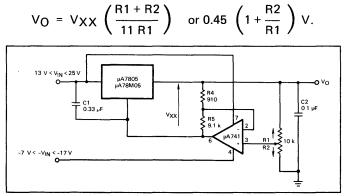

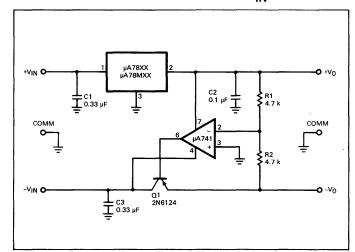

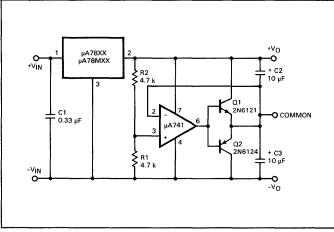

| Dual Polarity Regulators                                       | 3-7 |

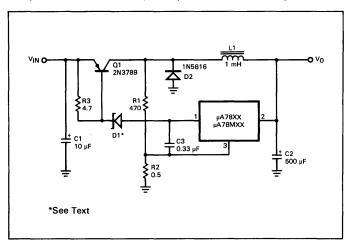

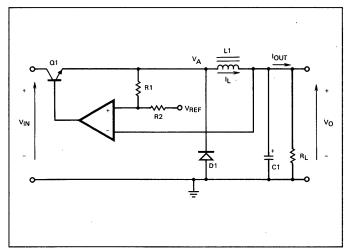

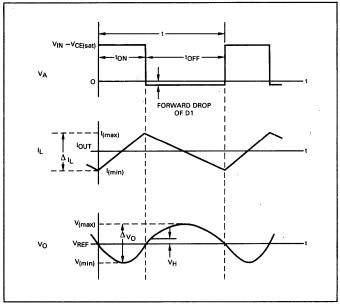

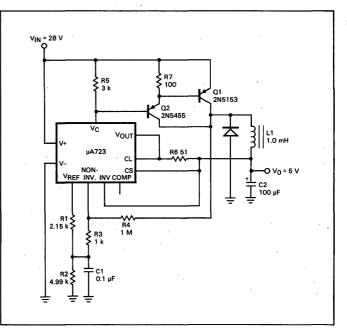

| Switching Regulators                                           | 3-8 |

# CHAPTER 4

| 79E00 NEGATIVE, 3-TERMINAL VOLTAGE REGULATORS (To be Announced) |     |

|-----------------------------------------------------------------|-----|

| INTRODUCTION                                                    | 4-3 |

| FUNCTIONAL DESCRIPTION                                          | 4-3 |

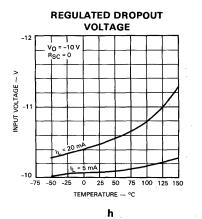

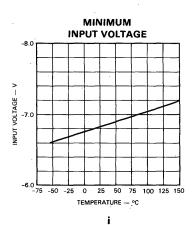

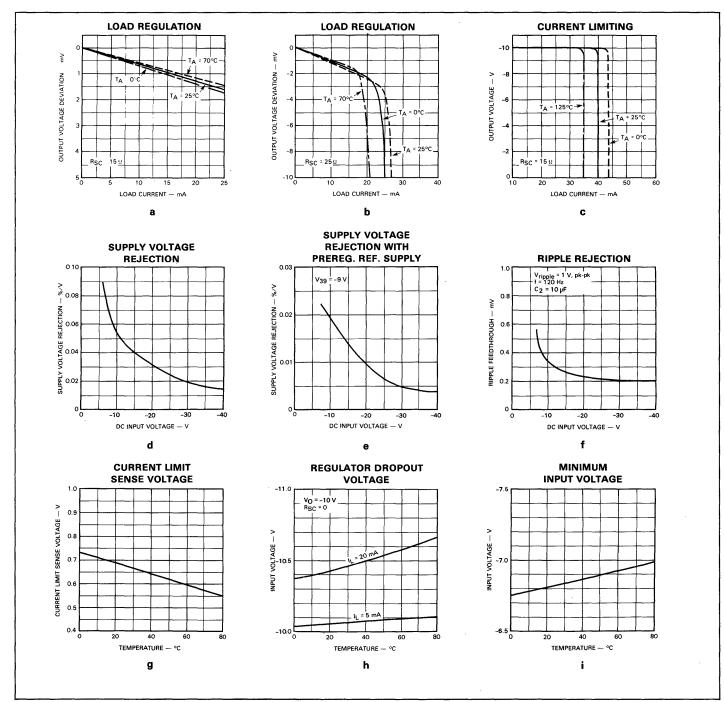

| TYPICAL PERFORMANCE CHARACTERISTICS                             | 4-4 |

| PACKAGING AND CONNECTION DIAGRAMS                               | 4-4 |

# CHAPTER 5

|                        | 79E00 NEGATIVE, 3-TERMINAL VOLTAGE REGULATOR APPLICATIONS |    |   |

|------------------------|-----------------------------------------------------------|----|---|

| BYPASSING              | BYPASSING                                                 | 5- | 3 |

| THERMAL CONSIDERATIONS | THERMAL CONSIDERATIONS                                    | 5- | 3 |

# **CHAPTER 5**

| CHAPTER 5                                | PAGE |

|------------------------------------------|------|

| TYPICAL APPLICATIONS                     |      |

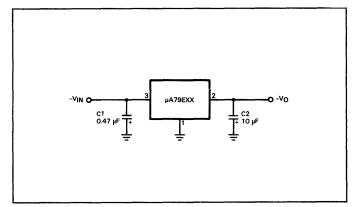

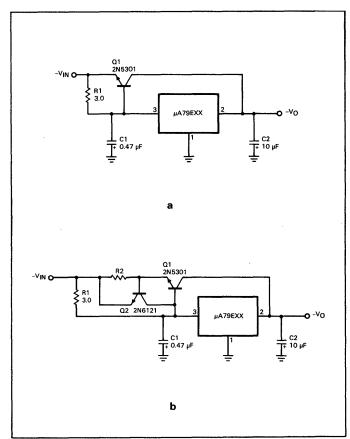

| Basic 3-Terminal Regulator               |      |

| High Current Negative Voltage Regulators |      |

# CHAPTER 6

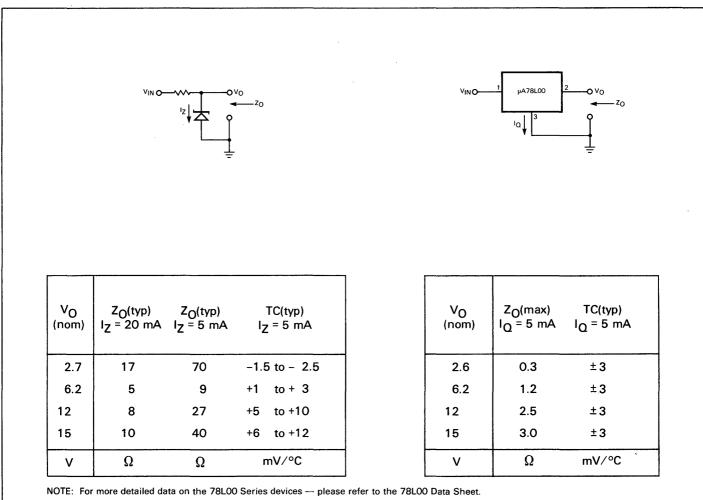

| 78L00 LOW CURRENT, POSITIVE VOLTAGE REGULATORS (To be Approvinced)                                                 |   |

|--------------------------------------------------------------------------------------------------------------------|---|

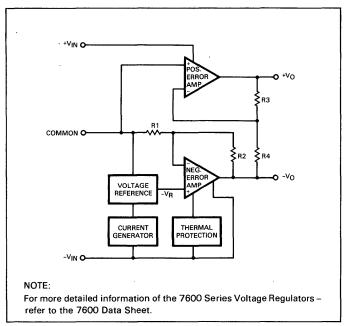

| 78L00 LOW CURRENT, POSITIVE VOLTAGE REGULATORS (To be Announced)<br>7600 DUAL POLARITY TRACKING VOLTAGE REGULATORS |   |

| INTRODUCTION                                                                                                       | 3 |

| 78L00 DESCRIPTION                                                                                                  | 3 |

| 7600 DESCRIPTION                                                                                                   | 4 |

# CHAPTER 7

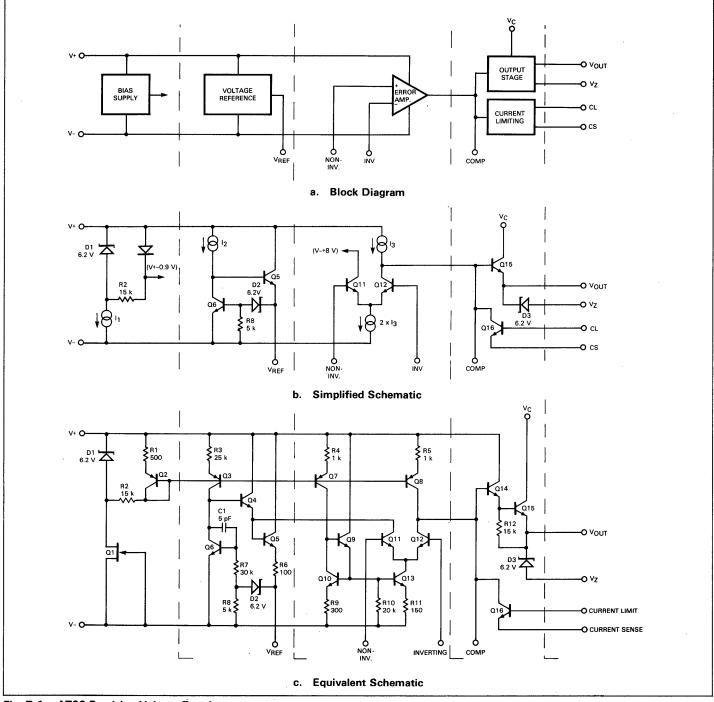

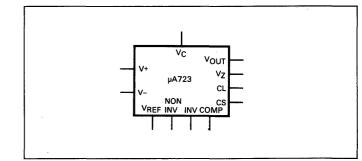

| μA723 PRECISION VOLTAGE REGULATOR               |     |

|-------------------------------------------------|-----|

|                                                 | 7-3 |

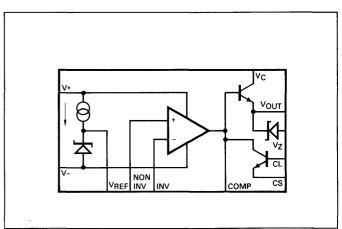

| FUNCTIONAL DESCRIPTION                          | 7-4 |

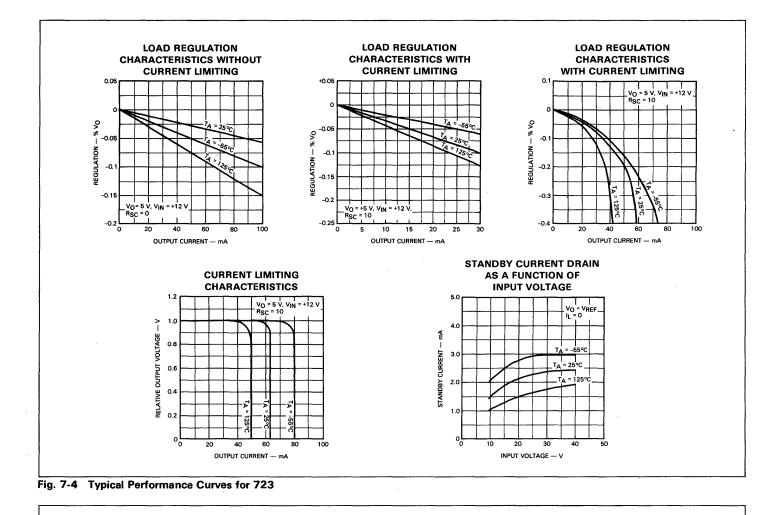

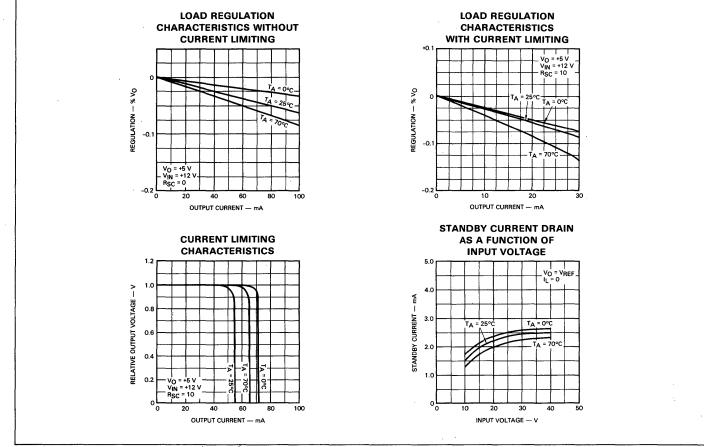

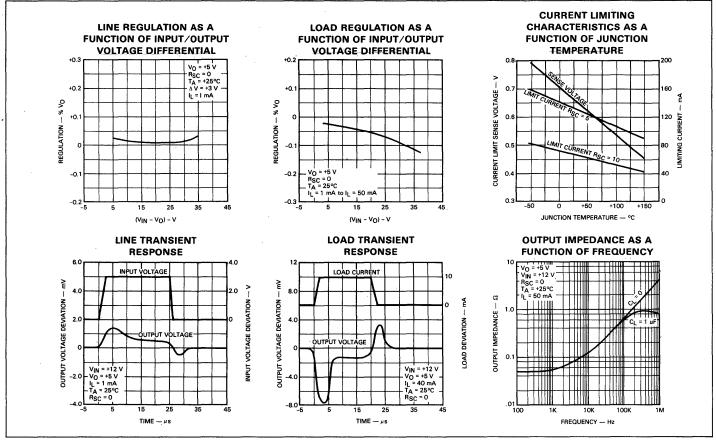

| CONDENSED SPECIFICATIONS AND PERFORMANCE CURVES | 7-5 |

| ELECTRICAL CHARACTERISTICS                      | 7-6 |

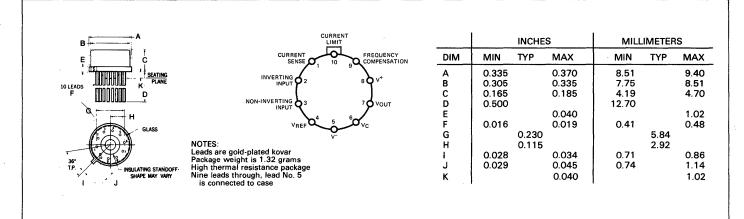

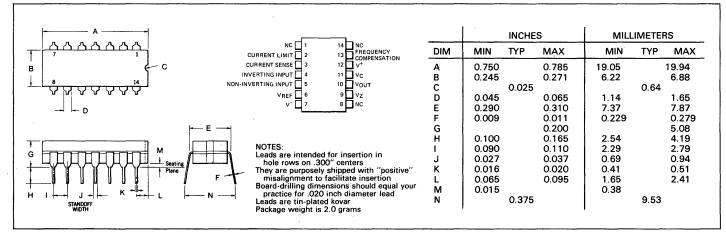

| PACKAGING AND CONNECTION DIAGRAMS               | 7-8 |

### CHAPTER 8

### µA723 PRECISION VOLTAGE REGULATOR APPLICATIONS

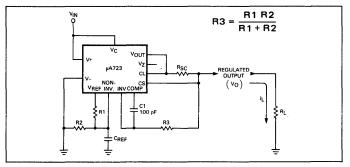

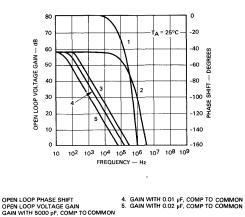

| FREQUENCY COMPENSATION                                                  |   |

|-------------------------------------------------------------------------|---|

| μA723 Open Loop Voltage Gain and Phase Shift as a Function of Frequency | 3 |

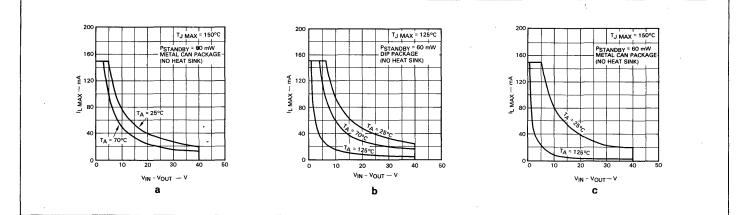

| THERMAL CONSIDERATIONS                                                  | 3 |

| µA723 Load Current Capabilities                                         | 3 |

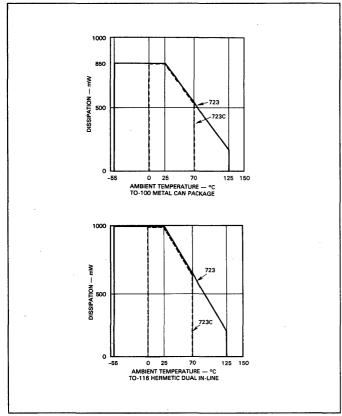

| Maximum Power Dissipation in Free Air                                   | 4 |

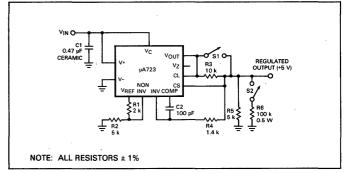

| FUNCTIONAL TEST CIRCUIT                                                 | 4 |

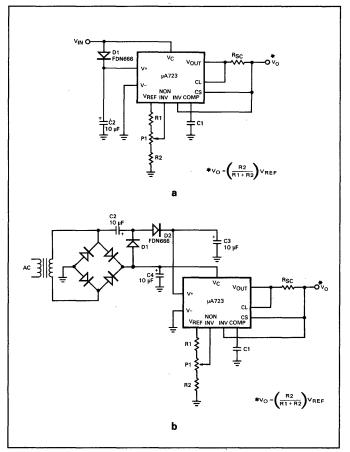

| TYPICAL APPLICATIONS                                                    | 4 |

| Introduction                                                            | 4 |

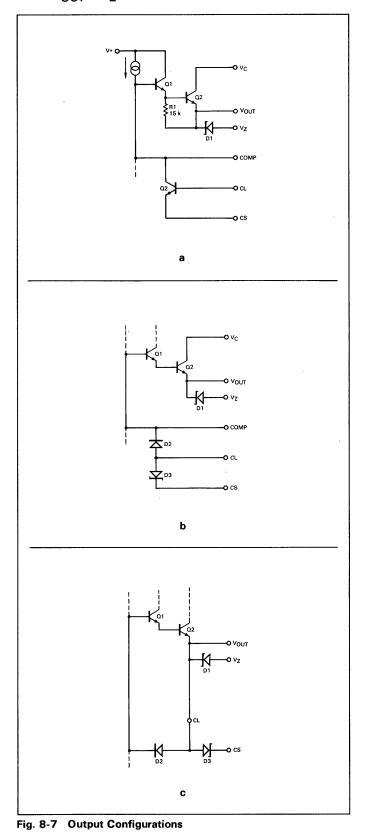

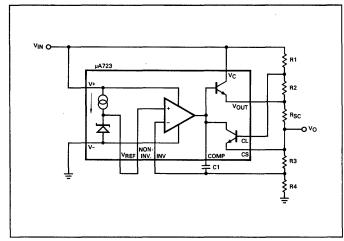

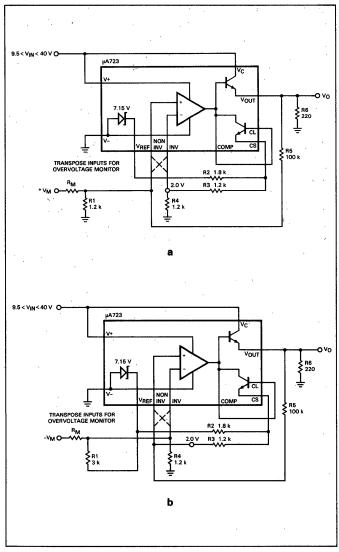

| Output Configurations                                                   | 5 |

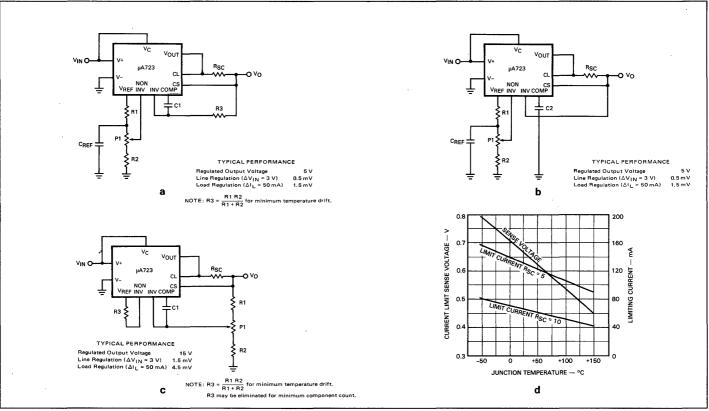

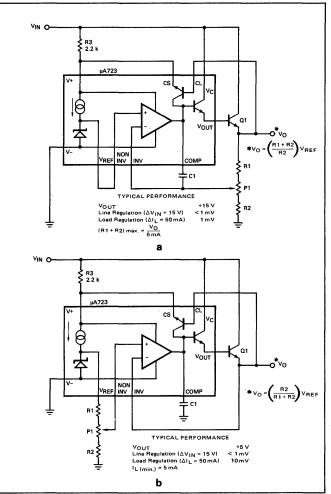

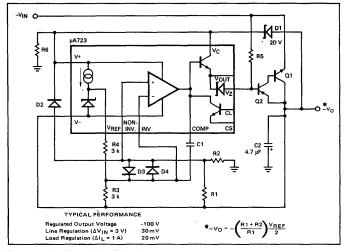

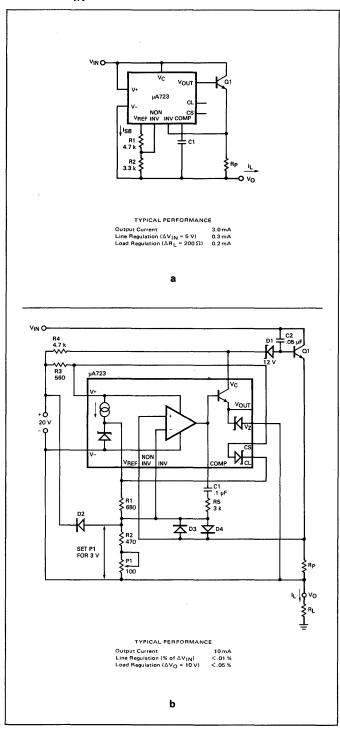

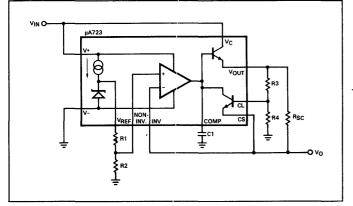

| Positive Regulators, 150 mA Maximum8-5                                  | 5 |

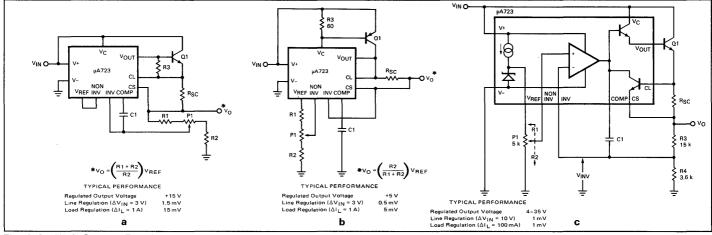

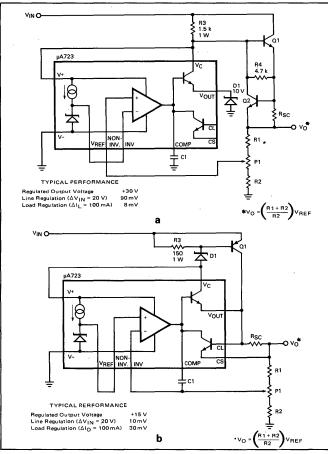

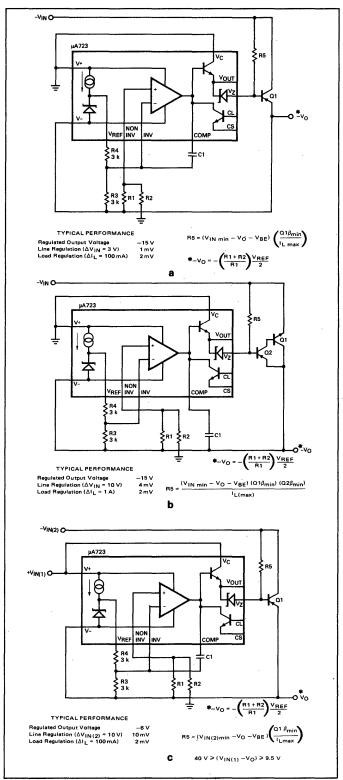

| Positive Regulators, High Output Current                                | 6 |

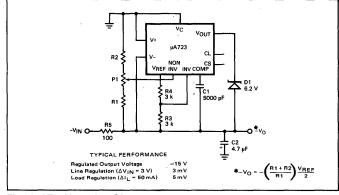

| Positive Shunt Regulator                                                |   |

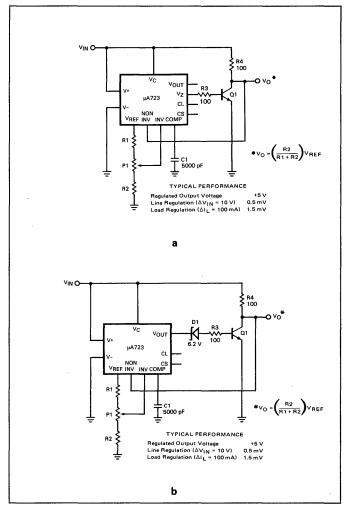

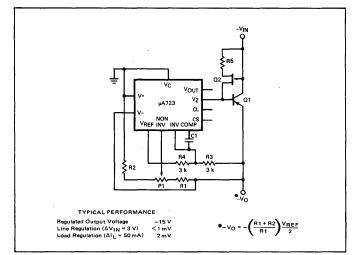

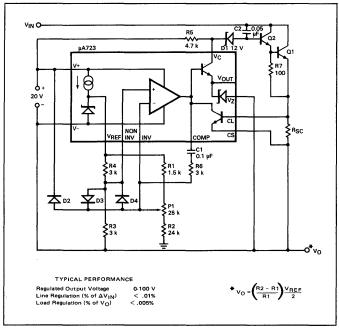

| Positive Regulators, High Line Rejection                                | 7 |

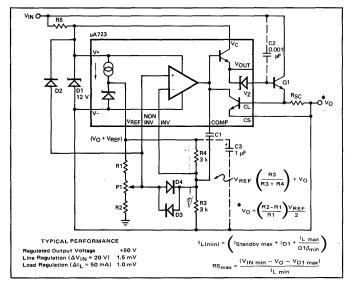

| Positive Regulators, High Input Voltage8-7                              | 7 |

| Positive Regulator, Floating                                            |   |

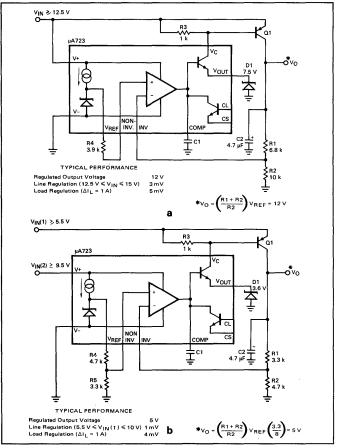

| Positive Regulators, Low Input/Output Differential                      | 8 |

| Positive Regulators, Marginal Input Voltage                             |   |

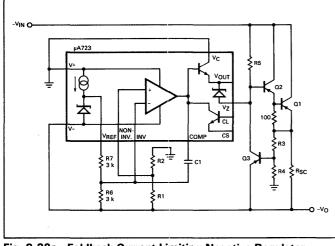

| Negative Regulators, Medium/High Output Current                         | 9 |

| Negative Shunt Regulator                                                |   |

| Negative Regulator, High Line Rejection8-10                             |   |

| Negative Regulator, Floating                                            | 0 |

| Current Regulators                                                      |   |

| Precision Voltage Regulator                                             |   |

| Foldback Current Limiting                                               |   |

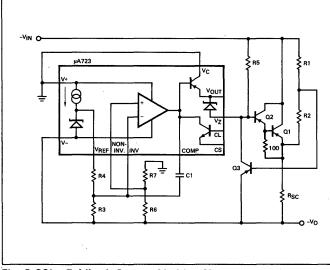

| Foldback Current Limiting, Positive Regulator                           | 2 |

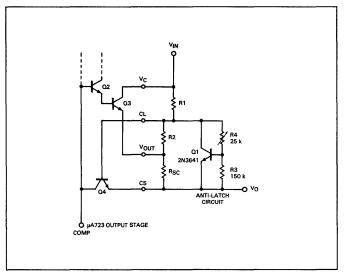

| Foldback Current Limiting, Negative Regulator8-12                       |   |

| Foldback Current Limiting, Modified8-12                                 |   |

| Foldback Current Limiting, Positive Regulator, Alternate Method         | 3 |

| Foldback Current Limiting, Negative Regulator, Alternate Method         |   |

| Foldback Current Limiting, FET                                          |   |

| Short Circuit Sensing, Low Loss                                         |   |

| Short Circuit Sensing, Temperature Stabilized                           |   |

| Remote Shutdown                                                         |   |

| Overvoltage Crowbar Protection                                          | 5 |

| Over/Under Voltage Monitoring8-1                                        |   |

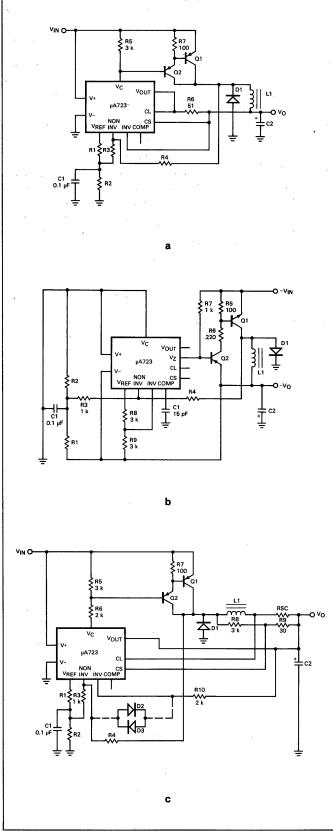

| Switching Regulators                                                    |   |

| Resistor Values for Standard Output Voltages                            | 7 |

# **CHAPTER 9**

| 104, 105 AND 109 VOLTAGE REGULATORS | PAGE |

|-------------------------------------|------|

| INTRODUCTION                        | 9-3  |

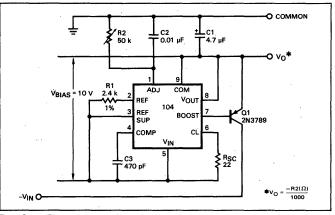

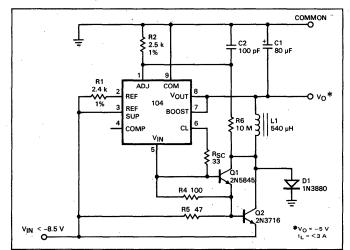

| 104 FAMILY                          | 9-3  |

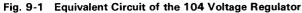

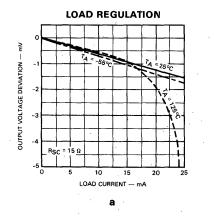

| TYPICAL PERFORMANCE CURVES          | 9-4  |

| ELECTRICAL CHARACTERISTICS          | 9-6  |

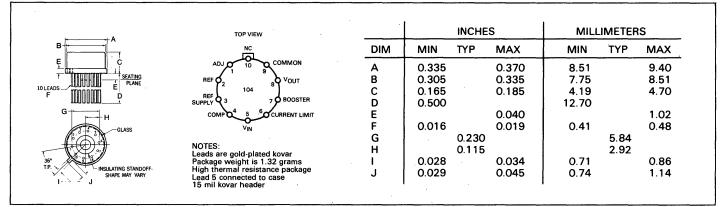

| PACKAGING AND CONNECTION DIAGRAM    | 9-7  |

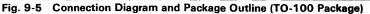

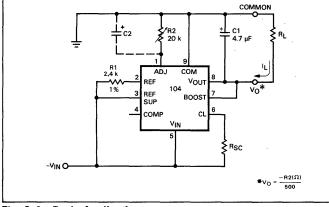

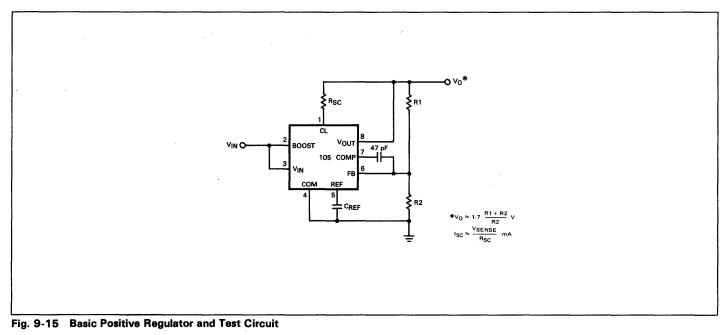

| BASIC APPLICATIONS                  | 9-7  |

| Floating Regulator                  | 9-7  |

| High Current Regulator              | 9-7  |

| Switching Regulator                 | 9-7  |

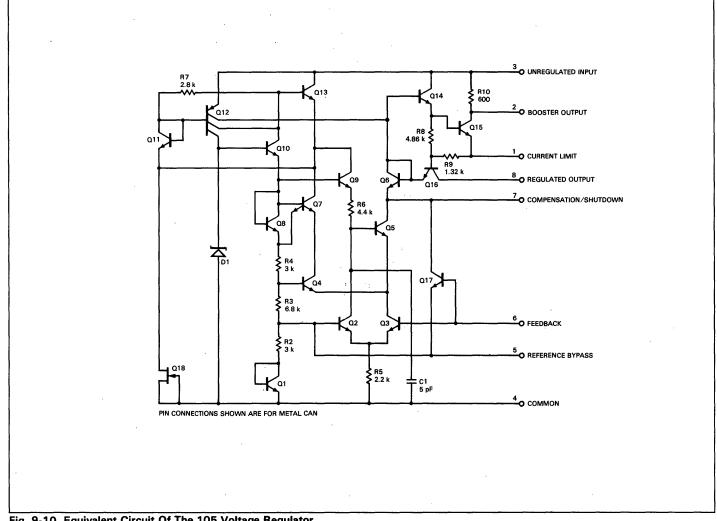

| 105 FAMILY                          | 9-8  |

| TYPICAL PERFORMANCE CURVES          |      |

| ELECTRICAL CHARACTERISTICS          |      |

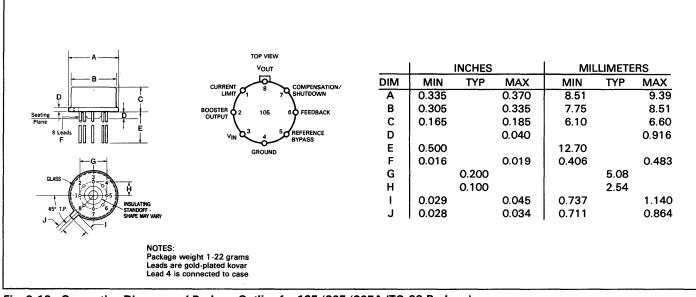

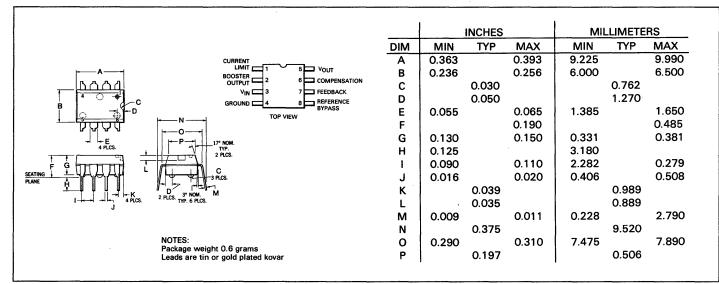

| PACKAGING AND CONNECTION DIAGRAM    |      |

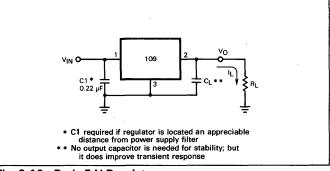

| 109 FAMILY                          | 9-14 |

| TYPICAL PERFORMANCE CURVES          |      |

| ELECTRICAL CHARACTERISTICS          |      |

| PACKAGING AND CONNECTION DIAGRAM    |      |

# APPENDIX A

| SWITCHING REGULATOR DESIGN |     |

|----------------------------|-----|

| INTRODUCTION               | A-3 |

| CIRCUIT OPERATION          | A-3 |

| DESIGN EXAMPLE             |     |

| POWER LOSSES               | A-4 |

# APPENDIX B

| POWER SUPPLY DESIGN |

|---------------------|

|---------------------|

| INTRODUCTION                                     | В-З  |

|--------------------------------------------------|------|

| DEFINITION OF TERMS                              | В-З  |

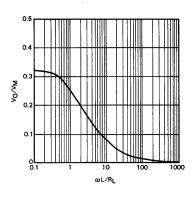

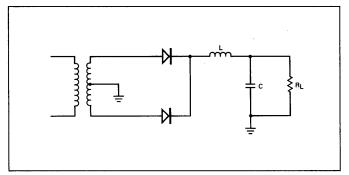

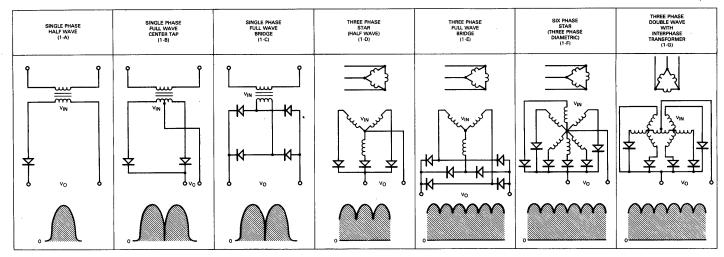

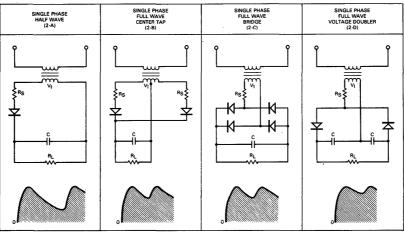

| SINGLE PHASE, HALF WAVE RECTIFIER                | В-З  |

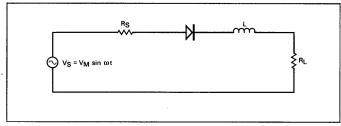

| HALF WAVE RECTIFIER WITH SERIES INDUCTIVE FILTER | В-4  |

| SINGLE PHASE, FULL WAVE RECTIFIER                | В-4  |

| Design Example                                   | B-5  |

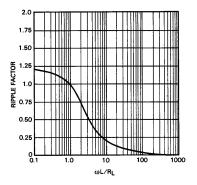

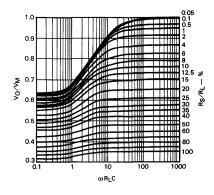

| LC SECTION FILTER                                | B-5  |

| Design Example                                   | B-6  |

| SWINGING CHOKE LC SECTION FILTER                 |      |

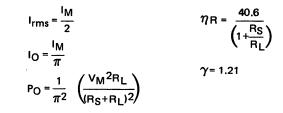

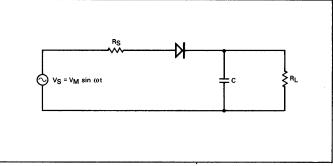

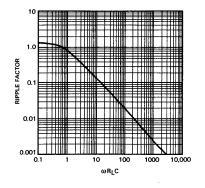

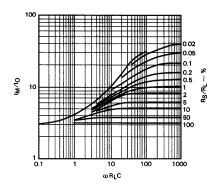

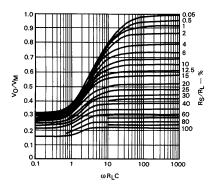

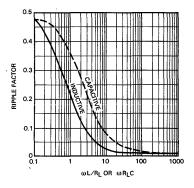

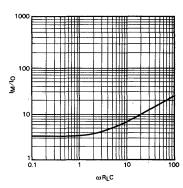

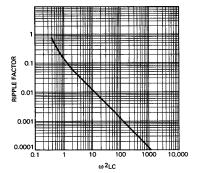

| CAPACITIVE INPUT FILTER CHARACTERISTICS          | B-8  |

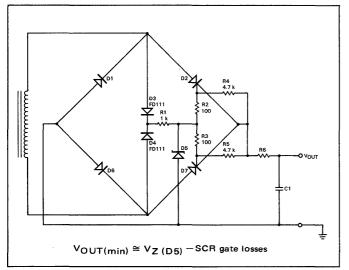

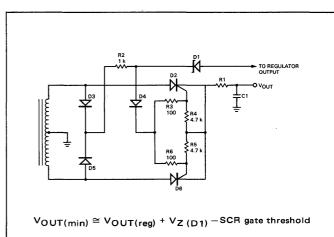

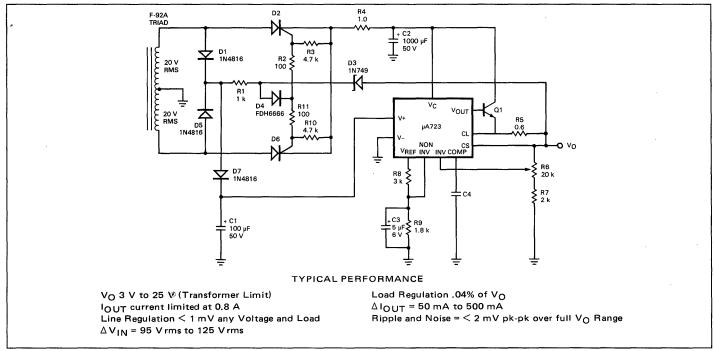

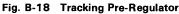

| PRE-REGULATORS                                   | B-8  |

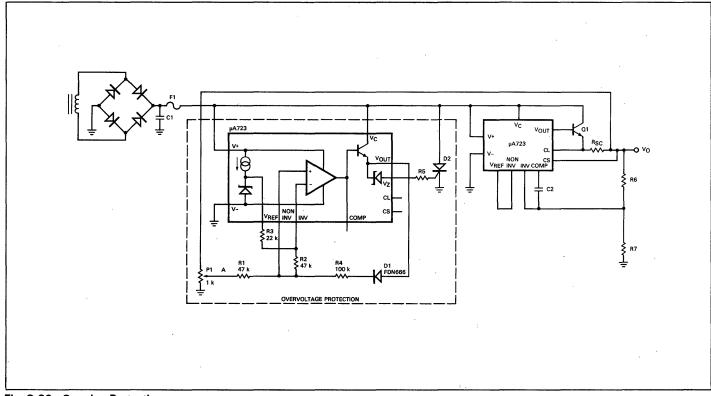

| COMPLETE CIRCUITS                                | B-9  |

| REFERENCES                                       | B-11 |

# APPENDIX C

| POWER TRANSISTORS                               |     |

|-------------------------------------------------|-----|

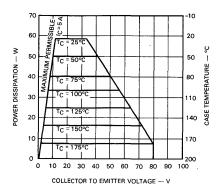

| INTRODUCTION                                    | C-3 |

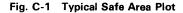

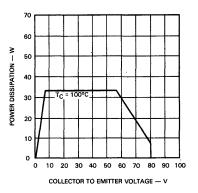

| SAFE AREA CONSIDERATIONS                        | C-3 |

| FORWARD BIASED AREA                             | C-3 |

| Safe Area Limiting Factors                      | C-3 |

| The Thermal Limitation                          |     |

| Heat Sinking                                    | C-4 |

| The Second Breakdown Limitation                 |     |

| Factors Influencing Second Breakdown Capability | C-5 |

| Power Device Technology                         | C-5 |

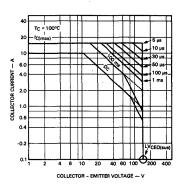

| Pulsed Operation                                | C-5 |

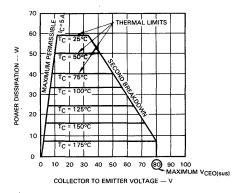

| REVERSE BIASED SAFE AREA                        | C-6 |

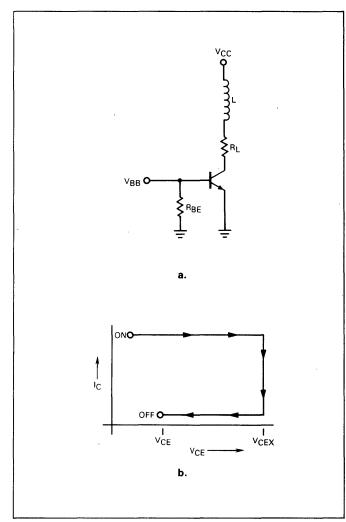

| Inductive Loads                                 | C-6 |

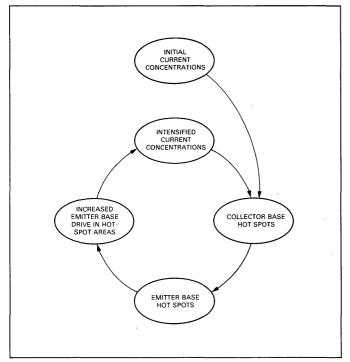

| Current Concentration During Reverse Bias       | C-6 |

| Factors Influencing Reverse Bias Safe Area      | C-6 |

| Specification of Reverse Bias Safe Area         | C-6 |

| SILICON POWER TRANSISTORS                       | C-6 |

| POWER TRANSISTOR SELECTION CHART                | C-7 |

# **IN THIS CHAPTER:**

- INTRODUCTION

- SPECIFICATIONS AND PARAMETERS

- SELECTION GUIDE

# CHAPTER 1 Introduction

In spite of the common, almost universal, use of regulated power supplies in systems design, they are still one of the factors most likely to be compromised in terms of engineering effort and design time. This is due to the wide variety of system power requirements. The main purpose of this handbook, then, is to provide the power supply designer with a complete, practical reference for voltage regulators and thus contribute to a shorter, more efficient design cycle.

Monolithic voltage regulators have improved tremendously, both in performance and reliability, since 1967. One of the most significant steps was the introduction of the 3-terminal, fully protected regulator in 1969. The industry's first (and present) standard voltage regulator is the  $\mu$ A723. This device and its wide scope of applications is discussed in Chapter 8. In direct contrast, 3-terminal regulators, such as the Fairchild  $\mu$ A7800 series, are designed for specific fixed-voltage applications. These devices require very few external components, are essentially blow-out proof, and are low in cost. With these features it is difficult, if not impossible, to justify building discrete component regulators, particularly for local on-card applications.

This handbook devotes two chapters to each major regulator family. Specifically covered are the µA7800, µA78M00, µA7600, µA79E00, and the µA723. The first chapters describe the internal design of the devices and their electrical characteristics. The subsequent chapters discuss electrical and thermal considerations useful as guidelines in device application, and a brief description of the primary circuit applications. Because there are many different types of regulators, more than one circuit approach to a particular system requirement is quite likely. In such cases, a value judgement must be made to select the optimum approach for that application. Later chapters describe new regulator developments at Fairchild and list some currently available secondsource devices. An aid in the successful application of voltage regulators is a selection guide covering the complete regulator line. Also included in this handbook are appendices covering switching regulator and power supply design, and a guide to the selection and operation of suitable power transistors.

A major premise of this handbook is that the reader is familiar with the basic operation of IC voltage regulators. Briefly stated: a temperature-compensated reference voltage is developed on-chip and is compared with the derived output voltage present in an error amplifier. This amplifier requires both high gain and wide bandwidth to ensure good regulation characteristics and fast transient response. It must also have low temperature drift to maintain a high order of output voltage stability under changing temperature conditions. The error amplifier drives the output stage, consisting of a Darlington pair. Also located on the chip are the necessary bias supplies, and various protection circuits.

Unless otherwise stated, line and load regulation characteristics are specified at a junction temperature of 25°C. This ensures that the specification limits represent true regulation limits unmasked by thermal effects. Therefore, to test for these characteristics, it is necessary to use a low duty cycle input signal to minimize device dissipation. Internal device heating during production testing is prevented by programming the automatic test equipment for very short test times (the entire regulator test cycle is completed in less than one second).

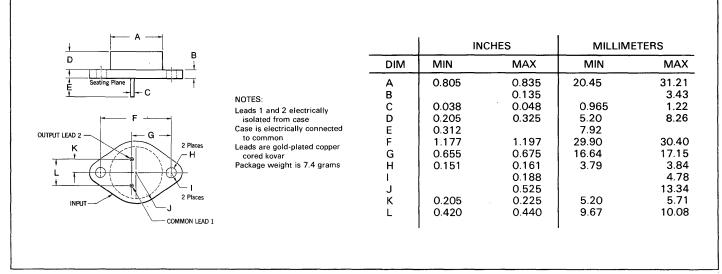

Throughout this book equivalent metric dimensions have been derived from the original inch dimensions.

#### SPECIFICATIONS AND PARAMETERS -

Some general comments on voltage regulator specifications and parameter definitions follow.

AVERAGE TEMPERATURE COEFFICIENT OF OUTPUT VOLTAGE — The percent change in output voltage for a specified ambient temperature change.

DROPOUT VOLTAGE — The input-to-output differential voltage at which the circuit ceases to regulate against further input voltage reductions.

**INPUT VOLTAGE RANGE** — The range of dc input voltage within which the regulator operates to tolerance.

INPUT-TO-OUTPUT VOLTAGE DIFFERENTIAL — The range between the input and output voltages outside of which the regulator does not operate to tolerance.

LINE REGULATION — The percent change in output voltage for a specified change in input voltage.

LOAD REGULATION — The percent change in output voltage for a specified change in load current.

LONG TERM STABILITY — Output voltage stability under accelerated life test conditions measured after 1000 hours at maximum rated voltage/power dissipation.

OUTPUT NOISE VOLTAGE — The rms value of noise voltage measured at the output with a constant load current and no input ripple.

OUTPUT RESISTANCE — The resistance, at a specified value of load current, seen at the output terminal.

OUTPUT VOLTAGE RANGE — The range of regulated output voltages over which certain specifications apply.

QUIESCENT CURRENT — That part of the regulator input current not delivered to the load.

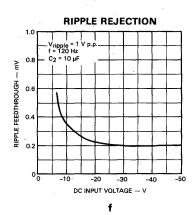

RIPPLE REJECTION — The ratio of peak-to-peak input ripple voltage to peak-to-peak output ripple voltage.

SHORT-CIRCUIT CURRENT LIMIT — The output current of the regulator measured with the output shorted to the negative supply.

STANDBY CURRENT DRAIN — The supply current drawn by the regulator under no output load and no reference voltage load.

TEMPERATURE STABILITY — The percent change in output voltage over a specified ambient temperature range.

With respect to the output voltage temperature coefficient, particularly in the case of 3-terminal regulators, the relevant temperature is the junction temperature, not the ambient temperature. This means an estimate must be made of worstcase operating junction temperatures for each application. Fortunately, these devices are well-characterized by their thermal characteristics, simplifying this task.

Operation of a regulator at, or near, its dropout voltage — or minimum permissible input-to-output voltage differential must take into account the absolute worst-case minimum input voltage, including any ripple voltage present.

All currently used 3-terminal regulators provide internal protection to guard against the more commonly experienced failure modes. These are discussed in Chapter 2. In extraordinary situations, however, certain additional precautions are essential to avoid damage to the device. A voltage supply connected to the output which exceeds the input voltage is one such situation. If the input shorts to ground, the larger voltage supply at the output causes a reversed current flow through the regulator, probably destroying the device. If using an auxilliary supply at the output from a possible short with a series diode. It is also essential that the normal output voltage of the regulator be greater than the second power source.

For the 723 regulator, ripple rejection is specified over a 50 Hz to 10 kHz frequency range; but 120 Hz only for all 3-terminal regulators. Characteristic curves, however, are

included to indicate the ripple rejection expected at any specific frequency up to 100 kHz. Note also that ripple rejection for the 3-terminal regulators is specified at a relatively high load current when compared to their allowed maximum. A particularly important point is that some 3-terminal devices exhibit a ripple rejection figure which degrades considerably as the load current is increased. This is due to self-heating of the monolithic chip which has an adverse effect on the regulator reference voltage. Since the chip thermal time constant is comparable to the ripple voltage period, ripple rejection is degraded. In the chip layout of Fairchild regulators, care was taken to ensure minimal thermal interaction from high dissipation areas of the chip to critical areas such as the voltage reference supply and the error amplifier input.

For fixed voltage applications, the preferred device is a 3terminal regulator, from the 78L, 78M or 7800 series exhibiting the lowest current/power ratings consistent with worstcase requirements of the application.

The 7600 series offers the most economical means of powering small and medium size analog computing systems, and the 79E series effectively covers the needs of emitter-coupled logic systems.

The universal 723 is not only capable of giving precision regulator performance in all the above applications, but can be equally efficient in more unusual applications; e.g., both positive and negative, high voltage regulators, very high line rejection regulators, low input/output differential voltage regulators, and many others detailed in Chapter 8.

| TYPE NO.                           | PACKAGE                              | MAX LOAD<br>CURRENT<br>A         | OUTPUT<br>VOLTAGE<br>V   | PD(MAX)<br>FREE AIR<br>W     | PD(MAX)<br>INF. HEAT SINK<br>W | MAX LOAD<br>REGULATION<br>(ZERO TO<br>MAX IL) | MAX LINE<br>REGULATION<br>(OVER A NOMINAL<br>V <sub>IN</sub> RANGE) |

|------------------------------------|--------------------------------------|----------------------------------|--------------------------|------------------------------|--------------------------------|-----------------------------------------------|---------------------------------------------------------------------|

| 78XX<br>78XXC<br>78XXC<br>78XXC    | TO-3<br>TO-3<br>TO-220               | 1.0                              | Fixed<br>(Seep 2-12)     | 3.5<br>3.0<br>2.0            | 15<br>15<br>15                 | 1%<br>2%<br>2%                                | 1%<br>2%<br>2%                                                      |

| 78MXX<br>78MXXC<br>78MXXC          | TO-39<br>TO-39<br>TO-220             | 0.5                              | Fixed<br>(Seep 2-12)     | 1.0<br>1.0<br>1.0            | 5.0<br>5.0<br>5.0              | 1%<br>2%<br>2%                                | 1%<br>2%<br>2%                                                      |

| 78LXXC<br>78LXXC                   | TO-92<br>TO-39                       | 0.1                              | Fixed                    | 0.7<br>0.8                   | 1.7<br>2.8                     | 2%<br>2%                                      | 2%<br>2%                                                            |

| 79EXX<br>79EXXC                    | TO-3<br>TO-3                         | 3.0 }                            | Fixed<br>(Negative)      | 3.5<br>3.0                   | 15<br>15                       | 1%<br>1%                                      | 1%<br>1%                                                            |

| 76XX<br>76XX                       | TO-100<br>Power DIP                  | 0.15                             | Fixed∕ Adj               | 0.8                          | <b>2.0</b><br>5.0              | 2%<br>2%                                      | 2%<br>2%                                                            |

| 723<br>723<br>723C<br>723C<br>723C | TO-100<br>TO-116<br>TO-100<br>TO-116 | 0.15                             | Adjustable               | 0.85<br>1.00<br>0.85<br>1.00 | 2.5<br>2.5                     | 0.5%<br>0.5%<br>0.6%<br>0.6%                  | 0.2%<br>0.2%<br>0.5%<br>0.5%                                        |

| 104<br>304                         | TO-100<br>TO-100                     | 0.025                            | Adjustable<br>(Negative) | 0.5<br>0.5                   |                                | 0.1%<br>0.1%                                  | 1%<br>1%                                                            |

| 105<br>305<br>305A<br>376          | TO-99<br>TO-99<br>TO-99<br>Mini-DIP  | 0.045<br>0.045<br>0.045<br>0.025 | Adjustable               | 0.5<br>0.5<br>0.5<br>0.45    |                                | 0.2%<br>0.2%<br>0.2%<br>0.2%                  | 1%<br>1%<br>1%<br>1%                                                |

| 109<br>209<br>309                  | TO-3<br>TO-3<br>TO-3                 | 1.0                              | 5.0                      | 3.5<br>3.5<br>3.0            | 20<br>20<br>20                 | 2%<br>2%<br>2%                                | 1%<br>1%<br>1%                                                      |

Table 1-1 Monolithic IC Voltage Regulators Selection Guide

# **IN THIS CHAPTER:**

- INTRODUCTION

- VOLTAGE REFERENCE

- ERROR AMPLIFIER

- THERMAL OVERLOAD PROTECTION

- FUNCTIONAL DESCRIPTION

- **TESTING PHILOSOPHY**

- CONSENSED SPECIFICATIONS

- TYPICAL PERFORMANCE CURVES

- TYPICAL ELECTRICAL CHARACTERISTICS

- PACKAGING AND CONNECTION DIAGRAMS

- ORDERING INFORMATION

# CHAPTER 2 7800/78M00 Positive, 3-Terminal Voltage Regulators

#### INTRODUCTION

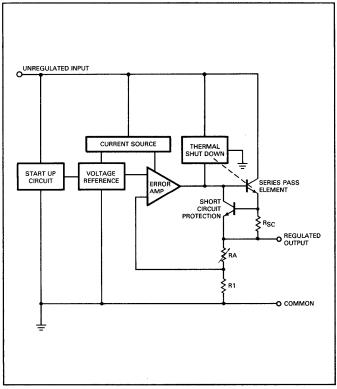

The 7800 series circuits are self contained, 3-terminal regulators specifically intended for use in a wide variety of fixed output voltage applications. The combination of internal current limiting, safe area compensation, and thermal shutdown makes these devices immune to the failure modes normally associated with power regulator applications.

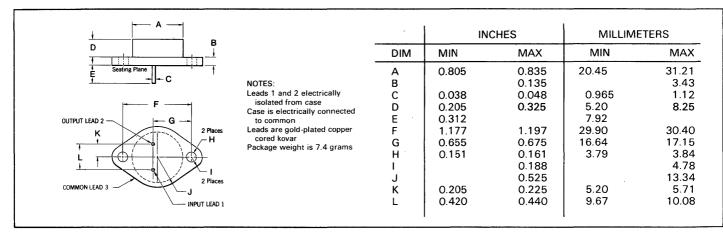

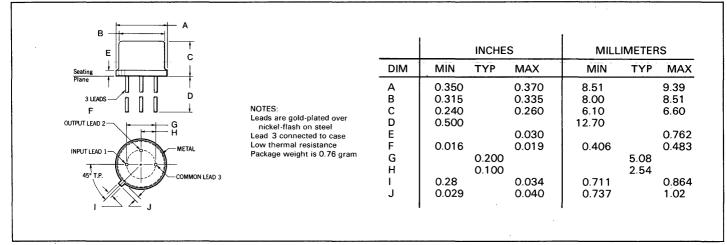

Two families of positive 3-terminal regulators are available differing only in their maximum output current rating.

- 78M00 series in a hermetic TO-39 package, or molded TO-220 package, rated at 0.5 A.

- 7800 series in a hermetic TO-3 package, or molded TO-220 package, rated at 1.0 A.

Since the electrical characteristics of the two families are virtually identical, only the 7800 series is described. Regulators are available in fixed output voltage options from 5 to 24 V. These options are first determined during the manufacturing process by the selection of an internal resistor matrix, RA, in the block diagram of *Figure 2-1* and, second, for an operating junction temperature range of -55 to  $+150^{\circ}$ C for the 7800 or 0 to  $+125^{\circ}$ C for the 7800C.

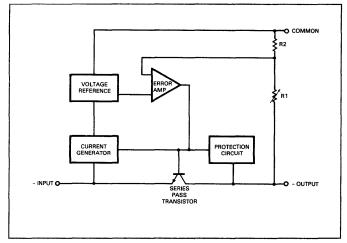

Fig. 2-1 Block Diagram of the 3-Terminal Regulator

Output voltages are specified at approximately  $\pm 4\%$  of the nominal voltage. In applications where closer tolerance outputs are required, external components may be added allowing the output voltage to be adjusted precisely. External pass transistors may be added to increase the current handling capabilities of the regulator. These, and other applications are illustrated in Chapter 3.

#### **VOLTAGE REFERENCE**

Temperature compensated Zener diodes are normally used as reference elements in IC voltage regulators; however, these diodes exhibit breakdown voltages above 6 V, thus imposing a lower limit on the input voltage to the regulator. Zeners also require excessively tight process controls to maintain a satisfactory tolerance for any nonadjustable (3-terminal) application.

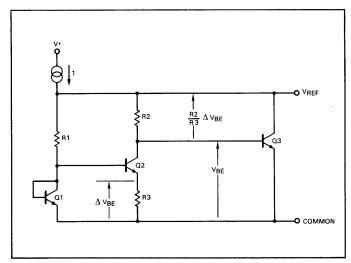

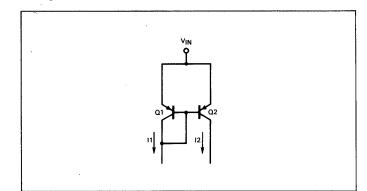

A voltage reference which does not use a Zener diode has been developed from the predictable temperature, current and voltage relationships in an emitter base junction. To obtain a temperature compensated reference voltage, the positive temperature coefficient of an emitter base voltage differential between two transistors operated at different current densities is added to the negative temperature coefficent of emitter base voltage. *Figure 2-2* shows such a reference. Transistor Q1 operates at a considerably higher current level than Q2 and the emitter base voltage differential is amplified by the voltage gain of transistor Q2.

Fig. 2-2 Voltage Reference Based on Base-Emitter Voltage

The reference voltage can be expressed as follows.

$$V_{BFF} = V_{BF3} + I_{CO2} R2 + I_{BO3} R2$$

$$V_{\text{REF}} = V_{\text{BE3}} + \frac{R^2}{R^3} \left( \Delta V_{\text{BE}} \right) + I_{\text{BQ3}} R^2$$

$$V_{\text{REF}} = V_{\text{BE3}} + \frac{R^2}{R^3} \left( \frac{KT}{q} \ln \frac{J^1}{J^2} \right) + I_{\text{BQ3}} R^2$$

$$V_{\text{REF}} \cong V_{\text{BE3}} + \frac{R^2}{R^3} \left( \frac{KT}{q} \ln \frac{R^2}{R^1} \right)$$

where J is current density.

By selecting the resistor ratios R2:R3 and R2:R1, a low voltage, temperature compensated reference is obtained.

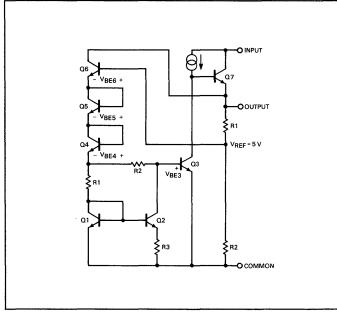

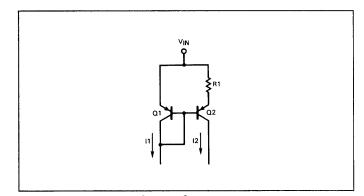

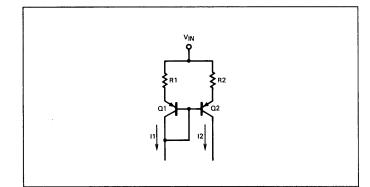

*Figure 2-3* shows a simplified schematic of the actual circuit used in the regulator. Transistors Q4, Q5 and Q6 are added to increase the reference level to 5 V.

Fig. 2-3 Simplified Circuit for the Regulator

The reference then becomes:

$$V_{\text{REF}} = (V_{\text{BE3}} + V_{\text{BE4}} + V_{\text{BE5}} + V_{\text{BE6}}) + \frac{R2}{R3} \left( \frac{KT}{q} \ln \frac{R2}{R1} \right)$$

Resistors R1, R2 and R3 are selected so that the reference voltage is constant over the temperature range and also has a nominal value of 5 V at room temperature.

An extremely tight reference voltage tolerance is, therefore, obtained without special process controls. This is because base emitter characteristics are better understood and more predictable than Zener references. Also, monolithic circuits lend themselves more readily to resistor and transistor matching. An external adjustment to trim output voltage is unnecessary in most applications. An additional benefit is that this reference has low noise output compared to a Zener reference, thus eliminating the need for a large bypass capacitor to remove noise.

#### ERROR AMPLIFIER

An error amplifier (see *Figure 2-1*) compares the output feedback signal with the voltage reference and corrects the output by the amount of the error. The regulator circuit shown in *Figure 2-3* has the error amplifier combined with the voltage reference. The advantage is that noise at the regulator output is minimized since the amplifier and reference are no longer separate sources of noise. In *Figure 2-3*, transistor Q3 is used as the error amplifier; and at the same time, its base emitter voltage is used as part of the reference.

A current source is used as the active load to the error amplifier. A negative feedback path is provided through feedback resistors R1 and R2. If the voltage at the output increases due to a reduction in load current, that voltage change is transmitted to the base of transistor Q3. Transistor Q3, then, conducts more, effectively reducing the base drive to the output transistor by current steering. The result is a decrease in output voltage, and this tends to correct the change in output voltage due to the load current change. As the loop settles, an equilibrium value at the output is reached. The output voltage is derived using the following formula.

Output Voltage =

$$V_{\text{REF}} \left( \frac{R1 + R2}{R2} \right)$$

Varying the resistor ratio R1 + R2:R2 yields different fixed output voltages.

#### THERMAL OVERLOAD PROTECTION

One of the benefits of including the series pass transistor on the chip is that it is then possible to incorporate both thermal and current overload protection.

Low power IC regulators usually rely on current limiting for overload protection as there is no practical way to sense junction temperature in a separate pass transistor. Excessive heating of the pass transistor, then, becomes one of the primary failure mechanisms of these solid state regulators. A thermal overload protection circuit in a monolithic regulator which contains the pass transistor limits the maximum temperature of the transistor junction. This limiting is independent of input voltage and the type of overload/degree of package heat sinking.

The base emitter junction of a transistor limiter is used to sense the temperature of the chip. The temperature limiter normally is biased below its activation threshold so that it does not affect circuit operation. If the chip temperature rises to its maximum limit due to a load fault or other conditions, the temperature limiter turns on. This removes the base drive to the output transistors and shuts down the regulator, preventing further chip heating.

#### **FUNCTIONAL DESCRIPTION**

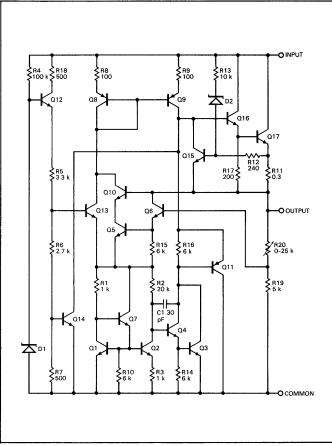

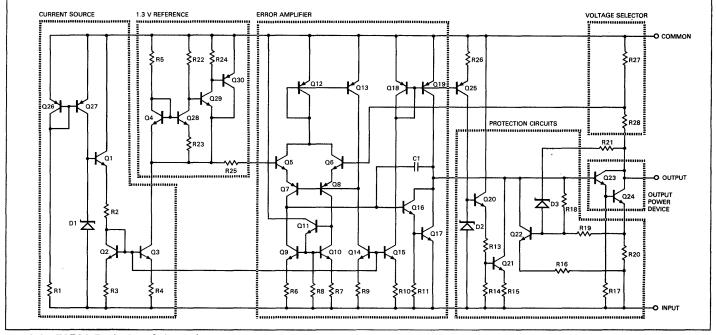

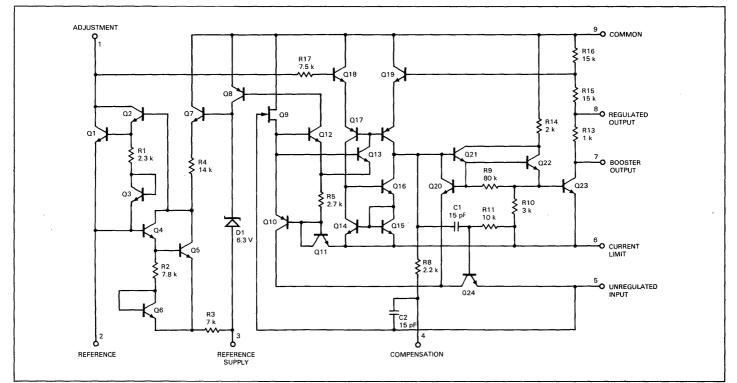

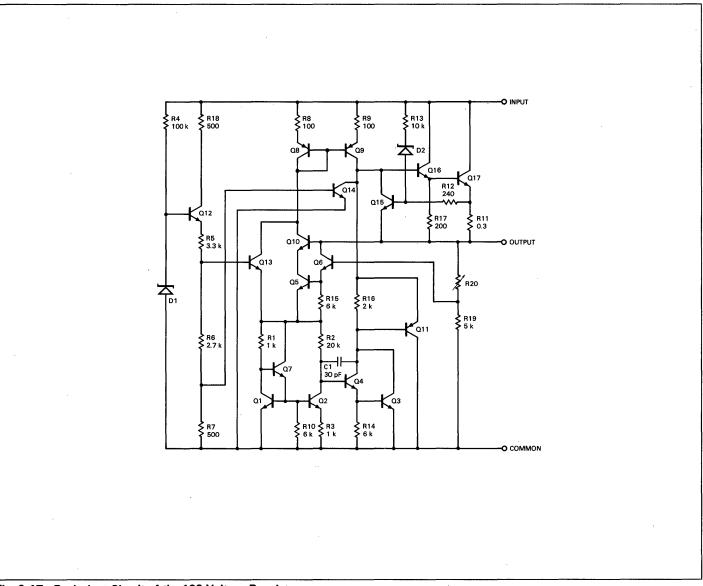

Figure 2-4 shows the equivalent schematic diagram of the IC regulator. Transistors Q1 through Q6 and resistors R1, R2 and R3 constitute a 5 V, temperature compensated internal voltage reference for the regulator. The base emitter voltages of transistors Q3, Q4, Q5 and Q6 provide the negative temperature coefficient component of the output voltage. The voltage drop across R2 is the positive temperature coefficient component. This is derived from the differential base emitter voltages across transistors Q1 and Q2, which operate at a current ratio of  $\approx$  20 to 1. The output voltage of the regulator is determined by selecting a ratio from a resistor matrix which multiplies the reference voltage. The current required by the load is supplied from the input terminal through the series pass transistor Q17, driven by transistor Q16. Transistor Q3 is the gain stage providing regulation. Its effective gain is increased by the pnp transistor Q11 which acts as a buffer to drive the active collector load formed by the pnp current source transistor pair, Q8 and Q9.

The current from Q8 and Q9 is set up by the current through resistor R1. During regulator turn on, the current in R1 flows first through transistor Q13 — part of a start up circuit containing Zener diode D1, transistors Q12 and Q13, and resistors R5, R6 and R7. After the device is in regulation, Q13 is biased off and the regulator takes over setting the current in R1, which now flows through Q5 and Q10. This start up circuit is required since the regulator which eventually is to supply the current in R1 is off during initial device turn on.

Thermal limiting is accomplished by transistor Q14. The base of Q14 is clamped to  $\approx 0.4$  V by the resistive divider string R5, R6 and R7 in the start up circuit. As the junction temperature rises, the turn on threshold of Q14 decreases. At a junction temperature of  $\approx 175^{\circ}$ C, transistor Q14 turns on and the base current drive to the drive transistor is removed. This shuts down the pass transistor and prevents further increases in chip temperature.

Fig. 2-4 Circuit Schematic of the 3-Terminal Regulator

Whereas this form of thermal protection is effective for *persistent* overloads which would cause excessive chip temperature, it is ineffective against *instantaneous* overloads which could result in a secondary breakdown of the pass transistor

or damage to metal interconnections due to abnormally high current density. Transistor Q15 and resistor R11 protect against instantaneous overloads by limiting output current. If the output current rises to a high level, the current through R11 will turn on Q15, thus shunting base current away from the driver transistor and preventing further increases in output current.

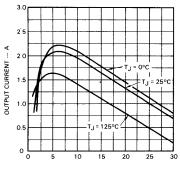

To ensure that the output transistor operates within its forward safe area, a compensating network is included to limit the instantaneous power in the output transistor. When the voltage across the pass transistor exceeds 8 V, current through resistor R13 and diode D2 reduces the limiting current. As illustrated in *Figure 2-5*, the higher the voltage across the pass transistor, the lower the limiting current.

INPUT-OUTPUT DIFFERENTIAL VOLTAGE - V

Fig. 2-5 Input-Output Differential vs Current Limit

An MOS capacitor of 30 pF is incorporated on the chip to ensure stable operation without the need for a bypass capacitor on the output.

*Table 2-1* shows the typical performance characteristics of the regulator.

| PARAMETER                                | TEST CONDITIONS<br>( $V_{OUT} = 5 V, T_J = 25^{\circ}C, V_{IN} = 10 V$<br>AND I <sub>OUT</sub> = 500 mA UNLESS | CHARACTERISTICS |                 |  |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--|--|--|

|                                          | OTHERWISE SPECIFIED)                                                                                           | 7805            | 78M05           |  |  |  |

| OUTPUT TOLERANCE                         |                                                                                                                | ±4%             | ±4%             |  |  |  |

| QUIESCENT CURRENT                        |                                                                                                                | 4.2 mA          | 4.5 mA          |  |  |  |

| OUTPUT RESISTANCE                        | f = 1 kHz                                                                                                      | 20 m $\Omega$   | 20 m Ω          |  |  |  |

| LINE REGULATION                          | °7 V ≼ V <sub>IN</sub> ≼ 25 V                                                                                  | 0.005%/V        | .0033%/V        |  |  |  |

| TEMPERATURE DRIFT                        | -20°C ≤ T <sub>J</sub> ≤ 125°C                                                                                 | 0.022%/°C       | 0.02%/°C        |  |  |  |

| MINIMUM INPUT VOLTAGE                    | I <sub>OUT</sub> = 1A (.5 A for 78MO5)                                                                         | 7.0 V           | 7.0 V           |  |  |  |

| OUTPUT NOISE VOLTAGE                     | 10 Hz ≼ f ≼ 100 kHz                                                                                            | 40 μV           | 40 μV           |  |  |  |

| RIPPLE REJECTION                         | f = 120 Hz                                                                                                     | 78 dB           | 80 dB           |  |  |  |

| THERMAL RESISTANCE<br>(JUNCTION TO CASE) | TO-3 PACKAGE<br>TO-220 PACKAGE<br>TO-39 PACKAGE                                                                | 4°C∕W<br>4°C∕W  | 5°C/W<br>20°C/W |  |  |  |

### **TESTING PHILOSOPHY**

The 7800 series device is tested in a manner reflecting its intended usage. The input/output voltage differential used to test each device in the series takes into account all the variations in a nominal, unregulated dc source.

For example, the 7812 is tested with a 7 V input/output differential which considers the following parameters and their variations.

- Minimum device input/output differential

- Power supply ripple

- Line voltage tolerance

- Diode drop variation and source impedance variations

*Table 2-2* presents the considerations resulting from the combination of all these factors and tolerances.

Therefore, not only is the 7812 tested with an additional guard band of 0.5 V (19 V total), but the input voltage range used for testing allows greater input voltage variation than found in actual use conditions. Other devices in the 7800 series are tested with the same practical considerations.

#### CONDENSED SPECIFICATIONS

The electrical characteristics listed below pertain specifically to the 7800 and 7800C series regulators. The 78M00 and 78M00C series have similar characteristics

except that nominal and peak output currents are 200 mA and 750 mA respectively, instead of 500 mA and 2.2 A for the 7800 and 7800C.

| $V_{IN} - V_O$ $2 V$ total       14.5 V         tine Variation = (10%) $1.4 V$ total       15.9 V         Ripple = (10%) $1.6 V$ total       17.5 V $R_s$ and $V_d$ = $1.0 V$                                   |                                     |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|

| ine       Variation = (10%)       14.5 V         ine       Variation = (10%)       1.4 V         iotal       15.9 V         tipple = (10%)       1.6 V         iotal       17.5 V $R_s$ and $V_d$ =       1.0 V | V <sub>O(max)</sub> =               | 12.5 V |

| ine Variation = (10%) $1.4 \text{ V}$ iotal       15.9 V         Ripple = (10%) $1.6 \text{ V}$ iotal       17.5 V         Rs and Vd = $1.0 \text{ V}$                                                          | V <sub>IN</sub> – V <sub>O</sub>    | 2 V    |

| iotal       15.9 V         tipple = (10%)       1.6 V         iotal       17.5 V $R_s$ and $V_d$ =       1.0 V                                                                                                  | Total                               | 14.5 V |

| Ripple = (10%) $1.6 V$ Total $17.5 V$ Rs and Vd = $1.0 V$                                                                                                                                                       | Line Variation = (10%)              | 1.4 V  |

| Total $17.5 \text{ V}$<br>R <sub>s</sub> and V <sub>d</sub> = $1.0 \text{ V}$                                                                                                                                   | Total                               | 15.9 V |

| $R_s$ and $V_d = 1.0 V$                                                                                                                                                                                         | Ripple = (10%)                      | 1.6 V  |

|                                                                                                                                                                                                                 | Total                               | 17.5 V |

| Total 18.5 V                                                                                                                                                                                                    | R <sub>s</sub> and V <sub>d</sub> = | 1.0 V  |

|                                                                                                                                                                                                                 | Total                               | 18.5 V |

Table 2-2 Derivation of Test Voltage

#### ABSOLUTE MAXIMUM RATINGS (7800, 7800C)

| Input Voltage (5 V through 18 V)                                | 35 V               |

|-----------------------------------------------------------------|--------------------|

| (24 V)                                                          | 40 V               |

| Internal Power Dissipation (Note 1)                             | Internally Limited |

| Storage Temperature Range                                       | –65°C to +150°C    |

| Operating Junction Temperature Range 7800                       | –55°C to +150°C    |

| 7800C                                                           | 0°C to +125°C      |

| Lead Temperature (Soldering, 60 second time limit) TO-3 Package | 300°C              |

| (Soldering, 10 second time limit) TO-220 Package                | 230°C              |

#### ABSOLUTE MAXIMUM RATINGS (78M00, 78M00C)

| Input Voltage (5 V through 15 V)                                 | 35 V                   |

|------------------------------------------------------------------|------------------------|

| (20 V, 24 V)                                                     | 40 V                   |

| Internal Power Dissipation (Note 1)                              | Internally Limited     |

| Storage Temperature Range                                        | -65°C to +200°C        |

| Operating Junction Temperature Range                             |                        |

| Military (78M00)                                                 | –55°C to +175°C        |

| Commercial (78M00C)                                              | 0°C to +175°C (TO-39), |

|                                                                  | 0°C to +125°C (TO-220) |

| Lead Temperature (Soldering, 60 second time limit) TO-39 Package | 300°C                  |

| (Soldering, 10 second time limit) TO-220 Package                 | 230°C                  |

#### Junction-to-Ambient

| TO-3 Package         | N |

|----------------------|---|

| TO-220 Package       | N |

| TO-39 Package 150°C/ | W |

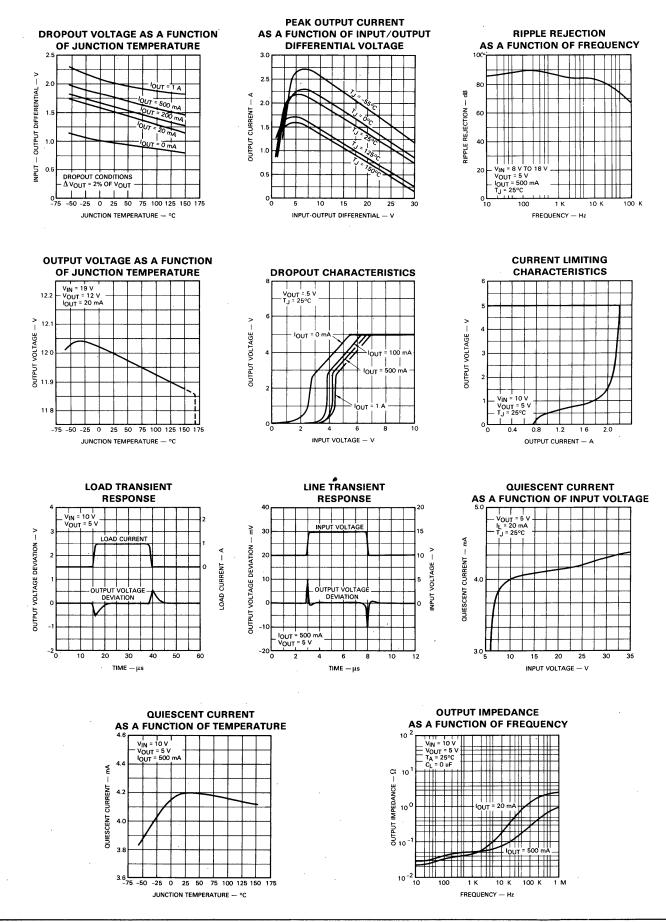

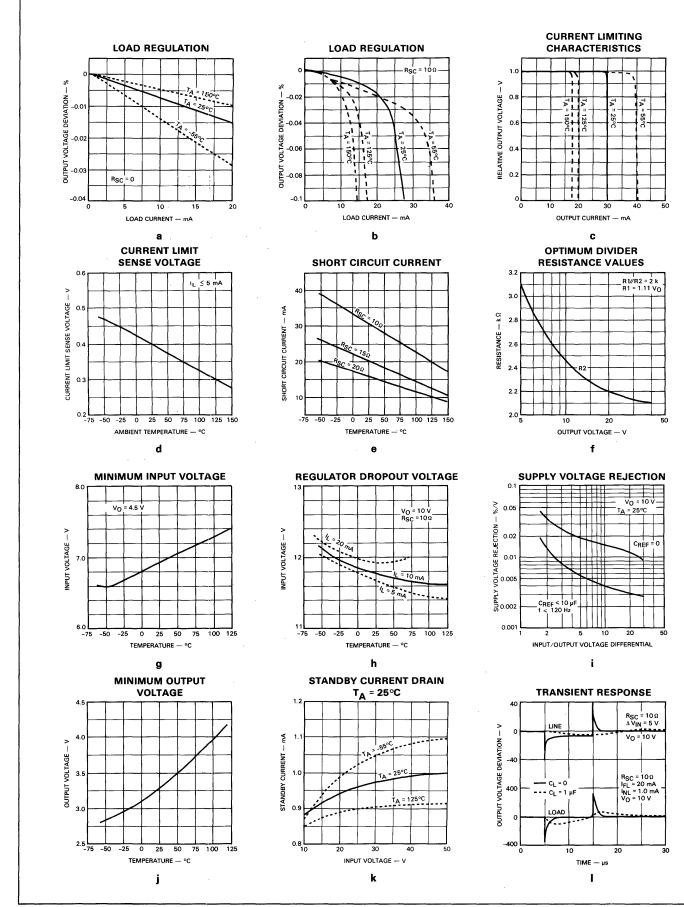

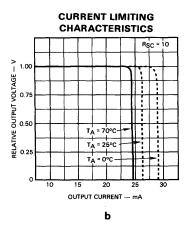

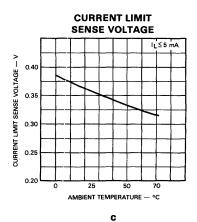

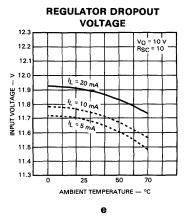

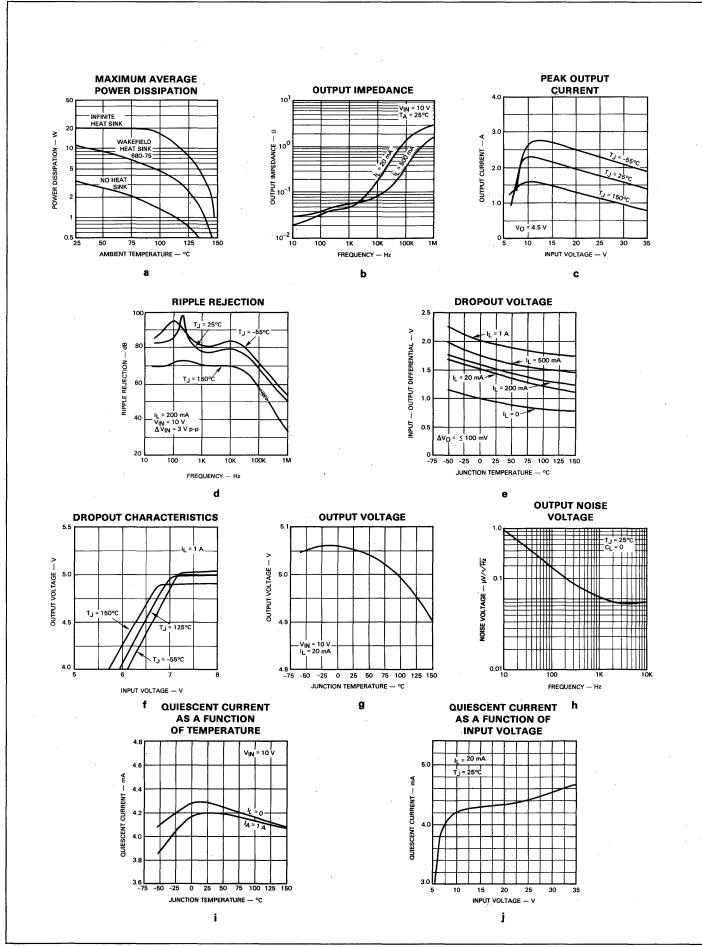

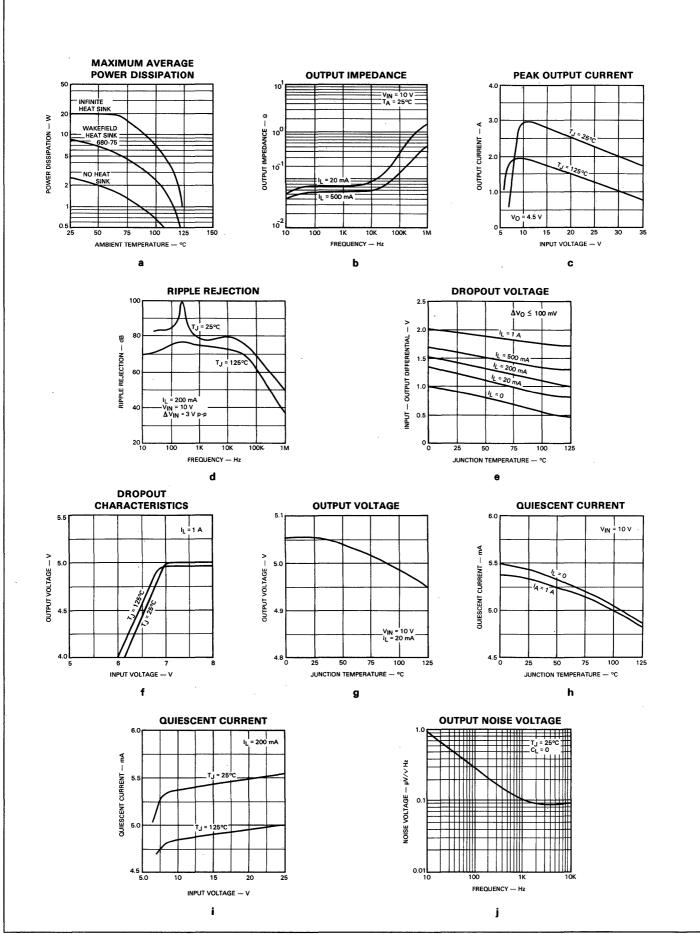

Fig. 2-6 Typical Performance Curves For 7800 Series

2

$V_{IN}$  = 10 V,  $I_{OUT}$  = 500 mA, -55°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (7805) 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C (7805C) unless otherwise specified

| PARAMETER                    |           | CONDITIONS                                                      |                                                    |      | 7805 |      |      |      |      |       |

|------------------------------|-----------|-----------------------------------------------------------------|----------------------------------------------------|------|------|------|------|------|------|-------|

|                              |           |                                                                 | CONDITIONS                                         | MIN  | ТҮР  | МАХ  | MIN  | ΤΥΡ  | МАХ  | UNITS |

| Output Voltage               |           | Тј = 25°С                                                       |                                                    | 4.8  | 5.0  | 5.2  | 4.8  | 5.0  | 5.2  | v     |

| Line Regulation              |           | T <sub>J</sub> = 25°C                                           | 7.0 V ≤ V <sub>IN</sub> ≤ 25V                      |      | 3.0  | 50   |      | 3.0  | 100  | mV    |

|                              |           | 11-200                                                          | 8.0 V ≤ V <sub>IN</sub> ≤ 12 V                     |      | 1.0  | 25   |      | 1.0  | 50   | mV    |

| Load Regulation              |           | Tj = 25°C                                                       | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.5 A                  |      | 15   | 50   |      | 15   | 100  | mV    |

|                              |           | 19 200                                                          | 250 mA ≤ I <sub>OUT</sub> ≤ 750 mA                 |      | 5.0  | 25   |      | 5.0  | 50   | mV    |

|                              |           | 8.0 V (7.0 V                                                    | / for 7805C) ≤ V <sub>IN</sub> ≤ 20 V              |      |      |      |      |      |      |       |

| Output Voltage               |           | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                               |                                                    | 4.65 |      | 5.35 | 4.75 |      | 5.25 | ° ∨   |

|                              |           | P ≤ 15 W                                                        |                                                    |      |      |      |      |      |      |       |

| Quiescent Current            |           | Tj = 25°C                                                       |                                                    |      | 4.2  | 6.0  |      | 4.2  | 8.0  | mA    |

| Quiescent Current Changes    | with line | 8.0 V (7.0 V for 7805C) $\leq$ V <sub>IN</sub> $\leq$ 25 V      |                                                    |      |      | 0.8  |      |      | 1.3  | mA    |

| Quiescent Cuirent Changes    | with load | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                               |                                                    |      |      | 0.5  |      |      | 0.5  | mA    |

| Output Noise Voltage         |           | T <sub>A</sub> = 25°C, 10 Hz ≤ f ≤ 100 kHz                      |                                                    |      | 40   |      |      | 40   |      | μV    |

| Long Term Stability          |           |                                                                 |                                                    |      |      | 20   |      |      | 20   | mV    |

| Ripple Rejection             |           | f = 120 Hz, 8.0 V ≤ V <sub>IN</sub> ≤ 18 V                      |                                                    | 68   | 78   |      | 62   | 78   |      | dB    |

| Dropout Voltage              |           | lour = 1.0 A, T <sub>J</sub> = 25°C                             |                                                    |      | 2.0  |      |      | 2.0  |      | V     |

| Output Resistance            |           | f = 1.0 kHz                                                     |                                                    |      | 17   |      |      | 17   |      | mΩ    |

| Short Circuit Current        |           | Тј = 25°С                                                       |                                                    |      | 750  |      |      | 750  |      | mA    |

| Peak Output Current          |           | T <sub>J</sub> = 25°C                                           |                                                    |      | 2.2  |      |      | 2.2  |      | А     |

| Augustan TC of Output Volta  |           | IOUT = 5.0                                                      | mA, $0^{\circ}C \le T_{J} \le 150^{\circ}C$ (7800) |      | -1.1 | 1    |      |      |      | mV/°C |

| Average TC of Output Voltage |           | I <sub>OUT</sub> = 5.0 mA, 0°C ≤ T <sub>J</sub> ≤ 125°C (7800C) |                                                    |      |      |      |      | -1.1 |      | mV/°C |

### ELECTRICAL CHARACTERISTICS

$V_{IN}$  = 11 V,  $I_{OUT}$  = 500 mA,  $-55^{\circ}C \le T_J \le 150^{\circ}C$  (7806)  $0^{\circ}C \le T_J \le 125^{\circ}C$  (7806C) unless otherwise specified

| PARAMETER                    |           | CONDITIONS                                                                              |                                                      |      | 7806 |      |      |      |      |       |

|------------------------------|-----------|-----------------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|------|------|------|-------|

|                              |           |                                                                                         | CONDITIONS                                           | MIN  | TYP  | MAX  | MIN  | TYP  | MAX  | UNITS |

| Output Voltage               |           | Tj = 25°C                                                                               |                                                      | 5.75 | 6.0  | 6.25 | 5.75 | 6.0  | 6.25 | v     |

| Line Regulation              |           | Тј = 25°С                                                                               | 8.0 V ≤ V <sub>IN</sub> ≤ 25 V                       |      |      | 5.0  |      |      | 120  | mV    |

|                              |           | ., 200                                                                                  | $9.0 V \le V_{IN} \le 13 V$                          |      |      | 1.5  |      |      | 60   | mV    |

| Load Regulation              |           | Tj = 25°C                                                                               | _5.0 mA ≤ I <sub>OUT</sub> ≤ 1.5 A                   | ļ    |      | 14   |      |      | 120  | mV    |

|                              |           |                                                                                         | 250 mA < 100T < 750 mA                               |      |      | 4.0  |      |      | 60   | mV    |

|                              |           | 9.0 V (8.0 V                                                                            | / for 7806C) ≤ V <sub>IN</sub> ≤ 21 V                | · ·  |      |      |      |      |      |       |

| Output Voltage               |           | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                                                       |                                                      | 5.65 |      | 6.35 | 5.7  |      | 6.3  | V     |

|                              |           | P≤ 15 W                                                                                 |                                                      |      |      |      |      |      |      |       |

| Quiescent Current            |           | T <sub>J</sub> = 25°C                                                                   |                                                      |      | 4.3  | 6.0  |      | 4.3  | 8.0  | mA    |

| Quiescent Current Change     | with line | 9.0 V (8.0 V for 7806C) $\leq$ V <sub>IN</sub> $\leq$ 25 V                              |                                                      |      |      | 0.8  |      |      | 1.3  | mA    |

| Quiescent Current Change     | with load | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                                                       |                                                      |      |      | 0.5  |      |      | 0.5  | mA    |

| Output Noise Voltage         |           | T <sub>A</sub> = 25°C, 10 Hz ≤ f ≤ 100 kHz                                              |                                                      |      | 45   |      |      | 45   |      | μV    |

| Long Term Stability          |           | · · · · · · · · · · · · · · · · · · ·                                                   |                                                      |      |      | 24   |      |      | 24   | mV    |

| Ripple Rejection             |           | f = 120 Hz, 9.0 V ≤ V <sub>IN</sub> ≤ 19 V                                              |                                                      | 65   | 75   |      | 59   | 75   |      | dB    |

| Dropout Voltage              |           | IOUT = 1.0 A, TJ = 25°C                                                                 |                                                      |      | 2.0  |      |      | 2.0  |      | V     |

| Output Resistance            |           | f = 1.0 kHz                                                                             |                                                      |      | 19   |      |      | 19   |      | mΩ    |

| Short Circuit Current T      |           | Tj = 25°C                                                                               |                                                      |      | 550  |      |      | 550  |      | mA    |

|                              |           | Tj = 25°C                                                                               |                                                      |      | 2.2  |      |      | 2.2  |      | А     |

| Average TC of Output Voltage |           | IOUT = 5.0                                                                              | $mA, 0^{\circ}C \leq T_{J} \leq 150^{\circ}C$ (7806) |      | -0.8 |      |      |      |      | mV/°C |

|                              |           | $I_{OUT} = 5.0 \text{ mA}, 0^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ (7806C) |                                                      | `    |      |      |      | -0.8 |      | mV/°C |

$V_{IN}$  = 14 V,  $I_{OUT}$  = 500 mA,  $-55^{\circ}C \le T_J \le 150^{\circ}C$  (7808)  $0^{\circ}C \le T_J \le 125^{\circ}C$  (7808C) unless otherwise specified

| PARAMETER                    |           | CONDITIONS                                                                                       |                                                    |     | 7808 |       |     | UNUTO |     |       |

|------------------------------|-----------|--------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|------|-------|-----|-------|-----|-------|

|                              |           |                                                                                                  | CONDITIONS                                         | MIN | түр  | МАХ   | MIN | ТҮР   | МАХ | UNITS |

| Output Voltage               |           | Т <sub>Ј</sub> = 25°С                                                                            |                                                    | 7.7 | 8.0  | 8.3   | 7.7 | 8.0   | 8.3 | v     |

| h ina Damitatian             |           | T - 05° 0                                                                                        | $10.5 V \le V_{IN} \le 25 V$                       |     | 6.0  | 80    |     | 6.0   | 160 | mV    |

| Line Regulation              |           | 1 J = 25 C                                                                                       | 11 V ≤ V <sub>IN</sub> ≤ 17 V                      |     | 2.0  | 40    |     | 2.0   | 80  | mV    |

| Land Davidation              |           | Тј = 25°С                                                                                        | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.5 A                  |     | 12   | 80    |     | 12    | 160 | mV    |

| Load Regulation              |           | 1j = 25 C                                                                                        | 250 mA ≤ I <sub>OUT</sub> ≤ 750 mA                 |     | 4.0  | 40    |     | 4.0   | 80  | mV    |

|                              |           | 11.5 V (10.                                                                                      | 5 V for 7808C) ≤ V <sub>IN</sub> ≤ 23 V            |     |      |       |     |       |     |       |

| Output Voltage               |           | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                                                                |                                                    | 7.6 |      | · 8.4 | 7.6 |       | 8.4 | v     |

|                              |           | P ≤ 15 W                                                                                         |                                                    |     |      |       | _   |       |     |       |

| Quiescent Current            |           | $T_J = 25^{\circ}C$                                                                              |                                                    |     | 4.3  | 6.0   |     | 4.3   | 8.0 | mA    |

| Quiescent Current Change     | with line | 11.5 V (10.5 V for 7808C) ≤ V <sub>IN</sub> ≤ 25 V                                               |                                                    |     |      | 0.8   |     |       | 1.0 | mA    |

| Quescent Current Change      | with load | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                                                                |                                                    |     |      | 0.5   |     |       | 0.5 | mA    |

| Output Noise Voltage         |           | $T_A = 25^{\circ}C$ , 19 Hz $\leq f \leq 100 \text{ kHz}$                                        |                                                    |     | 52   |       |     | 52    |     | μV    |

| Long Term Stability          |           |                                                                                                  |                                                    |     |      | . 32  |     |       | 32  | mV    |

| Ripple Rejection             |           | f = 120 Hz, 11.5 V ≤ V <sub>IN</sub> ≤ 21.5 V                                                    |                                                    |     | 72   |       | 56  | 72    |     | dB    |

| Dropout Voltage              |           | lout = 1.0 A, T <sub>J</sub> = 25°C                                                              |                                                    |     | 2.0  |       |     | 2.0   |     | V     |

| Output Resistance            |           | f = 1.0 kHz                                                                                      |                                                    |     | 16   |       |     | 16    |     | mΩ    |

| Short Circuit Current TJ     |           | T <sub>J</sub> = 25°C                                                                            |                                                    |     | 450  |       |     | 450   |     | mA    |

| Peak Output Current TJ = 25  |           | Tj = 25°C                                                                                        |                                                    |     | 2.2  |       |     | 2.2   |     | A     |

| Average TC of Output Volt    |           | IOUT = 5.0                                                                                       | mA, $0^{\circ}C \le T_{J} \le 150^{\circ}C$ (7808) |     | -0.8 |       |     |       |     | mV/°C |

| Average TC of Output Voltage |           | $I_{OUT} = 5.0 \text{ mA}, 0^{\circ} \text{C} \le T_{J} \le 125^{\circ} \text{C} (7808\text{C})$ |                                                    |     |      |       |     | -0.8  |     | mV/°C |

#### ELECTRICAL CHARACTERISTICS

$V_{IN}$  = 19 V,  $I_{OUT}$  = 500 mA, -55°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (7812) 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C (7812C) unless otherwise specified

| PARAMETER                    |           |                                                                                                |                                         |      | 7812            |      |      |      | UNITS |       |

|------------------------------|-----------|------------------------------------------------------------------------------------------------|-----------------------------------------|------|-----------------|------|------|------|-------|-------|

|                              |           |                                                                                                | CONDITIONS                              | MIN  | TYP             | MAX  | MIN  | ТҮР  | МАХ   | 01115 |

| Output Voltage               |           | Тј = 25°С                                                                                      |                                         | 11.5 | 12              | 12.5 | 11.5 | 12   | 12.5  | v     |

| Line Regulation              |           | T <sub>.I</sub> = 25°C                                                                         | 14.5 V ≤ V <sub>IN</sub> ≤ 30 V         |      | 10              | 120  |      | 10   | 240   | mV    |

|                              |           | 1 200                                                                                          | 16 V ≤ V <sub>IN</sub> ≤ 22 V           |      | 3.0             | 60   |      | 3.0  | 120   | mV    |

| Load Regulation              |           | TJ = 25°C                                                                                      | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.5 A       |      | 12              | 120  |      | 12   | 240   | mV    |

|                              |           | 19 200                                                                                         | 250 mA ≤ I <sub>OUT</sub> ≤ 750 mA      |      | 4.0             | 60   |      | 4.0  | 120   | mV    |

|                              | ļ         | 15.5 V (14.                                                                                    | 5 V for 7812C) ≤ V <sub>IN</sub> ≤ 27 V |      |                 |      |      |      |       | ļ     |

| Output Voltage               |           | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                                                              |                                         | 11.4 |                 | 12.6 | 11.4 |      | 12.6  | V V   |

|                              |           | P ≤ 15 W                                                                                       |                                         |      |                 |      |      |      |       |       |

| Quiescent Current            |           | T <sub>J</sub> = 25°C                                                                          |                                         |      | 4.3             | 6.0  |      | 4.3  | 8.0   | mA    |

| Quiescent Current Change     | with line | 15 V (14.5 V for 7812C) $\leq$ V <sub>IN</sub> $\leq$ 30 V                                     |                                         |      |                 | 0.8  |      |      | 1.0   | mA    |

|                              | with load | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                                                              |                                         |      |                 | 0.5  |      |      | 0.5   | mA    |

| Output Noise Voltage         |           | $T_A = 25^{\circ}C$ , 10 Hz $\leq f \leq 100 \text{ kHz}$                                      |                                         |      | 75              |      |      | 75   |       | μΑ    |

| Long Term Stability          |           |                                                                                                |                                         |      |                 | 48   |      |      | 48    | mA    |

| Ripple Rejection             |           | f = 120 Hz, 15 V ≤ V <sub>IN</sub> ≤ 25 V                                                      |                                         |      | 71 <sup>.</sup> |      | 55   | 71   |       | dB    |

| Dropout Voltage              |           | I <sub>OUT</sub> = 1.0 A, T <sub>J</sub> = 25°C                                                |                                         |      | 2.0             |      |      | 2.0  |       | V     |

| Output Resistance            |           | f = 1.0 kHz                                                                                    |                                         |      | 18              |      | •    | 18   | •     | mΩ    |

| Short Circuit Current        |           | Tj = 25°С                                                                                      | :                                       |      | 350             |      |      | 350  |       | mA    |

| Peak Output Current          |           | т <sub>ј</sub> = 25°С                                                                          |                                         |      | 2.2             |      |      | 2.2  |       | A     |

| Augusta TO of Output Male    |           | IOUT = 5.0                                                                                     | mA, 0°C ≤ TJ ≤ 150°C (7812)             |      | -1.0            |      |      |      |       | mV/°C |

| Average TC of Output Voltage |           | $I_{OUT} = 5.0 \text{ mA}, 0^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C} (7812\text{C})$ |                                         |      | k               |      | ·    | -1.0 |       | mV/°C |

$V_{IN}$  = 23 V,  $I_{OUT}$  = 500 mA, -55°C < T<sub>J</sub> < 150°C (7815) 0°C < T<sub>J</sub> < 125°C (7815C) unless otherwise specified

| PAD AMETED                                  |                |                                                                                                      | CONDITIONS                                         |      | 7815 |       | 7815C |      |       |      |

|---------------------------------------------|----------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|------|-------|-------|------|-------|------|

| PARAMETER                                   |                | CONDITIONS                                                                                           |                                                    | MIN  | ΤΥΡ  | МАХ   | MIN   | түр  | MAX   |      |

| Output Voltage                              |                | Tj = 25°C                                                                                            |                                                    | 14.4 | 15   | 15.6  | 14.4  | 15   | 15.6  | V    |

| Line Deputation                             |                | $T_{\rm e} = 05^{\circ} O$                                                                           | 17.5 V ≤ V <sub>IN</sub> ≤ 30 V                    |      | 11   | 150   |       | 11   | 300   | mV   |

| Line Regulation                             |                | $T_{J} = 25^{\circ}C \qquad \frac{17.5 \sqrt{3} \sqrt{3} \sqrt{10}}{20 \sqrt{5} \sqrt{20} \sqrt{5}}$ |                                                    | ]    | 3.0  | 75    |       | 3.0  | 150   | mV   |

| Load Regulation                             |                | Тј = 25°С                                                                                            | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.5 A                  |      | 12   | 150   |       | 12   | 150   | mV   |

|                                             |                | 1J-25 C                                                                                              | 250 mA ≤ I <sub>OUT</sub> ≤ 750 mA                 |      | 4.0  | 75    |       | 4.0  | 75    | mV   |

|                                             |                | 18.5 V (17.                                                                                          | 5 V for 7815 C) ≤ V <sub>IN</sub> ≤ 30 V           |      |      | [     |       |      |       |      |

| Output Voltage                              | Output Voltage |                                                                                                      | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                  |      |      | 15.75 | 14.25 |      | 15.75 | V    |

|                                             |                | P ≤ 15 W                                                                                             |                                                    |      |      |       |       |      |       |      |

| Quiescent Current                           |                | Tj = 25°C                                                                                            | · ·                                                | · ·  | 4.4  | 6.0   |       | 4.4  | 8.0   | mA   |

| 0                                           | with line      | 18.5 V (17.5 V for 7815C) ≤ V <sub>IN</sub> ≤ 30 V                                                   |                                                    |      |      | 0.8   |       |      | 1.0   | mA   |

| Quiescent Current Change                    | with load      | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                                                                    |                                                    |      |      | 0.5   |       |      | 0.5   | mA   |

| Output Noise Voltage                        | •              | T <sub>A</sub> = 25°C, 10 Hz ≤ f ≤ 100 kHz                                                           |                                                    |      | 90   |       |       | 90   |       | μV   |

| Long Term Stability                         | -              |                                                                                                      |                                                    |      |      | 60    |       |      | 60    | mV   |

| Ripple Rejection                            |                | f = 120 Hz, 18.5 V ≤ V <sub>IN</sub> ≤ 28.5 V                                                        |                                                    | 60   | 70   |       | . 54  | 70   |       | dB   |

| Dropout Voltage                             |                | IOUT = 1.0 A, TJ = 25°C                                                                              |                                                    |      | 2.0  |       |       | 2.0  |       | V    |

| Output Resistance                           |                | f = 1.0 kHz                                                                                          |                                                    |      | 19   |       |       | 19   |       | mΩ   |

| Short Circuit Current T <sub>J</sub> = 25°C |                | Tj = 25°C                                                                                            | Гј = 25°С                                          |      | 230  |       |       | 230  |       | mA   |

| Peak Output Current                         |                | Тј = 25°С                                                                                            | · · · · · · · · · · · · · · · · · · ·              |      | 2.1  |       |       | 2.1  |       | А    |

|                                             |                | IOUT = 5.0                                                                                           | mA, $0^{\circ}C \le T_{J} \le 150^{\circ}C$ (7815) |      | -1.0 |       |       |      |       | mV/° |

| Average TC of Output Volta                  | age            | IOUT = 5.0                                                                                           | mA, 0°C ≤ T」 ≤ 125°C (7815C)                       |      |      |       |       | -1.0 |       | mV/° |

### ELECTRICAL CHARACTERISTICS

$V_{IN}$  = 27 V,  $I_{OUT}$  = 500 mA, -55°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (7818) 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C (7818C) unless otherwise specified

| PARAMETER                 |           |                                                        | CONDITIONS                                                |      | 7818 |      | 7818C |      |      | UNITS |

|---------------------------|-----------|--------------------------------------------------------|-----------------------------------------------------------|------|------|------|-------|------|------|-------|

| FANAMETER                 |           | conditions                                             |                                                           | MIN  | түр  | MAX  | MIN   | ТҮР  | MAX  | 01115 |

| Output Voltage            |           | Тј = 25°С                                              |                                                           | 17.3 | 18   | 18.7 | 17.3  | 18   | 18.7 | v     |

| Line Regulation           |           | $T_1 = 25^\circ C$                                     | $21 V \leq V_{IN} \leq 33 V$ $24 V \leq V_{IN} \leq 30 V$ |      | 15   | 180  |       | 15   | 360  | mV    |

|                           |           |                                                        |                                                           |      | 5.0  | 90   |       | 5.0  | 180  | mV    |

| Load Regulation           |           | $T_1 = 25^{\circ}C$                                    | 5.0 mA $\leq$ I <sub>OUT</sub> $\leq$ 1.5 A               |      | 12   | 180  |       | 12   | 360  | mV    |

|                           |           | - j = 25 C                                             | 250 mA ≤ I <sub>OUT</sub> ≤ 750 mA                        |      | 4.0  | 90   |       | 4.0  | 180  | mV    |

| Output Voltage            |           | 22 V (21 V                                             | for 7818C) $\leq$ V <sub>IN</sub> $\leq$ 33 V             |      |      |      |       |      |      |       |

|                           |           | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                      |                                                           | 17.1 |      | 18.9 | 17.1  |      | 18.9 | V V   |

|                           |           | P ≤ 15 W                                               |                                                           |      |      |      |       |      |      |       |

| Quiescent Current         |           | TJ = 25°C                                              |                                                           |      | 4.5  | 6.0  |       | 4.5  | 8.0  | mA    |

| Quiescent Current Change  | with line | 22 V (21 V for 7818 C) $\leq$ V $_{ m IN}$ $\leq$ 33 V |                                                           |      |      | 0.8  |       |      | 1.0  | mA    |

| Quiescent Current Change  | with load | 5.0 mA ≤ I <sub>OUT</sub> ≤ 1.0 A                      |                                                           |      |      | 0.5  |       |      | 0.5  | mA    |

| Output Noise Voltage      |           | $T_A = 25^{\circ}C$ , 10 Hz $\leq f \leq$ 100 kHz      |                                                           |      | 110  |      |       | 110  |      | μΑ    |

| Long Term Stability       |           |                                                        |                                                           |      |      | 72   |       |      | 72   | mV    |

| Ripple Rejection          | 1         | f = 120 Hz, 22 V ≤ V <sub>IN</sub> ≤ 32 V              |                                                           | 59   | 69   |      | 53    | 69   |      | dB    |

| Dropout Voltage           |           | IOUT = 1.0 A, TJ = 25°C                                |                                                           |      | 2.0  |      |       | 2.0  |      | V     |

| Output Resistance         |           | f = 1.0 kHz                                            |                                                           |      | 22   |      |       | 22   |      | mΩ    |

| Short Circuit Current     |           | TJ = 25°C                                              |                                                           |      | 200  |      |       | 200  |      | mA    |

| Peak Output Current       |           | T <sub>J</sub> = 25°C                                  |                                                           |      | 2.1  |      |       | 2.1  |      | A     |

| Average TC of Output Valt |           | IOUT = 5.0                                             | mA, 0°C ≤ TJ ≤ 150°C (7818)                               |      | -1.0 |      |       |      |      | mV/°C |

| Average TC of Output Volt | aye       | IOUT = 5.0                                             | mA, 0°C ≤ TJ ≤ 125°C (7818C)                              |      |      |      |       | -1.0 |      | mV/°C |

$V_{IN}$  = 33 V,  $I_{OUT}$  = 500 mA, --55° C  $\leq$  T<sub>J</sub>  $\leq$  150° C (7824) 0° C  $\leq$  T<sub>J</sub>  $\leq$  125° C (7824C) unless otherwise specified

| PARAMETER                                                    |              |                                                | CONDITIONS                          |      | 7824 |      | 7824C |      |      | UNITS |