# SECTION 2 SIGNAL/CONNECTION DESCRIPTION

| 2.1  | INTRODUCTION                               |

|------|--------------------------------------------|

| 2.2  | POWER                                      |

| 2.3  | GROUND                                     |

| 2.4  | CLOCK AND PHASE LOCK LOOP2-7               |

| 2.5  | INTERRUPT AND MODE CONTROL                 |

| 2.6  | EXPANSION PORT (PORT A) 2-11               |

| 2.7  | HOST INTERFACE (HI08)                      |

| 2.8  | SYNCHRONOUS SERIAL INTERFACE 0 (SSI0) 2-18 |

| 2.9  | SYNCHRONOUS SERIAL INTERFACE 1 (SSI1)2-21  |

| 2.10 | GENERAL PURPOSE I/O, GPIO                  |

| 2.11 | TRIPLE TIMER                               |

| 2.12 | JTAG/ONCE INTERFACE2-26                    |

2-2 MOTOROLA DSP56603UM/AD

### 2.1 INTRODUCTION

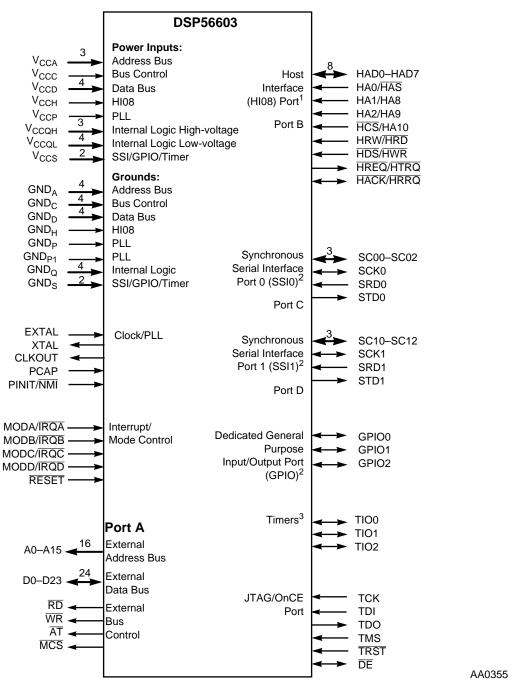

The input and output signals of the DSP56603 are organized into functional groups, as shown in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 2-2** through **Table 2-13**, each table row describes the signal or signals present on a pin.

The DSP56603 operates from a 3 V supply; however, some of the inputs can tolerate 5 V. A special notice for this feature is added to the signal descriptions of those inputs.

**Table 2-1** Functional Group Signal Allocations

| Functional Group                      | Number of<br>Signals | Detailed<br>Description |           |

|---------------------------------------|----------------------|-------------------------|-----------|

| Power (V <sub>CC</sub> )              |                      | 19                      | Table 2-2 |

| Ground (GND)                          |                      | 19                      | Table 2-3 |

| PLL and Clock Signals                 |                      | 5                       | Table 2-4 |

| Interrupt and Mode Control            |                      | 5                       | Table 2-5 |

| External Memory Port                  | Address Bus          | 16                      | Table 2-6 |

| (also referred to as Port A)          | 24                   |                         |           |

|                                       | Bus Control          | 4                       |           |

| Host Interface (HI08)                 | Port B (GPIO)        | 16                      | Table 2-8 |

| Synchronous Serial Interface 0 (SSI0) | Port C (GPIO)        | 6                       | Table 2-9 |

| Synchronous Serial Interface 1 (SSI1) | 6                    | Table 2-10              |           |

| General Purpose Input/Output (GPI     | 3                    | Table 2-11              |           |

| Triple Timer                          | 3                    | Table 2-12              |           |

| JTAG/On-Chip Emulation (OnCE) Po      | 6                    | Table 2-13              |           |

#### Introduction

Note: 1. The HI08 port supports a non-multiplexed or a multiplexed bus, single or double Data Strobe (DS), and single or double Host Request (HR) configurations. Since each these modes is configured independently, any combination of these modes is possible. The HI08 signals can also be configured alternately as GPIO signals (PB0–PB15).

- 2. The SSI0 and SSI1 signals can be configured alternatively as Port C GPIO signals (PC0–PC5) and Port D GPIO signals (PD0–PD5), respectively.

- 3. TIO0-TIO2 can be configured alternatively as GPIO signals.

Figure 2-1 DSP56603 Signals Identified by Functional Group

# 2.2 POWER

Table 2-2

Power Inputs

| Signal Name (number of pins) | Signal Description                                                                                                                                                                                                                                                                           |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCA</sub> (3)         | <b>Address Bus Power</b> — $V_{CCA}$ is an isolated power for sections of address bus I/O drivers, and must be tied externally to all other chip power inputs, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                               |

| V <sub>CCC</sub> (1)         | <b>Bus Control Power</b> — $V_{CCC}$ is an isolated power for the bus control I/O drivers, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                       |

| V <sub>CCD</sub> (4)         | <b>Data Bus Power</b> — $V_{CCD}$ is an isolated power for sections of data bus I/O drivers, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                     |

| V <sub>CCH</sub> (1)         | <b>Host Power</b> — $V_{CCH}$ is an isolated power for the HI08 logic, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                                           |

| V <sub>CCP</sub> (1)         | <b>PLL Power</b> — $V_{CCP}$ is $V_{CC}$ dedicated for Phase Lock Loop (PLL) use. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the $V_{CC}$ power rail.                                                                     |

| V <sub>CCQH</sub> (3)        | <b>Quiet Power High Voltage</b> — $V_{CCQH}$ is an isolated power for the CPU logic, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                             |

|                              | The voltage supplied to these inputs should equal the voltage supplied to I/O power inputs $V_{CCA}$ , $V_{CCC}$ , $V_{CCD}$ , $V_{CCH}$ , and $V_{CCS}$ .                                                                                                                                   |

| V <sub>CCQL</sub> (4)        | <b>Quiet Power Low Voltage—</b> V <sub>CCQL</sub> is an isolated power for the CPU logic, and should not be tied to the other chip power inputs. The user must provide adequate external decoupling capacitors.                                                                              |

|                              | The voltage supplied to these inputs should be equal to or lower than the voltage supplied to the $V_{CCQH}$ inputs. The user can lower the voltage supplied to $V_{CCQL}$ as long as it meets the MIPS requirements of the application, thus lowering the chip's overall power consumption. |

## Ground

Table 2-2

Power Inputs (Continued)

| Signal Name<br>(number of pins) | Signal Description                                                                                                                                                                                                                                                   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCS</sub> (2)            | <b>SSI, GPIO, and Timers Power</b> — $V_{CCS}$ is a isolated power for the SSIs, GPIO, and Timers logic, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors. |

# 2.3 GROUND

Table 2-3 Grounds

| UCTOF        | Signal Name (number of pins) | Signal Description                                                                                                                                                                                                                                                          |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEMICOND     | GND <sub>A</sub> (4)         | <b>Address Bus Ground</b> — $GND_A$ is an isolated ground for sections of address bus I/O drivers, and must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                                         |

| FREESCALE    | GND <sub>C</sub> (2)         | <b>Bus Control Ground</b> — $GND_C$ is an isolated ground for the bus control I/O drivers, and must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                                                 |

| RCHIVED BY F | GND <sub>D</sub> (4)         | <b>Data Bus Ground</b> — $GND_D$ is an isolated ground for sections of the data bus I/O drivers, and must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                                           |

| ARC          | GND <sub>H</sub> (1)         | <b>Host Ground</b> —GND $_{\rm H}$ is an isolated ground for the HI08 I/O drivers, and must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                                                         |

|              | GND <sub>P</sub> (1)         | <b>PLL Ground</b> —GND <sub>P</sub> is ground dedicated for PLL use, and should be provided with an extremely low impedance path to ground. $V_{CCP}$ should be bypassed to GND <sub>P</sub> with a 0.1 $\mu F$ capacitor located as close as possible to the chip package. |

|              | GND <sub>P1</sub> (1)        | <b>PLL Ground 1</b> —GND $_{P1}$ is ground dedicated for PLL use, and should be provided with an extremely low impedance path to ground.                                                                                                                                    |

2-6 DSP56603UM/AD MOTOROLA

## **Clock and Phase Lock Loop**

Table 2-3

Grounds (Continued)

| Signal Name<br>(number of pins) | Signal Description                                                                                                                                                                                                              |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND <sub>Q</sub> (4)            | <b>Quiet Ground</b> — $GND_Q$ is an isolated ground for the CPU logic, and must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.                         |

| GND <sub>S</sub> (2)            | SSIs, GPIO, and Timers Ground—GNDS is an isolated ground for the SSIs, GPIO, and Timers logic, and must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. |

## 2.4 CLOCK AND PHASE LOCK LOOP

Table 2-4 Clock and PLL Signals

| Signal<br>Name | Signal<br>Type | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                               |

|----------------|----------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL          | Input          | Input                    | <b>External Clock/Crystal Input</b> —EXTAL interfaces the internal crystal oscillator input to an external crystal or an external clock.                                                                                                                         |

| XTAL           | Output         | Chip-<br>driven          | Crystal Output—XTAL connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected.                                                                                                                |

| PCAP           | Input          | Indeter-<br>minate       | <b>PLL Capacitor</b> —PCAP is an input connecting an off-chip capacitor to the PLL filter. Connect one capacitor terminal to PCAP and the other terminal to V <sub>CCP</sub> .                                                                                   |

|                |                |                          | If the PLL is not used, PCAP may be tied to $V_{CC}$ , GND, or left floating.                                                                                                                                                                                    |

| CLKOUT         | Output         | Chip-<br>driven          | Clock Output—CLKOUT provides an output clock synchronized to the internal core clock phase. When the PLL is enabled, the Division Factor (DF) equals one, and the Multiplication Factor (MF) is less than or equal to four, CLKOUT is also synchronized to EXTAL |

|                |                |                          | When the PLL is disabled, the CLKOUT frequency is half the frequency of EXTAL.                                                                                                                                                                                   |

# Interrupt And Mode Control

Table 2-4 Clock and PLL Signals (Continued)

|          | Signal<br>Name | Signal<br>Type | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                       |

|----------|----------------|----------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •        | PINIT/<br>NMI  | Input          | Input                    | PLL Initial/Non-Maskable Interrupt—During assertion of RESET, the value of PINIT/NMI is written into the PLL Enable (PEN) bit of the PLL control register, determining whether the PLL is enabled or disabled.                           |

| NC. ZOOS |                |                |                          | After RESET deassertion and during normal instruction processing, the PINIT/NMI Schmitt-trigger input is a negative-edge-triggered Non-Maskable Interrupt (NMI) request internally synchronized to CLKOUT.  This input can tolerate 5 V. |

# 2.5 INTERRUPT AND MODE CONTROL

Table 2-5

Interrupt and Mode Control Signals

| Signa<br>Name |       | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET         | Input | Input                    | Reset—RESET is an active low, Schmitt-trigger input. Deassertion of the RESET signal is internally synchronized to the clock out (CLKOUT). When asserted, the chip is placed in the reset state and the internal phase generator is reset. The Schmitt-trigger input allows a slowly rising input, such as a capacitor charging, to reliably reset the chip. If the RESET signal is deasserted synchronous to CLKOUT, exact start-up timing is guaranteed, allowing multiple processors to start up synchronously and operate together. When the RESET signal is deasserted, the initial chip operating mode is latched from the MODA, MODB, MODC, and MODD inputs.  This input can tolerate 5 V. |

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

# Interrupt And Mode Control

Table 2-5

Interrupt and Mode Control Signals (Continued)

| Signal<br>Name | Signal<br>Type | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODA/<br>IRQA  | Input          | Input                    | Mode Select A/External Interrupt Request A—MODA/IRQA is an active low Schmitt-trigger input, internally synchronized to CLKOUT. MODA/IRQA selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of sixteen initial chip operating modes latched into the Operating Mode Register (OMR) when the RESET signal is deasserted. If IRQA is asserted synchronous to CLKOUT, multiple processors can be resynchronized using the WAIT instruction and asserting IRQA to exit the Wait state. If the processor is in the Stop standby state and IRQA is asserted, the processor exits the Stop state. |

| MODB/<br>IRQB  | Input          | Input                    | This input can tolerate 5 V.  Mode Select B/External Interrupt Request B—MODB/IRQB is an active low Schmitt-trigger input, internally synchronized to CLKOUT. MODB/IRQB selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of sixteen initial chip operating modes latched into the OMR register when the RESET signal is deasserted. If IRQB is asserted synchronous to CLKOUT, multiple processors can be resynchronized using the WAIT instruction and asserting IRQB to exit the Wait state.  This input can tolerate 5 V.                                                              |

# **Interrupt And Mode Control**

Table 2-5

Interrupt and Mode Control Signals (Continued)

| internally synchronized to CLKOUT. MODC/IRQC select the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select or of sixteen initial chip operating modes latched into the ON register when the RESET signal is deasserted. If IRQC is asserted synchronous to CLKOUT, multiple processors can be resynchronized using the WAIT instruction and asserting IRQC to exit the Wait state.  This input can tolerate 5 V.  MODD/IRQD is an active low Schmitt-trigger input, internally synchronized to CLKOUT. MODD/IRQD select the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select or of sixteen initial chip operating modes, latched into OMR when the RESET signal is deasserted. If IRQD is asserted synchronous to CLKOUT, multiple processors can be | Signal<br>Name | Signal<br>Type | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select or of sixteen initial chip operating modes, latched into OMR when the RESET signal is deasserted. If IRQD is asserted synchronous to CLKOUT, multiple processors can be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IRQC Source    | Input          | Input                    | C—MODC/IRQCn is an active low Schmitt-trigger input, internally synchronized to CLKOUT. MODC/IRQC selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of sixteen initial chip operating modes latched into the OMR register when the RESET signal is deasserted. If IRQC is asserted synchronous to CLKOUT, multiple processors can be resynchronized using the WAIT instruction and asserting IRQC to exit the Wait state.                              |

| This input can tolerate 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | Input          | Input                    | Mode Select D/External Interrupt Request D MODD/IRQD is an active low Schmitt-trigger input, internally synchronized to CLKOUT. MODD/IRQD selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of sixteen initial chip operating modes, latched into OMR when the RESET signal is deasserted. If IRQD is asserted synchronous to CLKOUT, multiple processors can be re-synchronized using the WAIT instruction and asserting IRQD to exit the Wait state. |

2-10 DSP56603UM/AD MOTOROLA

# 2.6 EXPANSION PORT (PORT A)

Table 2-6 Expansion Port, Port A Signals

| Signal<br>Name | Signal<br>Type   | State<br>During<br>Reset                                      | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0–A15         | Output           | Set<br>according<br>to chip<br>operating<br>mode <sup>1</sup> | Address Bus—These active high outputs specify the address for external program memory accesses. To minimize power dissipation, A0–A15 do not change state when external memory spaces are not being accessed.                                                                                                                                                                                                                         |

| D0-D23         | Input/<br>Output | Tri-stated                                                    | <b>Data Bus</b> —These active high, bidirectional input/outputs provide the bidirectional data bus for external program memory accesses. D0–D23 are tri-stated when no external bus activity occurs, and during hardware reset.                                                                                                                                                                                                       |

| MCS            | Output           | Pulled<br>high<br>internally                                  | Memory Chip Select—This signal is an active low output, and is asserted when an external memory access occurs.  MCS is deasserted during hardware reset.                                                                                                                                                                                                                                                                              |

| RD             | Output           | Pulled<br>high<br>internally                                  | <b>Read Enable</b> —This signal is an active low output. $\overline{RD}$ is asserted to read external memory on the data bus (D0–D23). $\overline{RD}$ is deasserted during hardware reset.                                                                                                                                                                                                                                           |

| WR             | Output           | Pulled<br>high<br>internally                                  | Write Enable—This signal is an active low output. $\overline{WR}$ is asserted to write external memory on the data bus (D0–D23). $\overline{WR}$ is deasserted during hardware reset.                                                                                                                                                                                                                                                 |

| ĀT             | Output           | Pulled<br>high<br>internally                                  | <b>Address Tracing</b> —This signal is an active low output. $\overline{AT}$ is asserted (for half of a clock cycle) whenever a new address is driven on the address bus (A0–A15) in the Program Address Tracing mode. The new address is either a reflection of internal fetch or internal program space move instruction or an external address driven for an external access. $\overline{AT}$ is deasserted during hardware reset. |

Note: 1. The A0–A15 pins are asserted according to the selected chip operating mode, as determined by the values on the MODA–MODD pins. Each mode has a different reset address. A0–A15 are latched to the value of that reset address minus 1. For example, if the reset address for a selected operating mode is \$0800, the address bus is asserted to \$07FF.

**Host Interface (HI08)**

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC.

# 2.7 HOST INTERFACE (HI08)

The HI08 provides a fast 8-bit port that can be connected directly to the host bus. The HI08 supports a variety of standard buses, and can be directly connected to a number of industry standard microcomputers, microprocessors, DSPs, and DMA hardware.

### 2.7.1 Host Port Usage Considerations

Careful synchronization is required when reading multiple-bit registers that are written by another asynchronous system. This is a common problem when two asynchronous systems are connected (as they are in the Host port). The considerations for proper operation are discussed in the following table:

Action Description Asynchronous read of When reading the receive byte registers, Receive High (RXH) register or Receive Low (RXL) register, the Host Interface receive byte registers programmer should use interrupts or poll the Receive Register Data Full (RXDF) flag, which indicates that data is available. This assures that the data in the receive byte registers is valid. Asynchronous write to The host interface programmer should not write to the transmit transmit byte registers byte registers, Transmit High (TXH) register or Transmit Low (TXL) register, unless the Transmit Register Data Empty (TXDE) bit is set, which indicates that the transmit byte registers are empty. This guarantees that the transmit byte registers transfer valid data to the Host Receive (HRX) register. Asynchronous write to The Host Interface programmer should change the Host Vector (HV) register only when the Host Command (HC) bit is clear. host vector This guarantees that the DSP interrupt control logic receives a stable vector.

**Table 2-7** Host Port Usage Considerations

# 2.7.2 Host Port Configuration

The signal functions associated with the HI08 vary according to the configuration determined by the HI08 Port Control Register (HPCR). Refer to **Section 7**, **Host Interface (HI08)**, for detailed descriptions of this and the other configuration registers used with the HI08.

2-12 DSP56603UM/AD MOTOROLA

# Table 2-8 Host Interface Signals

| Signal Name   | Signal Type        | State<br>During<br>Reset        | Signal Description                                                                                                                                                                                                                           |

|---------------|--------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HAD0-<br>HAD7 | Bi-directional     | Discon-<br>nected<br>internally | Host Data Bus—When the HI08 is programmed to interface a non-multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the Host Data bidirectional tri-state bus (HD0–HD7).                                       |

|               | Bi-directional     |                                 | Host Address and Data Bus—When the HI08 is programmed to interface a multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the Host Address/Data multiplexed bidirectional tri-state bus (HAD0–HAD7).         |

|               | Input or<br>Output |                                 | <b>Port B 0–7</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register (HPCR), these signals are individually programmed as inputs or outputs through the HI08 Data Direction Register (HDDR).                        |

|               |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                   |

| HA0/HAS       | Input              | Discon-<br>nected<br>internally | Host Address Input 0—When the HI08 is programmed to interface a non-multiplexed host bus and the HI function is selected, this signal is line 0 of the Host Address input bus (HA0).                                                         |

|               | Input              |                                 | Host Address Strobe—When the HI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is the Host Address Strobe (HAS) Schmitt-trigger input. The polarity of the address strobe is programmable. |

|               | Input or<br>Output |                                 | Port B 8—When the HI08 is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                                                                                |

|               |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                   |

# Host Interface (HI08)

Table 2-8 Host Interface Signals (Continued)

| Signal Name | Signal Type        | State<br>During<br>Reset        | Signal Description                                                                                                                                                                     |

|-------------|--------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HA1/HA8     | Input              | Discon-<br>nected<br>internally | Host Address Input 1—When the HI08 is programmed to interface a non-multiplexed host bus and the HI function is selected, this signal is line one of the Host Address input bus (HA1). |

| 2005        | Input              |                                 | <b>Host Address 8</b> —When the HI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is line eight of the input Host Address bus (HA8). |

| JCTOR, INC. | Input or<br>Output |                                 | <b>Port B 9</b> —When the HI08 is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                  |

| MICOND      |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                             |

| OHA2/HA9    | Input              | Discon-<br>nected<br>internally | Host Address Input 2—When the HI08 is programmed to interface a non-multiplexed host bus and the HI function is selected, this signal is line two of the Host Address input bus (HA2). |

| ÆÐ BY FRE   | Input              |                                 | <b>Host Address 9—</b> When the HI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is line nine of the input Host Address bus (HA9).  |

| ARCHII      | Input or<br>Output |                                 | Port B 10—When the HI08 is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                         |

|             |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                             |

2-14 DSP56603UM/AD MOTOROLA

# Table 2-8 Host Interface Signals (Continued)

| Signal Name | Signal Type        | State<br>During<br>Reset        | Signal Description                                                                                                                                                                                                                           |

|-------------|--------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRW/HRD     | Input              | Discon-<br>nected<br>internally | Host Read/Write—When the HI08 is programmed to interface a single-data-strobe host bus and the HI function is selected, this signal is the Read/Write input (HRW).                                                                           |

|             | Input              |                                 | Host Read Data—When the HI08 is programmed to interface a double-data-strobe host bus and the HI function is selected, this signal is the Read Data strobe Schmitt-trigger input (HRD). The polarity of the data strobe is programmable.     |

|             | Input or<br>Output |                                 | <b>Port B 11</b> —When the HI08 is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                                                                       |

|             |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                   |

| HDS/HWR     | Input              | Discon-<br>nected<br>internally | Host Data Strobe—When the HI08 is programmed to interface a single-data-strobe host bus and the HI function is selected, this signal is the Host Data Strobe Schmitt-trigger input (HDS). The polarity of the data strobe is programmable.   |

|             | Input              |                                 | Host Write Enable—When the HI08 is programmed to interface a double-data-strobe host bus and the HI function is selected, this signal is the Write Data Strobe Schmitt-trigger input (HWR). The polarity of the data strobe is programmable. |

|             | Input or<br>Output |                                 | Port B 12—When the HI08 is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                                                                               |

|             |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                   |

# Host Interface (HI08)

Table 2-8 Host Interface Signals (Continued)

| Signal Name                                      | Signal Type        | State<br>During<br>Reset        | Signal Description                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------|--------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCS/HA10                                         | Input              | Discon-<br>nected<br>internally | Host Chip Select—When the HI08 is programmed to interface a non-multiplexed host bus and the HI function is selected, this signal is the Host Chip Select input (HCS). The polarity of the chip select is programmable.                                                                                       |

| IC. 2005                                         | Input              |                                 | <b>Host Address 10—</b> When the HI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is line 10 of the input Host Address bus (HA10).                                                                                                                         |

| EMICONDUCTOR, INC. 200                           | Input or<br>Output |                                 | <b>Port B 13</b> —When the HI08 is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                                                                                                                                        |

| SEMICOL                                          |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                                    |

| HREQ/HTRQ  S  S  H  H  H  H  H  H  H  H  H  H  H | Output             | Discon-<br>nected<br>internally | Host Request—When the HI08 is programmed to interface a single host request host bus and the HI function is selected, this signal is the Host Request output (HREQ). The polarity of the host request is programmable. The host request can be programmed as a driven or open-drain output.                   |

| ARCHIVED                                         | Output             |                                 | Transmit Host Request—When the HI08 is programmed to interface a double host request host bus and the HI function is selected, this signal is the Transmit Host Request output (HTRQ). The polarity of the host request is programmable. The host request can be programmed as a driven or open-drain output. |

|                                                  | Input or<br>Output |                                 | <b>Port B 14</b> —When the HI08 is programmed to interface a multiplexed host bus and the signal is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                                                                       |

|                                                  |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                                    |

2-16 DSP56603UM/AD MOTOROLA

# Table 2-8 Host Interface Signals (Continued)

| Signal Name   | Signal Type        | State<br>During<br>Reset        | Signal Description                                                                                                                                                                                                                                                                                          |

|---------------|--------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HACK/<br>HRRQ | Input              | Discon-<br>nected<br>internally | Host Acknowledge —When the HI08 is programmed to interface a single host request host bus and the HI function is selected, this signal is the Host Acknowledge Schmitt-trigger input (HACK). The polarity of the host acknowledge is programmable.                                                          |

|               | Output             |                                 | Receive Host Request—When the HI08 is programmed to interface a double host request host bus and the HI function is selected, this signal is the Receive Host Request output (HRRQ). The polarity of the host request is programmable. The host request can be programmed as a driven or open-drain output. |

|               | Input or<br>Output |                                 | <b>Port B 15</b> —When the HI08 is configured as GPIO through the HPCR, this signal is individually programmed as an input or output through the HDDR.                                                                                                                                                      |

|               |                    |                                 | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                                  |

Synchronous Serial Interface 0 (SSI0)

# 2.8 SYNCHRONOUS SERIAL INTERFACE 0 (SSI0)

Two identical Synchronous Serial Interfaces (SSI0 and SSI1) provide a full-duplex serial port for serial communication with a variety of serial devices including one or more industry-standard codecs, other DSPs, or microprocessors. When either SSI port is disabled, it can be used for General Purpose I/O (GPIO).

**Table 2-9** Synchronous Serial Interface 0 (SSI0)

| 05                    | Signal<br>Name | Signal Type        | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                    |

|-----------------------|----------------|--------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTOR, INC. 2005       | SC00           | Input or<br>Output | Input                    | <b>Serial Control Signal 0</b> —The function of SC00 is determined by the selection of either Synchronous or Asynchronous mode. For Asynchronous mode, this signal is used for the receive clock I/O (Schmitt-trigger input). For Synchronous mode, this signal is used for or for Serial I/O Flag 0. |

| SEMICONDUCTOR         |                | Input or<br>Output |                          | <b>Port C 0</b> —When configured as PC0, signal direction is controlled through the SSI0 Port Direction Control Register (PRRC). The signal can be configured as SSI signal SC00 through the SSI0 Port Control Register (PCRC).                                                                       |

| CALE                  |                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                            |

| ARCHIVED BY FREESCALE | SC01           | Input or<br>Output | Input                    | <b>Serial Control Signal 1—</b> The function of SC00 is determined by the selection of either Synchronous or Asynchronous mode. For Asynchronous mode, this signal is used for the receive clock I/O (Schmitt-trigger input). For Synchronous mode, this signal is used for Serial I/O Flag 1.        |

|                       |                | Input or<br>Output |                          | <b>Port C 1</b> —When configured as PC1, signal direction is controlled through the PRRC register. The signal can be configured as an SSI signal SC01 through the PCRC register.                                                                                                                      |

|                       |                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                            |

2-18 DSP56603UM/AD MOTOROLA

# Synchronous Serial Interface 0 (SSI0)

Table 2-9

Synchronous Serial Interface 0 (SSI0) (Continued)

| Signal<br>Name | Signal Type        | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC02           | Input or<br>Output | Input                    | Serial Control Signal 2—SC02 is the frame sync for both the transmitter and receiver in Synchronous mode, and for the transmitter only in Asynchronous mode. When configured as an output, this signal is the internally generated frame sync signal. When configured as an input, this signal receives an external frame sync signal for the transmitter (and the receiver in synchronous operation). |

|                | Input or<br>Output |                          | <b>Port C 2</b> —When configured as PC2, signal direction is controlled through the PRRC register. The signal can be configured as an SSI signal SC02 through the PCRC register.                                                                                                                                                                                                                       |

|                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                                                                                                                             |

| SCK0           | Input or<br>Output | Input                    | <b>Serial Clock</b> —SCK0 is a bidirectional Schmitt-trigger input signal providing the serial bit rate clock for the SSI interface. The SCK0 is a clock input or output used by both the transmitter and receiver in Synchronous modes, or by the transmitter in Asynchronous modes.                                                                                                                  |

|                |                    |                          | Although an external serial clock can be independent of and asynchronous to the DSP system clock, it must exceed the minimum clock cycle time of 6T (i.e., the system clock frequency must be at least three times the external SSI clock frequency). The SSI needs at least three DSP phases inside each half of the serial clock.                                                                    |

|                | Input or<br>Output |                          | <b>Port C 3</b> —When configured as PC3, signal direction is controlled through the PRRC register. The signal can be configured as an SSI signal SCK0 through the PCRC register.                                                                                                                                                                                                                       |

|                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                                                                                                                             |

Table 2-9

Synchronous Serial Interface 0 (SSI0) (Continued)

Synchronous Serial Interface 0 (SSI0)

| Signa<br>Name | Signal Lyne        | State<br>During<br>Reset | Signal Description                                                                                                                                                                |

|---------------|--------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRD0          | Input              | Input                    | <b>Serial Receive Data</b> —SRD0 receives serial data and transfers the data to the SSI receive shift register. SRD0 is an input when data is being received.                     |

|               | Input or<br>Output |                          | <b>Port C 4</b> —When configured as PC4, signal directions is controlled through the PRRC register. The signal can be configured as an SSI signal SRD0 through the PCRC register. |

| 5. 2005       |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                        |

| STD0          | Output             | Input                    | <b>Serial Transmit Data</b> —STD0 is used for transmitting data from the serial transmit shift register. STD0 is an output when data is being transmitted.                        |

| MICONDO       | Input or<br>Output |                          | <b>Port C 5</b> —When configured as PC5, signal directions is controlled through the PRRC register. The signal can be configured as an SSI signal STD0 through the PCRC register. |

| T<br>D<br>D   |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                        |

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

# 2.9 SYNCHRONOUS SERIAL INTERFACE 1 (SSI1)

Table 2-10

Synchronous Serial Interface 1 (SSI1)

| Signal<br>Name | Signal Type        | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                    |

|----------------|--------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC10           | Input or<br>Output | Input                    | <b>Serial Control Signal 0</b> —The function of SC10 is determined by the selection of either Synchronous or Asynchronous mode. For Asynchronous mode, this signal is used for the receive clock I/O (Schmitt-trigger input). For Synchronous mode, this signal is used for or for Serial I/O Flag 0. |

|                | Input or<br>Output |                          | <b>Port D 0</b> —When configured as PD0, signal direction is controlled through the SSI1 Port Direction Control Register (PRRD). The signal can be configured as SSI signal SC10 through the SSI1 Port Control Register (PCRD).                                                                       |

|                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                            |

| SC11           | Input or<br>Output | Input                    | <b>Serial Control Signal 1</b> —The function of SC11 is determined by the selection of either Synchronous or Asynchronous mode. For Asynchronous mode, this signal is used for the receive clock I/O (Schmitt-trigger input). For Synchronous mode, this signal is used for Serial I/O Flag 1.        |

|                | Input or<br>Output |                          | <b>Port D 1</b> —When configured as PD1, signal direction is controlled through the PRRD register. The signal can be configured as an SSI signal SC11 through the PCRD register.                                                                                                                      |

|                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                            |

Synchronous Serial Interface 1 (SSI1)

# Table 2-10 Synchronous Serial Interface 1 (SSI1) (Continued)

|                                                | Signal<br>Name | Signal Type        | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------|--------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | SC12           | Input or<br>Output | Input                    | Serial Control Signal 2—SC12 is used for frame sync I/O. SC12 is the frame sync for both the transmitter and receiver in Synchronous mode, and for the transmitter only in Asynchronous mode. When configured as an output, this signal is the internally generated frame sync signal. When configured as an input, this signal receives an external frame sync signal for the transmitter (and the receiver in synchronous operation). |

| <b>DR, INC. 20</b>                             |                | Input or<br>Output |                          | <b>Port D 2</b> —When configured as PD2, signal direction is controlled through the PRRD register. The signal can be configured as an SSI signal SC12 through the PCRD register.                                                                                                                                                                                                                                                        |

| DUCTO                                          |                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                                                                                                                                                              |

| ALE SEMICON                                    | SCK1           | Input or<br>Output | Input                    | <b>Serial Clock</b> —SCK1 is a bidirectional Schmitt-trigger input signal providing the serial bit rate clock for the SSI interface. The SCK1 is a clock input or output used by both the transmitter and receiver in Synchronous modes, or by the transmitter in Asynchronous modes.                                                                                                                                                   |

| ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 |                |                    |                          | Although an external serial clock can be independent of and asynchronous to the DSP system clock, it must exceed the minimum clock cycle time of 6T (i.e., the system clock frequency must be at least three times the external SSI clock frequency). The SSI needs at least three DSP phases inside each half of the serial clock.                                                                                                     |

| ARCHI                                          |                | Input or<br>Output |                          | <b>Port D 3</b> —When configured as PD3, signal direction is controlled through the PRRD register. The signal can be configured as an SSI signal SCK1 through the PCRD register.                                                                                                                                                                                                                                                        |

|                                                |                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                                                                                                                                                                              |

2-22 **MOTOROLA** DSP56603UM/AD

# Synchronous Serial Interface 1 (SSI1)

Table 2-10

Synchronous Serial Interface 1 (SSI1) (Continued)

| Signal<br>Name | Signal Type        | State<br>During<br>Reset | Signal Description                                                                                                                                                               |

|----------------|--------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRD1           | Input              | Input                    | <b>Serial Receive Data</b> —SRD1 receives serial data and transfers the data to the SSI Receive Shift Register.                                                                  |

|                | Input or<br>Output |                          | <b>Port D 4</b> —When configured as PD4, signal direction is controlled through the PRRD register. The signal can be configured as an SSI signal SRD1 through the PCRD register. |

|                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                       |

| STD1           | Input              | Input                    | <b>Serial Transmit Data</b> —STD1 is used for transmitting data from the SSI Transmit Shift Register.                                                                            |

|                | Input or<br>Output |                          | <b>Port D 5</b> —When configured as PD5, signal direction is controlled through the PRRD register. The signal can be configured as an SSI signal STD1 through the PCRD register. |

|                |                    |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                       |

General Purpose I/O, GPIO

#### 2.10 **GENERAL PURPOSE I/O, GPIO**

Three dedicated General Purpose Input/Output (GPIO) signals are provided on the DSP56603. Each is reconfigurable as input, output, or tri-state. These signals are exclusively defined as GPIO, and do not offer additional functionality.

Table 2-11 General Purpose I/O (GPIO)

|                  | Signal<br>Name | Signal<br>Type     | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                     |

|------------------|----------------|--------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UCTOR, INC. 2005 | GPIO0          | Input or<br>Output | Input                    | General Purpose I/O 0—When a GPIO signal is used as input, the logic state is reflected to an internal register and can be read by the software. When a GPIO signal is used as output, the logic state is controlled by the software.  This input can tolerate 5 V. This pin is electrically disconnected internally during Stop mode. |

| SCALE SEMICONDU  | GPIO1          | Input or<br>Output | Input                    | General Purpose I/O 1—When a GPIO signal is used as input, the logic state is reflected to an internal register and can be read by the software. When a GPIO signal is used as output, the logic state is controlled by the software.  This input can tolerate 5 V. This pin is electrically disconnected internally during Stop mode. |

| RCHIVED BY FREE  | GPIO2          | Input or<br>Output | Input                    | General Purpose I/O 2—When a GPIO signal is used as input, the logic state is reflected to an internal register and can be read by the software. When a GPIO signal is used as output, the logic state is controlled by the software.  This input can tolerate 5 V. This pin is electrically disconnected internally during Stop mode. |

2-24 DSP56603UM/AD **MOTOROLA**

## 2.11 TRIPLE TIMER

Three identical and independent timers are implemented. The three timers can use internal or external clocking and can interrupt the DSP after a specified number of events (clocks), or can signal an external device after counting a specific number of internal events. When a timer port is disabled, it can be used for General Purpose I/O (GPIO).

**Table 2-12** Triple Timer Signals

| Signal<br>Name | Signal<br>Type        | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                       |

|----------------|-----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIO0           | Input<br>or<br>Output | GPIO<br>Input            | Timer 0 Schmitt-Trigger Input/Output —When TIO0 is used as an input, the timer module functions as an external event counter or measures external pulse width or signal period. When TIO0 is used as an output, the timer module functions as a timer and TIO0 provides the timer pulse. |

|                | Input<br>or           |                          | When TIO0 is not used by the timer module, it can be used for GPIO.                                                                                                                                                                                                                      |

|                | Output                |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                               |

| TIO1           | Input<br>or<br>Output | GPIO<br>Input            | Timer 1 Schmitt-Trigger Input/Output —When TIO1 is used as an input, the timer module functions as an external event counter or measures external pulse width or signal period. When TIO1 is used as an output, the timer module functions as a timer and TIO1 provides the timer pulse. |

|                | Input<br>or           |                          | When TIO1 is not used by the timer module, it can be used for GPIO.                                                                                                                                                                                                                      |

|                | Output                |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                               |

| TIO2           | Input<br>or<br>Output | GPIO<br>Input            | Timer 2 Schmitt-Trigger Input/Output —When TIO2 is used as an input, the timer module functions as an external event counter or measures external pulse width or signal period. When TIO2 is used as an output, the timer module functions as a timer and TIO2 provides the timer pulse. |

|                | Input<br>or           |                          | When TIO2 is not used by the timer module, it can be used for GPIO.                                                                                                                                                                                                                      |

|                | Output                |                          | When configured as an input, this pin can tolerate 5 V. This pin is electrically disconnected internally during Stop mode.                                                                                                                                                               |

# 2.12 JTAG/ONCE INTERFACE

Table 2-13 JTAG Interface / On-Chip Emulator Interface (OnCE) Signals

|               | Signal<br>Name | Signal Type    | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                            |

|---------------|----------------|----------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|