**Document Number: AN5349**

Rev. 0.1. 03/2019

# S32V234 Hardware Design Guide

#### 1. Introduction

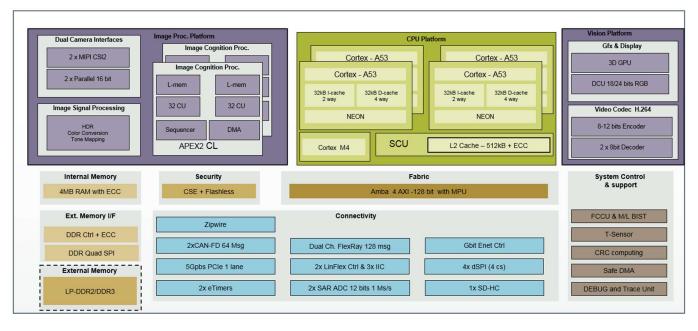

S32V234 is a high-performance automotive processor designed to support computationally intensive sensor fusion and vision applications that require automotive safety levels, consisting of up to four ARM® Cortex-A53®, one Cortex-M4®, dedicated modules and processors for acceleration of image vision processing tasks. The device architecture is developed with scalability in mind.

It enables users to leverage leading edge Camera Vision modules like APEX2, ISP, GPU and others.

This application note illustrates the S32V234 power supply options and details the external circuitry required for power supplies, oscillator connections, and supply decoupling pins. It also discusses configuration options for clock, reset, ADC modules, MIPI-CSI2 and Display interfaces, as well as recommended debug and peripheral communication connections and other major external hardware required for the device.

Please note that information from the S32V234 Reference Manual, Data Sheet, and/or Errata report may be repeated in this application note for the convenience of the reader. The Reference Manual, Data Sheet and Errata report are the official specifications for S32V234 and should be reviewed

#### **Contents**

| Introdu | action                                                                                                                       | 1                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|         |                                                                                                                              |                                                                  |

| 2.1.    |                                                                                                                              |                                                                  |

| S32V2   |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

|         |                                                                                                                              |                                                                  |

| 6.1.    |                                                                                                                              |                                                                  |

| DDR o   | connection information                                                                                                       | 17                                                               |

| 7.1.    | Resources for DDR signal routing recommer                                                                                    | dations17                                                        |

| PCI Ex  | xpress interface recommendations                                                                                             | 18                                                               |

| 8.1.    | PCI Express general routing guidelines                                                                                       | 18                                                               |

| 8.2.    | PCI Express coupling lane                                                                                                    | 18                                                               |

| 8.3.    | Additional resources for PCI Express signal:                                                                                 | routing                                                          |

| recomm  | endations                                                                                                                    | 18                                                               |

| MIPI-0  | CSI2 PCB considerations                                                                                                      | 19                                                               |

| 9.1.    | PCB considerations:                                                                                                          | 19                                                               |

| Unuse   | d peripherals                                                                                                                | 20                                                               |

|         | S32V2 2.1. S32V2 Power 4.1. 4.2. 4.3. Device 5.1. 5.2. PCB s 6.1. DDR c 7.1. PCI Es 8.1. 8.2. 8.3. recommodified MIPI-0 9.1. | S32V234 package overview Power supply 4.1. Power Supply Proposal |

for the most up-to-date information available for this device.

Figure 1. S32V234 block diagram

#### 1.1.1. S32V234-EVB2 Evaluation Board

The S32V234 EVB2 is the evaluation board created by NXP for this device. We recommend using it as example when creating a new board. This board was not designed for a real automotive production environment but can be helpful to answer many doubts about connecting interfaces and HW configurations for someone creating a new design. See <a href="https://www.nxp.com/s32v234evb">www.nxp.com/s32v234evb</a> for more details about this evaluation board. Note however that the DDR3/L byte lane prime connection on the EVB2 is known to be incorrect.

#### 1.1.2. Recommended Reference Manual Sections

The following sections are recommended reads for Hardware Engineers designing a PCB with S32V234 device:

- Chapter 2: Introduction. It will give a general overview of what is available on the device.

- Chapter 5: Signal Description. In addition to this chapter, the RM has some files attachments. Refer to the IO Signal table for details about each pin in the device.

- Chapter 20: System Integration Unit Lite2: This system provides control over all the electrical pin controls and GPIO.

- Chapter 22: Clocking. Provides a global understanding of the clock architecture

- Chapter 28: Reset Overview: Provides a general understanding of Reset architecture and modules.

- Chapter 67: Power Management

- Chapter 70: Functional Safety Overview: provides a quick reference regarding Functional Safety documentation available

# 2. S32V234 Design Checklist

This document provides a design checklist for the S32V234 processor. The design checklist tables recommend optimal design and provide explanations to help users understand better. All supplemental tables referenced by the checklist appear in sections following the design checklist tables.

### 2.1. Design Checklist Tables

#### 2.1.1. Reset, TEST Pin and Boot Mode Checklist

| Check | Recommendations                                                                                                                                                                                    | Explanation/Supplemental                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| box   |                                                                                                                                                                                                    | Recommendations                                                                                                                                                                                                          |

|       | The EXT_POR should be asserted until all the SOC Voltage supplies have stabilized after power supply ramp.                                                                                         | While the PMC module within the device will not de-assert the internal POR until supply voltages are stable. It is advisable to wait for supply stability to avoid unnecessary device resets caused by LVD/HVD triggered |

|       |                                                                                                                                                                                                    | resets.                                                                                                                                                                                                                  |

|       | 2. A 10KΩ pull-up is recommended on RESET. If a decoupling capacitor is used on the RESET or EXT_POR signals, the RC time constant must not exceed 1ms.                                            | If the time constant is such that the RESET signal rises too slowly, this may result in the input circuit oscillating.                                                                                                   |

|       | Check that TEST pin is connected to GND                                                                                                                                                            | This is for factory test only.                                                                                                                                                                                           |

|       | <ol> <li>BOOTMOD[0] (AC20) and<br/>BOOTMOD[1] (AC21) pins must<br/>not be left floating. Make sure<br/>these signals have been pulled<br/>up/down as required with a 10kΩ<br/>resistor.</li> </ol> | Use pull-up or pull-down resistors to select the desired boot mode. See RM for details.                                                                                                                                  |

|       | 5. Make sure all signals that require to be pulled to a defined input state are pulled with an external resistor up to 10kΩ instead of the internal pulls.                                         | Internal default weak pulls are not always strong enough, external pulls are always required for defined signal states. Use of 100k pad pull settings by software is not recommended.                                    |

# 2.1.2. Oscillator/ Crystal Checklist

| Check | Recommendations                                     | Explanation/Supplemental Recommendations |

|-------|-----------------------------------------------------|------------------------------------------|

| box   |                                                     |                                          |

|       | Choose 1 of the 2 clocking options;                 | Clock input may only be 40MHz            |

|       | Connect a 40MHz crystal between                     |                                          |

|       | EXTAL and XTAL.                                     |                                          |

|       | <ul> <li>Connect a suitable 40MHz single</li> </ul> |                                          |

|       | end clock input to EXTAL.                           |                                          |

|       | 2. If using an external oscillator                  | The erratum describes the conditions     |

|       | instead of a crystal check erratum                  | that must be met to properly boot        |

|       | e11133                                              | with an external oscillator              |

# 2.1.3. DDR3/L Checklist

| Check<br>box | Recommendations                                                                                                                                                                                       | Explanation/ Supplemental Recommendations                                                                                                         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 1. Connect the DDRO_ZN and DDR1_ZN balls on the processor to a 240Ω, 1% resistor to GND.                                                                                                              | This is a reference used during DRAM output buffer driver calibration.                                                                            |

|              | 2. If swapping of byte lanes has been used to ease layout routing. The S32V2 DM and DQS signals must match that of the connected byte lane (DM0, DQS0, nDQS0 must follow the Least significant byte). | Control signals must match the Byte Lane Data signals.                                                                                            |

|              | 3. If swapping bits within the byte lane, the prime bit of each byte (D0, D8, D16 etc ) must not be swapped.                                                                                          | During write leveling, the CLK sampling feedback Is driven onto the prime bit of each byte and sampled by S32V2 controller on the prime bit only. |

|              | 4. Only one ODT signal is required per CS signal.                                                                                                                                                     |                                                                                                                                                   |

|              | 5. The architecture for each chip inside the DRAM must be x16 or x32.                                                                                                                                 | This processor does not support byte mode                                                                                                         |

|              | 6. DDRx_CLKO should have more propagation delay to a memory chip on the PCB layout than the corresponding DQS for that                                                                                | This allows write leveling calibration perform correctly.                                                                                         |

| memory chip. The extra propagation delay should not exceed ½ clock. |                                                                                                                                                                                      |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7. 16 bit mode is not recommended due to reduced throughput         | S32V234 uses cases normally require high throughput and a 16bit bus will be limiting. In addition, erratum e11136 is applicable and calibrations routines need to be software based. |

#### 2.1.4. LPDDR2 Checklist

| Check | Recommendations                     | Explanation/ Supplemental            |

|-------|-------------------------------------|--------------------------------------|

| box   |                                     | Recommendations                      |

|       | 1. Only 32bit configuration mode is | For LPDDR2 the controller only       |

|       | supported                           | supports 32bit mode, check erratum   |

|       |                                     | e11136 for more details              |

|       | 2. Make sure your design does not   | Review erratum e11155, we don't      |

|       | use LPDDR2 memories that are        | recommend dual die memories for      |

|       | dual die and have a single CS.      | new designs.                         |

|       | 3. Connect the DDR0_ZN and          | This is a reference used during DRAM |

|       | DDR1_ZN balls on the processor to   | output buffer driver calibration.    |

|       | a 240Ω, 1% resistor to GND.         |                                      |

|       | 4. CKEO and CKE1 require external   | CKE[1:0] must be pulled down to meet |

|       | pull-down resistors to GND for      | the JEDEC sequence until the         |

|       | JEDEC compliance when using         | controller is configured and starts  |

|       | LPDDR2.                             | driving. NXP designs use 10kΩ        |

# 2.1.5. Power Supplies

| Check<br>box | Recommendations                                                                                      | Explanation/ Supplemental Recommendations                                                                           |

|--------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|              | For part numbers that GPU is not available VDD_LV_CORE_GPU power supply must be connected to ground. | Connecting the GPU Supply to ground will ensure no additional leakage current is consumed by the device.            |

|              | For part numbers with 2 cores     VDD_LV_CORE_ARM must be connected to ground.                       | Connecting the CPU supply to ground will ensure no additional leakage current is consumed by the device.            |

|              | Apart from the special cases of the VDD_LV_CORE_GPU and VDD_LV_CORE_ARM all remaining                | The device can malfunction if any of the supplies is not powered apart from the special cases mentioned on 1 and 2. |

| power supplies must be always powered                                                                                  |                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4. Make sure the supply voltage level properly matches the devices connected to the I/O being fed by that voltage rail | The device allows some supplies to work at 3.3V or 1.8V, double check that you don't have incompatible voltage connected to those rails or proper voltage level translators are used. |

#### 2.1.6. PCIe Checklist

| Check | Recommendations                       | Explanation/Supplemental               |

|-------|---------------------------------------|----------------------------------------|

| box   |                                       | Recommendations                        |

|       | 1. Use an appropriate reference clock | The PCIe standard specifies a 100 MHz  |

|       | generator.                            | clock (Refclk) with greater than ±300  |

|       |                                       | ppm frequency stability at both the    |

|       |                                       | transmitting and receiving devices.    |

|       | 2. The differential transmitter must  | To ensure PCle specification           |

|       | be AC coupled. Use a 0.1 μF-series    | compliance, AC coupling is required at |

|       | capacitor on PCIE_TX_P and a          | each transmitter. The receiver must    |

|       | second 0.1 μF on PCIE_TX_N.           | be DC coupled.                         |

|       | 3. Each PCIE_REXT ball should be      | The PHY uses an external resistor to   |

|       | connected to the ground through a     | calibrate the termination impedances   |

|       | 200Ω, 1% resistor.                    | of the high-speed inputs and outputs   |

|       |                                       | of the PHY.                            |

#### 2.1.7. MIPI CSI Checklist

| Check | Recommendations                      | Explanation/Supplemental             |

|-------|--------------------------------------|--------------------------------------|

| box   |                                      | Recommendations                      |

|       | 1. An accurate 15K ohm resistor with | Pin to connect an external reference |

|       | 1% variation or lower is required    | resistor to for autocalibration.     |

|       | for CSIn_ZQ                          |                                      |

#### 2.1.8. QSPI/NOR-Flash Checklist

| Check | Recommendations                       | Explanation/Supplemental             |

|-------|---------------------------------------|--------------------------------------|

| box   |                                       | Recommendations                      |

|       | 1. For HyperFlash (from Cypress), the | Make sure you order the NXP specific |

|       | interface supports the NXP            | HyperFlash (Cypress) part number     |

|       | specific Central Read Strobe (CRS)    | from your vendor.                    |

|       | functionality and is only supported   |                                      |

|       | on Flash A interface.                 |                                      |

#### 2.1.9. I2C Checklist

| Check<br>box | Recommendations                                                                                                                                                       | Explanation/Supplemental Recommendations                                                                                                                                                                                                                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Verify the target I <sup>2</sup> C interface clock rates.                                                                                                             | The I <sup>2</sup> C bus can only be operated as fast as the slowest peripheral on the bus. If faster operation is required, move the slow devices to another I <sup>2</sup> C port.                                                                      |

|              | 2. Verify that there are no I <sup>2</sup> C address conflicts on any of the I <sup>2</sup> C buses utilised.                                                         | There are multiple I <sup>2</sup> C ports available on the chip, so if a conflict exists, move one of the conflicting devices to a different I <sup>2</sup> C bus. If this is not possible, use an I <sup>2</sup> C bus switch (NXP part number PCA9646). |

|              | 3. Do not place more than one set of pull-up resistors on the I <sup>2</sup> C lines.                                                                                 | This could result in excessive loading and potential incorrect operation. Choose the pull-up value commensurate with the bus speed being utilized.                                                                                                        |

|              | 4. Ensure that the VCC rail powering the I <sup>2</sup> C interface balls match the supply voltage used for the pull-up resistors and slave I <sup>2</sup> C devices. | Prevent device damage or incorrect operation due to voltage mismatch.                                                                                                                                                                                     |

# 2.1.10. JTAG Standard Debug Connector Checklist

| Check<br>box | JTAG Signal | I/O<br>Type | Recommendation | Supplemental / Comments |

|--------------|-------------|-------------|----------------|-------------------------|

|              | TMS         | I           | 10kΩ pull-up   |                         |

| Check<br>box | JTAG Signal | I/O<br>Type | Recommendation Supplemental / Comments                                                             |                                                                            |  |

|--------------|-------------|-------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

|              | TCK         | I           | 10kΩ pull-down*                                                                                    | Is mandatory to place this pull-down otherwise LBIST can present failures. |  |

|              | TDO         | 0           | 10kΩ pull-up                                                                                       | This is a three-state output signal                                        |  |

|              | TDI         | I           | 10kΩ pull-up                                                                                       |                                                                            |  |

|              | JCOMP       | I/O         | Pull it down (10kΩ) if the debugger has access to the signal to overdrive it, otherwise pull it up | When this signal is pulled down it disables JTAG and boundary scan modes.  |  |

<sup>\*</sup> Mandatory

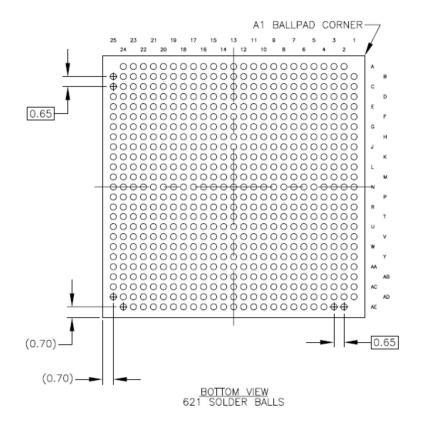

### 3. S32V234 package overview

The S32V324 is available in a single package type: 621 FC-BGA package that is suitable for development, debug and commercial production.

Package dimensions are given below. For complete details please review the package datasheet which is available on nxp.com with the following package number: 98ASA00819D

#### **Package**

-17x17mm FCPBGA 0.65mm pitch

-Die thickness: 30mil (780μm)

-Die size: 7.62mm x 7.51mm

-SRO: 0.35mm SMD

-Solder Ball: 96.5Sn3.5Ag 0.40mm

# 4. Power supply

The S32V234 processor includes a robust power management infrastructure. It provides power monitoring for all internal voltages and clock gating capabilities for peripheral and core modules. The

monitoring capability is used to ensure supply voltages and internal voltages are within the required operating ranges before the processor can exit from the reset state and enter operation.

The S32V234 processor does not have an on-chip regulator. An external switching regulator should be used to derive core supply. The analog voltage supplies needs to be protected from noise on digital supply, at least by means of decoupling capacitors. Better filters can be used if they do not affect regulator stability. A separate regulator for analog supply is preferred.

The S32V234 processor has only one operating mode, with no specific standby or stop modes. However, by taking advantage of the devices clock gating capabilities current consumption can be greatly reduced.

Run Mode: Entire SoC is powered and clock gated.

Run Mode with clock/power gating: the power consumption of the SoC can be managed by clock gating of the unused processing blocks and peripherals in the SoC and power gating blocks which supports it.

The main power supplies required are:

- 1.0 V external supply for the core voltage

- 1.8 V external supply for digital logic and interfaces, analog circuits and GPIO

- 3.3 V external supply for GPIO

- 1.2 V, 1.35 V or 1.5 V external supply for the DRAM I/O depending on the selected DRAM

## **4.1.** Power Supply Proposal

The S32V234 is an SOC composed of a variety of high-performance computing cores, high speed memory interfaces, peripherals and analog subsystem modules. The supply current drawn on the 1V voltage rails dominates the overall power consumption of the device, with considerable static power consumption (leakage) at Tj=125°C for the worst silicon (please refer to the device datasheet, section Power consumption for the current information). Dynamic power consumption can be managed with clock gating or with frequency adjustment. For applications which do not require the GPU or Second A53 core per cluster, a static power gating options is available which should drastically reduce the maximum static power consumption.

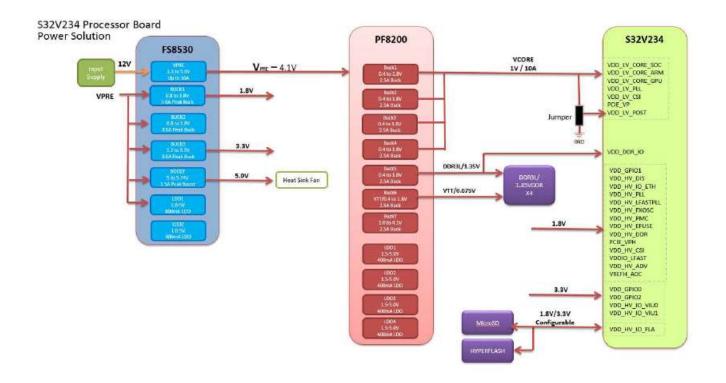

NXP recommends using a primary FS85/FS84 regulator Vbat (12V/24V) and the secondary PF8200 PMIC for S32V234. This validated system solution meets the load requirements of the S32V234 SoC for all use-cases and provides the necessary safety mechanisms to comply with ASIL B functional safety ratings (scalable to ASIL C with proper supply monitoring).

The recommended configuration is shown in the diagram below with the PF8200 rails connected as follows:

- Buck1 through 4 are configured in a Quad-phase architecture for best thermal distribution, ripple, noise and transient response. The Quad-phase DC-DC converter provides output current as high as 10A

- Buck 5 provides power to the DDR I/O rail

- Buck 6-7 supply the 1.8V/3.3V IO rails

- Buck 6 can optionally be used to provide VTT (by tracking Buck5/2)

- Four LDOs are also available to provide a low noise supply for the 1.5V-5V 400mA analog voltage supplies

The FS85/FS84 is an automotive grade, functionally safe multi-output power supply integrated circuit, with focus on Radar, Vision, ADAS, Radio and Infotainment applications. It includes multiple switch mode and linear voltage regulators. It offers external frequency synchronization input and output, for an optimized system EMC performance. In addition to this, FS85 provides Wake signals to achieve low power modes in the system.

The FS85/FS84 includes enhanced safety features, such as a fail-safe output, making it an integral part of a safety-oriented system partitioning, thereby covering different safety integrity levels (FS85 ASIL-D/FS84 ASIL-B/ PF82 ASIL-B). It is developed in compliance with ISO26262 standard.

For more details about the FS8x and PF8x power regulators, please contact local NXP Sales Representative.

### 4.2. Power supply signals and decoupling

Supply ramp rate on all rails must be below 25 V/mS. Refer to the datasheet for further operating conditions of the power supplies.

The Power supplies are divided into three groups. **CORE, IO & Analog.** The rails are further subdivided by their voltage and again by their function.

Table 4 lists all the SOC power domains with the corresponding pin names.

**SOC** supply pins

| Supply Voltage           |                               |                                          |  |  |  |  |

|--------------------------|-------------------------------|------------------------------------------|--|--|--|--|

| Function                 | Supply Voltage                | Description                              |  |  |  |  |

| VDD_GPIO0                | 3.3 V                         | Isolated I/O Voltage Supply for pad      |  |  |  |  |

|                          |                               | segment GPIO0 and PMC                    |  |  |  |  |

| VDD_GPIO <n=1,2></n=1,2> | 1.8 V or 3.3 V                | Isolated I/O 1.8V/3.3 V supply for multi |  |  |  |  |

| VDD_HV_IO_VIU0           |                               | voltage I/O segments                     |  |  |  |  |

| VDD_HV_IO_VIU1           |                               |                                          |  |  |  |  |

| VDD_HV_IO_DIS            |                               |                                          |  |  |  |  |

| VDD_HV_IO_FLA            |                               |                                          |  |  |  |  |

| VDD_HV_IO_ETH            | 1.5 V / 1.8 V / 2.5 V / 3.3 V | Isolated I/O supply for multi voltage    |  |  |  |  |

|                          |                               | Ethernet IO segment                      |  |  |  |  |

| VDD_DDR_IO               | 1.2 V / 1.35 V / 1.5 V        | LPDDR2/DDR3L/DDR3 IO Supply              |  |  |  |  |

| VDDIO_LFAST              | 1.8V                          | LFAST IO Bank Supply                     |  |  |  |  |

| VDD_LV_CORE_SOC,         | 1.0 V                         | Core Logic Low Voltage Supply            |  |  |  |  |

| VDD_LV_CORE_ARM,         |                               |                                          |  |  |  |  |

| VDD_LV_CORE_GPU          |                               |                                          |  |  |  |  |

| VDD_HV_CSI               | 1.8 V                         | Internal Analog and PLL subsystem        |  |  |  |  |

| VDD_HV_PLL,              |                               | supplies 1.8V                            |  |  |  |  |

| VDD_HV_LFASTPLL,         |                               |                                          |  |  |  |  |

| VDD_HV_FXOSC,            |                               |                                          |  |  |  |  |

| VDD_HV_PMC,              |                               |                                          |  |  |  |  |

| VDD_HV_EFUSE,            |                               |                                          |  |  |  |  |

| VDD_HV_DDR               |                               |                                          |  |  |  |  |

| VDD_HV_ADV               |                               |                                          |  |  |  |  |

| PCIE_VPH                 |                               |                                          |  |  |  |  |

| VREFH_ADC                |                               | ADC Voltage Reference                    |  |  |  |  |

| VDD_LV_CSI               | 1.0 V                         | Internal Analog and PLL subsystem        |  |  |  |  |

| VDD_LV_PLL               |                               | supplies 1.0V                            |  |  |  |  |

| PCIE_VP                  |                               |                                          |  |  |  |  |

<sup>\*</sup>VDD\_LV\_POST is for NXP internal test purposes only and must be connected to Ground in production board design.

### 4.2.1. Placing decoupling capacitors

Place small decoupling and larger bulk capacitors on the bottom side of the PCB. Placing the decoupling capacitors close to the power balls is critical to minimize inductance and ensure high-speed transient current required by the processor. See the S32V234-EVB layout for an example of the desired decoupling capacitor placement.

The following list introduces how to choose correct decoupling scheme:

- Place the largest capacitance in the smallest package that budget and manufacturing can support.

- Minimize trace length (inductance) to small caps

- Series inductance cancels out capacitance

- Tie caps to GND plane directly with a via

- Place capacitors close to the power ball of the associated package from the schematic

- The smaller the capacitor value, the closer to the SoC pins it should be placed

Recommended decoupling per power supply

| Supply Decoupling Additional Notes |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Supply                             | Capacitors  | Additional Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VDD CDIO (** 0.1.2)                | •           | No. 1 Acres 1 Acres 1 Acres 1 Acres 2 |  |  |  |

| VDD_GPIO <n=0,1,2></n=0,1,2>       | 1x 10 μF    | Number of decoupling capacitors are per power rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VDD_HV_IO_VIU0                     | 1x 1 μF     | Place one 0201 cap per power pin where possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VDD_HV_IO_VIU1                     | 1x 0.1 μF   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| VDD_HV_IO_DIS                      | 2x 0.01 μF  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| VDD_HV_IO_FLA                      | 1x 1000 pF  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| VDD_HV_IO_ETH                      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| VDDIO_LFAST                        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| VDD_DDR_IO                         | 8x 1 μF     | Place one 0201 cap per power/ground pin pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                    | 3x 0.1 μF   | <ul> <li>Use 22μf and 10μf bulk caps to supply sufficient current at point of load</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                    | 6x 0.01 μF  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                    | 4x 1000 pF  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                    | 3x 10 μF    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                    | 3x 22 μF    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| VDD_LV_CORE_SOC                    | 4 x 22 μF   | Place one 0201 cap per power/ground pin pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| VDD_LV_CORE_ARM                    | 4 x 10 μF   | Place 10uF caps near to the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| VDD_LV_CORE_GPU                    | 14 x 1 μF   | Place 22uF caps near to power supply circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |