# nVidia Hardware Documentation Release git

Marcelina Kościelnicka

May 24, 2021

# Contents

| 1  | Notational conventions                                   | 3     |

|----|----------------------------------------------------------|-------|

|    | 1.1 Introduction                                         | . 3   |

|    | 1.2 Bit operations                                       | . 3   |

|    | 1.3 Sign extension                                       | . 4   |

|    | 1.4 Bitfield extraction                                  | . 5   |

| 2  | nVidia hardware documentation                            | 7     |

|    | 2.1 nVidia GPU introduction                              | . 7   |

|    | 2.2 GPU chips                                            | . 13  |

|    | 2.3 nVidia PCI id database                               | . 28  |

|    | 2.4 PCI/PCIE/AGP bus interface and card management logic | . 77  |

|    | 2.5 Power, thermal, and clock management                 | . 81  |

|    | 2.6 GPU external device I/O units                        | . 99  |

|    | 2.7 Memory access and structure                          | . 102 |

|    | 2.8 PFIFO: command submission to execution engines       | . 142 |

|    | 2.9 PGRAPH: 2d/3d graphics and compute engine            | . 167 |

|    | 2.10 falcon microprocessor                               | . 316 |

|    | 2.11 Video decoding, encoding, and processing            | . 373 |

|    | 2.12 Performance counters                                | . 491 |

|    | 2.13 Display subsystem                                   | . 509 |

| 3  | nVidia Resource Manager documentation                    | 519   |

| C  | 3.1 PMU                                                  |       |

|    |                                                          |       |

| 4  | envydis and envyas documentation                         | 543   |

|    | 4.1 Using envydis and envyas                             | . 543 |

| 5  | TODO list                                                | 549   |

| 6  | Indices and tables                                       | 685   |

| In | dex                                                      | 687   |

Contents:

# CHAPTER 1

# Notational conventions

#### Contents

- Notational conventions

- Introduction

- Bit operations

- Sign extension

- Bitfield extraction

# 1.1 Introduction

Semantics of many operations are described in pseudocode. Here are some often used primitives.

## 1.2 Bit operations

In many places, the GPUs allow specifying arbitrary X-input boolean or bitwise operations, where X is 2, 3, or 4. They are described by a 2\*\*X-bit mask selecting the bit combinations for which the output should be true. For example, 2-input operation 0x4 (0b0100) is  $\sim v1 \& v2$ : only bit 2 (0b10) is set, so the only input combination (0, 1) results in a true output. Likewise, 3-input operation 0xaa (0b10101010) is simply a passthrough of first input: the bits set in the mask are 1, 3, 5, 7 (0b001, 0b011, 0b101, 0b111), which corresponds exactly to the input combinations which have the first input equal to 1.

The exact semantics of such operations are:

```

# single-bit version

def bitop_single(op, *inputs):

```

(continues on next page)

(continued from previous page)

```

# first, construct mask bit index from the inputs

bitidx = 0

for idx, input in enumerate(inputs):

if input:

bitidx |= 1 << idx

# second, the result is the given bit of the mask

return op >> bitidx & 1

def bitop(op, *inputs):

max_len = max(input.bit_length() for input in inputs)

res = 0

# perform bitop_single operation on each bit (+ 1 for sign bit)

for x in range(max_len + 1):

res |= bitop_single(op, *(input >> x & 1 for input in inputs)) << x

# all bits starting from max_len will be identical - just what sext does

return sext(res, max_len)

```

As further example, the 2-input operations on a, b are:

- 0x0: always 0

- 0x1:~a & ~b

- 0x2:a & ~b

- 0x3:~b

- 0x4:~a & b

- 0x5:~a

- 0x6:a ^ b

- 0x7:~a | ~b

- 0x8:a & b

- 0x9:~a ^ b

- 0xa:a

- 0xb:a | ~b

- 0xc:b

- 0xd:~a | b

- 0xe:a | b

- Oxf: always 1

For further enlightenment, you can search for GDI raster operations, which correspond to 3-input bit operations.

## 1.3 Sign extension

An often used primitive is sign extension from a given bit. This operation is known as sext after xtensa instruction of the same name and is formally defined as follows:

```

def sext(val, bit):

# mask with all bits up from #bit set

mask = -1 << bit

if val & 1 << bit:

# sign bit set, negative, set all upper bits

return val | mask

else:

# sign bit not set, positive, clear all upper bits

return val & ~mask</pre>

```

# **1.4 Bitfield extraction**

Another often used primitive is bitfield extraction. Extracting an unsigned bitfield of length 1 starting at position s in val is denoted by extr(val, s, l), and signed one by extrs(val, s, l):

```

def extr(val, s, l):

return val >> s & ((1 << l) - 1)

def extrs(val, s, l):

return sext(extrs(val, s, l), l - 1)</pre>

```

# CHAPTER 2

## nVidia hardware documentation

Contents:

# 2.1 nVidia GPU introduction

#### Contents

- nVidia GPU introduction

- Introduction

- Card schematic

- GPU schematic NV3:G80

- GPU schematic G80:GF100

- GPU schematic GF100-

### 2.1.1 Introduction

This file is a short introduction to nvidia GPUs and graphics cards. Note that the schematics shown here are simplified and do not take all details into account - consult specific unit documentation when needed.

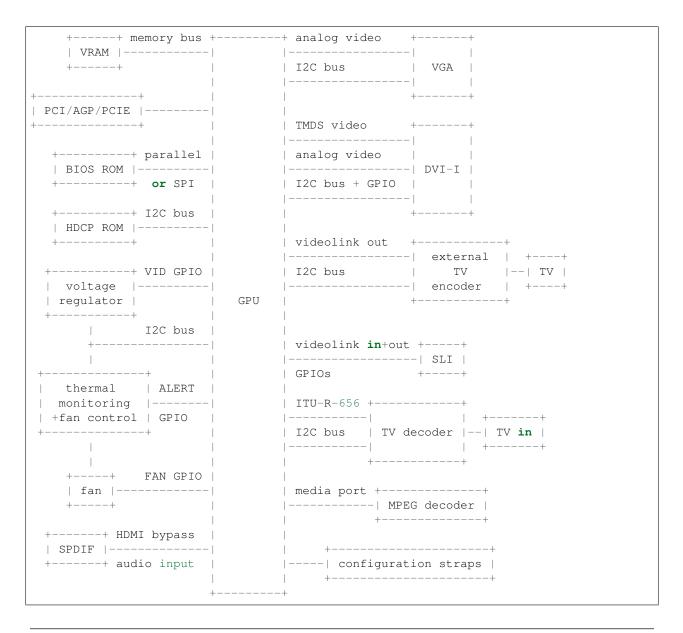

### 2.1.2 Card schematic

An nvidia-based graphics card is made of a main GPU chip and many supporting chips. Note that the following schematic attempts to show as many chips as possible - not all of them are included on all cards.

**Note:** while this schematic shows a TV output using an external encoder chip, newer cards have an internal TV encoder and can connect the output directly to the GPU. Also, external encoders are not limited to TV outputs - they're also used for TMDS, DisplayPort and LVDS outputs on some cards.

Note: in many cases, I2C buses can be shared between various devices even when not shown by the above schema.

In summary, a card contains:

- a GPU chip [see GPU chips for a list]

- a PCI, AGP, or PCI-Express host interface

- on-board GPU memory [aka VRAM] depending on GPU, various memory types can be supported: VRAM, EDO, SGRAM, SDR, DDR2, GDDR3, DDR3, GDDR5.

- a parallel or SPI-connected flash ROM containing the video BIOS. The BIOS image, in addition to standard

VGA BIOS code, contains information about the devices and connectors present on the card and scripts to boot up and manage devices on the card.

- configuration straps a set of resistors used to configure various functions of the card that need to be up before the card is POSTed.

- a small I2C EEPROM with encrypted HDCP keys [optional, some G84:GT215, now discontinued in favor of storing the keys in fuses on the GPU]

- a voltage regulator [starting with NV10 [?] family] starting with roughly NV30 family, the target voltage can be set via GPIO pins on the GPU. The voltage regulator may also have "power good" and "emergency shutdown" signals connected to the GPU via GPIOs. In some rare cases, particularly on high-end cards, the voltage regulator may also be accessible via I2C.

- optionally [usually on high-end cards], a thermal monitoring chip accessible via I2C, to supplement/replace the bultin thermal sensor of the GPU. May or may not include autonomous fan control and fan speed measurement capability. Usually has a "thermal alert" pin connected to a GPIO.

- a fan control and speed measurement done either by the thermal monitoring chip, or by the GPU via GPIOs.

- SPDIF input [rare, some G84:GT215] used for audio bypass to HDMI-capable TMDS outputs, newer GPUs include a builtin audio codec instead.

- on-chip video outputs video output connectors connected directly to the GPU. Supported output types depend on the GPU and include VGA, TV [composite, S-Video, or component], TMDS [ie. the protocol used in DVI digital and HDMI], FPD-Link [aka LVDS], DisplayPort.

- external output encoders usually found with older GPUs which don't support TV, TMDS or FPD-Link outputs directly. The encoder is connected to the GPU via a parallel data bus ["videolink"] and a controlling I2C bus.

- SLI connectors [optional, newer high-end cards only] video links used to transmit video to display from slave cards in SLI configuration to the master. Uses the same circuitry as outputs to external output encoders.

- TV decoder chip [sometimes with a tuner] connected to the capture port of the GPU and to an I2C bus rare, on old cards only

- external MPEG decoder chip connected to so-called mediaport on the GPU alleged to exist on some NV3/NV4/NV10 cards, but never seen in the wild

In addition to normal cards, nvidia GPUs may be found integrated on motherboards - in this case they're often missing own BIOS and HDCP ROMs, instead having them intergrated with the main system ROM. There are also IGPs [Integrated Graphics Processors], which are a special variant of GPU integrated into the main system chipset. They don't have on-board memory or memory controller, sharing the main system RAM instead.

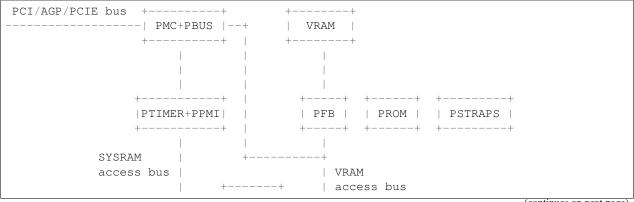

### 2.1.3 GPU schematic - NV3:G80

The GPU is made of:

- control circuitry:

- PMC: master control area

- PBUS: bus control and an area where "misc" registers are thrown in. Known to contain at least:

- \* HWSQ, a simple script engine, can poke card registers and sleep in a given sequence [NV17+]

- \* a thermal sensor [NV30+]

- \* clock gating control [NV17+]

- \* indirect VRAM access from host circuitry [NV30+]

- \* ROM timings control

- \* PWM controller for fans and panel backlight [NV17+]

- PPMI: PCI Memory Interface, handles SYSRAM accesses from other units of the GPU

- PTIMER: measures wall time and delivers alarm interrupts

- PCLOCK+PCONTROL: clock generation and distribution [contained in PRAMDAC on pre-NV40 GPUs]

- PFB: memory controller and arbiter

- PROM: VBIOS ROM access

- PSTRAPS: configuration straps access

- processing engines:

- *PFIFO*: gathers processing commands from the command buffers prepared by the host and delivers them to PGRAPH and PVPE engines in orderly manner

- PGRAPH: memory copying, 2d and 3d rendering engine

- PVPE: a trio of video decoding/encoding engines

- \* PMPEG: MPEG1 and MPEG2 mocomp and IDCT decoding engine [NV17+]

- \* PME: motion estimation engine [NV40+]

- \* PVP1: VP1 video processor [NV41+]

- PCOUNTER: performance monitoring counters for the processing engines and memory controller

- display engines:

- PCRTC: generates display control signals and reads framebuffer data for display, present in two instances on NV11+ cards; also handles GPIO and I2C

- PVIDEO: reads and preprocesses overlay video data

- PRAMDAC: multiplexes PCRTC, PVIDEO and cursor image data, applies palette LUT, coverts to output signals, present in two instances on NV11+ cards; on pre-NV40 cards also deals with clock generation

- PTV: an on-chip TV encoder

- misc engines:

- PMEDIA: controls video capture input and the mediaport, acts as a DMA controller for them

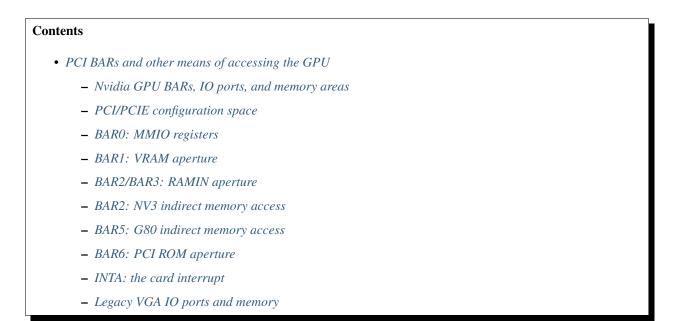

Almost all units of the GPU are controlled through MMIO registers accessible by a common bus and visible through PCI BAR0 [see *PCI BARs and other means of accessing the GPU*]. This bus is not shown above.

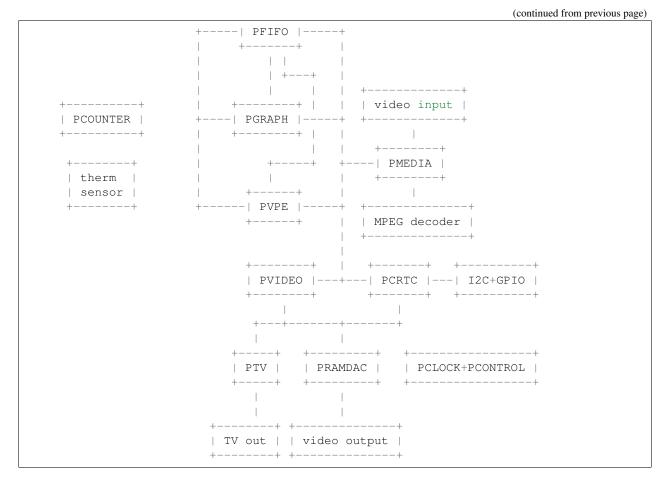

### 2.1.4 GPU schematic - G80:GF100

(continues on next page)

(continued from previous page)

```

| PCODEC | | | |

+----+ | +----+

+--| video decoding, crypt |

+----+

| PMEDIA |--+

+----+

```

The GPU is made of:

- control circuitry:

- PMC: master control area

- PBUS: bus control and an area where "misc" registers are thrown in. Known to contain at least:

- \* HWSQ, a simple script engine, can poke card registers and sleep in a given sequence

- \* clock gating control

- \* indirect VRAM access from host circuitry

- PTIMER: measures wall time and delivers alarm interrupts

- PCLOCK+PCONTROL: clock generation and distribution

- PTHERM: thermal sensor and clock throttling circuitry

- PDAEMON: card management microcontroller

- PFB: memory controller and arbiter

- processing engines:

- *PFIFO*: gathers processing commands from the command buffers prepared by the host and delivers them to PGRAPH and PVPE engines in orderly manner

- PGRAPH: memory copying, 2d and 3d rendering engine

- video decoding engines, see below

- PCOPY: asynchronous copy engine

- PVCOMP: video compositing engine

- PCOUNTER: performance monitoring counters for the processing engines and memory controller

- display and IO port units:

- PNVIO: deals with misc external devices

- \* GPIOs

- \* fan PWM controllers

- \* I2C bus controllers

- \* videolink controls

- \* ROM interface

- \* straps interface

- \* PNVIO/PDISPLAY clock generation

- PDISPLAY: a unified display engine

- PCODEC: audio codec for HDMI audio

• misc engines:

- PMEDIA: controls video capture input and the mediaport, acts as a DMA controller for them

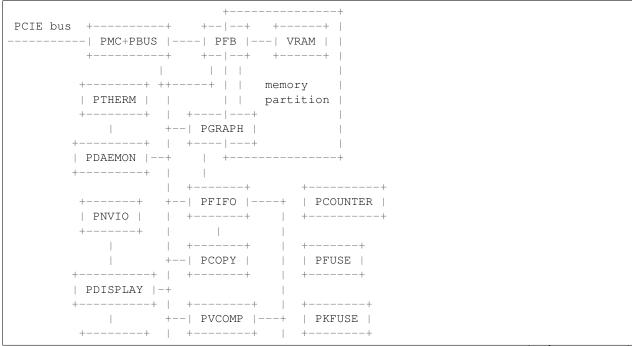

### 2.1.5 GPU schematic - GF100-

Todo: finish file

# 2.2 GPU chips

| Contents                            |                          |

|-------------------------------------|--------------------------|

| • GPU chips                         |                          |

| – Introduction                      |                          |

| – The GPU families                  |                          |

| * NV1 family: NV1                   |                          |

| * NV3 (RIVA) family: NV3, NV3T      |                          |

| * NV4 (TNT) family: NV4, NV5        |                          |

| * Celsius family: NV10, NV15, NV1A  | , NV11, NV17, NV1F, NV18 |

| * Kelvin family: NV20, NV2A, NV25,  | NV28                     |

| * Rankine family: NV30, NV35, NV31  | !, NV36, NV34            |

| * Curie family                      |                          |

| * Tesla family                      |                          |

| * Fermi/Kepler/Maxwell/Pascal/Volta | /Turing family           |

| - Comparison table                  |                          |

### 2.2.1 Introduction

Each nvidia GPU has several identifying numbers that can be used to determine supported features, the engines it contains, and the register set. The most important of these numbers is an 8-bit number known as the "GPU id". If two cards have the same GPU id, their GPUs support identical features, engines, and registers, with very minor exceptions. Such cards can however still differ in the external devices they contain: output connectors, encoders, capture chips, temperature sensors, fan controllers, installed memory, supported clocks, etc. You can get the GPU id of a card by reading from its PMC area.

The GPU id is usually written as NVxx, where xx is the id written as uppercase hexadecimal number. Note that, while cards before NV10 used another format for their ID register and don't have the GPU id stored directly, they are usually considered as NV1-NV5 anyway.

Nvidia uses "GPU code names" in their materials. They started out identical to the GPU id, but diverged midway through the NV40 series and started using a different numbering. However, for the most part nvidia code names correspond 1 to 1 with the GPU ids.

The GPU id has a mostly one-to-many relationship with pci device ids. Note that the last few bits [0-6 depending on GPU] of PCI device id are changeable through straps [see pstraps]. When pci ids of a GPU are listed in this file, the following shorthands are used:

**1234** PCI device id 0x1234

1234\* PCI device ids 0x1234-0x1237, choosable by straps

**123X** PCI device ids 0x1230-0x123X, choosable by straps

124X+ PCI device ids 0x1240-0x125X, choosable by straps

**124X\*** PCI device ids 0x1240-0x127X, choosable by straps

### 2.2.2 The GPU families

The GPUs can roughly be grouped into a dozen or so families: NV1, NV3/RIVA, NV4/TNT, Celsius, Kelvin, Rankine, Curie, Tesla, Fermi, Kepler, Maxwell, Pascal, Volta and Turing.

This aligns with big revisions of PGRAPH, the drawing engine of the card. While most functionality was introduced in sync with PGRAPH revisions, some other functionality [notably video decoding hardware] gets added in GPUs late in a GPU family and sometimes doesn't even get to the first GPU in the next GPU family. For example, NV11 expanded upon the previous NV15 chipset by adding dual-head support, while NV20 added new PGRAPH revision with shaders, but didn't have dual-head - the first GPU to feature both was NV25.

Also note that a bigger GPU id doesn't always mean a newer card / card with more features: there were quite a few places where the numbering actually went backwards. For example, NV11 came out later than NV15 and added several features.

Nvidia's card release cycle always has the most powerful high-end GPU first, subsequently filling in the lower-end positions with new cut-down GPUs. This means that newer cards in a single sub-family get progressively smaller, but also more featureful - the first GPUs to introduce minor changes like DX10.1 support or new video decoding are usually the low-end ones.

Whenever a range of GPUs is mentioned in the documentation, it's written as "NVxx:NVyy". This is left-inclusive, right-noninclusive range of GPU ids as sorted in the following list. For example, G200:GT218 means GPUs G200, MCP77, MCP79, GT215, GT216. NV20:NV30 effectively means all NV20 family GPUs.

The full known GPU list, sorted roughly according to introduced features, is:

- NV1 family: NV1

- NV3 (aka RIVA) family: NV3, NV3T

- NV4 (aka TNT) family: NV4, NV5

- Celsius family: NV10, NV15, NV1A, NV11, NV17, NV1F, NV18

- Kelvin family: NV20, NV2A, NV25, NV28

- Rankine family: NV30, NV35, NV31, NV36, NV34

- Curie family:

- NV40 subfamily: NV40, NV45, NV41, NV42, NV43, NV44, NV44A

- G70 subfamily: G70, G71, G73, G72

- the IGPs: C51, MCP61, MCP67, MCP68, MCP73

- the special snowflake: RSX

- Tesla family:

- G80 subfamily: G80

- G84 subfamily: G84, G86, G92, G94, G96, G98

- G200 subfamily: G200, MCP77, MCP79

- GT215 subfamily: GT215, GT216, GT218, MCP89

- Fermi family:

- GF100 subfamily: GF100, GF104, GF106, GF114, GF116, GF108, GF110

- GF119 subfamily: GF119, GF117

- Kepler family: GK104, GK107, GK106, GK110, GK110B, GK208, GK208B, GK20A, GK210

- Maxwell family: GM107, GM108, GM204, GM200, GM206, GM20B

- Pascal family: GP100, GP102, GP104, GP106, GP107, GP108

- Volta family: GV100

- Turing family: TU102, TU104, TU106, TU116, TU117

#### NV1 family: NV1

gpu-gen NV1

The first generation of nVidia GPUs. Includes only one GPU – the NV1. It has semi-legendary status, as it's very rare and hard to get. The GPU is also known by its SGS-Thomson code number, STG-2000. The most popular card using this GPU is Diamond EDGE 3D.

This GPU is unusual for multiple reasons:

- It has a builtin sound mixer with a MIDI synthetizer (aka PAUDIO). It is supposed to be paired with an audio codec (AD1848) for full integrated soundcard functionality.

- It is not fully VGA-compatible there is some VGA emulation, but it's quite rough and many features are not supported.

- It has no integrated DAC or clock generators it has to be paired with an accompanying external DAC, the STG-1732 or STG-1764 that will convert raw framebuffer contents to display pixels. It is also charged with generating the clocks for the GPU.

- The accompanying DAC chip also contains game port functionality, for a complete soundcard replacement.

- As if the game port was not enough, the DAC also supports two Sega Saturn controller ports.

- The so-called 3D engine renders textured quadratic surfaces, instead of triangles (as opposed to all later GPUs). Rendering triangles with it is pretty much impossible.

The GPU was jointly manufactured by SGS-Thomson and nVidia, and uses SGS' PCI vendor ID (there are apparently variants using nVidia's vendor id, but not much is known about these).

There's also NV2, which has even more legendary status. It was supposed to be another card based on quadratic surfaces, but it got stuck in development hell and never got released. Apparently it never got to the stage of functioning silicon. The device id of NV2 was supposed to be 0x0010.

#### NV3 (RIVA) family: NV3, NV3T

gpu-gen **NV3**

The first [moderately] sane GPUs from nvidia, and also the first to use AGP bus. There are two chips in this family, and confusingly both use GPU id NV3, but can be told apart by revision. The original NV3 is used in RIVA 128 cards, while the revised NV3, known as NV3T, is used in RIVA 128 ZX. NV3 supports AGP 1x and a maximum of 4MB of VRAM, while NV3T supports AGP 2x and 8MB of VRAM. NV3T also increased number

of slots in PFIFO cache. These GPUs were also manufactured by SGS-Thomson and bear the code name of STG-3000.

The NV3 GPU is made of the following functional blocks:

- host interface, connected to the host machine via PCI or AGP

- two PLLs, to generate video pixel clock and memory clock

- memory interface, connected to 2MB-8MB of external VRAM via 64-bit or 128-bit memory bus, shared with an 8-bit parallel flash ROM

- PFIFO, controlling command submission to PGRAPH and gathering commands through DMA to host memory or direct MMIO submission

- PGRAPH, the 2d/3d drawing engine, supporting windows GDI and Direct3D 5 acceleration

- VGA-compatible CRTC, RAMDAC, and associated video output circuitry, enabling direct connection of VGA analog displays and TV connection via an external AD722 encoder chip

- i2c bus to handle DDC and control mediaport devices

- · double-buffered video overlay and cursor circuitry in RAMDAC

- mediaport, a proprietary interface with ITU656 compatibility mode, allowing connection of external video capture or MPEG2 decoding chip

NV3 introduced RAMIN, an area of memory at the end of VRAM used to hold various control structures for PFIFO and PGRAPH. On NV3, RAMIN can be accessed in BAR1 at addresses starting from 0xc00000, while later cards have it in BAR0. It also introduced DMA objects, a RAMIN structure used to define a VRAM or host memory area that PGRAPH is allowed to use when executing commands on behalf of an application. These early DMA objects are limitted to linear VRAM and paged host memory objects, and have to be switched manually by host. See *NV3 DMA objects* for details.

#### NV4 (TNT) family: NV4, NV5

#### gpu-gen NV4

Improved and somewhat redesigned NV3. Notable changes:

- AGP x4 support

- redesigned and improved DMA command submission

- · separated core and memory clocks

- DMA objects made more orthogonal, and switched automatically by card

- redesigned PGRAPH objects, introducing the concept of object class in hardware

- added BIOS ROM shadow in RAMIN

- Direct3D 6 / multitexturing support in PGRAPH

- bumped max supported VRAM to 16MB

- [NV5] bumped max supported VRAM to 32MB

- [NV5] PGRAPH 2d context object binding in hardware

This family includes the original NV4, used in RIVA TNT cards, and NV5 used in RIVA TNT2 and Vanta cards.

#### Celsius family: NV10, NV15, NV1A, NV11, NV17, NV1F, NV18

#### gpu-gen Celsius

The notable changes in this generation are:

- NV10:

- redesigned memory controller

- max VRAM bumped to 128MB

- redesigned VRAM tiling, with support for multiple tiled regions

- greatly expanded 3d engine: hardware T&L, D3D7, and other features

- GPIO pins introduced for ???

- PFIFO: added REF\_CNT and NONINC commands

- added PCOUNTER: the performance monitoring engine

- new and improved video overlay engine

- redesigned mediaport

- NV15:

- introduced vblank wait PGRAPH commands

- minor 3d engine additions [logic operation, ...]

- NV1A:

- big endian mode

- PFIFO: semaphores and subroutines

- NV11:

- dual head support, meant for laptops with flat panel + external display

- NV17:

- builtin TV encoder

- ZCULL

- added VPE: MPEG2 decoding engine

- NV18:

- AGP x8 support

- second straps set

Todo: what were the GPIOs for?

| pciid | GPU  | pixel pipelines and | texture | date       | notes                                      |

|-------|------|---------------------|---------|------------|--------------------------------------------|

|       |      | ROPs                | units   |            |                                            |

| 0100* | NV10 | 4                   | 4       | 11.10.1999 | the first GeForce card [GeForce 256]       |

| 0150* | NV15 | 4                   | 8       | 26.04.2000 | the high-end card of GeForce 2 lineup      |

|       |      |                     |         |            | [GeForce 2 Ti,]                            |

| 01a0* | NV1A | 2                   | 4       | 04.06.200  | the IGP of GeForce 2 lineup [nForce]       |

| 0110* | NV11 | 2                   | 4       | 28.06.2000 | the low-end card of GeForce 2 lineup       |

|       |      |                     |         |            | [GeForce 2 MX]                             |

| 017X  | NV17 | 2                   | 4       | 06.02.2002 | the low-end card of GeForce 4 lineup       |

|       |      |                     |         |            | [GeForce 4 MX]                             |

| 01fX  | NV1F | 2                   | 4       | 01.10.2002 | the IGP of GeForce 4 lineup [nForce 2]     |

| 018X  | NV18 | 2                   | 4       | 25.09.2002 | 2 like NV17, but with added AGP x8 support |

NV1A and NV1F are IGPs and lack VRAM, memory controller, mediaport, and ROM interface. They use the internal interfaces of the northbridge to access an area of system memory set aside as fake VRAM and BIOS image.

#### Kelvin family: NV20, NV2A, NV25, NV28

#### gpu-gen Kelvin

The first cards of this family were actually developed before NV17, so they miss out on several features introduced in NV17. The first card to merge NV20 and NV17 additions is NV25. Notable changes:

- NV20:

- no dual head support again

- no PTV, VPE

- no ZCULL

- a new memory controller with Z compression

- RAMIN reversal unit bumped to 0x40 bytes

- 3d engine extensions:

- \* programmable vertex shader support

- \* D3D8, shader model 1.1

- PGRAPH automatic context switching

- NV25:

- a merge of NV17 and NV20: has dual-head, ZCULL, ...

- still no VPE and PTV

- NV28:

- AGP x8 support

The GPUs are:

| pciid | GPU  | vertex<br>shaders | pixel pipelines<br>and ROPs | texture<br>units | date      | notes                                 |

|-------|------|-------------------|-----------------------------|------------------|-----------|---------------------------------------|

| 0200* | NV20 | 1                 | 4                           | 8                | 27.02.200 | Of the only GPU of GeForce 3 lineup   |

|       |      |                   |                             |                  |           | [GeForce 3 Ti,]                       |

| 02a0* | NV2A | . 2               | 4                           | 8                | 15.11.200 | Ithe XBOX IGP [XGPU]                  |

| 025X  | NV25 | 2                 | 4                           | 8                | 06.02.200 | 2the high-end GPU of GeForce 4 lineup |

|       |      |                   |                             |                  |           | [GeForce 4 Ti]                        |

| 028X  | NV28 | 2                 | 4                           | 8                | 20.01.200 | Blike NV25, but with added AGP x8     |

|       |      |                   |                             |                  |           | support                               |

NV2A is a GPU designed exclusively for the original xbox, and can't be found anywhere else. Like NV1A and NV1F, it's an IGP.

Todo: verify all sorts of stuff on NV2A

#### Rankine family: NV30, NV35, NV31, NV36, NV34

#### gpu-gen Rankine

The infamous GeForce FX series. Notable changes:

- NV30:

- 2-stage PLLs introduced [still located in PRAMDAC]

- max VRAM size bumped to 256MB

- 3d engine extensions:

- \* programmable fragment shader support

- \* D3D9, shader model 2.0

- added PEEPHOLE indirect memory access

- return of VPE and PTV

- new-style memory timings

- NV35:

- 3d engine now supports depth bounds check

- NV31:

- no NV35 changes, this GPU is derived from NV30

- 2-stage PLLs split into two registers

- VPE engine extended to work as a PFIFO engine

- NV36:

- a merge of NV31 and NV35 changes from NV30

- NV34:

- a comeback of NV10 memory controller!

- NV10-style mem timings again

- no Z compression again

- RAMIN reversal unit back at 16 bytes

- 3d engine additions:

- \* ???

Todo: figure out NV34 3d engine changes

The GPUs are:

| pciid | GPU  | vertex<br>shaders | pixel pipelines<br>ROPs | s and | date       | notes                            |

|-------|------|-------------------|-------------------------|-------|------------|----------------------------------|

| 030X  | NV30 | 2                 | 8                       |       | 27.01.2003 | high-end GPU [GeForce FX 5800]   |

| 033X  | NV35 | 3                 | 8                       |       | 12.05.2003 | very high-end GPU [GeForce FX    |

|       |      |                   |                         |       |            | 59X0]                            |

| 031X  | NV31 | 1                 | 4                       |       | 06.03.2003 | low-end GPU [GeForce FX 5600]    |

| 034X  | NV36 | 3                 | 4                       |       | 23.10.2003 | middle-end GPU [GeForce FX 5700] |

| 032X  | NV34 | 1                 | 4                       |       | 06.03.2003 | low-end GPU [GeForce FX 5200]    |

The pci vendor id is 0x10de.

#### **Curie family**

gpu-gen Curie

This family was the first to feature PCIE cards, and many fundamental areas got significant changes, which later paved the way for G80. It is also the family where GPU ids started to diverge from nvidia code names. The changes:

- NV40:

- RAMIN bumped in size to max 16MB, many structure layout changes

- RAMIN reversal unit bumped to 512kB

- 3d engine: support for shader model 3 and other additions

- Z compression came back

- PGRAPH context switching microcode

- redesigned clock setup

- separate clock for shaders

- rearranged PCOUNTER to handle up to 8 clock domains

- PFIFO cache bumped in size and moved location

- added independent PRMVIO for two heads

- second set of straps added, new strap override registers

- new PPCI PCI config space access window

- MPEG2 encoding capability added to VPE

- FIFO engines now identify the channels by their context addresses, not chids

- BIOS uses all-new BIT structure to describe the card

- individually disablable shader and ROP units.

- added PCONTROL area to... control... stuff?

- memory controller uses NV30-style timings again

- NV41:

- introduced context switching to VPE

- introduced PVP1, microcoded video processor

- first natively PCIE card

- added PCIE GART to memory controller

- NV43:

- added a thermal sensor to the GPU

- NV44:

- a new PCIE GART page table format

- 3d engine: ???

- NV44A:

- like NV44, but AGP instead of PCIE

Todo: more changes

#### Todo: figure out 3d engine changes

The GPUs are:

| pciid | GPU id   | GPU names     | vertex<br>shaders | pixel<br>shaders | ROPs | date      | notes                  |

|-------|----------|---------------|-------------------|------------------|------|-----------|------------------------|

| 004X  | 0x40/0x4 | 5 NV40/NV45/N | V468              | 16               | 16   | 14.04.200 | 4AGP                   |

| 021X  |          |               |                   |                  |      |           |                        |

| 00cX  | 0x41/0x4 | 2 NV41/NV42   | 5                 | 12               | 12   | 08.11.200 | 4                      |

| 014X  | 0x43     | NV43          | 3                 | 8                | 4    | 12.08.200 | 4                      |

| 016X  | 0x44     | NV44          | 3                 | 4                | 2    | 15.12.200 | 4TURBOCACHE            |

| 022X  | 0x4a     | NV44A         | 3                 | 4                | 2    | 04.04.200 | 5 AGP                  |

| 009X  | 0x47     | G70           | 8                 | 24               | 16   | 22.06.200 | 5                      |

| 01dX  | 0x46     | G72           | 3                 | 4                | 2    | 18.01.200 | 6TURBOCACHE            |

| 029X  | 0x49     | G71           | 8                 | 24               | 16   | 09.03.200 | 6                      |

| 039X  | 0x4b     | G73           | 8                 | 12               | 8    | 09.03.200 | 6                      |

| 024X  | 0x4e     | C51           | 1                 | 2                | 1    | 20.10.200 | 5 IGP, TURBOCACHE      |

| 03dX  | 0x4c     | MCP61         | 1                 | 2                | 1    | ??.06.200 | 6 IGP, TURBOCACHE      |

| 053X  | 0x67     | MCP67         | 1                 | 2                | 2    | 01.02.200 | 6IGP, TURBOCACHE       |

| 053X  | 0x68     | MCP68         | 1                 | 2                | 2    |           | 7 IGP, TURBOCACHE      |

| 07eX  | 0x63     | MCP73         | 1                 | 2                | 2    | ??.07.200 | 7 IGP, TURBOCACHE      |

| -     | 0x4d     | RSX           | ?                 | ?                | ?    | 11.11.200 | 6FlexIO bus interface, |

|       |          |               |                   |                  |      |           | used in PS3            |

Todo: all geometry information unverified

Todo: any information on the RSX?

It's not clear how NV40 is different from NV45, or NV41 from NV42, or MCP67 from MCP68 - they even share pciid ranges.

The NV4x IGPs actually have a memory controller as opposed to earlier ones. This controller still accesses only host memory, though.

As execution units can be disabled on NV40+ cards, these configs are just the maximum configs - a card can have just a subset of them enabled.

#### **Tesla family**

#### gpu-gen **Tesla**

The card where they redesigned everything. The most significant change was the redesigned memory subsystem, complete with a paging MMU [see *Tesla virtual memory*].

- G80:

- a new VM subsystem, complete with redesigned DMA objects

- RAMIN is gone, all structures can be placed arbitrarily in VRAM, and usually host memory memory as well

- all-new channel structure storing page tables, RAMFC, RAMHT, context pointers, and DMA objects

- PFIFO redesigned, PIO mode dropped

- PGRAPH redesigned: based on unified shader architecture, now supports running standalone computations, D3D10 support, unified 2d acceleration object

- display subsystem reinvented from scratch: a stub version of the old VGA-based one remains for VGA compatibility, the new one is not VGA based and is controlled by PFIFO-like DMA push buffers

- memory partitions tied directly to ROPs

- G84:

- redesigned channel structure with a new layout

- got rid of VP1 video decoding and VPE encoding support, but VPE decoder still exists

- added VP2 xtensa-based programmable video decoding and BSP engines

- removed restrictions on host memory access by rendering: rendering to host memory and using blocklinear textures from host are now ok

- added VM stats write support to PCOUNTER

- PEEPHOLE moved out of PBUS

- PFIFO\_BAR\_FLUSH moved out of PFIFO

- G98:

- introduced VP3 video decoding engines, and the falcon microcode with them

- got rid of VP2 video decoding

- G200:

- developped in parallel with G98

- VP2 again, no VP3

- PGRAPH rearranged to make room for more MPs/TPCs

- streamout enhancements [ARB\_transform\_feedback2]

- CUDA ISA 1.3: 64-bit g[] atomics, s[] atomics, voting, fp64 support

- MCP77:

- merged G200 and G98 changes: has both VP3 and new PGRAPH

- only CUDA ISA 1.2 now: fp64 support got cut out again

- GT215:

- a new revision of the falcon ISA

- a revision to VP3 video decoding, known as VP4. Adds MPEG-4 ASP support.

- added PDAEMON, a falcon engine meant to do card monitoring and power maanagement

- PGRAPH additions for D3D10.1 support

- added HDA audio codec for HDMI sound support, on a separate PCI function

- Added PCOPY, the dedicated copy engine

- Merged PSEC functionality into PVLD

- MCP89:

- added PVCOMP, the video compositor engine

The GPUs in this family are:

| core  | hda   | id   | name        | TPCs | MPs/TPC | PARTs | date       | notes |

|-------|-------|------|-------------|------|---------|-------|------------|-------|

| pciid | pciid |      |             |      |         |       |            |       |

| 019X  | -     | 0x50 | G80         | 8    | 2       | 6     | 08.11.2006 |       |

| 040X  | -     | 0x84 | G84         | 2    | 2       | 2     | 17.04.2007 |       |

| 042X  | -     | 0x86 | G86         | 1    | 2       | 2     | 17.04.2007 |       |

| 060X+ | -     | 0x92 | G92         | 8    | 2       | 4     | 29.10.2007 |       |

| 062X+ | -     | 0x94 | G94         | 4    | 2       | 4     | 29.07.2008 |       |

| 064X+ | -     | 0x96 | G96         | 2    | 2       | 2     | 29.07.2008 |       |

| 06eX+ | -     | 0x98 | G98         | 1    | 1       | 1     | 04.12.2007 |       |

| 05eX+ | -     | 0xa0 | G200        | 10   | 3       | 8     | 16.06.2008 |       |

| 084X+ | -     | 0xaa | MCP77/MCP78 | 1    | 1       | 1     | ??.06.2008 | IGP   |

| 086X+ | -     | 0xac | MCP79/MCP7A | 1    | 2       | 1     | ??.06.2008 | IGP   |

| 0caX+ | 0be4  | 0xa3 | GT215       | 4    | 3       | 2     | 15.06.2009 |       |

| 0a2X+ | 0be2  | 0xa5 | GT216       | 2    | 3       | 2     | 15.06.2009 |       |

| 0a6X+ | 0be3  | 0xa8 | GT218       | 1    | 2       | 1     | 15.06.2009 |       |

| 08aX+ | -     | 0xaf | MCP89       | 2    | 3       | 2     | 01.04.2010 | IGP   |

Like NV40, these are just the maximal numbers.

Todo: geometry information not verified for G94, MCP77

#### Fermi/Kepler/Maxwell/Pascal/Volta/Turing family

#### gpu-gen Fermi

The card where they redesigned everything again.

- GF100:

- redesigned PFIFO, now with up to 3 subfifos running in parallel

- redesigned PGRAPH:

- \* split into a central HUB managing everything and several GPCs doing all actual work

- \* GPCs further split into a common part and several TPCs

- \* using falcon for context switching

- \* D3D11 support

- redesigned memory controller

- \* split into three parts:

- · per-partition low-level memory controllers [PBFB]

- · per-partition middle memory controllers: compression, ECC, ... [PMFB]

- a single "hub" memory controller: VM control, TLB control, ... [PFFB]

- memory partitions, GPCs, TPCs have independent register areas, as well as "broadcast" areas that can be used to control all units at once

- second PCOPY engine

- redesigned PCOUNTER, now having multiple more or less independent subunits to monitor various parts of GPU

- redesigned clock setting

- ...

- GF119:

- a major revision to VP3 video decoding, now called VP5. vµc microcode removed.

- another revision to the falcon ISA, allowing 24-bit PC

- added PUNK1C3 falcon engine

- redesigned I2C bus interface

- redesigned PDISPLAY

- removed second PCOPY engine

- GF117:

- PGRAPH changes:

\* ???

#### gpu-gen Kepler

An upgrade to Fermi.

- GK104:

- redesigned PCOPY: the falcon controller is now gone, replaced with hardware control logic, partially in PFIFO

- an additional PCOPY engine

- PFIFO redesign a channel can now only access a single engine selected on setup, with PCOPY2+PGRAPH considered as one engine

- PGRAPH changes:

- \* subchannel to object assignments are now fixed

- \* m2mf is gone and replaced by a new p2mf object that only does simple upload, other m2mf functions are now PCOPY's responsibility instead

- \* the ISA requires explicit scheduling information now

- \* lots of setup has been moved from methods/registers into memory structures

\* ???

• GK110:

- PFIFO changes:

\* ???

- PGRAPH changes:

- \* ISA format change

\* ???

#### Todo: figure out PGRAPH/PFIFO changes

gpu-gen Maxwell

gpu-gen **Pascal**

gpu-gen **Volta**

gpu-gen Turing

GPUs in Fermi/Kepler/Maxwell/Pascal/Volta/Turing families:

| core  | hda   | usb      | id         | name   | GPCs | TPCs | PARTs | MCs | ZCULLs | PCOPYs | HEADs | UNK7 | P   |

|-------|-------|----------|------------|--------|------|------|-------|-----|--------|--------|-------|------|-----|

| pciid | pciid | pciid    | . <u>~</u> |        |      | /GPC |       | L   | /GPC   |        |       |      | /(  |

| 06cX+ | 0be5  | -        | 0xc0       | GF100  | 4    | 4    | 6     | [6] | [4]    | [2]    | [2]   | -    | † - |

| 0e2X+ | 0beb  | -        | 0xc4       | GF104  | 2    | 4    | 4     | [4] | [4]    | [2]    | [2]   | -    | -   |

| 120X+ | 0e0c  | -        | 0xce       | GF114  | 2    | 4    | 4     | [4] | [4]    | [2]    | [2]   | -    | -   |

| 0dcX+ | 0be9  | -        | 0xc3       | GF106  | 1    | 4    | 3     | [3] | [4]    | [2]    | [2]   | -    | -   |

| 124X+ | 0bee  | -        | 0xcf       | GF116  | 1    | 4    | 3     | [3] | [4]    | [2]    | [2]   | -    | -   |

| 0deX+ | 0bea  | -        | 0xc1       | GF108  | 1    | 2    | 1     | 2   | 4      | [2]    | [2]   | -    | -   |

| 108X+ | 0e09  | -        | 0xc8       | GF110  | 4    | 4    | 6     | [6] | [4]    | [2]    | [2]   | -    | _   |

| 104X* | 0e08  | -        | 0xd9       | GF119  | 1    | 1    | 1     | 1   | 4      | 1      | 2     | -    | -   |

| 1140  | -     | -        | 0xd7       | GF117  | 1    | 2    | 1     | 1   | 4      | 1      | -[4]  | -    | 1   |

| 118X* | 0e0a  | -        | 0xe4       | GK104  | 4    | 2    | 4     | 4   | 4      | 3      | 4     | -    | 1   |

| 0fcX* | 0e1b  | -        | 0xe7       | GK107  | 1    | 2    | 2     | 2   | 4      | 3      | 4     | -    | 1   |

| 11cX+ | 0e0b  | -        | 0xe6       | GK106  | 3    | 2    | 3     | 3   | 4      | 3      | 4     | -    | 1   |

| 100X+ | 0e1a  | -        | 0xf0       | GK110  | 5    | 3    | 6     | 6   | 4      | 3      | 4     | -    | 2   |

| 100X+ | 0e1a  | -        | 0xf1       | GK110B | 5    | 3    | 6     | 6   | 4      | 3      | 4     | -    | 2   |

| ????  | ????  | -        | ????       | GK210  | ?    | ?    | ?     | ?   | ?      | ?      | ?     | -    | ?   |

| 128X+ | 0e0f  | -        | 0x108      | GK208  | 1    | 2    | 1     | 1   | 4      | 3      | 4     | -    | 1   |

| 128X+ | 0e0f  | <u> </u> | 0x106      | GK208B | 1    | 2    | 1     | 1   | 4      | 3      | 4     | -    | 1   |

| -     | -     | -        | 0xea       | GK20A  | 1    | 1    | 1     | 1   | 4      | 3      | -[4]  | -    | 1   |

| 138X+ | 0fbc  | -        | 0x117      | GM107  | 1    | 5    | 2     | 2   | 4      | 3      | 4     | 1    | 2   |

| 134X+ | ????  | -        | 0x118      | GM108  | 1    | 3    | 1     | 1   | 4      | 3      | 4     | 0    | ?   |

| 13cX+ | 0fbb  | -        | 0x124      | GM204  | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?   |

| core  | hda   | usb   | id    | name  | GPCs | TPCs | PARTs | MCs | ZCULLs | PCOPYs | HEADs | UNK7 | P  |

|-------|-------|-------|-------|-------|------|------|-------|-----|--------|--------|-------|------|----|

| pciid | pciid | pciid |       |       |      | /GPC |       |     | /GPC   |        |       |      | /( |

| 17cX+ | 0fb0  | -     | 0x120 | GM200 | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 140X+ | 0fba  | -     | 0x126 | GM206 | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| -     | -     | -     | 0x12b | GM20B | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 158X# | ????  | -     | 0x130 | GP100 | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1b0X# | 10ef  | -     | 0x132 | GP102 | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1b8X# | 10f0  | -     | 0x134 | GP104 | 4    | 5    | 4     | 4   | 4      | 4      | 4     | 2    | ?  |

| 1c0X# | 10f1  | -     | 0x136 | GP106 | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1c8X# | 0fb9  | -     | 0x137 | GP107 | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1d0X# | 0fb8  | -     | 0x138 | GP108 | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 10e5* | -     | -     | 0x13b | GP10B | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1d8X# | 10f2  | -     | 0x140 | GV100 | 6    | 7    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| -     | -     | -     | 0x15b | GV11B | ?    | ?    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1e0X# | 10f7  | 1ad6  | 0x162 | TU102 | 6    | 6    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1e8X# | 10f8  | 1ad8  | 0x164 | TU104 | 6    | 4    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1f0X# | 10f9  | 1ada  | 0x166 | TU106 | 3    | 6    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 218X# | 1aeb  | -     | 0x168 | TU116 | 3    | 4    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

| 1f8X# |       | -     | 0x167 | TU117 | 2    | 4    | ?     | ?   | ?      | ?      | ?     | ?    | ?  |

#### Table 1 - continued from previous page

Todo: it is said that one of the GPCs [0th one] has only one TPC on GK106

**Todo:** what the fuck is GK110B? and GK208B?

**Todo:** GK210

Todo: GK20A

Todo: GM20x, GP10x

Todo: another design counter available on GM107, another 4 on GP10x

Todo: TU117 one of the GPCs has only three TPCs (so 7 in total, not 8)

### 2.2.3 Comparison table

| Name | GPU id | GPU generation | Release date [approximate] | Bus interface | PCI vendor id | PCI device IDs |

|------|--------|----------------|----------------------------|---------------|---------------|----------------|

| NV1  | -      | NV1            | 09.1995                    | Pci           | 0x104a        | 0x0008-0x0009  |

| Name  | GPU id | GPU generation | Release date [approximate] | Bus interface | PCI vendor id | PCI device IDs  |

|-------|--------|----------------|----------------------------|---------------|---------------|-----------------|

| NV3   | -      | NV3            | 04.1997                    | Pci           | 0x12d2        | 0x0018-0x0019 · |

| NV3T  | -      | NV3            | 23.02.1998                 | Pci           | 0x12d2        | 0x0018-0x0019 · |

| NV4   | -      | NV4            | 23.03.1998                 | Pci           | 0x10de        | 0x0020 ·        |

| NV5   | -      | NV4            | 15.03.1999                 | Pci           | 0x10de        | 0x0028-0x002b · |

| NV6   | -      | NV4            | 15.03.1999                 | Pci           | 0x10de        | 0x002c-0x002f · |

| NVA   | -      | NV4            | 08.09.1999                 | Pci           | 0x10de        | 0x00a0 -        |

| NV10  | 0x010  | Celsius        | 11.10.1999                 | Pci           | 0x10de        | 0x0100-0x0103 · |

| NV15  | 0x015  | Celsius        | 26.04.2000                 | Pci           | 0x10de        | 0x0150-0x0153   |

| NV1A  | 0x01a  | Celsius        | 04.06.2001                 | Pci           | 0x10de        | 0x01a0-0x01a3 · |

| NV11  | 0x011  | Celsius        | 28.06.2000                 | Pci           | 0x10de        | 0x0110-0x0113 · |

| NV17  | 0x017  | Celsius        | 06.02.2002                 | Pci           | 0x10de        | 0x0170-0x017f · |

| NV1F  | 0x01f  | Celsius        | 01.10.2002                 | Pci           | 0x10de        | 0x01f0-0x01ff · |

| NV18  | 0x018  | Celsius        | 25.09.2002                 | Pci           | 0x10de        | 0x0180-0x018f · |

| NV20  | 0x020  | Kelvin         | 27.02.2001                 | Pci           | 0x10de        | 0x0200-0x0203 · |

| NV2A  | 0x02a  | Kelvin         | 15.11.2001                 | Pci           | 0x10de        | 0x02a0-0x02a3 · |

| NV25  | 0x025  | Kelvin         | 06.02.2002                 | Pci           | 0x10de        | 0x0250-0x025f · |

| NV28  | 0x028  | Kelvin         | 20.01.2003                 | Pci           | 0x10de        | 0x0280-0x028f · |

| NV30  | 0x030  | Rankine        | 27.01.2003                 | Pci           | 0x10de        | 0x0300-0x030f · |

| NV35  | 0x035  | Rankine        | 12.05.2003                 | Pci           | 0x10de        | 0x0330-0x033f · |

| NV31  | 0x031  | Rankine        | 06.03.2003                 | Pci           | 0x10de        | 0x0310-0x031f · |

| NV36  | 0x036  | Rankine        | 23.10.2003                 | Pci           | 0x10de        | 0x0340-0x034f · |

| NV34  | 0x034  | Rankine        | 06.03.2003                 | Pci           | 0x10de        | 0x0320-0x032f · |

| NV40  | 0x040  | Curie          | 14.04.2004                 | Pci           | 0x10de        | 0x0040-0x004f · |

| NV45  | 0x045  | Curie          | 14.04.2004                 | Pci           | 0x10de        | 0x0040-0x004f · |

| NV41  | 0x041  | Curie          | 08.11.2004                 | Pcie          | 0x10de        | 0x00c0-0x00cf · |

| NV42  | 0x042  | Curie          | 08.11.2004                 | Pcie          | 0x10de        | 0x00c0-0x00cf · |

| NV43  | 0x043  | Curie          | 12.08.2004                 | Pcie          | 0x10de        | 0x0140-0x014f · |

| NV44  | 0x044  | Curie          | 15.12.2004                 | Pcie          | 0x10de        | 0x0160-0x016f · |

| NV44A | 0x04a  | Curie          | 04.04.2005                 | Pci           | 0x10de        | 0x0220-0x022f · |

| G70   | 0x047  | Curie          | 22.06.2005                 | Pcie          | 0x10de        | 0x0090-0x009f · |

| G72   | 0x046  | Curie          | 18.01.2006                 | Pcie          | 0x10de        | 0x01d0-0x01df · |

| G71   | 0x049  | Curie          | 09.03.2006                 | Pcie          | 0x10de        | 0x0290-0x029f · |

| G73   | 0x04b  | Curie          | 09.03.2006                 | Pcie          | 0x10de        | 0x0390-0x039f · |

| C51   | 0x04e  | Curie          | 20.10.2005                 | Igp           | 0x10de        | 0x0240-0x024f · |

| MCP61 | 0x04c  | Curie          | 06.2006                    | Igp           | 0x10de        | 0x03d0-0x03df · |

| MCP67 | 0x067  | Curie          | 01.02.2006                 | Igp           | 0x10de        | 0x0530-0x053f · |

| MCP68 | 0x068  | Curie          | 07.2007                    | Igp           | 0x10de        | 0x0530-0x053f · |

| MCP73 | 0x063  | Curie          | 07.2007                    | Igp           | 0x10de        | 0x07e0-0x07ef · |

| RSX   | 0x04d  | Curie          | 11.11.2006                 | FlexIO        | -             | - ·             |

| G80   | 0x050  | Tesla          | 08.11.2006                 | Pcie          | 0x10de        | 0x0190-0x019f · |

| G84   | 0x084  | Tesla          | 17.04.2007                 | Pcie          | 0x10de        | 0x0400-0x040f · |

| G86   | 0x086  | Tesla          | 17.04.2007                 | Pcie          | 0x10de        | 0x0420-0x042f · |

| G92   | 0x092  | Tesla          | 29.10.2007                 | Pcie          | 0x10de        | 0x0600-0x061f · |

| G94   | 0x094  | Tesla          | 29.07.2008                 | Pcie          | 0x10de        | 0x0620-0x063f · |

| G96   | 0x096  | Tesla          | 29.07.2008                 | Pcie          | 0x10de        | 0x0640-0x065f · |

| G98   | 0x098  | Tesla          | 04.12.2007                 | Pcie          | 0x10de        | 0x06e0-0x06ff · |

| G200  | 0x0a0  | Tesla          | 16.06.2008                 | Pcie          | 0x10de        | 0x05e0-0x05ff · |

| MCP77 | 0x0aa  | Tesla          | 06.2008                    | Igp           | 0x10de        | 0x0840-0x085f · |

| MCP79 | 0x0ac  | Tesla          | 06.2008                    | Igp           | 0x10de        | 0x0860-0x087f · |

| GT215 $0x0a3$ Tesla $15.06.2009$ Pcie $0x10de$ $0x0ca0-0x0cbf$ GT216 $0x0a5$ Tesla $15.06.2009$ Pcie $0x10de$ $0x0a20-0x0a3f$ GT218 $0x0a8$ Tesla $15.06.2009$ Pcie $0x10de$ $0x0a60-0x0a7f$ MCP89 $0x0af$ Tesla $01.04.2010$ Igp $0x10de$ $0x0a60-0x08bf$ GF100 $0x0c0$ Fermi $26.03.2010$ Pcie $0x10de$ $0x06c0-0x06df$ GF104 $0x0c4$ Fermi $12.07.2010$ Pcie $0x10de$ $0x0e20-0x0e3f$ GF114 $0x0ce$ Fermi $25.01.2011$ Pcie $0x10de$ $0x0dc0-0x0ddf$ GF106 $0x0c3$ Fermi $03.09.2010$ Pcie $0x10de$ $0x120-0x121f$ GF108 $0x0c1$ Fermi $03.09.2010$ Pcie $0x10de$ $0x1240-0x125f$ GF110 $0x0c8$ Fermi $07.12.2010$ Pcie $0x10de$ $0x10de-0x0dff$ GF119 $0x0d9$ Fermi $05.01.2011$ Pcie $0x10de$ $0x10de-0x10ff$ GF117 $0x0d7$ Fermi $05.01.2011$ Pcie $0x10de$ $0x10de-0x10ff$ GF117 $0x0d7$ Fermi $05.01.2011$ Pcie $0x10de$ $0x10de-0x10ff$ GF117 $0x0d7$ Fermi $05.01.2012$ Pcie $0x10de$ $0x10d-0x10ff$ GF117 $0x0d7$ Fermi $04.2012$ Pcie $0x10de$ $0x1140-0x11ff$ GK104 $0x0e4$ Kepler $22.03.2012$ Pcie $0x10de$ $0x1110-0x11bf$                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GT2180x0a8Tesla15.06.2009Pcie0x10de0x0a60-0x0a7fMCP890x0afTesla01.04.2010Igp0x10de0x08a0-0x08bfGF1000x0c0Fermi26.03.2010Pcie0x10de0x06c0-0x06dfGF1040x0c4Fermi12.07.2010Pcie0x10de0x0e20-0x0e3fGF1140x0ceFermi25.01.2011Pcie0x10de0x1200-0x121fGF1060x0c3Fermi03.09.2010Pcie0x10de0x0dc0-0x0ddfGF1160x0cfFermi15.03.2011Pcie0x10de0x1240-0x125fGF1080x0c1Fermi03.09.2010Pcie0x10de0x0de0-0x0dffGF1100x0c8Fermi05.01.2011Pcie0x10de0x10de-0x107fGF1190x0d9Fermi05.01.2011Pcie0x10de0x1040-0x107fGF1170x0d7Fermi04.2012Pcie0x10de0x1140-0x117fGK1040x0e4Kepler22.03.2012Pcie0x10de0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MCP890x0afTesla01.04.2010Igp0x10de0x08a0-0x08bfGF1000x0c0Fermi26.03.2010Pcie0x10de0x06c0-0x06dfGF1040x0c4Fermi12.07.2010Pcie0x10de0x0e20-0x0e3fGF1140x0ceFermi25.01.2011Pcie0x10de0x1200-0x121fGF1060x0c3Fermi03.09.2010Pcie0x10de0x0dc0-0x0ddfGF1160x0cfFermi15.03.2011Pcie0x10de0x1240-0x125fGF1080x0c1Fermi03.09.2010Pcie0x10de0x0de0-0x0dffGF1100x0c8Fermi07.12.2010Pcie0x10de0x10de-0x10ffGF1190x0d9Fermi05.01.2011Pcie0x10de0x1040-0x107fGF1170x0d7Fermi04.2012Pcie0x10de0x1140-0x117fGK1040x0e4Kepler22.03.2012Pcie0x10de0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GF100         0x0c0         Fermi         26.03.2010         Pcie         0x10de         0x06c0-0x06df           GF104         0x0c4         Fermi         12.07.2010         Pcie         0x10de         0x0e20-0x0e3f           GF114         0x0ce         Fermi         25.01.2011         Pcie         0x10de         0x1200-0x121f           GF106         0x0c3         Fermi         03.09.2010         Pcie         0x10de         0x0dc0-0x0ddf           GF116         0x0cf         Fermi         15.03.2011         Pcie         0x10de         0x0dc0-0x0ddf           GF108         0x0c1         Fermi         03.09.2010         Pcie         0x10de         0x0de0-0x0dff           GF110         0x0c8         Fermi         05.03.2011         Pcie         0x10de         0x0de0-0x0dff           GF110         0x0c8         Fermi         05.01.2011         Pcie         0x10de         0x1040-0x109f           GF117         0x0d7         Fermi         05.01.2011         Pcie         0x10de         0x1040-0x107f           GF117         0x0d7         Fermi         04.2012         Pcie         0x10de         0x1140-0x117f           GK104         0x0e4         Kepler         22.03.2012 <t< td=""></t<> |

| GF1040x0c4Fermi12.07.2010Pcie0x10de0x0e20-0x0e3fGF1140x0ceFermi25.01.2011Pcie0x10de0x1200-0x121fGF1060x0c3Fermi03.09.2010Pcie0x10de0x0dc0-0x0ddfGF1160x0cfFermi15.03.2011Pcie0x10de0x1240-0x125fGF1080x0c1Fermi03.09.2010Pcie0x10de0x0de0-0x0dffGF1100x0c8Fermi07.12.2010Pcie0x10de0x1080-0x109fGF1190x0d9Fermi05.01.2011Pcie0x10de0x1040-0x107fGF1170x0d7Fermi04.2012Pcie0x10de0x1140-0x117fGK1040x0e4Kepler22.03.2012Pcie0x10de0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GF1140x0ceFermi25.01.2011Pcie0x10de0x1200-0x121fGF1060x0c3Fermi03.09.2010Pcie0x10de0x0dc0-0x0ddfGF1160x0cfFermi15.03.2011Pcie0x10de0x1240-0x125fGF1080x0c1Fermi03.09.2010Pcie0x10de0x0de0-0x0dffGF1100x0c8Fermi07.12.2010Pcie0x10de0x0de0-0x0dffGF1190x0d9Fermi05.01.2011Pcie0x10de0x1040-0x107fGF1170x0d7Fermi04.2012Pcie0x10de0x1140-0x117fGK1040x0e4Kepler22.03.2012Pcie0x10de0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GF1060x0c3Fermi03.09.2010Pcie0x10de0x0dc0-0x0ddfGF1160x0cfFermi15.03.2011Pcie0x10de0x1240-0x125fGF1080x0c1Fermi03.09.2010Pcie0x10de0x0de0-0x0dffGF1100x0c8Fermi07.12.2010Pcie0x10de0x1080-0x109fGF1190x0d9Fermi05.01.2011Pcie0x10de0x1040-0x107fGF1170x0d7Fermi04.2012Pcie0x10de0x1140-0x117fGK1040x0e4Kepler22.03.2012Pcie0x10de0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GF1160x0cfFermi15.03.2011Pcie0x10de0x1240-0x125fGF1080x0c1Fermi03.09.2010Pcie0x10de0x0de0-0x0dffGF1100x0c8Fermi07.12.2010Pcie0x10de0x1080-0x109fGF1190x0d9Fermi05.01.2011Pcie0x10de0x1040-0x107fGF1170x0d7Fermi04.2012Pcie0x10de0x1140-0x117fGK1040x0e4Kepler22.03.2012Pcie0x10de0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GF108         0x0c1         Fermi         03.09.2010         Pcie         0x10de         0x0de0-0x0dff           GF110         0x0c8         Fermi         07.12.2010         Pcie         0x10de         0x1080-0x109f           GF119         0x0d9         Fermi         05.01.2011         Pcie         0x10de         0x1040-0x107f           GF117         0x0d7         Fermi         04.2012         Pcie         0x10de         0x1140-0x117f           GK104         0x0e4         Kepler         22.03.2012         Pcie         0x10de         0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GF1100x0c8Fermi07.12.2010Pcie0x10de0x1080-0x109fGF1190x0d9Fermi05.01.2011Pcie0x10de0x1040-0x107fGF1170x0d7Fermi04.2012Pcie0x10de0x1140-0x117fGK1040x0e4Kepler22.03.2012Pcie0x10de0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GF119         0x0d9         Fermi         05.01.2011         Pcie         0x10de         0x1040-0x107f           GF117         0x0d7         Fermi         04.2012         Pcie         0x10de         0x1140-0x117f           GK104         0x0e4         Kepler         22.03.2012         Pcie         0x10de         0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GF117         0x0d7         Fermi         04.2012         Pcie         0x10de         0x1140-0x117f           GK104         0x0e4         Kepler         22.03.2012         Pcie         0x10de         0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GK104         0x0e4         Kepler         22.03.2012         Pcie         0x10de         0x1180-0x11bf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GK107         0x0e7         Kepler         24.04.2012         Pcie         0x10de         0x0fc0-0x0fff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GK106         0x0e6         Kepler         22.04.2012         Pcie         0x10de         0x11c0-0x11ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GK110         0x0f0         Kepler         21.02.2013         Pcie         0x10de         0x1000-0x103f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GK110B         0x0f1         Kepler         07.11.2013         Pcie         0x10de         0x1000-0x103f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |