# TMS320DM35x Digital Media System-on-Chip (DMSoC) Video Processing Front End (VPFE)

# Reference Guide

Literature Number: SPRUF71A

December 2007 – Revised June 2008

## **Contents**

| Pref | ace     |                                                             | . 17       |

|------|---------|-------------------------------------------------------------|------------|

| 1    | Video   | Processing Front End Overview                               | 20         |

|      | 1.1     | Purpose of the Video Processing Front End                   | . 21       |

|      | 1.2     | Features                                                    | . 22       |

|      | 1.3     | Functional Block Diagram                                    | . 25       |

|      | 1.4     | Supported Use Case Statement                                | . 25       |

|      | 1.5     | Industry Standard(s) Compliance Statement                   | . 26       |

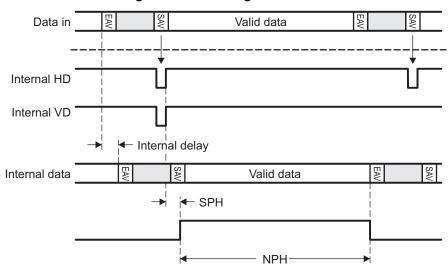

| 2    | VPFE/   | ISP I/O Interfacing                                         | 26         |

|      | 2.1     | Parallel Generic Interface Configuration (RAW)              | . 27       |

|      | 2.2     | ITU-R BT.656 Interface Configuration                        | . 32       |

|      | 2.3     | Generic YCbCr Interface Configuration                       | . 35       |

|      | 2.4     | VPFE I/O Multiplexing                                       | . 37       |

| 3    | VPFE/   | ISP Integration                                             | 40         |

|      | 3.1     | Clocking, Reset and Power Management Scheme                 | . 40       |

|      | 3.2     | Hardware Requests                                           | . 41       |

|      | 3.3     | VPSS Top-Level Register Mapping Summary                     | . 42       |

|      | 3.4     | VPFE/ISP Top-Level Signal Interaction                       | . 42       |

| 4    | VPFE/   | ISP Functional Description                                  | 43         |

|      | 4.1     | CCD/CMOS Controller (CCDC)                                  | . 43       |

|      | 4.2     | Image Pipe Interface (IPIPEIF)                              | . 56       |

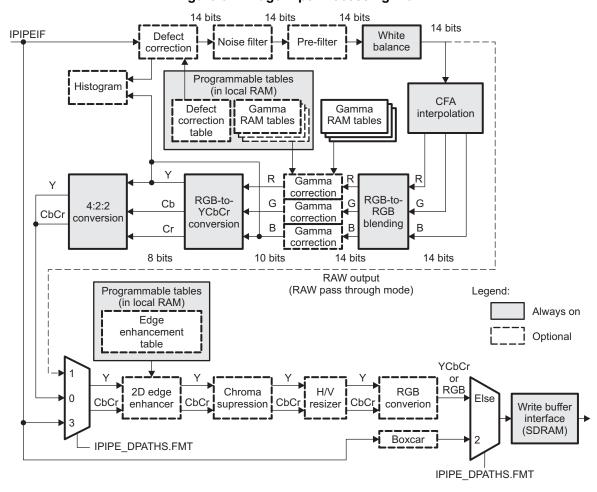

|      | 4.3     | Image Pipe (IPIPE)                                          | . 60       |

|      | 4.4     | Statistics Collection - Hardware 3A (H3A)                   | . 81       |

|      | 4.5     | VPFE Arbitration and Data Transfer Control (VPSSBL)         | . 81       |

| 5    | Progra  | amming Model                                                | 83         |

|      | 5.1     | Setup for Typical Configuration                             | . 83       |

|      | 5.2     | Resetting the Camera Subsystem                              | . 83       |

|      | 5.3     | Configuring the Clocks and the Control Signals              | . 83       |

|      | 5.4     | Programming the CCD/CMOS Controller (CCDC)                  | . 83       |

|      | 5.5     | Programming the Image Pipe Interface (IPIPEIF)              | . 88       |

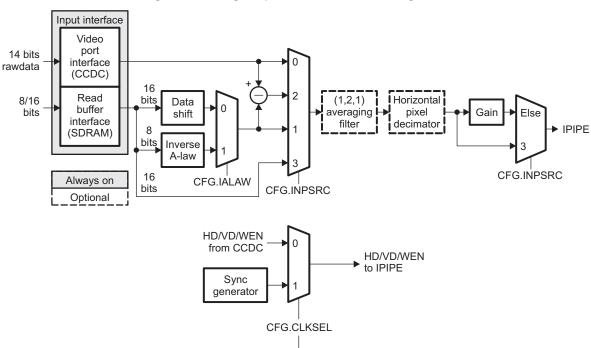

|      | 5.6     | Programming the Image Pipe (IPIPE)                          | . 91       |

|      | 5.7     | Programming the Hardware 3A (H3A)                           | 108        |

|      | 5.8     | Programming the Buffer Logic (VPSSBL and VPSSCLK Registers) | 111        |

| 6    | Regis   | ters                                                        | 113        |

|      | 6.1     | CCD Controller (CCDC) Registers                             | 113        |

|      | 6.2     | Image Pipe Input Interface Registers (IPIPEIF)              | 156        |

|      | 6.3     | Image Pipe Registers (IPIPE)                                | 164        |

|      | 6.4     | Hardware 3A Registers (H3A)                                 | 239        |

|      | 6.5     | VPSS Buffer Logic Registers (VPSSBL)                        | 262        |

|      | 6.6     | VPSS Clock Control Registers (VPSSCLK)                      | 269        |

| App  | endix A | Revision History                                            | <b>271</b> |

## List of Figures

| 1  | Functional Block Diagram                                        |    |

|----|-----------------------------------------------------------------|----|

| 2  | Video Processing Subsystem (VPSS) Block Diagram                 |    |

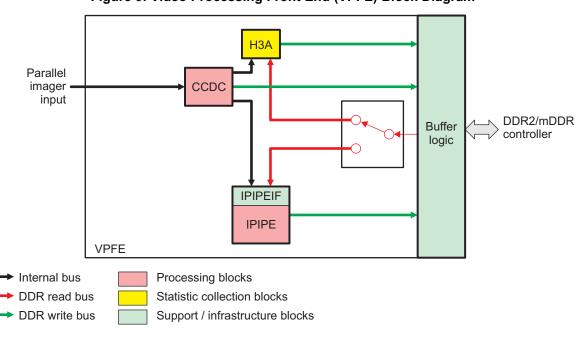

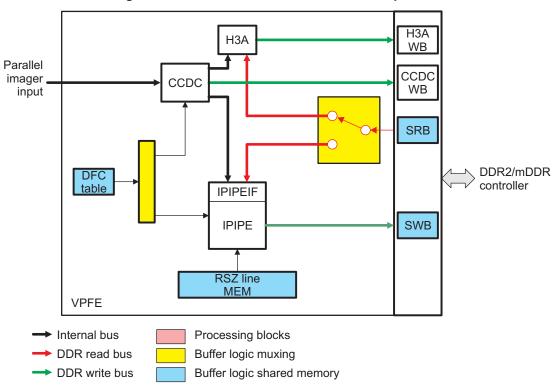

| 3  | Video Processing Front End (VPFE) Block Diagram and Data Flows  |    |

| 4  | Raw Mode Timing Diagram                                         | 31 |

| 5  | DDR2/mDDR controller Output Format                              | 31 |

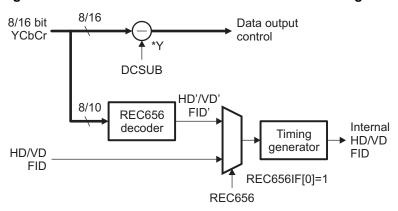

| 6  | BT.656 Signal Interface                                         | 33 |

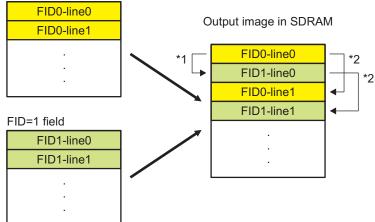

| 7  | BT.656 Mode Data Format in SDRAM                                | 34 |

| 8  | Pin Mux 0 Register (PINMUX0)                                    | 38 |

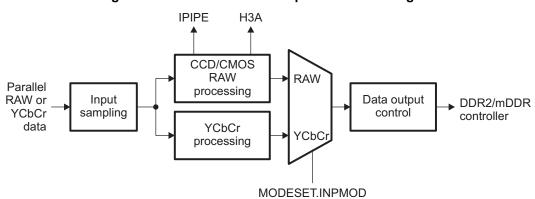

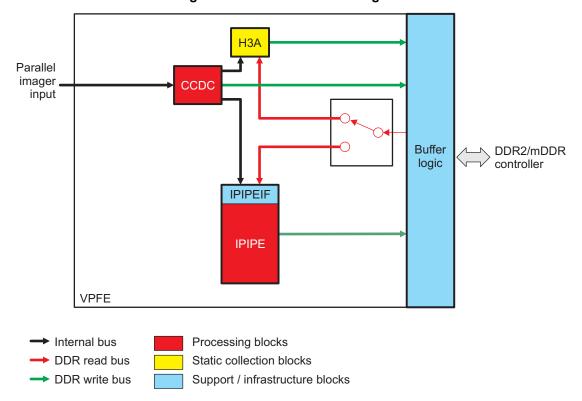

| 9  | Video Processing Front End (VPFE) Block Diagram                 |    |

| 10 | CCD Controller – Top Level Block Diagram                        |    |

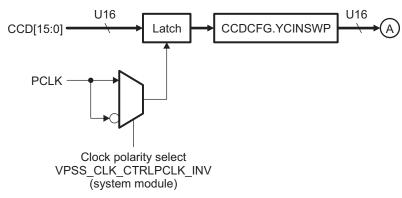

| 11 | CCD Controller – Input Formatting                               |    |

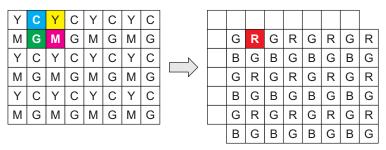

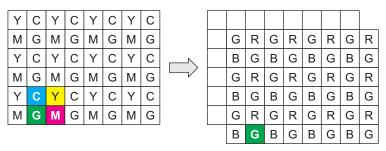

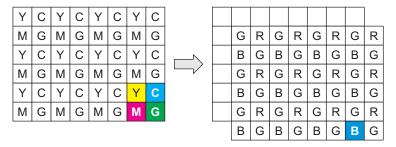

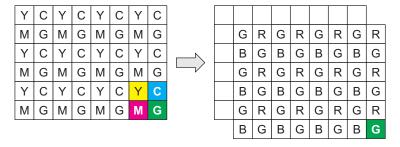

| 12 | CCD Controller Color Patterns                                   |    |

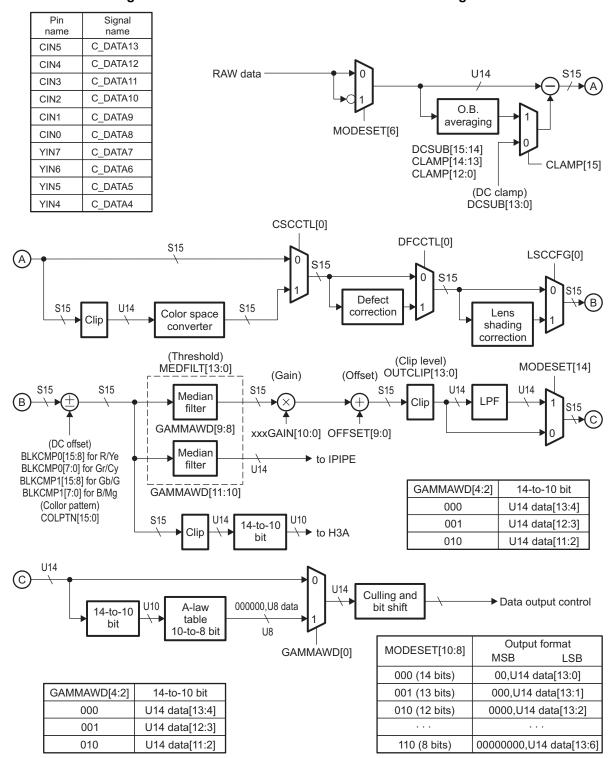

| 13 | CCD/CMOS Controller RAW Data Processing Flow                    |    |

| 14 | CCD Controller Optical Black Averaging and Application          |    |

| 15 | Color Space Converter Functional Block Diagram                  |    |

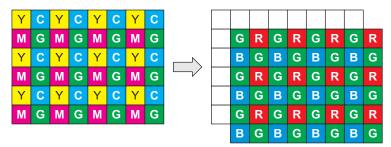

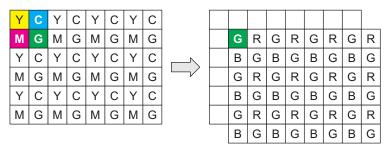

| 16 | Color Space Converter Operation.                                |    |

| 17 | Color Space Converter Operation.                                |    |

| 18 | Color Space Conversion                                          |    |

| 19 | First Pixel/First Line Generation                               |    |

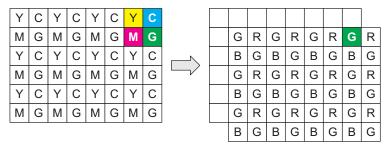

| 20 | Second Pixel/First Line Generation                              |    |

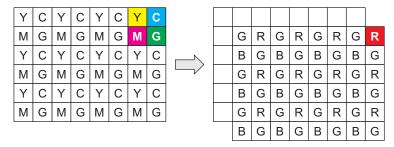

| 21 | Second Last Pixel/First Line Generation                         |    |

| 22 | Last Pixel/First Line Generation                                |    |

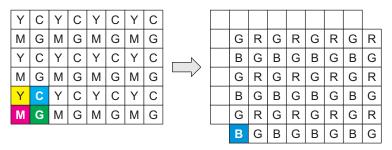

| 23 | First Pixel/Last Line Generation                                |    |

| 24 | Second Pixel/Last Line Generation                               |    |

| 25 | Second Last Pixel/Last Line Generation                          |    |

| 26 | Last Pixel/Last Line Generation                                 |    |

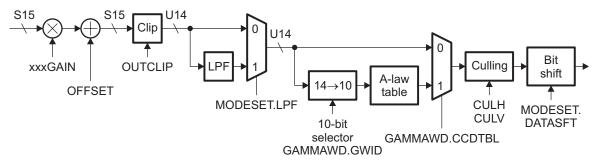

| 27 | Output Formatter Functional Model                               |    |

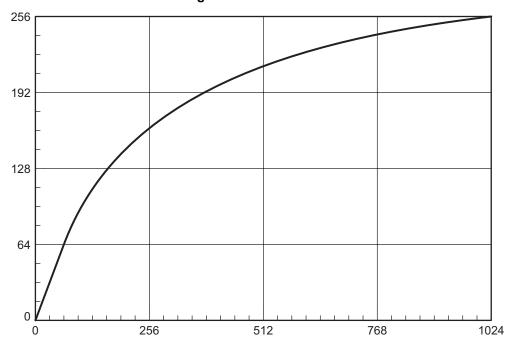

| 28 | A-Law Table                                                     |    |

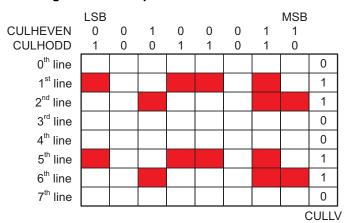

| 29 | Example for Decimation Pattern                                  |    |

| 30 | SDRAM Output Format                                             |    |

| 31 | CCD/CMOS Controller YCbCr Data Processing Flow.                 |    |

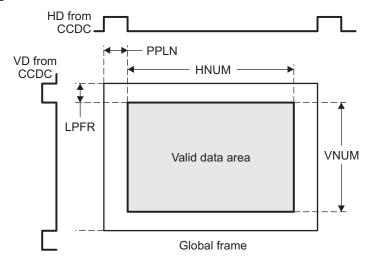

| 32 | Frame Image Format Conversion                                   |    |

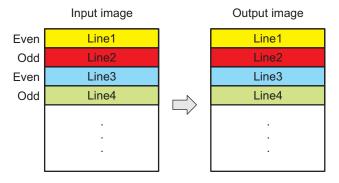

| 33 | Example Formats of Input and Output Image                       |    |

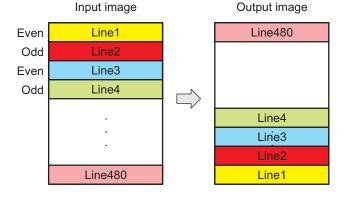

| 34 | Image Pipe Interface Processing Flow                            |    |

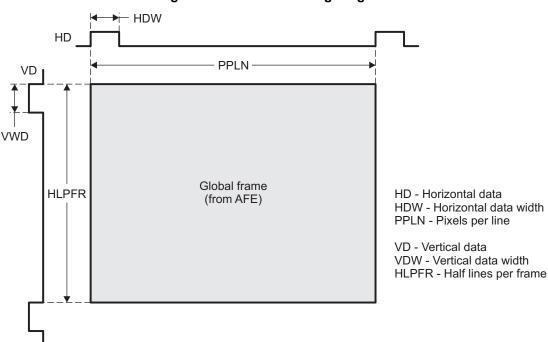

| 35 | Global Frame Definition in SDRAM Input Modes (except Darkframe) |    |

| 36 | Global Frame Definition in Darkframe Subtract Mode              |    |

| 37 | Image Pipe Processing Flow                                      |    |

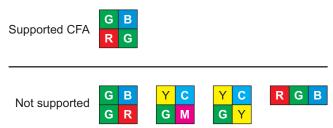

| 38 | CFA Arrangements                                                |    |

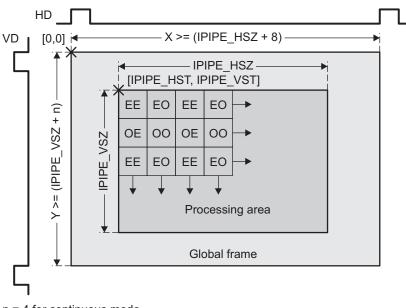

| 39 | Processing Area Within Global Frame                             |    |

| 40 | Defect Information Packet                                       |    |

| 41 | Numbering in Defect Correction Algorithm                        |    |

| 42 | Defect Correction Functional Model                              |    |

| 43 | Mirroring in Defect Correction and Noise Filter.                |    |

| 44 | Noise Filter Array                                              |    |

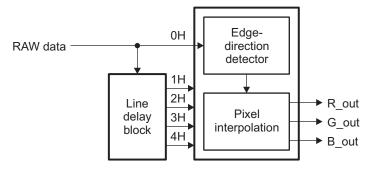

| 45 | CFA Interpolation Functional Model                              |    |

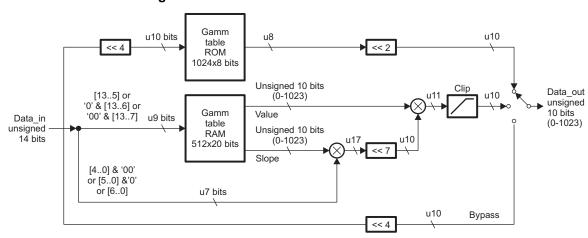

| 46 | Gamma Correction Functional Model                               |    |

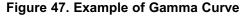

| 47 | Example of Gamma Curve                                          |    |

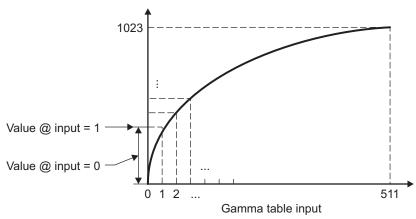

| 48 | ROM Gamma Table.                                                |    |

| 49 | RGB2YCbCr Conversion Functional Model                           |    |

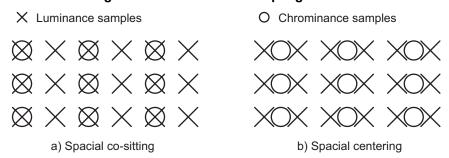

| 50 | Chroma Sub-Sampling Position                                    |    |

| 51 | 4:2:2 Conversion Functional Model                               |    |

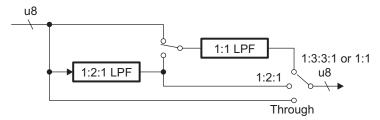

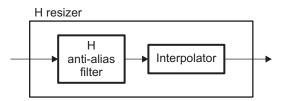

| 52 | Horizontal Resize Functional Model                              |    |

|    |                                                                 |    |

| 53       | Output Interface Functional Model                                       |     |

|----------|-------------------------------------------------------------------------|-----|

| 54       |                                                                         |     |

| 55<br>50 | Linear Buffer                                                           |     |

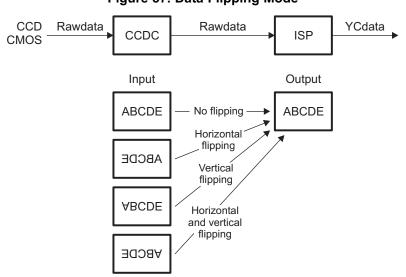

| 56       | Ring Buffer  Data Flipping Mode                                         |     |

| 57       | 11 0                                                                    |     |

| 58       | Write Start Address at Each Flipping Mode                               |     |

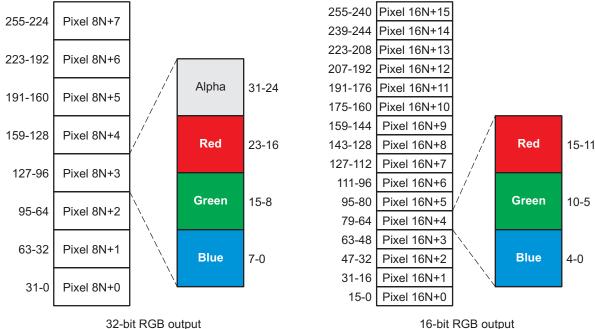

| 59       | Output Data Format to SDRAM                                             |     |

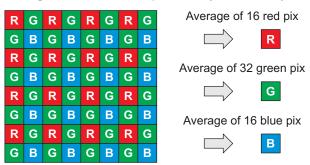

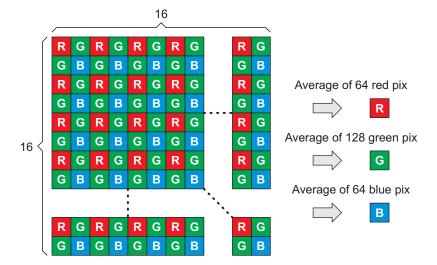

| 60       | Boxcar Operation (8 × 8 block)                                          |     |

| 61       | Boxcar Data Packing in SDRAM                                            |     |

| 62       | Histogram Processing Flow                                               |     |

| 63       | Region Priority                                                         |     |

| 64<br>65 | VPFE Shared Memories and Multiplexers                                   |     |

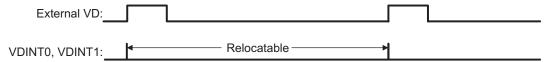

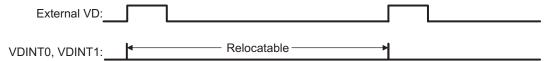

| 65<br>66 | VPFE Data Flow Diagram  VDINT0/VDINT1 Interrupt Behavior When VDPOL = 0 |     |

| 66       | ·                                                                       |     |

| 67       | VDINT0/VDINT1 Interrupt Behavior When VDPOL = 1                         |     |

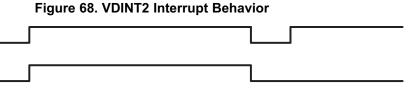

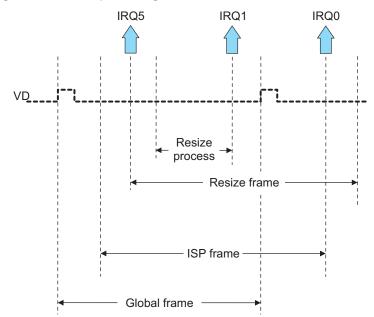

| 68       | Interrupt Timing When Resized Area = Resize Frame                       |     |

| 69<br>70 | Interrupt Timing When Resized Area < Resize Frame                       |     |

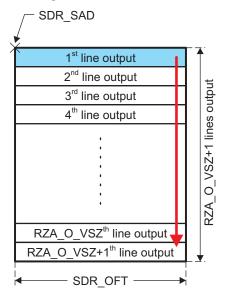

| 70<br>71 | Lateral Overhead Pixels                                                 |     |

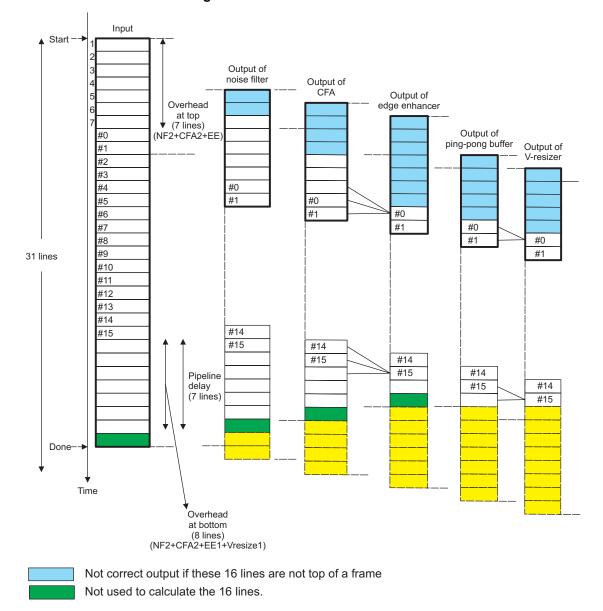

| 71<br>72 | Vertical Overhead Pixels                                                |     |

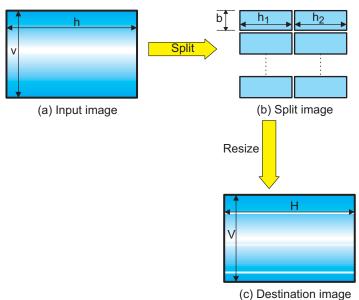

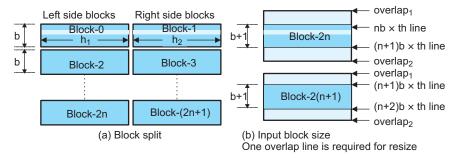

| 72<br>73 | Frame Division Mode - V                                                 |     |

| 73<br>74 | Register Settings for Frame Division Mode - V                           |     |

| 74<br>75 | Frame Division Mode - H                                                 |     |

| 75<br>76 | Blocks in Frame Division Mode - H                                       |     |

| 70<br>77 | Register Settings for Frame Division Mode - H                           |     |

| 77<br>78 | Register Settings for Frame Division Mode - H                           |     |

| 70<br>79 | Memory Settings for Frame Division Mode - H                             |     |

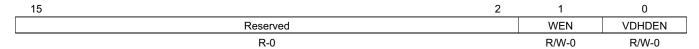

| 80       | Synchronization Enable Register (SYNCEN)                                |     |

| 81       | Mode Setup Register (MODESET)                                           |     |

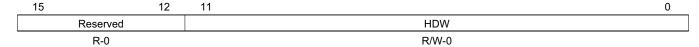

| 82       | HD Pulse Width Register (HDWIDTH)                                       |     |

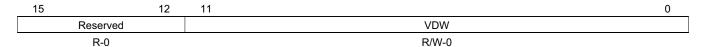

| 83       | VD Pulse Width Register (VDWIDTH)                                       |     |

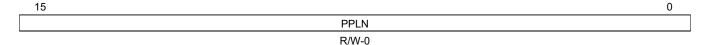

| 84       | Pixels Per Line Register (PPLN)                                         |     |

| 85       | Lines Per Frame Register (LPFR)                                         |     |

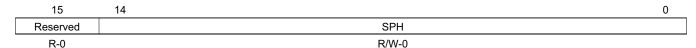

| 86       | Start Pixel Horizontal Register (SPH)                                   |     |

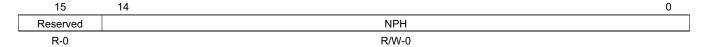

| 87       | Number of Pixels Horizontal Register (NPH)                              |     |

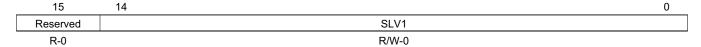

| 88       | Start Line Vertical - Field 0 Register (SLV0)                           |     |

| 89       | Start Line Vertical - Field 0 Register (SLV0)                           |     |

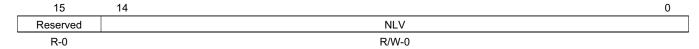

| 90       | Number of Lines Vertical Register (NLV)                                 |     |

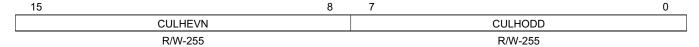

| 91       | Culling Horizontal Register (CULH)                                      |     |

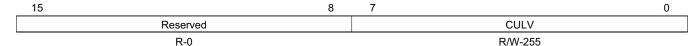

| 92       | Culling Vertical Register (CULV)                                        |     |

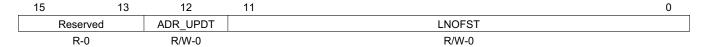

| 93       | Horizontal Size Register (HSIZE)                                        |     |

| 94       | SDRAM Line Offset Register (SDOFST)                                     |     |

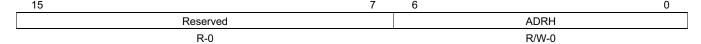

| 95       | SDRAM Address - High Register (STADRH)                                  |     |

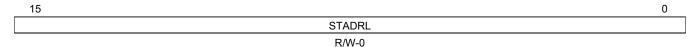

| 96       | SDRAM Address - Low Register (STADRL)                                   |     |

| 97       | CCD Data Clamping Register (CLAMP)                                      |     |

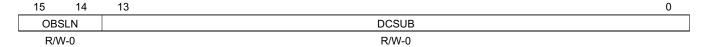

| 98       | DC Clamp Register (DCSUB)                                               |     |

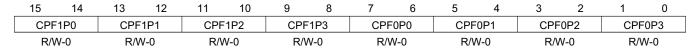

| 99       | CCD Color Pattern Register (COLPTN)                                     |     |

| 100      |                                                                         | 129 |

| 101      |                                                                         | 129 |

| 102      |                                                                         | 130 |

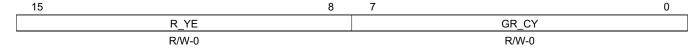

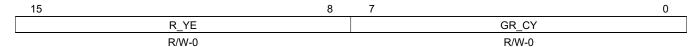

| 103      | CCD Gain Adjustment - R/Ye Register (RYEGAIN)                           |     |

| 104      | CCD Gain Adjustment - Gr/Cy Register (GRCYGAIN)                         |     |

| 105      | CCD gain adjustment - Gb/G register (GBGGAIN).                          |     |

| 106 | , , ,                                                           |     |

|-----|-----------------------------------------------------------------|-----|

| 107 | ,                                                               |     |

| 108 | Output Clipping Value Register (OUTCLIP)                        | 133 |

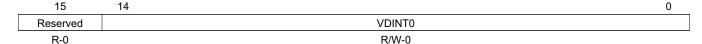

| 109 | VD Interrupt #0 Register (VDINT0)                               | 133 |

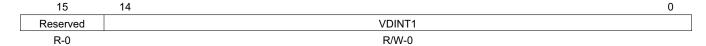

| 110 | VD Interrupt #1 Register (VDINT1)                               | 133 |

| 111 | Gamma Correction Settings Register (GAMMAWD)                    | 134 |

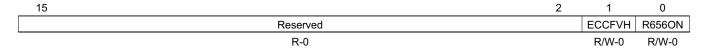

| 112 | REC656 Control Register (REC656IF)                              | 135 |

| 113 | CCD Configuration Register (CCDCFG)                             | 136 |

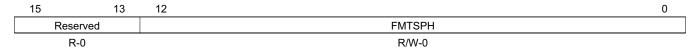

| 114 | Start Pixel Horizontal Register (FMTSPH)                        | 137 |

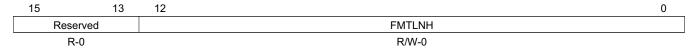

| 115 | Number Of Pixels Register (FMTLNH)                              | 137 |

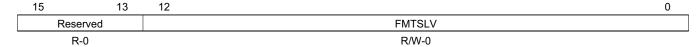

| 116 | Start Line Vertical Register (FMTSLV)                           | 138 |

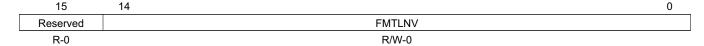

| 117 | Number of Lines Register (FMTLNV)                               | 138 |

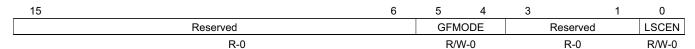

| 118 | Lens Shading Correction Configuration 1 Register (LSCCFG1)      | 139 |

| 119 | Lens Shading Correction Configuration 2 Register (LSCCFG2)      | 140 |

| 120 | Lens Shading Correction - Center Position (H0) Register (LSCH0) | 141 |

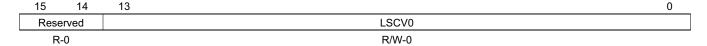

| 121 | Lens Shading Correction - Center Position (V0) Register (LSCV0) | 141 |

| 122 |                                                                 |     |

| 123 |                                                                 |     |

| 124 |                                                                 |     |

| 125 |                                                                 |     |

| 126 |                                                                 |     |

| 127 |                                                                 |     |

| 128 | · , , , , , , , , , , , , , , , , , , ,                         |     |

| 129 |                                                                 |     |

| 130 |                                                                 |     |

| 131 |                                                                 |     |

| 132 |                                                                 |     |

| 133 |                                                                 |     |

| 134 |                                                                 |     |

| 135 |                                                                 |     |

| 136 | ,                                                               |     |

| 137 |                                                                 |     |

| 138 |                                                                 |     |

| 139 |                                                                 |     |

| 140 |                                                                 |     |

| 141 |                                                                 |     |

| 142 |                                                                 |     |

| 143 |                                                                 |     |

| 144 |                                                                 |     |

| 145 |                                                                 |     |

| 146 |                                                                 |     |

| 147 |                                                                 |     |

| 148 |                                                                 |     |

| 149 |                                                                 |     |

| 150 |                                                                 |     |

| 151 |                                                                 |     |

| 151 |                                                                 |     |

| 153 |                                                                 |     |

| 154 |                                                                 |     |

| 155 |                                                                 |     |

| 156 |                                                                 |     |

| 157 |                                                                 |     |

| 158 |                                                                 |     |

| 100 | inpuroutput bata i atiis Negistei (ii ii L_bi ATIIO)            | 170 |

| 159 | Color Pattern Register (IPIPE_COLPAT)                              |     |

|-----|--------------------------------------------------------------------|-----|

| 160 | Vertical Start Position Register (IPIPE_VST)                       | 172 |

| 161 | Vertical Processing Size Register (IPIPE_VSZ)                      | 172 |

| 162 | Horizontal Start Position Register (IPIPE_HST)                     | 173 |

| 163 | Horizontal Processing Size Register (IPIPE_HSZ)                    | 173 |

| 164 | ARM Gated Clock Control Register (GCL_ARM)                         | 174 |

| 165 | CCD Gated Clock Control Register (GCL_CCD)                         | 174 |

| 166 | SDR Gated Clock Control Register (GCL_SDR)                         |     |

| 167 | Internal Table Selection Register (RAM_MODE)                       | 177 |

| 168 | Address Register (RAM_ADR)                                         | 178 |

| 169 | Write Data Register (RAM_WDT)                                      | 178 |

| 170 | Read Data Register (RAM_RDT)                                       | 178 |

| 171 | Interrupt Enable Register (IRQ_EN)                                 | 179 |

| 172 | Interval of IRQ-2 Register (IRQ_RZA)                               | 180 |

| 173 | Interval of IRQ-3 Register (IRQ_RZB)                               | 180 |

| 174 | Defect Correction Enable Register (DFC_EN)                         | 181 |

| 175 | Copy Method Selection (from Top or from Bottom) Register (DFC_SEL) | 181 |

| 176 | Start Address in LUT Register (DFC_ADR)                            |     |

| 177 | Number of Available Entries in LUT Register (DFC_SIZ)              | 182 |

| 178 | 2D Noise Filter Enable Register (D2F_EN)                           |     |

| 179 | Noise Filter Configuration Register (D2F_CFG)                      |     |

| 180 | Noise Filter LUT Values (Threshold) Register (D2F_THR[32])         | 184 |

| 181 | Noise Filter LUT Values (Intensity) Register (D2F_STR[32])         |     |

| 182 | PreFilter Enable Register (PRE_EN)                                 |     |

| 183 | PreFilter Type Register (PRE_TYP)                                  | 185 |

| 184 | Shift Value of Adaptive Gain Register (PRE_SHF)                    |     |

| 185 | Constant Gain or Adaptive Gain Slope Register (PRE_GAIN)           | 186 |

| 186 | Threshold G Register (PRE_THR_G)                                   | 187 |

| 187 | Threshold B Register (PRE_THR_B)                                   | 187 |

| 188 | Threshold 1 Register (PRE_THR_1)                                   | 188 |

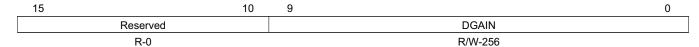

| 189 | Digital Gain Register (WB2_DGN)                                    | 188 |

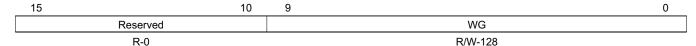

| 190 | White Balance Gain (Red) Register (WB2_WG_R)                       | 189 |

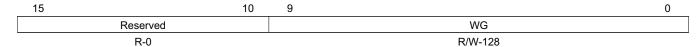

| 191 | White Balance Gain (Gr) Register (WB2_WG_GR)                       | 189 |

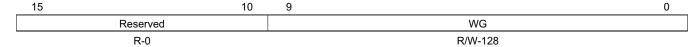

| 192 | White Balance Gain (Gb) Register (WB2_WG_GB)                       | 190 |

| 193 | White Balance Gain (Blue) Register (WB2_WG_B)                      | 190 |

| 194 | Matrix Coefficient RR Register (RGB_MUL_RR)                        | 191 |

| 195 | Matrix Coefficient GR Register (RGB_MUL_GR)                        | 191 |

| 196 | Matrix Coefficient BR Register (RGB_MUL_BR)                        | 192 |

| 197 | Matrix Coefficient RG Register (RGB_MUL_RG)                        | 192 |

| 198 | Matrix Coefficient GG Register (RGB_MUL_GG)                        | 193 |

| 199 | Matrix Coefficient BG Register (RGB_MUL_BG)                        | 193 |

| 200 | Matrix Coefficient RB Register (RGB_MUL_RB)                        | 194 |

| 201 | Matrix Coefficient GB Register (RGB_MUL_GB)                        | 194 |

| 202 | Matrix Coefficient BB Register (RGB_MUL_BB)                        | 195 |

| 203 | R Output Offset Register (RGB_OFT_OR)                              | 195 |

| 204 | G Output Offset Register (RGB_OFT_OG)                              | 196 |

| 205 | B Output Offset Register (RGB_OFT_OB)                              | 196 |

| 206 | Gamma Correction Configuration Register (GMM_CFG)                  | 197 |

| 207 | Luminance Adjustment (Contrast and Brightness) Register (YCC_ADJ)  | 198 |

| 208 | Matrix Coefficient RY Register (YCC_MUL_RY)                        | 198 |

| 209 | Matrix Coefficient GY Register (YCC_MUL_GY)                        | 199 |

| 210 | Matrix Coefficient BY Register (YCC_MUL_BY)                        | 199 |

| 211 | Matrix Coefficient RCb Register (YCC_MUL_RCB)                      | 200 |

| 212 | Matrix Coefficient GCb Register (YCC_MUL_GCB)                         | 200 |

|-----|-----------------------------------------------------------------------|-----|

| 213 | Matrix Coefficient BCb Register (YCC_MUL_BCB)                         | 201 |

| 214 | Matrix Coefficient RCr Register (YCC_MUL_RCR)                         | 201 |

| 215 | Matrix Coefficient GCr Register (YCC_MUL_GCR)                         | 202 |

| 216 | Matrix Coefficient BCr Register (YCC_MUL_BCR)                         | 202 |

| 217 | Y Output Offset Register (YCC_OFT_Y)                                  |     |

| 218 | Cb Output Offset Register (YCC_OFT_CB)                                |     |

| 219 | Cr Output Offset Register (YCC_OFT_CR)                                |     |

| 220 | Saturation (Luminance Minimum) Register (YCC_Y_MIN)                   |     |

| 221 | Saturation (Luminance Maximum) Register (YCC_Y_MAX)                   |     |

| 222 | Saturation (Chrominance Minimum) Register (YCC_C_MIN)                 |     |

| 223 | Saturation (Chrominance Maximum) Register (YCC C MAX)                 |     |

| 224 | Chrominance Position (for 422 Down Sampler) Register (YCC_PHS)        |     |

| 225 | Edge Enhancer Enable Register (YEE_EN)                                |     |

| 226 | MedianNR Enable Register (YEE_EMF)                                    |     |

| 227 | HPF Shift Length Register (YEE_SHF)                                   |     |

| 228 | HPF Coefficient 00 Register (YEE_MUL_00)                              |     |

| 229 | HPF Coefficient 01 Register (YEE_MUL_01)                              |     |

|     |                                                                       |     |

| 230 | HPF Coefficient 40 Register (YEE_MUL_02)                              |     |

| 231 | HPF Coefficient 10 Register (YEE_MUL_10)                              |     |

| 232 | HPF Coefficient 11 Register (YEE_MUL_11)                              |     |

| 233 | HPF Coefficient 12 Register (YEE_MUL_12)                              |     |

| 234 | HPF Coefficient 20 Register (YEE_MUL_20)                              |     |

| 235 | HPF Coefficient 21 Register (YEE_MUL_21)                              |     |

| 236 | HPF Coefficient 22 Register (YEE_MUL_22)                              |     |

| 237 | Fault Color Suppression Enable Register (FCS_EN)                      |     |

| 238 | Type selection of HPF Register (FCS_TYP)                              |     |

| 239 | Down Shift Size (HPF) Register (FCS_SHF_Y)                            |     |

| 240 | Down Shift Size (GAIN) Register (FCS_SHF_C)                           |     |

| 241 | Threshold Register (FCS_THR)                                          |     |

| 242 | Intensity Register (FCS_SGN)                                          |     |

| 243 | Lower Limit of Chroma Gain Register (FCS_LTH)                         |     |

| 244 | Processing Mode Register (RSZ_SEQ)                                    |     |

| 245 | Vertical Anti aliasing Filter Register (RSZ_AAL)                      |     |

| 246 | Resizer Enable Register (RSZ_EN)                                      |     |

| 247 | One Shot Mode Register (RSZ_MODE)                                     |     |

| 248 | Vertical Start Position of the Input Register (RSZ_I_VST)             |     |

| 249 | Vertical Size of the Input Register (RSZ_I_VSZ)                       |     |

| 250 | Horizontal Start Position of the Input Register (RSZ_I_HST)           |     |

| 251 | Vertical Size of the Output Register (RSZ_O_VSZ)                      |     |

| 252 | Horizontal Start Position of the Output Register (RSZ_O_HST)          |     |

| 253 | Horizontal Size of the Output Register (RSZ_O_HSZ)                    |     |

| 254 | Initial Phase of Vertical Resizing Process Register (RSZ_V_PHS)       |     |

| 255 | Phase of Last Value in Previous Resize Process Register (RSZ_V_PHS_0) | 222 |

| 256 | Vertical Resize Parameter Register (RSZ_V_DIF)                        | 222 |

| 257 | Actual Number of Output Lines Register (RSZ_V_SIZ_O)                  | 223 |

| 258 | Initial Phase of Horizontal Resizing Process Register (RSZ_H_PHS)     | 223 |

| 259 | Horizontal Resize Parameter Register (RSZ_H_DIF)                      | 224 |

| 260 | Interpolation Method for Horizontal Rescaling Register (RSZ_H_TYP)    | 224 |

| 261 | Selection of Horizontal LPF Intensity Register (RSZ_H_LSE)            |     |

| 262 | Horizontal LPF Intensity Register (RSZ_H_LPF)                         |     |

| 263 | RGB Output Enable Register (RSZ_RGB_EN)                               |     |

| 264 | RGB Output Bit Mode (32 or 16 bit) Register (RSZ_RGB_TYP)             |     |

|     |                                                                       |     |

| 265 | YC422 to YC444 Conversion Method Register (RSZ_RGB_BLD)                        | 227 |

|-----|--------------------------------------------------------------------------------|-----|

| 266 | SDRAM Base Address MSB Register (RSZ_SDR_BAD_H)                                | 227 |

| 267 | SDRAM Base Address LSB Register (RSZ_SDR_BAD_L)                                | 228 |

| 268 | SDRAM Start Address MSB Register (RSZ_SDR_SAD_H)                               | 228 |

| 269 | SDRAM Start Address LSB Register (RSZ_SDR_SAD_L)                               | 229 |

| 270 | SDRAM Line Offset Register (RSZ_SDR_OFT)                                       | 229 |

| 271 | Start Line of SDRAM Pointer Register (RSZ_SDR_PTR_S)                           | 230 |

| 272 | End Line of SDRAM Pointer Register (RSZ_SDR_PTR_E)                             |     |

| 273 | Output of Current Pointer Value (Read Only) Register (RSZ_SDR_PTR_O)           | 232 |

| 274 | Boxcar Enable Register (BOX_EN)                                                |     |

| 275 | One Shot Mode Register (BOX_MODE)                                              | 233 |

| 276 | Block Size (16x16 or 8x8) Register (BOX TYP)                                   | 233 |

| 277 | Down Shift Value of Input Register (BOX_SHF)                                   | 234 |

| 278 | Histogram Enable Register (HST_EN)                                             |     |

| 279 | One Shot Mode Register (HST_MODE)                                              |     |

| 280 | Histogram Source Select Register (HST_SEL)                                     |     |

| 281 | Histogram Parameters Select Register (HST_PARA)                                |     |

| 282 | Vertical Start Position Register (HST_VST)                                     |     |

| 283 | Vertical Size Register (HST_VSZ)                                               |     |

| 284 | Horizontal Start Position Register (HST HST)                                   |     |

| 285 | Horizontal Size Register (HST_HSZ)                                             |     |

| 286 | Peripheral Revision and Class Information Register (PID)                       |     |

| 287 | Peripheral Control Register (PCR)                                              |     |

| 288 | Setup for the AF Engine Paxel Configuration Register (AFPAX1)                  |     |

| 289 | Setup for the AF Engine Paxel Configuration Register (AFPAX2)                  |     |

| 290 | Start Position for AF Engine Paxels Register (AFPAXSTART)                      |     |

| 291 | Start Position for IIRSH Register (AFIIRSH)                                    |     |

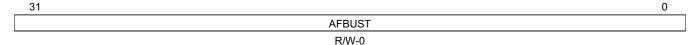

| 292 | SDRAM/DDRAM Start Address for AF Engine Register (AFBUFST)                     |     |

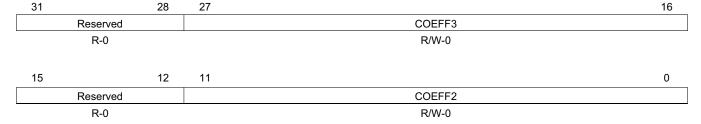

| 293 | IIR Filter Coefficient Data for SET 0 Register (AFCOEF010)                     |     |

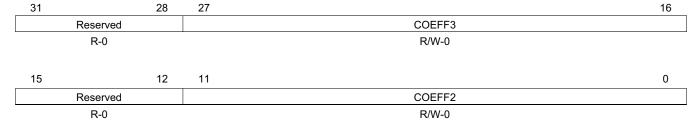

| 294 | IR Filter Coefficient Data for Set 0 Register (AFCOEF032)                      |     |

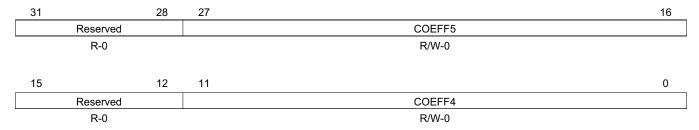

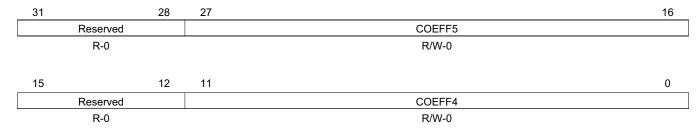

| 295 | IIR Filter Coefficient Data for SET 0 Register (AFCOEFF054)                    |     |

| 296 | IIR Filter Coefficient Data for SET 0 Register (AFCOEFF076)                    |     |

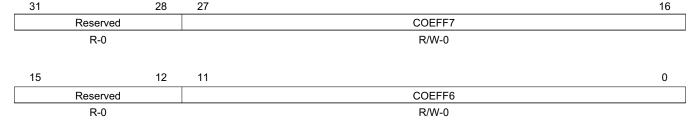

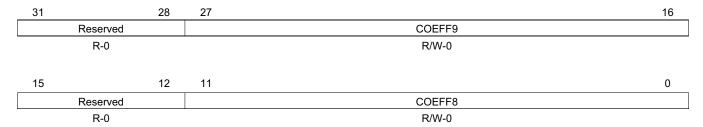

| 297 | IIR Filter Coefficient Data for SET 0 Register (AFCOEFF098)                    |     |

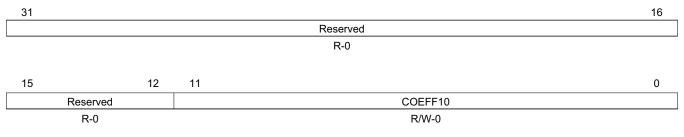

| 298 | IIR Filter Coefficient Data for SET 0 Register (AFCOEFF0010)                   |     |

| 299 | IIR Filter Coefficient Data for SET 1 Register (AFCOEF110)                     |     |

| 300 | IIR Filter Coefficient Data for SET 1 Register (AFCOEF132)                     |     |

| 301 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF154)                    |     |

| 302 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF176)                    |     |

| 303 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF198)                    |     |

| 304 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF1010)                   |     |

| 305 | Configuration for AE/AWB Windows Register (AEWWIN1)                            |     |

| 306 | Start Position for AE/AWB Windows Register (AEWINSTART)                        |     |

| 307 | Start Position and Height for Black Line of AE/AWB Windows Register (AEWINBLK) |     |

| 308 | Configuration for Subsample Data in AE/AWB Window Register (AEWSUBWIN)         |     |

| 309 | SDRAM/DDRAM Start Address for AE/AWB Engine Output Data Register (AEWBUFST)    |     |

| 310 | SDRAM/DDRAM Read Address for AE/AWB Engine Register (RSDR_ADDR)                |     |

| 311 | Line Offset for the Read Data Register (RADR OFFSET)                           |     |

| 312 | Frame Size for SDRAM Read Data Register (SDR_FRSIZE)                           |     |

| 313 | Peripheral Revision and Class Information Register (PID)                       |     |

| 314 | Peripheral Control Register (PCR)                                              |     |

| 315 | Interrupt Status Register (INTSTAT)                                            |     |

| 316 | Interrupt Selection Register (INTSEL)                                          |     |

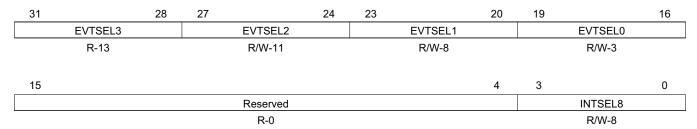

| 317 | Event Selection Register (EVTSEL)                                              |     |

| 017 | Evolit Goldon Register (Evidee)                                                | 201 |

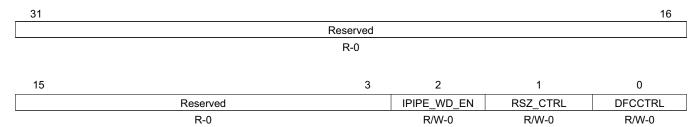

| 318 | Shared Memory Master Select Register (MEMCTRL)           | 268 |

|-----|----------------------------------------------------------|-----|

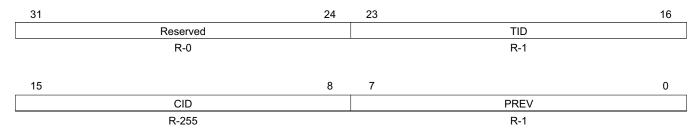

| 319 | Peripheral Revision and Class Information Register (PID) | 269 |

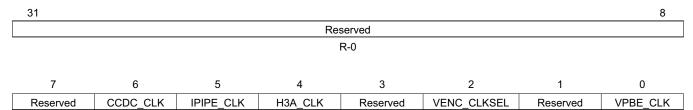

| 320 | VPSS Clock Control Register (CLKCTRL)                    | 270 |

## **List of Tables**

| 1  | Interface Signals for Video Processing Front End               | . 26 |

|----|----------------------------------------------------------------|------|

| 2  | Interface Signals for Parallel Raw Mode                        | . 27 |

| 3  | Imager Data Connection Examples                                | . 28 |

| 4  | Available Gain Functions for Bit Shifting the Data             | . 28 |

| 5  | CCD/CMOS Interface Signals                                     | . 29 |

| 6  | Interface Signals for ITU-R BT.656 Mode                        | . 32 |

| 7  | ITU-R BT.656 Interface Signals                                 | . 33 |

| 8  | Video Timing Reference Codes for SAV and EAV                   | . 34 |

| 9  | F, V, H Signal Descriptions                                    | . 34 |

| 10 | F, V, H Protection (Error Correction) Bits                     | . 34 |

| 11 | Interface Signals for Generic YCbCr Mode                       | . 35 |

| 12 | Table 16. YCbCr Interface Signals                              | . 36 |

| 13 | DDR2/mDDR Controller Storage Format for YCbCr Processing       | . 36 |

| 14 | Signals for VPFE Digital Capture Modes                         | . 37 |

| 15 | Pin Mux 0 Register (PINMUX0) Field Descriptions                | . 38 |

| 16 | Clock Domains                                                  | . 40 |

| 17 | VPSS Events                                                    | . 41 |

| 18 | ARM Interrupts - VPSS                                          | . 41 |

| 19 | EDMA Events - VPSS                                             |      |

| 20 | VPFE Module Register Map                                       | . 42 |

| 21 | YCbCr Mode SDRAM Output Format                                 | . 53 |

| 22 | Available Processing for Input Modes                           | . 61 |

| 23 | Label Descriptions From Figure 39                              |      |

| 24 | YcbCr-422 Memory Format                                        | . 70 |

| 25 | SDRAM Write Registers                                          |      |

| 26 | Recommended SHIFT Values to Get 16-Bit Output Resolution       | . 77 |

| 27 | Regions and Bins for Histogram                                 | . 79 |

| 28 | Recommended SHIFT Values                                       | . 80 |

| 29 | VPFE Memory Master Selection                                   | . 82 |

| 30 | CCDC Required Configuration Parameters                         |      |

| 31 | CCDC Conditional Configuration Parameters                      | . 84 |

| 32 | IPIPE Interface Required Configuration Parameters              | . 89 |

| 33 | Table 52. IPIPE Interface Conditional Configuration Parameters | . 89 |

| 34 | IPIPE Required Configuration Parameters                        | . 91 |

| 35 | IPIPE Conditional Configuration Parameters                     | . 92 |

| 36 | IPIPE Events                                                   | . 98 |

| 37 | IPIPE Resizer Status Registers                                 | . 99 |

| 38 | AF Engine Required Configuration Parameters                    | 108  |

| 39 | AF Engine Conditional Configuration Parameters                 | 108  |

| 40 | AEW Engine Required Configuration Parameters                   | 109  |

| 41 | AEW Engine Conditional Configuration Parameters                | 109  |

| 42 | VPSSBL and VPSSCLK Required Configuration Parameters           | 111  |

| 43 | Video Processing Front End Sub-Module Register Map             |      |

| 44 | CCD Controller (CCDC) Registers                                |      |

| 45 | Synchronization Enable Register (SYNCEN) Field Descriptions    | 115  |

| 46 | Mode Setup Register (MODESET) Field Descriptions               |      |

| 47 | HD Pulse Width Register (HDWIDTH) Field Descriptions           |      |

| 48 | VD Pulse Width Register (VDWIDTH) Field Descriptions           |      |

| 49 | Pixels Per Line Register (PPLN) Field Descriptions             |      |

|    |                                                                |      |

| 50  | Lines Per Frame Register (LPFR) Field Descriptions                                    |     |

|-----|---------------------------------------------------------------------------------------|-----|

| 51  | Start Pixel Horizontal Register (SPH) Field Descriptions                              |     |

| 52  | Number of Pixels Horizontal Register (NPH) Field Descriptions                         |     |

| 53  | Start Line Vertical - Field 0 Register (SLV0) Field Descriptions                      |     |

| 54  | Start Line Vertical - Field 1 Register (SLV1) Field Descriptions                      |     |

| 55  | Number of Lines Vertical Register (NLV) Field Descriptions                            |     |

| 56  | Culling Horizontal Register (CULH) Field Descriptions                                 |     |

| 57  | Culling Vertical Register (CULV) Field Descriptions                                   |     |

| 58  | Horizontal Size Register (HSIZE) Field Descriptions                                   |     |

| 59  | SDRAM Line Offset Register (SDOFST) Field Descriptions                                |     |

| 60  | SDRAM Address - High Register (STADRH) Field Descriptions                             |     |

| 61  | SDRAM Address - Low Register (STADRL) Field Descriptions                              |     |

| 62  | CCD Data Clamping Register (CLAMP) Field Descriptions                                 |     |

| 63  | DC Clamp Register (DCSUB) Field Descriptions                                          |     |

| 64  | CCD Color Pattern Register (COLPTN) Field Descriptions                                |     |

| 65  | Black Compensation #1 Register (BLKCMP0) Field Descriptions                           |     |

| 66  | Black Compensation #2 Register (BLKCMP1) Field Descriptions                           |     |

| 67  | CCD Median Filter Register (MEDFILT) Field Descriptions                               |     |

| 68  | CCD Gain Adjustment - R/Ye Register (RYEGAIN) Field Descriptions                      |     |

| 69  | CCD Gain Adjustment - Gr/Cy Register (GRCYGAIN) Field Descriptions                    |     |

| 70  | CCD gain adjustment - Gb/G register (GBGGAIN) Field Descriptions                      |     |

| 71  | CCD Gain Adjustment - B/Mg Register (BMGGAIN) Field Descriptions                      |     |

| 72  | CCD Offset Adjustment Register (OFFSET) Field Descriptions                            |     |

| 73  | Output Clipping Value Register (OUTCLIP) Field Descriptions                           |     |

| 74  | VD Interrupt #0 Register (VDINT0) Field Descriptions                                  | 133 |

| 75  | VD Interrupt #1 Register (VDINT1) Field Descriptions                                  | 133 |

| 76  | Gamma Correction Settings Register (GAMMAWD) Field Descriptions                       | 134 |

| 77  | REC656 Control Register (REC656IF) Field Descriptions                                 | 135 |

| 78  | CCD Configuration Register (CCDCFG) Field Descriptions                                | 136 |

| 79  | Start Pixel Horizontal Register (FMTSPH) Field Descriptions                           | 137 |

| 80  | Number Of Pixels Register (FMTLNH) Field Descriptions                                 | 137 |

| 81  | Start Line Vertical Register (FMTSLV) Field Descriptions                              | 138 |

| 82  | Number of Lines Register (FMTLNV) Field Descriptions                                  | 138 |

| 83  | Lens Shading Correction Configuration 1 Register (LSCCFG1) Field Descriptions         | 139 |

| 84  | Lens Shading Correction Configuration 2 Register (LSCCFG2) Field Descriptions         | 140 |

| 85  | Lens Shading Correction - Center Position (H0) Register (LSCH0) Field Descriptions    | 141 |

| 86  | Lens Shading Correction - Center Position (V0) Register (LSCV0) Field Descriptions    | 141 |

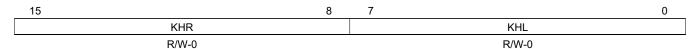

| 87  | Lens Shading Correction - Horizontal Coefficients Register (LSCKH) Field Descriptions | 142 |

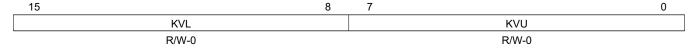

| 88  | Lens Shading Correction - Vertical Coefficients Register (LSCKV) Field Descriptions   | 142 |

| 89  | Lens Shading Correction - Memory Control Register (LSCMEMCTL) Field Descriptions      | 143 |

| 90  | Lens Shading Correction - Memory Write Data Register (LSCMEMD) Field Descriptions     | 144 |

| 91  | Lens Shading Correction - Memory Read Data Register (LSCMEMQ) Field Descriptions      | 144 |

| 92  | Defect Correction - Control Register (DFCCTL) Field Descriptions                      | 145 |

| 93  | Defect Correction - Vertical Saturation Level Register (DFCVSAT) Field Descriptions   | 146 |

| 94  | Defect Correction - Memory Control Register (DFCMEMCTL) Field Descriptions            | 147 |

| 95  | Defect Correction - Set V Position Register (DFCMEM0) Field Descriptions              |     |

| 96  | Defect Correction - Set H Position Register (DFCMEM1) Field Descriptions              |     |

| 97  | Defect Correction - Set SUB1 Register (DFCMEM2) Field Descriptions                    |     |

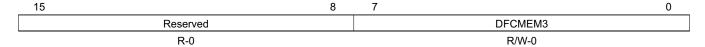

| 98  | Defect Correction - Set SUB2 Register (DFCMEM3) Field Descriptions                    |     |

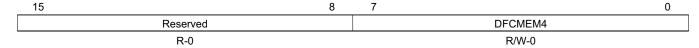

| 99  | Defect Correction - Set SUB3 Register (DFCMEM4) Field Descriptions                    |     |

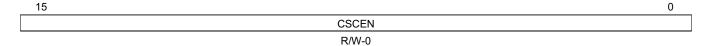

| 100 | Color Space Converter Enable Register (CSCCTL) Field Descriptions                     |     |

| www. | tı | CO | m |

|------|----|----|---|

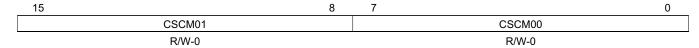

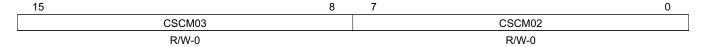

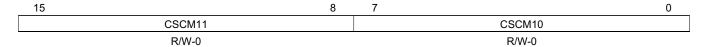

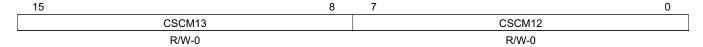

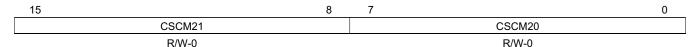

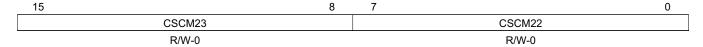

| 101 | Color Space Converter - Coefficients #0 Register (CSCM0) Field Descriptions           | 151 |

|-----|---------------------------------------------------------------------------------------|-----|

| 102 | Color Space Converter - Coefficients #1 Register (CSCM1P) Field Descriptions          | 151 |

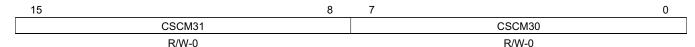

| 103 | Color Space Converter - Coefficients #2 Register (CSCM2) Field Descriptions           |     |

| 104 | Color Space Converter - Coefficients #3 Register (CSCM3) Field Descriptions           |     |

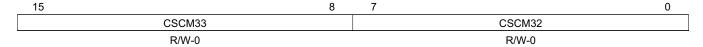

| 105 | Color Space Converter - Coefficients #4 Register (CSCM4) Field Descriptions           |     |

| 106 | Color Space Converter - Coefficients #5 Register (CSCM5) Field Descriptions           |     |

| 107 | Color Space Converter - Coefficients #6 Register (CSCM6) Field Descriptions           |     |

| 108 | Color Space Converter - Coefficients #7 Register (CSCM7) Field Descriptions           |     |

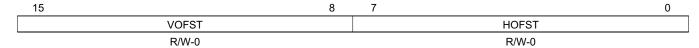

| 109 | Data Offset Register (DATAOFST) Field Descriptions                                    |     |

| 110 | Image Pipe Input Interface Register Map (IPIPEIF)                                     |     |

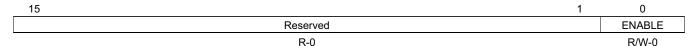

| 111 | IPIPE I/F Enable Register (ENABLE) Field Descriptions                                 |     |

| 112 | IPIPE I/F Configuration Register (CFG) Field Descriptions                             |     |

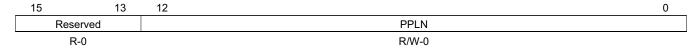

| 113 | PIPE I/F Interval of HD / Start pixel in HD Register (PPLN) Field Descriptions        |     |

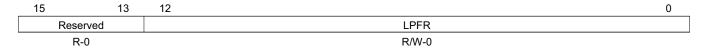

| 114 | IPIPE I/F Interval of VD / Start line in VD Register (LPFR) Field Descriptions        |     |

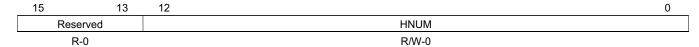

| 115 | IPIPE I/F Number of valid pixels per line Register (HNUM) Field Descriptions          |     |

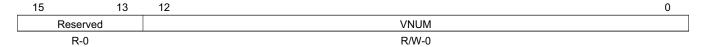

| 116 | IPIPE I/F Number of Valid Lines per Frame Register (VNUM) Field Descriptions          |     |

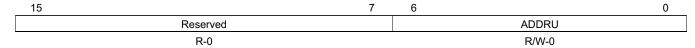

| 117 | IPIPE I/F Memory Address (Upper) Register (ADDRU) Field Descriptions                  |     |

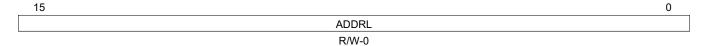

| 118 | IPIPE I/F Memory Address (Lower) Register (ADDRL) Field Descriptions                  |     |

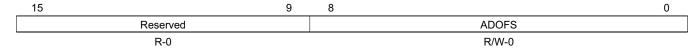

| 119 | IPIPE I/F Address Offset of Each Line Register (ADOFS) Field Descriptions             |     |

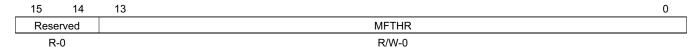

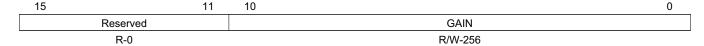

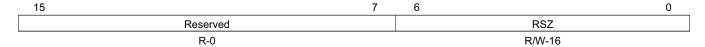

| 120 | IPIPE I/F Horizontal Resizing Parameter Register (RSZ) Field Descriptions             |     |

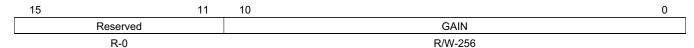

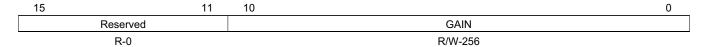

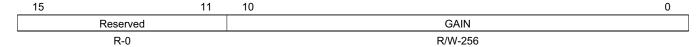

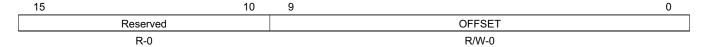

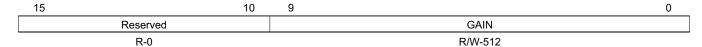

| 121 | IPIPE I/F Gain Parameter Register (GAIN) Field Descriptions                           |     |

| 122 | Image Pipe Registers (IPIPE)                                                          |     |

| 123 | IPIPE Enable Register (IPIPE_EN) Field Descriptions                                   |     |

| 124 | One Shot Mode Register (IPIPE_MODE) Field Descriptions                                |     |

| 125 | Input/Output Data Paths Register (IPIPE_DPATHS) Field Descriptions                    |     |

| 126 | Color Pattern Register (IPIPE_COLPAT) Field Descriptions                              |     |

| 127 | Vertical Start Position Register (IPIPE_VST) Field Descriptions                       |     |

| 128 | Vertical Processing Size Register (IPIPE_VSZ) Field Descriptions                      |     |

| 129 | Horizontal Start Position Register (IPIPE_HST) Field Descriptions                     |     |

| 130 | Horizontal Processing Size Register (IPIPE_HSZ) Field Descriptions                    |     |

| 131 | ARM Gated Clock Control Register (GCL_ARM) Field Descriptions                         |     |

| 132 | CCD Gated Clock Control Register (GCL_CCD) Field Descriptions                         |     |

| 133 | SDR Gated Clock Control Register (GCL_SDR) Field Descriptions                         |     |

| 134 | Internal Table Selection Register (RAM_MODE) Field Descriptions                       |     |

| 135 | Address Register (RAM_ADR) Field Descriptions                                         |     |

| 136 | Write Data Register (RAM_WDT) Field Descriptions                                      |     |

| 137 | Read Data Register (RAM_RDT) Field Descriptions                                       |     |

| 138 | Interrupt Enable Register (IRQ_EN) Field Descriptions                                 |     |

| 139 | Interval of IRQ-2 Register (IRQ_RZA) Field Descriptions                               |     |

| 140 | Interval of IRQ-3 Register (IRQ_RZB) Field Descriptions                               |     |

| 141 | Defect Correction Enable Register (DFC_EN) Field Descriptions                         |     |

| 142 | Copy Method Selection (from Top or from Bottom) Register (DFC_SEL) Field Descriptions |     |

| 143 | Start Address in LUT Register (DFC_ADR) Field Descriptions                            |     |

| 144 | Number of Available Entries in LUT Register (DFC_SIZ) Field Descriptions              |     |

| 145 | 2D Noise Filter Enable Register (D2F_EN) Field Descriptions                           |     |

| 146 | Noise Filter Configuration Register (D2F_CFG) Field Descriptions                      |     |

| 147 | Noise Filter LUT Values (Threshold) Register (D2F_THR[32]) Field Descriptions         |     |

| 148 | Noise Filter LUT Values (Intensity) Register (D2F_STR[32]) Field Descriptions         |     |

| 149 | PreFilter Enable Register (PRE_EN) Field Descriptions                                 |     |

| 150 | PreFilter Type Register (PRE_TYP) Field Descriptions                                  |     |

| 151 | Shift Value of Adaptive Gain Register (PRE_SHF) Field Descriptions                    | 186 |

| 152 | Constant Gain or Adaptive Gain Slope Register (PRE_GAIN) Field Descriptions          | 186 |

|-----|--------------------------------------------------------------------------------------|-----|

| 153 | Threshold G Register (PRE_THR_G) Field Descriptions                                  | 187 |

| 154 | Threshold B Register (PRE_THR_B) Field Descriptions                                  | 187 |

| 155 | Threshold 1 Register (PRE_THR_1) Field Descriptions                                  | 188 |

| 156 | Digital Gain Register (WB2_DGN) Field Descriptions                                   | 188 |

| 157 | White Balance Gain (Red) Register (WB2_WG_R) Field Descriptions                      | 189 |

| 158 | White Balance Gain (Gr) Register (WB2_WG_GR) Field Descriptions                      | 189 |

| 159 | White Balance Gain (Gb) Register (WB2_WG_GB) Field Descriptions                      | 190 |

| 160 | White Balance Gain (Blue) Register (WB2_WG_B) Field Descriptions                     | 190 |

| 161 | Matrix Coefficient RR Register (RGB_MUL_RR) Field Descriptions                       | 191 |

| 162 | Matrix Coefficient GR Register (RGB_MUL_GR) Field Descriptions                       | 191 |

| 163 | Matrix Coefficient BR Register (RGB_MUL_BR) Field Descriptions                       | 192 |

| 164 | Matrix Coefficient RG Register (RGB_MUL_RG) Field Descriptions                       | 192 |

| 165 | Matrix Coefficient GG Register (RGB_MUL_GG) Field Descriptions                       | 193 |

| 166 | Matrix Coefficient BG Register (RGB_MUL_BG) Field Descriptions                       | 193 |

| 167 | Matrix Coefficient RB Register (RGB_MUL_RB) Field Descriptions                       | 194 |

| 168 | Matrix Coefficient GB Register (RGB_MUL_GB) Field Descriptions                       | 194 |

| 169 | Matrix Coefficient BB Register (RGB_MUL_BB) Field Descriptions                       | 195 |

| 170 | R Output Offset Register (RGB_OFT_OR) Field Descriptions                             | 195 |

| 171 | G Output Offset Register (RGB_OFT_OG) Field Descriptions                             | 196 |

| 172 | B Output Offset Register (RGB_OFT_OB) Field Descriptions                             | 196 |

| 173 | Gamma Correction Configuration Register (GMM_CFG) Field Descriptions                 | 197 |

| 174 | Luminance Adjustment (Contrast and Brightness) Register (YCC_ADJ) Field Descriptions | 198 |

| 175 | Matrix Coefficient RY Register (YCC_MUL_RY) Field Descriptions                       | 198 |

| 176 | Matrix Coefficient GY Register (YCC_MUL_GY) Field Descriptions                       | 199 |

| 177 | Matrix Coefficient BY Register (YCC_MUL_BY) Field Descriptions                       | 199 |

| 178 | Matrix Coefficient RCb Register (YCC_MUL_RCB) Field Descriptions                     | 200 |

| 179 | Matrix Coefficient GCb Register (YCC_MUL_GCB) Field Descriptions                     | 200 |

| 180 | Matrix Coefficient BCb Register (YCC_MUL_BCB) Field Descriptions                     | 201 |

| 181 | Matrix Coefficient RCr Register (YCC_MUL_RCR) Field Descriptions                     | 201 |

| 182 | Matrix Coefficient GCr Register (YCC_MUL_GCR) Field Descriptions                     | 202 |

| 183 | Matrix Coefficient BCr Register (YCC_MUL_BCR) Field Descriptions                     | 202 |

| 184 | Y Output Offset Register (YCC_OFT_Y) Field Descriptions                              | 203 |

| 185 | Cb Output Offset Register (YCC_OFT_CB) Field Descriptions                            | 203 |

| 186 | Cr Output Offset Register (YCC_OFT_CR) Field Descriptions                            | 204 |

| 187 | Saturation (Luminance Minimum) Register (YCC_Y_MIN) Field Descriptions               | 204 |

| 188 | Saturation (Luminance Maximum) Register (YCC_Y_MAX) Field Descriptions               | 205 |

| 189 | Saturation (Chrominance Minimum) Register (YCC_C_MIN) Field Descriptions             | 205 |

| 190 | Saturation (Chrominance Maximum) Register (YCC_C_MAX) Field Descriptions             | 206 |

| 191 | Chrominance Position (for 422 down sampler) Register (YCC_PHS) Field Descriptions    | 206 |

| 192 | Edge Enhancer Enable Register (YEE_EN) Field Descriptions                            | 207 |

| 193 | MedianNR Enable Register (YEE_EMF) Field Descriptions                                | 207 |

| 194 | HPF Shift Length Register (YEE_SHF) Field Descriptions                               | 208 |

| 195 | HPF Coefficient 00 Register (YEE_MUL_00) Field Descriptions                          | 208 |

| 196 | HPF Coefficient 01 Register (YEE_MUL_01) Field Descriptions                          |     |

| 197 | HPF Coefficient 02 Register (YEE_MUL_02) Field Descriptions                          |     |

| 198 | HPF Coefficient 10 Register (YEE_MUL_10) Field Descriptions                          |     |

| 199 | HPF Coefficient 11 Register (YEE_MUL_11) Field Descriptions                          |     |

| 200 | HPF Coefficient 12 Register (YEE_MUL_12) Field Descriptions                          |     |

| 201 | HPF Coefficient 20 Register (YEE_MUL_20) Field Descriptions                          |     |

| 202 | HPF Coefficient 21 Register (YEE MUL 21) Field Descriptions                          |     |

| www | ٠t١. | CO | m |

|-----|------|----|---|

| 203 | HPF Coefficient 22 Register (YEE_MUL_22) Field Descriptions                              | 212 |

|-----|------------------------------------------------------------------------------------------|-----|

| 204 | Fault Color Suppression Enable Register (FCS_EN) Field Descriptions                      |     |

| 205 | Type selection of HPF Register (FCS_TYP) Field Descriptions                              |     |

| 206 | Down Shift Size (HPF) Register (FCS_SHF_Y) Field Descriptions                            |     |

| 207 | Down Shift Size (GAIN) Register (FCS_SHF_C) Field Descriptions                           | 214 |

| 208 | Threshold Register (FCS_THR) Field Descriptions                                          | 215 |

| 209 | Intensity Register (FCS_SGN) Field Descriptions                                          | 215 |

| 210 | Lower Limit of Chroma Gain Register (FCS_LTH) Field Descriptions                         | 215 |

| 211 | Processing Mode Register (RSZ_SEQ) Field Descriptions                                    |     |

| 212 | Vertical Anti aliasing Filter Register (RSZ_AAL) Field Descriptions                      | 217 |

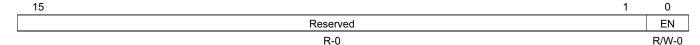

| 213 | Resizer Enable Register (RSZ_EN) Field Descriptions                                      | 217 |

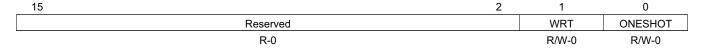

| 214 | One Shot Mode Register (RSZ_MODE) Field Descriptions                                     | 218 |

| 215 | Vertical Start Position of the Input Register (RSZ_I_VST) Field Descriptions             | 218 |

| 216 | Vertical Size of the Input Register (RSZ_I_VSZ) Field Descriptions                       | 219 |

| 217 | Horizontal Start Position of the Input Register (RSZ_I_HST) Field Descriptions           | 219 |

| 218 | Vertical Size of the Output Register (RSZ_O_VSZ) Field Descriptions                      | 220 |

| 219 | Horizontal Start Position of the Output Register (RSZ_O_HST) Field Descriptions          | 220 |

| 220 | Horizontal Size of the Output Register (RSZ_O_HSZ) Field Descriptions                    |     |

| 221 | Initial Phase of Vertical Resizing Process Register (RSZ_V_PHS) Field Descriptions       | 221 |

| 222 | Phase of Last Value in Previous Resize Process Register (RSZ_V_PHS_O) Field Descriptions |     |

| 223 | Vertical Resize Parameter Register (RSZ_V_DIF) Field Descriptions                        | 222 |

| 224 | Actual Number of Output Lines Register (RSZ_V_SIZ_O) Field Descriptions                  |     |

| 225 | Initial Phase of Horizontal Resizing Process Register (RSZ_H_PHS) Field Descriptions     |     |

| 226 | Horizontal Resize Parameter Register (RSZ_H_DIF) Field Descriptions                      | 224 |

| 227 | Interpolation Method for Horizontal Rescaling Register (RSZ_H_TYP) Field Descriptions    | 224 |

| 228 | Selection of Horizontal LPF Intensity Register (RSZ_H_LSE) Field Descriptions            | 225 |

| 229 | Horizontal LPF Intensity Register (RSZ_H_LPF) Field Descriptions                         | 225 |

| 230 | RGB Output Enable Register (RSZ_RGB_EN) Field Descriptions                               | 226 |

| 231 | RGB Output Bit Mode (32 or 16 bit) Register (RSZ_RGB_TYP) Field Descriptions             | 226 |

| 232 | YC422 to YC444 Conversion Method Register (RSZ_RGB_BLD) Field Descriptions               | 227 |

| 233 | SDRAM Base Address MSB Register (RSZ_SDR_BAD_H) Field Descriptions                       | 227 |

| 234 | SDRAM Base Address LSB Register (RSZ_SDR_BAD_L) Field Descriptions                       | 228 |

| 235 | SDRAM Start Address MSB Register (RSZ_SDR_SAD_H) Field Descriptions                      | 228 |

| 236 | SDRAM Start Address LSB Register (RSZ_SDR_SAD_L) Field Descriptions                      | 229 |

| 237 | SDRAM Line Offset Register (RSZ_SDR_OFT) Field Descriptions                              | 229 |

| 238 | Start Line of SDRAM Pointer Register (RSZ_SDR_PTR_S) Field Descriptions                  | 230 |

| 239 | End Line of SDRAM Pointer Register (RSZ_SDR_PTR_E) Field Descriptions                    | 231 |

| 240 | Output of Current Pointer Value (Read Only) Register (RSZ_SDR_PTR_O) Field Descriptions  | 232 |

| 241 | Boxcar Enable Register (BOX_EN) Field Descriptions                                       |     |

| 242 | One Shot Mode Register (BOX_MODE) Field Descriptions                                     | 233 |

| 243 | Block Size (16x16 or 8x8) Register (BOX_TYP) Field Descriptions                          | 233 |

| 244 | Down Shift Value of Input Register (BOX_SHF) Field Descriptions                          | 234 |

| 245 | Histogram Enable Register (HST_EN) Field Descriptions                                    |     |

| 246 | One Shot Mode Register (HST_MODE) Field Descriptions                                     | 235 |

| 247 | Histogram Source Select Register (HST_SEL) Field Descriptions                            |     |

| 248 | Histogram Parameters Select Register (HST_PARA) Field Descriptions                       |     |

| 249 | Vertical Start Position Register (HST_VST) Field Descriptions                            |     |

| 250 | Vertical Size Register (HST_VSZ) Field Descriptions                                      |     |

| 251 | Horizontal Start Position Register (HST_HST) Field Descriptions                          |     |

| 252 | Horizontal Size Register (HST_HSZ) Field Descriptions                                    |     |

| 253 | Hardware 3A Register Map (H3A)                                                           |     |

| 254 | Peripheral ID Register (PID) Field Description                                                    | 240 |

|-----|---------------------------------------------------------------------------------------------------|-----|

| 255 | Peripheral Control Register (PCR) Field Descriptions                                              | 241 |

| 256 | Setup for the AF Engine Paxel Configuration Register (AFPAX1) Field Descriptions                  | 243 |

| 257 | Setup for the AF Engine Paxel Configuration Register (AFPAX2) Field Descriptions                  | 244 |

| 258 | Start Position for AF Engine Paxels Register (AFPAXSTART) Field Descriptions                      | 245 |

| 259 | Start Position for IIRSH Register (AFIIRSH) Field Descriptions                                    | 246 |

| 260 | SDRAM/DDRAM Start Address for AF Engine Register (AFBUFST) Field Descriptions                     | 246 |

| 261 | IIR Filter Coefficient Data for SET 0 Register (AFCOEF010) Field Descriptions                     | 247 |

| 262 | IR Filter Coefficient Data for Set 0 Register (AFCOEF032) Field Descriptions                      | 247 |

| 263 | IIR Filter Coefficient Data for SET 0 Register (AFCOEFF054) Field Descriptions                    | 248 |

| 264 | IIR Filter Coefficient Data for SET 0 Register (AFCOEFF076) Field Descriptions                    | 249 |

| 265 | Lens Center (LD) Register (CENTER) Field Descriptions                                             | 249 |

| 266 | IIR Filter Coefficient Data for SET 0 Register (AFCOEFF0010) Field Descriptions                   | 250 |

| 267 | IIR Filter Coefficient Data for SET 1 Register (AFCOEF110) Field Descriptions                     | 251 |

| 268 | IIR Filter Coefficient Data for SET 1 Register (AFCOEF132) Field Descriptions                     | 251 |

| 269 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF154) Field Descriptions                    | 252 |

| 270 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF176) Field Descriptions                    | 252 |

| 271 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF198) Field Descriptions                    | 253 |

| 272 | IIR Filter Coefficient Data for SET 1 Register (AFCOEFF1010) Field Descriptions                   | 254 |

| 273 | Configuration for AE/AWB Windows Register (AEWWIN1) Field Descriptions                            | 255 |

| 274 | Start Position for AE/AWB Windows Register (AEWINSTART) Field Descriptions                        | 256 |

| 275 | Start Position and Height for Black Line of AE/AWB Windows Register (AEWINBLK) Field Descriptions | 257 |

| 276 | Configuration for Subsample Data in AE/AWB Window Register (AEWSUBWIN) Field Descriptions         | 258 |

| 277 | SDRAM/DDRAM Start Address for AE/AWB Engine Output Data Register (AEWBUFST) Field Descriptions    | 259 |

| 278 | SDRAM/DDRAM Read Address for AE/AWB Engine Register (RSDR ADDR) Field Descriptions                |     |

| 279 | Line Offset for the Read Data Register (RADR_OFFSET) Field Descriptions                           | 260 |

| 280 | Frame Size for SDRAM Read Data Register (SDR_FRSIZE) Field Descriptions                           | 261 |

| 281 | VPSS Buffer Logic Register Map (VPSSBL)                                                           | 262 |

| 282 | Peripheral ID Register (PID) Field Description                                                    | 262 |

| 283 | Peripheral Control Register (PCR) Field Descriptions                                              | 263 |

| 284 | Interrupt Status Register (INTSTAT) Field Descriptions                                            | 264 |

| 285 | Interrupt Selection Register (INTSEL) Field Descriptions                                          | 266 |

| 286 | Event Selection Register (EVTSEL) Field Descriptions                                              | 267 |

| 287 | Shared Memory Master Select Register (MEMCTRL) Field Descriptions                                 | 268 |

| 288 | VPSS Clock Control Register Map (VPSSCLK)                                                         | 269 |

| 289 | Peripheral ID Register (PID) Field Description                                                    | 269 |

| 290 | VPSS Clock Control Register (CLKCTRL) Field Descriptions                                          | 270 |

| A-1 | Changes Made in This Revision                                                                     | 271 |

## Read This First

#### **About This Manual**

This document describes the operation of the Video Processing Front End in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

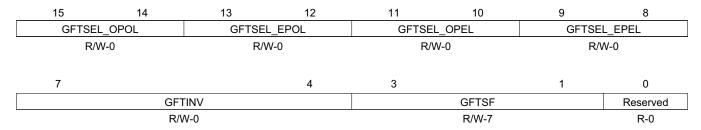

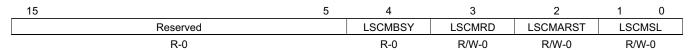

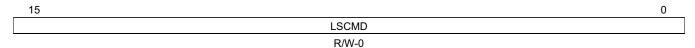

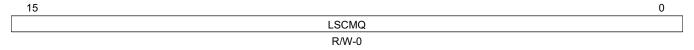

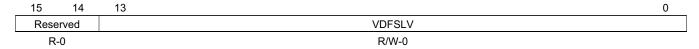

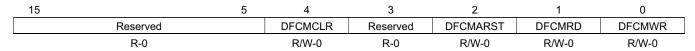

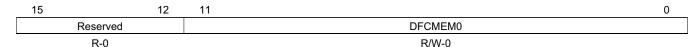

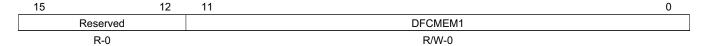

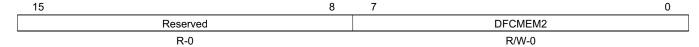

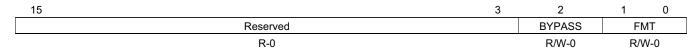

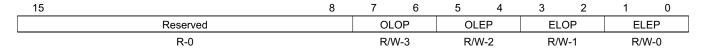

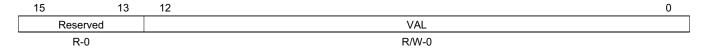

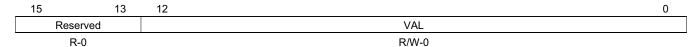

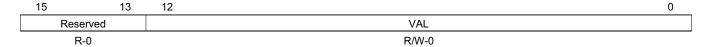

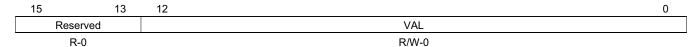

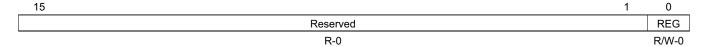

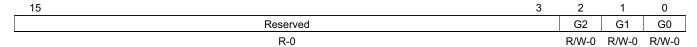

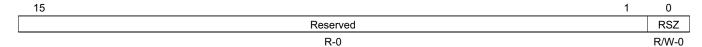

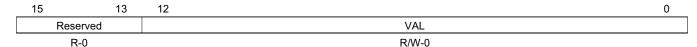

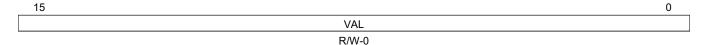

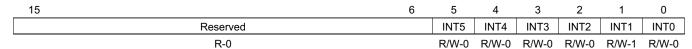

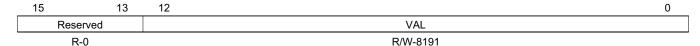

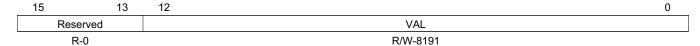

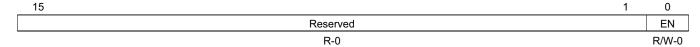

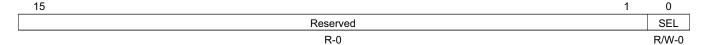

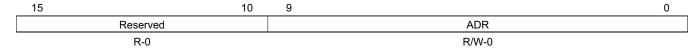

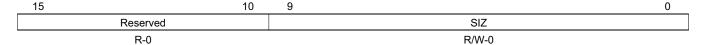

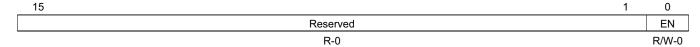

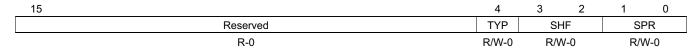

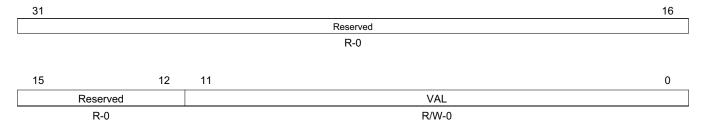

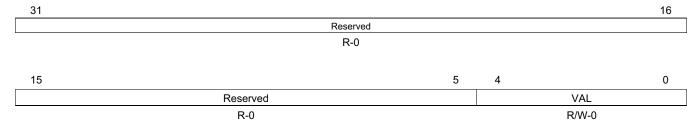

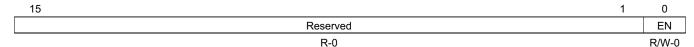

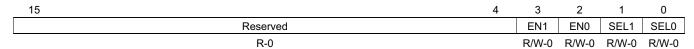

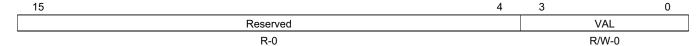

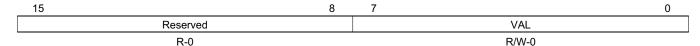

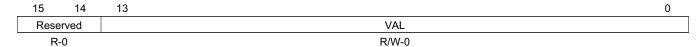

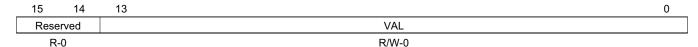

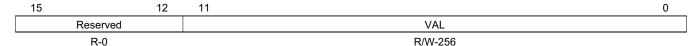

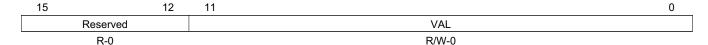

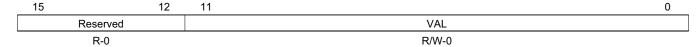

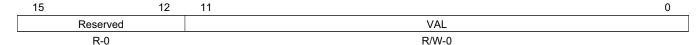

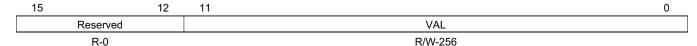

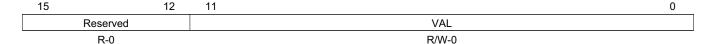

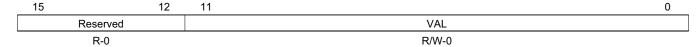

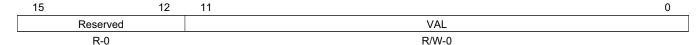

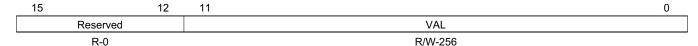

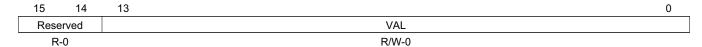

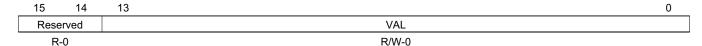

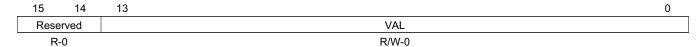

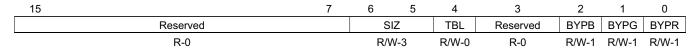

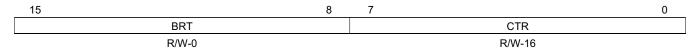

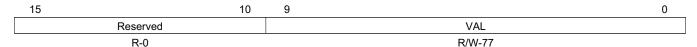

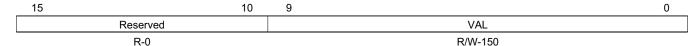

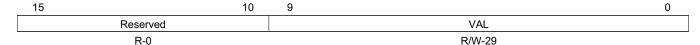

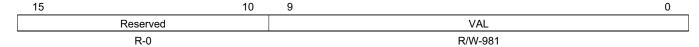

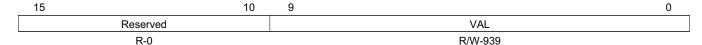

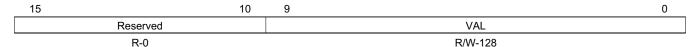

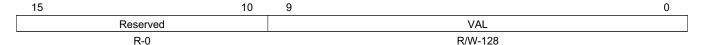

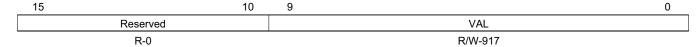

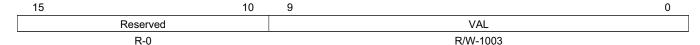

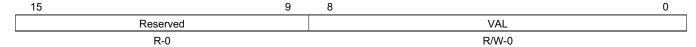

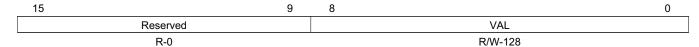

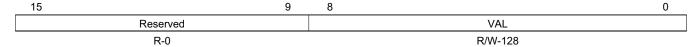

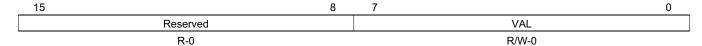

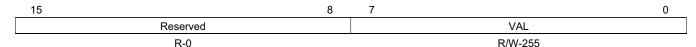

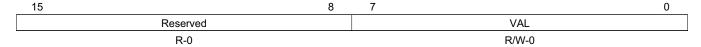

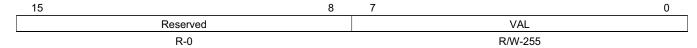

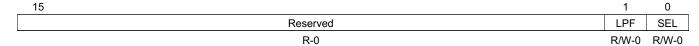

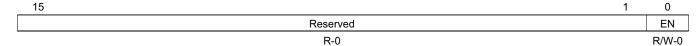

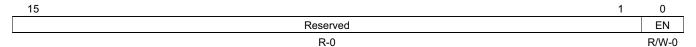

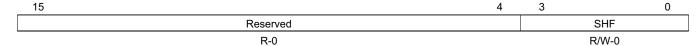

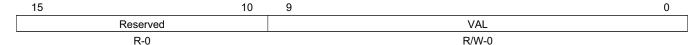

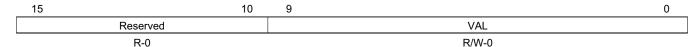

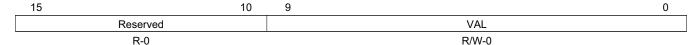

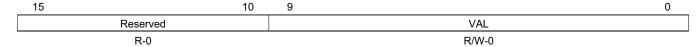

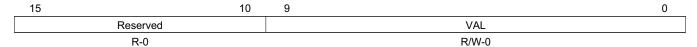

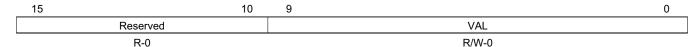

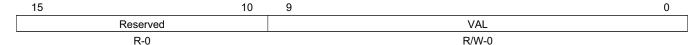

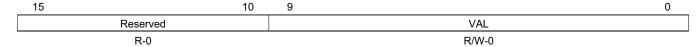

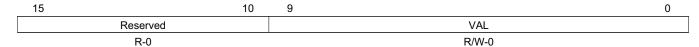

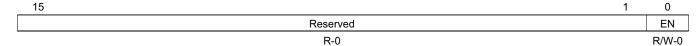

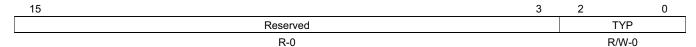

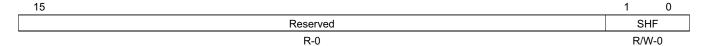

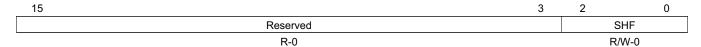

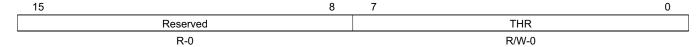

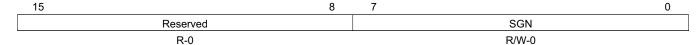

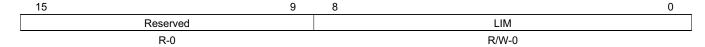

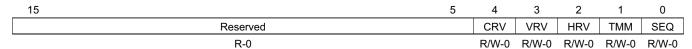

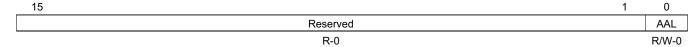

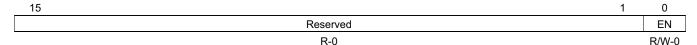

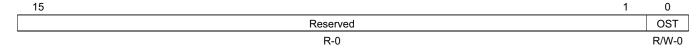

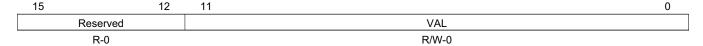

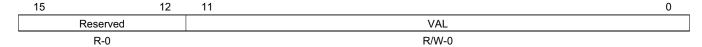

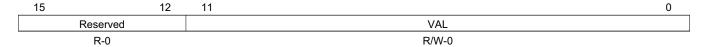

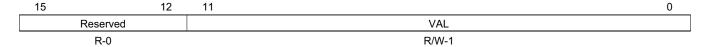

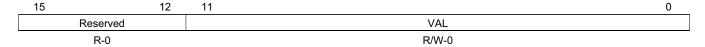

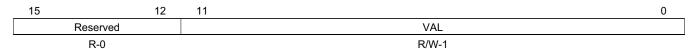

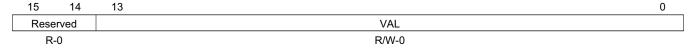

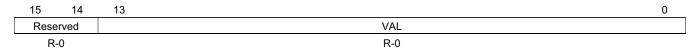

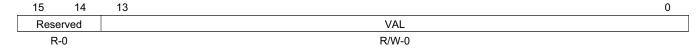

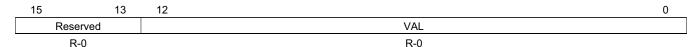

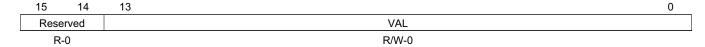

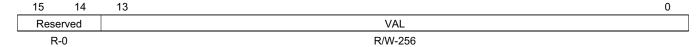

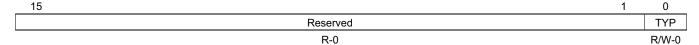

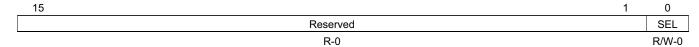

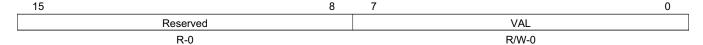

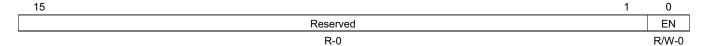

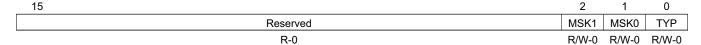

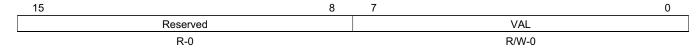

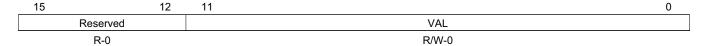

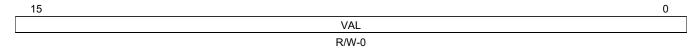

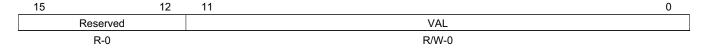

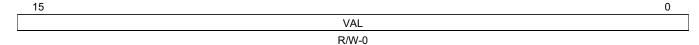

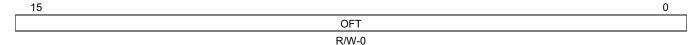

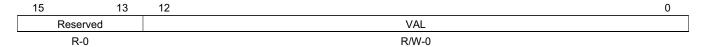

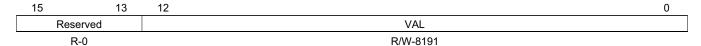

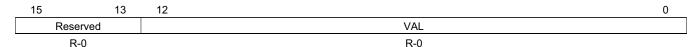

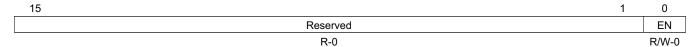

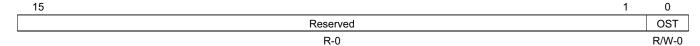

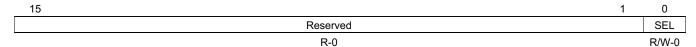

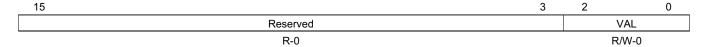

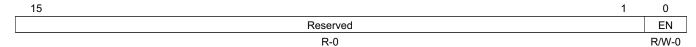

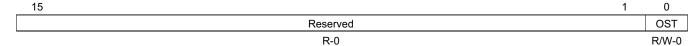

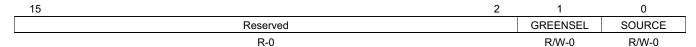

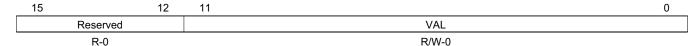

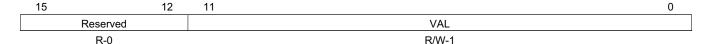

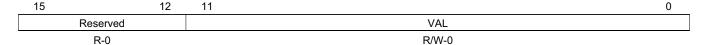

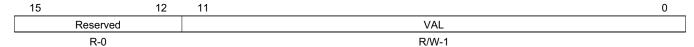

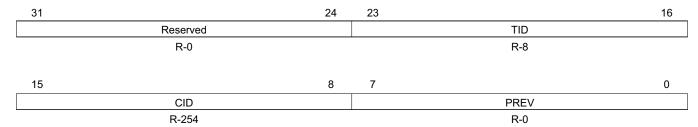

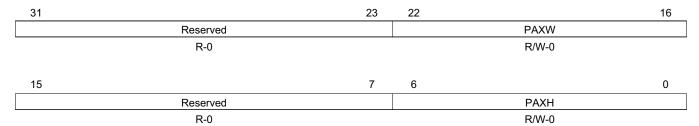

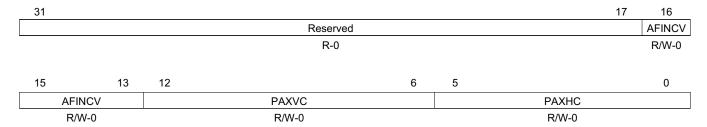

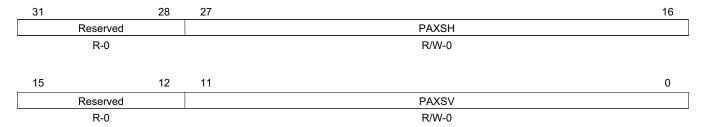

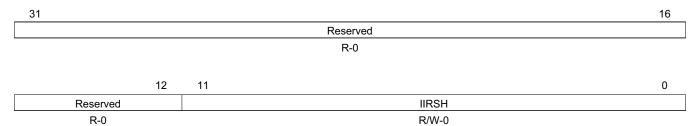

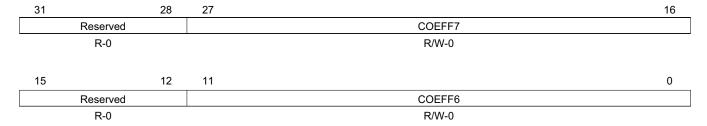

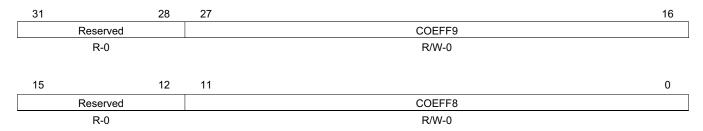

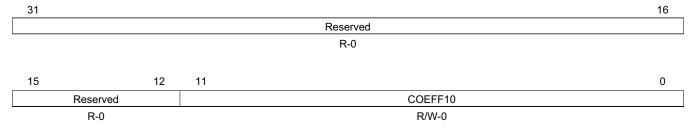

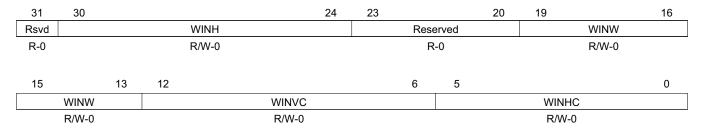

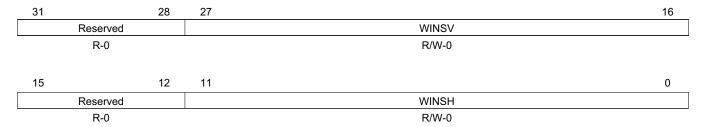

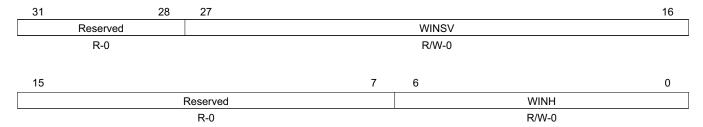

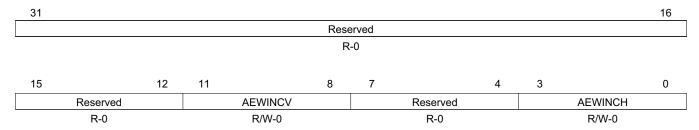

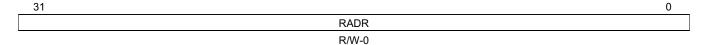

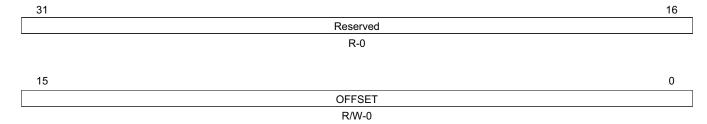

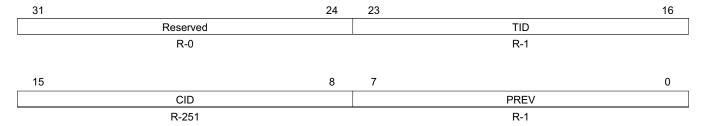

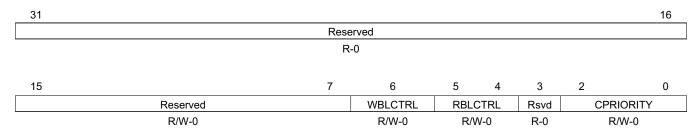

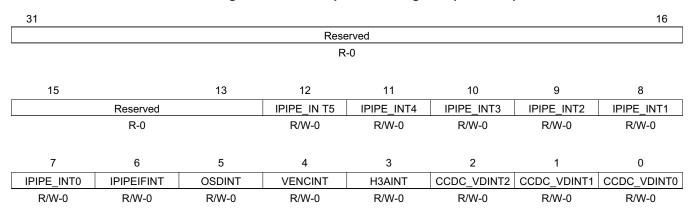

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

### **Related Documentation From Texas Instruments**

The following documents describe the TMS320DM35x Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the internet at www.ti.com.

- SPRS463 TMS320DM355 Digital Media System-on-Chip (DMSoC) Data Manual This document describes the overall TMS320DM355 system, including device architecture and features, memory map, pin descriptions, timing characteristics and requirements, device mechanicals, etc.

- <u>SPRZ264</u> *TMS320DM355 DMSoC Silicon Errata* Describes the known exceptions to the functional specifications for the TMS320DM355 DMSoC.

- SPRUFB3 TMS320DM35x Digital Media System-on-Chip (DMSoC) ARM Subsystem Reference Guide This document describes the ARM Subsystem in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the components of the ARM Subsystem, the peripherals, and the external memories.

- SPRUED1 TMS320DM35x Digital Media System-on-Chip (DMSoC) Asynchronous External Memory Interface (EMIF) Reference Guide This document describes the asynchronous external memory interface (EMIF) in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The EMIF supports a glueless interface to a variety of external devices.

- SPRUED2 TMS320DM35x Digital Media System-on-Chip (DMSoC) Universal Serial Bus (USB)

Controller Reference Guide This document describes the universal serial bus (USB) controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The USB controller supports data throughput rates up to 480 Mbps. It provides a mechanism for data transfer between USB devices and also supports host negotiation.

- SPRUED3 TMS320DM35x Digital Media System-on-Chip (DMSoC) Audio Serial Port (ASP)

Reference Guide This document describes the operation of the audio serial port (ASP) audio interface in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The primary audio modes that are supported by the ASP are the AC97 and IIS modes. In addition to the primary audio modes, the ASP supports general serial port receive and transmit operation, but is not intended to be used as a high-speed interface.

- SPRUED4 TMS320DM35x Digital Media System-on-Chip (DMSoC) Serial Peripheral Interface (SPI) Reference Guide This document describes the serial peripheral interface (SPI) in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The SPI is a high-speed synchronous serial input/output port that allows a serial bit stream of programmed length (1 to 16 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI is normally used for communication between the DMSoC and external peripherals. Typical applications include an interface to external I/O or peripheral expansion via devices such as shift registers, display drivers, SPI EPROMs and analog-to-digital converters.

- SPRUED9 TMS320DM35x Digital Media System-on-Chip (DMSoC) Universal Asynchronous Receiver/Transmitter (UART) Reference Guide This document describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The UART peripheral performs serial-to-parallel conversion on data received from a peripheral device, and parallel-to-serial conversion on data received from the CPU.

- SPRUEE0 TMS320DM35x Digital Media System-on-Chip (DMSoC) Inter-Integrated Circuit (I2C) Peripheral Reference Guide This document describes the inter-integrated circuit (I2C) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The I2C peripheral provides an interface between the DMSoC and other devices compliant with the I2C-bus specification and connected by way of an I2C-bus. External components attached to this 2-wire serial bus can transmit and receive up to 8-bit wide data to and from the DMSoC through the I2C peripheral. This document assumes the reader is familiar with the I2C-bus specification.

- SPRUEE2 TMS320DM35x Digital Media System-on-Chip (DMSoC) Multimedia Card (MMC)/Secure Digital (SD) Card Controller Reference Guide This document describes the multimedia card (MMC)/secure digital (SD) card controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The MMC/SD card is used in a number of applications to provide removable data storage. The MMC/SD controller provides an interface to external MMC and SD cards. The communication between the MMC/SD controller and MMC/SD card(s) is performed by the MMC/SD protocol.

- SPRUEE4 TMS320DM35x Digital Media System-on-Chip (DMSoC) Enhanced Direct Memory

Access (EDMA) Controller Reference Guide This document describes the operation of the

enhanced direct memory access (EDMA3) controller in the TMS320DM35x Digital Media

System-on-Chip (DMSoC). The EDMA controller's primary purpose is to service user-programmed

data transfers between two memory-mapped slave endpoints on the DMSoC.

- SPRUEE5 TMS320DM35x Digital Media System-on-Chip (DMSoC) 64-bit Timer Reference Guide

This document describes the operation of the software-programmable 64-bit timers in the

TMS320DM35x Digital Media System-on-Chip (DMSoC). Timer 0, Timer 1, and Timer 3 are used

as general-purpose (GP) timers and can be programmed in 64-bit mode, dual 32-bit unchained

mode, or dual 32-bit chained mode; Timer 2 is used only as a watchdog timer. The GP timer modes

can be used to generate periodic interrupts or enhanced direct memory access (EDMA)

synchronization events and Real Time Output (RTO) events (Timer 3 only). The watchdog timer

mode is used to provide a recovery mechanism for the device in the event of a fault condition, such

as a non-exiting code loop.

- SPRUEE6 TMS320DM35x Digital Media System-on-Chip (DMSoC) General-Purpose Input/Output (GPIO) Reference Guide This document describes the general-purpose input/output (GPIO) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of the input by reading the state of an internal register. When configured as an output, you can write to an internal register to control the state driven on the output pin.

- <u>SPRUEE7</u> *TMS320DM35x Digital Media System-on-Chip (DMSoC) Pulse-Width Modulator (PWM)*\*\*Reference Guide This document describes the pulse-width modulator (PWM) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

- SPRUEH7 TMS320DM35x Digital Media System-on-Chip (DMSoC) DDR2/Mobile DDR (DDR2/mDDR) Memory Controller Reference Guide This document describes the DDR2/mDDR memory controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The DDR2/mDDR memory controller is used to interface with JESD79D-2A standard compliant DDR2 SDRAM and mobile DDR devices.

- SPRUF71 TMS320DM35x Digital Media System-on-Chip (DMSoC) Video Processing Front End (VPFE) Reference Guide This document describes the Video Processing Front End (VPFE) in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

- SPRUF72 TMS320DM35x Digital Media System-on-Chip (DMSoC) Video Processing Back End (VPBE) Reference Guide This document describes the Video Processing Back End (VPBE) in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

- SPRUF74 TMS320DM35x Digital Media System-on-Chip (DMSoC) Real-Time Out (RTO) Controller Reference Guide This document describes the Real Time Out (RTO) controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

- SPRUFC8 TMS320DM35x Digital Media System-on-Chip (DMSoC) Peripherals Overview

Reference Guide This document provides an overview of the peripherals in the TMS320DM35x

Digital Media System-on-Chip (DMSoC).

- <u>SPRAAR3</u> *Implementing DDR2/mDDR PCB Layout on the TMS320DM35x DMSoC* This provides board design recommendations and guidelines for DDR2 and mobile DDR.

#### **Trademarks**

## Video Processing Front End (VPFE)

## 1 Video Processing Front End Overview

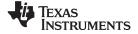

The Digital Media System-on-Chip (DMSoC), Figure 1, is a highly integrated, programmable platform for digital still/video cameras and other mobile imaging devices. Designed to offer camera manufacturers the ability to produce affordable DSC products with high picture quality, this device combines programmable image processing capability with a highly integrated imaging peripheral set. The device also enables seamless interface to most additional external devices required for a complete digital camera digital implementation via the Video Processing Front End Subsystem (VPFE). The interface is flexible enough to support various types of CCD and CMOS sensors, signal conditioning circuits, power management, SDRAM, SRAM, shutter, Iris and auto-focus motor controls.

Figure 1. Functional Block Diagram

## 1.1 Purpose of the Video Processing Front End

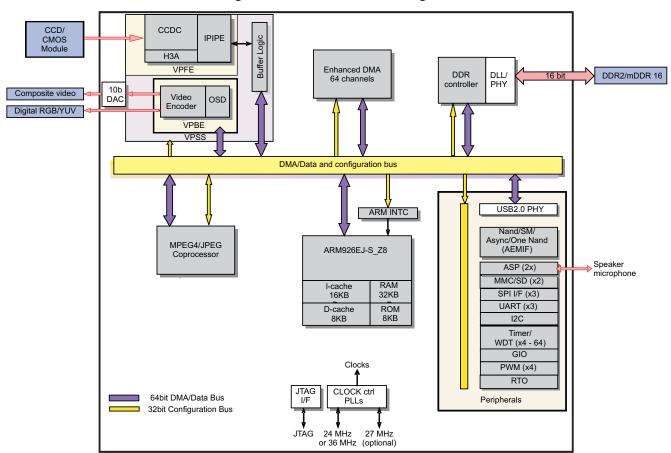

The device contains a Video Processing Subsystem (VPSS), Figure 2, that provides an input interface (Video Processing Front End or VPFE) for external imaging peripherals such as image sensors, video decoders, etc.; and an output interface (Video Processing Back End or VPBE) for display devices, such as analog SDTV displays, digital LCD panels, HDTV video encoders, etc.

In addition to these peripherals, there is a set of common buffer memory and DMA control to ensure efficient use of the DDR2/mDDR controller burst bandwidth. The buffer logic/memory is a unique block that is tailored for seamlessly integrating the VPSS into an image/video processing system. It acts as the primary source or sink to all the VPFE and VPBE modules that are either requesting or transferring data from/to DDR2/mDDR controller. In order to efficiently utilize the external DDR2/mDDR controller bandwidth, the buffer logic/memory interfaces with the DMA system via a high bandwidth bus (64-bit wide). The buffer logic/memory (divided into the read and write buffers and arbitration logic) is capable of performing the following functions. It is imperative that the VPSS utilize DDR2/mDDR controller bandwidth efficiently due to both its large bandwidth requirements and the real-time requirements of the VPSS modules.

Figure 2. Video Processing Subsystem (VPSS) Block Diagram

#### 1.2 Features

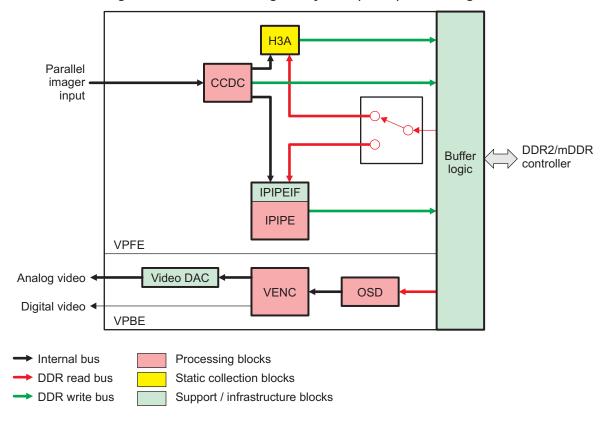

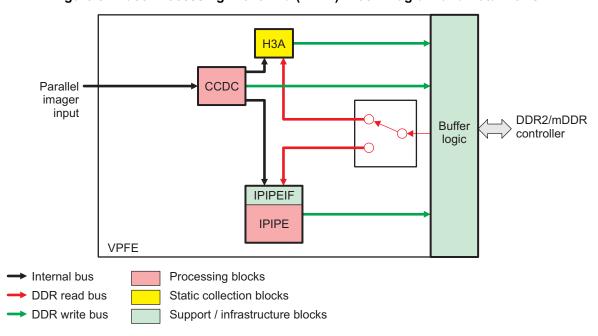

The VPFE block is comprised of the CCD Controller (CCDC), Image Pipe (IPIPE), Image Pipe Interface (IPIPEIF), and Hardware 3A Statistic Generator (H3A) blocks. Together, these modules provide the device with a powerful and flexible front-end interface. These modules can be broken down into two distinct types. The first type consists of major processing modules that are in the direct data flow path and affect the input image data stream. These are described below:

- The CCD Controller (CCDC) provides an interface to image sensors and digital video sources.

- The image pipe (IPIPE) is a parameterized hardwired image processing block whose image processing

functions can be customized for each sensor type to realize good still image quality as well supporting

video frame rates for digital still camera preview displays and video recording modes. An image resizer

is also fully integrated within this module. Additionally, the IPIPE contains the following statistic

collection function: histogram and the boundary signal calculator (for motion vector compensation).

In addition to the modules that directly affect that input image data, there is one independent module that provides statistics on the incoming images to aid designers of camera systems.

The hardware 3A (H3A) module is designed to support the control loops for auto focus (AF), auto white balance (AWB) and auto exposure (AE) by collecting metrics on the RAW image data from the CCD controller.

## 1.2.1 CCD Controller (CCDC)

The CCDC is responsible for accepting RAW (unprocessed) image/video data from a sensor (CMOS or CCD). In addition, the CCDC can accept YCbCr video data in numerous formats, typically from so-called video decoder devices. In the case of RAW inputs, the CCDC output requires additional image processing to transform the RAW input image to the final processed image. This processing can be done in the Image Pipe. The CCDC is programmed via control and parameter registers. The following features are supported by the CCDC module.

- Support for conventional Bayer pattern sensor format.