# Intel<sup>®</sup> Itanium<sup>®</sup> Processor Family System Abstraction Layer Specification

**Revision 3.4**

Document Number: 245359-009

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel Itanium<sup>®</sup> processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2000-2008, Intel Corporation.

\*Other brands and names are the property of their respective owners.

# **Contents**

| 1 | Introd       | luction                                                          |    |

|---|--------------|------------------------------------------------------------------|----|

|   | 1.1          | Objectives                                                       |    |

|   | 1.2          | Firmware Model                                                   |    |

|   | 1.3          | System Abstraction Layer Overview                                |    |

|   | 1.4          | Firmware Entrypoints                                             |    |

|   | 1.5          | Related Documents                                                |    |

|   | 1.6          | Revision History                                                 | 13 |

| 2 | Platfo       | rm Requirements                                                  | 15 |

|   | 2.1          | Firmware Address Space                                           | 15 |

|   | 2.2          | PAL/SAL ROM Space                                                |    |

|   | 2.3          | Simplified Firmware Address Map                                  |    |

|   | 2.4          | Example Firmware Organization Using a Protected Boot Block       |    |

|   | 2.5          | Firmware Interface Table                                         |    |

|   | 2.6          | Resources Required for Legacy Compatibility                      |    |

|   | 2.7          | Chipset and Shadowing Requirements                               |    |

|   | 2.8          | Platform Support for Variant Architectural Features              |    |

|   | 2.9          | Platform Considerations Related to Processor Physical Location   |    |

|   | 2.10<br>2.11 | Non-Volatile Memory Requirements                                 |    |

|   |              | ·                                                                |    |

| 3 | Boot S       | Sequence                                                         |    |

|   | 3.1          | Overview of the Code Flow after Hard Reset                       |    |

|   | 3.2          | SAL_RESET                                                        |    |

|   | 3.3          | Itanium® Architecture-based Operating System Loader Requirements | 43 |

| 4 | Machi        | ne Checks                                                        | 49 |

|   | 4.1          | SAL_CHECK                                                        | 49 |

|   | 4.2          | Corrected Machine Checks                                         |    |

|   | 4.3          | Platform Errors                                                  | 53 |

|   | 4.4          | Polling for Corrected Errors                                     |    |

|   | 4.5          | OS_MCA                                                           |    |

|   | 4.6          | Procedures Used in Machine Check Handling                        | 56 |

|   | 4.7          | Machine Checks in MP Configurations                              |    |

|   | 4.8          | OS_MCA Hand-off State                                            | 66 |

| 5 | Initial      | ization Event                                                    | 69 |

|   | 5.1          | SAL_INIT                                                         | 69 |

|   | 5.2          | OS_INIT                                                          | 70 |

|   | 5.3          | OS_INIT Hand-off State                                           |    |

|   | 5.4          | Return from OS_INIT Procedure                                    |    |

|   | 5.5          | MP INIT Support                                                  | 72 |

| 6 | Platfo       | rm Management Interruptions                                      | 73 |

|   | 6.1          | SALE_PMI Overview                                                |    |

|   | 6.2          | SALE_PMI Initialization                                          |    |

|   | 6.3          | SALE_PMI Processing                                              | 74 |

|   | 6.4          | Special Considerations for Multiprocessor Configurations         | 74 |

| 7 | IΔ-32        | Support (Optional)                                               | 75 |

| , | 7.1          | IA-32 Support Model                                              |    |

|   | 7.1          | IA-32 Support Requirements                                       |    |

| _ |              |                                                                  |    |

| 8 | •            | g Conventions                                                    |    |

|   | 8.1          | SAL Calling Conventions                                          |    |

|   | 8.2          | Software Interface Conventions for SAL Procedures                | 85 |

| 9   | SAL P      | Procedures                                                     | 89  |

|-----|------------|----------------------------------------------------------------|-----|

|     | 9.1        | SAL Runtime Services Overview                                  |     |

|     | 9.2        | SAL Procedures that Invoke PAL Procedures                      | 91  |

|     | 9.3        | SAL Procedure Summary                                          | 91  |

| Α   | Gloss      | ary                                                            | 117 |

| В   |            | Record Structures                                              |     |

| D   |            |                                                                |     |

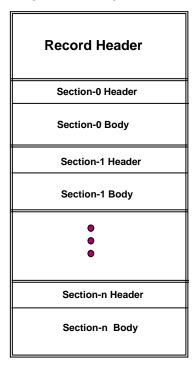

|     | B.1<br>B.2 | Overview Error Record Structure                                |     |

|     | Б.2        | EITOI Record Structure                                         | 1∠3 |

|     |            |                                                                |     |

| Fig | jures      | S                                                              |     |

| 3   | 1-1        | Firmware Model                                                 | 8   |

|     | 1-2        | Firmware Services Model                                        |     |

|     | 1-3        | Firmware Entrypoints Logical Model                             |     |

|     | 2-1        | Simplified Firmware Address Map                                |     |

|     | 2-2        | Firmware Address Map                                           |     |

|     | 2-3        | Firmware Address Map with Split PAL_A Components               |     |

|     | 2-3<br>2-4 | Firmware Interface Table                                       |     |

|     | 2-4<br>2-5 |                                                                |     |

|     |            | Firmware Interface Table Entry                                 |     |

|     | 3-1        | Local ID Register Format                                       |     |

|     | 3-2        | Control Flow of Boot Process in a Multiprocessor Configuration |     |

|     | 3-3        | Wake-up Memory Variable Format                                 |     |

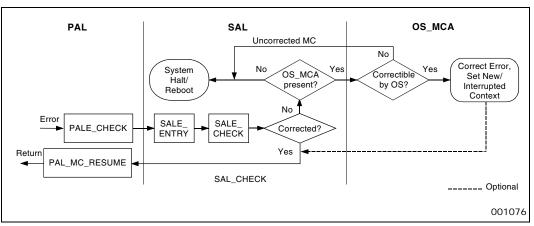

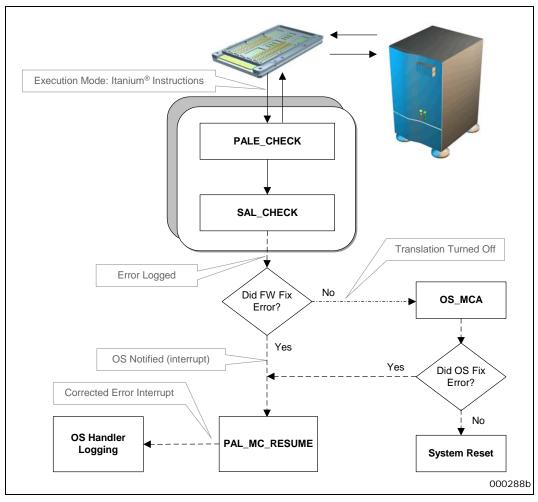

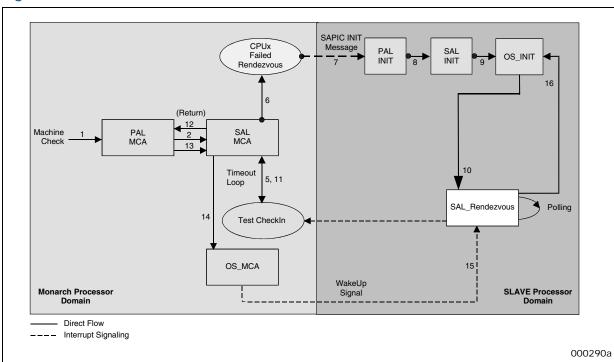

|     | 4-1        | Overview of Machine Check Flow                                 |     |

|     | 4-2        | Machine Check Code Flow                                        |     |

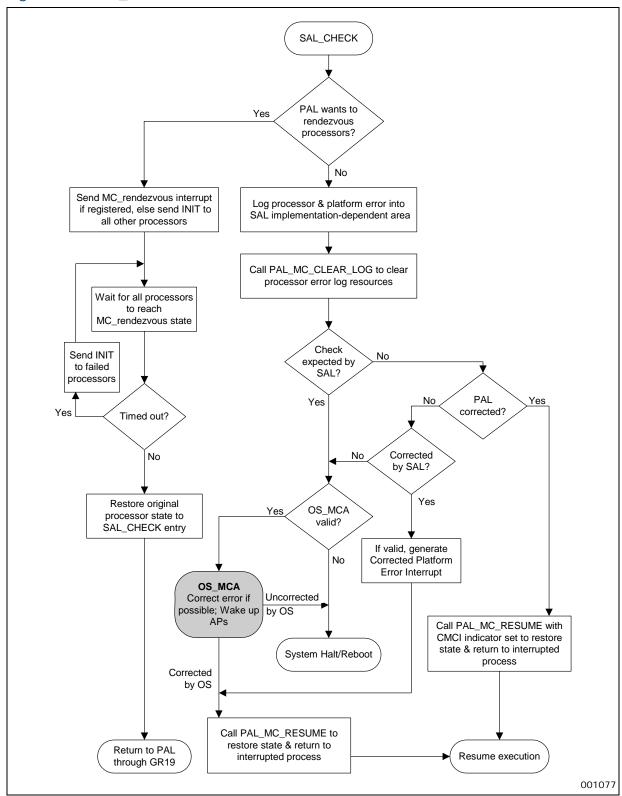

|     | 4-3        | SAL_CHECK Detailed Flow on the Monarch Processor               |     |

|     | 4-4        | Normal SAL Rendezvous Flow                                     |     |

|     | 4-5        | Failed SAL Rendezvous Flow                                     |     |

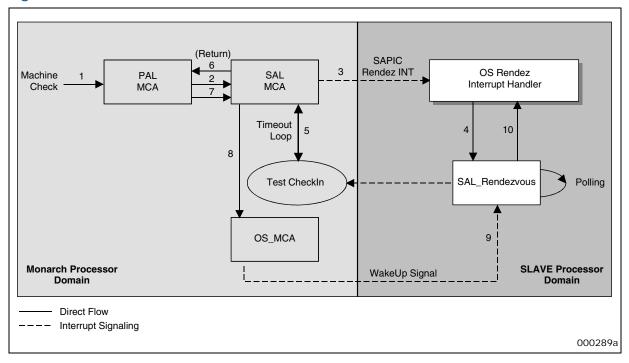

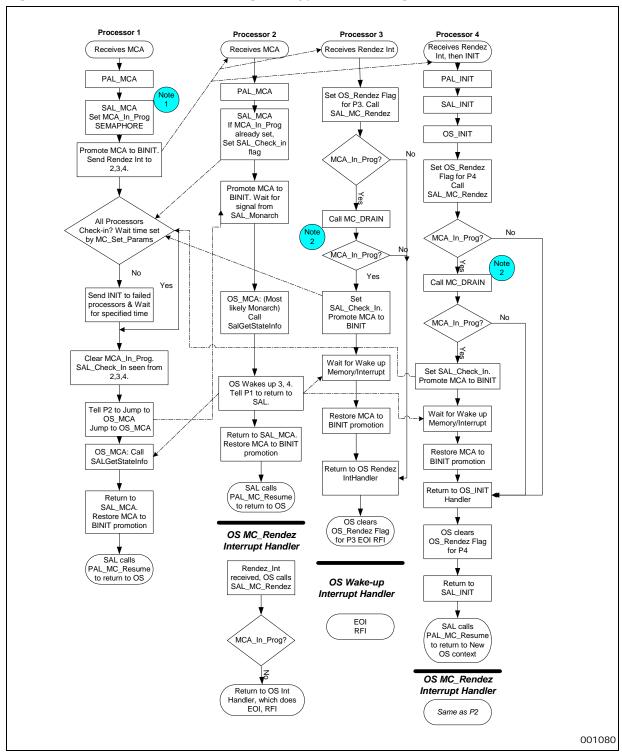

|     | 4-6        | Machine Check Handling in a Typical MP Configuration           |     |

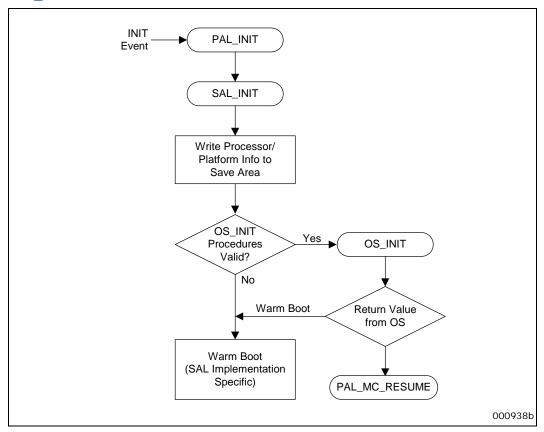

|     | 5-1        | SAL_INIT Control Flow                                          |     |

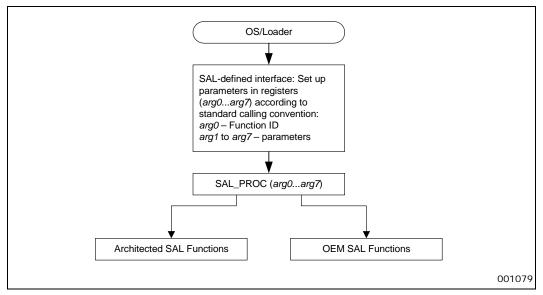

|     | 8-1        | Control Flow of the SAL Procedure Interface                    |     |

|     | 9-1        | Layout of plat_log_info Return Value                           | 115 |

|     |            |                                                                |     |

| Tal | bles       |                                                                |     |

| ıaı |            | Firmware Address Space                                         | 15  |

|     | 2-1        | ·                                                              |     |

|     | 2-2        | FIT Types                                                      |     |

|     | 2-3        | 1 MB Compatibility Memory Address Space                        |     |

|     | 2-4        | IA-32 Compatibility I/O Ports                                  |     |

|     | 3-1        | SAL Actions Based on Processor Self-Test State                 |     |

|     | 3-2        | OS_BOOT_RENDEZ to SAL System Register Conventions              |     |

|     | 3-3        | SAL System Table Header                                        |     |

|     | 3-4        | SAL System Table Entry Types                                   |     |

|     | 3-5        | Entrypoint Descriptor Entry Format                             |     |

|     | 3-6        | Platform Features Descriptor Entry                             |     |

|     | 3-7        | Translation Register Descriptor Entry                          |     |

|     | 3-8        | Purge Translation Cache Coherence Domain Entry                 |     |

|     | 3-9        | Coherence Domain Information                                   |     |

|     | 3-10       | Application Processor Wake-up Descriptor Entry                 |     |

|     | 8-1        | Definition of Terms                                            |     |

|     | 8-2        | State Requirements for PSR                                     |     |

|     | 8-3        | System Register Conventions                                    | 82  |

| 8-4 | General Registers – Standard Calling Conventions   |     |

|-----|----------------------------------------------------|-----|

|     | SAL Return Status                                  |     |

|     | SAL Procedures Invoking PAL Procedures             |     |

| 9-2 | SAL Procedures                                     | 91  |

|     | GUID Format                                        |     |

| B-2 | GUID Ordering in Memory                            | 126 |

| B-3 | Error Section Error_Recovery_Info Field Definition | 127 |

| B-4 | Format of Variable Length Info Structure           | 134 |

| B-5 | Error Status Fields                                | 144 |

| B-6 | Error Types                                        | 145 |

## 1 Introduction

### 1.1 Objectives

This document describes the functionality of the System Abstraction Layer (SAL) for Itanium $^{\circledR}$  architecture-based systems.

This document specifies requirements to develop platform firmware for Itanium architecture-based systems. A companion document, the *Unified Extensible Firmware Interface Specification*, describes additional interfaces that must be implemented to access devices on the platform. The *Unified Extensible Firmware Interface Specification* is a requirement for Itanium architecture-based firmware.

This document is intended for firmware designers, system designers, and writers of diagnostic and low level operating system software. This document is an architectural specification describing the platform-dependent firmware interfaces needed to support the objectives listed below. It does not require a specific implementation, nor is it intended to document PC infrastructure specifications.

The primary objectives of Itanium architecture-based firmware are to:

- Enable boot of Itanium architecture-based operating systems.

- Ensure that the firmware interfaces encapsulate the platform implementation differences within the hardware abstraction layers and device driver layers of operating systems.

- Separate the platform abstraction from the processor abstraction.

- Enable platform differentiation, hardware innovation, and optimization of Itanium architecture-based platforms.

- Support the scaling of systems from the low-end to the high-end including servers, workstations, mainframe alternatives, and supercomputers. Features supported will include high availability, error logging and recovery, large memory support, multiprocessing, and broader and deeper I/O hierarchies (possibly greater than 100 I/O cards).

- While using Itanium instructions is preferred, IA-32 BIOS code can be used in SAL.

The extent of the IA-32 BIOS reuse is implementation-dependent, but all SAL entrypoints from the Processor Abstraction Layer (PAL) will use the Itanium system environment.

- Optionally, enable the use of legacy PC peripherals, option ROMs, and PCI cards with IA-32 Plug-and-Play expansion ROMs.

#### 1.2 Firmware Model

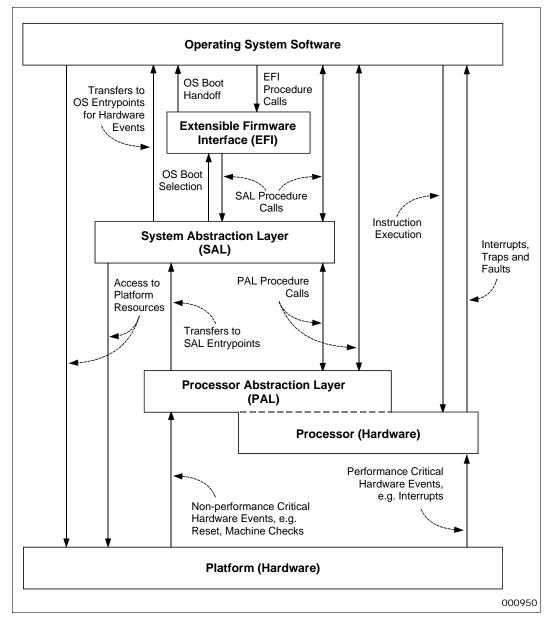

As shown in Figure 1-1, Itanium architecture-based firmware has three components:

- 1. Processor Abstraction Layer

- 2. System Abstraction Layer

- 3. Extensible Firmware Interface

Figure 1-1. Firmware Model

PAL encapsulates processor implementation-specific features and is required in the Itanium architecture. PAL is not multiprocessor (MP) aware but is thread-aware for Itanium architecture processors that support multi-threading. SAL is the platform-specific firmware component that isolates operating systems and other higher level software from implementation differences in the platform. EFI provides a legacy free API interface to the operating system loader.

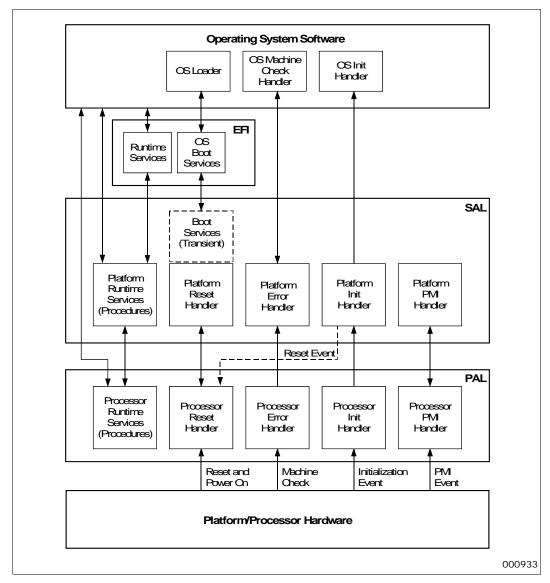

PAL, SAL, and EFI together provide system initialization and boot, Machine Check Abort (MCA) handling, Platform Management Interrupt (PMI) handling, and other processor and system functions which would vary between implementations. The interaction of the various functional firmware blocks is shown in Figure 1-2.

Figure 1-2. Firmware Services Model

## 1.3 System Abstraction Layer Overview

SAL provides the following functionality for an Itanium architecture-based platform:

- Initialize, configure, and test the platform hardware. This includes the memory and I/O subsystems, the necessary boot devices, and platform-specific hardware.

- Select the bootstrap processor (BSP) in a MP platform and set the configurable processor features. An Itanium architecture processor has its own PAL firmware for initialization and test. PAL has no knowledge of the platform, so further platform-specific action is necessary to integrate the processor with the rest of the system. For example, SAL must configure, test, and initialize memory before the processor cache to memory interface can be established and tested.

- Optionally encapsulate and provide the environment to run IA-32 BIOS and plug-in cards containing IA-32 Option ROMs.

- Provide low level service routines to aid EFI and the operating system loader in establishing the environment necessary for the operating system.

- Provide common data structures to the operating system to convey initialization and configuration information.

- Provide the necessary services and common infrastructure to support MP configurations.

- Provide runtime service routines to encapsulate those functions of the platform for EFI and the operating system while they are running.

- Provide the functions to aid in the logging and recovery from Machine Check conditions (SAL\_CHECK and OS\_MCA interface).

- Provide the functions necessary to aid in the logging and recovery from INIT conditions (SAL\_INIT and OS\_INIT interface).

- Provide the functions necessary to handle the platform management events (SALE\_PMI interface).

- · Optionally, provide the functions to aid in the recovery from a corrupted boot ROM.

- Optionally, provide a user interface to aid in system configuration, information passing, and troubleshooting.

### 1.4 Firmware Entrypoints

Figure 1-3. Firmware Entrypoints Logical Model

### 1.4.1 Processor Abstraction Layer Entrypoints

The following hardware events can trigger the execution of a PAL entrypoint:

- · Power-on/reset

- · Hardware errors (both correctable and uncorrectable)

- · Initialization request

- PMIs

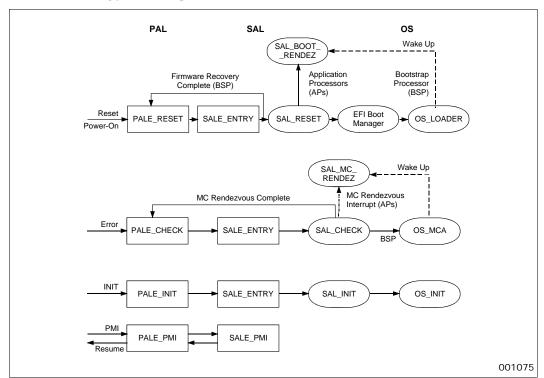

These hardware events trigger the execution of one of the following PAL entrypoints (as shown in Figure 1-1 and Figure 1-3):

- 1. PALE\_RESET initializes the processor following power-on or reset. This PAL entrypoint calls the SALE\_ENTRY entrypoint in the SAL to test for firmware recovery. SALE\_ENTRY, in turn, calls SAL\_RECOVERY\_CHECK to perform recovery if the firmware recovery indication is present on the platform, otherwise it returns to PAL via SALE\_ENTRY. If firmware recovery is required, the SAL recovery code will accomplish the firmware recovery function, reset the recovery indication, and then trigger a system wide reset, causing re-entry into the PALE\_RESET. If SAL reports to PAL that a firmware recovery condition does not exist, PAL conducts additional processor tests and then branches to SALE\_ENTRY. SALE\_ENTRY then branches to a procedure within SAL called SAL\_RESET to initialize the system.

- 2. PALE\_CHECK saves the minimal processor state, determines if errors are processor related, saves processor-related error information, and corrects errors where possible (for example, by flushing a corrupted instruction cache line and marking the cache line as unusable). PALE\_CHECK then branches to the SALE\_ENTRY entrypoint. SALE\_ENTRY, in turn, branches to SAL\_CHECK to complete error logging, correction, and reporting. PALE\_CHECK is entered as a response to processor or platform errors.

- 3. PALE\_INIT is entered as a response to an initialization event. PALE\_INIT saves minimal processor state and branches to SALE\_ENTRY. SALE\_ENTRY, in turn, branches to SAL\_INIT.

- 4. PALE\_PMI is entered as a response to a platform management event. PALE\_PMI determines the type of platform management event and branches to SALE\_PMI for certain conditions.

## 1.4.2 System Abstraction Layer Entrypoints

Following are the entrypoints from PAL into SAL:

SALE\_ENTRY is the entrypoint PAL branches to after a power-on, reset, machine check, or initialization event. The code at this entrypoint uses the hand-off value in a general register to jump to SAL for reset, firmware recovery, machine check, and INIT events.

These functions are available from SALE ENTRY:

- SAL\_RESET within SAL is entered for system initialization after PAL has initialized the processor. SAL\_RESET functionality is described in Chapter 3.

- SAL\_RECOVERY\_CHECK within SAL is entered after a power-on reset from PAL to test if a recovery condition is present. Only SAL has enough knowledge of platform resources to determine if a firmware recovery condition is present.

- SAL\_CHECK within SAL is entered for logging errors and correcting platform related errors where possible. SAL\_CHECK functionality is described in Chapter 4.

- SAL\_INIT within SAL is entered for saving the state of the system and performing additional functions as defined in Chapter 5.

- 2. SALE\_PMI is the entrypoint for handling platform management events in an implementation-dependent manner.

### 1.4.3 Operating System Handlers

There are several entrypoints from SAL into an operating system (or equivalent software):

- OS\_LOADER is the entrypoint the BSP enters from SAL\_RESET after the system has been initialized and the operating system loader image has been loaded by the EFI component from the boot device. Refer to the *Unified Extensible Firmware Interface Specification* for details.

- OS\_BOOT\_RENDEZ is the operating system MP rendezvous handler. It is entered

from SAL when operating system loader on the BSP wakes up the application

processors (APs), to permit synchronization of APs in an MP environment.

- OS\_MCA is the operating system MCA handler that is called from SAL\_CHECK to allow the OS to handle the machine checks that are not corrected by hardware, PAL, or SAL.

- OS\_INIT is the operating system handler that is called from SAL\_INIT to handle a valid INIT event.

#### 1.5 Related Documents

The following documents contain additional material related to Itanium architecture-based platforms:

- Advanced Configuration and Power Interface Specification Intel/Microsoft/Toshiba

- BIOS Boot Specification, 1996 Compaq/Phoenix/Intel

- BIOS Enhanced Disk Drive Specification, Version 3.0 Phoenix

- Bootable CD-ROM Format Specification, 1994 Phoenix/IBM

- CBIOS for IBM Computers and Compatibles Phoenix

- Unified Extensible Firmware Interface Specification UEFI Forum

- Intelligent Platform Management Initiative Specification Intel, NEC, HP, Dell

- Intel<sup>®</sup> Itanium<sup>®</sup> Architecture Software Developer's Manual Intel

- Intel® Itanium® Processor Family Error Handling Guide Intel

- Itanium<sup>®</sup> Software Conventions and Runtime Architecture Guide Intel

- PCI BIOS Specification PCI SIG

- PCI Local Bus Specification PCI SIG

- · Plug and Play ISA Specification, 1994 Microsoft

## 1.6 Revision History

The revision number of the SAL specification supported by the SAL implementation is specified in the SAL System Table Header (refer to Table 3-3, "SAL System Table Header").

| Date          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2009      | Revision 3.4. In Section B.2.4.8, the PCIe 1.1/2.0 error section PCIe_OEM_DATA_STRUCT has been aligned to an 8-byte boundary. The error sections for processor machine check, deconfigured processor self-test errors and PCIe 1.1/2.0 VARIABLE_LENGTH_DATA_OFFSET values have been corrected to reflect the offset from the beginning of the error section to the variable-length data portion of the error section.                                                                                                                                                                                                                                                                                                                                                                             |

| March 2008    | Revision 3.3. Added Error Section clarification for latent error handling. Added clarification for PAL relocation. Removed non-mapped resource runtime access section. Added SAL br0 loop changes. Added SAL arg0 usage clarification. Added OS_MCA handling clarifications. Incorporated changes from SAL Specification Update June 2004 and SAL Specification Update August 2005. Incorporated changes from SAL Specification Update November 2006, but dropped Document Change 1 and 2.                                                                                                                                                                                                                                                                                                        |

| December 2003 | Removed references to IA-32 Operating System boot. Clarified OS_BOOT_RENDEZ usage and handoff requirements. Added SAL_PHYSICAL_ID_INFO call. Added extensions to SAL procedures to address PCI Express. Added clarifications to address multithreaded processors. Clarified use of SAL_SET_VECTORS checksum. Added example of GUID memory ordering. Added additional information on SAL procedure error return values. Clarified usage of fields in the SAL Error Record Header and Error Section Header. Included notes on SAL use of Translation Registers (TRs). Added Error Record alignment requirements. Updated glossary definitions. Clarified memory state on firmware to OS handoff. Clarified SAL Revision numbering. Incorporated changes from SAL Specification Update January 2003. |

| November 2002 | Split PAL_A information added. Enhancements and clarifications to SAL_CACHE_FLUSH, SAL_MC_RENDEZ, and SAL_GET_STATE_INFO calls. Entrypoint descriptor field and memory attribute aliasing attributes added. IVA requirements in virtual addressing mode specified, and SAL/PAL flow for PAL firmware-corrected error modified. Error record revision value update and usage requirements defined. Clarifications and extensions to the error record and section headers, memory error section, PCI bus sections and PCI component sections.                                                                                                                                                                                                                                                       |

| July 2001     | Platform requirement clarifications, Boot sequence clarifications, Additions to OS restrictions for boot sequence, Changes to MCA SAL_CHECK, Platform Errors, and OS_MCA sections, Added SAL procedures callable by OS_INIT, Clarification to Interface Conventions to SAL Procedures, Added changes regarding re-entrancy of SAL Runtime Services, Clarifications to SAL procedure definitions, Added terms to the glossary                                                                                                                                                                                                                                                                                                                                                                      |

| January 2001  | MCA related changes, Platform Error definition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| July 2000     | Reflected changes in MCA handling due to PAL MCA changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| January 2000  | Changes to some SAL procedure definitions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| June 1999     | Defined hand-off to EFI, Removed NVRAM functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| August 1998   | Defined NVRAM record formats, changes to SAL procedures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| February 1998 | Initial definition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# 2 Platform Requirements

### 2.1 Firmware Address Space

The firmware address space occupies the 16 MB region below 4 GB (addresses 0xFF00\_0000 through 0xFFFF\_FFFF). This address space is shown in Table 2-1.

#### Table 2-1. Firmware Address Space

| 0xFFFF_FFFF |               |

|-------------|---------------|

|             | PAL/SAL ROM   |

|             |               |

|             |               |

|             | SAL Resources |

| 0xFF00_0000 |               |

The firmware address space is logically partitioned into two major functional blocks: the ROM area (shared by the SAL and PAL) and the SAL resources area. The ROM area is placed in the address space such that its ending address is 0xFFFF\_FFFF. The SAL resources area occupies the portion of 16 MB firmware address space not occupied by the ROM area. SAL code can use the special hardware resources that the platform has implemented in the SAL Resources area. The hardware resources may include scratch RAM, non-volatile memory (NVRAM), environment control, and status registers. The location of the hardware resources within the SAL resources area is platform-dependent.

## 2.2 PAL/SAL ROM Space

The PAL/SAL ROM space within the firmware address space must contain the PAL and SAL code areas and a table called the Firmware Interface Table (FIT). See Section 2.5.

PAL code is broken into two subcomponents:

- PAL A, which is independent of processor stepping.

- PAL\_B, which is processor stepping-dependent.

These two subcomponents are required. The PAL\_A block contains a limited subset of PAL procedures that can be invoked by SAL while performing a firmware recovery. (Refer to Volume 2 of the <code>Intel® Itanium® Architecture Software Developer's Manual</code> for details.) The PAL\_B block contains the PAL procedures that can be invoked by SAL and the operating system.

In a similar fashion, SAL code can be broken into two subcomponents. Unlike the PAL, the SAL subcomponents need not be separate components:

- SAL\_A which contains the SALE\_ENTRY entrypoint and code needed for firmware recovery.

- SAL\_B which contains code to test and initialize the platform.

The PAL\_A, PAL\_B, SAL, and FIT components are architecturally required.

PAL A code can transition to:

- Code in the PAL\_B using the FIT. First, the beginning address of the PAL\_B block is determined from the FIT. Then, the entrypoints within the PAL\_B block (for example, PAL\_RESET) are determined in a PAL implementation-dependent manner.

- Code in the SAL address space at SALE\_ENTRY, which serves as the entrypoint for reset, recovery, machine check and INIT events.

In order to conserve space in the firmware ROM, portions of the SAL code may be compressed. SAL code that is executed out of ROM such as early stages of the Reset sequence and code for handling Machine check and INIT cannot be compressed.

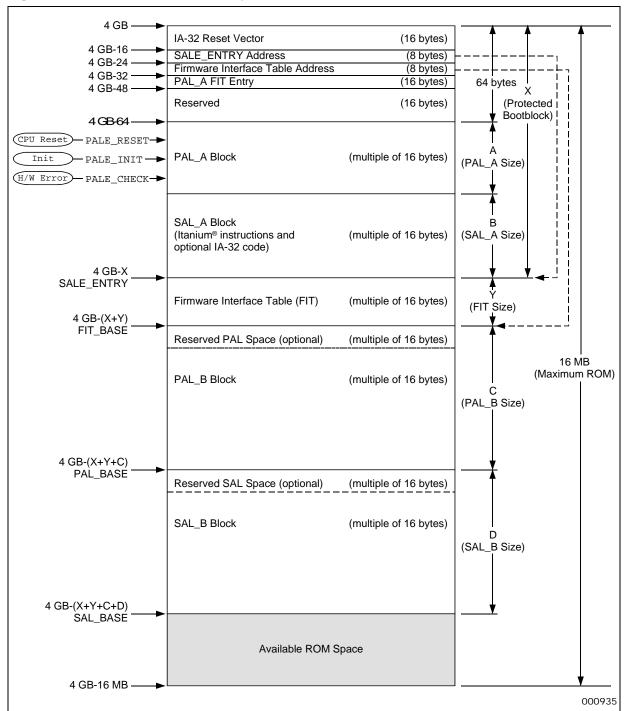

## 2.3 Simplified Firmware Address Map

A simplified example of the firmware address map that shows the *minimum* architectural components is shown in Figure 2-1. Refer to Section 2.4.1 for description of the fields. This layout cannot be used with a protected boot block.

# 2.4 Example Firmware Organization Using a Protected Boot Block

This section describes a typical firmware organization using flash ROM that contains a protected boot block.

A protected boot block refers to a block of the flash ROM that the hardware protects from modification. Code in this block can contain logic to restore PAL/SAL code in the erasable portion of the flash part after a previous flash programming attempt has been accidentally aborted. Firmware using a protected boot block requires some data structures in addition to the minimum architectural requirements discussed earlier.

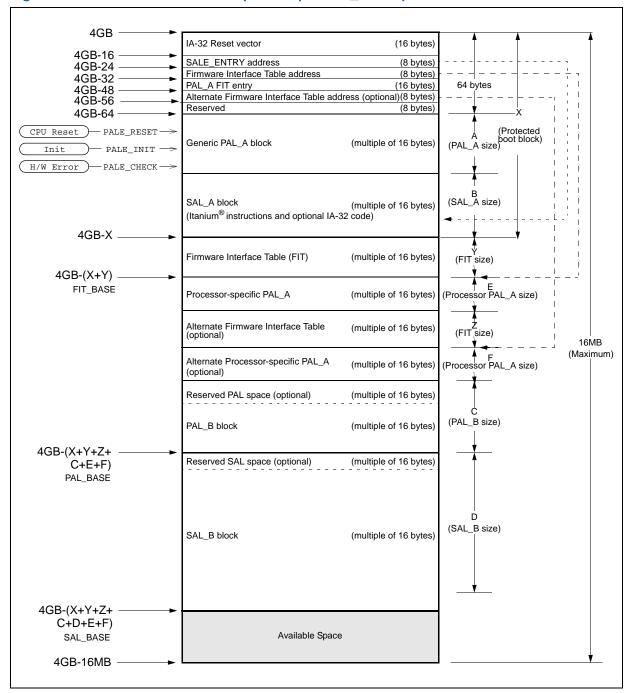

There are two primary layouts of the firmware address space that support a protected boot block. The first layout (shown in Figure 2-2) has one PAL\_A component. In this layout, the PAL\_A component must be within the protected boot block.

The second layout (shown in Figure 2-3) splits the PAL\_A block into two components. The first component is referred to as the generic PAL\_A and the second component is the processor-specific PAL\_A. The generic PAL\_A resides in the protected boot block and will work across processor generations for a given platform. The processor-specific PAL\_A resides outside the protected boot block and is particular to processor generation.

In both layouts, the SALE\_ENTRY entrypoint and the code needed for firmware recovery (located in SAL\_A) must be located in the protected boot block.

4 GB -IA-32 Reset Vector (16 bytes) 4 GB-16 -SAL Entrypoint (SALE\_ENTRY) (8 bytes) 4 GB-24 -Firmware Interface Table Address (8 bytes) 4 GB-32 -64 bytes FIT entry for PAL\_A (16 bytes) 4 GB-48 -Reserved (16 bytes) 4 GB-64 -(CPU Reset)—PALE\_RESET -PAL\_A Binary Block (multiple of 16 bytes) >—PALE\_INIT —▶ Init (PAL\_A Size) (H/W Error)—PALE\_CHECK -PAL\_B Binary Block (multiple of 16 bytes) (PAL B Size) 4 GB - (A+B+64) -Firmware Interface Table (FIT) (multiple of 16 bytes) (FIT Size) SAL\_A Binary Block (multiple of 16 bytes) (SAL\_A Size) SALE\_ENTRY -16 MB (Maximum 4 GB -ROM) (A+B+64+Y+C) Available ROM Space 4 GB-16 MB -001078

Figure 2-1. Simplified Firmware Address Map

## 2.4.1 Firmware Components

The firmware address space is shared by the SAL and the PAL. Some of the SAL/PAL boundaries are implementation-dependent. The firmware address space contains several regions and locations as shown in Figure 2-2 and Figure 2-3 below for a typical implementation.

The firmware address space contains the following regions and locations:

• The 16 bytes at (4 GB – 16) contains the IA-32 reset vector for legacy compatibility.

Figure 2-2. Firmware Address Map

Figure 2-3. Firmware Address Map with Split PAL\_A Components

- The 8 bytes at (4 GB 24) contain the address of the SALE\_ENTRY entrypoint. Bit 63 of this address must be set to 1 to specify the uncacheable memory attribute in physical addressing mode.

- The 8 bytes at (4 GB 32) contain the pointer to the FIT. Bit 63 of this address

must be set to 1. The FIT need not be located immediately before the protected

boot block. However, the FIT cannot be moved to a different location since its

address is contained in the protected boot block.

- The 16 bytes at (4 GB 48) describe the characteristics of the PAL\_A component (or generic PAL\_A in the split PAL\_A model) in the ROM: base address, size, version number, type, and so on. This is represented in the FIT entry format. Bit 63 of the address field within this FIT entry must be set to 1 and the type field must have a value of 0x0F.

- The 8 bytes at 0xFFFF\_FFC8 (4 GB-56) contains the physical address of the Alternate FIT. This pointer is optional and is only needed if the firmware contains an alternate FIT table. If no alternate FIT table is provided, a value of 0x0 should be encoded in this entry.

- The 8 bytes at (4 GB 64) are reserved.

- The PAL\_A code (also known as the generic PAL\_A code in the split PAL\_A model) resides below the (4GB 64) address. This variable size area contains the hardware-triggered entrypoints (PALE\_RESET, PALE\_INIT, and PALE\_CHECK). In the model where PAL\_A is not split, the PAL\_A code will perform minimum processor initialization. In the split PAL\_A model, the generic PAL\_A will search the FIT table(s) to find the processor-specific PAL\_A code. It will then branch to this code to perform the processor-specific initialization:

- The PAL\_A code block must be a multiple of 16 bytes in length. PAL\_A uses the FIT entry of the PAL\_B to reach continuation entrypoints in PAL\_B for reset, machine check, and initialization.

- The code in the PAL\_A block(s) contains enough capability to initialize the processor, invoke the SALE\_ENTRY procedure for test of the recovery indication, and continue with normal PAL execution in the PAL\_B code area.

- SAL\_A code occupies the bottom of the protected boot block. To provide maximum flexibility and to conserve space in the protected boot block, this area will primarily contain code for firmware recovery. When entered for other conditions such as normal reset, machine check, or initialization, the code in this block will find the continuation entrypoints in the SAL\_B block (using the FIT or other means) and jump to the same. The method by which SALE\_ENTRY code reaches continuation entrypoints in SAL\_B for reset, machine check, and initialization is SAL implementation-dependent.

#### Note:

The sizes of the PAL\_A (generic PAL\_A in the split PAL\_A model) and SAL\_A code blocks shown in Figure 2-2 and Figure 2-3 are not needed during firmware execution but may be needed by the utility that merges these components to format the protected boot block portion of the flash ROM.

- Below the protected boot block is the FIT. It consists of 16-byte entries containing starting address and size information of the remaining firmware components.

Optionally, an alternate FIT may be included in the firmware. The alternate FIT will only be used if the primary FIT failed its checksum. This feature allows hand-off to the SAL recovery code, even if there is a primary FIT checksum failure. Refer to Section 2.5 for FIT details.

- Below the FIT(s) is the processor-specific PAL\_A. This component is only available

on processors that support a split PAL\_A firmware model. One processor-specific

PAL\_A is architecturally required in this model. The firmware may optionally contain

two or more processor-specific PAL\_A components.

- Below the FIT is the code for the IA-32 BIOS, EFI, SAL\_B, and PAL\_B components.

There are no ordering requirements for the firmware components within the flash

ROM.

- The PAL\_B binary block contains PAL code that is not required for firmware recovery. The PAL\_B code area is a multiple of 16 bytes in length and must be aligned on a 32K-byte boundary. PAL\_B's FIT entry contains the address and size of the PAL\_B binary block.

- The remainder of the SAL/PAL ROM area is occupied by the SAL\_B code. SAL\_B's

FIT entry (if present in the FIT) contains the address and size of the SAL\_B binary

block.

Note:

Code within SAL (SAL\_A and SAL\_B) may include IA-32 code. The location of the SAL\_B and IA-32 BIOS code within the SAL/PAL ROM area is implementation- dependent. Some SAL implementations may separate the code containing Itanium instructions and IA-32 instructions as separate firmware blocks with unique FIT entry types. In a similar fashion, the SAL\_B component may include the EFI component or a separate FIT entry may point to the EFI component.

#### 2.5 Firmware Interface Table

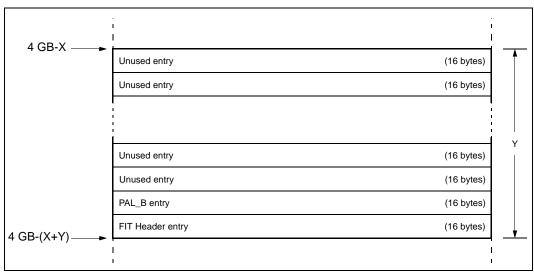

The FIT contains starting addresses and sizes for the firmware components that are outside the protected boot block. Because these code blocks may be compiled at different times and places, code in one block (such as PAL\_A) cannot branch to code in another block (such as PAL\_B) directly. The FIT allows code in one block to find entrypoints in another. Figure 2-4 shows the FIT layout.

Figure 2-4. Firmware Interface Table

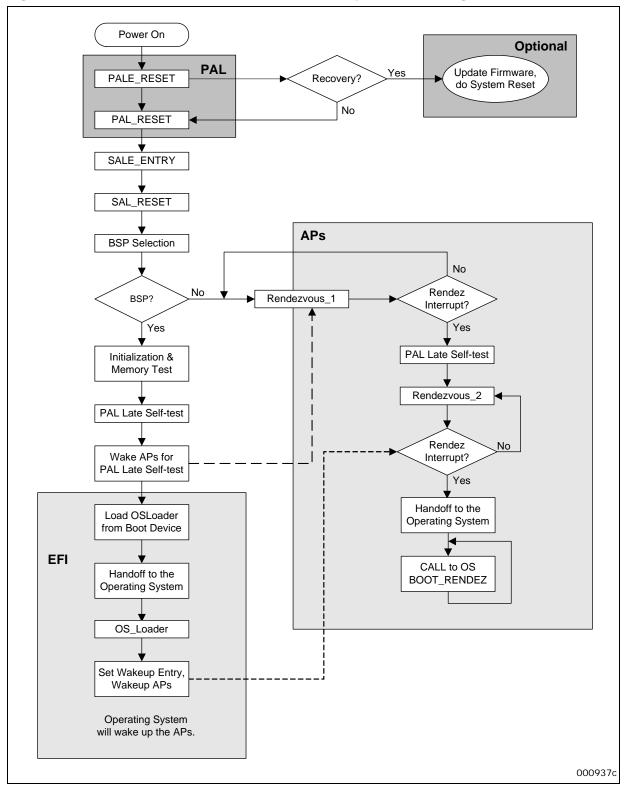

Each active FIT entry contains information for the corresponding firmware component. The first two entries are used to describe the FIT table itself and the PAL\_B block respectively and these two entries are architecturally required. FIT entries shall be in ascending order of entry types, otherwise firmware behavior is unpredictable. The FIT entry format is shown in Figure 2-5.

Figure 2-5. Firmware Interface Table Entry

Address is the base address of the component and it must be aligned on a 16-byte boundary. For the FIT Header entry, this field contains the ASCII value of '\_FIT\_<sp><sp> <sp>' where <sp> represents the space character. For the processor-specific PAL\_A and PAL\_B entries, bit 63 of the address field must be set to 1 to indicate the uncacheable memory attribute in physical addressing mode. The PAL\_B component must be aligned on a 32K-byte boundary.

Size is the size of the component in paragraphs of 16 bytes.

*Version* contains the component's version number. For the FIT Header Entry, the value in this field will indicate the revision number of the FIT data structure.

$C_{-}V$  is a one bit field that indicates whether the component has a valid checksum. If this bit is zero, the value in the *Chksum* field is not valid.

Type contains the seven-bit type code for the entry. Types are defined in Table 2-2.

Table 2-2. FIT Types

| Туре                                                           | Meaning                                                                                                |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 0x00<br>0x01<br>0x02-0x0D<br>0x0E<br>0x0F<br>0x10-0x7E<br>0x7F | FIT Header entry PAL_B Reserved Processor-specific Pal_A PAL_A (also generic PAL_A) OEM-defined Unused |

The type code of 0x0F is used for PAL\_A. Since PAL\_A's binary image is located near the end of the 4 GB firmware address space (flash ROM organization with protected boot block), its FIT entry is also located within the protected boot block (at 4 GB - 48) and not in the FIT table. The OEM may define unique types for one or more blocks of SAL\_B, EFI, IA-32 BIOS, and so on, within the OEM-defined type range of 0x10 to 0x7E.

Chksum contains the component's checksum. The modulo sum of all the bytes in the component and the value in this field (Chksum) must add up to zero. This field is only valid if the  $C\_V$  field is non-zero. The checksum may be verified by firmware or software prior to its use. If the checksum option is selected for the FIT in the FIT Header entry (FIT type 0), the modulo sum of all the bytes in the FIT table must add up to zero. The PAL\_A FIT entry is not part of the FIT table and hence not included in the checksum computation of the FIT.

With this address layout, when one of the firmware components changes, only that component's flash portion requires changes. This address layout can also support multiple ROMs for the firmware components, and such ROMs are not restricted to reside below 4 GB.

## 2.6 Resources Required for Legacy Compatibility

All platforms shall implement a minimum of 64 MB of memory. The area of memory below 1 MB is defined as the compatibility area and is used by firmware when initializing and executing IA-32 BIOS (refer to Table 2-3). The requirements specified below need not be implemented on the platform if legacy compatibility is not required.

Table 2-3. 1 MB Compatibility Memory Address Space

| 0x000F_FFFF | Shadowed IA-32 System BIOS                                 |

|-------------|------------------------------------------------------------|

| 0x000F_0000 |                                                            |

| 0x000E_FFFF | Shadowed IA-32 Extended System BIOS/Option ROM/Memory Area |

| 0x000E_0000 |                                                            |

| 0x000D_FFFF | Shadowed IA-32 Option ROM BIOS                             |

|             |                                                            |

| 0x000C_0000 |                                                            |

| 0x000B_FFFF | VGA Frame Buffer                                           |

|             |                                                            |

| 0x000A_0000 |                                                            |

| 0x0009_FFFF | Memory                                                     |

|             |                                                            |

|             |                                                            |

| 0x0000_0500 |                                                            |

| 0x0000_04FF | IA-32 BIOS RAM Data Area                                   |

| 0x0000_0400 |                                                            |

| 0x0000_03FF | IA-32 Interrupt Vector Area                                |

| 0x0000_0000 |                                                            |

Within the 1 MB compatibility memory address space, empty spaces can be mapped to system memory. For example, a server platform may choose to implement the system console on a serial port and eliminate the VGA frame buffer and the VGA BIOS components. IA-32 stack should be allocated in the memory region (0x0000\_0500 to 0x0009\_FFFF) for use by the real mode IA-32 BIOS code.

Itanium architecture-based platforms may optionally use I/O adapter cards containing IA-32 option ROMs during the boot process. A portion of the SAL code may also contain IA-32 code. Such IA-32 code as well as IA-32 operating systems may rely on the existence of legacy components. If it is necessary to support such IA-32 code, Itanium architecture-based platforms may implement the I/O ports specified in the Table 2-4 or alternatively, the SAL can trap some or all IA-32 I/O instructions and emulate the I/O ports that are not present on the platform. Refer to Section 7.2.4, "IA-32 Support Environment" for more details.

Table 2-4. IA-32 Compatibility I/O Ports

| Port      | Description                                |

|-----------|--------------------------------------------|

| 0x20-0x21 | Programmable Interrupt Controller (Master) |

| 0x40-0x43 | Programmable Interval Timer                |

| 0x70-0x71 | CMOS NVRAM Address, Data Ports             |

| 0xA0-0xA1 | Programmable Interrupt Controller (Slave)  |

## 2.7 Chipset and Shadowing Requirements

Chipset implementations have the following SAL requirements:

- The firmware code and data within the firmware address range must be accessible

from the processor without any special system fabric initialization sequence. This

implies that the system fabric is implicitly initialized at power-on for accessing the

firmware address space.

- Firmware may copy ROM-based code and data structures to RAM to increase

performance and to allow for updates of ROM based data structures by initialization

firmware. Platforms may implement any write protection for these shadowed areas.

Since hardware events such as reset, machine check and initialization enter

architected PAL entrypoints in the ROM around the 4 GB address, chipsets shall not

disable accesses (by aliasing or other means) to the PAL/SAL ROM area subsequent

to the shadowing of firmware code.

- Itanium instructions provide the necessary memory management features to prevent writes to the shadowed RAM areas while executing IA-32 code. The Itanium instruction set provides instructions to synchronize the instruction and data caches in the presence of self-modifying code.

- Chipsets need not implement in-line shadowing (read cycles going to ROM, write cycles going to RAM) for copying IA-32 code segments to memory addresses in the range of 0xE0000 to 0xFFFFF.

# 2.8 Platform Support for Variant Architectural Features

Platform implementations may vary in the features they implement and remain architecturally compliant. As an example, some platforms will implement bus lock while other platforms will not. This has implications for software running on these platforms, and therefore this information must be communicated to software. SAL firmware is responsible for knowing the architecture implementation variations and correctly communicating the information to software. How SAL knows about the architectural variant is implementation-dependent. The following lists the features which fall into this category and describe the method of abstraction to software.

- Bus Lock: If the processor supports the bus lock signal and the platform implements bus lock, then SAL shall set the Default Control Register Lock Check Enable bit to 0 (DCR.lc = 0), otherwise the DCR.lc shall be set to 1. The operating system shall not alter DCR.lc bit setting if it is set to 1. Refer to the PAL call PAL\_BUS\_ SET\_FEATURES in the Intel® Itanium® Architecture Software Developer's Manual for information on masking bus lock signal and executing the locked transaction as a series of non-atomic transactions.

- Lowest Priority Interrupt: SAL shall communicate to the operating system, through the SAL System Table (Table 3-6), whether this feature is supported by the platform.

- Address Space Attributes: SAL shall communicate to software the supportable

access attributes for all valid address space mappings. This information is provided

to the operating system by the EFI component. As an example of this architectural

implementation options, consider two memory controllers where one supports subcache line writes to memory and another which does not. The first case would be

described as write-through or write-back cacheable, whereas the second case

would be described as supporting only write-back cacheable. Similarly, the UCE

memory attribute indicates whether the address space permits the exporting of the

fetchadd operation outside the processor. Memory attribute features for address

spaces are fully described in the Intel® Itanium® Architecture Software Developer's Manual.

## 2.9 Platform Considerations Related to Processor Physical Location

Following are the SAL requirements from the platform pertaining to the physical locations of processors in an MP configuration:

- The platforms shall provide a mechanism to generate unique geographic identifiers for those physical components that have software visibility. As an example, imagine a complex MP implementation that has more than one main system bus to which processors are attached. Each logical processor returns its logical address on the bus via a call to PAL\_FIXED\_ADDR, but this PAL call does not reflect the multinode configuration of the platform. It is therefore required that the platform provide some mechanism for SAL to ascertain which bus a processor is attached to. SAL will use this value to load the Streamlined Advanced Programmable Interrupt Controller (SAPIC) EID field in the Local ID register (CR.LID) of the processor(s). This is necessary for supporting interprocessor interrupts. The above example is not meant to limit this requirement to processors, as multiple host I/O bridges and multiple memory controllers, and so on, may also have a similar requirement. Platforms may implement unique ways of providing the SAPIC EID value. For example, in a single-node system, SAL may use the hardcoded value of zero for this field. Another example is a node controller that provides different EID values for processors connected to different buses in the system. It is expected that these mechanisms will be very simple, to facilitate exchange of interprocessor interrupts between processors (if needed), to determine the BSP node and the BSP processor in an MP environment. The BSP selection needs to be done very early in the boot sequence and during firmware recovery. Since multiple processors may be attempting to read the EID, a scheme that involves writing an index followed by reading the value from a node controller I/O port or the CMOS NVRAM I/O port may be prone to errors.

- A multi-Translation Lookaside Buffer (TLB) coherence domain platform must provide a mechanism for detecting which TLB coherence domain the processor is located in.

## 2.10 Non-Volatile Memory Requirements

Itanium architecture-based platform hardware must provide a minimum of 32KB of NVRAM to hold the error log captured during uncorrected machine check events. There may be additional NVRAM requirements to hold information on the operating systems that can be booted from the platform, the platform configuration, and so on. Refer to the *Extensible Firmware Interface Specification* for requirement details as well as the interfaces to the NVRAM space.

The NVRAM must preserve memory contents when the system power is off. Some possible NVRAM implementations are battery-backed SRAM and flash memory. The physical address and size of each NVRAM object in the system will be specified in Table 3-5, "Entrypoint Descriptor Entry Format" with:

- *Memory type* classification of *Regular Memory* and *Memory Usage* classification of *Firmware Reserved Memory* for battery-backed SRAM implementation, and

- Memory type classification of Firmware Address Space when NVRAM is implemented as part of the firmware flash ROM.

## 2.11 Miscellaneous Platform Requirements

Following are the additional platform requirements for SAL:

- If firmware recovery is supported in SAL, Itanium architecture-based platforms must provide a mechanism for user-requested firmware recovery.

- Itanium architecture-based platforms must support simple hardware or software implementations for BSP selection, for example, write once port. This is necessary since only the BSP is allowed to execute the firmware recovery code.

- Itanium architecture-based platforms must provide mechanisms to determine the base frequency of the platform (clock input to the processor).

- Itanium architecture-based platform hardware must provide a mechanism for firmware to reset all components within the platform.

- Itanium architecture-based platform hardware must provide a switch or other mechanism that produces an INIT signal. This feature, generally known as the CrashDump switch, may be used to effect a crash dump on a "hung system."

- Itanium architecture-based platform hardware must provide user friendly mechanisms for displaying the progress of the boot and firmware recovery, for example, LCD display.

# 3 Boot Sequence

#### 3.1 Overview of the Code Flow after Hard Reset

This chapter describes the firmware execution sequence from reset to operating system launch.

PALE\_RESET is an entry point within the PAL\_A code area near 4 GB in the firmware address space. All processors begin execution at this point on system reset. The exact implementation PALE\_RESET is implementation dependent. PALE\_RESET initializes and tests the processor using stepping-independent code. It will then call SALE\_ENTRY with the *Recovery Check* function to verify if the user has requested firmware recovery in a platform-dependent manner.

SALE\_ENTRY is the shared SAL\_A entrypoint from code in the PAL\_A and PAL\_B blocks for reset, recovery, machine check, and initialization events. PAL code obtains the SALE\_ENTRY entrypoint from the 8-byte pointer at location 4 GB – 24. The state of the processor on entry into SALE\_ENTRY is described in the Intel® Itanium® Architecture Software Developer's Manual. A general register (GR20) indicates the event causing entry into SALE\_ENTRY – reset, recovery check, machine check, or initialization. SALE\_ENTRY uses this argument to jump to internal entrypoints within SAL – SAL\_RESET, SAL\_RECOVERY\_CHECK, SAL\_CHECK, or SAL\_INIT.

PAL\_A passes status information to SALE\_ENTRY on the health of the processor and whether the version of the PAL\_B in the firmware is compatible with the processor's stepping. Table 3-1 shows the recommended SAL actions based on the self-test state parameter provided by PAL\_A.

|--|

| Processor Health           | SAL Handling                                                                                                                                                                        |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catastrophic Failure       | None. PAL disables interrupts and Machine Checks, then keeps the processor in a spin loop in PAL or in a halt state.                                                                |

| Healthy                    | Proceed with SAL Reset.                                                                                                                                                             |

| Performance<br>Restricted  | Proceed with SAL Reset if this is the only processor in the system. Else, try to inform the user. The processor may be an attached processor in a MP configuration.                 |

| Functionally<br>Restricted | Try to inform the user. Disable interrupts and Machine Checks, then go into a spin loop. Operating systems may not boot successfully if key processor functionality is unavailable. |

The code in SAL\_A will initiate recovery and update the firmware if:

- The platform indicates a user-requested recovery.

- The PAL\_A code reports an authentication failure on the PAL\_B component in the firmware.

- The PAL\_A code reports checksum or other errors in the FIT or the PAL\_B component.

- The PAL\_A code reports on all the processors that the version of the PAL\_B in the firmware is incompatible with the stepping level of the processors in the system.

### 3.1.1 Code Flow During Recovery

If firmware recovery is required, the SAL recovery code shall authenticate a new firmware image using a PAL\_A procedure. The SAL code will then accomplish the firmware recovery function, reset the recovery indication, and trigger a system wide reset causing re-entry into PALE\_RESET. SAL recovery code contains the logic to update one or more of the firmware components from OEM supported media.

Note:

The firmware recovery code in SAL\_A must be independent of processor stepping and must not invoke code in the PAL\_B block.

In a multiprocessing environment, the recovery code will first select a BSP. SAL shall not select a processor as the Bootstrap processor (BSP) unless it is reported as healthy or performance restricted by PAL and the version of PAL\_B in the system is compatible with the processor stepping. The BSP will rendezvous the APs and then proceed with the recovery of firmware. Note that the processors that are incompatible with the version of PAL\_B in the system must not be woken up until the PAL\_B component is updated.

Since PAL\_B functionality cannot be invoked during recovery, only a limited set of PAL procedures in the PAL\_A are available for use by the SAL recovery code. (Refer to the Intel® Itanium® Architecture Software Developer's Manual for details.) Furthermore, if SAL\_A invokes the IA-32 BIOS, the floating-point transcendental instructions listed below cannot be executed from the IA-32 instruction set:

F2XM1, FCOS, FPATAN, FPTAN, FPREM, FPREM1, | FSIN, FSINCOS, FYL2X, FYL2XP1

#### 3.1.2 Boot Flow

If a recovery condition does not exist, SALE\_ENTRY shall return to PALE\_RESET on all the processors that are compatible with the version of PAL\_B in the system, using the return address provided by PALE\_RESET to begin the second stage of processor test and initialization. If SAL\_A did not result in such a return, the processor may run in a degraded (functionally restricted) mode. The PAL\_PROC address provided to SALE\_ENTRY at the time of *Recovery Check* supports only a subset of the PAL procedures. (See the *Intel® Itanium® Architecture Software Developer's Manual* for details.)

On return from SALE\_ENTRY, the PALE\_RESET code obtains the address of the FIT from location (4 GB - 32) and then uses the FIT to get the address of the PAL\_B component in the non-recovery portion of the flash ROM. PAL\_A code will locate the address of the PAL\_RESET in the PAL\_B block and jump to it. The processor stepping-dependent code in the PAL\_B block will then perform the complete processor testing (processor late self-test) and initialization and then re-enter the SALE\_ENTRY with the function value of *Normal Reset*. Code at SALE\_ENTRY will jump to the code in the SAL\_B block to continue the boot sequence and will eventually boot the machine to the operating system.

### 3.2 SAL\_RESET

SAL\_RESET is responsible for performing platform test and initialization and invoking the EFI environment, which then invokes the operating system loader. SAL\_RESET may also be entered from SAL\_INIT if an OS\_INIT handler is not registered with SAL. One of

the parameters passed into SAL\_RESET (zero value in GR32) indicates that SAL\_RESET was entered from PALE\_RESET. GR32 must be non-zero if SALE\_ENTRY is entered from locations other than PALE\_RESET.

SAL\_RESET functionality can be subdivided into the following phases:

- Initialization

- · BSP identification

- · Platform initialization

- · Operating system boot

#### 3.2.1 Initialization Phase

This phase begins execution at SAL\_RESET and is performed on all the processors in the system. The Local ID (LID register) is described in the Intel® Itanium® Architecture Software Developer's Manual. It is the SAL's responsibility to uniquely initialize this register in each logical processor prior to performing BSP selection and enabling interrupts in an MP system. For uniprocessor (UP) systems, SAL must initialize this register prior to enabling interrupts. The operating system must not change the value that SAL stored into this register. Otherwise, routing of interrupts to the correct processor may not function correctly. The LID register's format is shown in Figure 3-1.

#### Figure 3-1. Local ID Register Format

|    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|----|---|---|---|---|---|---|---|

| id |    |    |    |    |    |    |    |    |    |    | ei | id |    |    |    |    |    |    |    |    |    | re | ese | rve | ed |   |   |   |   |   |   |   |

|         | 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 | 55 | 54 | 53 | 52 | 51 | 50 | 49 | 48 | 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| ignored |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

SAL must invoke the PAL\_PLATFORM\_ADDR procedure on all processors to set the physical address of the SAPIC Interrupt block memory and the IA-32 I/O port space if the default address values are not used. The default address for the SAPIC Interrupt block memory is 0x00000000\_FEE00000 and the default address for the IA-32 I/O port space is the 64 MB region below the highest physical address supported by the processor implementation. SAL will use a value that does not conflict with other devices on the platform. The operating system shall not change either of these address values. SAL will set up the IOBASE register (AR.k0) that provides the high order bits of the virtual address of the IA-32 I/O port block, to the same value as its physical address, to maintain identity mapping.

# 3.2.2 Bootstrap Processor Identification Phase in a Multiprocessor Configuration

Bootstrap processor selection is executed on all processors. The PAL\_FIXED\_ADDR procedure will be called to obtain a unique address on the bus to which the processor is connected. SAL will use this address and bus identification information to derive a unique geographical address for the processor and use the same in the selection of the boot processor. The determination of the unique geographical address is implementation-dependent. SAL shall not select a processor as the BSP unless it is reported as healthy by PAL and the version of PAL\_B in the system is compatible with the processor stepping.

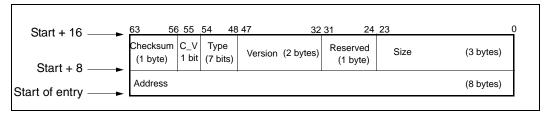

Refer to Figure 3-2 for SAL processing steps in a MP configuration. The APs will set up processor-specific resources such as the Interrupt Vector Address (IVA) and wait in the rendezvous state (Rendezvous\_1 in Figure 3-2) until the SAL on the BSP wakes them

up for further processing. Processors in the rendezvous state will disable external interrupts and poll for the rendezvous interrupt vector which the BSP will utilize to wake up the sleeping APs. The BSP will continue with platform initialization. When sufficient memory has been tested, the BSP will wake the APs with a rendezvous interrupt so that they can run late self-test. After the APs have finished the late self-test, they will return to the rendezvous state (Rendezvous\_2).

The BSP continues with platform initialization by loading the EFI firmware, which searches for bootable devices, loads the operating system loader, and transfers control to it. These steps are described in later sections of this document and the *Extensible Firmware Interface Specification*.

#### 3.2.2.1 Rendezvous Functionality

Rendezvous functionality is required only in MP environments and is utilized in two different ways:

- To wake up the APs during boot: The APs stay in a loop until woken up by the SAL layer on the BSP. The BSP wakes up the APs at various stages of booting to conduct processor and platform tests. Once these tests are completed, the APs return to the wait loop within SAL. Also, once the operating system kernel takes over, it will wake up the APs based on the wake up information provided by the SAL (refer to Section 3.2.5 and Table 3-10).

- To bring the APs to a spin loop during machine check rendezvous and to wake up

the APs after machine check processing is completed: The operating system

specifies the external interrupt vector to be used by SAL to bring the APs to a spin

loop as well as the external interrupt vector/memory variable to be used for the

wake up. Refer to "SAL\_MC\_SET\_PARAMS" on page 104 for details.

For the wake up functionality, the mechanism could be an external interrupt vector in the range of 0x10 to 0xFF or a memory variable.

If external interrupt mechanism is chosen, APs will disable interrupts and poll the local SAPIC IRR register for the bit corresponding to the selected rendezvous interrupt to be set. The Task Priority Register (TPR) must be set such that a read of the IVR register will return the rendezvous interrupt vector (instead of the spurious interrupt), if one is pending. On receipt of the interrupt, the AP will read the IVR register and issue an End of Interrupt (EOI) to the local SAPIC to clear the interrupt bit. The AP will execute the next phase of SAL code and, if necessary, return to the wait loop.

Figure 3-2. Control Flow of Boot Process in a Multiprocessor Configuration

If a memory variable wake-up mechanism is chosen, the APs will disable interrupts and poll the memory variable for the unique value that matches the contents of their Local ID Register in bits 16-31 and a value of 0xFFFF in bits 0-15 (refer to Figure 3-3). The BSP will set this value to wake up one AP at a time. The AP will clear the memory variable to zero, execute the next phase of SAL code and, if necessary, return to the wait loop.

#### Figure 3-3. Wake-up Memory Variable Format

| 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------------------------|-------------------------|---------------------------------------|

| id                      | eid                     | value of 0xFFFF                       |

SAL exports details of the wake-up mechanism to the operating system through the SAL System Table (refer to Table 3-3) so that the operating system kernel code on the BSP may wake up the APs when appropriate. While memory variable mechanism may be used by the BSP and APs during the platform initialization phase, SAL shall indicate only the external interrupt wake-up mechanism to the operating system. The operating system shall not use the indicated external interrupt vector until it takes over the IVA. The operating system on the BSP will invoke the SAL\_SET\_VECTORS procedure to set the continuation point for the APs within the operating system kernel (OS\_BOOT\_RENDEZ) and then trigger the wake up of the APs. SAL will transition the APs to the registered OS\_BOOT\_RENDEZ entrypoint.

#### 3.2.3 Platform Initialization Phase

This phase is primarily executed on the BSP. The APs will execute some of the steps described below. This phase will perform the following functions, the ordering of which is implementation- dependent:

- 1. Initialize the IVA to point to a 32 KB Interrupt Vector Table (IVT) in the firmware address space. Some SAL implementations may choose to build the IVT in RAM after finding the first 64 MB of memory. This step must be accomplished on all the processors in an MP environment.

- 2. Initialize the system fabric and chipsets. The method of handling the initialization is implementation-dependent.

- 3. On a cold boot, SAL will initialize at least the first 4 MB of memory for BSP late self-test. This self-test is done by calling the PAL\_TEST\_PROC procedure which returns information on whether the processor is healthy or not. This PAL procedure tests the path from the processor to the memory through the caches and returns information on whether the processor is fully functional. This PAL procedure will not return to the SAL if the processor under test experiences a catastrophic failure. SAL must contain logic to select a new BSP if necessary. SAL shall shut down the system if there are no healthy or performance-restricted processors in the system. After this point, the memory stack and RSE can be tested and enabled in the Itanium system environment.

- 4. Issue a rendezvous interrupt to wake up APs for a late self-test using the PAL\_TEST\_PROC procedure. The SAL code on the BSP must contain sufficient logic to detect APs that experience a catastrophic failure during the late self-test. On completion of late self-test, the BSP will set the APs back to the rendezvous state (Rendezvous\_2 in Figure 3-2). After this stage, caches have been fully tested.

APs entering the rendezvous state at this point are required to execute the following steps to ensure that their caches only contain prefetches for firmware code and data. This restriction allows the processors to be safely removed during an on-line deletion operation without OS intervention.

- Call PAL\_PTCE\_INFO to get information needed to purge translation caches, then use the parameters returned to execute the loop describing the ptc.e (purge translation cache entry) instruction in the Intel Itanium Architecture Software Developers Manual, Revision 2.2, Volume 3, Section 2.2.

- 2. Call PAL\_PREFETCH\_VISIBILITY with trans\_type=1

- 3. Call PAL\_CACHE\_FLUSH with the inv parameter set to 1.

- 4. Call PAL\_MC\_DRAIN

After this sequence the processor ma enter into the rendezvous state.

#### Note:

In multithreaded processors, PAL\_TEST\_PROC will disable the other thread while running, for up to several seconds. In addition, the architectural requirement that PAL\_TEST\_PROC cannot be called with the same memory buffer on multiple processors also applies to threads. SAL must not call this procedure with the same buffer on separate threads at the same time.

- 5. Search for console using implementation-dependent algorithms. If found, initialize the console so that the progress of the boot may be displayed.

- Map and initialize memory. The memory test is implementation-dependent. The memory test includes testing of refresh logic and testing all the address lines for shorts.

- 7. Initialize the interrupt controllers to all interrupts disabled.

- 8. Allocate memory for use by PAL and SAL near the top of physical memory. This area should be below 4 GB if IA-32 code needs to call the SAL code with Itanium instructions, since IA-32 code can only address memory up to 4 GB.