# **Altera SDK for OpenCL**

**Custom Platform Toolkit User Guide**

# **Contents**

| ra SDK for OpenCL Custom Platform Toolkit User Guide                                              | 1-1                                                          |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Prerequisites for the Altera SDK for OpenCL Custom Platform Toolkit                               | 1-1                                                          |

| Overview of the AOCL Custom Platform                                                              |                                                              |

| Directories and Files in an AOCL Custom Platform                                                  | 1-3                                                          |

| Recommendations for Structuring the Custom Platform Directory                                     | 1-3                                                          |

| Custom Platform Automigration for Forward Compatibility                                           | 1-4                                                          |

| Customizing Automigration                                                                         | 1-4                                                          |

| Creating an AOCL Custom Platform                                                                  | 1-5                                                          |

| Designing the Board Hardware                                                                      | 1-5                                                          |

| Creating the Board XML Files                                                                      | 1-10                                                         |

| Creating the MMD Library                                                                          | 1-15                                                         |

| Setting Up the Altera Client Driver                                                               |                                                              |

| Providing AOCL Utilities Support                                                                  | 1-18                                                         |

| Testing the Hardware Design                                                                       |                                                              |

| Applying for the Altera Preferred Board Status                                                    | 1-20                                                         |

| Shipping Recommendations                                                                          | 1-22                                                         |

| Document Revision History                                                                         | 1-22                                                         |

|                                                                                                   |                                                              |

| ra SDK for OpenCL Custom Platform Toolkit Reference Mate                                          | erial 2-1                                                    |

| The Board Qsys Subsystem                                                                          |                                                              |

| Altera SDK for OpenCL-Specific Qsys System Components                                             |                                                              |

| XML Elements, Attributes, and Parameters in the board_spec.xml File                               |                                                              |

| board                                                                                             |                                                              |

| device                                                                                            | 2-7                                                          |

| global_mem                                                                                        |                                                              |

| host                                                                                              |                                                              |

| channels                                                                                          |                                                              |

| interfaces                                                                                        |                                                              |

| interface                                                                                         |                                                              |

| compile                                                                                           |                                                              |

| MMD API Descriptions                                                                              |                                                              |

| aocl_mmd_get_offline_info                                                                         |                                                              |

| aocl_mmd_get_info                                                                                 | 2-15                                                         |

|                                                                                                   |                                                              |

| aoci mmd open                                                                                     | 2-18                                                         |

| aocl_mmd_openaocl_mmd_close                                                                       | 2-18<br>2-19                                                 |

| aocl_mmd_close                                                                                    | 2-18<br>2-19<br>2-19                                         |

| aocl_mmd_closeaocl_mmd_read                                                                       | 2-18<br>2-19<br>2-19<br>2-19                                 |

| aocl_mmd_close<br>aocl_mmd_readaocl_mmd_write                                                     |                                                              |

| aocl_mmd_closeaocl_mmd_readaocl_mmd_writeaocl_mmd_copy                                            |                                                              |

| aocl_mmd_closeaocl_mmd_readaocl_mmd_writeaocl_mmd_copyaocl_mmd_copyaocl_mmd_set_interrupt_handler |                                                              |

| aocl_mmd_closeaocl_mmd_readaocl_mmd_writeaocl_mmd_copy                                            | 2-18<br>2-19<br>2-19<br>2-19<br>2-20<br>2-21<br>2-22<br>2-23 |

| aocl_mmd_shared_mem_freefree | 2-24 |

|------------------------------|------|

| aocl_mmd_reprogram           | 2-25 |

| Document Revision History    |      |

# Altera SDK for OpenCL Custom Platform Toolkit User Guide

2015.11.02

UG-OCL007

The Altera SDK for OpenCL Custom Platform Toolkit User Guide outlines the procedure for creating an Altera  $^{\odot}$  Software Development Kit (SDK) for OpenCL  $^{\top}$  (AOCL) Custom Platform.

The Altera SDK for OpenCL<sup>(1)(2)</sup> Custom Platform Toolkit provides the necessary tools for implementing a fully functional Custom Platform. The Custom Platform Toolkit is available in the *ALTERAOCLSDKROOT*/ **board** directory, where the environment variable *ALTERAOCLSDKROOT* points to the location of the AOCL installation.

The goal is to enable an AOCL user to target any given Custom Platform seamlessly by performing the following tasks:

- 1. Acquire an accelerator board and plug it into their system.

- 2. Acquire the Custom Platform and unpack it to a local directory.

- **3.** Set the environment variable *AOCL\_BOARD\_PACKAGE\_ROOT* to point to this local directory.

- **4.** Set the environment variable *QUARTUS\_ROOTDIR\_OVERRIDE* to point to installation directory of the Quartus® Prime Standard Edition software or the Quartus Prime Pro Edition software, depending on the target device.

- 5. Invoke the aocl install utility command.

- **6.** Compile the OpenCL kernel and build the host application.

- 7. Set environment variables to point to the location of the memory-mapped device (MMD) library.

- For Windows systems, set the *PATH* environment variable.

- For Linux systems, set the *LD\_LIBRARY\_PATH* environment variable.

- **8.** Run the host application.

# Prerequisites for the Altera SDK for OpenCL Custom Platform Toolkit

The Altera SDK for OpenCL Custom Platform Toolkit User Guide assumes that you have prior hardware design knowledge necessary for using the Custom Platform Toolkit to create an Altera SDK for OpenCL Custom Platform.

ISO 9001:2008 Registered

<sup>(1)</sup> OpenCL and the OpenCL logo are trademarks of Apple Inc. used by permission of the Khronos Group™.

<sup>(2)</sup> The Altera SDK for OpenCL is based on a published Khronos Specification, and has passed the Khronos Conformance Testing Process. Current conformance status is available at www.khronos.org/conformance.

<sup>© 2015</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at <a href="https://www.altera.com/common/legal.html">www.altera.com/common/legal.html</a>. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

You must have experiences in the following hardware design areas:

- Quartus Prime software design with Qsys, HDL and Tcl

- Altera intellectual property (IP) necessary to communicate with the physical interfaces of the board

- High speed design, timing analysis and Synopsys Design Constraints (SDC) constraints

- FPGA architecture, including clock and global routing, floorplanning, and I/O

- Team-based design (that is, incremental compilation)

You must install the Quartus Prime software, the relevant device support file(s), and the AOCL on your machine. Depending on the target device, you must install the Quartus Prime Standard Edition software, the Quartus Prime Pro Edition software, or both. Refer to the *Altera SDK for OpenCL Getting Started Guide* for installation instructions.

You have the following Custom Platform design options:

- Refer to the information in this document to create a Custom Platform from the templates available in the Custom Platform Toolkit.

- Refer to the information in this document and the *Altera Stratix V Network Reference Platform Porting Guide* to create a Custom Platform by modifying relevant files in s5\_net.

- Download the Altera Stratix<sup>®</sup> V Network Reference Platform (s5\_net) from the Altera SDK for OpenCL FPGA Platforms page on the Altera website. The link for the download is under **Custom**.

- Refer to the information in the following documents to create a Custom Platform by modifying relevant files in the Cyclone<sup>®</sup> V SoC Development Kit Reference Platform (c5soc), available with the AOCL:

- 1. Altera SDK for OpenCL Custom Platform Toolkit User Guide

- 2. Altera Cyclone V SoC Development Kit Reference Platform Porting Guide

- 3. Cyclone V SoC Development Board Reference Manual

#### **Related Information**

- Altera SDK for OpenCL Getting Started Guide

- Altera Stratix V Network Reference Platform Porting Guide

- Altera Cyclone V SoC Development Kit Reference Platform Porting Guide

- Cyclone V SoC Development Board Reference Manual

- Altera SDK for OpenCL FPGA Platforms page on the Altera website

### Overview of the AOCL Custom Platform

An Altera SDK for OpenCL Custom Platform is a collection of tools and libraries necessary for the communication between the Altera Offline Compiler (AOC) and the FPGA boards.

Currently, the AOC targets a single Custom Platform at a time.

The environment variable AOCL\_BOARD\_PACKAGE\_ROOT points to the path of the **board\_env.xml** board environment eXtensible Markup Language (XML) file within a Custom Platform. A given Custom Platform installation can include several board variants of the same board interface. You might have different FPGA parts, or you might want to support different subsets of board interfaces. Colocating the board variants allows simultaneous communication with different boards in a multiple-device environment.

An AOCL Custom Platform contains the following components:

- Quartus Prime skeleton project—A Quartus Prime project for your board, which the AOC modifies to include the compiled kernel. This project must include a post-place-and-route partition for all logic not controlled by the kernel clock.

- Board installation setup—A description of your board and its various components.

- **Generic I/O interface**—An MMD software library that implements basic I/O between the host and the board.

- **Board utilities**—An implementation of AOCL utilities for managing the accelerator board, including tasks such as installing and testing the board.

### Directories and Files in an AOCL Custom Platform

Populate your Altera SDK for OpenCL Custom Platform with files, libraries and drivers that allow an OpenCL kernel to run on the target FPGA board.

Table 1-1: Contents within the Top-Level Custom Platform Directory

| Content               | Description                                                                                                                                                                                                                                                                                     |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| board_env.xml         | The XML file that describes the board installation to the AOCL.                                                                                                                                                                                                                                 |

| <hardware></hardware> | Directory containing the Quartus Prime projects for the supported boards within a given Custom Platform. Specify the name of this directory in the <b>board_env.xml</b> file. Within this directory, the AOCL assumes that any subdirectory containing a <b>board_spec.xml</b> file is a board. |

| include               | Directory containing board-specific header files.                                                                                                                                                                                                                                               |

| source                | Directory containing board-specific files, libraries and drivers.                                                                                                                                                                                                                               |

| platform              | Directory containing platform-specific (for example, x86_64 Linux) drivers and utilities.                                                                                                                                                                                                       |

# **Recommendations for Structuring the Custom Platform Directory**

For ease of use, consider adopting the Altera $^{\otimes}$ -recommended directory structure and naming convention when you create an Altera SDK for OpenCL $^{\text{\tiny TM}}$  Custom Platform.

- Make the *ALTERAOCLSDKROOT/board* directory the location of the board installation, where *ALTERAOCLSDKROOT* points to the location of the AOCL installation.

- **Attention:** Do not remove any existing subdirectories from the **ALTERAOCLSDKROOT/board** directory.

- Create a **<boord\_vendor\_name>** subdirectory within the **ALTERAOCLSDKROOT/board** directory to store the Custom Platform.

- Store the contents of a given Custom Platform in a *ALTERAOCLSDKROOT/board/<board\_vendor\_name>/* <board\_family\_name> subdirectory.

- Assign unique names to software libraries (for example, lib<board\_vendor\_name>\_

<board\_family\_name>.so) to avoid name collisions.

Altera SDK for OpenCL Custom Platform Toolkit User Guide

For example, if you (ABC Incorporated) create a Custom Platform for a family of boards named XYZ, set up your Custom Platform such that the AOCL user can access XYZ by performing the following tasks:

- 1. Install the XYZ Custom Platform in *ALTERAOCLSDKROOT/board/ABC/XYZ*, where *ALTERAOCLSDK-ROOT* is the environment variable that points to the absolute path to the AOCL installation package.

- 2. Set the AOCL\_BOARD\_PACKAGE\_ROOT environment variable to point to ALTERAOCLSDKROOT/board/ABC/XYZ.

# **Custom Platform Automigration for Forward Compatibility**

The automigration feature updates an existing Altera-registered Custom Platform for use with the current version of the Quartus Prime Design Suite® (QPDS) and the Altera SDK for OpenCL.

**Important:** Automigration is more likely to complete successfully if your Custom Platform resembles an Altera Reference Platform as closely as possible.

The following information applies to a Custom Platform that is version 14.0 and beyond:

- 1. To update a Custom Platform for use with the current version of the QPDS, which includes the AOCL, do not modify your Custom Platform. The automigration capability detects the version of your Custom Platform based on certain characteristics and updates it automatically.

- 2. If you have modified a Custom Platform and you want to update it for use with the current version of the QPDS, which includes the AOCL, implement all features mandatory for the current version of the Custom Platform. After you modify a Custom Platform, automigration can no longer correctly detect its characteristics. Therefore, you must upgrade your Custom Platform manually.

A successfully-migrated Custom Platform will preserve its original functionality. In most cases, new features in a new QPDS or AOCL version will not interfere with Custom Platform functionality.

When the Altera Offline Compiler compiles a kernel, it probes the **board\_spec.xml** file for the following information:

- 1. The version of the Custom Platform, as specified by the version attribute of the board XML element.

- 2. The platform type, as specified by the platform\_type parameter of the auto\_migrate attribute within the compile XML element.

Based on the information, the AOCL names a set of fixes it must apply during Custom Platform migration. It applies the fixes to the Quartus Prime project that the AOC uses to compile the OpenCL kernel. It also generates an **automigration.rpt** report file in the AOCL user's current working directory describing the applied fixes.

The automigration process does not modify the installed Custom Platform.

**Note:** If automigration fails, contact your local Altera field applications engineer for assistance.

### **Customizing Automigration**

You and the Altera SDK for OpenCL user both have the ability to disable the automigration of an installed Custom Platform. In addition, you may choose which named fixes, identified by the AOCL, you want to apply to your Custom Platform.

1. Disable automigration in one of the following manners:

- If you are a board developer, within the compile XML element in the **board\_spec.xml** file, set the platform\_type parameter of the auto\_migrate attribute to none.

- If you are an AOCL user, invoke the aoc --no-auto-migrate command.

- 2. To explicitly include or exclude fixes that the AOCL identifies, in the **board\_spec.xml** file, subscribe or unsubscribe to each fix by listing it in the include fixes or exclude fixes parameter, respectively. The include fixes and exclude fixes parameters are part of the auto\_migrate attribute within the compile element. When listing multiple fixes, separate each fix by a comma.

Refer to the **automigration.rpt** file for the names of the fixes that you specify in the include fixes and exclude fixes parameters.

# **Creating an AOCL Custom Platform**

The following topics outline the tasks you must perform to create a Custom Platform for use with the Altera SDK for OpenCL.

- 1. Designing the Board Hardware on page 1-5

- To design an accelerator board for use with the Altera SDK for OpenCL, you must create all the board and system components, and the files that describe your hardware design to the Altera Offline Compiler.

- 2. Creating the Board XML Files on page 1-10

Your Custom Platform must include the XML files that describe your Custom Platform and each of your hardware system to the Altera SDK for OpenCL.

- 3. Creating the MMD Library on page 1-15

- Your Custom Platform requires an MMD layer necessary for communication with the accelerator board.

- 4. Setting Up the Altera Client Driver on page 1-17

- The ACD allows the AOCL to automatically find and load the Custom Platform libraries at host runtime.

- 5. Providing AOCL Utilities Support on page 1-18

- Each Custom Platform you develop for use with the Altera SDK for OpenCL must support a set of AOCL utilities. These utilities enable users to manage the accelerator board through the AOCL.

- **6.** Testing the Hardware Design on page 1-20

- After you create the software utilities and the MMD layer, and your hardware design achieves timing closure, test the design.

### **Designing the Board Hardware**

To design an accelerator board for use with the Altera SDK for OpenCL, you must create all the board and system components, and the files that describe your hardware design to the Altera Offline Compiler.

Each board variant in the Custom Platform consists of a Quartus Prime project, and a **board\_spec.xml** XML file that describes the system to the AOC. The **board\_spec.xml** file describes the interfaces necessary to connect to the kernel. The AOC generates a custom circuit based on the data from the **board\_spec.xml** file. Then it incorporates the OpenCL kernel into the Qsys system you create for all nonkernel logic.

You must preserve the design of all nonkernel logic. You can preserve your design in the Quartus Prime software via one of the following methods:

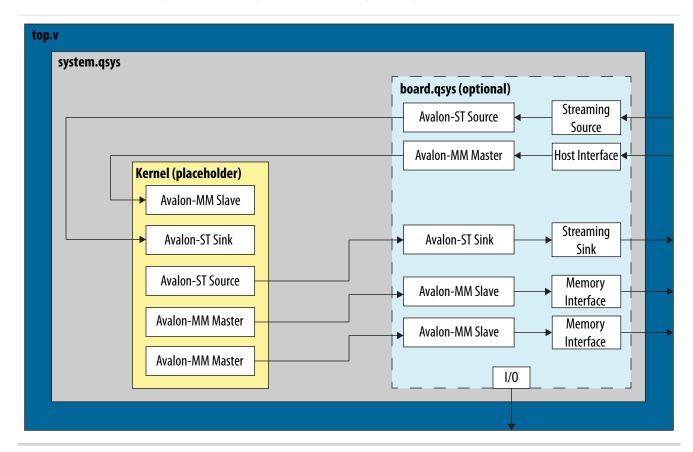

- Create a design partition containing all nonkernel logic under a single HDL hierarchy and then export the partition. For example, you may create and export a **board.qsys** Qsys subsystem (see figure below). The top-level **system.qsys** Qsys system can then instantiate this exported board Qsys subsystem.

- Implement the Configuration via Protocol (CvP) configuration scheme, which preserves all logic outside a design partition. In this case, you only need to create a partition around the kernel logic. You may place all nonkernel logic into a single top-level Qsys system file (for example, system.qsys).

You must design all the components and the **board\_spec.xml** file that describe the system to the AOCL.

Figure 1-1: Example System Hierarchy with a Board Qsys Subsystem

- 1. Creating the Board Qsys System on page 1-6

- To create your board system in a Qsys subsystem, you may modify the **board.qsys** template in the Custom Platform Toolkit.

- **2. Establishing Guaranteed Timing Flow** on page 1-9

Deliver a design partition for nonkernel logic that has a clean timing closure flow as part of your Custom Platform.

### **Creating the Board Qsys System**

When designing your board hardware, you have the option to create a Qsys subsystem within system.qsys that contains all the board logic. In addition to organizing your design code, having this subsystem allows you to create a Quartus Prime partition that you can preserve. To create your board system in a Qsys subsystem, you may modify the board.qsys template in the Custom Platform Toolkit.

An implementation of a board Qsys subsystem might include the following components:

- Proper reset sequencing

- Altera SDK for OpenCL-specific components

- Host-to-FPGA communication IP

- Memory IP used for AOCL global memory

- Streaming channels to board-specific interfaces

Refer to *The Board Qsys System* section for more information.

Templates of the following hardware design files are available in the *ALTERAOCLSDKROOT*/board/custom\_platform\_toolkit/board\_package/hardware/template directory:

- board.qsys

- system.qsys

- top.v

- top.qpf

- board\_spec.xml

Template of the post\_flow.tcl file is available in the *ALTERAOCLSDKROOT*/board/custom\_platform\_toolkit/board\_package/hardware/template/scripts directory of the Custom Platform Toolkit.

To create nonkernel logic, perform the following tasks in the **system.qsys** top-level Qsys system or in a board Qsys subsystem:

1. In Qsys, add your host and memory IPs to the Qsys system, and establish all necessary connections and exports.

**Attention:** You might need to acquire separate IP licenses. For a list of available licensed and unlicensed IP solutions, visit the All Intellectual Property page of the Altera website. For more information about each IP, click the link in the Product Name column to navigate to the product page.

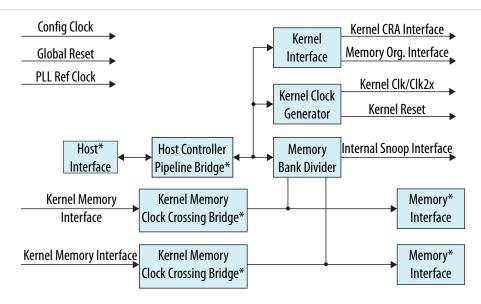

- a. Connect your host interface clock such that it drives por\_reset\_controller/clk. Your design's global reset and clock inputs are fed to a reset counter (por\_reset\_counter). This reset counter then synchronizes to the host interface clock in the Merlin Reset Controller (por\_reset\_controller).

- The por\_reset\_counter ACL SW Reset component implements the power-on reset. It resets all the device hardware by issuing a reset for a number of cycles after the FPGA completes its configuration.

- **b.** Modify the parameters of the pipe\_stage\_host\_ctrl Avalon® Memory-Mapped (Avalon-MM) Pipeline Bridge component such that it can receive requests from your host IP. Connect your host interface's Avalon-MM master port to the s0 port of pipe\_stage\_host\_ctrl. Connect the m0 port of pipe\_stage\_host\_ctrl to all the peripherals that must communicate with your host interface, including the OpenCL Kernel Clock Generator and the OpenCL Kernel Interface components.

- c. Adjust the number of <code>clock\_cross\_kernel\_mem\_<N></code> Avalon-MM Clock Crossing Bridge components to match the number of memory interfaces on your board. This component performs clock crossing between the kernel and memory interfaces. Modify the parameters of each component so that they are consistent with the parameters of the OpenCL Memory Bank Divider component and the <code>interface</code> attribute described in <code>board\_spec.xml</code>. Connect the <code>m0</code> master, clock, and reset ports of <code>clock\_cross\_kernel\_mem\_<N></code> (that is, <code>m0</code>, <code>m0\_clk</code>, and <code>m0\_reset</code>, respectively) to your memory IP.

**Important:** Connect m0\_reset in such a way that assertion of kernel\_reset from the OpenCL Memory Bank Divider component triggers this reset.

2. Customize the AOCL-specific Qsys system components...

Attention: If you use the board.qsys system template to create a Qsys subsystem, note that it is preconfigured with the necessary connections between the AOCL-specific system components and the appropriate interfaces exported to match the board\_spec.xml file.

Altera recommends that you preserve the preconfigured connections as much as possible.

- a. In Qsys, click Tools > Options. In the Options dialog box, add ALTERAOCLSDKROOT/ip/board to the Qsys IP Search Path and then click Finish.

- **b.** Instantiate the OpenCL Kernel Clock Generator component. Specify the component parameters, and connect the signals and ports as outlined in the *OpenCL Kernel Clock Generator* section.

- **c.** Instantiate the OpenCL Kernel Interface component. Specify the component parameters, and connect the signals and ports as outlined in the *OpenCL Kernel Interface* section.

- **d.** For each global memory type, instantiate the OpenCL Memory Bank Divider component. Specify the component parameters, and connect the signals and ports as outlined in the *OpenCL Memory Bank Divider* section.

Attention: Set the parameters such that the resulting bank masters have the equivalent address bits and burst widths as those from the kernel, as defined in the interface attribute of the global\_mem element in the board\_spec.xml file. For each memory bank, Qsys generates a master that inherits the same characteristics as your specifications.

- **3.** If you choose to create a Qsys subsystem for the nonkernel logic, export any necessary I/Os to the top-level **system.qsys** Qsys system.

- 4. Edit the top-level top.v file to instantiate system.qsys and connect any board-specific I/Os.

- 5. Set up the top.qpf Quartus Prime project with all the necessary settings for your board design.

- **6.** Modify the **post\_flow.tcl** file to include the Tcl code that generates the **fpga.bin** file during Quartus Prime compilation.

The **fpga.bin** file is necessary for programming the board.

7. Edit the **board\_spec.xml** file to include board-specific descriptions.

#### **Related Information**

- All Intellectual Property page on the Altera website

- OpenCL Kernel Clock Generator on page 2-2

- OpenCL Kernel Interface on page 2-3

- OpenCL Memory Bank Divider on page 2-4

- The Board Qsys Subsystem on page 2-1

### General Quality of Results Considerations for the Exported Board Partition

When generating a post-place-and-route partition, take into account several design considerations for the exported board partition that might have unexpected consequences on the Altera SDK for OpenCL compilation results. The best approach to optimizing the board partition is to experiment with a range of different OpenCL kernels.

The list below captures some of the parameters that might impact the quality of AOCL compilation results:

#### Resources Used

Minimize the number of resources the partition uses to maximize the resources available for the OpenCL kernels.

### Kernel Clock Frequency

Altera recommends that the kernel clock has a high clock constraint (for example, greater than 350 MHz for a Stratix V device). The amount of logic in the partition clocked by the kernel clock should be relatively small. This logic should not limit the kernel clock speed for even the simplest OpenCL kernels. Therefore, at least within the partition, the kernel clock should have a high clock constraint.

### Host-to-Memory Bandwidth

The host-to-memory bandwidth is the transfer speed between the host processor to the physical memories on the accelerator card. To measure this memory bandwidth, compile and run the host application included with the Custom Platform Toolkit.

### • Kernel-to-Memory Bandwidth

The kernel-to-memory bandwidth is the maximum transfer speed possible between the OpenCL kernels and global memory.

To measure this memory bandwidth, compile and run the host program included in the /tests/boardtest/host directory of the Custom Platform Toolkit.

### • Fitter Quality of Results (QoR)

To ensure that OpenCL designs consuming much of the device's resources can still achieve high clock frequencies, region-constrain the partition to the edges of the FPGA. The constraint allows OpenCL kernel logic to occupy the center of the device, which has the most connectivity with all other nodes.

Test compile large designs to ensure that other Fitter-induced artifacts in the partition do not interfere with the QoR of the kernel compilations.

### Routability

The routing resources that the partition consumes can affect the routability of a compiled OpenCL design. A kernel might use every digital signal processing (DSP) block or memory block on the FPGA; however, routing resources that the partition uses might render one of these blocks unroutable. This routing issue causes compilation of the Quartus Prime project to fail at the fitting step. Therefore, it is imperative that you test a partition with designs that use all DSP and memory blocks.

### **Establishing Guaranteed Timing Flow**

Deliver a design partition for nonkernel logic that has a clean timing closure flow as part of your Custom Platform.

1. Create a placed and routed design partition using the incremental compilation feature of the Quartus Prime software. This is the design partition for nonkernel logic.

Send Feedback

For more information on how to use the incremental compilation feature to generate a timing-closed design partition, refer to the *Quartus Prime Incremental Compilation for Hierarchical and Team-Based Design* chapter in Volume 1 of the *Quartus Prime Standard Edition Handbook*.

- 2. Import the post-fit partition from Step 1 into the top-level design as part of the compilation flow.

- **3.** Run the *ALTERAOCLSDKROOT*/ip/board/bsp/adjust\_plls.tcl script as a post-flow process, where *ALTERAOCLSDKROOT* points to the path of the Altera SDK for OpenCL installation.

The adjust\_plls.tcl script determines the maximum kernel clock frequency and stores it in the pll\_rom on-chip memory of the OpenCL Kernel Clock Generator component.

### **Related Information**

Quartus Prime Incremental Compilation for Hierarchical and Team-Based Design

### **Creating the Board XML Files**

Your Custom Platform must include the XML files that describe your Custom Platform and each of your hardware system to the Altera SDK for OpenCL. You may create these XML files in simple text editors (for example, WordPad for Windows, and vi for Linux).

Creating the board\_env.xml File on page 1-10

The board\_env.xml file describes your Custom Platform to the AOCL.

Creating the board\_spec.xml File on page 1-13

The **board\_spec.xml** XML file contains metadata necessary to describe your hardware system to the Altera SDK for OpenCL.

### Creating the board\_env.xml File

For the Altera Offline Compiler to target a Custom Platform, the Altera SDK for OpenCL user has to set the environment variable *AOCL\_BOARD\_PACKAGE\_ROOT* to point to the Custom Platform directory in which the **board\_env.xml** file resides.

The **board\_env.xml** file describes your Custom Platform to the AOCL.

Together with the other contents of the Custom Platform, the **board\_env.xml** file sets up the board installation that enables the AOC to target a specific accelerator board.

A board\_env.xml template is available in the /board\_package directory of the Custom Platform Toolkit.

- 1. Create a board\_env top-level XML element. Within board\_env, include the following XML elements:

- hardware

- platform

Include a platform element for each operating system that your Custom Platform supports.

- 2. Within each platform element, include the following XML elements:

- mmdlib

- linkflags

- linklibs

- utilbindir

- **3.** Parameterize each element and corresponding attribute(s) with information specific to your Custom Platform, as outline in the table below:

Table 1-2: Specifications of XML Elements and Attributes in the board\_env.xml File

| Element    | Attribute Description                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| board_env  | version: The AOCL Custom Platform Toolkit release you use to create your Custom Platform.                                                                            |

|            | Attention: The Custom Platform version must match the AOCL version you use to develop the Custom Platform.                                                           |

|            | name: Name of the board installation directory containing your Custom Platform.                                                                                      |

| hardware   | dir: Name of the subdirectory, within the board installation directory, that contains the board variants.                                                            |

|            | default: The default board variant that the AOC targets when the AOCL user does not specify an explicit argument for theboard<br><pre></pre>                         |

| platform   | name: Name of the operating system.                                                                                                                                  |

|            | Refer to the Altera SDK for OpenCL Getting Started Guide and the Altera RTE for OpenCL Getting Started Guide for more information.                                   |

| mmdlib     | A string that specifies the path to the MMD library of your Custom Platform.                                                                                         |

|            | To load multiple libraries, specify them in an ordered, commaseparated list. The host application will load the libraries in the order that they appear in the list. |

| linkflags  | A string that specifies the linker flags necessary for linking with the MMD layer available with the board.                                                          |

|            | <b>Tip:</b> You can use %a to reference the AOCL installation directory and %b to reference your board installation directory.                                       |

| linklibs   | A string that specifies the libraries the AOCL must link against to use the MMD layer available with the board.                                                      |

|            | Note: Include the alterahalmmd library, available with the AOCL, in this field because the library is necessary for all devices with an MMD layer.                   |

| utilbindir | Directory in which the AOCL expects to locate the AOCL utility executables (that is, install, uninstall, program, diagnose and flash).                               |

|            | <b>Tip:</b> You can use %a to reference the AOCL installation directory and %b to reference your board installation directory.                                       |

Your **board\_env.xml** file should resemble the following example:

```

<?xml version="1.0"?>

<board_env version="15.1" name="a10_ref">

<hardware dir="hardware" default="a10_ref"></hardware>

<platform name="linux64">

<mmdlib>%b/linux64/lib/libaltera_a10_ref_mmd.so</mmdlib>

<linkflags>-L%b/linux64/lib</linkflags>

<linklibs>-lalterahalmmd -laltera_a10_ref_mmd</linklibs>

<utilbindir>%b/linux64/libexec</utilbindir>

</platform>

<platform name="windows64">

<mmdlib>%b/windows64/bin/altera_a10_ref_mmd.dll//mmdlib>

<linkflags>/libpath:%b/windows64/lib</linkflags>

<linklibs>alterahalmmd.lib altera a10 ref mmd.lib</linklibs>

<utilbindir>%b/windows64/libexec</utilbindir>

</platform>

</board_env>

```

#### **Related Information**

- Prerequisites for the Altera SDK for OpenCL

- Prerequisites for the Altera RTE for OpenCL

### Testing the board\_env.xml File

After you generate the **board\_env.xml** file, test the file within your board installation directory to ensure that the Altera® Offline Compiler recognizes the board installation.

- **1.** Set the environment variable *AOCL\_BOARD\_TOOLKIT\_ROOT* to point to the Custom Platform subdirectory in which your **board\_env.xml** file resides.

- 2. At the command prompt, invoke the aocl board-xml-test command to verify that the Altera SDK for OpenCL can locate the correct field values.

The AOCL generates an output similar to the one below:

**3.** Invoke the aoc --list-boards command to verify that the AOC can identify and report the board variants in the Custom Platform.

For example, if your Custom Platform includes two FPGA boards, the AOCL generates an output similar to the one below:

The last board installation test takes place when you use the AOC to generate a design for your board.

#### **Related Information**

- Creating the board\_env.xml File on page 1-10

- Testing the Hardware Design on page 1-20

### Creating the board\_spec.xml File

The **board\_spec.xml** XML file contains metadata necessary to describe your hardware system to the Altera SDK for OpenCL.

For detailed descriptions on the type of information you must include in the **board\_spec.xml** file, refer to the *XML Elements*, *Attributes*, *and Parameters in the board\_spec.xml File* section. A **board\_spec.xml** template is available in the *ALTERAOCLSDKROOT*/board/custom\_platform\_toolkit/board\_package/hardware/template directory of the Custom Platform Toolkit.

1. Structure the **board\_spec.xml** file to include the following XML elements and attributes:

Table 1-3: XML Elements and Attributes Specified in the board\_spec.xml File

| Element    | Attribute                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------|

| board      | version, name                                                                                       |

| device     | device_model, used_resources                                                                        |

| global_mem | name, max_bandwidth, interleaved_bytes, config_addr, [default], interface                           |

| host       | kernel_config                                                                                       |

| [channels] | interface                                                                                           |

| interfaces | interface, kernel_clk_reset                                                                         |

| compile    | <pre>project, revision, qsys_file, generic_kernel, generate_cmd, synthesize_cmd, auto_migrate</pre> |

**2.** For the board element, specify the board version and the name of the accelerator board. The name of the board must match the name of the directory in which the **board\_spec.xml** file resides.

**Important:** The board version must match the AOCL version you use to develop the Custom Platform.

**Attention:** The board name must contain a combination of only letters, numbers, underscores (\_), hyphens (-), or periods (.) (for example: s5\_net).

- 3. For the device element, perform the following steps to specify the name of the device model file.

- **a.** Navigate to the *ALTERAOCLSDKROOT*/share/models/dm directory, where *ALTERAOCLSDKROOT* points to the path to the AOCL installation. The directory contains a list of device models files that describe available FPGA resources on accelerator boards.

- **b.** If your device is listed in the **dm** directory, specify the device\_model attribute with the name of the device model file. Proceed to Step 4.

Altera SDK for OpenCL Custom Platform Toolkit User Guide

For example, device\_model="5sgsed8k2f40c2\_dm.xml"

- **c.** If your device is not listed in the **dm** directory, or if your board uses an FPGA that does not have a device model, create a new device model by performing the tasks described in Steps d to g:

- d. Copy a device model from the ALTERAOCLSDKROOT/share/models/dm directory (for example, 5sgxma7h2fe35c2\_dm.xml).

- **e.** Place your copy of the device model in the Custom Platform subdirectory in which your **board\_ spec.xml** file resides.

- f. Rename the file, and modify the values to describe the part your board uses.

- **g.** In the **board\_spec.xml** file, update the device\_model attribute of the device element with the name of your file.

- **4.** For the device element, specify the parameters in the used\_resources attribute to describe the FPGA resources that the board design consumes in the absence of any OpenCL kernel.

If your design includes a defined partition around all the board logic, you can extract the data from the Partition Statistics section of the Fitter report.

- **5.** For each global memory type, specify the following information:

- **a.** Name of the memory type.

- **b.** The combined maximum global memory bandwidth.

You can calculate this bandwidth value from datasheets of your memories.

**c.** The size of the data that the Altera Offline Compiler interleaves across memory banks.

**Note:** interleaved\_bytes = burst\_size X width\_bytes

- **d.** If you have a homogeneous memory system, proceed to Step e. If you have a heterogeneous memory system, for each global memory type, specify the <code>config\_addr</code> attribute with the base address of the ACL Mem Organization Control Qsys component (mem\_org\_mode).

- **e.** If you choose to set a global memory type as default, assign a value of 1 to the optional default attribute.

- If you do not include this attribute, the first memory defined in the **board\_spec.xml** file becomes the default memory.

- **f.** Specify the parameters in the interface attribute to describe the characteristics of each memory interface.

- **6.** For the host element, specify the parameters in the kernel\_config attribute to describe the offset at which the kernel resides. Determine the start of the offset from the perspective of the kernel\_cra master in the OpenCL Kernel Interface Qsys component.

- 7. If your board provides channels for direct OpenCL kernel-to-I/O accesses, include the channels element for all channel interfaces. Specify the parameters in the interface attribute to describe the characteristics of each channel interface.

- **8.** Include the interfaces element to describe the kernel interfaces connecting to and controlling OpenCL kernels. Include one of each interface types (that is master, irg, and streamsource).

- **a.** Specify the parameters in the interface attribute to describe the characteristics of each kernel interface.

For the streamsource interface type, also specify the clock attribute with the name of the clock the snoop stream uses. Usually, this clock is the kernel clock.

Important: Update the width of the snoop interface (acl\_internal\_snoop) specified with the streamsource kernel interface. Updating the width ensures that the global\_mem interface entries in board\_spec.xml match the characteristics of the bank<N> Avalon

Memory-Mapped (Avalon-MM) masters from corresponding OpenCL Memory Bank Divider component for the default memory.

- **b.** Specify the parameters in the kernel\_clk\_reset attribute to include the exported kernel clock and reset interfaces as kernel interfaces.

- **9.** Include the compile element and specify its attributes to control the Quartus Prime compilation, registration, and automigration.

Below is the XML code of an example **board\_spec.xml** file:

```

<?xml version="1.0"?>

<board version="15.0" name="a10_ref">

<compile project="top" revision="top" qsys_file="system.qsys" generic_kernel="1">

<generate cmd="qsys-generate --synthesis=VERILOG system.qsys"/>

<synthesize cmd="quartus_sh --flow compile top -c top"/>

<auto_migrate platform_type="a10_ref" >

<include fixes=""/>

<exclude fixes=""/>

</auto_migrate>

</compile>

<device device_model="10ax115s2f45i2sges_dm.xml">

<used resources>

<alms num="6566"/> <!-- ALMs used in final placement - ALMs used for</pre>

registers -->

<ffs num="20030"/>

<dsps num="0"/>

<rams num="112"/>

</used_resources>

</device>

<!-- DDR4-2133 -->

<global_mem name="DDR" max_bandwidth="17064" interleaved_bytes="1024"</pre>

config addr="0x018">

<interface name="board" port="kernel_mem0" type="slave" width="512"</pre>

maxburst="16" address="0x00000000" size="0x80000000" latency="240"/>

</global_mem>

<host>

<kernel_config start="0x00000000" size="0x0100000"/>

</host>

<interfaces>

<interface name="board" port="kernel_cra" type="master" width="64" misc="0"/>

<interface name="board" port="kernel_irq" type="irq" width="1"/>

<interface name="board" port="acl_internal_snoop" type="streamsource"</pre>

enable="SNOOPENABLE" width="31" clock="board.kernel_clk"/>

<kernel_clk_reset clk="board.kernel_clk" clk2x="board.kernel_clk2x"</pre>

reset="board.kernel_reset"/>

</interfaces>

</board>

```

#### **Related Information**

XML Elements, Attributes, and Parameters in the board\_spec.xml File on page 2-6

# **Creating the MMD Library**

Your Custom Platform requires an MMD layer necessary for communication with the accelerator board.

You must implement a file I/O-like software interface such as open, read, write, and close to communicate with the accelerator board over any medium. The result of your implementation is a set of linker arguments that allows an OpenCL host application to link against the MMD layer of the target board. A dynamic link library (DLL) that fully implements the MMD layer is also necessary for the communication.

### Figure 1-2: AOCL Software Architecture

This figure depicts the four layers of the Altera SDK for OpenCL software architecture: runtime, hardware abstraction layer (HAL), MMD layer, and kernel mode driver.

# Runtime (OpenCL API)

HAL for memory transfers and kernel launches

MMD layer for raw read and write operations

Kernel mode driver for accessing communication medium

### **Board Hardware**

The following tasks outline the procedure for creating an MMD library for use with PCI Express<sup>®</sup> (PCIe<sup>®</sup>).

1.

2. Name a new library file that implements the MMD layer in the following manner: <br/>

<b

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<br/>

<unique\_string> is a designation that you create. Altera recommends that you include information such as revision and interface type.

$\langle a|so|lib|dll\rangle$  is the file extension. It can be an archive file (**.a**), a shared object file (**.so**), a library file (**.lib**), or a dynamic link library file (**.dll**).

Example library file name: altera\_svdevkit\_pcierev1\_mmd.so

- **3.** Include the *ALTERAOCLSDKROOT*/board/custom\_platform\_toolkit/mmd/aocl\_mmd.h header file in the operating system-specific implementation of the MMD layer.

- The **aoci\_mmd.h** file and the *MMD API Descriptions* reference section contain full details on the MMD application programming interface (API) descriptions, their arguments, and their return values.

- **4.** Implement the MMD layer for your Custom Platform, and compile it into a C/C++ library. Example source codes of a functional MMD library are available in the **<path\_to\_s5\_net>/source/host/ mmd** directory of the Stratix V Network Reference Platform. In particular, the **acl\_pcie.cpp** file implements the API functions defined in the **aocl\_mmd.h** file.

If the AOCL users need to load a particular library at runtime, deliver the library in a directory that the operating system can locate. Instruct the AOCL users to add the library path to the *LD\_LIBRARY\_PATH* (for Linux) or *PATH* (for Windows) environment variable at runtime.

**5.** Modify the mmdlib and linkflags elements in the **board\_env.xml** file by specifying the library flags necessary for linking with the MMD layer.

#### **Related Information**

MMD API Descriptions on page 2-14

### **Kernel Power-up State**

The OpenCL kernel is an unknown state after you power-up your system or reprogram your FPGA. As a result, the MMD layer does not enable or respond to any interrupts from the kernel during these periods. The kernel is in a known state only after aocl\_mmd\_set\_interrupt\_handler is called. Therefore, enable interrupts from the kernel only after the handler becomes available to the MMD layer.

The general sequence of calls for a single host application is as follows:

- 1. get\_offline\_info

- 2. open

- 3. get\_info

- 4. set\_status\_handler

- 5. set\_interrupt\_handler

- 6. get\_info /read/write/copy/yield

- 7. close

### **Setting Up the Altera Client Driver**

The Altera SDK for OpenCL supports the Altera Client Driver (ACD) custom extension. The ACD allows the AOCL to automatically find and load the Custom Platform libraries at host runtime.

**Attention:** To allow AOCL users to use the ACD, you must remove the MMD library from the linklibs element in the **board\_env.xml** file.

### **Enumerating the Custom Platform ACD on Windows**

Specify the Custom Platform libraries in the registry key **HKEY\_LOCAL\_MACHINE\SOFTWARE** \**Altera\OpenCL\Boards**. Enter one value for each library. Each value must include the path to the library as the string value, and a **dword** setting of 0.

For example:

[HKEY\_LOCAL\_MACHINE\SOFTWARE\Altera\OpenCL\Boards] "c:\\board\_vendor a\\my\_board\_mmd.dll"=dword:00000000

To enumerate Custom Platform ACDs on Windows, the ACD Loader scans the value in the registry key **HKEY\_LOCAL\_MACHINE\SOFTWARE\Altera\OpenCL\Boards**. For each value in this key, the **dword** parameter specifies the path to a DLL and a numerical data value. If the **dword** data is 0, the Installable Client Driver (ICD) Loader attempts to open the corresponding DLL. If the DLL is an MMD library, then the AOCL attempts to open any board that is associated with that library.

In this case, the ACD opens the library c:\\board\_vendor a\\my\_board\_mmd.dll.

If the registry key specifies multiple libraries, the Loader loads the libraries in the order that they appear in the key. If there is an order dependency between the libraries available with your Custom Platform, ensure that you list the libraries accordingly in the registry key.

### **Enumerating the Custom Platform ACD on Linux**

Enter the absolute paths of Custom Platform libraries in an .acd file. Store the .acd file in the /opt/Altera/ OpenCL\_boards/ directory.

To enumerate Custom Platform ACDs on Linux, the ACD Loader scans the files with the extension .acd in the path /opt/Altera/OpenCL\_boards/. The ACD Loader opens each .acd file in this path as a text file. Each .acd file should contain the absolute path to every library in the Custom Platform, one library per line. The ICD Loader attempts to open each library. If the library is an MMD library, then the AOCL attempts to open any board that is associated with that library.

For example, consider the file /opt/Altera/OpenCL\_boards/PlatformA.acd. If it contains the line /opt/PlatformA/libPlatformA\_mmd.so, the ACD Loader loads the library /opt/PlatformA/libPlatformA\_mmd.so.

If the .acd file specifies multiple libraries, the Loader loads the libraries in the order that they appear in the file. If there is an order dependency between the libraries available with your Custom Platform, ensure that you list the libraries accordingly in the .acd file.

For more information on how AOCL users link their host applications to the ICD and ACD, refer to the Linking Your Host Application to the Khronos ICD Loader Library section in the Altera SDK for OpenCL Programming Guide.

#### **Related Information**

Linking Your Host Application to the Khronos ICD Loader Library

### **Providing AOCL Utilities Support**

Each Custom Platform you develop for use with the Altera SDK for OpenCL must support a set of AOCL utilities. These utilities enable users to manage the accelerator board through the AOCL.

If you create a new Custom Platform, perform the following tasks to create executables of the AOCL utilities and then store them in the **utilbindir** directory of your Custom Platform:

**Tip:** Within the respectively. Scripts for the install and uninstall utilities are available in the capath\_to\_s5\_net>/<OS\_platform>/libexec directory.

You can find the source code for the diagnose utility in the path\_to\_a10\_ref>/source/util/diagnostic directory within the Arria<sup>®</sup> 10 FPGA Development Kit Reference Platform. Contact your Altera field application engineer or technical account manager for more information.

- 1. Create an install utility executable that sets up the current host computer with the necessary drivers to communicate with the board via the MMD layer. The install utility takes no argument. For example, the PCIe-based MMD might need to install PCIe drivers into the host operating system. Executable call: aocl install

- 2. Create an uninstall utility executable that removes the current host computer drivers (for example, PCIe drivers) used for communicating with the board. The uninstall utility takes no argument.

- Executable call: aocl uninstall

- **3.** Create a diagnose utility executable that confirms the board's integrity and the functionality of the MMD layer.

The diagnose utility must support the following internal calling modes:

| Calling Mode                                                                              | Description                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -probe                                                                                    | Prints all available devices in a Custom Platform. For a given hardware configuration, the utility lists the devices in the same order, and each device is associated with the same identification string each time. |

| -probe <i><device_name></device_name></i>                                                 | Queries the specified device and prints summary statistics abou the device.                                                                                                                                          |

| <pre><device_name></device_name></pre>                                                    | Performs a full diagnostic test for the specified device.                                                                                                                                                            |

| where <i><device name=""></device></i> is the string that corresponds to the FPGA device. | The utility generates the message DIAGNOSTIC_PASSED as the output. Otherwise, the utility generates the message DIAGNOSTIC_FALIED.                                                                                   |

When users invoke the diagnose utility command without an argument, it queries the devices in the Custom Platform and supplies a list of valid < device\_name > strings assigned to the list of devices.

Executable call without argument: aocl diagnose

When users invoke the diagnose utility command with a < device\_name > argument, the utility runs your diagnostic test for the board. A user may give a board a different logical device name than the physical device name associated with the Custom Platform. The aocl utility simply converts the user-side logical device name to the Custom Platform-side physical device name. If the diagnostic test runs successfully, the utility generates the message DIAGNOSTIC\_PASSED as the output. Otherwise, the utility generates the message DIAGNOSTIC\_FALIED.

Executable call with argument: aocl diagnose <device\_name>.

4. Create a program utility executable that receives the **fpga.bin** file and configures that design onto the FPGA. Although the main method for FPGA programming is via the host and the MMD, make this utility available to users who do not have a host system or who perform offline reprogramming.

The program utility command takes < device\_name > and an Altera Offline Compiler Executable file name (<kernel\_filename>.aocx) as arguments. When users invoke the command, the AOCL extracts the fpga.bin file and passes it to the program utility.

Important: Altera highly recommends that the program utility links with and calls the aocl\_mmd\_reprogram function implemented in the MMD layer. Refer to the aocl\_mmd\_reprogram and Reprogram Support reference sections for more information.

Executable call: aocl program <device\_name> <kernel\_filename>.aocx, where <device name> is the acl number that corresponds to the FPGA device.

5. Create a flash utility executable that receives the **fpga.bin** file and programs that design into the flash memory on the board. The flash utility command takes < *device\_name* > and a .aocx file name as arguments. When users invoke the command, the AOCL extracts the **fpga.bin** file and passes it to the flash utility.

Executable call: aocl flash <device\_name> <kernel\_filename>.aocx, where <device name> is the acl number that corresponds to the FPGA device.

When users invoke a utility command, the utility probes the current Custom Platform's **board\_env.xml** file and executes the **<utility\_executable>** file within the **utilibindir** directory.

#### **Related Information**

- Creating the board\_env.xml File on page 1-10

- Reprogram Support on page 2-25

- aocl\_mmd\_reprogram on page 2-25

### **Testing the Hardware Design**

After you create the software utilities and the MMD layer, and your hardware design achieves timing closure, test the design.

To test the hardware design, perform the following tasks:

- Navigate to the boardtest.cl OpenCL kernel within the ALTERAOCLSDKROOT/board/custom\_platform\_ toolkit/tests/boardtest directory.

- ALTERAOCLSDKROOT points to the location of the Altera SDK for OpenCL installation.

- 2. Compile your kernel to generate an Altera Offline Compiler Executable file (.aocx) by invoking the aoc --no-interleaving default boardtest.cl command.

- **3.** Program the accelerator board by invoking the aocl program acl0 boardtest.aocx command.

- **4.** Invoke the commands aocl compile-config and aocl link-config. Confirm they include flags necessary for your MMD layer to compile and link successfully.

- **5.** Build the **boardtest** host application.

- For Windows systems, you may invoke the make command or use Microsoft Visual Studio.

- If you invoke the make command, the Makefile is located in the ALTERAOCLSDKROOT/board/custom\_platform\_toolkit/tests/boardtest directory.

- If you build your host application in Microsoft Visual Studio, the **boardtest.sin** and **main.cpp** files are located in the *ALTERAOCLSDKROOT*/board/custom\_platform\_toolkit/tests/boardtest/host directory.

- For Linux systems, invoke the make -f Makefile.linux command.

- The Makefile.linux file is located in the ALTERAOCLSDKROOT/board/custom\_platform\_toolkit/tests/boardtest directory.

- **6.** Run the **boardtest** executable.

**Attention:** To ensure that your hardware design produces consistent performance, you might have to test it using multiple OpenCL kernels in addition to **boardtest.cl**.

To qualify as an Altera preferred board, rigorous testing across multiple boards is necessary. Specifically, you should perform overnight testing of all Custom Platform tests and executes the AOCL example designs on multiple boards . All board variants within a Custom Platform must go through the testing process.

# **Applying for the Altera Preferred Board Status**

Registering your Custom Platform and the supported FPGA boards in the Altera Preferred Board Partner Program allows them to benefit from ongoing internal testing across versions of the Quartus Prime Design Suite. Altera-tested Custom Platforms and boards are more likely to be forward compatible with future QPDS versions.

For your Custom Platform and the supported FPGA boards to achieve the Altera Preferred Board status, you must generate the following data and submit it to Altera:

- 1. The output from invoking the aocl board-xml-test command.

- **2.** The output from invoking the aoc --list-boards command.

- **3.** The outputs from the host compilation, host execution, and all Quartus Prime report files (.rpt). Also, for each board in your Custom Platform, the acl\_quartus\_report.txt file from the following tests:

- **a.** All tests included in the *ALTERAOCLSDKROOT*/board/custom\_platform\_toolkit/tests directory, where *ALTERAOCLSDKROOT* points to location of the Altera SDK for OpenCL installation.

- **b.** Compilations of the following examples on the OpenCL Design Examples page of the Altera website:

- 1. Vector Addition

- 2. Matrix Multiplication

- 3. FFT (1D)

- **4.** FFT (2D)

- **5.** Sobel Filter

- **6.** Finite Difference Computation (3D)

- **4.** For each board in the Custom Platform, a summary of the following:

- **a.** HOST-TO-MEMORY BANDWIDTH as reported by the boardtest test in the Custom Platform Toolkit (/ tests/boardtest).

- **b.** KERNEL-TO-MEMORY BANDWIDTH as reported by the boardtest test.

- **c.** Throughput in swap-and-execute(s) reported by the swapper test in the Custom Platform Toolkit (*t* **tests/swapper**).

- **d.** Actual clock freq as reported in the acl\_quartus\_report.txt file from the blank test in the Custom Platform Toolkit (ALTERAOCLSDKROOT/board/custom\_platform\_toolkit/tests/blank).

**Important:** Use global routing to reduce consumption of local routing resources. Using global routing is necessary because it helps meet timing and improve kernel performance (Fmax). Use global or regional routing for any net with fan-out greater than 5000, and for kernel clock, 2x clock and reset. Check the Non-Global High Fan-Out Signals report in the Resource subsection, which is under the Fitter section of the Compilation Report.

- 5. Submit the necessary number of boards to Altera for in-house regression testing. Regression testing tests the out-of-the-box experience for each board variant on each operating system that your Custom Platform supports. Ensure that you test the procedure outlined below before you submit your boards:

- **a.** Install the board into the physical machine.

- **b.** Boot the machine and invoke the aocl install utility command.

- c. Invoke the aocl diagnose command.

- **d.** Run the AOCL test programs. The tester can also invoke the aocl program *<device\_name> <kernel\_filename>*.cl command to verify the functionality of the program utility.

#### **Related Information**

OpenCL Design Examples page on the Altera website

# **Shipping Recommendations**

Before shipping your Altera-verified board to Altera SDK for OpenCL users, program the flash memory of the board with the hello\_world OpenCL design example. Programming the flash memory of the board with the hello\_world.aocx hardware configuration file allows the AOCL user to power on the board and observe a working kernel.

Download the hello\_world OpenCL design example from the OpenCL Design Examples page on the Altera website.

For more information, refer to the **README.txt** file available with the hello\_world OpenCL design example and the *Programming the Flash Memory of an FPGA* sections in the *Altera SDK for OpenCL Getting Started Guide*.

#### **Related Information**

- OpenCL Design Examples on the Altera website

- Programming the Flash Memory of an FPGA on Windows

- Programming the Flash Memory of an FPGA on Linux

# **Document Revision History**

Table 1-4: Document Revision History of the AOCL Custom Platform Design Chapter of the Altera SDK for OpenCL Custom Platform Toolkit User Guide

| Date             | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November<br>2015 | 2015.11.02 | <ul> <li>Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i>.</li> <li>Changed instances of <i>Altera Complete Design Suite</i> to <i>Quartus Prime Design Suite</i>.</li> <li>Updated the support requirement for the diagnose utility in the <i>Providing AOCL Utilities Support</i> section.</li> <li>In the <i>Creating the board_env.xml File</i> section, added the mmdlib XML element to the list of elements included in the <b>board_env.xml</b> file.</li> </ul> |

| May 2015         | 15.0.0     | Added the Setting Up the Altera Client Driver section.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Date             | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December<br>2014 | 14.1.0  | <ul> <li>Specified that the Custom Platform Toolkit is available in the ALTERAOCLSDKROOT/board directory.</li> <li>Added the uninstall utility executable in the Providing AOCL Utilities Support section.</li> <li>Indicated that the version attributes in the board_env.xml and board_spec.xml files have to match the Altera Complete Design Suite and Altera SDK for OpenCL version you use to develop the Custom Platform.</li> <li>Added instruction for including the compile eXtensible Markup Language element and its associated attributes in the board_spec.xml file in the section Creating the board_spec.xml File.</li> <li>Added information on the automigration of Custom Platform in sections Custom Platform Automigration and Customizing Automigration.</li> <li>Removed the Generating the Rapid Prototyping Library section.</li> </ul> |