## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

### Objective

This example demonstrates how to use the adjustable gain feature of the programmable gain amplifier (PGA) Component in PSoC CY8C4Axx devices during runtime.

### **Overview**

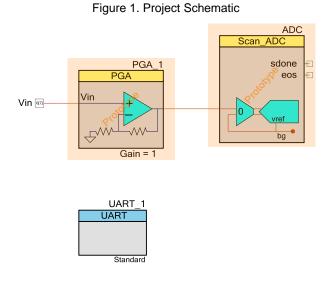

The project adjusts the gain of the PGA in 3-dB steps from 0 to 30 dB. At each gain, the output of the PGA is measured with the analog-to-digital converter (ADC) and printed out to a terminal emulator with the universal asynchronous receiver transmitter (UART) Component.

## Requirements

Tool: PSoC Creator 4.1 or higher

Programming Language: C (GCC 4.9.0) or higher

Associated Parts: All PSoC CY8C4Axx Analog Coprocessor devices

Related Hardware: CY8CKIT-048 PSoC Analog Coprocessor Pioneer Kit

## Design

This project demonstrates the use of a PGA Component in a circuit and how to change the gain during runtime in firmware. An external voltage is applied to the pin labeled "Vin" (P0[7]), which is the input to the PGA. The program slowly increases the PGA's gain in 3-dB steps from a gain of 1, to a gain of 32, then starts over again at a gain of 1. At each gain step, the ADC will measure the output of the PGA. The ADC's result and gain will be printed with a UART (UART\_1) through P0[5]. The results are printed in the following format: "Gain = xx, yyy mVolts", where 'xx' is the gain in dB and 'yyy' is the voltage in millivolts. Any common terminal emulator will be able to display the information.

#### **Design Considerations**

Because the gain of the PGA will go to 32 (30 dB), and the ADC's range is 0 to 2.4 volts in this configuration, the maximum voltage that you can apply to Vin without saturating the ADC is about 74 mV ( $0.074 \times 32 = -2.4$  volts). Any voltage between the power supply rails may be applied to Vin without damaging the PGA or the PSoC device.

### **Hardware Setup**

A power supply and a potentiometer can be used to supply a voltage to Vin (P0[7]). The result will stream out of the PSoC devices' UART TX signal through P0[5].

To see the output of the project, you will need to use a terminal emulator. There are several free emulators such as TeraTerm, Putty, or Hyperterm. The UART terminal settings are 9600 baud, 8 data bits, and 1 stop bit.

## Components

Table 1 lists the PSoC Creator Components used in this example, as well as the hardware resources used by each.

| Component or User Module | Hardware Resources                           |

|--------------------------|----------------------------------------------|

| PGA_1                    | 1/2 CTB (Continuous<br>Time Block)           |

| ADC                      | Scan_ADC                                     |

| UART_1                   | Serial Communication<br>Block (SCB)          |

| Vin                      | General Purpose Input<br>Output (GPIO) P0[7] |

| UART_1:tx                | GPIO (P0[5])                                 |

| Table 1. List of PSoC Creator | Components |

|-------------------------------|------------|

|-------------------------------|------------|

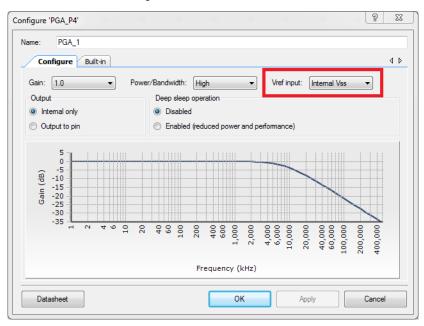

#### **Parameter Settings**

There is only one change in the default PGA settings to make it work for this code example. The Vref input was changed from "External" to "Internal Vss". All other parameters were left as default as shown in Figure 2.

Figure 2. PGA User Interface

Several parameters were changed in the ADC's interface. Figure 3 highlights where each of these changes in the list below are made.

- A. Sequenced channels set to '1'.

- B. Changed Input mode to 'Single ended'.

- C. Enabled averaging by selecting the check box.

- D. Set the Minimum acquisition time to '1000'.

- E. Changed Sample mode to 'Single shot, triggered'.

| Figure 3.  | ADC Use  | r Interface |

|------------|----------|-------------|

| i iguio o. | 1.00 000 | micinauo    |

| Configure 'Scan_ADC'                     | ? <u>-</u>                                                                                                                                                       | x |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Name: ADC                                |                                                                                                                                                                  |   |

| Config0 Common Built-in                  | ٩                                                                                                                                                                | Þ |

| Scan Filter                              |                                                                                                                                                                  |   |

| Timing<br>Free-run scan rate (SPS): 5000 | Achieved: Available rates:<br>222,222 SPS 222,222 to 222,222 SPS<br>12 MHz 1 to 1.6 MHz<br>4.500 us Sample Mode<br>Continuous<br>Single shot<br>Use soc terminal |   |

| Input Range                              |                                                                                                                                                                  |   |

| Vref select: System bandgap              | ▼ 1.200 V 12-bit code range: Volt range:                                                                                                                         |   |

| Vref bypass                              | Diff.: 0x800 to 0x7FF Vn-Vref to Vn+Vref                                                                                                                         |   |

| Vneg for S/E: Vref                       | S/E: 0x000 to 0xFFF 0 to 2*Vref                                                                                                                                  |   |

| Result Data Format                       | Interrupt Limits                                                                                                                                                 |   |

| Diff. result format: Signed              | ▼ Compare mode: Result < Low ▼                                                                                                                                   |   |

| S/E result format: Unsigned              | ▼ Low (hex): 200 🐳 High (hex): E00 🛓                                                                                                                             |   |

| Samples averaged: 2                      | Diff. value (V): 0.30 V 1.20 V                                                                                                                                   |   |

| Averaging mode: Sequential, Fixed        | S/E value (V):         0.30 V         2.10 V           Diff. avg (V):         0.30 V         1.20 V                                                              |   |

| Alternate resolution: 8-bit              | <ul> <li>✓ S/E avg (V): 0.30 V</li> <li>✓ 2.10 V</li> </ul>                                                                                                      |   |

|                                          |                                                                                                                                                                  |   |

| Channels<br>Number of channels:          |                                                                                                                                                                  |   |

| Ch. En Resolution Inpu                   | out mode Avg Minimum acq. Achieved Limit Sat.<br>time (ns) acq. time (ns) interrupt interrupt                                                                    |   |

| 0 📝 12-bit 👻 Single ended                |                                                                                                                                                                  |   |

| В                                        | C D                                                                                                                                                              |   |

| Datasheet                                | OK Apply Cancel                                                                                                                                                  |   |

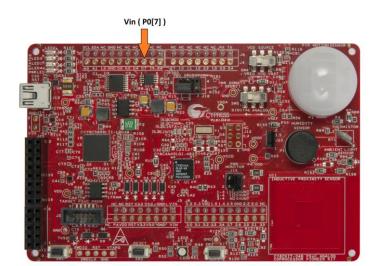

## Operation

To test the project, compile and program the PSoC device. Connect the test voltage to pin P0[7] as indicated in Figure 4. The input voltage should be between 0 and ~74 millivolts because the PGA will provide a gain between 1 and 32. An input voltage above ~74 mV will saturate the ADC because in this configuration, the maximum input to the ADC is 2.4 volts.

The CY8CKIT-048 development kit has a serial-to-USB converter built into the kit. Port P0[5] is connected directly to the RX input of the serial-to-USB converter, so no additional connection is required. Run a terminal emulator on your development PC and set it to 9600 baud, 8 data bits, and 1 parity bit. Select the COM port that is labeled "Cypress KitProg2 USB-UART" in the port selection of your terminal emulator settings. The ADC reading for each gain setting should be scrolling down the screen. Use a voltmeter to measure the input voltage and compare with the results on the terminal emulator. Remember that input voltages above ~74 mV will saturate the ADC with a gain of 32.

Figure 4. CY8CKIT-048

## **Related Documents**

Table 2 lists all relevant application notes, device datasheets, and Component datasheets.

Table 2. Related Documents

| Application Notes                               |                                                    |  |  |

|-------------------------------------------------|----------------------------------------------------|--|--|

| AN211293                                        | Getting Started with PSoC Analog Coprocessor       |  |  |

| PSoC Creator Component D                        | atasheets                                          |  |  |

| PGA                                             | Programmable Gain Amplifier                        |  |  |

| ADC                                             | PSoC 4 Scanning SAR ADC                            |  |  |

| Pins                                            | General Purpose IO Pins                            |  |  |

| Device Documentation                            |                                                    |  |  |

| Cy8C4Axx Datasheet                              | PSoC Analog Coprocessor: CY8C4Axx Family Datasheet |  |  |

| Development Kit (DVK) Documentation             |                                                    |  |  |

| CY8CKIT-048 PSoC Analog Coprocessor Pioneer Kit |                                                    |  |  |

| PSoC® Family Web Page                           |                                                    |  |  |

| PSoC Analog Coprocessor                         |                                                    |  |  |

# **Document History**

Document Title: CE204024 - PSoC® CY8C4Axx Programmable Gain Amplifier

Document Number: 002-04024

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                              |

|----------|---------|--------------------|--------------------|--------------------------------------------------------------------|

| **       | 5262424 | MEH                | 05/06/2016         | New Code Example                                                   |

| *A       | 5435468 | MEH                | 09/28/2016         | Updated project with version 1.20 of Scan ADC.<br>Updated template |

| *В       | 5723938 | MEH                | 05/19/2017         | Changed ADC type from ADC_SAR_SEQ to Scan_ADC                      |

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| ARM® Cortex® Microcontrollers | cypress.com/arm        |

|-------------------------------|------------------------|

| Automotive                    | cypress.com/automotive |

| Clocks & Buffers              | cypress.com/clocks     |

| Interface                     | cypress.com/interface  |

| Internet of Things            | cypress.com/iot        |

| Memory                        | cypress.com/memory     |

| Microcontrollers              | cypress.com/mcu        |

| PSoC                          | cypress.com/psoc       |

| Power Management ICs          | cypress.com/pmic       |

| Touch Sensing                 | cypress.com/touch      |

| USB Controllers               | cypress.com/usb        |

| Wireless Connectivity         | cypress.com/wireless   |

### **PSoC® Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Videos | Blogs | Training | Components

### **Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

© Cypress Semiconductor Corporation, 2016-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or system (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.