# Programmer's Guide

## DLPC900 Programmer's Guide

### Table of Contents

|                                                                   |    |

|-------------------------------------------------------------------|----|

| <b>Read This First</b>                                            | 4  |

| About This Manual                                                 | 4  |

| Related Documents from Texas Instruments                          | 4  |

| If You Need Assistance                                            | 4  |

| <b>1 Interface Protocol</b>                                       | 5  |

| 1.1 I <sup>2</sup> C Interface                                    | 5  |

| 1.1.1 I <sup>2</sup> C Transaction Structure                      | 5  |

| 1.1.1.1 I <sup>2</sup> C START Condition                          | 5  |

| 1.1.1.2 I <sup>2</sup> C STOP Condition                           | 5  |

| 1.1.1.3 DLPC900 Slave Address                                     | 5  |

| 1.1.1.4 DLPC900 Sub-Address and Data Bytes                        | 5  |

| 1.1.2 Example I <sup>2</sup> C Read Command Sequence              | 6  |

| 1.1.2.1 Read Command Example with Parameters                      | 6  |

| 1.1.2.3 Example I <sup>2</sup> C Write Command Sequence           | 7  |

| 1.2 USB Interface                                                 | 7  |

| 1.2.1 USB Transaction Sequence                                    | 7  |

| 1.2.2 USB Read Transaction Sequence Example                       | 9  |

| 1.2.3 USB Write Transaction Sequence Example                      | 10 |

| 1.3 INIT_DONE Signal                                              | 10 |

| <b>2 DLPC900 Control Commands</b>                                 | 11 |

| 2.1 DLPC900 Status Commands                                       | 11 |

| 2.1.1 Hardware Status                                             | 12 |

| 2.1.2 System Status                                               | 13 |

| 2.1.3 Main Status                                                 | 13 |

| 2.1.4 Retrieve Firmware Version                                   | 14 |

| 2.1.5 Reading Hardware Configuration and Firmware Tag Information | 14 |

| 2.1.6 Read Error Code                                             | 15 |

| 2.1.7 Read Error Description                                      | 15 |

| 2.2 DLPC900 Firmware Programming Commands                         | 16 |

| 2.2.1 Read Status                                                 | 16 |

| 2.2.2 Enter Program Mode                                          | 18 |

| 2.2.3 Exit Program Mode                                           | 18 |

| 2.2.4 Read Control                                                | 19 |

| 2.2.5 Start Address                                               | 19 |

| 2.2.6 Erase Sector                                                | 20 |

| 2.2.7 Download Flash Data Size                                    | 20 |

| 2.2.8 Download Data                                               | 20 |

| 2.2.9 Calculate Checksum                                          | 21 |

| 2.2.10 Controller Enable/Disable Command                          | 21 |

| 2.3 Chipset Control Commands                                      | 22 |

| 2.3.1 Chipset Configuration Commands                              | 22 |

| 2.3.1.1 Power Mode                                                | 22 |

| 2.3.1.2 DMD Park/Unpark                                           | 23 |

| 2.3.1.3 Curtain Color                                             | 23 |

| 2.3.2 Parallel Interface Configuration                            | 24 |

| 2.3.2.1 Parallel Port Configuration                               | 24 |

| 2.3.2.2 Input Data Channel Swap                                   | 25 |

| 2.3.3 Input Source Commands                                       | 25 |

| 2.3.3.1 Port and Clock Configuration                              | 25 |

| 2.3.3.2 Input Source Configuration                                | 26 |

| 2.3.3.3 Input Pixel Data Format                                   | 27 |

**Table of Contents**

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 2.3.3.4 Internal Test Pattern Select.....                          | 27 |

| 2.3.3.5 Internal Test Patterns Color.....                          | 28 |

| 2.3.3.6 Load Image.....                                            | 29 |

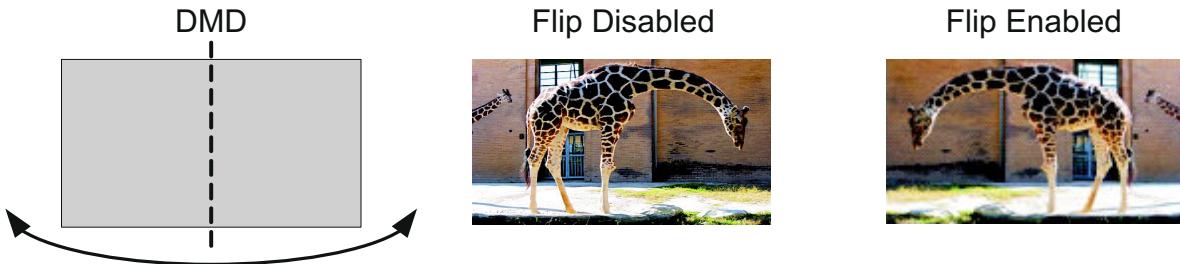

| 2.3.4 Image Flip.....                                              | 29 |

| 2.3.4.1 Long-Axis Image Flip.....                                  | 29 |

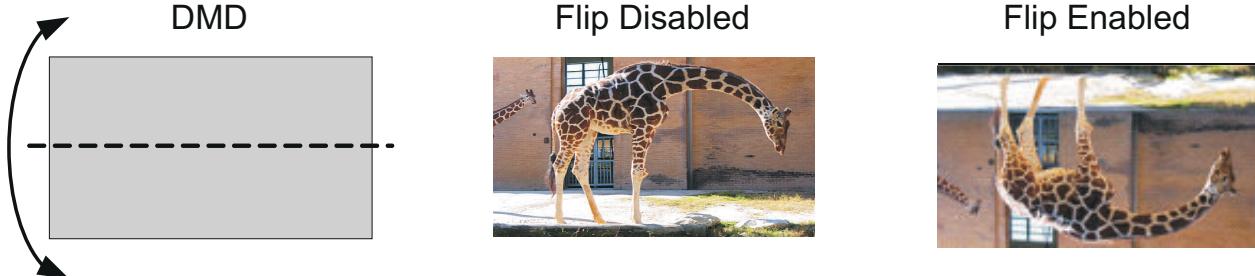

| 2.3.4.2 Short Axis Image Flip.....                                 | 30 |

| 2.3.5 IT6535 Power Mode.....                                       | 30 |

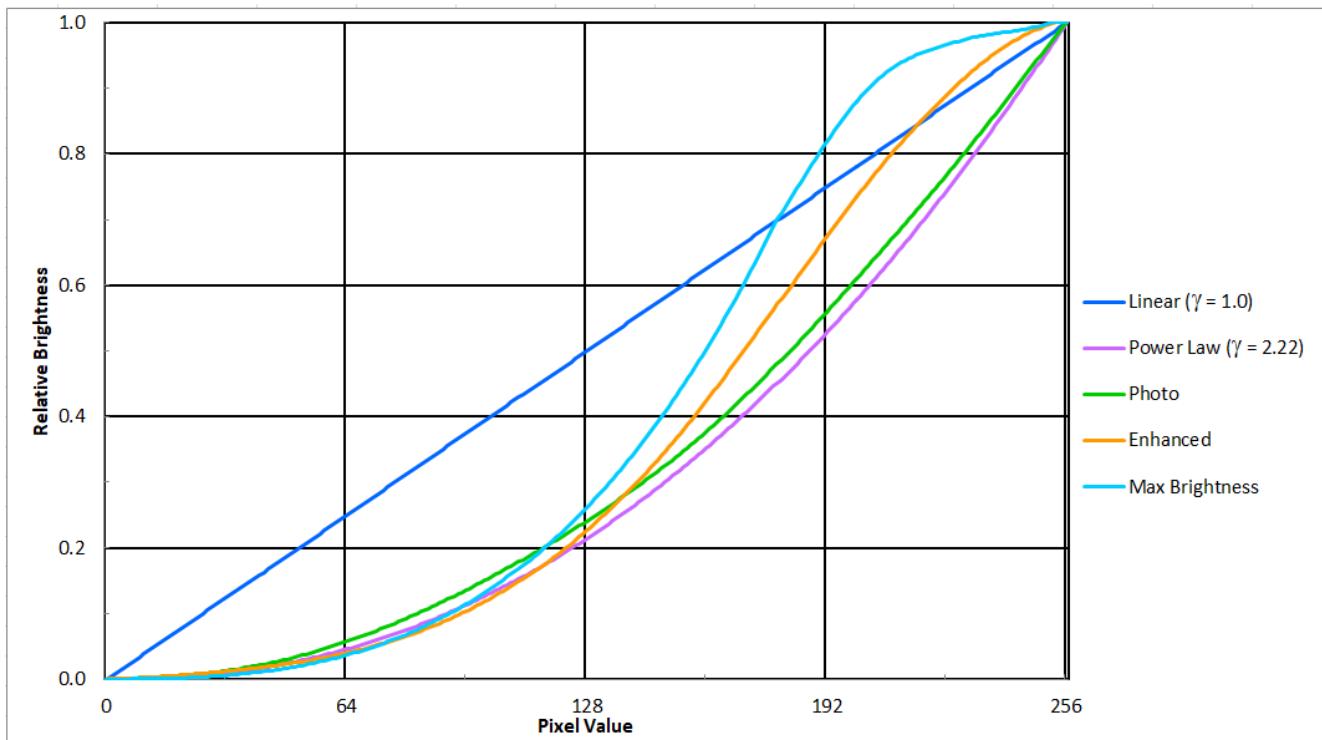

| 2.3.6 Gamma Configuration and Enable.....                          | 31 |

| 2.3.7 LED Driver Commands.....                                     | 33 |

| 2.3.7.1 LED Enable Outputs.....                                    | 33 |

| 2.3.7.2 LED Driver Current.....                                    | 35 |

| 2.3.7.3 Minimum LED Pulse Width in microseconds (μs).....          | 36 |

| 2.3.7.4 Minimum LED Pulse Width in nanoseconds (ns).....           | 36 |

| 2.3.7.5 Get Minimum LED Pattern Exposure in microseconds (μs)..... | 36 |

| 2.3.7.6 Get Minimum LED Pattern Exposure in nanoseconds (ns).....  | 36 |

| 2.3.8 GPIO Commands.....                                           | 37 |

| 2.3.8.1 GPIO Configuration.....                                    | 37 |

| 2.3.8.2 GPIO Clock Configuration.....                              | 38 |

| 2.3.8.3 GPIO Busy.....                                             | 38 |

| 2.3.9 Pulse Width Modulated (PWM) Control.....                     | 38 |

| 2.3.9.1 PWM Setup.....                                             | 39 |

| 2.3.9.2 PWM Enable.....                                            | 39 |

| 2.3.10 Batch File Commands.....                                    | 40 |

| 2.3.10.1 Batch File Name.....                                      | 40 |

| 2.3.10.2 Batch File Execute.....                                   | 40 |

| 2.3.10.3 Batch File Delay.....                                     | 40 |

| 2.3.10.4 Batch File Example.....                                   | 41 |

| 2.4 Display Mode Commands.....                                     | 41 |

| 2.4.1 Display Mode Selection.....                                  | 45 |

| 2.4.1.1 Video Mode Resolution.....                                 | 46 |

| 2.4.1.2 Input Display Resolution.....                              | 46 |

| 2.4.1.3 DMD Block Load.....                                        | 46 |

| 2.4.1.4 Minimum Exposure Times.....                                | 47 |

| 2.4.1.5 DMD Idle Mode.....                                         | 48 |

| 2.4.2 Image Header.....                                            | 49 |

| 2.4.3 Pattern Image Compression.....                               | 49 |

| 2.4.3.1 Run-Length Encoding.....                                   | 49 |

| 2.4.3.2 Enhanced Run-Length Encoding.....                          | 50 |

| 2.4.4 Pattern Display Commands.....                                | 51 |

| 2.4.4.1 Trigger Commands.....                                      | 51 |

| 2.4.4.2 LED Enable Delay Commands.....                             | 54 |

| 2.4.4.3 Pattern Display Commands.....                              | 56 |

| 2.4.4.4 Pattern On-The-Fly Commands.....                           | 60 |

| 2.4.4.5 I <sup>2</sup> C Pass Through Commands.....                | 62 |

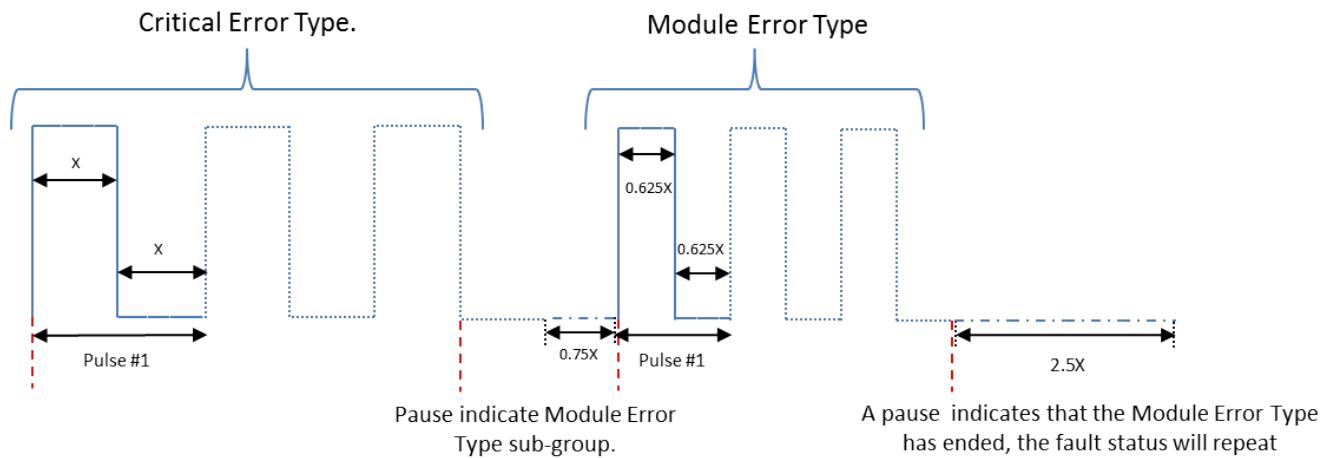

| 3 DLPC900 Fault Status.....                                        | 64 |

| 3.1 DLPC900 FAULT_STATUS Location(s).....                          | 64 |

| 3.2 DLPC900 FAULT_STATUS Interpretation.....                       | 64 |

| 4 Power-Up and Power-Down and Initialization Considerations.....   | 65 |

| 4.1 Power Up.....                                                  | 65 |

| 4.2 Power Down.....                                                | 65 |

| 4.3 Power-Up Auto-Initialization.....                              | 65 |

| 5 Command Examples.....                                            | 66 |

| 5.1 Video Pattern Mode Example.....                                | 66 |

| 5.2 Pre-Stored Pattern Mode Example.....                           | 66 |

| 5.3 Pattern On-The-Fly Example.....                                | 67 |

| 5.4 I <sup>2</sup> C Pass Through Write Example.....               | 67 |

| 5.5 I <sup>2</sup> C Pass Through Read Example.....                | 67 |

| A Register Quick Reference.....                                    | 68 |

| A.1 I <sup>2</sup> C Register Quick Reference.....                 | 68 |

| A.2 Command Guide.....                                             | 70 |

| B Batch File Command Descriptors.....                              | 72 |

| B.1 Command Descriptors.....                                       | 72 |

| Revision History.....                                              | 74 |

## List of Figures

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| Figure 1-1. I <sup>2</sup> C Read Command Waveform Diagram.....         | 6  |

| Figure 1-2. I <sup>2</sup> C Read Data Waveform Diagram.....            | 6  |

| Figure 1-3. I <sup>2</sup> C Write Command Waveform Diagram.....        | 7  |

| Figure 1-4. USB HID Protocol.....                                       | 8  |

| Figure 1-5. USB Multi-Transfer Transaction.....                         | 8  |

| Figure 2-1. Image Long-Axis Flip Example.....                           | 30 |

| Figure 2-2. Image Short-Axis Flip Example.....                          | 30 |

| Figure 2-3. Gamma Chart.....                                            | 32 |

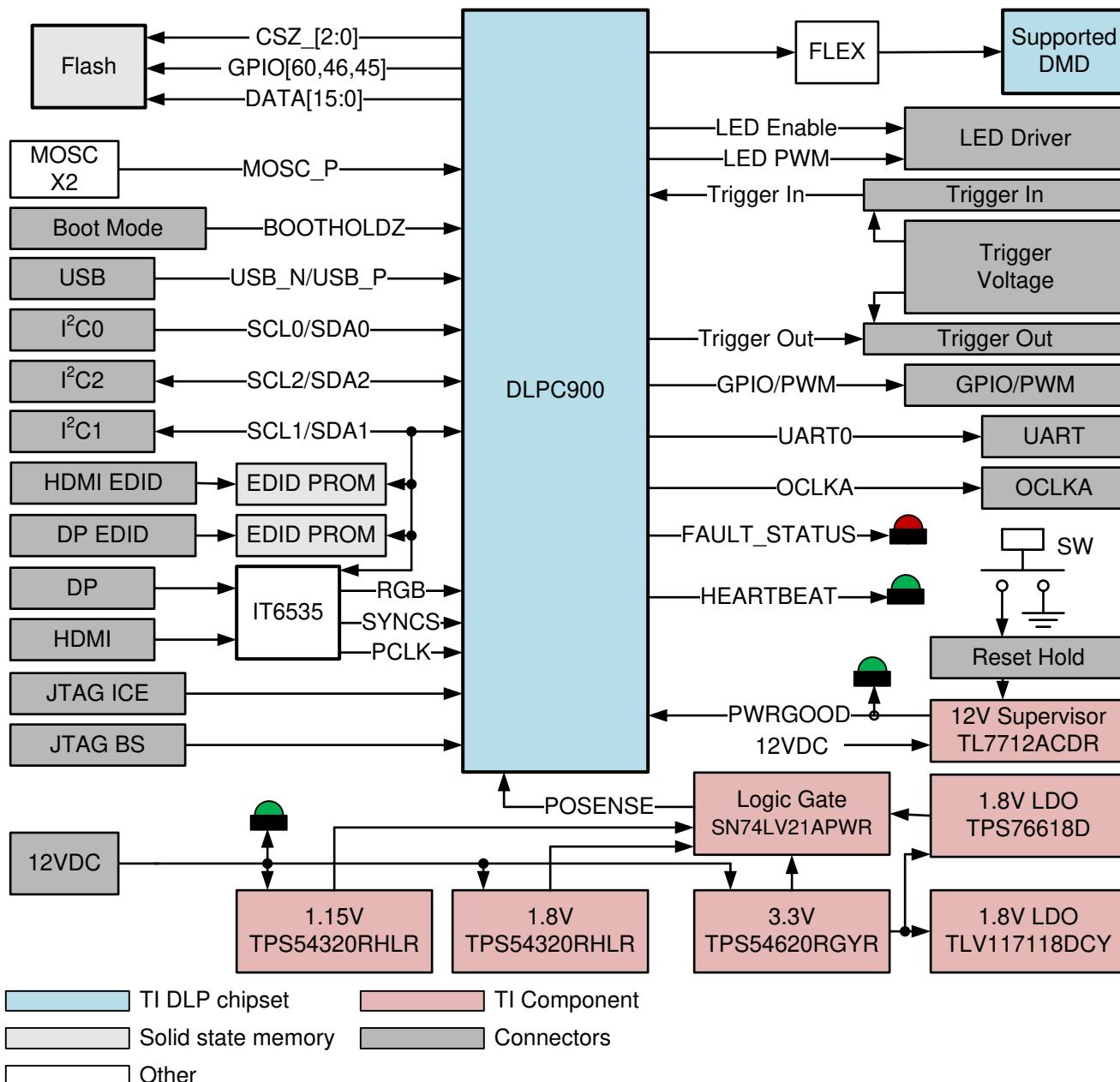

| Figure 2-4. DLPC900 Single Controller System Block Diagram.....         | 42 |

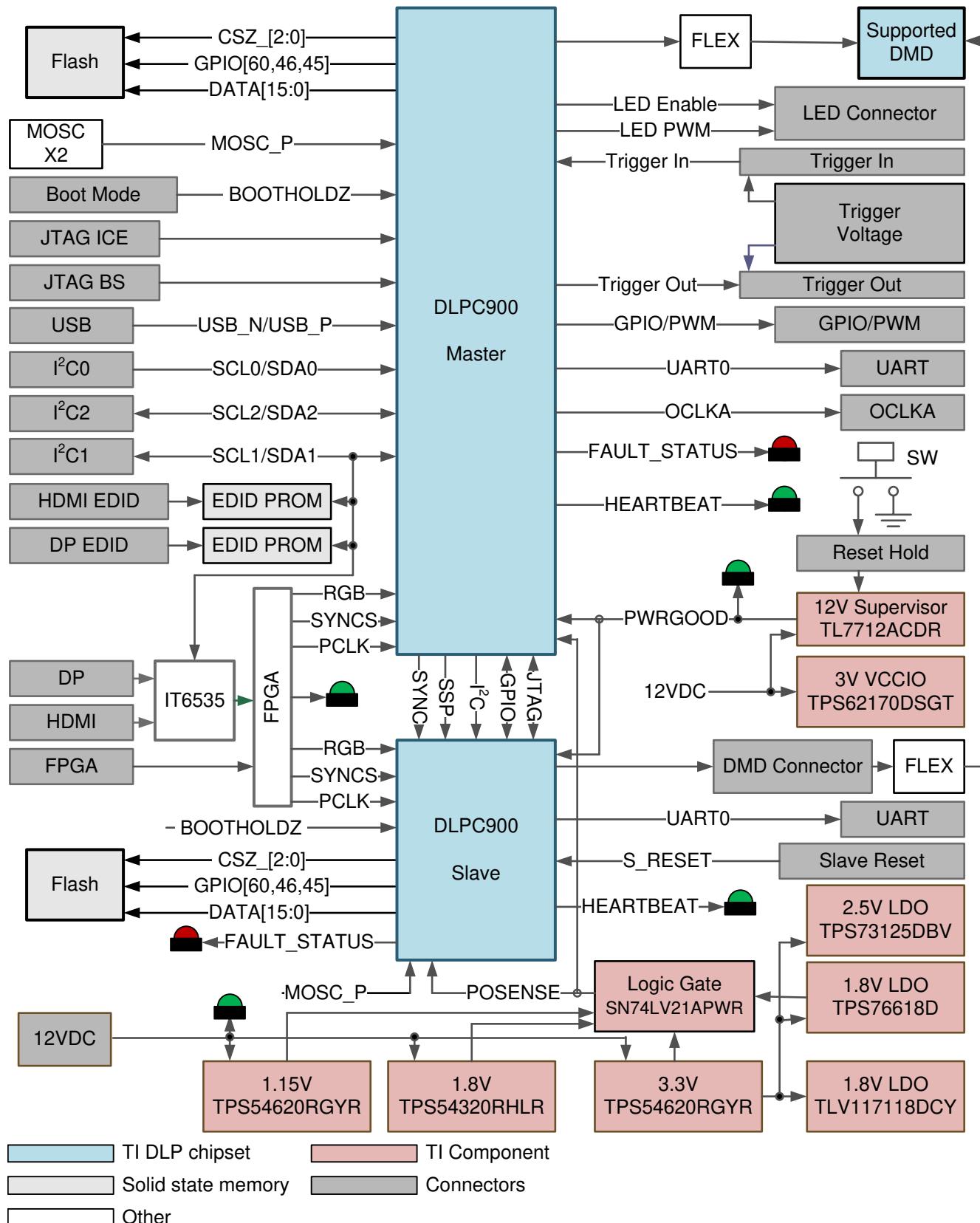

| Figure 2-5. DLPC900 Dual Controller System Block Diagram.....           | 43 |

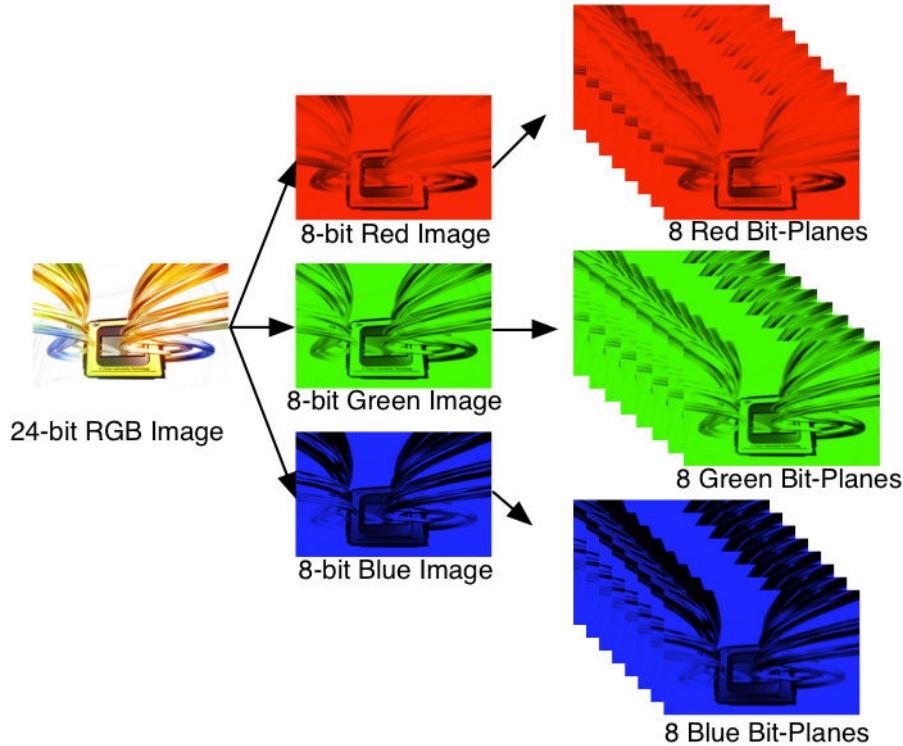

| Figure 2-6. Bit-Planes of a 24-Bit RGB Image.....                       | 44 |

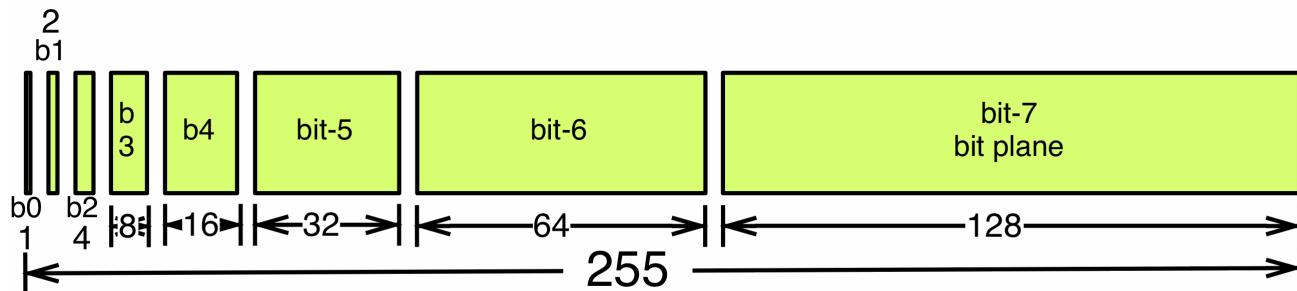

| Figure 2-7. Bit Partition in a Frame for an 8-Bit Monochrome Image..... | 44 |

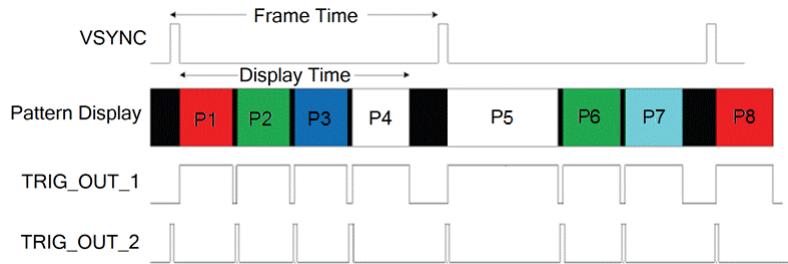

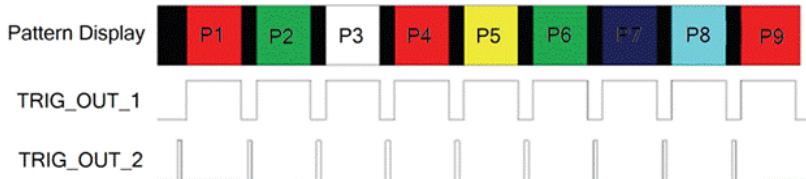

| Figure 2-8. Video Pattern Mode Timing Diagram Example.....              | 52 |

| Figure 2-9. Pre-Stored Pattern Mode Timing Diagram Example.....         | 52 |

| Figure 3-1. DLPC900 FAULT_STATUS Format.....                            | 64 |

## Trademarks

LightCrafter™ and E2E™ are trademarks of Texas Instruments.

DLP® are registered trademarks of Texas Instruments.

All trademarks are the property of their respective owners.

## Read This First

### About This Manual

This document specifies the command and control interface to the DLPC900 controller and defines all applicable commands, default settings, and control register bit definitions.

### Related Documents from Texas Instruments

- DLPC900 Data Sheet, [DLPS037](#)

- DLP500YX Data Sheet, [DLPS193](#)

- DLP6500FLQ Data Sheet, [DLPS040](#)

- DLP6500FYE Data Sheet, [DLPS053](#)

- DLP670S Data Sheet, [DLPS194](#)

- DLP9000 Data Sheet, [DLPS036](#)

- DLP® LightCrafter™ Single DLPC900 Controller Evaluation Module (EVM) User's Guide, [DLP0101](#)

- DLP® LightCrafter™ Dual DLPC900 Controller Evaluation Module (EVM) User's Guide, [DLP0102](#)

### If You Need Assistance

Visit the TI E2E™ support forums at [DLP Products and MEMS TI E2E Community](#).

## 1 Interface Protocol

This chapter describes the interface protocol between the DLPC900 and a host processor. The DLPC900 supports two host interface protocols: I<sup>2</sup>C and USB 1.1 slave interfaces.

### 1.1 I<sup>2</sup>C Interface

The DLPC900 controller uses the I<sup>2</sup>C protocol to exchange commands and data with a host processor. The I<sup>2</sup>C protocol is a two-wire serial data bus. One wire, SCL, serves as a serial clock, while the second wire, SDA, serves as serial data. Several different devices can be connected together in an I<sup>2</sup>C bus. Each device is software addressable by a unique address. Communication between devices occurs in a simple I<sup>2</sup>C "master-to-slave" relationship.

#### 1.1.1 I<sup>2</sup>C Transaction Structure

All I<sup>2</sup>C transactions are composed of a number of bytes, combined in the following order:

**START Condition, 7-Bit Slave Address Byte + 1 R/W Bit, Sub-Address Byte, N-Data Bytes, STOP Condition**

Where N in *N-Data Bytes* varies based on the sub-address.

##### 1.1.1.1 I<sup>2</sup>C START Condition

All I<sup>2</sup>C transactions begin with a START condition. A START condition is defined by a high-to-low transition on the SDA line, followed by a high-to-low transition on the SCL line.

##### 1.1.1.2 I<sup>2</sup>C STOP Condition

All I<sup>2</sup>C transactions end with a STOP condition. A STOP condition is defined by a low-to-high transition on the SDA line, followed by a low-to-high transition on the SCL line.

##### 1.1.1.3 DLPC900 Slave Address

The DLPC900 offers a programmable slave address. Refer to the App Defaults Settings found in the DLPC900 LightCrafter GUI Firmware tab to set a different slave address. The default I<sup>2</sup>C settings are shown in [Table 1-1](#). The Write Slave Address must be an even 7-bit address, and the Read Slave Address must be the Write Slave Address plus 1.

**Table 1-1. I<sup>2</sup>C Slave Settings**

| ADDRESSING MODE | DEFAULT WRITE ADDRESS | DEFAULT READ ADDRESS | MAXIMUM CLOCK RATE (kHz) |

|-----------------|-----------------------|----------------------|--------------------------|

| 7-bit           | 0x34                  | 0x35                 | 400                      |

##### 1.1.1.4 DLPC900 Sub-Address and Data Bytes

The DLPC900 I<sup>2</sup>C sub-address corresponds to the byte address of the DLPC900 commands described in [Appendix A](#). Most I<sup>2</sup>C sub-addresses have a Read and Write command pair where the Write command equals the Read command with the most significant bit set. For example, [Table 1-2](#) and [Table 1-4](#) show the Input Data Channel Swap sub-address command pair is (0x04,0x84), where the Write sub-address command 0x84 is the Read sub-address command 0x04 with the most significant bit set. Each sub-address command requires a certain number of data bytes, and each command is followed by variable length data where the **least significant byte is first for each parameter**.

---

#### Note

The DLPC900 I<sup>2</sup>C command data is formatted with the least significant byte first for each parameter in the data. This maintains the same format with the USB protocol.

The DLPC900 internal command buffer has a maximum of 512 bytes and it is shared between the Read and Write commands; therefore, whenever a Read command is executed it must be followed by I<sup>2</sup>C operation with the Read Slave Address to retrieve the data otherwise the data is overwritten by the next command executed. See [Section 1.1.2](#) for a Read command example.

### 1.1.2 Example I<sup>2</sup>C Read Command Sequence

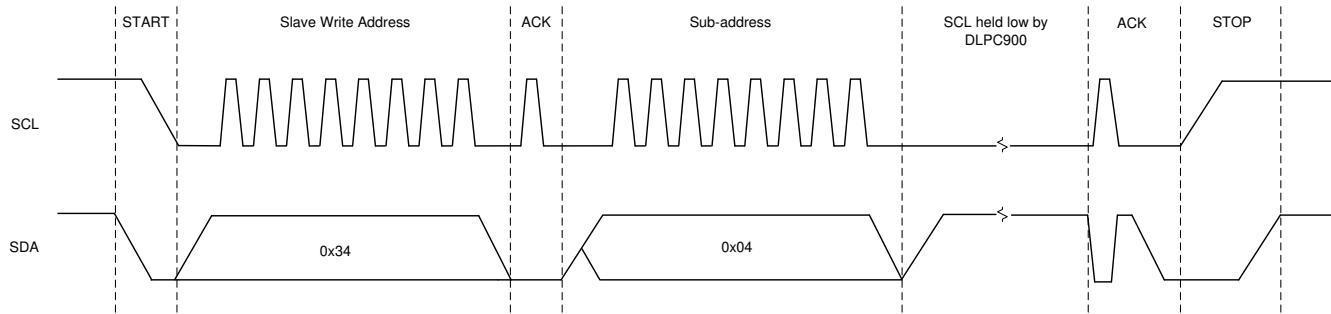

To execute a command to read the Input Data Channel Swap setting, the host builds a sequence of bytes containing the slave address, the sub-address, and the data (if any), and performs the following steps:

1. The host performs the required START condition followed by sending the sequence of bytes.

2. The DLPC900 holds the SCL line low to indicate it is busy.

3. The host waits for the DLPC900 to release the SCL line.

4. Once the SCL line goes high, the host performs a STOP condition.

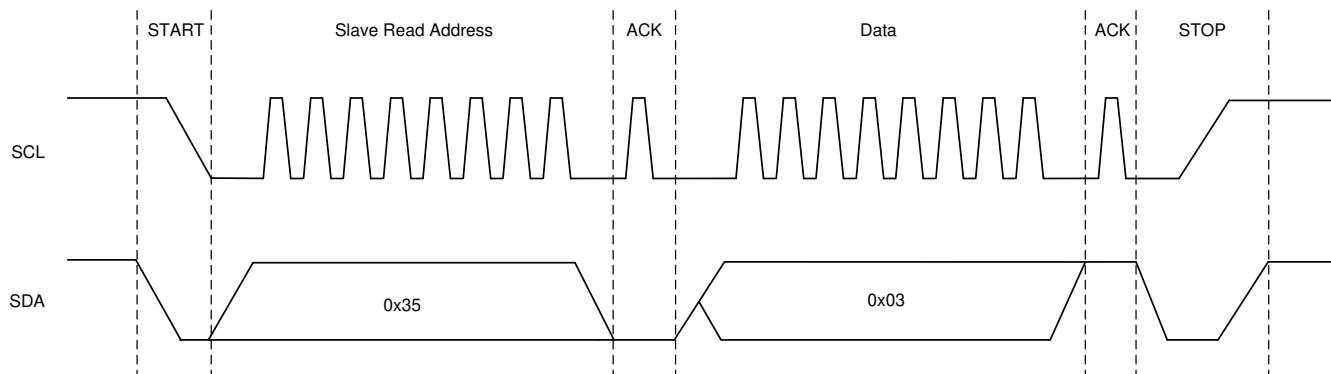

5. The host then performs a START condition followed by sending the Read Slave Address (0x35), and then reads the required number of bytes and concludes with a STOP condition.

An example of the above read command sequence is shown in [Table 1-2](#), and a waveform diagram of a host executing this read sequence is shown in [Figure 1-1](#) and [Figure 1-2](#).

**Table 1-2. Read Command Sequence Example (1)**

| SLAVE ADDRESS | SUB-ADDRESS | DATA |

|---------------|-------------|------|

| 34            | 04          |      |

| 35            |             | 03   |

(1) All values shown are in HEX notation.

**Figure 1-1. I<sup>2</sup>C Read Command Waveform Diagram**

**Figure 1-2. I<sup>2</sup>C Read Data Waveform Diagram**

#### 1.1.2.1 Read Command Example with Parameters

Some Read sub-address commands require a parameter(s) to be included in the sequence. For example, the command in [Section 2.3.8.1](#) has multiple GPIO to choose from. Therefore, the GPIO selection parameter must be included in the Read byte sequence in order to retrieve the configuration for the GPIO chosen. [Table 1-3](#) shows the two I<sup>2</sup>C operations, where the first row contains the parameter data 06 which indicates GPIO 6. The second row is the returned data of 06 03, where 06 was the chosen GPIO 6 and has a configuration of 03.

**Table 1-3. Read Command with Parameter Sequence Example (1)**

| SLAVE ADDRESS | SUB-ADDRESS | DATA  |

|---------------|-------------|-------|

| 34            | 44          | 06    |

| 35            |             | 06 03 |

(1) All values shown are in HEX notation.

### 1.1.3 Example I<sup>2</sup>C Write Command Sequence

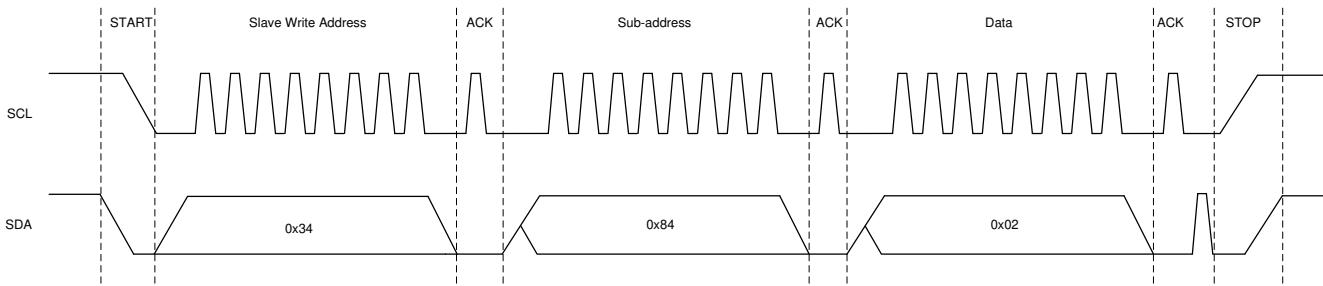

To execute a command to set the Input Data Channel Swap value, the host builds a sequence of bytes containing the slave address, the sub-address, and the data, and performs the following steps.

1. The host performs the required START condition followed by sending the sequence of bytes.

2. The host performs a STOP condition.

An example of the above write command sequence is shown in [Table 1-4](#), and a waveform diagram of a host executing this write sequence is shown in [Figure 1-3](#).

**Table 1-4. Write Command Sequence Example (1)**

| SLAVE ADDRESS | SUB-ADDRESS | DATA |

|---------------|-------------|------|

| 34            | 84          | 02   |

(1) All values shown are in HEX notation.

**Figure 1-3. I<sup>2</sup>C Write Command Waveform Diagram**

## 1.2 USB Interface

The DLPC900 controller also supports the USB 1.1 human interface device (HID) to exchange commands and data with a host processor. The USB commands are variable length data packets that are sent with the **least significant byte first for each parameter**.

### 1.2.1 USB Transaction Sequence

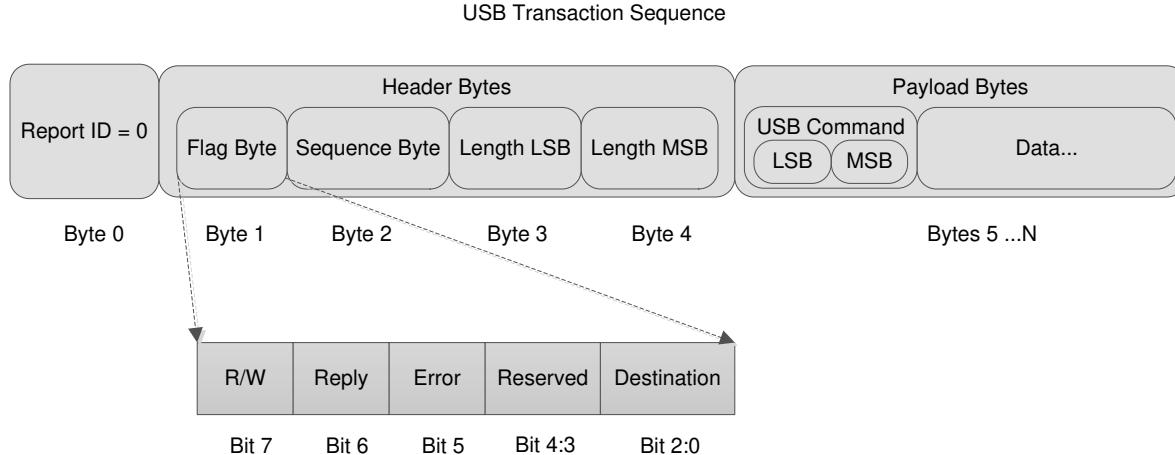

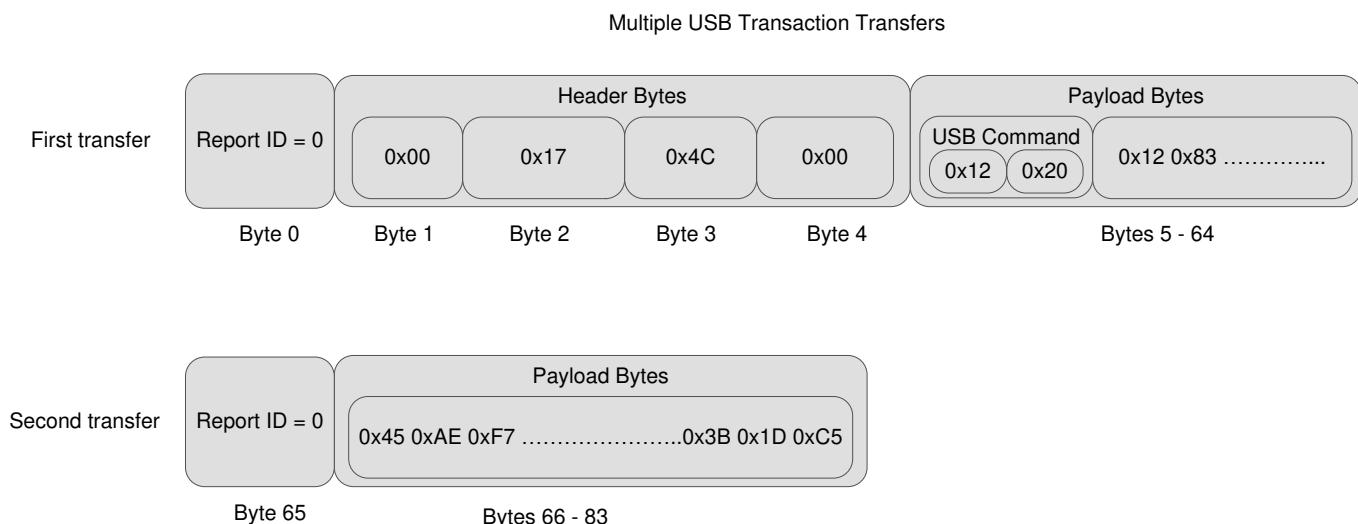

The USB 1.1 HID protocol has the structure shown in [Figure 1-4](#). The host must build a stream of bytes that consist of the Report ID, Header, and the payload. The following is a description of these three parts.

**Report ID:** The Report ID is always set to 0 and always the leading byte of all transfers.

**Header:** The header consists of four bytes.

1) Flag Byte: Shown in [Figure 1-4](#) and described in the Read and Write examples in [Section 1.2.2](#) and [Section 1.2.3](#).

2) Sequence Byte: The sequence byte can be a rolling counter. It is used primarily when the host wants a response from the DLPC900. The DLPC900 responds with the same sequence byte that the host sent. The host can then match the sequence byte from the command it sent with the sequence byte from the DLPC900 response.

3) Length: Two bytes in length, this denotes the number of data bytes in the Payload only.

**Payload Bytes:** The payload bytes consist of the USB command followed by the data that is associated with the command.

**Figure 1-4. USB HID Protocol**

During a Write operation, the host transmits the entire transaction sequence to the DLPC900, and the DLPC900 performs the operation associated with the Write command. During a Read operation, the host transmits the entire transaction sequence to the DLPC900, and the DLPC900 performs the operation associated with the Read command. Therefore, both Write and Read transactions are considered *writes* to the DLPC900 where the host performs an API level *Writefile* to the HID driver. The difference is when the DLPC900 executes a Read operation, where the DLPC900 places the response into its internal buffer and waits for the host to perform an API level *Readfile* to the HID driver and only then does the DLPC900 transmit the response data back to the host.

The DLPC900 internal command buffer has a maximum of 512 bytes and it is shared between both the Write and Read operations; therefore, whenever the host performs a Read operation, it must be followed by the *Readfile* to the HID driver to get the response otherwise the response data is overwritten by the next Write or Read operation.

The HID protocol is limited to 64 byte transfers in both directions. Therefore, commands that are larger than 64 bytes require multiple transfers. Whenever such a command is used, only the very first transfer requires the Header and the USB Command. The Report ID is always the leading byte of all transfers. [Figure 1-5](#) shows an example of a Write command that contains 76 bytes and requires two transfers. Notice that the first transfer contains 65 bytes, which is correct. The host hardware level HID driver extracts the Report ID before transmitting or receiving the data over the USB bus.

**Figure 1-5. USB Multi-Transfer Transaction**

### 1.2.2 USB Read Transaction Sequence Example

To perform a Read operation on the DLPC900, the host must assemble a sequence of bytes that corresponds to the command being used. The following [Table 1-5](#) shows an example on how to read the curtain color intensity of each color.

**Table 1-5. Read Operation Example (1)**

| REPORT ID<br>BYTE | FLAG<br>BYTE | SEQUENCE<br>BYTE | LENGTH (2) | USB COMMAND (2) |

|-------------------|--------------|------------------|------------|-----------------|

| 00                | C0           | 11               | 02 00      | 00 11           |

(1) All values shown are in HEX notation.

(2) LSB precedes the MSB for each parameter.

1. Report ID byte: Always set to 0.

2. Flag byte. Where:

- Bits 2:0 are set to 0x0 for regular DLPC900 operation.

- Bit 6 is set to 0x1 to indicate the host wants a reply from the device.

- Bit 7 is set to 0x1 to indicate a read transaction.

3. Sequence byte: The sequence byte can be a rolling counter. It is used primarily when the host wants a response from the DLPC900. The DLPC900 responds with the same sequence byte that the host sent. The host can then match the sequence byte from the command it sent with the sequence byte from the DLPC900 response.

4. Length: Two bytes in length, this denotes the number of data bytes in the sequence and excludes the number of bytes in steps 1 through 4. It denotes the total number of bytes sent in steps 5 (command bytes).

5. USB Command: Two byte USB command.

6. Once the host transmits the data over the USB interface, the DLPC900 responds to the Read operation by placing the response data in its internal buffer. The host must then perform a HID driver read operation. [Table 1-6](#) shows the response data sent back from the DLPC900.

- a. Report ID: Always set to 0.

- b. Flag byte: The same as was sent plus error bit. The host may check the error flag (bit 5) as follows.

- i. 0 = No errors.

- ii. 1 = Command not found or command failed.

- c. Sequence byte: The same as was sent. The host may match the sent sequence byte with the response sequence byte.

- d. Length: Number of data bytes. The host must assemble the data according to the definition of the command.

**Table 1-6. Read Response Example (1)**

| REPORT ID<br>BYTE | FLAG<br>BYTE | SEQUENCE<br>BYTE | LENGTH (2) | DATA (2)          |

|-------------------|--------------|------------------|------------|-------------------|

| 00                | C0           | 11               | 06 00      | FF 01 FF 01 FF 01 |

(1) All values shown are in HEX notation.

(2) LSB precedes the MSB for each parameter.

### 1.2.3 USB Write Transaction Sequence Example

To perform a Write operation on the DLPC900, the host must assemble a sequence of bytes that corresponds to the command being used. The following [Table 1-7](#) shows an example on how to set the curtain color intensity of each color to 511.

**Table 1-7. Write Operation Example <sup>(1)</sup>**

| REPORT ID<br>BYTE | FLAG<br>BYTE | SEQUENCE<br>BYTE | LENGTH <sup>(2)</sup> | USB COMMAND <sup>(2)</sup> | DATA <sup>(2)</sup> |

|-------------------|--------------|------------------|-----------------------|----------------------------|---------------------|

| 00                | 00           | 12               | 08 00                 | 00 11                      | FF 01 FF 01 FF 01   |

(1) All values shown are in HEX notation.

(2) LSB precedes the MSB for each parameter.

1. Report ID byte: Always set to 0.

2. Flag byte. Where:

- Bits 2:0 are set to 0x0 for regular DLPC900 operation.

- Bit 6 is set to 0x0 to indicate the host does not want a reply from the device. This bit is set to 0x1 only if a reply is needed, which is usually not required.

- Bit 7 is set to 0x0 to indicate a write transaction.

3. Sequence byte: The sequence byte can be a rolling counter. It is used primarily when the host wants a response from the DLPC900. Normally during a write operation, the DLPC900 does not respond; however, the host can continue to increment the sequence byte for the next command operation.

4. Length: Two bytes in length, this denotes the number of data bytes in the sequence and excludes the number of bytes in steps 1 through 4. It denotes the total number of bytes sent in steps 5 (command bytes) and 6 (data bytes).

5. USB Command: Two byte USB command.

6. Data: The data appropriate to the command.

### 1.3 INIT\_DONE Signal

The DLPC900 does not have a dedicated INIT\_DONE signal output to indicate that it has completed its power-up initialization and is ready to accept commands. The user may configure one of the nine GPIOs available as an INIT\_DONE signal output simply by adding the GPIO configuration into the default batch file that is executed at power-up. A 10-kΩ pull-down resistor must be connected to the GPIO that is used.

The following is an example of adding the configuration for GPIO\_08 to a batch file, where GPIO\_08 is configured as an output and the signal is set high. When this command is added to the top of the batch file, the GPIO output goes high in approximately 800 ms from the time POSENSE goes high:

GPIO\_CONFIG: 0x8 0x3

## 2 DLPC900 Control Commands

This chapter lists the DLPC900 control commands.

The following sections list the supported control commands of the DLPC900. In the *Type* column, 'wr' type is a writeable field through I<sup>2</sup>C or USB write transactions. Data can also be read through I<sup>2</sup>C or USB read transactions for 'wr' type bits. Type *r* is read-only. Write transactions to read-only fields are ignored.

The Reset column in all of the following command tables is the default value after power up. These values may be overwritten after power up.

---

### Note

**Reserved bits and registers.** When writing to valid command bit fields, set all bits marked as unused or reserved to 0, unless specified otherwise.

---

### Note

**Momentary Image Corruption During Command Writes.** Certain commands may cause brief visual artifacts in the display image under some circumstances. Command data values may always be read without impacting displayed image. To avoid momentary image corruption due to a command, disable the LEDs prior to the command write, then re-enable the LEDs after all commands have been issued.

---

### Note

**Writing or reading from undocumented registers is NOT recommended.**

---

## 2.1 DLPC900 Status Commands

The DLPC900 has the following set of status commands:

Hardware Status

System Status

Main Status

Retrieve Firmware Version

Read Error Codes

### 2.1.1 Hardware Status

The hardware status command provides status information on the sequencer, digital micromirror device (DMD) controller, and initialization of DLPC900.

**Table 2-1. Hardware Status Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x20             | 0x1A0A |

**Table 2-2. Hardware Status Command Definition**

| BYTE | BITS             | DESCRIPTION                                                                                                                                           | RESET                                                  | TYPE |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------|

| 0    | 0                | Internal Initialization<br>0 = Error<br>1 = Successful                                                                                                | d1                                                     | r    |

|      | 1                | 0 = No Error<br>1 = Incompatible Controller or DMD<br><br><b>Note</b><br>This error also occurs if the wrong firmware for the system has been loaded. | d0                                                     | r    |

|      | 2                | DMD Reset Controller Error<br>0 = No error has occurred<br>1 = Multiple overlapping bias or reset operations are accessing the same DMD block.        | d0                                                     | r    |

|      | 3                | Forced Swap Error<br>0 = No error has occurred.<br>1 = Forced Swap Error occurred.                                                                    | d0                                                     | r    |

|      | 4 <sup>(1)</sup> | 0 = No Slave Controller Present<br>1 = Slave Controller Present and Ready                                                                             | d0 (single controller DMD)<br>d1 (dual controller DMD) | r    |

|      | 5                | Reserved                                                                                                                                              | d0                                                     | r    |

|      | 6                | Sequencer Abort Status Flag<br>0 = No error has occurred<br>1 = Sequencer has detected an error condition that caused an abort                        | d0                                                     | r    |

|      | 7                | Sequencer Error<br>0 = No error has occurred.<br>1 = Sequencer detected an error.                                                                     | d0                                                     | r    |

(1) When the DLPC900 is combined with a single controller DMD, this bit is 0. When two DLPC900 controllers are combined with a dual controller DMD, this bit must be 1 for proper operation. If the bit is 0 and the DLPC900 is combined with a dual controller DMD, this indicates a malfunction in one or both controllers.

#### Note

Any error condition indicates a fault condition and it must be corrected.

## 2.1.2 System Status

The system status command provides the DLPC900 status on internal memory tests.

**Table 2-3. System Status Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x21             | 0x1A0B |

**Table 2-4. System Status Command Definition**

| BYTE | BITS | DESCRIPTION                                                                                | RESET | TYPE |

|------|------|--------------------------------------------------------------------------------------------|-------|------|

| 0    | 0    | Internal Memory Test<br>0 = Internal Memory Test failed<br>1 = Internal Memory Test passed | d1    | r    |

|      | 1:7  | Reserved                                                                                   |       |      |

## 2.1.3 Main Status

The main status command provides the status of DMD park and DLPC900 sequencer, frame buffer, and gamma correction.

**Table 2-5. Main Status Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x22             | 0x1A0C |

**Table 2-6. Main Status Command Definition**

| BYTE | BITS | DESCRIPTION                                                                                                      | RESET | TYPE |

|------|------|------------------------------------------------------------------------------------------------------------------|-------|------|

| 0    | 0    | DMD Park Status<br>0 = DMD micromirrors are not parked<br>1 = DMD micromirrors are parked                        | d1    | r    |

|      |      | Sequencer Run Flag<br>0 = Sequencer is stopped<br>1 = Sequencer is running normally                              |       |      |

|      |      | Video Frozen Flag<br>0 = Video is running (Normal frame change)<br>1 = Video is frozen (Displaying single frame) |       |      |

|      | 3    | External video source locked<br>0 = External source not locked<br>1 = External source locked                     | d0    | r    |

|      |      | Port 1 syncs valid<br>0 = Port 1 syncs not valid<br>1 = Port 1 syncs valid                                       |       |      |

|      |      | Port 2 syncs valid<br>0 = Port 2 syncs not valid<br>1 = Port 2 syncs valid                                       |       |      |

|      | 7:6  | Reserved                                                                                                         | d0    | r    |

## 2.1.4 Retrieve Firmware Version

This command reads the version information of the DLPC900 firmware.

**Table 2-7. Retrieve Firmware Version Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x11             | 0x0205 |

**Table 2-8. Get Version Command Definition**

| BYTE  | BITS                   | DESCRIPTION                                                                                                                                                   | RESET                                               | TYPE |

|-------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|

| 3:0   | 15:0<br>23:16<br>31:24 | Application software revision:<br>Application software patch number<br>Application software minor revision<br>Application software major revision             | Matches firmware version read from stored firmware. | r    |

| 7:4   | 15:0<br>23:16<br>31:24 | API software revision:<br>API patch number<br>API minor revision<br>API major revision                                                                        | d0                                                  | r    |

| 11:8  | 15:0<br>23:16<br>31:24 | Software configuration revision:<br>Software configuration patch number<br>Software configuration minor revision<br>Software configuration major revision     | d0                                                  | r    |

| 15:12 | 15:0<br>23:16<br>31:24 | Sequencer configuration revision:<br>Sequencer configuration patch number<br>Sequencer configuration minor revision<br>Sequencer configuration major revision | d0                                                  | r    |

## 2.1.5 Reading Hardware Configuration and Firmware Tag Information

This command reads the hardware configuration of the system and also returns the 31 byte ASCII firmware tag information.

**Table 2-9. Reading Hardware Configuration and Firmware Tag Information Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x12             | 0x0206 |

**Table 2-10. Reading Hardware Configuration and Firmware Tag Command Response**

| BYTE | VALUE       | DESCRIPTION                            | RESET              | TYPE |

|------|-------------|----------------------------------------|--------------------|------|

| 0    | 0x00        | Unknown                                | Read from firmware | r    |

|      | 0x01        | DLP6500 hardware                       |                    |      |

|      | 0x02        | DLP9000 hardware                       |                    |      |

|      | 0x03        | DLP670S hardware <sup>(1)</sup>        |                    |      |

|      | 0x04        | DLP500YX hardware <sup>(1)</sup>       |                    |      |

|      | 0x05 - 0xFF | Reserved                               |                    |      |

| 32:1 |             | 31 byte ASCII firmware tag information |                    | r    |

(1) Firmware version 6.x introduces support for two new DMD devices. These are shown in [Table 2-10](#)

## 2.1.6 Read Error Code

This command retrieves the error code number from the DLPC900 of the last executed command.

**Table 2-11. Read Error Code Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x32             | 0x0100 |

**Table 2-12. Read Error Code Command Definition**

| BYTE | VALUE  | DESCRIPTION                                         | RESET | TYPE |

|------|--------|-----------------------------------------------------|-------|------|

| 0    | 0      | No error                                            |       |      |

|      | 1      | Batch file checksum error                           |       |      |

|      | 2      | Device failure                                      |       |      |

|      | 3      | Invalid command number                              |       |      |

|      | 4      | Incompatible controller / DMD                       |       |      |

|      | 5      | Command not allowed in current mode                 |       |      |

|      | 6      | Invalid command parameter                           |       |      |

|      | 7      | Item referred by the parameter is not present       |       |      |

|      | 8      | Out of resource (RAM / Flash)                       |       |      |

|      | 9      | Invalid BMP compression type                        |       |      |

|      | 10     | Pattern bit number out of range                     | 0     | r    |

|      | 11     | Pattern BMP not present in flash                    |       |      |

|      | 12     | Pattern dark time is out of range                   |       |      |

|      | 13     | Signal delay parameter is out of range              |       |      |

|      | 14     | Pattern exposure time is out of range               |       |      |

|      | 15     | Pattern number is out of range                      |       |      |

|      | 16     | Invalid pattern definition (errors other than 9-15) |       |      |

|      | 17     | Pattern image memory address is out of range        |       |      |

|      | 18-254 | Not defined                                         |       |      |

|      | 255    | Internal Error                                      |       |      |

## 2.1.7 Read Error Description

This command retrieves the error descriptive string from the DLPC900 of the last executed command. The string is composed of character bytes ending with a null termination character.

**Table 2-13. Read Error Description Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x33             | 0x0101 |

**Table 2-14. Read Error Description Command Definition**

| BYTE  | BITS | DESCRIPTION                                                                              | RESET | TYPE |

|-------|------|------------------------------------------------------------------------------------------|-------|------|

| 127:0 | All  | Error description for the last executed command. 0 terminated string of character bytes. | 0     | r    |

## 2.2 DLPC900 Firmware Programming Commands

The Programming commands manage downloading a new firmware image into flash memory. This can be done over I<sup>2</sup>C or USB interfaces. The commands in the DLPC900 Programming Commands section are only valid in **program mode** except for Enter Program Mode (I<sup>2</sup>C: 0x30 or USB 0x3001), which exits normal mode and enters program mode. Once in program mode, the user must issue the proper Exit Program Mode (I<sup>2</sup>C: 0x30 or USB 0x0030) command to return to normal mode. **While in program mode, commands outside of this section do not work.**

Flash memory has the address layout shown in [Table 2-15](#). The design is for up to a single 128 megabyte flash device for storing the firmware.

---

### Note

Depending on memory needs the design can also be used for a single 16, 32, or 64 megabyte flash memory.

---

The firmware consists of the bootloader, the main application, any sequences/images stored in flash (optional), and 1 Megabyte of reserved space. This area (0x9000000 - 0x9FFFFFF) must not be overwritten.

The bootloader is located at the *beginning* of flash memory block 0. The size of the bootloader is 128 kilobytes, beginning at address 0xF9000000. The bootloader is necessary for operation. If the bootloader becomes corrupted in some way it may render the device inoperable requiring JTAG to reprogram. The bootloader is followed by the main application and 1 megabyte of reserved space. Pattern/sequence data starts at 0x9240000. Patterns may not span memory block boundaries.

---

### Note

**Writing across memory block boundaries is not permitted.** Patterns must not span across block boundaries between blocks because of the extended addressing schema. If a pattern does not fit in a given block, the entire, 24-bit image (or composite image) must be moved into next block.

---

**Table 2-15. Flash Device Layout**

| Memory Block | Address Space (Start and End)                                                                                                                                                                       | Single Flash Memory Addressed | Megabytes | Contents                                                                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | 0xF9000000 - 0xF9FFFFFF<br><b>Reserved:</b><br><i>Bootloader</i><br>0xF9000000 - 0xF901FFFF<br><i>Application binary</i><br>0xF9020000 - 0xF913FFFF<br><i>1 megabyte</i><br>0xF9140000 - 0xF923FFFF | 0x00000000 - 0x00FFFFFF       | 0 - 15    | <ul style="list-style-type: none"> <li>• <b>Bootloader</b></li> <li>• <b>Application binary</b></li> <li>• <b>1 megabyte reserved space</b></li> <li>• Sequences/patterns</li> </ul> |

| 1            | 0xFA000000 - 0xFAFFFFFF                                                                                                                                                                             | 0x01000000 - 0x01FFFFFF       | 16 - 31   | Patterns only                                                                                                                                                                        |

| 2            | 0xF8000000 - 0xF8EFFFFFF                                                                                                                                                                            | 0x02000000 - 0x02FFFFFF       | 32 - 47   | Patterns only                                                                                                                                                                        |

| 3            | 0x03000000 - 0x03FFFFFF                                                                                                                                                                             | 0x03000000 - 0x03FFFFFF       | 48 - 63   | Patterns only                                                                                                                                                                        |

| 4            | 0x04000000 - 0x04FFFFFF                                                                                                                                                                             | 0x04000000 - 0x04FFFFFF       | 64 - 79   | Patterns only                                                                                                                                                                        |

| 5            | 0x05000000 - 0x05FFFFFF                                                                                                                                                                             | 0x05000000 - 0x05FFFFFF       | 80 - 95   | Patterns only                                                                                                                                                                        |

| 6            | 0x06000000 - 0x06FFFFFF                                                                                                                                                                             | 0x06000000 - 0x06FFFFFF       | 96 - 111  | Patterns only                                                                                                                                                                        |

| 7            | 0x07000000 - 0x07FFFFFF                                                                                                                                                                             | 0x07000000 - 0x07FFFFFF       | 112 - 127 | Patterns only                                                                                                                                                                        |

### 2.2.1 Read Status

This command indicates if the flash is ready to be programmed and also if a flash operation is in progress.

**Table 2-16. Read Status Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x23             | 0x0000 |

Table 2-17. Read Status Command Definition

| BYTE | BITS | DESCRIPTION                                                                                                                    | RESET                                                  | TYPE |

|------|------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------|

| 0    | 0    | Master ready<br>0 = Master not ready<br>1 = Master ready                                                                       | d1                                                     | r    |

|      | 1    | Slave ready (Valid only on Dual DLPC900 board)<br>0 = Slave not ready<br>1 = Slave ready                                       | d0 (single controller DMD)<br>d1 (dual controller DMD) |      |

|      | 2    | Slave controller flash busy (Valid only on Dual DLPC900 board)<br>0 = Slave not busy<br>1 = Slave busy                         | d0                                                     |      |

|      | 3    | Master controller flash busy<br>0 = Master not busy<br>1 = Master busy                                                         | d0                                                     |      |

|      | 4    | Reserved                                                                                                                       | d0                                                     |      |

|      | 5    | Slave controller present (Valid only on Dual DLPC900 board)<br>0 = Slave not present<br>1 = Slave present                      | d0 (single controller DMD)<br>d1 (dual controller DMD) |      |

|      | 6    | Slave controller program mode (Valid only on Dual DLPC900 board)<br>0 = Slave not in program mode<br>1 = Slave in program mode | d0 (single controller DMD)<br>d1 (dual controller DMD) |      |

|      | 7    | Master controller program mode<br>0 = Master not in program mode<br>1 = Master in program mode                                 | d1                                                     |      |

| 1    | 3:0  | Major Version                                                                                                                  | x                                                      |      |

| 1    | 7:4  | Minor version                                                                                                                  | x                                                      |      |

| 2    | 7:0  | Patch version                                                                                                                  | x                                                      |      |

| 3    | 7:0  | Controller ID                                                                                                                  | x52                                                    |      |

| 4    | 7:0  | Bootloader ID<br>65h = Single DLPC900<br>90h = Dual DLPC900                                                                    | x65 (Single DLPC900)<br>x90 (Dual DLPC900)             |      |

| 5    | 7:0  | Bytes 1 - 15 are from Master or Slave                                                                                          | d1                                                     |      |

|      |      | 0 = Bytes 1 - 15 are from Slave                                                                                                |                                                        |      |

|      |      | 1 = Bytes 1 - 15 are from Master                                                                                               |                                                        |      |

| 6    | 7:0  | Data (LSB)                                                                                                                     | d0                                                     |      |

| 7    | 7:0  | Data                                                                                                                           | d0                                                     |      |

| 8    | 7:0  | Data                                                                                                                           | d0                                                     |      |

| 9    | 7:0  | Data (MSB)                                                                                                                     | d0                                                     |      |

| 10   | 7:0  | Reserved                                                                                                                       | x3                                                     |      |

| 11   | 7:0  | Reserved                                                                                                                       | d0                                                     |      |

| 12   | 7:0  | Data (LSB)                                                                                                                     | d0                                                     |      |

| 13   | 7:0  | Data                                                                                                                           | d0                                                     |      |

| 14   | 7:0  | Data                                                                                                                           | d0                                                     |      |

| 15   | 7:0  | Data (MSB)                                                                                                                     | d0                                                     |      |

## 2.2.2 Enter Program Mode

This command tells the controller to enter its programming mode and jump to the boot loader. If the boot loader receives this command, then the command has no effect.

**Table 2-18. Enter Program Mode Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Write            |        |

| 0x30             | 0x3001 |

**Table 2-19. Enter Program Mode Command Definition**

| BYTE | BITS | DESCRIPTION                                                  | RESET | TYPE |

|------|------|--------------------------------------------------------------|-------|------|

| 0    | 1:0  | Program Mode<br>1 = Enter Program Mode – Jump to boot loader | d0    | w    |

|      | 7:2  | Reserved                                                     |       |      |

## 2.2.3 Exit Program Mode

This command tells the controller to exit its programming mode. If the application receives the exit command, the command has no effect.

**Table 2-20. Exit Program Mode Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Write            |        |

| 0x30             | 0x0030 |

**Table 2-21. Exit Program Mode Command Definition**

| BYTE | BITS | DESCRIPTION                                                                  | RESET | TYPE |

|------|------|------------------------------------------------------------------------------|-------|------|

| 0    | 1:0  | Program Mode<br>2 = Exit Program Mode – Reset controller and run application | d0    | w    |

|      | 7:2  | Reserved                                                                     |       |      |

## 2.2.4 Read Control

This command reads the Flash Manufacturer and Device IDs, as well as the Checksum, after the Calculate Checksum command is executed.

**Table 2-22. Read Control Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x15             | 0x0015 |

**Table 2-23. Query Flash IDs Command Definition**

| BYTE | BITS | DESCRIPTION                                                                                                                                | RESET | TYPE |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 0    | 3:0  | ID<br>0 = Request Checksum<br>xB = Request Number of flash present<br>xC = Requests Flash Manufacturer ID<br>xD = Requests Flash Device ID | d0    | r    |

|      | 7:4  | Reserved                                                                                                                                   |       |      |

## 2.2.5 Start Address

The Start Address command serves three purposes.

- 1) Specifies the start address of the flash download write operation. It is the responsibility of the user to ensure that the start address is on a sector boundary in the current flash device.

- 2) Specifies the start address where checksum operation begins.

- 3) Specifies the sector address to be erased. The address must be the start of a sector.

The Flash Data Size command always follows 1 and 2 above, which defines how many bytes to be downloaded or how many bytes to include for the checksum operation.

**The user must avoid erasing the first 128 kilobytes of the boot flash as this contains the boot image. The user must also avoid erasing other sectors that contain firmware that are required for proper controller operation.**

**Table 2-24. Start Address Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Read             |        |

| 0x32             | 0x0032 |

**Table 2-25. Start Address Command Definition**

| BYTE | BITS | DESCRIPTION                                                                                                                                          | RESET | TYPE |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 3:0  | 31:0 | 4 byte flash address. Byte 0 is LSB, byte 4 is MSB.<br>Valid Range:<br>0x03000000 - 0x07FFFFFF<br>0xF8000000 - 0xFAEFFFFF<br>0xF9000000 - 0xF9FFFFFF | x0    | w    |

## 2.2.6 Erase Sector

This is a system write command to erase a sector of flash memory. **Do not execute this command until valid data has been written to the Flash Start Address. Users are responsible for ensuring that a valid address has been written.** The Busy bit is set in the Boot Loader status byte while the sector erase is in progress. No data is associated with this command.

**Table 2-26. Erase Sector Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Write            |        |

| 0x28             | 0x0028 |

---

**Note**

TI cautions against erasing the boot sector of the device as this contains key initialization parameters and the flash programming functionality. Only the sector that contains the start address is erased, not all sectors from the start address to the end of the device. Users must either pre-erase all sectors to be programmed, or erase and program each sector individually.

## 2.2.7 Download Flash Data Size

System write command to specify the size of the following flash download. The data size is sent to tell the Boot Loader how many bytes to expect to program into the flash device. It is also used for specifying the checksum range when requesting that operation.

**Table 2-27. Download Flash Data Size Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Write            |        |

| 0x33             | 0x0033 |

**Table 2-28. Download Data Size Command Definition**

| BYTE | BITS | DESCRIPTION                                                                 | RESET | TYPE |

|------|------|-----------------------------------------------------------------------------|-------|------|

| 3:0  | 31:0 | 4 Byte flash size. Valid Range 4 - 0x2FFFFFF. Byte 0 is LSB, byte 3 is MSB. | x0    | w    |

## 2.2.8 Download Data

This command contains the flash data to be programmed. The maximum data size which can be sent in each command is 512 bytes, which corresponds to a data length of 514. The number of bytes downloaded by consecutive download data commands must match the predefined Flash Data Size for the operation to be successful.

**Table 2-29. Download Data Command**

| I <sup>2</sup> C | USB    |

|------------------|--------|

| Write            |        |

| 0x25             | 0x0025 |

**Table 2-30. Download Data Command Definition**

| BYTE  | BITS   | DESCRIPTION          | RESET | TYPE |

|-------|--------|----------------------|-------|------|

| 0     | 7:0    | Length LSB           |       |      |

| 1     | 7:0    | Length MSB           |       |      |

| 513:2 | 4095:0 | Up to 512 Data Bytes | x0    | w    |

| 514   | 7:0    | Checksum             |       |      |

## 2.2.9 Calculate Checksum

This command calculates the checksum. Executing this command causes the Boot Loader to read the data in the flash memory and calculate a 4-byte 8-bit checksum. The Busy bit is set in the Boot Loader status byte while the checksum computation is in progress. After completion, the 4-byte checksum can be read back through the Read Control command. The data range to be summed is specified by writing appropriate data with the Flash Start Address and Flash Data Size commands. There is no data associated with this command.

**Table 2-31. Calculate Checksum Command**

| I <sup>2</sup> C |  | USB    |

|------------------|--|--------|

| Write            |  |        |

| 0x26             |  | 0x0026 |

## 2.2.10 Controller Enable/Disable Command

This command stops the given controller from executing any further commands until enabled by the same command. This command is intended to be used when two DLPC900 controllers are combined with a dual controller DMD, where one controller is the I<sup>2</sup>C master and the other is the I<sup>2</sup>C slave.

**Table 2-32. Controller Enable/Disable Command**

| I <sup>2</sup> C |  | USB    |

|------------------|--|--------|

| Write            |  |        |

| 0x31             |  | 0x0031 |

**Table 2-33. Controller Enable/Disable Command Definition**

| BYTE | BITS | DESCRIPTION                                                   | RESET | TYPE |

|------|------|---------------------------------------------------------------|-------|------|

| 0    | 0    | 1 – Disable Master Controller<br>0 – Enable Master Controller | x0    | w    |

|      | 1    | 1 – Disable Slave Controller<br>0 – Enable Slave Controller   |       |      |

|      | 7:2  | Reserved                                                      | x0    | w    |

## 2.3 Chipset Control Commands

The DLPC900 I<sup>2</sup>C and USB control commands are accepted in any order, except when special sequencing is required (for example, setting up the flash). Each control command is validated for sub-address and parameter errors as it is received. Commands failing validation are ignored. On power up, it is necessary to wait for DLPC900 to complete its initialization before sending any I<sup>2</sup>C or USB commands.

### 2.3.1 Chipset Configuration Commands

The Chipset Configuration commands enable control of the power mode, DMD park state and image curtain display.

#### 2.3.1.1 Power Mode

The Power Control places the DLPC900 in a standby state and powers down the DMD interface. Enter Standby mode prior to any planned system power shutdowns to safely park the micro-mirrors. Enable Standby mode only after all data for the last frame to be displayed has been transferred to the DLPC900. Standby mode must be disabled prior to sending any new data. After executing this command, the host may poll the system status using I<sup>2</sup>C commands 0x20, x21, and 0x22 or USB commands 0x1A0A, 0x1A0B, and 0x1A0C to attain status.

**Table 2-34. Power Mode Command**

| I <sup>2</sup> C |       | USB    |

|------------------|-------|--------|

| Read             | Write | 0x0200 |

| 0x07             | 0x87  |        |

**Table 2-35. Power Mode Command Definition**

| BYTE | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RESET | TYPE |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 0    | 1:0  | Power Mode<br>0 = Return to Normal mode from Standby Mode of operation. In Normal mode, the selected external source is displayed.<br>1 = Enter Standby mode to place the DMD in a standby state. Standby disables the front end input data interfaces and park and power down parts of the DMD. <p><b>Note</b><br/>Standby mode requires a wait period of two minutes to run 50/50 and park the DMD. Three additional seconds are needed to complete all operations before issuing a Return to Normal command.</p> <p><b>Note</b><br/>Once Standby has been issued the only command accepted by the DLPC900 controller board is Return to Normal (0). Any other command can result in unexpected behavior. Particularly a Park/Unpark is not accepted until Normal mode is resumed.</p> | d0    | wr   |

|      | 2    | 2 = Perform a software reset<br><br>If a software reset is performed in a batch file, no further commands in the batch file are processed resulting in an "idx" (batch file line index number) error. A USB or I <sup>2</sup> C connection must be established before starting a new batch file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | w    |

|      | 3    | <b>Note</b><br>If a hardware reset is performed while the system is in standby mode the system needs to poll the status again to recognize that normal operation has resumed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | r    |

|      | 7:2  | 3 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d0    | r    |

|      |      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |      |

### 2.3.1.2 DMD Park/Unpark

The DMD Park command parks the mirrors of the DMD. The DMD Unpark command unparks the mirrors of the DMD. Because the Standby command execution includes the parking of the DMD, the Park command is unneeded for planned power down events. Therefore using the isolated Park/Unpark command is no longer recommended except for debugging purposes.

If the system is not going to be powered down it is recommended to set the DMD to Idle Mode (see [Section 2.4.1.5](#)).

#### Note

Except for Video Mode it is required to issue a Stop command before issuing a Park command. If the Display Mode is set to Pre-stored pattern mode, Video pattern mode or Pattern On-The-Fly mode, the pattern sequence must be stopped prior to execution of this command. The device stops the pattern sequence by calling Pattern Display Start/Stop ([Section 2.4.4.3.1](#)).

It is only Video Mode that resumes without further command after the device issues an Unpark command to return mirrors to operation. For all other mode, the device must resend a Pattern Display LUT Configuration command and Pattern Display LUT Reorder Configuration command before restarting display of patterns sequence.

**Table 2-36. DMD Park and Unpark Command**

| I <sup>2</sup> C |       | USB    |

|------------------|-------|--------|

| Read             | Write |        |

| 0x14             | 0x94  | 0x0609 |

**Table 2-37. DMD Park and Unpark Command Definition**

| BYTE | BITS | DESCRIPTION                                                                                                                                     | RESET | TYPE |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 0    | 0    | 0 = Unpark DMD. Controller returns to the last commanded operating mode.<br>1 = Park DMD. Mirrors go to parked state. LED outputs are disabled. | d0    | wr   |

|      | 7:1  | Reserved                                                                                                                                        | d0    | r    |

### 2.3.1.3 Curtain Color

This register provides image curtain control. When enabled and the input source is set to external video with no video source connected, a solid color field is displayed on the entire DMD display. The Display Curtain Control provides an alternate method of masking temporary source corruption from reaching the display due to on-the-fly reconfiguration. It is also useful for optical test and debug support.

**Table 2-38. Curtain Color Command**

| I <sup>2</sup> C |       | USB    |

|------------------|-------|--------|

| Read             | Write |        |

| 0x06             | 0x86  | 0x1100 |

**Table 2-39. Display Curtain Command Definition**

| BYTE | BITS  | DESCRIPTION                                     | RESET | TYPE |

|------|-------|-------------------------------------------------|-------|------|

| 1:0  | 9:0   | Red color intensity in a scale from 0 to 1023   | d0    | wr   |

|      | 15:10 | Reserved                                        | d0    | r    |

| 3:2  | 9:0   | Green color intensity in a scale from 0 to 1023 | d0    | wr   |

|      | 15:10 | Reserved                                        | d0    | r    |

| 5:4  | 9:0   | Blue color intensity in a scale from 0 to 1023  | d1023 | wr   |

|      | 15:10 | Reserved                                        | d0    | r    |

### 2.3.2 Parallel Interface Configuration

The Parallel Interface Configuration manages the operation of the RGB parallel interface.

#### 2.3.2.1 Parallel Port Configuration

The Parallel Port Configuration command reads the parallel port configuration details.

**Table 2-40. Parallel Port Configuration Command**

| I <sup>2</sup> C |       | USB    |

|------------------|-------|--------|

| Read             | Write |        |

| 0x64             | N/A   | 0x1A3C |

**Table 2-41. Parallel Port Configuration Command Definition**

| BYTE  | BITS | DESCRIPTION                                                                                                                      | RESET          | TYPE |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------|----------------|------|

| 1:0   | 32:0 | Total DMD Area - pixels per line<br><br><b>Note</b><br>This is the entire width in pixels of the native DMD resolution           | Read from EDID | r    |

| 3:2   | 32:0 | Total DMD Area - lines per frame                                                                                                 | Read from EDID | r    |

| 5:4   | 32:0 | Active Area - pixels per line<br><br><b>Note</b><br>For dual DLPC900 DMDs this is half of the width of the native DMD resolution | Read from EDID | r    |

| 7:6   | 32:0 | Active Area - lines per frame                                                                                                    | Read from EDID | r    |

| 9:8   | 32:0 | Active Area - first pixel                                                                                                        | Read from EDID | r    |

| 11:10 | 32:0 | Active Area - first line                                                                                                         | Read from EDID | r    |

| 13:12 | 32:0 | Bottom Field - first line                                                                                                        | Read from EDID | r    |

| 17:14 | 64:0 | Pixel Clock - frequency in Hz                                                                                                    | Read from EDID | r    |

### 2.3.2.2 Input Data Channel Swap

The Input Data Channel Swap commands configure the specified input data ports and maps the data sub-channels. The DLPC900 interprets channel A as Green, channel B as Red, and channel C as Blue.

**Table 2-42. Input Data Channel Swap Command**

| I <sup>2</sup> C |       | USB    |

|------------------|-------|--------|

| Read             | Write |        |

| 0x04             | 0x84  | 0x1A37 |

**Table 2-43. Input Data Channel Swap Command Definition**

| BYTE | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RESET | TYPE |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 0    | 0    | Port Number<br>0 – Port 1<br>1 – Port 2                                                                                                                                                                                                                                                                                                                                                                                                                       | 0     | w    |

|      | 3:1  | Swap parallel interface data sub-channel:<br>0 - ABC = ABC<br>No swapping of data sub-channels<br>1 - ABC = CAB<br>Data sub-channels are right shifted and circularly rotated<br>2 - ABC = BCA<br>Data sub-channels are left shifted and circularly rotated<br>3 - ABC = ACB<br>Data sub-channels B and C are swapped<br>4 - ABC = BAC<br>Data sub-channels A and B are swapped<br>5 - ABC = CBA<br>Data sub-channels A and C are swapped<br>6 & 7 - Reserved | d4    | wr   |