# **PROFIBUS**

## **User's manual**

Version: **2.80 (December 2018)**

Model no.: **MAProfibus-ENG**

### **Translation of the original documentation**

All values in this manual are current as of its creation. We reserve the right to change the contents of this manual without notice. B&R Industrial Automation GmbH is not liable for technical or editorial errors and defects in this manual. In addition, B&R Industrial Automation GmbH assumes no liability for damages that are directly or indirectly attributable to the delivery, performance or use of this material. We point out that the software and hardware designations and brand names of the respective companies used in this document are subject to general trademark, brand or patent protection.

|                                                                       |           |

|-----------------------------------------------------------------------|-----------|

| <b>1 Technical description.....</b>                                   | <b>7</b>  |

| 1.1 X20 bus controller.....                                           | 7         |

| 1.1.1 Order data.....                                                 | 7         |

| 1.1.2 Technical data.....                                             | 7         |

| 1.1.3 LED status indicators.....                                      | 8         |

| 1.1.3.1 State diagnostics via the Status/Error LEDs.....              | 9         |

| 1.1.4 Operating and connection elements.....                          | 9         |

| 1.1.4.1 PROFIBUS DP interface.....                                    | 9         |

| 1.1.4.2 PROFIBUS DP node number switches.....                         | 10        |

| 1.1.4.3 Automatic transfer rate detection.....                        | 10        |

| 1.2 X67 bus controller.....                                           | 11        |

| 1.2.1 Order data.....                                                 | 11        |

| 1.2.2 Technical data.....                                             | 11        |

| 1.2.3 LED status indicators.....                                      | 14        |

| 1.2.4 Operating and connection elements.....                          | 15        |

| 1.2.4.1 PROFIBUS DP interface.....                                    | 15        |

| 1.2.4.2 PROFIBUS DP node number.....                                  | 15        |

| 1.2.4.3 Automatic transfer rate detection.....                        | 16        |

| 1.3 Firmware installed prior to delivery.....                         | 16        |

| <b>2 Installation.....</b>                                            | <b>17</b> |

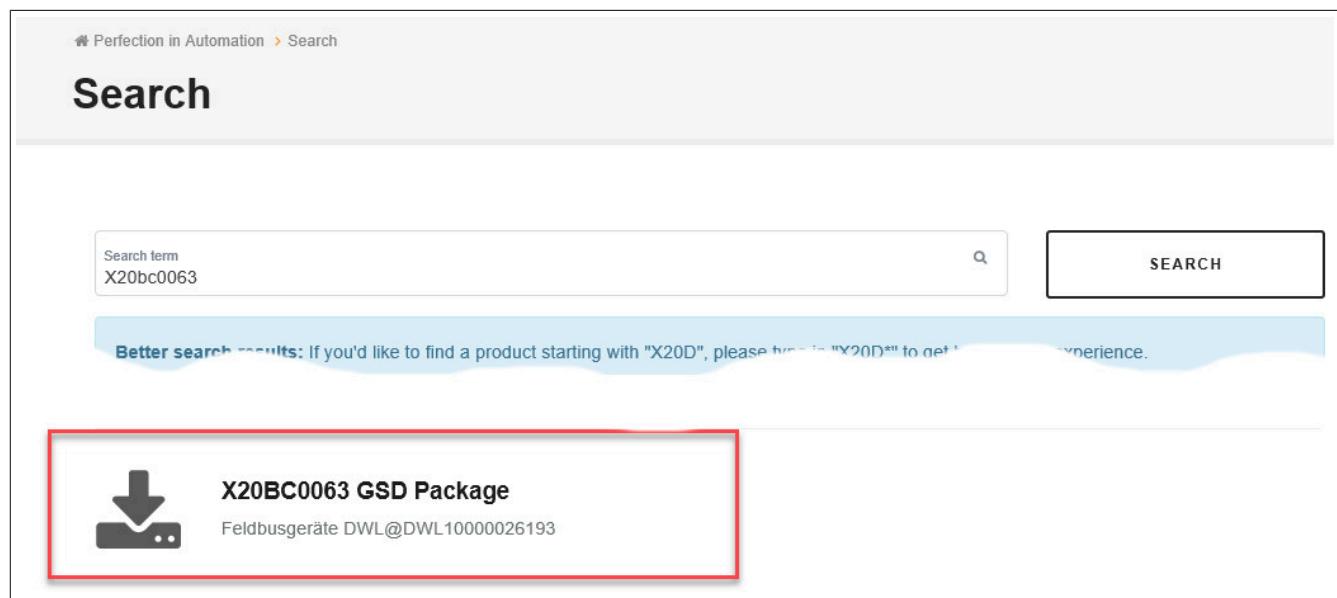

| 2.1 GSD file.....                                                     | 18        |

| 2.2 Bitmaps.....                                                      | 18        |

| <b>3 Configuration.....</b>                                           | <b>19</b> |

| 3.1 Configuring the I/O modules.....                                  | 20        |

| 3.2 Configuring the bus controller.....                               | 21        |

| 3.2.1 Data format.....                                                | 21        |

| 3.2.2 Slot diagnostics.....                                           | 21        |

| 3.2.3 Bus controller behavior for missing modules.....                | 21        |

| 3.2.4 Supply voltage warnings.....                                    | 21        |

| 3.2.5 X2X cycle time.....                                             | 22        |

| 3.2.6 Slowest I/O modules.....                                        | 22        |

| 3.3 Structure of the PROFIBUS DP parameter telegram.....              | 23        |

| 3.4 Additional information for the certification authority.....       | 24        |

| 3.4.1 Minimum requirements for parameter and configuration data.....  | 24        |

| 3.4.2 Parameter data for the operation of other I/O modules.....      | 24        |

| 3.4.3 Checking the parameter and configuration data.....              | 24        |

| <b>4 Diagnostics.....</b>                                             | <b>25</b> |

| 4.1 LED display.....                                                  | 25        |

| 4.1.1 State diagnostics via the Status/Error LEDs.....                | 25        |

| 4.1.2 Communications LEDs.....                                        | 25        |

| 4.1.3 LED blink code when switched on.....                            | 26        |

| 4.1.4 Forcing a boot from the factory default sector.....             | 26        |

| 4.2 PROFIBUS DP diagnostics telegram.....                             | 27        |

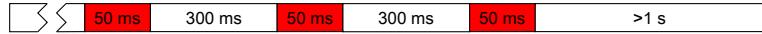

| 4.2.1 Displaying diagnostics information in the engineering tool..... | 27        |

| 4.2.2 Evaluating the diagnostics telegram during runtime.....         | 27        |

| 4.2.3 Boot behavior.....                                              | 27        |

| 4.2.4 Structure of the diagnostics telegram.....                      | 28        |

| 4.2.4.1 Diagnostic flag 1.....                                        | 28        |

| 4.2.4.2 Diagnostic flag 2.....                                        | 28        |

| 4.2.4.3 Internal error.....                                           | 29        |

| 4.2.4.4 Single channel error.....                                     | 29        |

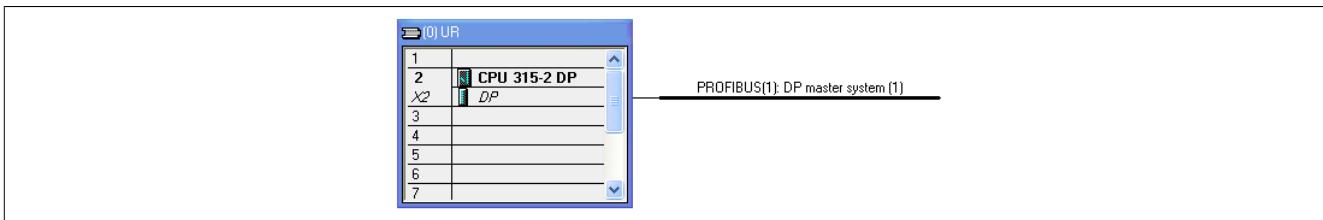

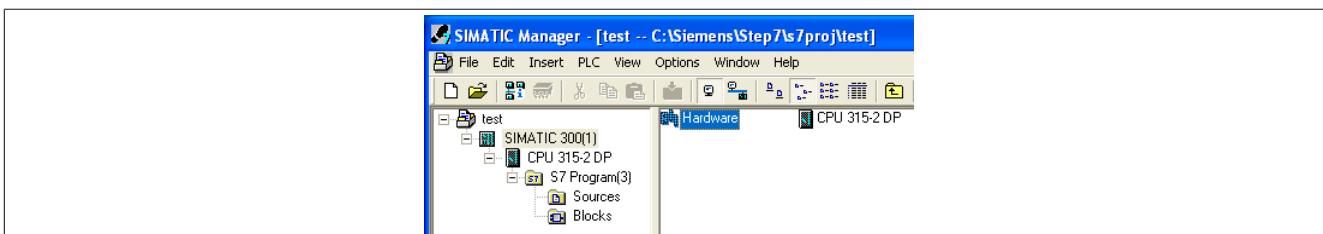

| <b>5 Use with SIMATIC Manager.....</b>                                | <b>30</b> |

| 5.1 Project environment.....                                          | 30        |

|                                                            |           |

|------------------------------------------------------------|-----------|

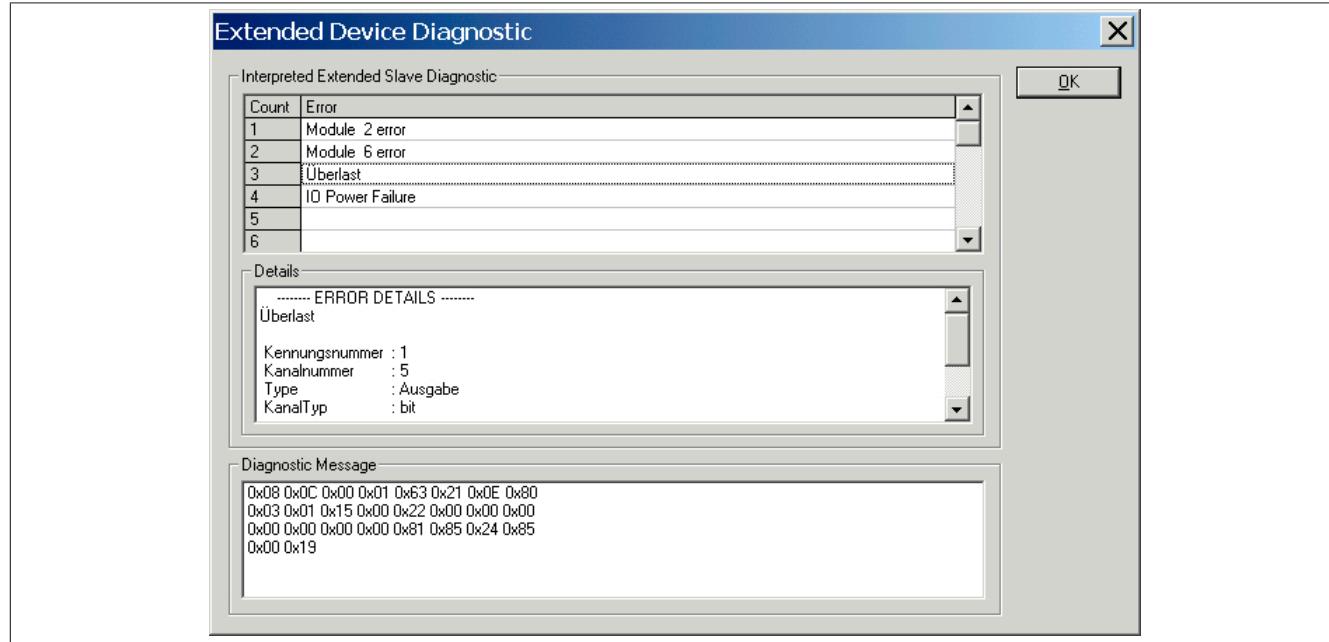

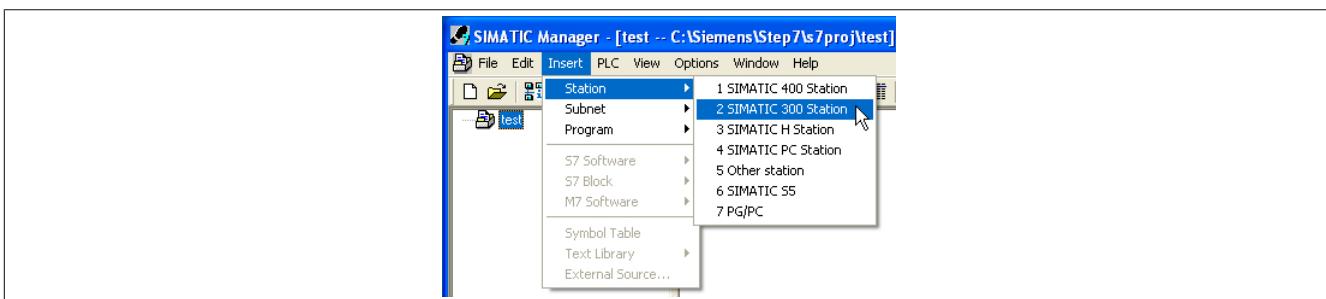

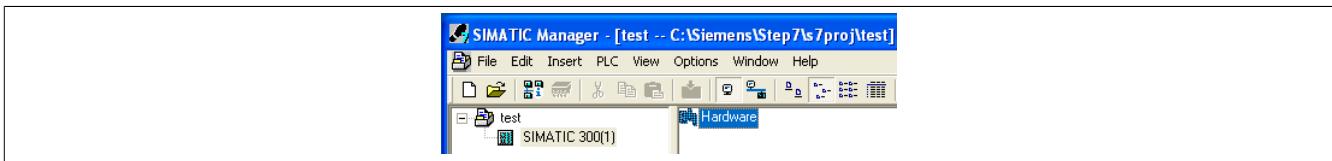

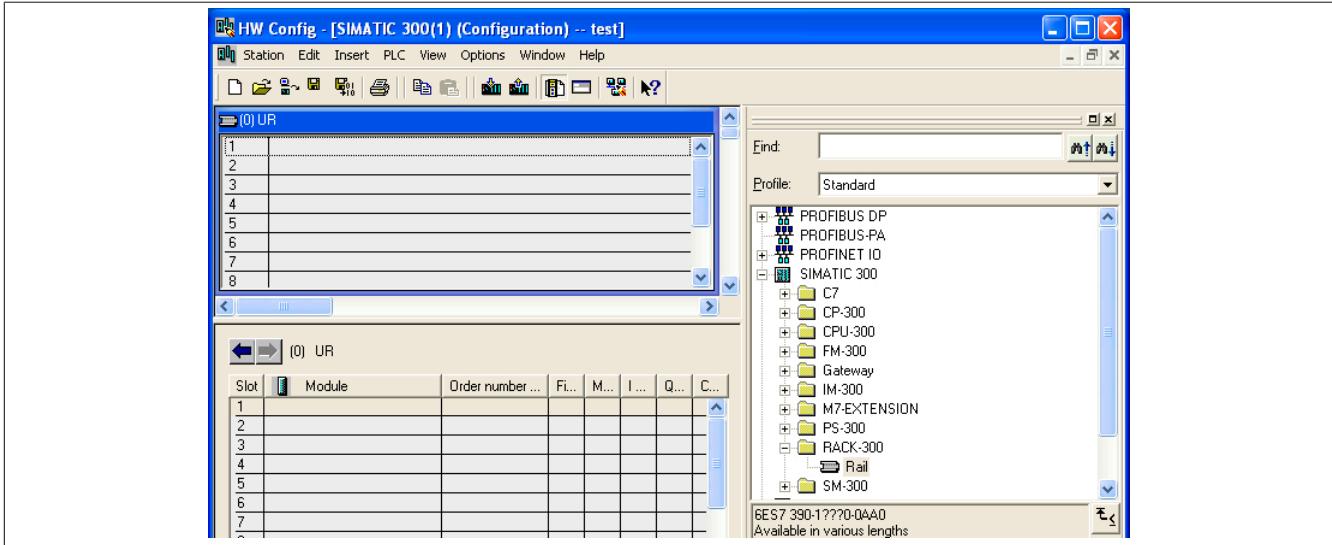

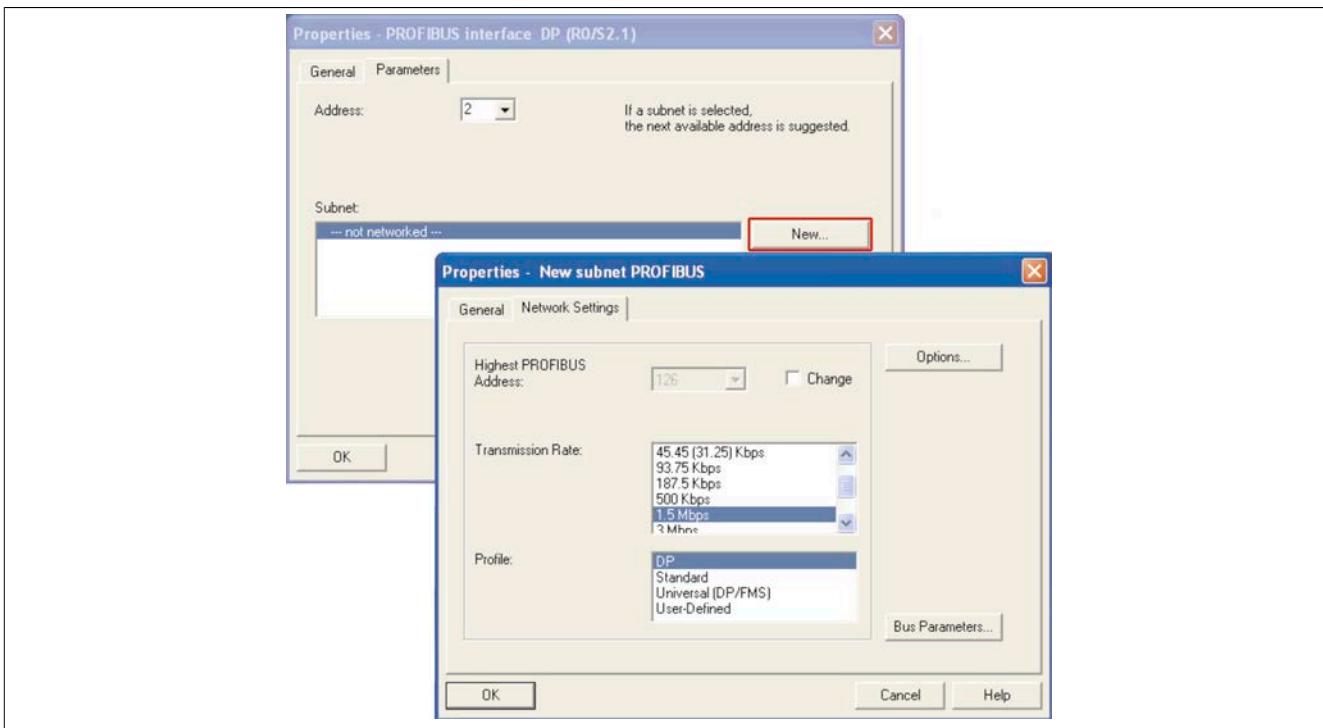

| 5.1.1 Creating a new project manually.....                 | 30        |

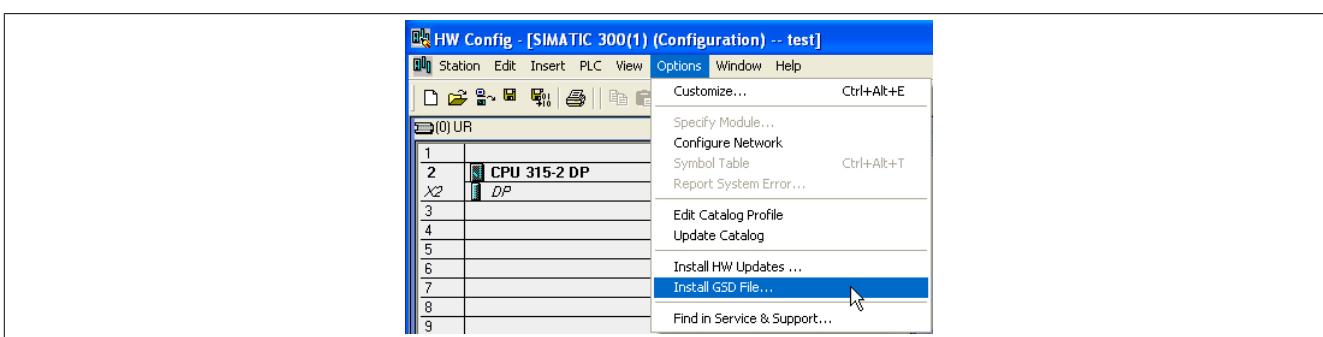

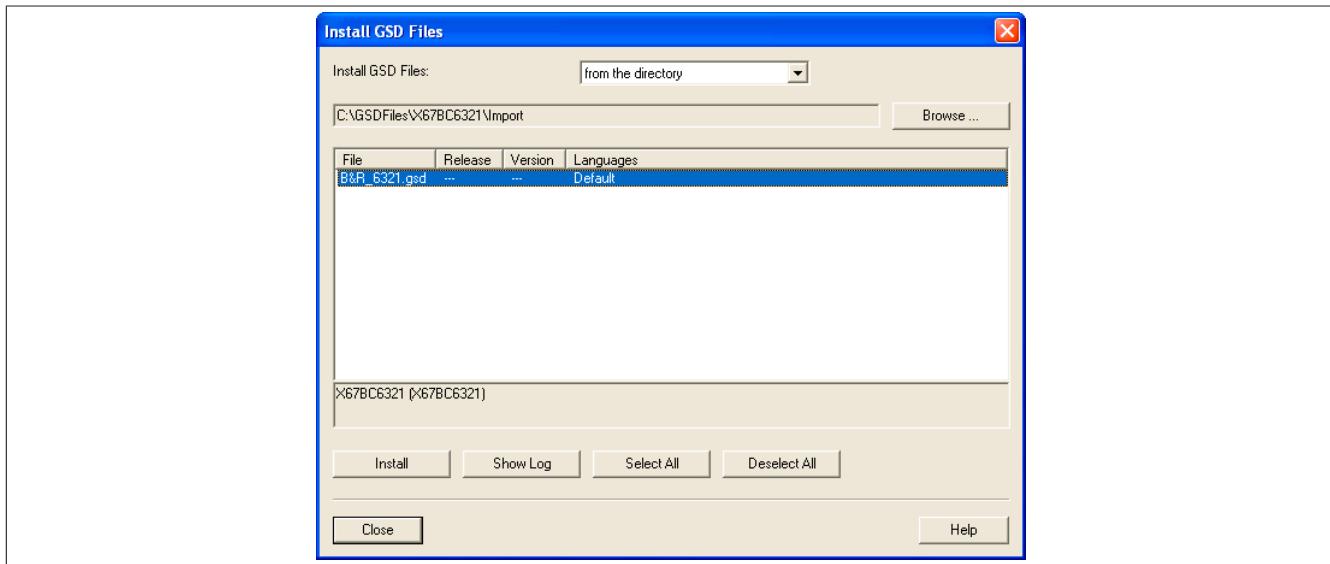

| 5.2 Installing the GSD file.....                           | 32        |

| 5.3 Integrating PROFIBUS DP bus controllers.....           | 33        |

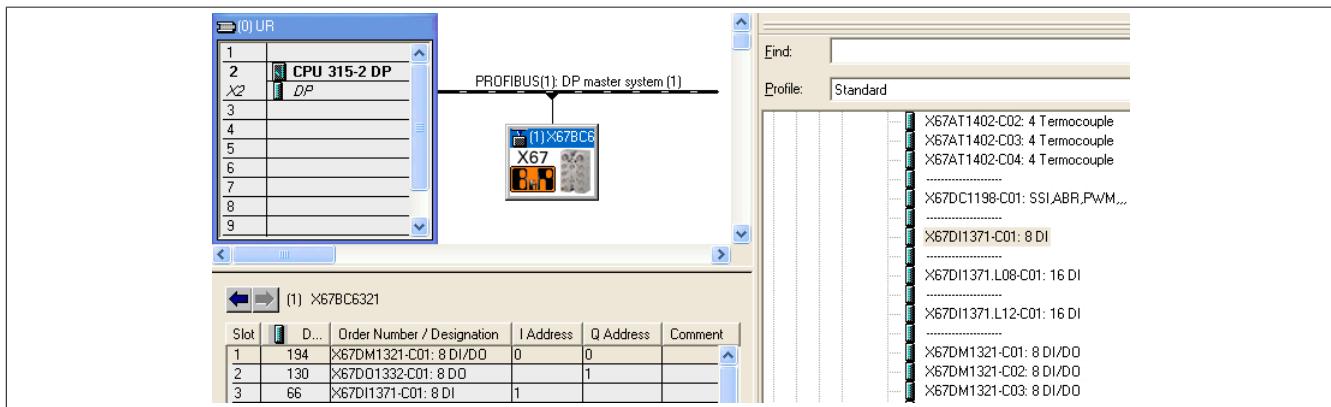

| 5.4 Extending X2X Link.....                                | 35        |

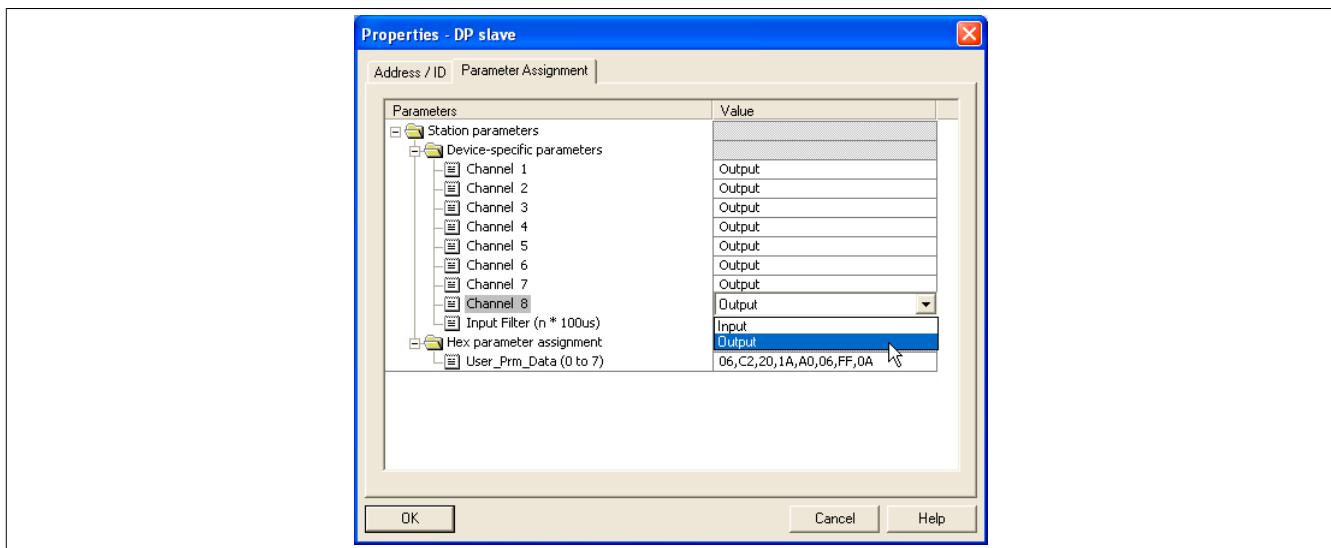

| 5.4.1 Configuring the I/O modules.....                     | 35        |

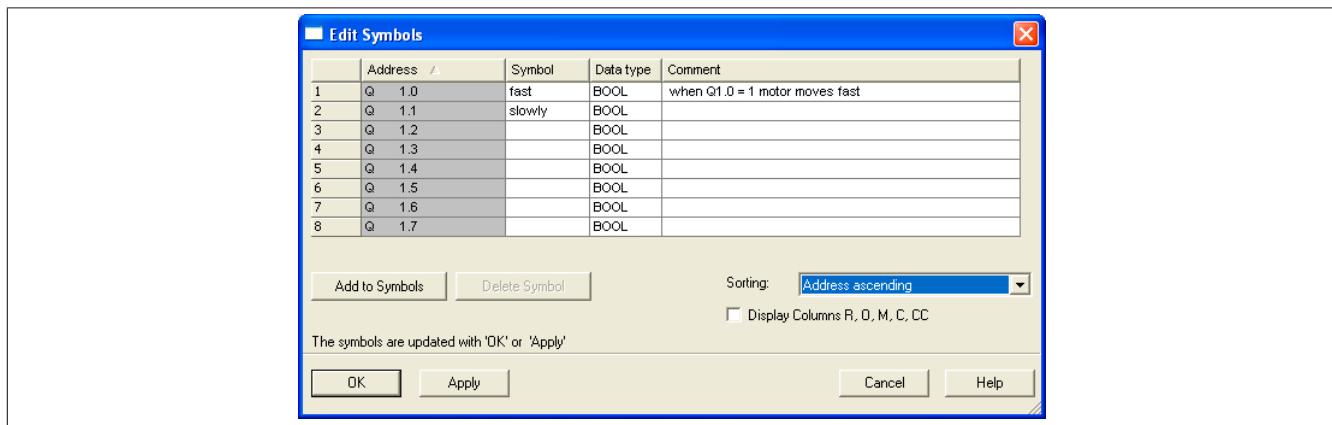

| 5.4.2 Variable assignment.....                             | 36        |

| 5.5 Configuration download.....                            | 36        |

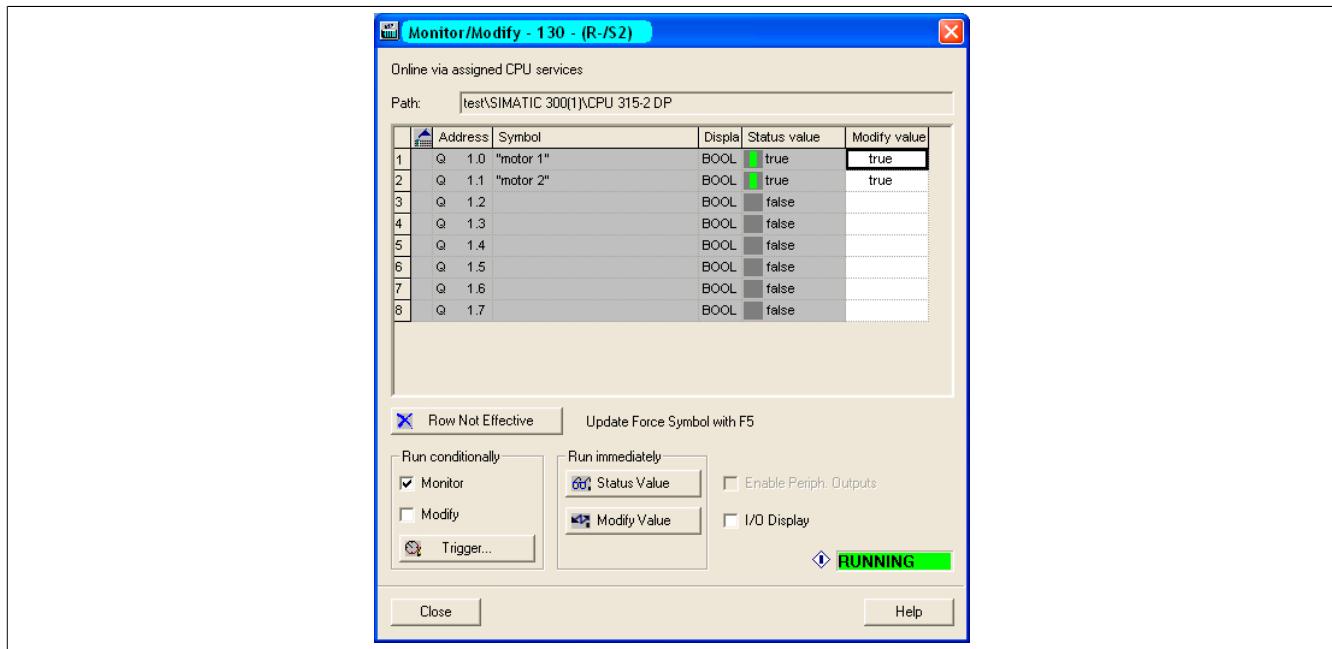

| 5.6 Controlling the modules.....                           | 36        |

| <b>6 Register description.....</b>                         | <b>37</b> |

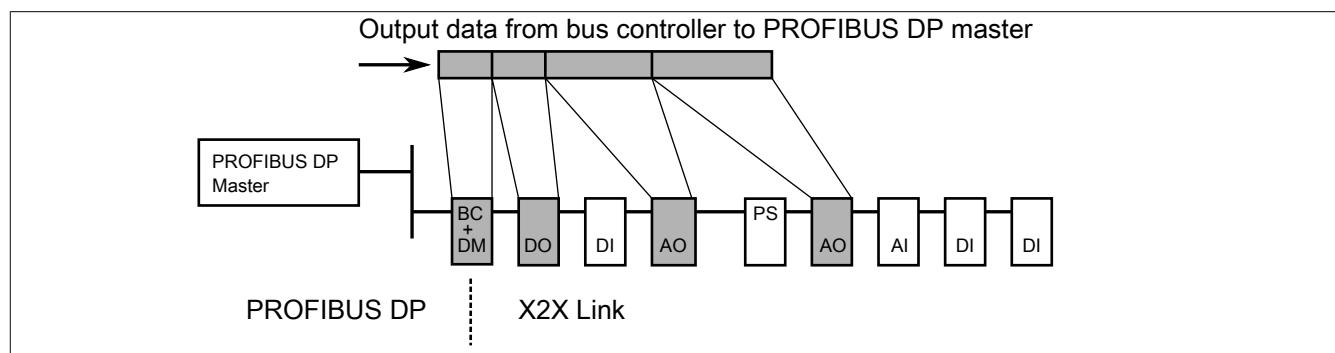

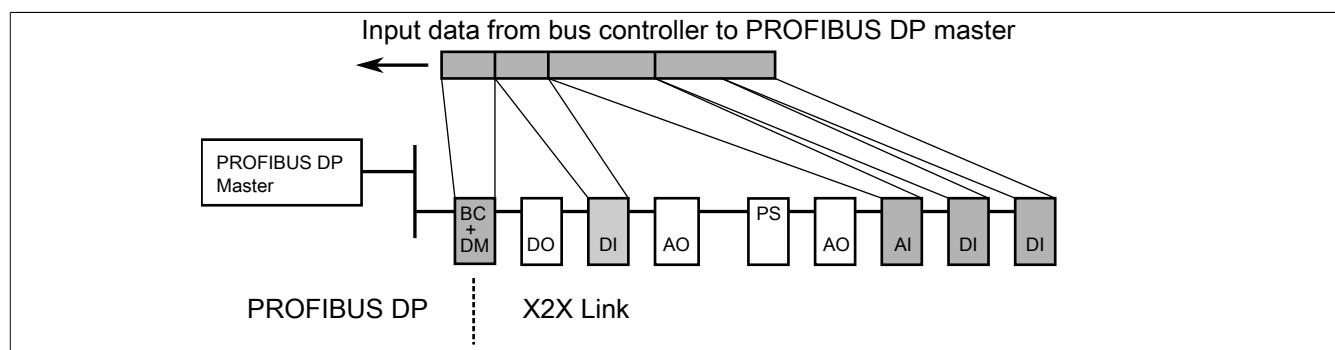

| 6.1 Structure of PROFIBUS data.....                        | 37        |

| 6.2 Module list.....                                       | 38        |

| 6.2.1 Additional information.....                          | 38        |

| 6.2.2 PROFIBUS GSD-function models.....                    | 38        |

| 6.2.3 Overview of the terms used in the tables.....        | 38        |

| 6.3 X20 I/O system.....                                    | 39        |

| 6.3.1 Bus receivers/transmitters.....                      | 39        |

| 6.3.1.1 X20BR9300 / X20BT9x00.....                         | 39        |

| 6.3.2 Power supply modules.....                            | 40        |

| 6.3.2.1 X20PS21x0 / X20PS33x0 / X20PS940x.....             | 40        |

| 6.3.3 Digital input modules.....                           | 41        |

| 6.3.3.1 X20DIx37x / X20DIx653 / X20DI0471 / X20DI6553..... | 41        |

| 6.3.3.2 X20DI2377.....                                     | 42        |

| 6.3.3.3 X20DI4375.....                                     | 44        |

| 6.3.3.4 X20DI4760.....                                     | 47        |

| 6.3.4 Digital output modules.....                          | 48        |

| 6.3.4.1 X20DOx32x / X20DOx33x.....                         | 48        |

| 6.3.4.2 X20DOx529 / X20DOx649.....                         | 49        |

| 6.3.4.3 X20DOx623.....                                     | 50        |

| 6.3.4.4 X20DO6325.....                                     | 52        |

| 6.3.4.5 X20DOx633.....                                     | 54        |

| 6.3.4.6 X20DO6639.....                                     | 57        |

| 6.3.4.7 X20DO8323.....                                     | 58        |

| 6.3.5 Digital mixed modules.....                           | 60        |

| 6.3.5.1 X20DM9324.....                                     | 60        |

| 6.3.6 Analog input modules.....                            | 61        |

| 6.3.6.1 X20AI1744.....                                     | 61        |

| 6.3.6.2 X20AIx222.....                                     | 63        |

| 6.3.6.3 X20AI2237.....                                     | 65        |

| 6.3.6.4 X20AIx322.....                                     | 67        |

| 6.3.6.5 X20AI2437.....                                     | 69        |

| 6.3.6.6 X20AI2438.....                                     | 70        |

| 6.3.6.7 X20AIx622.....                                     | 74        |

| 6.3.6.8 X20AIx632.....                                     | 77        |

| 6.3.6.9 X20AI8221.....                                     | 80        |

| 6.3.6.10 X20AI8321.....                                    | 82        |

| 6.3.6.11 X20AIx744.....                                    | 84        |

| 6.3.6.12 X20AP31x1.....                                    | 88        |

| 6.3.7 Analog output modules.....                           | 92        |

| 6.3.7.1 X20AO2437.....                                     | 92        |

| 6.3.7.2 X20AO2438.....                                     | 93        |

| 6.3.7.3 X20AOx622.....                                     | 97        |

| 6.3.7.4 X20AOx632 / X20AO4635.....                         | 98        |

| 6.3.8 Temperature modules.....                             | 99        |

| 6.3.8.1 X20ATx222.....                                     | 99        |

| 6.3.8.2 X20AT4232.....                                     | 101       |

| 6.3.8.3 X20AT2311.....                                     | 103       |

|                                                             |     |

|-------------------------------------------------------------|-----|

| 6.3.8.4 X20ATx402.....                                      | 105 |

| 6.3.8.5 X20ATx312.....                                      | 108 |

| 6.3.8.6 X20ATA492.....                                      | 110 |

| 6.3.8.7 X20ATC402.....                                      | 112 |

| 6.3.9 Communication modules.....                            | 114 |

| 6.3.9.1 X20CS1011.....                                      | 114 |

| 6.3.9.2 X20CS1013.....                                      | 117 |

| 6.3.9.3 X20CS1020 / X0CS1030.....                           | 121 |

| 6.3.9.4 X20CS1070.....                                      | 125 |

| 6.3.10 Motor modules.....                                   | 129 |

| 6.3.10.1 X20MM2436.....                                     | 129 |

| 6.3.10.2 X20MM4456.....                                     | 133 |

| 6.3.10.3 X20SM14x6.....                                     | 139 |

| 6.3.11 Other modules.....                                   | 141 |

| 6.3.11.1 X20CM8281.....                                     | 141 |

| 6.3.11.2 X20CMRx1x.....                                     | 144 |

| 6.3.11.3 X20PD0011 / X20PD0012 / X20PD0016 / X20PD2113..... | 146 |

| 6.3.11.4 X20PS4951.....                                     | 147 |

| 6.3.12 Counter modules.....                                 | 148 |

| 6.3.12.1 X20CM1201.....                                     | 148 |

| 6.3.12.2 X20CM1941.....                                     | 150 |

| 6.3.12.3 X20DC1073.....                                     | 151 |

| 6.3.12.4 X20DC1176 / X20DC137A.....                         | 153 |

| 6.3.12.5 X20DC1178.....                                     | 156 |

| 6.3.12.6 X20DC1x96.....                                     | 158 |

| 6.3.12.7 X20DCxx98.....                                     | 161 |

| 6.3.12.8 X20DC2190.....                                     | 162 |

| 6.3.12.9 X20DC2395.....                                     | 167 |

| 6.3.12.10 X20DC2396.....                                    | 169 |

| 6.3.12.11 X20DC4395.....                                    | 172 |

| 6.4 X67 I/O system.....                                     | 175 |

| 6.4.1 Digital input modules.....                            | 175 |

| 6.4.1.1 X67DI137x.....                                      | 175 |

| 6.4.2 Digital output modules.....                           | 176 |

| 6.4.2.1 X67DO1332.....                                      | 176 |

| 6.4.2.2 X67DO9332.L12-C01.....                              | 177 |

| 6.4.3 Digital mixed modules.....                            | 178 |

| 6.4.3.1 X67DM1321 (8-channel).....                          | 178 |

| 6.4.3.2 X67DM1321 (16-channel).....                         | 181 |

| 6.4.3.3 X67DM93x1.....                                      | 184 |

| 6.4.3.4 X67DV1311.....                                      | 186 |

| 6.4.4 Analog input modules.....                             | 187 |

| 6.4.4.1 X67AI1x23 / X67AI1x33.....                          | 187 |

| 6.4.4.2 X67AI2744.....                                      | 190 |

| 6.4.4.3 X67AI4850.....                                      | 192 |

| 6.4.5 Analog output modules.....                            | 193 |

| 6.4.5.1 X67AO1x23.....                                      | 193 |

| 6.4.6 Analog mixed modules.....                             | 194 |

| 6.4.6.1 X67AM1x23.....                                      | 194 |

| 6.4.7 Communication modules.....                            | 196 |

| 6.4.7.1 X67IF1121-1.....                                    | 196 |

| 6.4.8 Motor modules.....                                    | 200 |

| 6.4.8.1 X67MM2436.....                                      | 200 |

| 6.4.8.2 X67SM2436 / X67SM4320.....                          | 207 |

| 6.4.9 Other modules.....                                    | 209 |

| 6.4.9.1 X67UM1352.....                                      | 209 |

| 6.4.9.2 X67UM4389.....                                      | 212 |

## Table of contents

|                                                                      |     |

|----------------------------------------------------------------------|-----|

| 6.4.10 Temperature modules.....                                      | 214 |

| 6.4.10.1 X67AT13xx.....                                              | 214 |

| 6.4.10.2 X67AT1402.....                                              | 216 |

| 6.4.11 Counter modules.....                                          | 218 |

| 6.4.11.1 X67DC1198.....                                              | 218 |

| 6.5 Additional X2X I/O modules.....                                  | 221 |

| 6.5.1 Keypad modules.....                                            | 221 |

| 6.5.1.1 4XP0000.00-K12 / K39 / K47.....                              | 221 |

| 6.5.1.2 4XP0000.00-K19 / K20 / K30 / K40 /K95.....                   | 221 |

| 6.5.1.3 4XP0000.00-K21 / K22 / K41 / K46.....                        | 221 |

| 6.5.1.4 4XP0000.00-K62.....                                          | 222 |

| 6.5.1.5 4XP0000.00-K64 / K74 / K75.....                              | 222 |

| 6.5.1.6 4XP0000.00-K76 / K94 / KA4.....                              | 222 |

| 6.5.1.7 4XP0000.00-K85.....                                          | 222 |

| 6.5.2 Keypad extension for APC.....                                  | 223 |

| 6.5.2.1 5ACCKP01.185B-C01 / .240C-C01.....                           | 223 |

| 6.5.2.2 5AC800.EXT3.....                                             | 223 |

| 6.5.2.3 5AC800.EXT3-K03.....                                         | 223 |

| 6.5.2.4 5AC800.EXT3-K05.....                                         | 224 |

| 6.5.3 Keypad extension for panels.....                               | 225 |

| 6.5.3.1 5AP933.156B-K10.....                                         | 225 |

| 6.5.3.2 5AP93D.156B-K02.....                                         | 225 |

| 6.5.3.3 5AP980.1505-B10.....                                         | 225 |

| 6.5.3.4 5PC725.1505-K01X2X.....                                      | 225 |

| 6.5.3.5 5PP320.1043.K03.....                                         | 225 |

| 6.5.4 Valve connections.....                                         | 226 |

| 6.5.4.1 0AC190.1-NOR.....                                            | 226 |

| 6.5.4.2 7XV1xx.50-xx.....                                            | 227 |

| 6.5.5 Compact I/O.....                                               | 228 |

| 6.5.5.1 7XX408.50-1.....                                             | 228 |

| 6.5.5.2 7XX436.50-1.....                                             | 231 |

| 6.6 ACOPOSmicro.....                                                 | 235 |

| 6.6.1 80PS080X3.10-010.....                                          | 235 |

| 6.6.2 80SD100XD.C044-01 / 80SD100XD.C0XX-01 / 80SD100XS.C0XX-01..... | 237 |

| 6.7 ACOPOSinverter.....                                              | 240 |

| 6.7.1 ACPI_X64.....                                                  | 240 |

# 1 Technical description

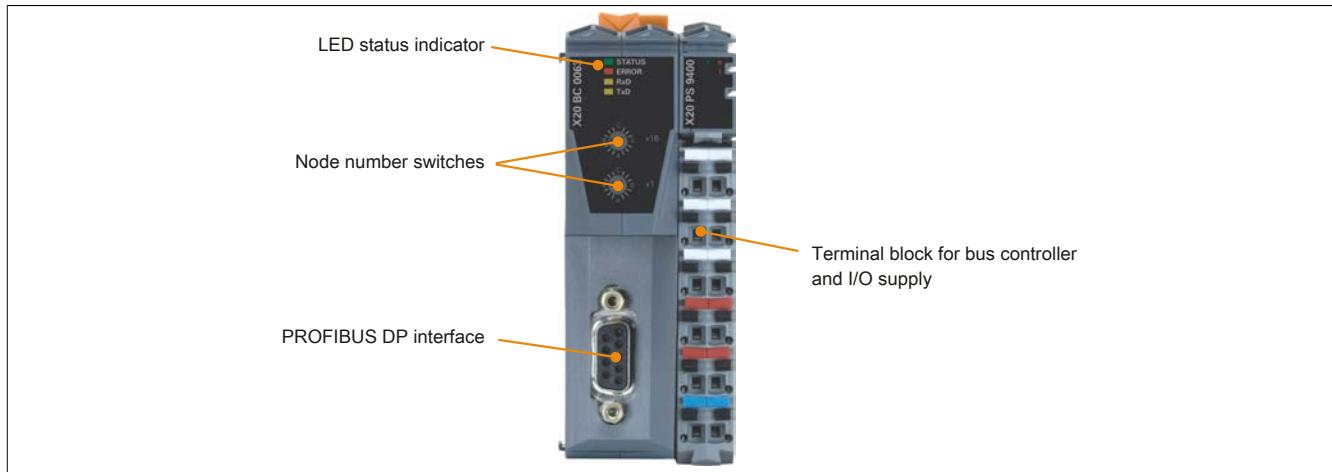

## 1.1 X20 bus controller

### 1.1.1 Order data

| Model number                              | Short description                                                                                                                          | Figure |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <b>Bus controllers</b>                    |                                                                                                                                            |        |

| X20BC0063                                 | X20 bus controller, 1 PROFIBUS DP interface, 9-pin DSUB connection, order bus base, power supply module and terminal block separately      |        |

| <b>Required accessories</b>               |                                                                                                                                            |        |

| <b>System modules for bus controllers</b> |                                                                                                                                            |        |

| X20BB80                                   | X20 bus base, for X20 base module (BC, HB, etc.) and X20 power supply module, X20 end plates (left and right) X20AC0SL1/X20AC0SR1 included |        |

| X20PS9400                                 | X20 power supply module, for bus controller and internal I/O power supply, X2X Link power supply                                           |        |

| X20PS9402                                 | X20 power supply module, for bus controller and internal I/O power supply, X2X Link power supply, supply not electrically isolated         |        |

| <b>Terminal blocks</b>                    |                                                                                                                                            |        |

| X20TB12                                   | X20 terminal block, 12-pin, 24 VDC keyed                                                                                                   |        |

| <b>Optional accessories</b>               |                                                                                                                                            |        |

| <b>Infrastructure components</b>          |                                                                                                                                            |        |

| 0G1000.00-090                             | Bus connector, RS485, for PROFIBUS networks                                                                                                |        |

Table 1: X20BC0063 - Order data

### 1.1.2 Technical data

| Model number                                                     | X20BC0063                                                                                                     |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| <b>Short description</b>                                         |                                                                                                               |

| Bus controller                                                   | PROFIBUS DP V0 slave                                                                                          |

| <b>General information</b>                                       |                                                                                                               |

| B&R ID code                                                      | 0x1F1C                                                                                                        |

| Status indicators                                                | Module status, bus function, data transfer                                                                    |

| Diagnostics                                                      |                                                                                                               |

| Module status                                                    | Yes, using status LED and software                                                                            |

| Bus function                                                     | Yes, using status LED                                                                                         |

| Data transfer                                                    | Yes, using status LED                                                                                         |

| Power consumption                                                |                                                                                                               |

| Bus                                                              | 2.3 W                                                                                                         |

| Additional power dissipation caused by actuators (resistive) [W] | -                                                                                                             |

| Certifications                                                   |                                                                                                               |

| CE                                                               | Yes                                                                                                           |

| KC                                                               | Yes                                                                                                           |

| UL                                                               | cULus E115267<br>Industrial control equipment                                                                 |

| HazLoc                                                           | cCSAus 244665<br>Process control equipment<br>for hazardous locations<br>Class I, Division 2, Groups ABCD, T5 |

| ATEX                                                             | Zone 2, II 3G Ex nA nC IIA T5 Gc<br>IP20, Ta (see X20 user's manual)<br>FTZÚ 09 ATEX 0083X                    |

| GOST-R                                                           | Yes                                                                                                           |

| <b>Interfaces</b>                                                |                                                                                                               |

| Fieldbus                                                         | PROFIBUS DP V0 slave                                                                                          |

| Design                                                           | 9-pin female DSUB connector                                                                                   |

| Max. distance                                                    | 1200 m                                                                                                        |

| Transfer rate                                                    | Max. 12 Mbit/s                                                                                                |

| Default transfer rate                                            | Automatic transfer rate detection                                                                             |

| Min. cycle time <sup>1)</sup>                                    |                                                                                                               |

| Fieldbus                                                         | No limitations                                                                                                |

| X2X Link                                                         | 400 µs                                                                                                        |

| Synchronization between bus systems possible                     | No                                                                                                            |

Table 2: X20BC0063 - Technical data

|                                        |                                                                                                                                                      |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>Model number</b>                    | <b>X20BC0063</b>                                                                                                                                     |  |

| <b>Electrical characteristics</b>      |                                                                                                                                                      |  |

| Electrical isolation                   | PROFIBUS isolated from I/O<br>PROFIBUS not isolated from bus                                                                                         |  |

| <b>Operating conditions</b>            |                                                                                                                                                      |  |

| Mounting orientation                   |                                                                                                                                                      |  |

| Horizontal                             | Yes                                                                                                                                                  |  |

| Vertical                               | Yes                                                                                                                                                  |  |

| Installation elevation above sea level |                                                                                                                                                      |  |

| 0 to 2000 m                            | No limitations                                                                                                                                       |  |

| >2000 m                                | Reduction of ambient temperature by 0.5°C per 100 m                                                                                                  |  |

| Degree of protection per EN 60529      | IP20                                                                                                                                                 |  |

| <b>Environmental conditions</b>        |                                                                                                                                                      |  |

| Temperature                            |                                                                                                                                                      |  |

| Operation                              |                                                                                                                                                      |  |

| Horizontal mounting orientation        | -25 to 60°C                                                                                                                                          |  |

| Vertical mounting orientation          | -25 to 50°C                                                                                                                                          |  |

| Derating                               | -                                                                                                                                                    |  |

| Storage                                | -40 to 85°C                                                                                                                                          |  |

| Transport                              | -40 to 85°C                                                                                                                                          |  |

| Relative humidity                      |                                                                                                                                                      |  |

| Operation                              | 5 to 95%, non-condensing                                                                                                                             |  |

| Storage                                | 5 to 95%, non-condensing                                                                                                                             |  |

| Transport                              | 5 to 95%, non-condensing                                                                                                                             |  |

| <b>Mechanical properties</b>           |                                                                                                                                                      |  |

| Note                                   | Order 1x X20TB12 terminal block separately<br>Order 1x X20PS9400 or X20PS9402 power supply module separately<br>Order 1x X20BB80 bus base separately |  |

| Spacing <sup>2)</sup>                  | 37.5 <sup>+0.2</sup> mm                                                                                                                              |  |

Table 2: X20BC0063 - Technical data

- 1) The minimum cycle time defines how far the bus cycle can be reduced without communication errors occurring.

- 2) Spacing is based on the width of the X20BB80 bus base. In addition, an X20PS9400 or X20PS9402 supply module is always required for the bus controller.

### 1.1.3 LED status indicators

| Figure                                                                              | LED              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

|-------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------|-----|-----|-----------------------------|----|----|---------|----|----------|-----------------|----------|-----|-----------------------------|----|-----|--------------------------|----------|----------|--------------|-----|----------|---------------------|--------------|--------------|----------------|

|  | STATUS and ERROR | <p>Status indicator for PROFIBUS DP bus controller.</p> <table border="1"> <thead> <tr> <th>STATUS (green)</th> <th>ERROR (red)</th> <th>Description</th> </tr> </thead> <tbody> <tr> <td>Off</td> <td>Off</td> <td>HARDWARE FAULT / POWER FAIL</td> </tr> <tr> <td>On</td> <td>On</td> <td>BUS OFF</td> </tr> <tr> <td>On</td> <td>Blinking</td> <td>WAIT FOR CONFIG</td> </tr> <tr> <td>Blinking</td> <td>Off</td> <td>DATA EXCHANGE - DIAGNOSTICS</td> </tr> <tr> <td>On</td> <td>Off</td> <td>DATA EXCHANGE - NO ERROR</td> </tr> <tr> <td>Blinking</td> <td>Blinking</td> <td>CONFIG ERROR</td> </tr> <tr> <td>Off</td> <td>Blinking</td> <td>SERVICE MODE - BOOT</td> </tr> <tr> <td>Single flash</td> <td>Single flash</td> <td>HARDWARE FAULT</td> </tr> </tbody> </table> <p>For a more detailed description see "State diagnostics via the Status/Error LEDs" on page 9.</p> | STATUS (green) | ERROR (red) | Description | Off | Off | HARDWARE FAULT / POWER FAIL | On | On | BUS OFF | On | Blinking | WAIT FOR CONFIG | Blinking | Off | DATA EXCHANGE - DIAGNOSTICS | On | Off | DATA EXCHANGE - NO ERROR | Blinking | Blinking | CONFIG ERROR | Off | Blinking | SERVICE MODE - BOOT | Single flash | Single flash | HARDWARE FAULT |

| STATUS (green)                                                                      | ERROR (red)      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| Off                                                                                 | Off              | HARDWARE FAULT / POWER FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| On                                                                                  | On               | BUS OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| On                                                                                  | Blinking         | WAIT FOR CONFIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| Blinking                                                                            | Off              | DATA EXCHANGE - DIAGNOSTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| On                                                                                  | Off              | DATA EXCHANGE - NO ERROR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| Blinking                                                                            | Blinking         | CONFIG ERROR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| Off                                                                                 | Blinking         | SERVICE MODE - BOOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

| Single flash                                                                        | Single flash     | HARDWARE FAULT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

|                                                                                     | RxD              | This yellow LED lights up when the bus controller is receiving data from the PROFIBUS DP fieldbus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

|                                                                                     | TxD              | This yellow LED lights up when the bus controller is sending data via the PROFIBUS DP fieldbus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |             |             |     |     |                             |    |    |         |    |          |                 |          |     |                             |    |     |                          |          |          |              |     |          |                     |              |              |                |

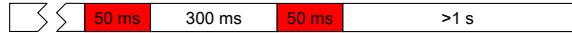

### 1.1.3.1 State diagnostics via the Status/Error LEDs

The condition of the PROFIBUS DP bus controller is diagnosed using the LED status indicators "STATUS" and "ERROR".

| STATUS<br>(green) | ERROR<br>(red) | Function                                                                                                                                                                                                                                                                                 | Solution                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off               | Off            | HARDWARE FAULT / POWER FAILURE                                                                                                                                                                                                                                                           | <ul style="list-style-type: none"> <li>Check wiring of supply voltage.</li> </ul>                                                                                                                                                                                                                                                                                             |

| On                | On             | BUS OFF <ul style="list-style-type: none"> <li>Baud rate not detected</li> <li>No connection to the DP master</li> <li>DP master not active</li> </ul>                                                                                                                                   | <ul style="list-style-type: none"> <li>Check the PROFIBUS network</li> <li>Check the PROFIBUS master</li> </ul>                                                                                                                                                                                                                                                               |

| On                | Blinking       | WAIT FOR CONFIG <ul style="list-style-type: none"> <li>Transfer rate has been detected, but the PROFIBUS master has not yet configured the bus controller</li> </ul>                                                                                                                     | <ul style="list-style-type: none"> <li>Check the node number switch</li> <li>Check the slave address in the master configuration</li> </ul>                                                                                                                                                                                                                                   |

| Blinking          | Off            | DATA EXCHANGE - DIAGNOSTICS <ul style="list-style-type: none"> <li>The bus controller is still initializing the I/O modules</li> <li>The I/O modules configured by the master cannot be found</li> <li>An error has occurred on one or more I/O modules (short circuit, etc.)</li> </ul> | <ul style="list-style-type: none"> <li>Initialization can take a few seconds depending on the number of I/O modules connected</li> <li>Check the wiring and power supply for the I/O modules</li> <li>Read diagnostic messages in the respective PROFIBUS master's engineering tool</li> </ul>                                                                                |

| On                | Off            | DATA EXCHANGE <ul style="list-style-type: none"> <li>Cyclic data exchange with the PROFIBUS DP master</li> </ul>                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                               |

| Blinking          | Blinking       | CONFIG ERROR <ul style="list-style-type: none"> <li>One or more I/O modules found do not match with the configuration of the PROFIBUS DP master</li> <li>The configuration received from the PROFIBUS master is invalid</li> </ul>                                                       | <ul style="list-style-type: none"> <li>Check the wiring of the X2X Link and the order of I/O modules</li> <li>Check configuration of the PROFIBUS master</li> <li>Read diagnostic messages in the respective PROFIBUS master's engineering tool</li> <li>Check the configuration being used - it is possible that the number of configured I/O modules is too high</li> </ul> |

| Off               | Blinking       | SERVICE MODE - BOOT <ul style="list-style-type: none"> <li>The bus controller's node number has been set to 255 (0xFF) - after 2 s the bus controller starts in service mode</li> </ul>                                                                                                  | <ul style="list-style-type: none"> <li>Set a valid node number</li> </ul>                                                                                                                                                                                                                                                                                                     |

| Single flash      | Single flash   | HARDWARE FAULT                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

### 1.1.4 Operating and connection elements

#### 1.1.4.1 PROFIBUS DP interface

| Interface                                         | Pinout |           |

|---------------------------------------------------|--------|-----------|

|                                                   | Pin    | RS485     |

| 9-pin female DSUB connector                       | 1      | Reserved  |

|                                                   | 2      | Reserved  |

|                                                   | 3      | RxD/TxD-P |

|                                                   | 4      | CNTR-P    |

|                                                   | 5      | DGND      |

|                                                   | 6      | CP        |

|                                                   | 7      | Reserved  |

|                                                   | 8      | RxD/TxD-N |

|                                                   | 9      | CNTR-N    |

| CNTR ... Directional switch for external repeater |        |           |

1) Cable color: Red

2) Cable color: Green

### 1.1.4.2 PROFIBUS DP node number switches

The PROFIBUS DP node number is configured using both number switches of the bus controller.

| Switch position | Node number |

|-----------------|-------------|

| 0x00            | Not allowed |

| 0x01 - 0x7D     | 1 to 125    |

| 0x7E - 0xFF     | Not allowed |

### 1.1.4.3 Automatic transfer rate detection

After booting or after a communication timeout, the bus controller goes into the status "Baud Search". This means the bus controller behaves passively on the bus.

The bus controller always begins the search for the configured transfer rate with the highest transfer rate. If a complete error-free telegram is not received during monitoring time, then the search is continued using the next lowest transfer rate.

| Transfer rate |

|---------------|

| 12 Mbit/s     |

| 6 Mbit/s      |

| 3 Mbit/s      |

| 1.5 Mbit/s    |

| 500 kbit/s    |

| 187.5 kbit/s  |

| 93.75 kbit/s  |

| 45.45 kbit/s  |

| 19.2 kbit/s   |

| 9.6 kbit/s    |

## 1.2 X67 bus controller

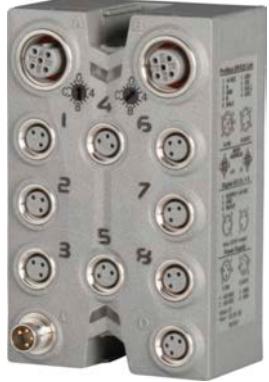

### 1.2.1 Order data

| Model number  | Short description                                                                                                                                                                                                                      | Figure                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|               | <b>Bus controller modules</b>                                                                                                                                                                                                          |                                                                                     |

| X67BC6321     | X67 bus controller, 1 PROFIBUS DP interface, X2X Link power supply 3 W, 8 digital channels configurable as inputs or outputs, 24 VDC, 0.5 A, configurable input filter, 2 event counters 50 kHz                                        |                                                                                     |

| X67BC6321.L08 | X67 bus controller, 1 PROFIBUS DP interface, X2X Link power supply 15 W, 16 digital channels configurable as inputs or outputs, 24 VDC, 0.5 A, configurable input filter, 2 event counters 50 kHz, M8 connectors, high-density module  |                                                                                     |

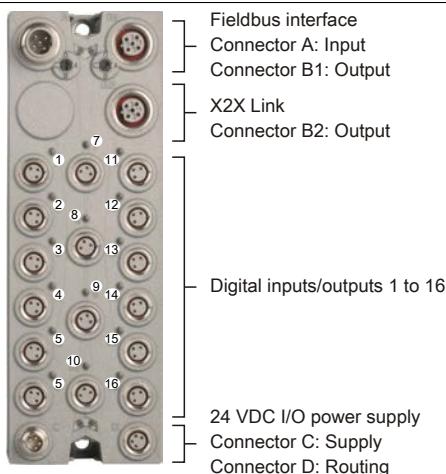

| X67BC6321.L12 | X67 bus controller, 1 PROFIBUS DP interface, X2X Link power supply 15 W, 16 digital channels configurable as inputs or outputs, 24 VDC, 0.5 A, configurable input filter, 2 event counters 50 kHz, M12 connectors, high-density module |  |

Table 3: X67BC6321, X67BC6321.L08, X67BC6321.L12 - Order data

### 1.2.2 Technical data

| Model number                              | X67BC6321                                                                                              | X67BC6321.L08                                                                                           | X67BC6321.L12   |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|

| <b>Short description</b>                  |                                                                                                        |                                                                                                         |                 |

| Bus controller                            |                                                                                                        | PROFIBUS DP V0                                                                                          |                 |

| <b>General information</b>                |                                                                                                        |                                                                                                         |                 |

| Inputs/Outputs                            | 8 digital channels, configurable as inputs or outputs using software, inputs with additional functions | 16 digital channels, configurable as inputs or outputs using software, inputs with additional functions |                 |

| Isolation voltage between channel and bus |                                                                                                        | 500 V <sub>Eff</sub>                                                                                    |                 |

| Nominal voltage                           |                                                                                                        | 24 VDC                                                                                                  |                 |

| B&R ID code                               |                                                                                                        |                                                                                                         |                 |

| Bus controller                            | 0x1436                                                                                                 | 0x1AEB                                                                                                  | 0x1AEC          |

| Internal I/O module                       | 0x1311                                                                                                 | 0x1A1C                                                                                                  | 0x1A1D          |

| Sensor/Actuator power supply              |                                                                                                        | 0.5 A summation current                                                                                 |                 |

| Status indicators                         |                                                                                                        | I/O function for each channel, supply voltage, bus function                                             |                 |

| Diagnostics                               |                                                                                                        |                                                                                                         |                 |

| Outputs                                   |                                                                                                        | Yes, using status LED and software                                                                      |                 |

| I/O power supply                          |                                                                                                        | Yes, using status LED and software                                                                      |                 |

| Connection type                           |                                                                                                        |                                                                                                         |                 |

| Fieldbus                                  |                                                                                                        | M12, B-keyed                                                                                            |                 |

| X2X Link                                  |                                                                                                        | M12, B-keyed                                                                                            |                 |

| Inputs/Outputs                            | 8x M8, 3-pin                                                                                           | 16x M8, 3-pin                                                                                           | 8x M12, A-keyed |

| I/O power supply                          |                                                                                                        | M8, 4-pin                                                                                               |                 |

| Power output                              | 3 W X2X Link power supply for I/O modules                                                              | 15 W X2X Link supply for I/O modules                                                                    |                 |

| Power consumption                         |                                                                                                        |                                                                                                         |                 |

| Fieldbus                                  | 3.8 W                                                                                                  |                                                                                                         | 3.25 W          |

| Internal I/O                              | 2 W                                                                                                    |                                                                                                         | 2.04 W          |

| X2X Link power supply                     | 7.5 W at maximum power output for connected I/O modules                                                | 23.63 W at maximum power output for connected I/O modules                                               |                 |

| Electrical isolation                      |                                                                                                        |                                                                                                         |                 |

| Fieldbus - X2X Link                       |                                                                                                        | No                                                                                                      |                 |

| Channel - Bus                             |                                                                                                        | Yes (PROFIBUS DP and X2X Link)                                                                          |                 |

| Channel - Channel                         |                                                                                                        | No                                                                                                      |                 |

| Certifications                            |                                                                                                        |                                                                                                         |                 |

| CE                                        |                                                                                                        | Yes                                                                                                     |                 |

| KC                                        |                                                                                                        | Yes                                                                                                     |                 |

| UL                                        |                                                                                                        | cULus E115267<br>Industrial control equipment                                                           |                 |

| HazLoc                                    |                                                                                                        | cCSAus 244665<br>Process control equipment<br>for hazardous locations                                   |                 |

|                                           |                                                                                                        | Class I, Division 2, Groups ABCD, T5                                                                    |                 |

| ATEX                                      |                                                                                                        | Zone 2, II 3G Ex nA IIA T5 Gc<br>IP67, Ta = 0 - Max. 60°C<br>TÜV 05 ATEX 7201X                          |                 |

| GOST-R                                    |                                                                                                        | Yes                                                                                                     |                 |

| <b>Interfaces</b>                         |                                                                                                        |                                                                                                         |                 |

| Fieldbus                                  |                                                                                                        | PROFIBUS DP V0                                                                                          |                 |

Table 4: X67BC6321, X67BC6321.L08, X67BC6321.L12 - Technical data

## Technical description

| Model number                                       | X67BC6321                                              | X67BC6321.L08                                                                                                                                          | X67BC6321.L12 |

|----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Design                                             | M12 interface (female connector on module)             | 2x M12 interface for the Y-connector integrated in the module                                                                                          |               |

| Max. distance                                      |                                                        | 1200 m                                                                                                                                                 |               |

| Transfer rate                                      |                                                        | Max. 12 Mbit/s                                                                                                                                         |               |

| Default transfer rate                              |                                                        | Automatic transfer rate detection                                                                                                                      |               |

| Min. cycle time <sup>1)</sup>                      |                                                        |                                                                                                                                                        |               |

| Fieldbus                                           |                                                        | No limitations                                                                                                                                         |               |

| X2X Link                                           |                                                        | 400 µs                                                                                                                                                 |               |

| Synchronization between bus systems possible       |                                                        | No                                                                                                                                                     |               |

| PROFIBUS DP ID                                     | 0x6321                                                 | 0xBC60                                                                                                                                                 | 0xBC61        |

| Terminating resistor                               | Can be optionally screwed onto the Y-connector         | Can be optionally screwed onto the integrated Y-connector                                                                                              |               |

| <b>I/O power supply</b>                            |                                                        |                                                                                                                                                        |               |

| Nominal voltage                                    |                                                        | 24 VDC                                                                                                                                                 |               |

| Voltage range                                      |                                                        | 18 to 30 VDC                                                                                                                                           |               |

| Integrated protection                              |                                                        | Reverse polarity protection                                                                                                                            |               |

| Power consumption                                  |                                                        |                                                                                                                                                        |               |

| Sensor/Actuator power supply                       |                                                        | Max. 12 W <sup>2)</sup>                                                                                                                                |               |

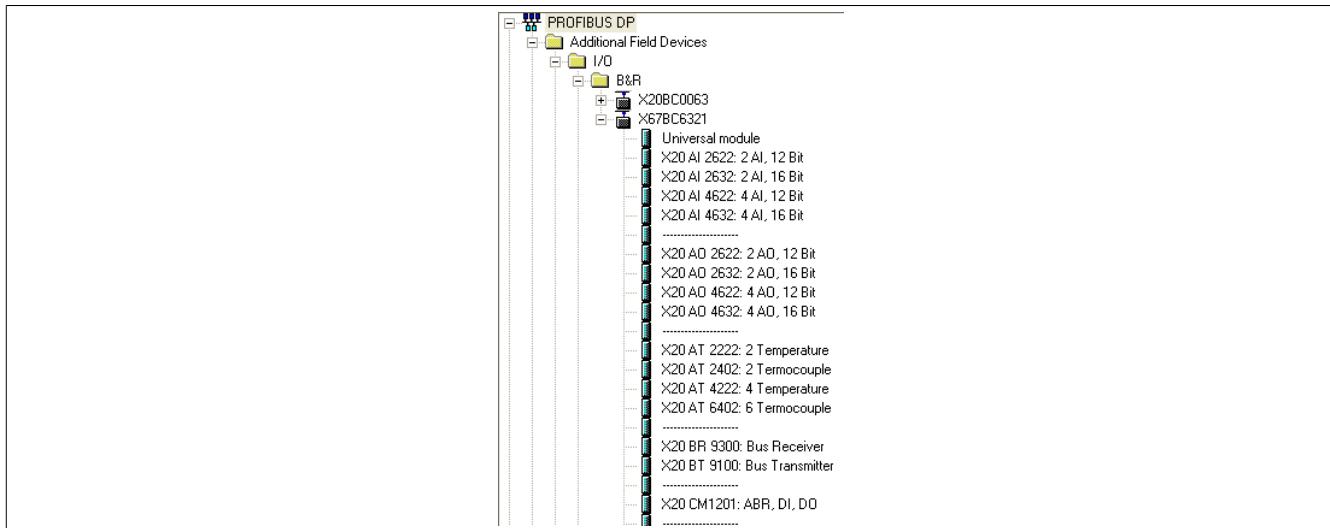

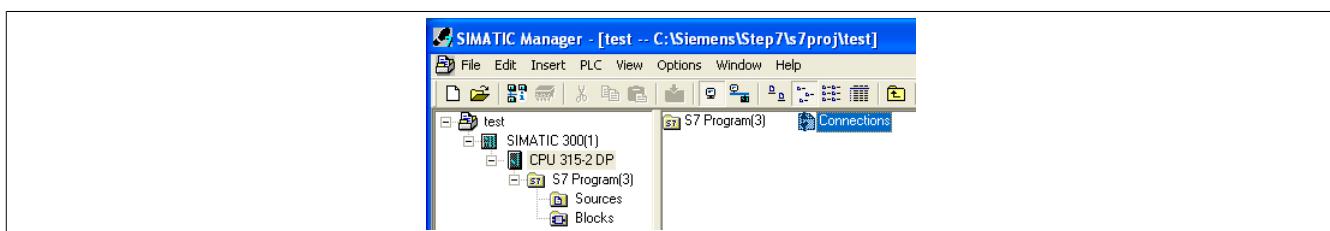

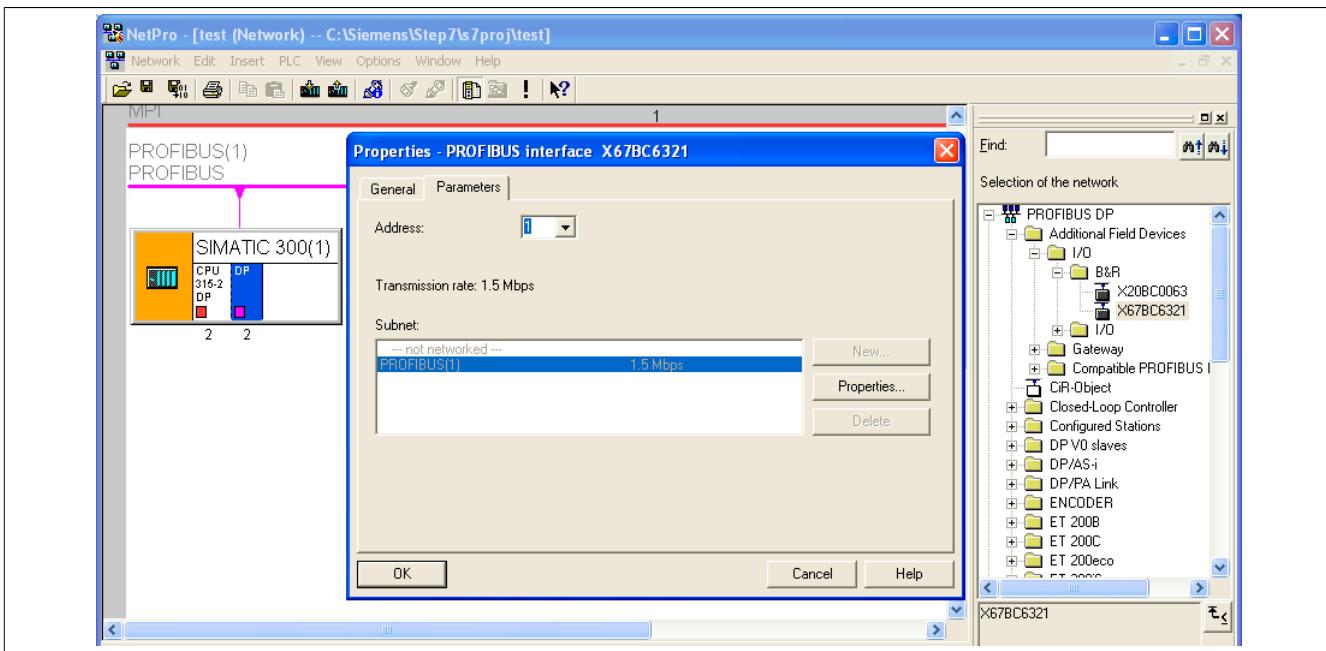

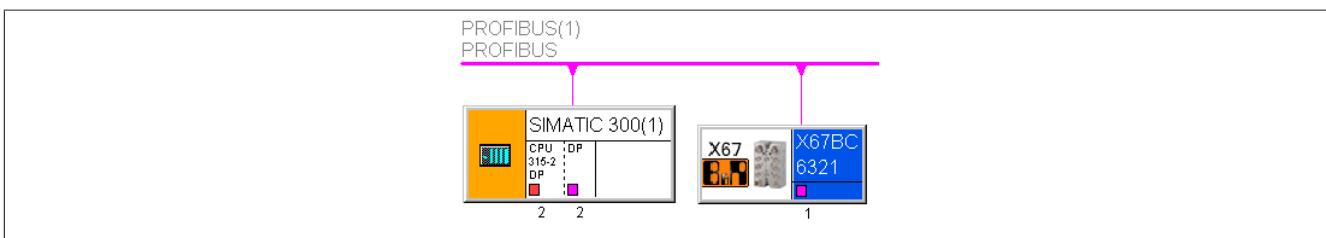

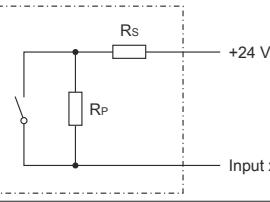

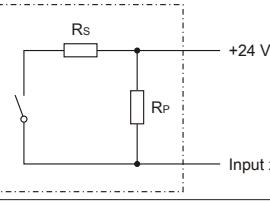

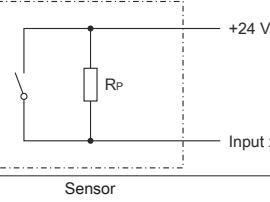

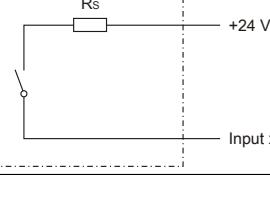

| <b>Sensor/Actuator power supply</b>                |                                                        |                                                                                                                                                        |               |