# COMPUTER DESIGN

THE MAGAZINE OF MODERN DIGITAL ELECTRONICS

96133 7083

# This 16-bit, real-time computer is so fast you can have one in 45 days.

It's our SEL 810A, for high-speed data acquisition and control. All integrated circuits, 3 levels of priority interrupt, 4K memory, teletype, high-speed hardware multiply and divide, real-time I/O structure, and an outstanding software package. Over 50 in the field. Price: \$23,950. Systems Engineering Laboratories, 6901 West Sunrise Blvd., Fort Lauderdale, Florida 33310, Area Code 305 587-2900. Offices also in Washington, D.C.; Los Angeles, California; Boston, Massachusetts; San Francisco, California; Cleveland, Ohio; Houston, Texas; Huntsville, Alabama; and Orlando, Florida.

# Systems Engineering Laboratories

# where will you be in 1973? Five years at Sanders will make you immeasurably more accom-

plished.

Here you will work on new things, designing and building systems to answer yet unsolved problems — significant problems that can change the way we live, perhaps the course of history. To carry out such an assignment you are going to have to find new answers.

Answers in turn raise further questions.

This is progress — cutting a path to what is meaningful through the choking flow of random data that all too often is a substitute for thought.

This is the opportunity at Sanders. Here your role can be personally and professionally rewarding.

WRITE to Mr. T.J. Auger today for career information. The address: Sanders Associates, Inc., Dept. 296 CD, 95 Canal Street, Nashua, New Hampshire 03060.

COMPUTER SYSTEM ENGINEERS ■ DIGITAL DESIGN ENGINEERS ■ PROJ-ECT ENGINEERS ■ PRODUCT DESIGNERS ■ SYSTEM ANALYSTS ■ SYS-TEM PROGRAMMERS - APPLICATION PROGRAMMERS

CREATING NEW DIRECTIONS IN ELECTRONICS

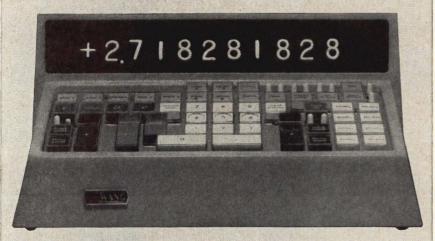

# The world's most versatile PERSONAL CALCULATING **SYSTEM**

# thinks in logarithms... answers in decimals

## THE MODEL 370 GIVES YOU MOST OF THE ADVANTAGES OF A BIG COMPUTER . . . . . . .

- Expandable, random-access core

- Looping, branching, subroutines

- Extraordinary power and versatility

handles statistical computations, simultaneous equations, problems with logs and exponentials, etc.

- Time-sharing fully compatible with standard 320 series for "in-field" expandability

- Extensive software library

- Modular design buy only the functions you need; add more capabilities at any time.

### WITH NONE OF THE DISADVANTAGES

- No major investment required price in upper "calculator" range

- No waiting always available at your fingertips

- No special language needed programs in minutes in simple keyboard format

- No space problems compact keyboard/control console takes little more room than a phone on your desk; small electronics unit takes no more room than a desk drawer and may be located up to 50° away.

Let us tell you more about the extraordinary WANG Model 370. Write for complete data.

CIRCLE NO. 3 ON INQUIRY CARD

DEPARTMENT 1-U, 836 NORTH STREET, TEWKSBURY, MASSACHUSETTS 01876 • TEL. (617) 851-7311

# SALES OFFICES

#### BOSTON

Lindsay H. Caldwell Professional Bldg. Baker Ave. W. Concord, Mass. phone: (617) 369-6660

#### **NEW YORK**

Kaiser, McElwain, Dolbey Advertising Sales, Inc. 60 E. 42nd St. New York, N.Y. phone: (212) YU 6-2654

#### CHICAGO

Robert Dunn 2 N. Riverside Place Chicago, Ill. 60645 phone: (312) 372-6266

Donald C. White 616 Dalton Place Northbrook, Ill. 60062 phone: (312) 272-6459

#### LOS ANGELES

David Barton 672 So. Lafayette Park Pl. Los Angeles 57, California phone: (213) 382-1121

#### SAN FRANCISCO

David Barton 672 So. Lafayette Park Pl. Los Angeles 57, California phone: (213) 382-1121

#### FT. LAUDERDALE

Dan Wiper 2801 E. Oakland Park Blvd. Ft. Lauderdale, Fla. 33308 phone: (305) 563-1376

Publisher and Editor

ROBERT BROTHERSTON

Associate Publisher

ANTHONY SALTALAMACCHIA

Managing Editor

WILLIAM G. KEYWORTH

Editorial Advisers

RICHARD AHRONS

ELI ANFENGER

JAMES R. BRIGHT

GERHARD L. HOLLANDER

BERNARD M. GORDON

WALDRON S. MacDONALD

ROBERT S. SENATOR

HAROLD H. SEWARD

Contributing Editors

T. PAUL BOTHWELL

A. S. BUCHMAN

M. P. de REGT

RUDOLPH J. KADLEC

ROBERT P. FORAN

RICHARD B. LAWRANCE

WALTER A. LEVY

H. S. MIILLER

MADELINE SULLIVAN

Washington Editor HAROLD V. SEMLING, JR.

Art Director

JAMES FLORA

Production Manager TERRY ARMENTI

Tech. Illus. JOHN BROTHERSTON

Editorial Ass't.

PRISCILLA HANNON

Adv. Prod. JOAN WASIUK

Circ. Mgr.

ALMA BROTHERSTON

Vice Pres.-Sales LINDSAY H. CALDWELL

Editorial & Executive Offices Prof. Bldg., Baker Ave., W. Concord, Mass. 01781 Tel. 369-6660

Computer Design is published monthly. Copyright 1968 by Computer Design Publishing Corporation. Accepted as controlled circulation publication at Post Office at Boston, Massachusetts. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS — FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box A, Winchester, Mass. 01890. Subscription rate to nonqualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscribers is \$25.00 per year; \$2.50 per copy.

Circulation over 40,000

# COMPUTER DESIGN

THE MAGAZINE OF MODERN DIGITAL ELECTRONICS

#### **FEATURES**

#### 36 SOLID-STATE CIRCUITS CONFERENCE

Schedule and abstracts of papers of particular interest to Computer Design readers

#### 38 A REVIEW OF DIGITAL DIFFERENTIAL ANALYZERS

A discussion of applications, advantages and disadvantages of digital differential analyzers, how they are designed, programmed and used and recent improvements that make them faster and more accurate.

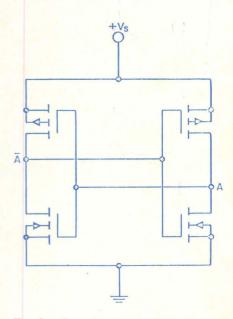

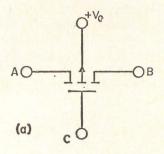

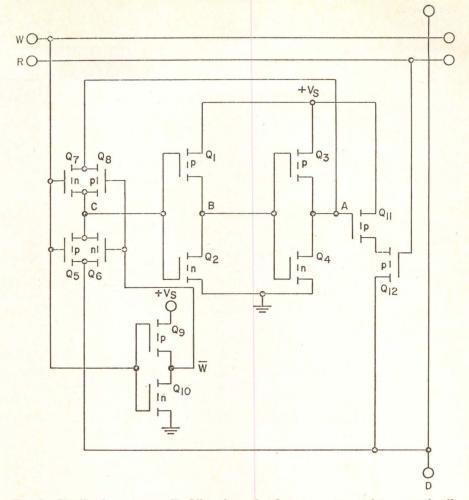

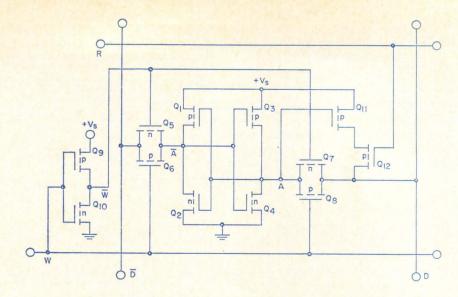

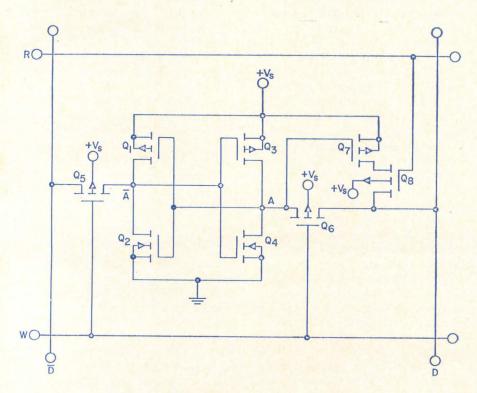

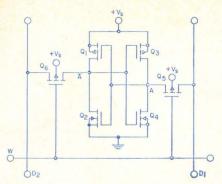

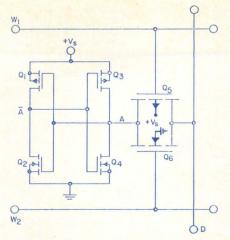

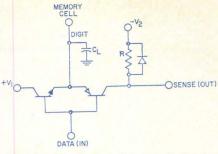

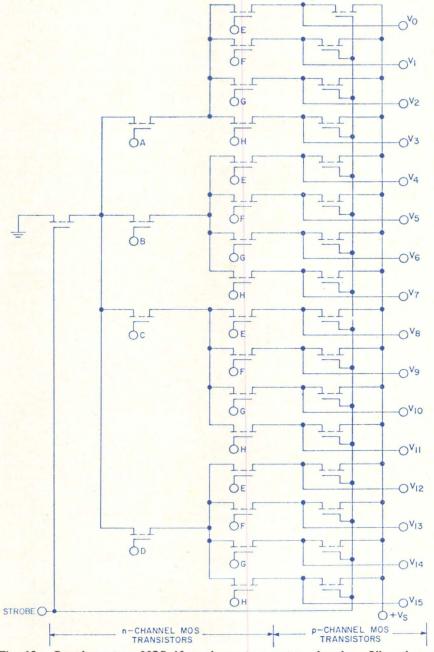

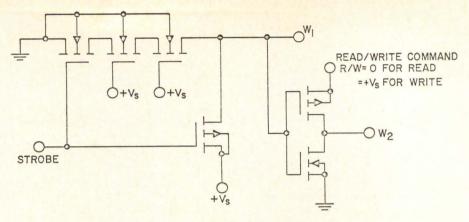

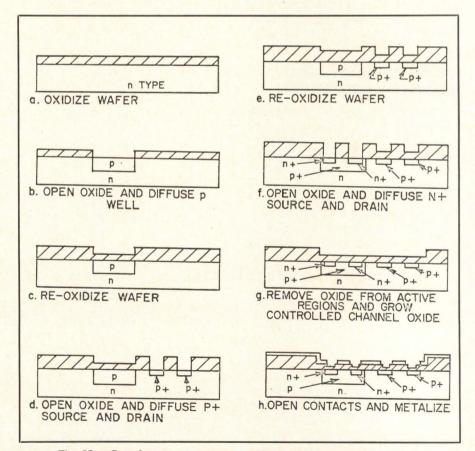

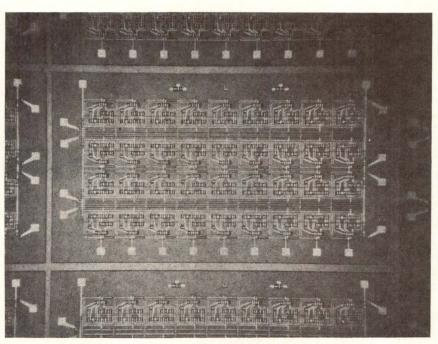

# THE DEVELOPMENT OF A LARGE INTEGRATED COMPLEMENTARY MOS MEMORY ARRAY

Work accomplished toward fabricating a 16-word by 18-digit complementary MOS, memory array, including decoder and word drivers on a single silicon chip is described.

# 56 SIMULATION OF A SMALL LOGIC SYSTEM WITH A FORTRAN PROGRAM

A design problem of a small logic system is used as an example to demonstrate application of a simulation program.

# 62 NEGATIVE RADIX ARITHMETIC PART 8: COMPLEMENTARY ARITHMETIC

In this last part of this series the author points out that the potential of negative radix arithmetic lies in using it to do things that are impractical using conventional arithmetic.

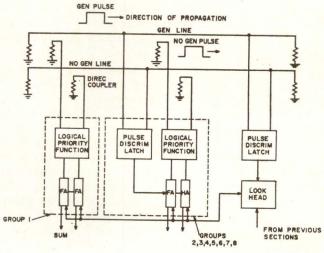

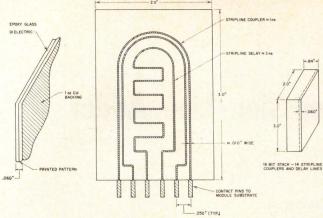

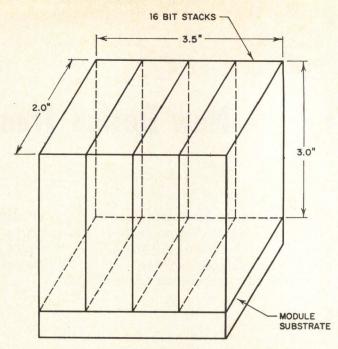

#### 67 A NEW-DESIGN TRANSMISSION-LINE ADDER

Use of directional couplers adds another dimension to logical adder design. Carry propagations are now free of current delays, permitting fast add times without use of additional logical decisions for look-ahead capabilities.

### **DEPARTMENTS**

- 14 CD READERS' FORUM: A COMPATIBLE LOGIC SYSTEM

- 22 CD COMMENTARY: IMPACT OF LSI ON COMPUTER MEMORIES

- 28 INDUSTRY NEWS

- 70 NEW PRODUCTS

- 82 NEW LITERATURE

| Reader | subscription | cards | . opposite   | pg pg | į. 1 |

|--------|--------------|-------|--------------|-------|------|

| Reader | inquiry card | s     | <br>opposite | pg.   | 88   |

# If Brand-Rex is already supplying wire and cable to Burroughs, Control Data, G. E., Honeywell, IBM, NCR, Univac and RCA.

# why are we so interested in making connections with you right now?

Brand-Rex can help make wire and cable procurement the easiest part of your next computer. Here's what we offer:

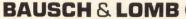

BROAD PRODUCT LINE Brand-Rex is the largest supplier of wire and cable to the computer industry. Our EDP line includes back-panel wires, hook-up wires, miniature air-spaced coaxial cables, power supply wires, patch cord wires, interconnecting and communication cables.

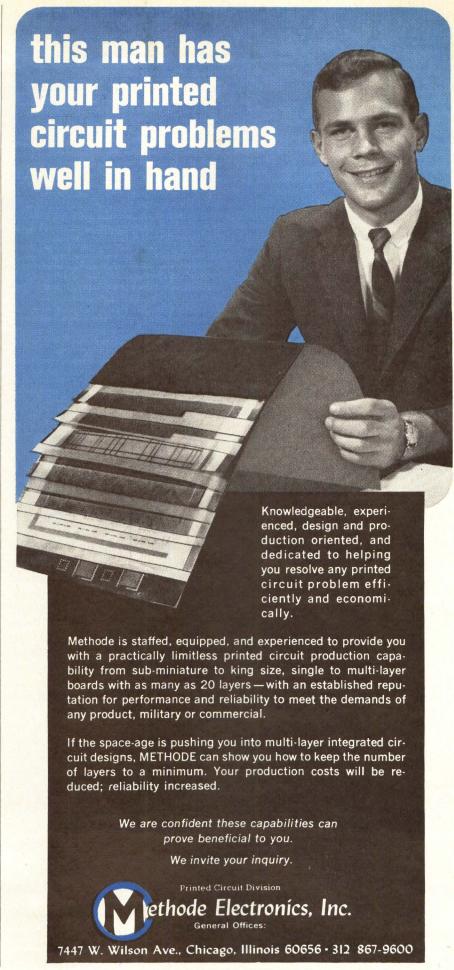

DESIGN CAPABILITY We're probably already making the wire and cable you

need. If not, we can quickly develop new constructions for new applications. The miniature 95 ohm coaxial cable illustrated here was specifically designed for one of the leading data processing systems. Brand-Rex designs cable to standard specifications or to your specific requirements. (Over 3,000 new designs last year alone.)

Any insulation. Any configuration.

U.L. APPROVAL We are well equipped to help you get U.L. approvals. Brand-Rex has more of them on computer wire and cable than any other manufacturer.

ENGINEERING KNOW-HOW With more than 16 years' experience serving the computer field, you'll find our engineers enger and able to work with you — from drawing board to production line. Call Brand-Rex now — while your next design project is only a gleam in your eye

AMERICAN ENTA CORPORATION

BRAND-REX DIVISION WILLIAMSTIC, CONNECTICUT DI PHONE 203 423

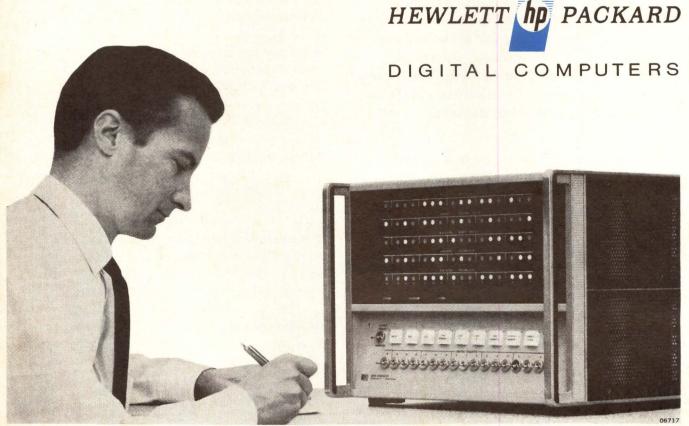

# What good is getting an answer in microseconds

if set-up takes weeks? Computer set-up time is cut from weeks to less than an hour...with the new Hewlett-Packard 2115A. Here's a computer especially designed for fast, simple set-up whether for a scientific computation application or for hooking up a complete computer instrumentation system.

Take the hardware...just use standard plug-in cards, plug in the peripheral cable...and the interface is complete...a snap. The same story of simplicity is true for the software, using standard peripheral drivers. Your system's ready to go to work in under an hour.

The 2115A offers extensive software, including FORTRAN, ALGOL and BASIC compilers and a relocatable assembler. Other features you get with this powerful small computer include 16-bit word length, 2  $\mu \rm sec$  cycle time, 4K or 8K memory; 8 channels of I/O in the main frame, 40 channels with an external extender. The standard plug-in interfaces are offered for all the usual peripherals . . . and general-purpose interfaces are available for your particular I/O devices.

Price, including Teleprinter, \$16,500.

Make your move now toward time-saving, work-saving computer set up. You can do it with a call to your local HP field engineer. Or get all the information by writing Hewlett-Packard, Palo Alto, California 94304; Europe: 54 Route des Acacias, Geneva.

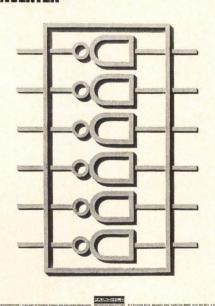

# The great LSI race.

While the rest of the semiconductor industry tried to squeeze enough ICs on a chip to get into the MSI/LSI business, Fairchild turned systems inside out. We were looking for an intelligent alternative to component mentality. Our investigation led to a whole new set of design criteria for medium and large scale integration devices.

# A computer isn't a computer.

It's a digital logic system. It has the same functional needs as any other digital system: control, memory, input/output and arithmetic. There's no logical reason to custom design a complex circuit for each system. That's why Fairchild MSIs and LSIs are designed to function as fundamental

building blocks in any digital logic system. Even if it's a computer.

# A little complexity goes a long way.

Anybody can package a potpourri of circuitry and call it MSI or LSI. But, that's not the problem. Why multiply components, when you should divide the system? Like we did. We found that sub-systems have a common tendency toward functional overlap. There are too many devices performing similar functions. More stumbling blocks than building blocks. Our remedy is a family of MSIs and LSIs with multiple applications. The Fairchild 9300 universal register, for example, can also function as a modulo counter, shift register, binary to BCD shift converter, up/down counter, serial to parallel (and parallel to serial) converter, and a half-dozen other devices.

# Watch out for that first step.

There are all kinds of complex circuits. Some of them have a lot of headache potential. Especially if you want to interface them with next year's MSIs and LSIs. We decided to eliminate the problem before it got into your system. All Fairchild building blocks share the same compatible design characteristics.

We're also making the interface devices that tie them together. For example, our 9301 one-of-ten decoder can be used as an input/output between our universal register, dual full adder

and memory cell.

(It could also get a

job as an expandable

digital demultiplexer,

minterm generator

or BCD decoder.)

# Hurry. Before the price goes down.

Gate for gate, today's complex circuits are about the same price as discrete ICs. But, by the time you're ready to order production quantities, the price should be a lot lower. At least ours will. The reason is simple: Fairchild devices are extremely versatile. There are fewer of them. But, they do more jobs. That means we'll be producing large quantities of each device. That also means low unit cost to you. And you'll have fewer devices to inventory. And fewer to assemble.

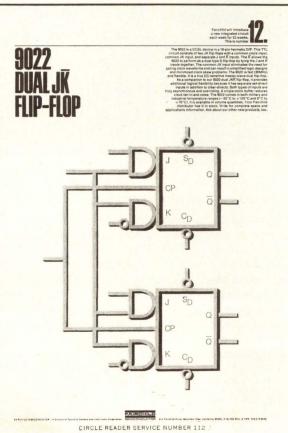

If you agree with our approach to medium and large scale integration, we'd like to tell you more about it. There are two ways you can get additional information. One is by mail. Simply write us on your company letterhead. You can also get more data by watching the trade press. Fairchild is introducing a new integrated circuit each week for 52 weeks. (We started on October 9, 1967.)

Many of them

Many of them

will be MSI and LSI.

If you'd like to

see the last few

we've introduced,

turn the page.

#### FAIRCHILD SEMICONDUCTOR

A Division of Fairchild Camera and Instrument Corporation 313 Fairchild Drive, Mountain View, California 94040 (415) 962-5011, TWX: 910-379-6435

# RECAP:

9112 HIGH LEVEL HEX CONVERTER

The BTT is part of our new tamby of high noise immunimental part of our new tamby of high noise immunimage part of the part of the part of high noise immunmental part of the part of the part of high noise immuniness part of the topic layers and the part of the part of the part of the single immension personnel mindred case in community a 0.0 to 20 yi operates from 0°C to +70°C. It comes in an termelic of intering package and it available in volving quantities. Facility distribution have in in stack new Write for complete pages is application information. All about our other new products.

CIRCLE READER SERVICE NUMBER 106

9989 FOUR-BIT BINARY COUNTER The 1988 is a low-cast. Night as model to counter in genting with preset opposition, in a congestion entire. So, the low-cast support in the congestion entire. So, the low-cast congestion of the Congestion constraint presenting in the congestion of the congestion constraint present on the congestion of the congestion of the constraint present on the congestion of the COP Primary applications of coulder counters, went on the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of the congestion of the congestion of the studies of the congestion of th

CIRCLE READER SERVICE NUMBER 107

µA719 HIGH FREQUENCY COMMUNICATIONS SYSTEM acch week for 52 weeks.

The µAT9 is a new linear integrated circuit for military are integrated properties. It is a further in a set of the properties of t

AGC QUAD

NAG CENTRE SAIL FRANCES CONSESSES BENEGONOSIONED SES FANCES NUMBER 108

CIRCLE READER SERVICE NUMBER 108

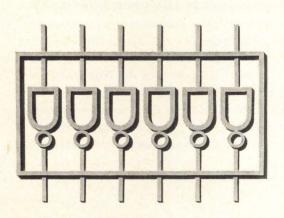

9935 EXPANDABLE HEX INVERTER Such classes (1) to the second of the second

CIRCLE READER SERVICE NUMBER 109

Fairchild is introducing a new integrated circuit every week. The last two months look like this.

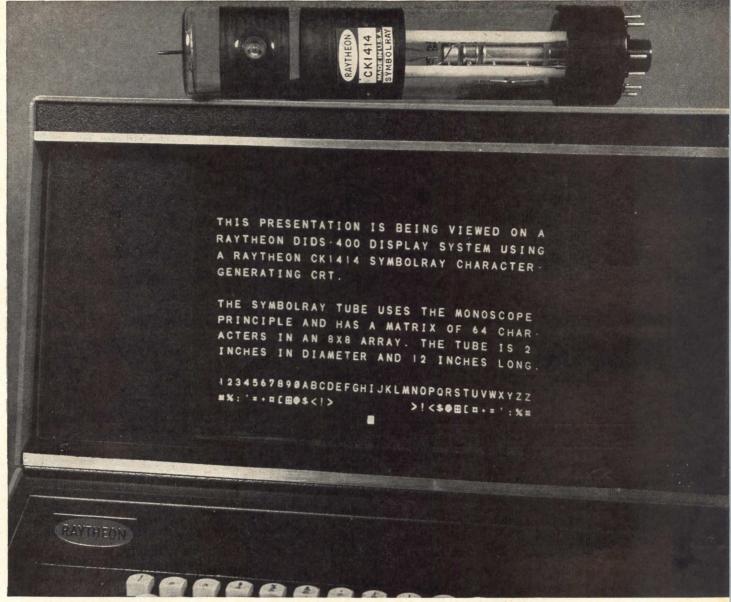

# Data Display Devices from Raytheon

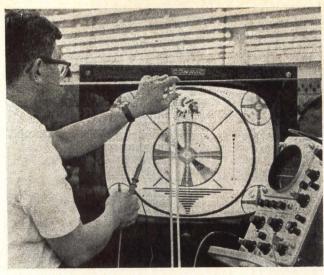

The presentation you see above was generated by a Symbolray\* Cathode Ray Tube identical to the one lying on the console. A new type of monoscope, the Symbolray can generate alphanumerics from electrical signals for cathode-ray display or for hard copy print-out. The presentation here is shown on a Raytheon tube (CK1415) used in a Raytheon DIDS-400 display system.

An economical method of generating characters. Priced at less than \$100 in quantities of 1,000, the Symbolray provides a more economical method of generating

electronic displays than using large numbers of circuit cards.

The output of the Symbolray operating as a monoscope is obtained by electrically deflecting the electron beam to desired characters on the target and scanning them sequentially with small raster. The display cathode ray tube on which this output is viewed is scanned in synchronism. When the Symbolray method is used in conjunction with buffermemory techniques, full messages can be displayed — as shown above. The Symbolray tube uses electrostatic deflection and

focus, and is available in designs with 64 and 96 character matrices.

Raytheon's wide range of Dataray\* CRTs cover the screen sizes from 7 to 24". Electrostatic, magnetic and combination deflection types are available for writing alphanumeric characters while raster scanning. Raytheon also offers combination deflection or "diddle plate" types and all standard phosphors. Or, Raytheon can meet your special CRT design requirements.

For more information—or a demonstration—call or write your Raytheon regional sales office.

Cathode-Ray Projection Tube. A new family of Projectoray\* CRTs provide high quality projection of television or other displays. As compared with more conventional projection tubes, the Projectoray provides substantial improvement in life and brightness without sacrifice in picture quality.

These devices are available in designs which utilize refractive optics or Schmidt optics, with one special design using a Schmidt spherically-curved mirror built within the cathode-ray tube.

The high light output and long life—more than 500 operation hours—are due to novel design. The phosphor screens are deposited on thermally conductive materials capable of being cooled readily by air flow or liquid cooling techniques to inhibit screen burning. The final display will provide 15 footlamberts on a 3-foot by 4-foot lenticular screen, permitting operation of the projection system in a lighted room.

Dataray\* Cathode Ray Tubes. Raytheon makes a wide range of industrial CRTs—including special types—in screen sizes from 7" to 24". Electrostatic, magnetic, and combination deflection types are available for writing alphanumeric characters while raster scanning. All standard phosphors are available and specific design requirements can be met. Combination deflection or "diddle plate" types include CK1395P (24" rectangular tube), CK1400P (21" rectangular), and CK1406P (17" rectangular).

Datavue\* Side-view Tubes. Type 8754 with numerals close to the front, permits wide-angle viewing. These sideview, in-line visual readout tubes display single numerals 0 through 9, preselected symbols, + and - signs, and decimal points. Their 5/8" high characters are easily read from a distance of 30 feet. Less than \$5 each in 500 lots, they can be supplied with lacquer coating to eliminate the need for expensive filters. Datavue types are interchangeable with NL840, 841, 842, 843, and 848 tubes.

Datavue\* End-View Tubes. Raytheon makes round (CK8421) and rectangular (CK8422) Datavue indicator tubes on automated equipment capable of high production rates and top quality. The CK8422 rectangular tube is also available with decimal point, ± symbols, and in other special versions. Both round and rectangular types fit existing sockets and conform to EIA ratings. These ultralong-life tubes are designed for 200,000 hours or more of dynamic operation.

Recording Storage Tubes. The two new designs shown utilize miniaturized guns and necks to provide high deflection and focus sensitivity, resulting in savings in coil and power supply weight and size. They provide Kiloline resolution, long storage and fast erase capability. The single-gun version is Type CK1537 and the dual-gun version is Type CK1535.

Raytheon's complete line of electrical-output storage tubes feature high resolution and non-destructive reading. Information can be written and stored by sequential techniques or by random-access writing. Complete, gradual or selective erasure is possible.

Raytheon storage tubes are readily available for applications in radar scan conversion, slow-down video, signal processing, signal enhancement, time delay, and stop motion.

Send Reader Service Card for literature on the:

| are on the.             |    |

|-------------------------|----|

| Symbolray CRT           | 50 |

| Projectoray CRTs        | 51 |

| Datavue Indicator Tubes | 52 |

| Recording Storage Tubes | 53 |

| Dataray CRTs            | 54 |

|                         |    |

Or call your Raytheon regional sales office. Or write to Raytheon Company, Components Division, Quincy, Mass. 02169.

\*Trademark of Raytheon Company

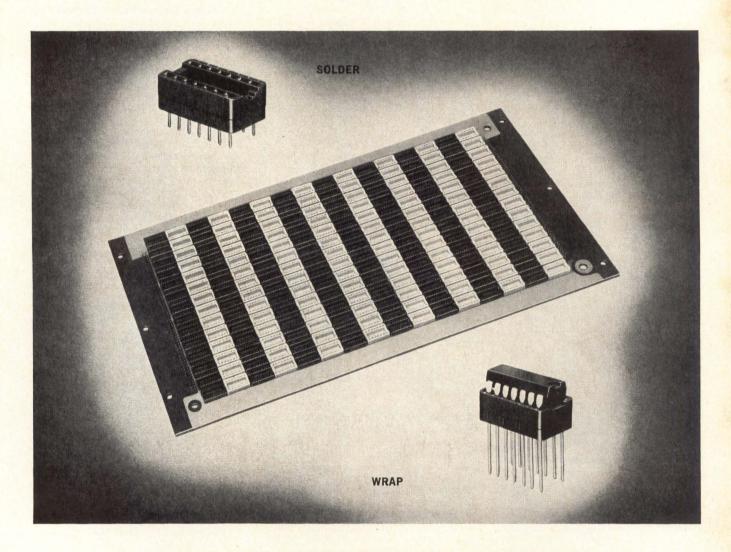

# Now, sockets & systems from Texas Instruments.

LOW COST - HIGH RELIABILITY.

LOW PROFILE - HIGH DENSITY.

YOUR BEST BUY IS TI.

TI MATERIALS DIVISION, ATTLEBORO, MASS. 02703.

# TEXAS INSTRUMENTS

INCORPORATED

CIRCLE NO. 7 ON INQUIRY CARD

Now, all of the advantages of the well-known "Cradle" Relay—a time-proven design—plus the benefit of Underwriters' Laboratories Component Recognition. Available in 4PDT and 6PDT, the TU154 is intended for applications in industrial control and data processing systems, where long life, reliability and maximum economy are needed. Send for complete details and brochure today.

Allied Control Co., Inc. 2 East End Ave., New York, N.Y. 10021 • (212) 288-7403

88-7403 TU 154

Component—Switches, Magneticality Operated.

Allied Control Co. Jac.

3 S. End Are. New York, N. Y. 1002.

the Park of the Control of the Con

# hat do you think?

# CD READERS' FORUM

# **COMPATIBLE LOGIC SYSTEM**

by R. E. Connally

Editor's Note: The following letter and accompanying article have proven to us that an industrywide standard for logic symbols is still a vital issue.

#### Gentlemen:

I have been on your subscription list since February of this year and have been following your "Readers' Forum" sequence on Logic Symbol Standard with great interest. I was disappointed when I read your October issue in which you mention your long campaign for an industry-wide standard is no longer considered a vital issue.

With new textbooks being written every day and the great proliferation of integrated circuit logic modules into commercial and consumer products, a single, easily understood logic symbol standard is vitally needed, now! To this end I would like to submit the following letter to your "CD Readers' Forum" section.

Very truly yours, R. E. Connally Research Associate Radiochemical Analysis Battelle Northwest Battelle Memorial Inst. Richland, Wash. The long-standing debate over a logic symbols standard need not be resolved by the acceptance of one standard and the rejection of the other. The two logic symbols standards now in use can be compatible with each other if we follow a few simple rules:

- 1. The distinctive shape symbols of the Military Standard 806B will be used.

- 2. The rules of USA Standard Y32.14 will be followed, with certain restrictions.

- a. The 1-state will be high (H) (POSITIVE LOGIC).

- b. The logic negation symbol will also indicate that a low (L) level is required to implement an input or that an output is low (L) when implemented.

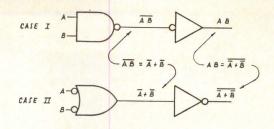

- 3. When signal lines are labeled with English titles we must recognize that the English title is negated whenever we pass through the logic negation symbol, in entering or leaving a logic symbol. For example in Case I of Figure 1 we negate the literal after we have applied the AND connective. In Case II we take the negation of the literals A and B before we combine them with the OR connective.

With these restrictions on the Y32.14 Standard the resulting logic diagram can't be distinguished from a logic diagram based on the 806B Standard. Those who prefer 806B can continue to use their familiar symbols. Those

who prefer Y32.14 will recognize we have utilized the wide flexibility incorporated into this standard to implement the compatible logic system. Those who have no strong attachment to either standard should welcome a settlement to the logic standards dispute if a compatible logic system were to find industry-wide accep-

tance.

The suggested restrictions for Y32.14 are taken from the following USAS Y32.14 paragraphs:

Either the distinctive shape or the uniform shape symbols are allowed in paragraph 1.2.1. Paragraph 6.9.1 specifies a triangular symbol for an amplifier where the gain can be of any value and of either sign. A gain of —1 is included in this set, therefore our inverting amplifier symbol can be identical to the 806B triangle. Paragraph 4.4.4 allows us to omit the small, filled (high level indicating), right triangle if it is understood we are using "Positive Logic". From Appendix D we find the low level indicator may be replaced by its opposite kind and adjacent small circle (logic negation symbol). This results in the small circles indicating a low activating level and lines without small circles indicating a high activating level as in Standard 806B.

In order to obtain universal interpretation of Boolean statements taken from separate logic diagrams, it is preferred that we assign English titles as follows:

1. The assignment for gate outputs which are low when implemented should show the entire output expression as negated. And, conversely, we should not negate the entire expression for outputs which are high when implemented.

2. When the English title is a single letter the Boolean assignment is straight forward. The output of a gate, flip flop or single shot which is high upon implementation is assigned the English letter. The output which is low upon implementation is assigned the negated English letter.

As an example of preferred English titles, in Figure 1 we have shown a logic gate followed by an inverter. Let us examine this condition in more detail by use of Case I, Case II and their truth table. For Case I the ouput is low when implemented and for Case II the output is high when implemented. However, we see from the truth table that only one gate is implemented for any particular input combination, the other gate is not implemented. The output of the implemented gate will take on the level indicated by its output line (low for a small circle, high otherwise). The nonimplemented gate will have an output level opposite to that indicated by its output line. Thus, the two gates not only have opposite indicated output levels, but when one is implemented, the other is not implemented. The net result is identical electrical outputs with equal Boolean expressions. However the form of the English titled output is a function of the logician's original choice of logic symbol.

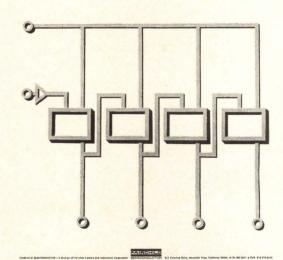

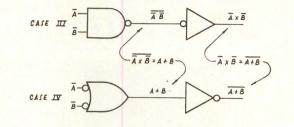

When drawing a logic diagram from a circuit diagram the logician must recognize that each gate can be represented by two equivalent logic symbols which follows from DeMorgan's Theorem as shown in Figure 2. We have found this transition to involve three steps in sequence as follows: A FAIRCHILD #94G GATE, FOLLOWED BY AN ELECTRIC INVERTER

|                      | A INPUT | B INPUT | GATE OUTPUT | INVERTER OUTPUT |

|----------------------|---------|---------|-------------|-----------------|

|                      | L       | L       | Н           | 4               |

| CASE II IMPLEMENTED  | L       | Н       | Н           | L               |

|                      | H       | L       | Н           | L               |

| CASE I IMPLEMENTED { | H       | Н       | L           | Н               |

TRUTH TABLE OF A #946 LOGIC GATE, CASE I & CASE II

Fig. 1. Examples of Boolean assignments.

EXAMPLES OF CONVERTING HARDWARE TO LOGIC SYMBOLS

| HARDWARE                                                            | LOGIC SYMBOL PAIR   |

|---------------------------------------------------------------------|---------------------|

| O OP +GV H 2K 1.75 K 6K  O OP +GV H S FAIRCHILD 94G 1/NTESPATED CKT |                     |

| D OR +GV NORTHERN SCIENTIFIC                                        |                     |

| 0 0R +10V 4.7 K<br>0 0R +10V 5.6 K \$18 K<br>R 1 D L -10V 7         |                     |

| O DP 7GV NORTHERN SCIENTIFIC                                        |                     |

| 0 0P + GV 4GV 27.7K 3.9K 250pF 100K VICTOREEN                       | -\sum_{i} -\sum_{j} |

Fig. 2. Examples of converting hardware to logic symbols.

# INVAC

DUPLICATORS,

VERIFIERS,

and CODECONVERTERS

INVAC Off-Line Tape Preparation Systems, Series \$10-\$50 combine the capabilities of standard INVAC Tape Punches, Readers, and associated electronic logic circuitry to duplicate, verify, or code convert using any tape material or code.

- . . . Optional Editing Switches

- . . . Optional Parity Error Detection

- ... Optional Blank Skip

- . . . Optional Code Delete Skip

- ... Optional Character Recognition

- . . . Optional Tape Rewind Panel.

HIGH SPEED KEYBOARD enhances system versatility. Makes new tape. Edits existing tapes.

Write for data

CORPORATION

26 Fox Road, Waltham, Massachusetts 02154 Tel. (617) 899-2380

PHOTOELECTRIC KEYBOARDS • TAPE PUNCHES

READERS AND HANDLERS • I/O TYPEWRITERS

PRINTERS AND SYSTEMS

CIRCLE NO. 9 ON INQUIRY CARD

- 1. The logician must first decide whether he wants to consider the logic gate as performing and AND or an OR function. Once selected, the proper symbol is drawn.

- 2. The inputs are analyzed one at a time to determine the electric level which implements the logic function selected. If a low (L) input implements the function, the logic negation symbol is used to show that a low (L) electric level is required for implementation. If a high (H) input implements the function, no special symbol is required on the input line.

- 3. The output of the logic circuit is analyzed to determine the output electric level which results when the gate is implemented. The logic negation symbol is used to indicate a low (L) output when implemented. If the implemented output is high (H) no special symbol is required on the output line.

### **DEFINITIONS**

**DeMorgan's Theorem** DeMorgan's Theorem changes the form and not the value of a Boolean expression and is implemented as follows:

- 1. Add parentheses around all product terms.

- 2. Negate the entire function.

- 3. Change all connectives (exchange all x for + and all + for x).

- 4. Negate each literal. For example: AB + CD = (AD) + (CD) =  $(\overline{\overline{A} + \overline{B}}) (\overline{\overline{C}} + \overline{\overline{D}})$

Implement To implement is to satisfy the input conditions which are indicated by a particular distinctive shape logic symbol. A logic gate will have the indicated output level when implemented and the opposite level when not implemented.

Literal An alphabetic letter or combination of letters (sometimes an acronym or a mnemonic sequence) used to indicate a Boolean variable.

Logic Negation Symbol A small circle drawn at the point where a single line joins a logic symbol indicates a logic negation.

NAND Gate A logic gate with a low output only when all inputs are high. Symbol (a) of Figure 2.

NAND/NOR Gate Any AND or OR logic gate with a negated output. Symbols (a), (b), (e) and (f) of Figure 2.

Negation The negation of a binary variable x is the opposite of x, written either x' (x-prime) or x (x-bar). x is also called not x.

NOR Gate A logic gate with a low output when at least one input is high. Symbol (e) of Figure 2.

Positive Logic If all signal line terminals in a logic diagram have the same pair of physical states, and if both are electric potentials or currents, and if the more positive is consistently selected as the 1-state, the diagram is said to have positive logic.

Truth Table A tabulation of all possible input level combinations and their resulting output level.

# NEW FROM MICRO SWITCH solid-state-encoded keyboard assemblies

Complete keyboards—assembled, encoded, and ready to interface with your equipment.

These new keyboards feature reliability, flexibility and customized appearance that will give new sales appeal to your equipment. Exclusive new solid-state encoding and dry reed switch input assure your user the maximum in up time, and these features assure you the

minimum in maintenance.

You get a wide choice of customdesign opportunities to reduce your engineering and production costs. A unique new electronic interlock to increase operator speed and efficiency over existing approaches. An electronic strobe to delay the read cycle until the output is stabilized. Input flexibility to match your requirements. MICRO SWITCH capabilities provide efficient factory assembly techniques to give you a customized keyboard at a price competitive with fixed format keyboards.

When you think of keyboards, think of MICRO SWITCH. Our Field Engineers can be a valuable asset to your design team. Call a Branch Office today. Or write for complete information.

## MICRO SWITCH

FREEPORT, ILLINOIS 61032

A DIVISION OF HONEYWELL

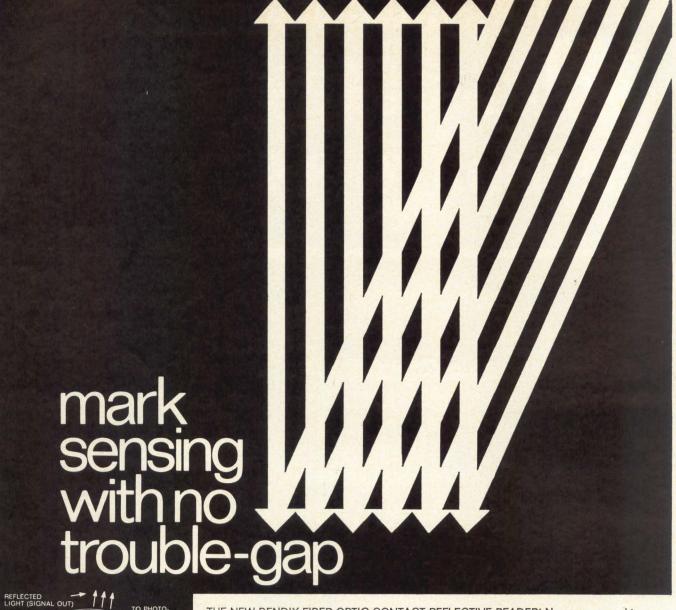

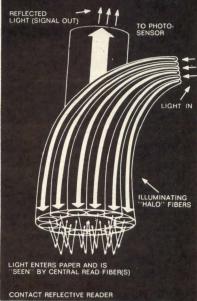

THE NEW BENDIX FIBER OPTIC CONTACT REFLECTIVE READER! Now you can achieve a new consistently reliable, extraordinarily high level of efficiency in your data processing mark-sensing, punch tape reading and magnetic tape monitoring. Efficiency in signal-to-noise ratio of 100:1. The answer: the unique, new fiber optic read head developed by Mosaic — it rides in contact with the paper!

The Mosaic fiber optic reflective reader components are based on a new discovery by Mosaic: that with certain fiber sizes and bundle configurations, very high signal-to-noise ratios can be achieved with the sensor head in contact with the paper. A special fused flexible fiber bundle was designed and fabricated to utilize the phenomenon: a central core of read fibers .008" in diameter, surrounded by a halo of thirteen .003" illuminating fibers. The result is the elimination of the trouble-gap in mark-sensing: the critical gap ordinary fiber optic readers need to angle light onto the work so it can reflect back into the pick-up fibers.

Gone with the gap is the troublesome collecting point for dirt carried by the paper: contaminants that cause rapid degeneration of signal-to-noise ratios and resultant sensor errors. Gone, too, are the clear epoxy or transparent plastic gap-fillers utilized with ordinary read heads — compromisers at best which do nothing to increase efficiency. Dramatic efficiency. Consistent, superior performance with signal-to-noise ratios of 100:1. Reliability never possible before. This is what you achieve with the new fiber optic contact reflective reader from Mosaic — the largest single source of fiber optic technology in the world. Contact Mosaic Fabrications Division, The Bendix Corporation, Galileo Park, Sturbridge, Massachusetts 01518. Telephone: 617/347-9191.

**Electronics**

CIRCLE NO. 11 ON INQUIRY CARD

Write for complete descriptive literature, today!

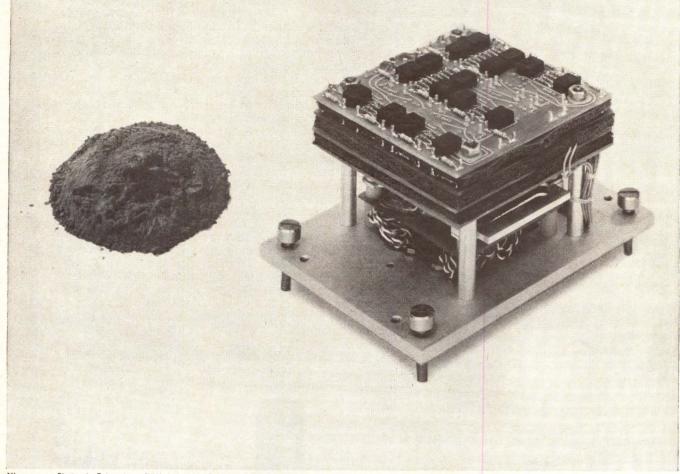

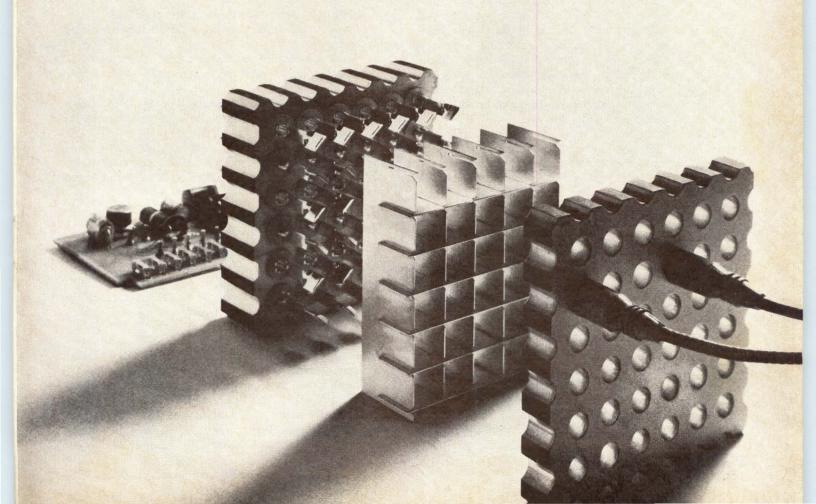

# How do you gruntle the buyer of memory stacks?

# (Take a powder and control it all the way).

The man who buys memory stacks (or planes or just cores) knows that a myriad of tiny variables which affect performance can pass right through the tightest spec. It's nobody's fault, but still it leaves the buyer disgruntled.

How to gruntle him? Well, this is what we do at Ferroxcube. We control the entire process from formulation of the powder for the cores to the planes or stacks that go out the door. To the naked eye

QC procedure. But some of it goes deeper. It's the kind of control you associate with a veteran airline pilot whose experience amounts almost to intuition. As pioneers in ferrites and core memory compo- stacks, talk with the people who nents, we have people like that in pioneered ferrite technology. As control at every vital stage of man- a conversation piece, a sheaf of ufacture.

This is one reason why Ferrox- Write for it today. acting requirements (example: Ferroxcube military stacks that exceed the en- Saugerties, New York

much of this looks like textbook vironmental requirements of MIL-E-16400 and MIL-E-5400). And it's the main reason why every production unit performs like the prototype you approved.

> If you specify cores, planes or technical literature awaits you.

Albuquerque—Electronic Enterprises, (505) 256-1585; Baltimore—Eastern Components, (301) 322-1412; Dayton—(513) 253-3158; Encino, Cal.—(213) 788-2060; Englewood, Col.—(303) 771-2000; Houston—Noakes Engineering, (713) 529-6213; Irving, Texas—Noakes Engineering, (214) 255-0441; Lansing, Mich.—(517) 482-7140; Minneapolis—(612) 888-4681; Northlake, III.—(312) 261-7880; Orlando—(305) 841-6380; Philadelphia—Eastern Components, (215) 927-6262; Phoenix—(602) 265-1792; San Francisco—Wm. J. Purdy Agents, (415) 863-3300; Saugerties, N. Y.—(914) 246-2811; Union, N. J.—(201) 964-1844; Waltham, Mass.—(617) 899-3110; Toronto, Ontario—Philips Electron Devices, Ltd., (416) 425-5161.

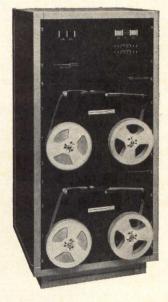

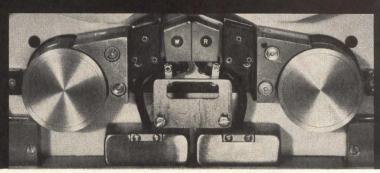

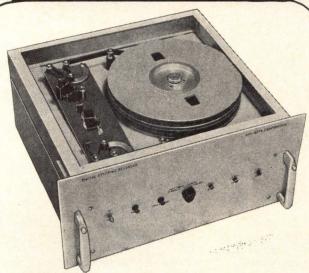

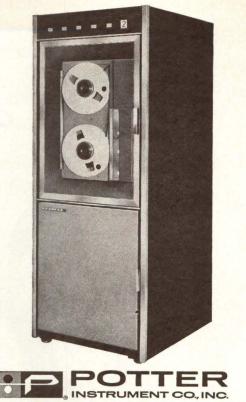

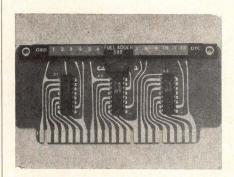

# IBM STARTED SOMETHING WITH ITS DUAL-CAPSTAN TAPE DRIVE.

# (MIDWESTERN FINISHED THE JOB.)

In the field of high performance digital tape transports for use with computer systems, there are really only four names to consider: IBM, Midwestern Instruments, Ampex and Potter. If it's an IBM system you're working with, there are only two logical choices: IBM and Midwestern. If data reliability to the order of 109 data bits is any criteria, there's only one choice: Midwestern's 4000 series transport.

Both IBM and Midwestern tape transport designs utilize a rapid-response, dual-capstan drive. This eliminates the necessity for programmed delays which are required by single-capstan drive systems. But not even IBM's original equipment can equal the trouble-free performance, the extended tape life and the data reliability of the patented, positive-pressure dual-capstan drive developed by Midwestern.

Midwestern's 4000 series transports cover the complete range of operating speeds required by various computer systems, from a low of 25 ips to a high of 150 ips, at bit densities of 200, 556 or 800 bpi (1600 bpi on special order). These units can be provided in either 7 track or 9 track configurations, and all are available to interface with either discrete component or integrated circuitry.

These Midwestern 4000 series transports and IBM original equipment units are the *only* field-proven IBM-compatible digital tape transports—the only units actually working on line with IBM computers at various customer installations. What's more, no other unit (*including* IBM) can guarantee data reliability in the order of one transient error per 109 data bits. If the 4000 series can out-perform IBM units on their own computing systems, doesn't it stand to reason they're the best choice for *your* system application?

If you'd like to hear more about our 'small wonder' 4000 series digital tape transports, just give us a call (collect) at 918-627-1111. We're programmed for fast analysis of any digital tape transport application, no matter how unique.

MIDWESTERN TELEX

6422 E. 41st STREET • TULSA, OKLAHOMA 74135 PHONE (918) 627-1111 • TWX (918) 627-6030 • TELEX 049-589 A SUBSIDIARY OF THE TELEX CORPORATION

MIDWESTERN INSTRUMENTS, INC.

CIRCLE NO. 13 ON INQUIRY CARD

# DATA COMMUNICATIONS

equipment for on-line, real-time processing

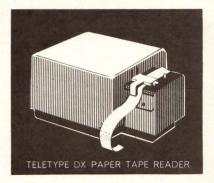

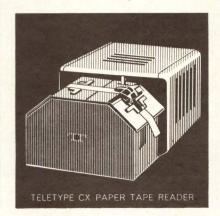

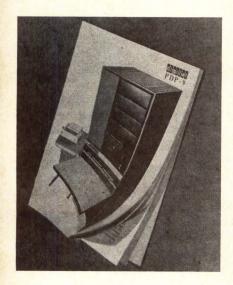

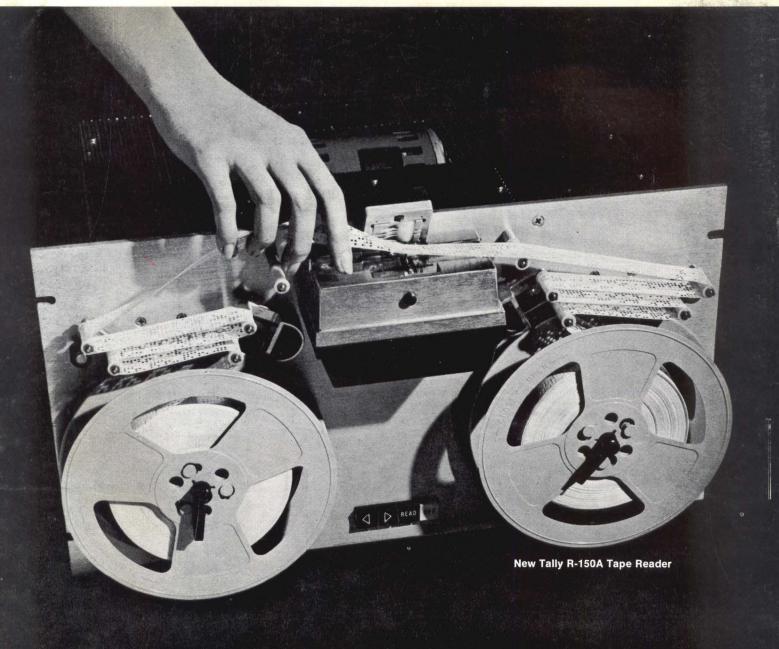

# two talented tape terminals

Input of taped data at high speeds into computers and other business machines is just one of the many applications of Teletype CX and DX paper tape readers. These units also are used as the sending terminals of high-speed tape-to-tape systems to transmit data collected by slower speed equipment. Data is sent vast distances accurately, automatically.

#### OPERATING SPEEDS

The Teletype DX reader generates parallel-wire signals. Equipped with step-by-step feeding, the DX reader operates at any speed up to 240 characters per second (2400 words per minute) without modifications.

machines that make data move

Operating speed of the CX reader is 105 char/sec (1050 wpm). It generates parallel-wire signals that may be converted externally to sequential signals by Teletype electronic storage and conversion equipment.

Both readers are capable of sending 5, 6, 7, or 8-level coded data including the official United States of America Standard Code for Information Interchange (ASCII). They also may be equipped to control computers, buffer storage units, and other electronic register elements.

#### ASSURES LONGER LIFE

These Teletype readers utilize precision machined parts and rubber motor mounts to permit quieter operation and longer life. A TAUT TAPE mechanism can stop the readers

until the tape is slackened. A TAPE OUT switch automatically can stop the readers at the end of tape.

The CX reader has a pulse generator that provides synchronization to accurately control timing of code intelligence to associated equipment.

Both readers are available as selfcontained units or can be mounted in upright cabinets with driving electronics for use as sending terminals in tape-to-tape systems as well as for many other applications.

### COMBINES WITH HIGH-SPEED PUNCHES

For high-speed data transmission and reception over vast distances, the CX and DX readers can be combined with a Teletype BRPE and DRPE paper tape punch. The BRPE punch operates at 105 char/sec (1050 wpm) and the DRPE up to 240 char/sec (2400 wpm).

For more about these two talented tape terminals, contact: Teletype Corporation, Dept. 71A, 5555 Touhy Avenue, Skokie, Illinois 60076.

# commentary

Comments and opinions on topics of current interest to digital design engineering personnel. A monthly column organized and prepared under the direction of T. PAUL BOTHWELL, Contributing Editor.

# THE IMPACT OF L. S. I. ON COMPUTER MEMORIES

by

T. PAUL BOTHWELL

Vice President, Engineering

Computer Controls Division

Honeywell, Incorporated

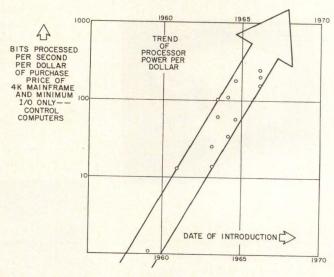

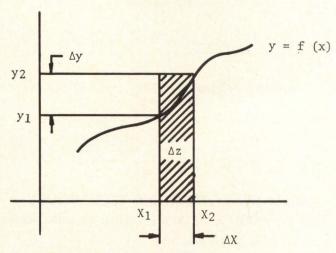

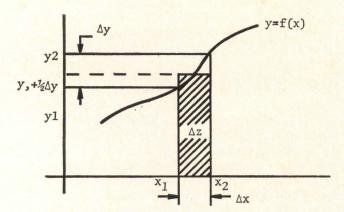

Computational capability has developed at an astonishing rate during the brief life of the electronic digital computer. Figure 1 shows than since 1959, computing power per dollar of first cost for small scientific computers has not only been increasing, but accelerating. It constitutes a straight-line trend on a logarithmic scale—a 200-to-1 improvement during the past eight years. Computing power is the word length multiplied by the average number of instructions (weighted) executed per second in a machine having a 4,000-word mainframe with minimum paper tape I/O.

Can the performance per computer dollar go on increasing at this pace? Not indefinitely. History tells us that all products eventually level off. Has that time come for computers?

#### Two Important Power Factors

Much of the gain in computing power per dollar has come about through the evolution of the magnetic core memory. During the dozen years that core memory has dominated main memory design, both cost per bit and cycle time have been reduced by a factor of ten, which represents a gain in memory value of 100 during these years. Another factor in gain of computer power, of course, is the lowering cost and rising speed of semiconductors. This achievement, together with the ingenuity of the logic designers, has greatly increased value in the non-memory part of computers, and has contributed to the growth in memory value.

Memory costs will continue to reduce. Core memory will probably give way to the plated wire memory. But even when we consider the substantial cost and per-

Fig. 1

formance improvements this will offer, it is hard to foresee another hundred-to-one reduction.

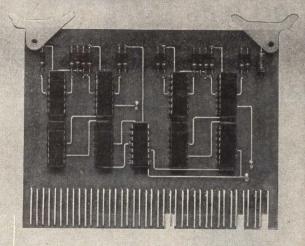

#### L.S.I. As A Factor

It seems, then, that the trend of the last few years may not continue beyond this decade unless something new enters the picture. And that "something" may be future developments in integrated-circuit technology — conveniently lumped into the term "L.S.I." As used here, the term applies to a chip containing more than 100 logic gates.

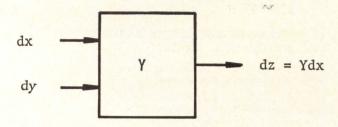

As I/C technology advances, circuits are growing more and more complex. We measure this complexity by the number of logic gates per chip (Fig. 2). A chip with up

# DATA COMMUNICATIONS

equipment for on-line, real-time processing

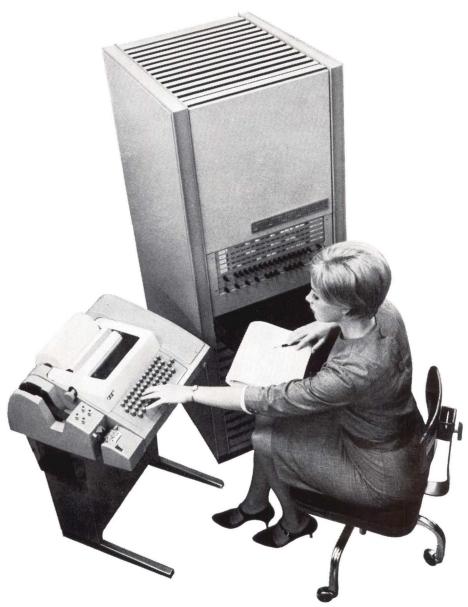

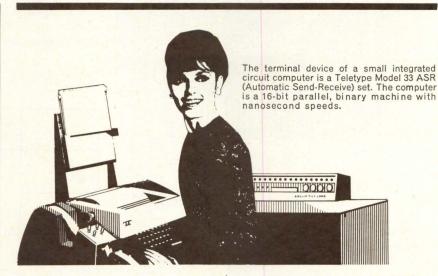

# keeping track of the ins and outs

Teletype data communications equipment serves as the terminals in a variety of computer systems. Many systems designers specify Teletype terminal equipment because they have found the sets to be the most reliable, versatile, and economical available.

The examples below point up the many capabilities of Teletype equipment as used in a number of different computer systems.

# AIDS SCIENTIFIC COMPUTATIONS

Primarily designed for control applications and scientific computations, a computer that uses monolithic integrated circuits can be operated alone, as a multiprocessor system, or as a satellite to a larger computer system. A Teletype Model 35 KSR (keyboard send-receive) set is the system's terminal. It uses an 8-level code compatible with the United States of America Standard Code for Information Interchange (ASCII).

# AIDS BILLING AND INVOICING

An electronic billing and invoicing machine uses a Teletype Model 33 ASR (automatic send-receive) set to provide on-line communications involving a variety of accounting data. Continuous pin-feed invoice forms with multiple copies are used in the system. In addition, a punched byproduct tape is prepared for further analysis by management.

Users of a time shared computer system can contact the computer for service and inputs of all instructions, data, and plot programs through standard Teletype equipment. The computer processes the data and transmits via a Model 33 ASR set a complete plot program, including identification codes for that particular plotter and output signals for remote on-line plotting.

A compact 16-bit real-time computer provides high-speed data acquisition and control. The system multiplies and divides faster, has a faster throughput and costs less than many larger systems. It uses a Teletype Model 33 ASR set as its terminal.

### AIDS TO YOUR SYSTEMS

These are only a few of the many Teletype equipment applications in both large and small computer systems. To learn how Teletype equipment can aid the systems you're designing, send for our brochure, "ALL ABOUT TELETYPE EQUIPMENT." Contact: Teletype Corporation, Dept. 71A, 5555 Touhy Avenue, Skokie, Illinois 60076.

machines that make data move

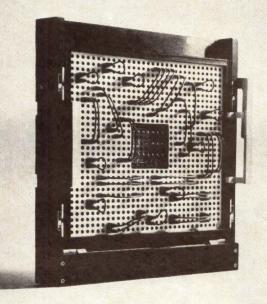

# reduce system size 7:1 with MicroVersaLOGIC IC Modules

The complete MicroVersaLOGIC line gives you all the ready-made building blocks you need for anything from a register to an entire digital system—with a 7:1 size reduction because of MicroVersaLOGIC's high density IC packaging.

MicroVersaLOGIC also means increased reliability over discrete components, lower power requirements, greatly reduced costs. MicroVersaLOGIC features NAND, NOR logic with wired OR capacity at the collector, operates to 5v. logic levels, has excellent noise rejection of over 1v. There are over 20 basic module types, all meticulously designed and assembled to give you utmost reliability.

Our new MicroVersaLOGIC brochure will show you how easy and economical it is to design digital systems with Micro-VersaLOGIC IC Modules. Write or call.

to 10 gates is simply an integrated circuit; 20 or 30, functional array; close to 100, M.S.I. L.S.I. is still a few years away, but is certainly coming, and it is interesting to speculate its impact on memories.

By its nature, L.S.I. is applicable where large numbers of similar circuits are required, where interconnection between the circuits can be made all on the same wafer of silicon and where it offers the lowest unit circuit cost. Industry sources project costs as low as a penny per gate in five or ten years.

Now, remembering that two gates can make a flip-flop, and that a flip-flop is still one of the fastest and simplest memory elements ever devised, it is clear that L.S.I. will be used for the construction of memories.

Many different types of memories are used in computers today, however, and many more have been suggested for the computers of tomorrow. Which of these are likely to make effective use of L.S.I.?

Although many L.S.I. enthusiasts would disagree, I believe it will be a long time before L.S.I. can achieve the performance and economic advantages of magnetic main memories and mass memories. The development of batch fabricated magnetic devices, represented by flat film and plated wire, the extreme desirability of the non-volatile storage properties, and the high level of technological momentum in magnetics combine to provide

#### DEFINITIONS

|                         | INTEGRATED | FUNCTIONAL<br>ARRAYS | MSI      | LSI    |

|-------------------------|------------|----------------------|----------|--------|

| NO. OF<br>GATES         | 1-10       | 8 –30                | 30-100   | 100    |

| NO. OF<br>COMPONENTS    | 5-50       | 50-300               | 150-1000 | 500    |

| NO. OF<br>PINS          | 14-30      | 14-50                | 14-50    | 30-100 |

| INTERNALLY<br>CONNECTED | NO         | YES                  | YES      | YES    |

Fig. 2

formidable obstacles to the integrated circuit as the primary memory device.

In contrast, however, application of L.S.I. to peripheral buffers and the more specialized memories is not only technically feasible today, but will offer increasing advantages during the next decade. Since cost per bit of a core memory rises steeply as the size is reduced, core memory will soon lose its cost advantage for small memories. Moreover, many of the more specialized memories, such as read-only and scratch-pad units, can make good use of the very high speed available from L.S.I. technology.

The advent of L.S.I. is going to stimulate the introduction of more specialized memories into computer systems. Specialized memories, such as scratch-pads, read-only memories and content addressable memories, have long been attractive to the computer designer, but

# DATA COMMUNICATIONS

equipment for on-line, real-time processing

# ...at the press of a button

Time. In today's data communications and processing systems it is measured in microseconds. And Teletype R&D engineers know it. For instance, look at the Push Button Data Generator they have developed to cope with the situation.

The PBDG is an automatic data preparation unit that simplifies and speeds the flow of fixed data. By preprograming fixed data into the PBDG, you can automatically print up to 24 alphanumerics and other characters by pressing a single button.

# AIDS COMPUTER OPERATION

The PBDG can be used wherever there is a need for automatic handling of repetitive data. For instance, in a time sharing system, the intricate instructions needed to activate the computer for a particular user can be programed into the PBDG, and transmitted automatically to the computer merely by pressing the appropriate button.

In addition, the PBDG offers many important advantages to data communications and processing operations. Information is stored and reproduced in the same form every

time at the press of a button. Data is easily programed or reprogramed for automatic transmission of fixed data. This saves time, saves key strokes, and eliminates errors.

#### GENERATES 288 CHARACTERS

Operating on either a 5 or 8-level code, the basic Teletype PBDG unit consists of 12 pushbuttons capable

Cabinet at right of this Teletype Model 35 ASR set houses control panel and circuitry of Push Button Data Generator

of generating a total of 288 characters. The PBDG can be used as a self-contained unit or combined with other Teletype equipment to punch paper tape, print page copy, or transmit to a remote unit.

Programing is made and/or changed simply by movement of push-on type terminals. Notechnical skill is needed to make or change a program. The unit also may be programed to stop on any predetermined character position. This permits insertion of variable information from a keyboard. After the variable data has been entered, automatic entry of fixed data is continued at the press of a button.

#### AVAILABLE IN SPECIAL CABINET

Where space permits, the PBDG control panel and its associated electronics can be housed in a Teletype printer console. When more than 24 pushbuttons are needed, special cabinets can be provided that contain as many as 96 buttons in units of 12.

For more information about transmitting your data at the press of a button, simply request our PBDG data sheet by contacting: Teletype Corporation, Dept. 71A, 5555 Touhy Avenue, Skokie, Illinois 60076.

machines that make data move

# A NEW DIMENSION IN COMPUTER COMPATIBILITY

Magnetic tape unit complete with interface designed for peripheral use with your small computer.

Slew mode write or read at speeds of 1000 to 3000 char/sec Incremental writing to 500 char/sec. Choice of 200, 556 or 800 BPI, 7 track or 9 track. All computer compatibility features including IR GAP, LRCC, EOF. Low Cost.

Main Office: 4315 Baltimore Ave. Bladensburg, Md. 20710 • (301) 277-9378

CIRCLE NO. 18 ON INQUIRY CARD

### MEMORY REQUIREMENTS

| Memory Type              | Price Range<br>Cents/Bit |

|--------------------------|--------------------------|

| Mass Memories            | 0.5 to 0.01              |

| Main Memories            | 5 to 10                  |

| Peripheral Buffers       | 10 to 25                 |

| Specialized Memories     | 10 to 100                |

| Read Only Memories       |                          |

| Control Memories         |                          |

| Scratch Pads             |                          |

| Content Addressable Memo | ories                    |

because of their excessive cost (Fig. 3) have been bypassed in favor of more main memory and software devices. Such memories can have dramatic effects on overall computer power and will have a significant effect in maintaining the power-per-dollar trend.

Fig. 3

L.S.I., by virtue of the great reduction in the length of interconnections and the even smaller geometry of the transistor junctions, will permit faster logic switching in the computer, thus increasing the demand for more memory speed. The need, therefore, to relieve the main memory of as much mundane work as possible will be intensified. This, in turn, will increase the need for more specialized memories to take over suitable functions.

#### Conclusion

L.S.I. will have primary impact in changing our approach to memory and computer system organization, resulting in many more economic, specialized memory devices. These devices, in turn, will modify our views on the role and mode of use of the memory, software logic and system architecture.

Computer architecture has really changed very little in a decade — in fact, almost two decades. The early concept of a single main memory into and out of which all information is pumped as it is stored and processed has not changed appreciably. Ten years or more of design has been devoted primarily to optimizing that principle and re-optimizing it in the light of new components and new application knowledge.

L.S.I. will change many of the rules which have been axioms for system architects for ten years. The availability of economic, fast, specialized memories will gradually modify the basic single memory concept which has held sway so long; and this will lead us into a new era of computer power in the 1970's. We are a long way from the end of the road in computer power per dollar.

We have a complete line of photodevices - from a 50-cent epoxy transistor to a \$4,000 custom photo array. Light-emitting and light-sensing devices for everything from computers to electric organs. They can translate keyboard signals, read punched cards and tape, measure height and volume, perform character recognition, read motion picture sound track. You name it. Write for complete information and we'll throw in a glossary of the latest photometric and radiometric terms.

FAIRCHILD SEMICONDUCTOR / A Division of Fairchild Camera and Instrument Corporation 313 Fairchild Drive, Mountain View, California 94040, (415) 962-5011 TWX: 910-379-6435 SEMICONDUCTOR

# What this country needs is a good 50¢ phototransistor.

CIRCLE NO. 19 ON INQUIRY CARD

# INDUSTRY NEWS

PHOTO-DIGITAL STORAGE SYS-TEM-The Atomic Energy Commission recently completed installation of what is claimed to be the world's largest computer storage system at the University of California Lawrence Radiation Laboratory. More than one trillion bits of information-enough data to provide the average person with nearly 200 years of uninterrupted reading-can be stored by this photo-digital storage system which was built for the AEC by International Business Machines Corporation under a \$1 million contract. Any item in the system's file is directly accessible upon request and can be retrieved in seconds without scanning other items in the memory. Information is handled entirely automatically within the system.

When fully activated, the IBM Photo-Digital Storage

System will store and retrieve information for a network of interconnecting computer systems at the Livermore Laboratory. This network—said to be one of the most powerful time-sharing data processing facilities in operation—stores and analyzes data obtained from large-scale computations.

The photo-digital system

The photo-digital system stores information at very high densities by using a beam of electrons to record the data on 1.3- by 2.7-inch "chips"—pieces of high-resolution, photographic film. Nearly five million bits of information can be packed on a single film chip.

The chips are positioned in a vacuum chamber for recording, and the information is "written" during repeated sweeps of the beam across the chip surface. The beam, in effect, paints data as combinations of dark and clear spots corresponding to the zeros and ones of the binary language of the computer. Sensitive control devices in the recorder continually align and adjust the beam.

The photo-digital system houses its own film-processing "laboratory" which develops the film chips under automatic control. Chips are treated individually with chemicals, then washed and dried to prepare them for filing.

Recorded chips are transported and stored in protective plastic cells somewhat smaller than a cigarette package. A single cell holds 32 chips and could store enough information to process a complete payroll for a 30,000-man company.

Cells are blown through transport tubes connecting the processing stations to the storage area. This pneumatic transport network is designed for two-way travel at speeds reaching 25 feet per second.

In the storage area, cells

# speed reader

Digiswitch® and Miniswitch®, the industry's standard in thumbwheel switches. Rapid setting for rapid reading. With large, clear symbols for improved accuracy.

Digitran switches read great. Look great. And save you up to 50% in panel space. Digitran switches make your product look better, sell better. And modular design lets you use any number of digits.

Digitran switches are easy to use,

and we make them easier to use: As the world's largest, most experienced thumb-wheel switch manufacturer, we have more application experience than anyone else. We can save you hours of design time.

Send for our complete catalog. We'll speed it to you.

THE DIGITRAN COMPANY

Subsidiary of Becton, Dickinson and Company ED

855 S. Arroyo Pkwy./Pasadena, Cal. 91105

Tel: (213) 449-3110/TWX 910-588-3794

CIRCLE NO. 20 ON INQUIRY CARD

# A word to the do-it-yourself module builder:

# Don't.

Buy our J Series modules instead.

The J Series is our new family of general purpose, all integrated circuit logic modules. Their performance almost matches that of our famous T Series modules,

These will cost you less.

but they cost about 25% less. They're made to the same dimensions as the T Series, with the same 52 pin connectors, so they're physically interchangeable. We make them for our own seismic recorder systems, so they're rugged and reliable. Now, as of January, you can buy them (com-

plete with mounting hardware, racks and power supplies, if you wish) in any of 25 different functions.

And save yourself the time and cost of making your own: designing, assembling, testing, new procedures, new equipment, new personnel, additional training, to say nothing of the added paper work.

If you're building systems, you must have better things to do than go into the module assembly business. Such as reading our J Series catalog. It's free.

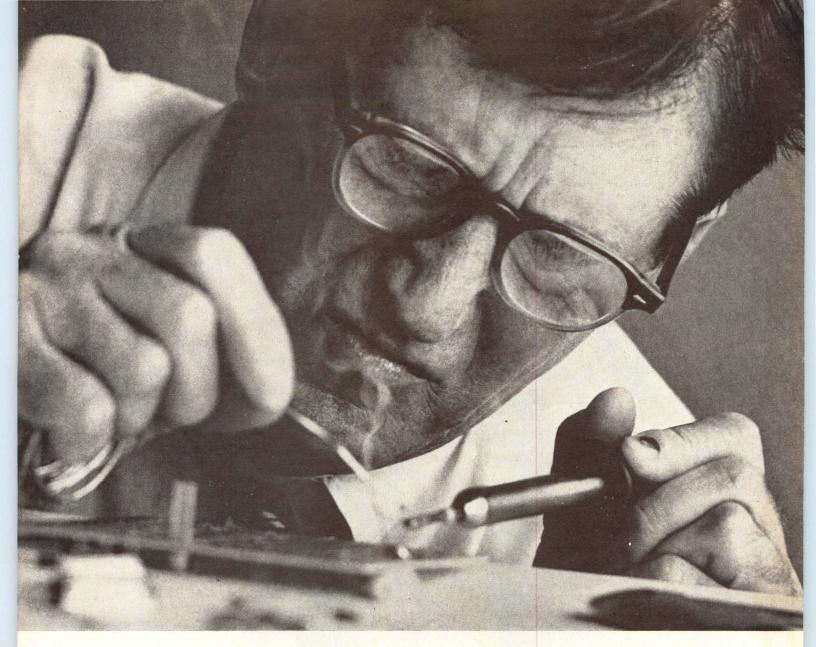

FACT stands for Flexible Automatic Circuit Tester. It doesn't pull any punches.

It's a completely automatic system for continuity and leakage testing. Fully programmable with card or tape input.

When a computer won't play, or there's a circuit discrepancy in any type of electrical harness or assembly — FACT pinpoints the failure exactly.

And reports the fault and precise location to the operator.

FACT'S fast. Testing is performed at an average rate of 3000/minute. FACT'S flexible. Adaptation to new

projects requires only new tapes or test decks, plus the appropriate adapter cables.

It's completely modular — designed for easy expansion and adaptable to a wide variety of test conditions.

FACT is now reporting wiring discrepancies for many commercial military and space programs. And producing significant cost/schedule savings.

Write Hughes for the good news. FACT Systems, P.O. Box 90929, Los Angeles, California 90009. FACT'S available off-the-shelf. In 90 days or less.

HUGHES

HUGHES AIRCRAFT COMPANY

CIRCLE NO. 22 ON INQUIRY CARD

are placed in individual compartments of movable trays resembling a stack of egg crates. A computer keeps track of all records stored in the trays and initiates requests for the retrieval of information.

Individual cells are withdrawn from any location in the file and pneumatically delivered to a reader where the selected chip is read by a high-speed flying spot scanner. Data is automatically checked and corrected before it is transmitted to the computer.

The photo-digital system operates under the control of a stored-program processor similar to the control computers which regulate an automatic assembly line or traffic network. This control processor is part of the system and sets in motion the many discrete mechanical, electrical, and chemical processing steps that make up such activities as positioning the storage trays or developing the film chip.

Requests are translated into action by the processor in response to a program that speeds the flow of events by allowing many independent actions to occur at one time in a variety of combinations. The control program also acts as a tool for continuous, automatic diagnosis of the system's performance.

A second photo-digital system is scheduled for the Lawrence Radiation Laboratory facility located on the Berkeley campus of the University of California. Somewhat smaller in capacity, this system will store masses of data used to track and identify atomic particles.

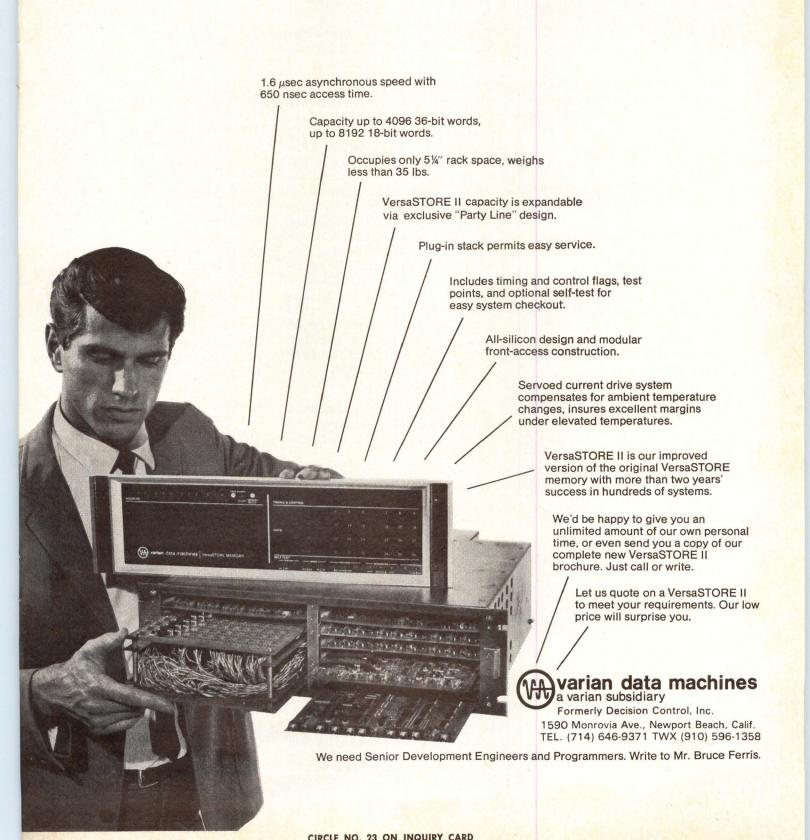

Both systems were developed by IBM's development laboratories in San Jose, Calif. The new VersaSTORE II core memory system can give you all the speed, capacity, and convenience you'll ever need.

It can also save you a few bucks.

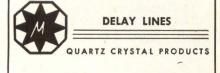

## DELAY LINES

#### **GENERAL**

Delay .4 to 10,000 usec at frequencies from 10 to 400 mc. Wide bandwidth and low spurious response for excellent pulse reproduction and dynamic range.

#### COMPUTER STORAGE SYSTEMS

Ultrasonic delay lines using fused quartz or special glasses represent an ideal medium for high-speed Computer Storage, up to 20 mc rates.

Send for Microsonics' Brochure #5350.

#### DIGITAL DELAY LINES

Delay lines for storage of high-speed digital pulses with zero temperature coefficient of delay for Computer applications. Design Bulletin available on request.

#### MAGNETOSTRICTIVE DELAY LINES

Microsonics, Inc. has a broad delay line and systems experience with capability to deliver both off-the-shelf and custom-designed systems for any specific application.

Systems provide for the delay or storage of both analog and digital signals and are available to handle all modes of modulation (RZ, NRZ and Bipolar). Output signals are available in either clocked or unclocked signal.

Send for Microsonics' Brochure #M735.

#### VARIABLE AND TAPPED DELAY LINES

Featuring all usual advantages of superior fixed Delay Lines.

## MICROSONICS INC.

A subsidiary of the SANGAMO ELECTRIC CO.

60 Winter Street Weymouth, Mass.

Area Code (617) 337-4200

REPORT ON MEETING OF IFIP GENERAL ASSEMBLY IN MEXICO CITY. At the meeting of the General Assembly of the International Federation for Information Processing (IFIP) held recently in Mexico City two further countries were admitted to membership - Yugoslavia and Cuba. This brings the number of countries represented on IFIP to 28. Professor R. Tomovic is the delegate for Yugoslavia and Mr. Rual Alvarez Marcer for Cuba.

#### President-elect

Professor A. A. Dorodnicyn of the U.S.S.R. has been elected to succeed Dr. A. P. Speiser as President of IFIP following IFIP Congress 68. A second Vice-President-Mr. D. Chevion of Israel was elected and given responsibility for co-ordinating and supervising the activities of the IFIP special interest groups and IFIP Technical Committee 3 (TC3-Education). Professor L. Lukaszewicz of Poland will continue as Vice-President and be responsible for the activities of the other IFIP Technical Committees.

#### IFIP Congress 71

Yugoslavia will be the host country for IFIP Congress 71 which will be held in Ljubljana.

Administrative Data Processing Group

The bylaws of the Administrative Data Processing Group were approved by the General Assembly and the Group will become operative when at least five member countries have ratified the bylaws and appointed delegates to serve with the Group.

New IFIP technical committee formed

A new IFIP technical committee—TC 4—has been formed. Its area of interest will be medical data processing and Professor F. Gremy of France has been elected its first chairman.

Joint Conference

In association with other professional organizations, IFIP are to sponsor a number of joint conferences over the next two years. first will be held in June 1968 at Novosibirsk in the U.S.S.R. and the subject will be "Optimal programming in process control and economics". In June 1968, an IFAC/IFIP conference on the state of the art in the application of control computers will be held in Toronto; and plans are being considered for an IFAC/IFIP conference in 1969 on programming languages for numerically-controlled chine tools. In September 1969 a conference on hybrid computing will be held in Munich, Germany in association with the A.I.C.A.

SEEING IS BELIEVING-Work pioneered by IBM and continued by IBM, United Aircraft, and General Motors has resulted in the production of holograms of objects that do not exist. Computers, after being programmed with information about what an object should look like, calculate the interference pattern that the object would produce. This pattern is recorded and transferred to a transparency. When the transparency is viewed in monochromatic light. a three-dimensional image of the "object" appears. So far the images have been of relatively simple objects like letters or geometrical figures, but the technique should have wide application. For example, designs of objects could be displayed and studied in three dimensions before being built. Computers also can be used to translate holograms of very large or very small objects into useful display sizes. Several possible uses of this technique have already become apparent to researchers. acoustical hologram of a

# The world's lowest cost Core Memory...right in the palm of your hand

We build some pretty sophisticated without a qualm. core memory systems-but not everybody needs them. A lot of you out there have asked for a compact, no-nonsense, inexpensive memory for such applications as data transmission buffering, data logging, formatting and CRT refresh. Thus challenged, we came up with (it wasn't easy) the FI-1-a 1024 lets you abandon even delay lines specific applications.

Briefly, the FI-1 has a full cycle time of  $2\mu$ sec and access time of 900 nsec. Power? Just ±6v. Utilizing ICs we have packed address decoding, ferrite core drivers, data I/O circuits and internal timing logic for half cycle operation into a handful-size package. And there's still room in it for an extra universal x 1 core memory system at a cost that circuit card to add logic functions for Single quantity cost? Just \$650.

Designers, arise! You have nothing to lose but the limitations of other storage techniques. For complete data on the FI-1 Memory System, get on the horn (collect) or write for Bulletin

Ferroxcube & Systems Division, Englewood, Colorado

Albuquerque—Electronic Enterprises, (505) 256-1585; Baltimore—Eastern Components, (301) 322-1412; Dayton—(513) 253-3158; Encino, Cal.—(213) 788-2060; Englewood, Col.—(303) 771-2000; Houston—Noakes Engineering, (713) 529-6213; Irving, Texas—Noakes Engineering, (214) 255-0441; Lansing, Mich.—(517) 482-7140; Minneapolis—(612) 888-4681; Northlake, III.—(312) 261-7880; Orlando—(305) 841-6380; Philadelphia—Eastern Components, (215) 927-6262; Phoenix—(602) 265-1792; San Francisco—Wm. J. Purdy Agents, (415) 863-3300; Saugerties, N. Y.—(914) 246-2811; Union, N. J.—(201) 964-1844; Waltham, Mass.—(617) 899-3110; Toronto, Ontario—Philips Electron Devices, Ltd., (416) 425-5161.

# Any day now you computer people will make an incredible discovery:

Nobody has made custom power supplies longer than Varo.

Or with a better performance record.

Or to tougher mil specs. Funny we haven't crossed paths with you folks.

Funny?

It's incredible!

Let's discover each other.

Write Rex Carter, Varo,

Inc., Static Power Division,

1600 Dallas North Parkway,

Plano, Texas 75074.

TWX 9108605640

TELEX 73-2713

large object, like a submarine or part of the ocean floor, can be made with long wavelength sound energy. A computer calculates the interference pattern that would have been formed with short wavelength light energy and produces the transparency of this pattern. In the developed hologram, the object would be small enough to study in an ordinary room. It is also possible to reverse the process and to enlarge a hologram made of a microscopic object. In this case, the original hologram would be made with radiation having a very short wavelength. The computer would calculate the interference pattern for longer wavelength radiation, and the result would be an enlarged three dimensional image of the object.

AUTOMATIC TICKET AGENCIES-Computicket Corporation, a subsidiary of Computer Sciences Corp., has awarded a \$3.3 million contract for production of electronic terminals that will serve as neighborhood box offices in company's computerbased instant ticketing system. The terminals will be manufactured by Wyle Laboratories. El Segundo, Calif., to specifications developed by Computicket engineers. The terminals will be installed in neighborhood markets, banks, and other retail and commercial outlets, and will be linked by private communication lines to a central computer complex. The units will be used to request seats to sports, theater, and other entertainment events, and to print the actual admission tickets for these Television-like events. screens at each terminal will instantly display the computer's response to requests. The development of the Computicket terminals is said to have a significance extending beyond the ticketing business. The units are flexible enough in their design to satisfy the inquiry, response and high speed printing requirements of a number of other important applications; for example, travel and hotel reservations, inventory control and credit checking. The first terminals produced will be installed in the Southern California Computicket network, which will begin operation next spring. Similar networks will be established in New York and other metropolitan areas throughout the United States in 1968 and 1969. The ultimate plan is to form a nationwide Computicket network.

RCA TO BUILD \$11.7 MILLION COMPUTER PLANT-RCA has announced plans to build a 220,000 square-foot facility in Marlboro, Mass. for the engineering and production of computer peripheral equipment. Construction of the new plant, to be located on a 128-acre site on Interstate Highway 495, will begin in 1968, with the target date for initial occupancy scheduled for early 1969. A 50,000-squaretemporary foot facility has been leased near Framingham, Mass., to recruit and train the personnel who will form the nucleus of the permanent operation four miles away. Engineering efforts will begin at the Framingham plant around January 1968. Initially, a limited number of different types of electronic data processing devices for RCA's Spectra 70 systems will be assembled at the Marlboro plant. At full operation, a broad range of computer peripheral devices will be designed and manufactured. According to James R. Bradburn, Vice President and General Manager of RCA Electronic Data Processing, the new plant will be built with an eye toward additional expansion in the early 1970's.

It's no longer \$30K and up to give your system big computer power.

The DATA 620/i comes in at less than one-half that amount. And it gives you more raw computer muscle than the \$30K machine.

It's because the DATA 620/i was designed from scratch for *systems* work, no double-duty design, no we-cover-the-waterfront philosophy. It's a pure, lean computer for systems.

Fully IC'd for reliability and small size, the DATA 620/i handles 16 and 18 bit words, operates at 1.8  $\mu$ sec speed, with more than 100 basic commands and a 4K to 32K word memory. It comes with Party Line I/O, complete software proven out by the DATA 620, and a full selection of peripherals and options.

We know of more than 300 systems that couldn't afford not to have the DATA 620/i, because that's how many we sold in the first six months. We'd be happy to show you what it can do for your system, or at least send you our illustrated brochure full of functional and operational information. Just call or write.

# Now that the DATA 620/i computer is out can you afford not to use it in your system?

We need Senior Development Engineers and Programmers.

Write to Mr. Bruce Ferris.

varian data machines

a varian subsidiary

Formerly Decision Control, Inc.

### 1968 SOLID-STATE CIRCUITS CONFERENCE

## University of Pennsylvania and Sheraton Hotel Philadelphia, Pa., Feb. 14, 15, 16, 1968 TECHNICAL PROGRAM SUMMARY

Reflecting the extraordinary growth of solid-state technology, this year's International Solid-State Circuits Conference has scheduled more papers than ever before—15 formal sessions comprising 78 invited and contributed papers authored by over 140 scientists, engineers and educators from here and abroad will be presented at the University of Pennsylvania.

In the evenings, informal discussions will again be held at the Sheraton Hotel. Twelve sessions, with over 80 participants, are on the agenda.

Those daytime sessions and evening informal discussions of prime interest to Computer Design readers are listed in the following schedule.

### FORMAL OPENING — Wed., 1:45-2:45 p.m., Irvine Auditorium

### KEYNOTE ADDRESS: MAKING INTEGRATED ELECTRONICS TECHNOLOGY WORK

R. N. Noyce, Fairchild Semi-Conductor, Mountain View, Calif.

Applications of large-scale integration require solutions to technical, organizational, economic and logistic problems significantly more complex than those in applications of today's integrated circuits. The solution will require greater flexibility and communication between vendor and user.

### SESSION III — INVITED: THE FUTURE OF INTEGRATED ELECTRONICS IN SYSTEMS — Wed., 2:50-5:30 p.m., Irvine Auditorium

Moderator: R. L. Petritz, Texas Instruments, Inc., Dallas, Texas

Progress in integrated electronics has had a widespread impact on the electronics industry prompting a critical appraisal of its productive application to real systems. In the keynote address, technology problems and their interface with customers were underscored. The following invited papers will report on allied problems. The first three will discuss the application of the technology to three major systems: computers, telecommunications and consumers. The concluding presentation will consider a new approach to integrated electronics through recent discoveries of bulk phenomena in semiconductors.

### 3.1: THE IMPACT OF LSI IN LARGE COMPUTER SYSTEMS

M. O. Paley, IBM Corp., Menlo Park, Calif.

LSI technology offers significant performance gain in large computers through higher-speed switching and higher circuit density. The challenge to the system designer is to balance this increased logic with high performance memory, input-output considerations and architectural innovations.

### 3.2: INTEGRATED ELECTRONICS IN TELECOM-MUNICATIONS

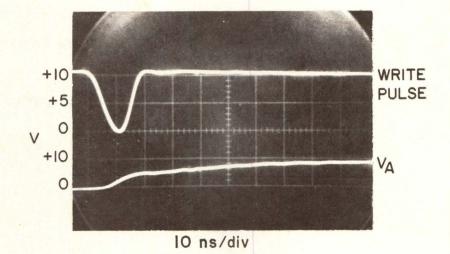

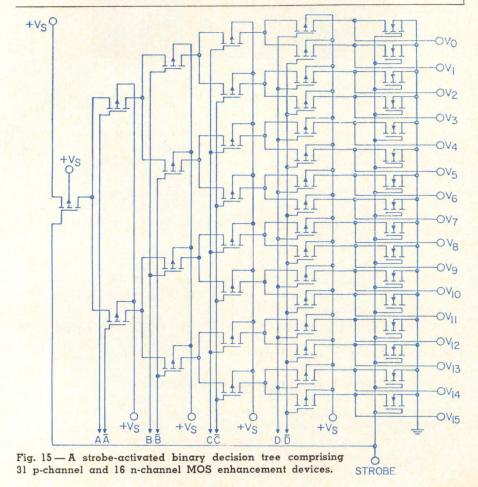

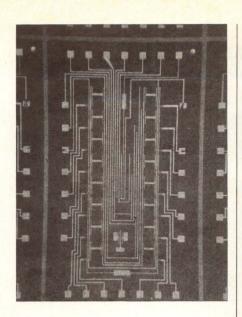

G. C. Dacey, Bell Telephone Laboratories, Inc., Holmdel, N. J.