# Section 54. Graphics LCD (GLCD) Controller

This section of the manual contains the following major topics:

| 54.1 | Introduction              |  |

|------|---------------------------|--|

| 54.2 | Control Registers         |  |

| 54.3 | Operation                 |  |

| 54.5 | Interrupts                |  |

| 54.6 | Related Application Notes |  |

| 54.7 | Revision History          |  |

|      |                           |  |

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all PIC32 devices.

Please consult the note at the beginning of the "Graphics LCD (GLCD) Controller" chapter in the current device data sheet to determine whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Web site at: http://www.microchip.com.

## 54.1 INTRODUCTION

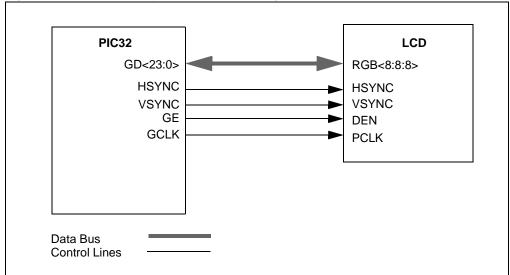

The Graphics LCD (GLCD) Controller is designed to interface with display glasses using a built-in analog drive to individually control pixels on the screen. The GLCD Controller transfers display data from a memory device and formats it for a display device. The parallel interface at the pins will operate at standard 3.3V output, which requires 28 pins for 24-bit color, and is typically shared by the general purpose I/O functions on the device.

## 54.1.1 Features

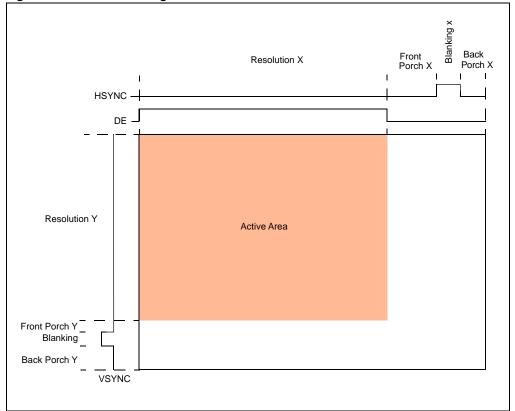

The timing of the programmable vertical and horizontal synchronization signals timing is provided to meet the timing requirements of the display.

Device-specific features include (refer to the specific device data sheet to determine the supported features for your device):

- Supports a variety of color depths and resolutions

- Supports multiple design timing layers, which include:

- Configurable Alpha Blending

- Configurable Stride and Pitch

- Supports various input and output formats

Features common to all devices include:

- Dithering for 18-bit displays

- High-quality YUV conversion

- Global color palette look-up table (CLUT) supporting 256 colors

- · Global gamma correction, brightness and contrast support

- Programmable cursors supporting 16 colors (including 1 transparent)

- Programmable polarity on HSYNC, VSYNC, DE, and PCLK

- Integrated DMA to offload the CPU

- Programmable (level/edge) interrupt on HSYNC and VSYNC

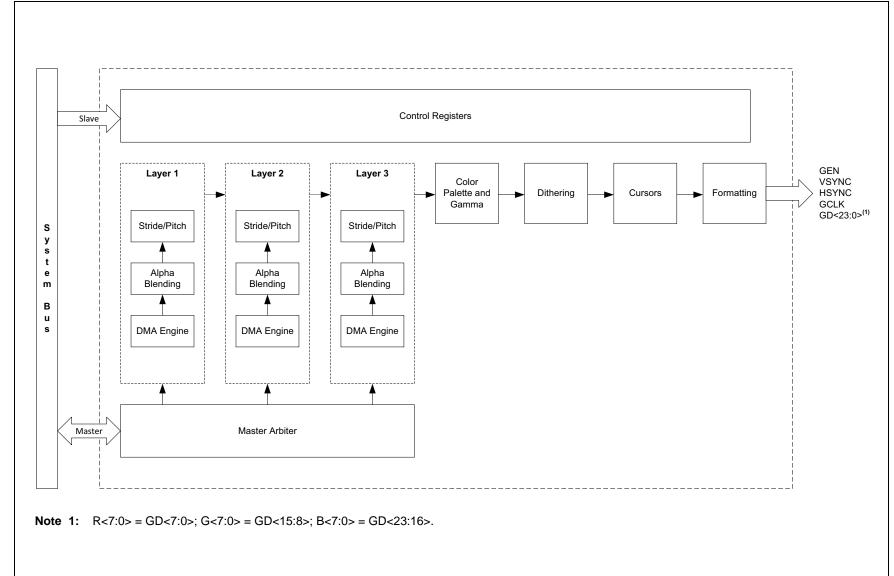

Figure 54-1 illustrates a block diagram of the GLCD controller.

## Figure 54-1: Graphics LCD Controller Block Diagram

Section 54. Graphics LCD (GLCD) Controller

## 54.2 CONTROL REGISTERS

The Graphics LCD (GLCD) Controller has the following Special Function Registers (SFRs):

• GLCDMODE: Graphics LCD Controller Mode Register

This register controls the enabling of the GLCD Controller, sets the polarity for the timing signals, and also controls the enabling of the global color look-up table. This register also controls the global color option of RGB, YUV, or Blank. Dithering can be enabled for ramping up color outputs to meet LCD color specifications.

• GLCDCLKCON: Graphics LCD Controller Clock Control Register

This register controls the amount of lines that can be prefetched before starting the frame and also contains the main clock divisor control bits to set up proper timing.

• GLCDBGCOLOR: Graphics LCD Controller Background Color Register

This register contains the 32-bit value that will be the main background color for the GLCD Controller. It accepts a 24-bit RGB color value along with an 8-bit Alpha value.

- GLCDRES: Graphics LCD Controller Resolution Register

- This register contains the main X and Y resolutions to be used for the GLCD Controller.

- GLCDFPORCH: Graphics LCD Controller Front Porch Register

This register contains the X and Y dimensions for the Front Porch to be used for the GLCD Controller.

• GLCDBLANKING: Graphics LCD Controller Blanking Register

This register contains the X and Y dimensions for the Blanking period to be used for the GLCD Controller.

• GLCDBPORCH: Graphics LCD Controller Back Porch Register

This register contains the X and Y dimensions for the Blanking period to be used for the GLCD Controller.

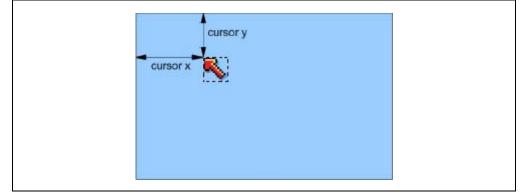

• GLCDCURSOR: Graphics LCD Controller Cursor Register

This register contains the X and Y start dimensions for the Cursor of the GLCD Controller.

• GLCDLxMODE: Graphics LCD Controller Layer 'x' Mode Register ('x' = 0-2)

These registers contain the control for the enabling of the layer. They also support the control for the blending of the layer along with the blending type. Each layer can have its own color mode, which is also selected using this register. Bilinear filtering can be enabled to smooth edges.

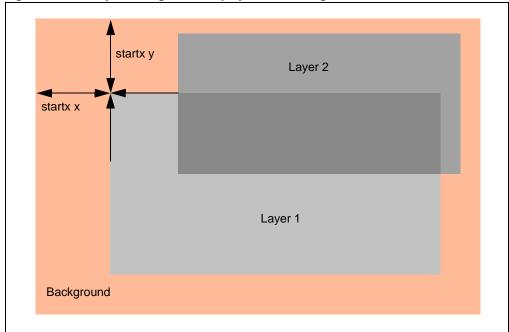

• GLCDLxSTART: Graphics LCD Controller Layer 'x' Start Register ('x' = 0-2)

These registers contain the X and Y start dimensions of the layer to be used.

• GLCDLxSIZE: Graphics LCD Controller Layer 'x' SIZE Register ('x' = 0-2)

These registers contain the X and Y size of the layer to be used.

• GLCDLxBADDR: Graphics LCD Controller Layer 'x' Base Address Register ('x' = 0-2)

These registers contain the X and Y start address in memory for the frame buffer to be accessed by the layer.

• GLCDLxSTRIDE: Graphics LCD Controller Layer 'x' Stride Register ('x' = 0-2)

These registers contain the distance from a frame buffer line to line-in memory. A stride is needed if the frame buffer is not stored continuously.

• GLCDLxRES: Graphics LCD Controller Layer 'x' Resolution Register ('x' = 0-2)

These registers contain the X and Y dimensions for the resolution of the layer.

GLCDINT: Graphics LCD Controller Interrupt Register

This register enables timing interrupts from the GLCD Controller, including HSYNC and VSYNC, as well as which type of edge trigger source to be used.

GLCDSTAT: Graphics LCD Controller Status Register

This register contains the status of the GLCD Controllers including the last row CSYNC, VSYNC, HSYNC, DE, and which state the GLCD Controller is in. The state can either be active or blanking.

• GLCDCLUTx: Graphics LCD Controller Global Color Lookup Table Register 'x' ('x' = 0-255)

These registers contain the global color lookup table component values used by the GLCD controller.

• GLCDCURDATAx: Graphics LCD Controller Cursor Data 'n' Register ('n' = 0-127)

These registers contain the color values for the 32 x 32 pixel Cursor that are to be used with the Cursor LUT.

• GLCDCURLUTx: Graphics LCD Controller Cursor LUT Register 'x' ('x' = 0-15)

These registers contain the 24-bit color values of the LUT used by the Cursor color LUT.

Table 54-1 provides a summary of all Graphics LCD (GLCD) Controller Special Function Registers (SFRs). Corresponding registers appear after the summaries, which include a detailed description of each bit.

## Table 54-1: Graphics LCD Controller Register Map

| Register<br>Name | Bit<br>Range | Bit 31/15 | Bit 30/14    | Bit 29/13      | Bit 28/12    | Bit 27/11       | Bit 26/10     | Bit 25/9      | Bit 24/8      | Bit 23/7     | Bit 22/6    | Bit 21/5  | Bit 20/4     | Bit 19/3       | Bit 118/2 | Bit 17/1  | Bit 16/0 |

|------------------|--------------|-----------|--------------|----------------|--------------|-----------------|---------------|---------------|---------------|--------------|-------------|-----------|--------------|----------------|-----------|-----------|----------|

| GLCDMODE         | 31:16        | LCDEN     | CURSOR<br>EN | _              | VSYNC<br>POL | HSYNC<br>POL    | DEPOL         | -             | DITHER        | VSYNC<br>CYC | PCLK<br>POL | -         | PGRAMP<br>EN | FORCE<br>BLANK | _         | _         | _        |

| GLCDMODE         | 15:0         | —         | _            | —              | _            | _               | _             | YUV<br>OUTPUT | FORMAT<br>CLK | R            | GBSEQ<2:    | )>        | —            | —              | —         | _         | _        |

| GLCDCLKCON       | 31:16        | —         | _            | —              | _            | -               | _             | -             | —             | _            | —           | -         | _            | _              | _         | —         | _        |

| GEODOERGON       | 15:0         | —         | —            |                |              | LPREFET         | CH<5:0>       |               |               | —            | —           |           |              |                | 0IV<5:0>  |           |          |

| GLCDBGCOLOR      | 31:16        |           |              |                | RED<         |                 |               |               |               |              |             |           |              | EN<7:0>        |           |           |          |

| GEODDOGOLOIX     | 15:0         |           |              |                | BLUE<        | <7:0>           |               |               |               |              |             |           | ALPH         | IA<7:0>        |           |           |          |

| GLCDRES          | 31:16        | —         | —            | —              | —            |                 |               |               |               |              |             | X<10:0>   |              |                |           |           |          |

| GEODINEO         | 15:0 —       |           |              |                | —            | RESY<10:0>      |               |               |               |              |             |           |              |                |           |           |          |

| GLCDFPORCH       | 31:16        | —         | —            | —              | —            |                 |               |               |               |              | FPOR        | CHX<10:0> |              |                |           |           |          |

| CEODITI CINCIT   | 15:0         | —         | —            | —              | —            |                 |               |               |               |              |             | CHY<10:0> |              |                |           |           |          |

| GLCDBLANKING     | 31:16        | —         | —            | —              | —            |                 |               |               |               |              | BLANK       | NGX<10:0: | <b>&gt;</b>  |                |           |           |          |

| GEODDEANNING     | 15:0         | —         | —            | —              | —            | BLANKINGY<10:0> |               |               |               |              |             |           |              |                |           |           |          |

| GLCDBPORCH       | 31:16        | —         | —            | —              | —            |                 | BPORCHX<10:0> |               |               |              |             |           |              |                |           |           |          |

|                  | 15:0         | —         | —            | —              | —            |                 |               |               |               |              |             | CHY<10:0> |              |                |           |           |          |

|                  | 31:16        | —         | —            | —              | —            |                 | CURSORX<10:0> |               |               |              |             |           |              |                |           |           |          |

| CEODOCINOCIN     | 15:0         | —         | —            | —              | _            | CURSORY<10:0>   |               |               |               |              |             |           |              |                |           |           |          |

| GLCDL0MODE       | 31:16        | LAYEREN   | DISABIFIL    | FORCE<br>ALPHA | MUL<br>ALPHA | _               | _             | _             | _             | ALPHA<7:0>   |             |           |              |                |           |           |          |

|                  | 15:0         |           | DESTBLE      | ND<3:0>        |              |                 | SRCBLE        | ND<3:0>       |               | —            | —           | —         | —            |                | COLOR     | /ODE<3:0> |          |

| GLCDL0START      | 31:16        | —         | _            | —              | _            |                 |               |               |               |              |             | TX<10:0>  |              |                |           |           |          |

| ecobeded and     | 15:0         | —         | _            | —              | _            |                 |               |               |               |              |             | TY<10:0>  |              |                |           |           |          |

| GLCDL0SIZE       | 31:16        | —         | —            | —              | —            |                 |               |               |               |              |             | X<10:0>   |              |                |           |           |          |

| GEODEGOIZE       | 15:0         | —         | —            | —              | —            |                 |               |               |               |              |             | Y<10:0>   |              |                |           |           |          |

| GLCDL0BADDR      | 31:16        |           |              |                |              |                 |               |               | -             | DR<31:16>    |             |           |              |                |           |           |          |

| GEOBEOBRIDBIN    | 15:0         |           |              |                |              |                 |               |               | BASEAD        | DR<15:0>     | -           |           |              | -              |           |           |          |

| GLCDL0STRIDE     | 31:16        | —         | —            | —              | —            | —               | —             | —             | —             | —            | —           | —         | —            | —              | —         | _         | —        |

| GEODEGOTABE      | 15:0         |           |              |                |              |                 |               |               | STRID         | E<15:0>      |             |           |              |                |           |           |          |

| GLCDL0RES        | 31:16        | —         | _            | —              | _            |                 |               |               |               |              |             | X<10:0>   |              |                |           |           |          |

|                  | 15:0         | —         | —            | —              | —            |                 |               |               |               |              | RES         | Y<10:0>   |              |                |           |           |          |

| GLCDL1MODE       | 31:16        | LAYEREN   |              | FORCE<br>ALPHA | MUL<br>ALPHA | _               | _             | _             | _             |              |             |           | ALPH         | IA<7:0>        |           |           |          |

|                  | 15:0         |           | DESTBLE      | ND<3:0>        |              |                 | SRCBLE        | ND<3:0>       |               |              | _           | —         | _            |                | COLOR     | /ODE<3:0> |          |

| GLCDL1START      | 31:16        |           | _            | —              | _            |                 |               |               |               |              | STAR        | TX<10:0>  |              |                |           |           |          |

| GLODEISTARI      | 15:0         | _         | _            |                | _            |                 |               |               |               |              | STAR        | TY<10:0>  |              |                |           |           |          |

DS60001379A-page 54-6

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: For the PIXELxy bits, 'x' = 0-31 and 'y' = 0-31 (i.e., GLCDCURDATA0 contains PIXEL00 through PIXEL07 with PIXEL00 in the most significant nibble).

|                  | P            |            |                 |                       | ····         | (         |              |                       |          |                             |          |                       |                 |          |           |                        |          |

|------------------|--------------|------------|-----------------|-----------------------|--------------|-----------|--------------|-----------------------|----------|-----------------------------|----------|-----------------------|-----------------|----------|-----------|------------------------|----------|

| Register<br>Name | Bit<br>Range | Bit 31/15  | Bit 30/14       | Bit 29/13             | Bit 28/12    | Bit 27/11 | Bit 26/10    | Bit 25/9              | Bit 24/8 | Bit 23/7                    | Bit 22/6 | Bit 21/5              | Bit 20/4        | Bit 19/3 | Bit 118/2 | Bit 17/1               | Bit 16/0 |

| GLCDL1SIZE       | 31:16        | —          |                 | —                     | —            |           |              |                       |          |                             | SIZE     | X<10:0>               |                 |          |           |                        |          |

| GLODETSIZE       | 15:0         | —          |                 | —                     | _            |           | SIZEY<10:0>  |                       |          |                             |          |                       |                 |          |           |                        |          |

| GLCDL1BADDR      | 31:16        |            |                 |                       |              |           |              |                       | BASEAD   | DR<31:16>                   | •        |                       |                 |          |           |                        |          |

| GLCDLIBADDR      | 15:0         |            | BASEADDR<15:0>  |                       |              |           |              |                       |          |                             |          |                       |                 |          |           |                        |          |

| GLCDL1STRIDE     | 31:16        | —          |                 | —                     | —            | —         | —            | —                     | —        | —                           | —        | —                     | —               | —        |           | —                      | —        |

| GLODETSTRIDE     | 15:0         |            | STRIDE<15:0>    |                       |              |           |              |                       |          |                             |          |                       |                 |          |           |                        |          |

| GLCDL1RES        | 31:16        |            | _               | —                     | _            |           | RESX<10:0>   |                       |          |                             |          |                       |                 |          |           |                        |          |

| GEODETIKEO       | 15:0         |            | _               | —                     | _            |           |              |                       |          |                             | RES      | SY<10:0>              |                 |          |           |                        |          |

| GLCDL2MODE       | 31:16        | LAYEREN    | DISABIFIL       | FORCE<br>ALPHA        | MUL<br>ALPHA | _         | -            | -                     | -        |                             |          |                       | ALPH            | HA<7:0>  |           |                        |          |

|                  | 15:0         |            | DESTBLE         | ND<3:0>               |              |           | SRCBLE       | ND<3:0>               |          | —                           | —        | —                     | —               |          | COLOR     | MODE<3:0>              |          |

|                  | 31:16        | —          | _               | —                     | —            |           | STARTX<10:0> |                       |          |                             |          |                       |                 |          |           |                        |          |

| GLCDL2START      | 15:0         | —          |                 | _                     | —            |           | STARTY<10:0> |                       |          |                             |          |                       |                 |          |           |                        |          |

|                  | 31:16        | —          | —               | 1 —                   | —            |           |              |                       |          |                             | SIZE     | X<10:0>               |                 |          |           |                        |          |

| GLCDL2SIZE       | 15:0         | —          |                 | —                     | —            |           |              |                       |          |                             | SIZE     | Y<10:0>               |                 |          |           |                        |          |

| GLCDL2BADDR      | 31:16        |            | BASEADDR<31:16> |                       |              |           |              |                       |          |                             |          |                       |                 |          |           |                        |          |

| GLCDLZBADDR      | 15:0         |            | BASEADDR<15:0>  |                       |              |           |              |                       |          |                             |          |                       |                 |          |           |                        |          |

| GLCDL2STRIDE     | 31:16        | —          |                 | —                     | —            | —         | —            | —                     | —        | —                           | —        | —                     | —               | —        |           | —                      | —        |

| GLCDL231 RIDE    | 15:0         |            |                 |                       |              |           |              |                       | STRID    | )E<15:0>                    |          |                       |                 |          |           |                        |          |

| GLCDL2RES        | 31:16        | -          | _               | -                     | —            |           |              |                       |          |                             | RES      | X<10:0>               |                 |          |           |                        |          |

| GLUDLZKES        | 15:0         | _          | _               | —                     | _            |           |              |                       |          |                             | RES      | SY<10:0>              |                 |          |           |                        |          |

| GLCDINT          | 31:16        | IRQCON     |                 | -                     | —            | -         | —            | -                     | -        | -                           | —        | _                     | -               | -        | —         | -                      | -        |

| GLODINI          | 15:0         |            | _               | —                     | _            | _         | —            | _                     | _        | _                           | _        | _                     | _               | —        | —         | HSYNCINT               | VSYNCIN  |

| GLCDSTAT         | 31:16        | —          | _               | —                     | —            | —         | —            | —                     | —        | —                           | —        | —                     | —               | —        | —         | —                      | -        |

| GLODSTAT         | 15:0         |            | _               | —                     | _            | _         | —            | _                     | _        | _                           | _        | LROW                  | _               | VSYNC    | HSYNC     | DE                     | ACTIVE   |

| GLCDCLUTx        | 31:16        | —          | _               | —                     | —            | —         | —            | —                     | —        |                             |          |                       | REI             | D<7:0>   |           |                        |          |

| ('x' = 0-255)    | 15:0         |            |                 |                       | GREEN        | N<7:0>    |              |                       |          | BLUE<7:0>                   |          |                       |                 |          |           |                        |          |

| GLCDCURDATAX     | 31:16        |            |                 | /<3:0> <sup>(1)</sup> |              |           |              | /<3:0> <sup>(1)</sup> |          | PIXELxy<3:0> <sup>(1)</sup> |          |                       | PIXELxy<3:0>(1) |          |           |                        |          |

| ('x' = 0-127)    | 15:0         |            | PIXELxy         | /<3:0>(1)             |              |           | PIXELxy      | /<3:0> <sup>(1)</sup> |          |                             | PIXELx   | y<3:0> <sup>(1)</sup> |                 |          | PIXEL     | xy<3:0> <sup>(1)</sup> |          |

| GLCDCURLUTx      | 31:16        | _          |                 | —                     | —            | —         |              | —                     | —        |                             |          |                       | REI             | D<7:0>   |           |                        |          |

| ('x' = 0-15)     | 15:0         | GREEN<7:0> |                 |                       |              |           |              |                       |          |                             |          | BLU                   | E<7:0>          |          |           |                        |          |

|                  |              |            |                 |                       |              |           |              |                       |          |                             |          |                       |                 |          |           |                        |          |

#### Table 54-1: Graphics LCD Controller Register Map (Continued)

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note

1:

For the PIXELxy bits, 'x' = 0-31 and 'y' = 0-31 (i.e., GLCDCURDATA0 contains PIXEL00 through PIXEL07 with PIXEL00 in the most significant nibble).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 31:24        | LCDEN             | CURSOR<br>EN      | _                 | VSYNC<br>POL      | HSYNC<br>POL      | DEPOL             | _                | DITHER           |

|              | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 23:16        | VSYNC<br>CYC      | PCLKPOL           | —                 | PGRAMP<br>EN      | FORCE<br>BLANK    |                   | —                | Ι                |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | -                 | -                 | -                 | -                 | -                 |                   | YUV<br>OUTPUT    | FORMAT<br>CLK    |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | F                 | RGBSEQ<2:0        | >                 | _                 | _                 |                   | _                |                  |

## Register 54-1: GLCDMODE: Graphics LCD Controller Mode Register

| Legend | • |

|--------|---|

| Legenu | • |

| - <b>J</b>        |                  |                      |                                    |  |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

| bit 31 | LCDEN: LCD Controller Module Enable bit<br>1 = LCD Controller module is enabled<br>0 = LCD Controller module is not enabled     |

|--------|---------------------------------------------------------------------------------------------------------------------------------|

| bit 30 | <b>CURSOREN:</b> Programmable Cursor Enable bit<br>1 = Programmable cursor is enabled<br>0 = Programmable cursor is enabled     |

| bit 29 | Unimplemented: Read as '0'                                                                                                      |

| bit 28 | VSYNCPOL: Vertical Sync Polarity bit                                                                                            |

|        | <ul><li>1 = VSYNC polarity is negative</li><li>0 = VSYNC polarity is positive</li></ul>                                         |

| bit 27 | HSYNCPOL: Horizontal Sync Polarity bit                                                                                          |

|        | <ul><li>1 = HSYNC polarity is negative</li><li>0 = HSYNC polarity is positive</li></ul>                                         |

| bit 26 | DEPOL: DE Polarity bit                                                                                                          |

|        | <ul><li>1 = DE polarity is negative</li><li>0 = DE polarity is positive</li></ul>                                               |

| bit 25 | Unimplemented: Read as '0'                                                                                                      |

| bit 24 | DITHER: Dithering Enable bit                                                                                                    |

|        | <ul><li>1 = Dithering is enabled</li><li>0 = Dithering is not enabled</li></ul>                                                 |

| bit 23 | VSYNCCYC: Vertical Sync for Single Cycle Per Line Enable bit                                                                    |

|        | <ul><li>1 = VSYNC for a single cycle per line is enabled</li><li>0 = VSYNC for a single cycle per line is not enabled</li></ul> |

| bit 22 | PCLKPOL: Pixel Clock Out Polarity bit                                                                                           |

|        | <ul><li>1 = Pixel clock out polarity is negative</li><li>0 = Pixel clock out polarity is positive</li></ul>                     |

| bit 21 | Unimplemented: Read as '0'                                                                                                      |

| bit 20 | PGRAMPEN: Palette Gamma Ramp Enable bit                                                                                         |

|        | <ul><li>1 = Palette gamma ramp is enabled</li><li>0 = Palette gamma ramp is not enabled</li></ul>                               |

|        |                                                                                                                                 |

## Register 54-1: GLCDMODE: Graphics LCD Controller Mode Register (Continued)

- bit 19 FORCEBLANK: Force Output to Blank bit

- 1 = Forces output to blank

- 0 = No effect

- bit 18-10 Unimplemented: Read as '0'

- bit 9 YUVOUTPUT: YUV Output Enable bit

- 1 = YUV is enabled

- 0 = RGB is enabled

- bit 8 FORMATCLK: Formatting Clock Divide Enable bit

- 1 = Formatting clock is not divided

- 0 = Formatting clock is divided

- bit 7-5 RGBSEQ<2:0>: RGB Sequential Mode Enable bit

- 111 **= BT.656**

- 110 = YUYV

- 101 = Reserved

- 100 = Reserved

- 011 = Reserved

- 010 = Reserved

- 001 = Reserved

- 000 = Parallel RGB (RGB888, RGB666, RGB323)

- bit 4-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |  |  |

| 15.0         | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | —                 | LPREFETCH<5:0>    |                   |                   |                   |                  |                  |  |  |

| 7:0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   | —                 |                   |                   | CLKDI             | V<5:0>            |                  |                  |  |  |

## Register 54-2: GLCDCLKCON: Graphics LCD Controller Clock Control Register

## Legend:

| 11 | Legena.          |                  |                                    |                    |  |  |  |

|----|------------------|------------------|------------------------------------|--------------------|--|--|--|

| I  | R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -  | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-14 Unimplemented: Read as '0'

bit 13-8 LPREFETCH<5:0>: Lines Prefetch bits

These bits represent the number of lines to be prefetched before starting the frame (through DMA). The maximum value is 2<sup>LPREFETCH</sup> = 32.

#### bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **CLKDIV<5:0>:** Clock Divider bits

- 111111 = Reserved 111110 = Reserved . . 011111 = Divided by 31 01110 = Divided by 30 011101 = Divided by 29 . . . 000011 = Divided by 3 000010 = Divided by 2 000001 = Divided by 1 000000 = Divided by 0

| Note: | If the value of CLKDIV<5:0> is even, PCLK = (PLL_CLOCK/CLOCKDIV) with a duty cycle of 50%. If the |

|-------|---------------------------------------------------------------------------------------------------|

|       | value of CLKDIV<5:0> is odd, PCLK = (PLL_CLOCK/CLOCKDIV) with a duty cycle of 60 to 40%.          |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | RED<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | GREEN<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | BLUE<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | ALPHA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

## Register 54-3: GLCDBGCOLOR: Graphics LCD Controller Background Color Register

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-24 **RED<7:0>:** Color Red as Background bits

These bits specify that the color red is to be used as the background color.

bit 23-16 **GREEN<7:0>:** Color Green as Background bits These bits specify that the color red is to be used as the background color.

bit 15-8 **BLUE<7:0>:** Color Blue as Background bits These bits specify that the color red is to be used as the background color. bit 7-0 **ALPHA<7:0>:** Color Alpha as Background bits

These bits specify that the color alpha is to be used as the background color.

Note: If all of the bits in this register are set (RED, GREEN, BLUE and ALPHA), RGBA color is used as the background.

| Negister .   | Register 34-4. GLCDRES. Graphics ECD Controller Resolution Register |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|---------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | U-0                                                                 | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | —                                                                   | —                 | _                 | _                 | —                 |                   | RESX<10:8>       |                  |  |  |

| 00.40        | R/W-0                                                               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | RESX<7:0>                                                           |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0                                                               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                                                                   | —                 | —                 | _                 | —                 |                   | RESY<10:8>       |                  |  |  |

| 7:0          | R/W-0                                                               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                                                                     |                   |                   | RESY<             | <7:0>             |                   |                  |                  |  |  |

## Register 54-4: GLCDRES: Graphics LCD Controller Resolution Register

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

bit 26-16 **RESX<10:0>:** X Dimension Pixel Resolution bits These bits specify the pixel resolution for the X dimension.

bit 15-11 Unimplemented: Read as '0'

bit 10-0 **RESY<10:0>:** Y Dimension Pixel Resolution bits These bits specify the pixel resolution for the Y dimension.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | —                 | —                 | —                 |                   | -                 | FP                | ORCHX<10:        | 8>               |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FPORCHX<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | —                 | —                 | _                 | _                 | FP                | ORCHY<10:        | 8>               |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | FPORCH            | Y<7:0>            |                   |                  |                  |  |  |

### Register 54-5: GLCDFPORCH: Graphics LCD Controller Front Porch Register

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

- bit 26-16 **FPORCHX<10:0>:** X Dimension Front Porch Lines bits These bits specify the front porch X dimension lines.

- bit 15-11 Unimplemented: Read as '0'

- bit 10-0 **FPORCHY<10:0>:** Y Dimension Front Porch Pixel Clocks bits These bits specify the front porch Y dimension pixel clocks.

| Register 54-6:  | GLCDBLANKING: Grau | ohics LCD Controller Blanking Register |  |

|-----------------|--------------------|----------------------------------------|--|

| nogiotor e i ei |                    |                                        |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | —                 | —                 | —                 | _                 | —                 | BLA               | NKINGX<10        | ):8>             |  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | BLANKINGX<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | —                 | —                 | _                 | _                 | BLA               | NKINGY<10        | ):8>             |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | BLANKING          | GY<7:0>           |                   |                  |                  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

bit 26-16 BLANKINGX<10:0>: X Dimension Blanking Period bits

These bits specify the HSYNC pulse length for the X dimension blanking period.

bit 15-11 Unimplemented: Read as '0'

bit 10-0 **BLANKINGY<10:0>:** Y Dimension Blanking Period bits These bits specify the VSYNC lines for the Y dimension blanking period.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | —                 | —                 | —                 |                   | -                 | BP                | ORCHX<10:        | 8>               |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | BPORCHX<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | —                 | —                 | _                 | _                 | BP                | ORCHY<10:        | 8>               |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | BPORCH            | Y<7:0>            |                   |                  |                  |  |  |

### Register 54-7: GLCDBPORCH: Graphics LCD Controller Back Porch Register

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

- bit 26-16 BPORCHX<10:0>: X Dimension Back Porch Lines bits These bits specify the front porch X dimension lines.

- bit 15-11 Unimplemented: Read as '0'

- bit 10-0 **BPORCHY<10:0>:** Y Dimension Back Porch Pixel Clocks bits These bits specify the front porch Y dimension pixel clocks.

| <u> </u>     |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | —                 | —                 | —                 | _                 | —                 | CU                | RSORX<10:        | 8>               |  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CURSORX<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | —                 | —                 | _                 | _                 | CU                | RSORY<10:        | 8>               |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | CURSOR            | Y<7:0>            |                   |                  |                  |  |  |

Register 54-8: GLCDCURSOR: Graphics LCD Controller Cursor Register

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

bit 26-16 **CURSORX<10:0>:** Cursor X Dimension Position bits These bits specify the X dimension position of the cursor

bit 15-11 Unimplemented: Read as '0'

bit 10-0 **CURSORY<10:0>:** Cursor Y Dimension Position bits These bits specify the Y dimension position of the cursor

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | LAYEREN           | DISABIFIL         | FORCE<br>ALPHA    | MUL<br>ALPHA      | —                 | —                 | —                | —                |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        |                   |                   |                   | ALPHA             | <7:0>             |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | DESTBLEND<3:0>    |                   |                   |                   | SRCBLEND<3:0>     |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | _                 | _                 | _                 |                   | COLORM            | ODE<3:0>         |                  |  |

## Register 54-9: GLCDLxMODE: Graphics LCD Controller Layer 'x' Mode Register ('x' = 0-2)

| 7:0        | _                                                                | —                                         | —               | _             |                 | COLORM       | 10DE<3:0>     |       |  |  |  |  |

|------------|------------------------------------------------------------------|-------------------------------------------|-----------------|---------------|-----------------|--------------|---------------|-------|--|--|--|--|

|            |                                                                  |                                           |                 |               |                 |              |               |       |  |  |  |  |

| Legend:    |                                                                  |                                           |                 |               |                 |              |               |       |  |  |  |  |

| R = Read   | able bit                                                         |                                           | W = Writable    | e bit         | U = Unimple     | emented bit, | read as '0'   |       |  |  |  |  |

| -n = Value | e at POR                                                         |                                           | '1' = Bit is se | t             | '0' = Bit is cl | leared       | x = Bit is un | known |  |  |  |  |

|            |                                                                  |                                           |                 |               |                 |              |               |       |  |  |  |  |

| bit 31     | LAYEREN: Layer Enable bit                                        |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 1 = Layer is enabled                                             |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 0 = Layer is not enabled                                         |                                           |                 |               |                 |              |               |       |  |  |  |  |

| bit 30     | DISABIFIL: D                                                     | DISABIFIL: Disable Bilinear Filtering bit |                 |               |                 |              |               |       |  |  |  |  |

|            | 1 = Bilinear filtering is enabled                                |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 0 = Bilinear fil                                                 | ltering is not e                          | nabled          |               |                 |              |               |       |  |  |  |  |

| bit 29     | FORCEALPH                                                        | IA: Force Alph                            | na with Globa   | l Alpha bit   |                 |              |               |       |  |  |  |  |

|            | 1 = Force alpha with global alpha is enabled                     |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 0 = Force alpha with global alpha is not enabled                 |                                           |                 |               |                 |              |               |       |  |  |  |  |

| bit 28     | MULALPHA: Premultiply Image Alpha bit                            |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 1 = Premultiply image alpha is enabled                           |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 0 = Premultiply image alpha is not enabled                       |                                           |                 |               |                 |              |               |       |  |  |  |  |

| bit 27-24  | Unimplement                                                      | ted: Read as                              | '0'             |               |                 |              |               |       |  |  |  |  |

| bit 23-16  | ALPHA<7:0>                                                       | : Layer Alpha                             | bits            |               |                 |              |               |       |  |  |  |  |

|            | These bits contain the Layer Alpha value ranging from 0 to 0xFF. |                                           |                 |               |                 |              |               |       |  |  |  |  |

| bit 15-12  | DESTBLEND                                                        | <3:0>: Destin                             | ary Blending    | Function bits |                 |              |               |       |  |  |  |  |

|            | 1111 = Reserved                                                  |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 1110 = Reser                                                     | rved                                      |                 |               |                 |              |               |       |  |  |  |  |

|            | 1101 = Blend inverted destination                                |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 1100 = Reser                                                     |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 1011 = Reser<br>1010 = Blend                                     |                                           | ation           |               |                 |              |               |       |  |  |  |  |

|            | 1001 = Reser                                                     |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 1000 = Reser                                                     | rved                                      |                 |               |                 |              |               |       |  |  |  |  |

|            | 0111 = Blend                                                     | l inverted sour                           | rce and inverte | ed global     |                 |              |               |       |  |  |  |  |

|            | 0110 = Blend                                                     | 0                                         |                 |               |                 |              |               |       |  |  |  |  |

|            | 0101 = Blend                                                     |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 0100 = Blend<br>0011 = Blend                                     |                                           | and alpha glo   | odal          |                 |              |               |       |  |  |  |  |

|            | 0011 = Blend                                                     |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            |                                                                  |                                           |                 |               |                 |              |               |       |  |  |  |  |

|            | 0001 = Blend                                                     | I white                                   |                 |               |                 |              |               |       |  |  |  |  |

## Register 54-9: GLCDLxMODE: Graphics LCD Controller Layer 'x' Mode Register ('x' = 0-2) (Continued)

bit 11-8 SRCBLEND<3:0>: Source Blending Function bits

- 1111 = Reserved

- 1110 = Reserved

- 1101 = Blend inverted destination

- 1100 = Reserved

- 1011 = Reserved

- 1010 = Blend alpha destination

- 1001 = Reserved

- 1000 = Reserved

- 0111 = Blend inverted source and inverted global

- 0110 = Blend inverted global

- 0101 = Blend inverted source

- 0100 = Blend alpha source and alpha global

- 0011 = Blend alpha global

- 0010 = Blend alpha source

- 0001 = Blend white

- 0000 = Blend black

- bit 7-4 Unimplemented: Read as '0'

#### bit 3-0 COLORMODE<3:0>: Color Mode bits

- 1111 = Reserved

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Reserved

- 1011 = RGB888 color format

- 1010 = YUYV color format

- 1001 = L4 gray scale/palette format

- 1000 = L1 gray scale/palette format

- 0111 = L8 gray scale/palette format

- 0110 = 32-bit ARGB8888 color format

- 0101 = 16-bit RGB565 color format

- 0100 = 8-bit RGB332 color format

- 0011 = Reserved

- 0010 = 32-bit RGBA8888 color format

- 0001 = 16-bit RGBA5551 color format

- 0000 = 8-bit color palette look-up table (LUT8)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | —                 |                   |                   |                   | —                 | S                 | TARTX<10:8       | ~                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | STARTX            | (<7:0>            |                   |                  |                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | _                 | _                 | _                 | —                 | S                 | TARTY<10:8       | ~                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | STARTY            | <7:0>             |                   |                  |                  |

### **Register 54-10:** GLCDLxSTART: Graphics LCD Controller Layer 'x' Start Register ('x' = 0-2)

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

- bit 26-16 STARTX<10:0>: Layer Start X Dimension bits

- These bits specify the pixel offset of the starting X dimension of the layer.

- bit 15-11 **Unimplemented:** Read as '0'

- bit 10-0 **STARTY<10:0>:** Layer Start Y Dimension bits These bits specify the pixel offset of the starting Y dimension of the layer.

## Register 54-11: GLCDLxSIZE: Graphics LCD Controller Layer 'x' SIZE Register ('x' = 0-2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0                    |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | 5                 | SIZEX<10:8>      | ZEX<10:8><br>R/W-0 R/W-0 |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                    |  |  |

| 23:16        |                   |                   |                   | SIZEX             | <7:0>             |                   |                  |                          |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0                    |  |  |

| 15:8         | —                 | _                 | —                 | _                 | _                 | SIZEY<10:8>       |                  |                          |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                    |  |  |

| 7:0          |                   |                   |                   | SIZEY             | <7:0>             |                   |                  |                          |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'

bit 26-16 SIZEX<10:0>: Layer Size X Dimension bits

These bits specify the pixel size of the layer in the X dimension.

- bit 15-11 Unimplemented: Read as '0'

- bit 10-0 **SIZEY<10:0>:** Layer size Y Dimension bits These bits specify the pixel size of the layer in the Y dimension.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   |                   | BASEADD           | R<31:24>          |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | BASEADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | BASEADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | BASEADE           | )R<7:0>           |                   |                  |                  |  |

## Register 54-12: GLCDLxBADDR: Graphics LCD Controller Layer 'x' Base Address Register ('x' = 0-2)

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-0 **BASEADDR<31:0>:** Base Address of the Framebuffer bits These bits specify the base address of the framebuffer.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | —                 | _                 |                   |                   | _                 | -                |                  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   | STRIDE<15:8>      |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | STRIDE            | <7:0>             |                   |                  |                  |  |

#### **Register 54-13:** GLCDLxSTRIDE: Graphics LCD Controller Layer 'x' Stride Register ('x' = 0-2)

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 **Unimplemented:** Read as '0'

bit 15-0 STRIDE<15:0>: Layer Stride bits

These bits specify the distance from line to line in bytes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | —                 | _                 | _                 | _                 | —                 | I                 | RESX<10:8>       |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        |                   |                   |                   | RESX<             | <7:0>             |                   |                  | R/W-0<br>R/W-0   |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | I                 | RESY<10:8>       |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | RESY<             | <7:0>             |                   |                  |                  |  |  |

## Register 54-14: GLCDLxRES: Graphics LCD Controller Layer 'x' Resolution Register ('x' = 0-2)

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-27 Unimplemented: Read as '0'