# **Intel<sup>®</sup> High Level Synthesis Compiler**

# **Best Practices Guide**

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **19.1**

# Contents

| 1. Intel <sup>®</sup> HLS Compiler Best Practices Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2. Best Practices for Coding and Compiling Your Component5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 3. Interface Best Practices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 3.1. Choose the Right Interface for Your Component.73.1.1. Pointer Interfaces.83.1.2. Avalon Memory Mapped Master Interfaces.103.1.3. Avalon Memory Mapped Slave Interfaces.133.1.4. Avalon Streaming Interfaces.153.1.5. Pass-by-Value Interface.173.2. Avoid Pointer Aliasing.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 4. Loop Best Practices20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 4.1. Reuse Hardware By Calling It In a Loop.214.2. Parallelize Loops.224.2.1. Pipeline Loops.224.2.2. Unroll Loops.244.2.3. Example: Loop Pipelining and Unrolling.244.3. Construct Well-Formed Loops.274.4. Minimize Loop-Carried Dependencies.274.5. Avoid Complex Loop-Exit Conditions.284.6. Convert Nested Loops into a Single Loop.294.7. Declare Variables in the Deepest Scope Possible.295. Memory Architecture Best Practices.31                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| <ul> <li>5.1. Example: Overriding a Coalesced Memory Architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture.       31         5.2. Example: Overriding a Banked Memory Architecture.       33         5.3. Merge Memories to Reduce Area.       34         5.3.1. Example: Merging Memories Depth-Wise.       35         5.3.2. Example: Merging Memories Width-Wise.       37         5.4. Example: Specifying Bank-Selection Bits for Local Memory Addresses.       39         6. Image System of Tasks.       45                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture.       31         5.2. Example: Overriding a Banked Memory Architecture.       33         5.3. Merge Memories to Reduce Area.       34         5.3.1. Example: Merging Memories Depth-Wise.       35         5.3.2. Example: Merging Memories Width-Wise.       37         5.4. Example: Specifying Bank-Selection Bits for Local Memory Addresses.       39         6. Image: System of Tasks.       45         6.1. Image: Executing Multiple Loops in Parallel.       45                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture.       31         5.2. Example: Overriding a Banked Memory Architecture.       33         5.3. Merge Memories to Reduce Area.       34         5.3.1. Example: Merging Memories Depth-Wise.       35         5.3.2. Example: Merging Memories Width-Wise.       37         5.4. Example: Specifying Bank-Selection Bits for Local Memory Addresses.       39         6. Image: System of Tasks.       45         6.1. Image: Executing Multiple Loops in Parallel.       45         6.2. Image: Sharing an Expensive Compute Block.       46                                                                                                                                                                                |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture.       31         5.2. Example: Overriding a Banked Memory Architecture.       33         5.3. Merge Memories to Reduce Area.       34         5.3.1. Example: Merging Memories Depth-Wise.       35         5.3.2. Example: Merging Memories Width-Wise.       37         5.4. Example: Specifying Bank-Selection Bits for Local Memory Addresses.       39         6. Implementing Multiple Loops in Parallel.       45         6.1. Implementing a Hierarchical Design.       46                                                                                                                                                                                                                                         |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture.       31         5.2. Example: Overriding a Banked Memory Architecture.       33         5.3. Merge Memories to Reduce Area.       34         5.3.1. Example: Merging Memories Depth-Wise.       35         5.3.2. Example: Merging Memories Width-Wise.       37         5.4. Example: Specifying Bank-Selection Bits for Local Memory Addresses.       39         6. PD       System of Tasks.       45         6.1. PRD       Executing Multiple Loops in Parallel.       45         6.2. PRD       Sharing an Expensive Compute Block.       46         6.3. PRD       Implementing a Hierarchical Design.       46         6.4. PRD       Avoiding Potential Performance Pitfalls.       46                           |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture.       31         5.2. Example: Overriding a Banked Memory Architecture.       33         5.3. Merge Memories to Reduce Area.       34         5.3.1. Example: Merging Memories Depth-Wise.       35         5.3.2. Example: Merging Memories Width-Wise.       37         5.4. Example: Specifying Bank-Selection Bits for Local Memory Addresses.       39         6. Implementing Multiple Loops in Parallel.       45         6.1. Implementing a Hierarchical Design.       46                                                                                                                                                                                                                                         |  |  |  |  |  |

| 5.1. Example: Overriding a Coalesced Memory Architecture.       31         5.2. Example: Overriding a Banked Memory Architecture.       33         5.3. Merge Memories to Reduce Area.       34         5.3.1. Example: Merging Memories Depth-Wise.       35         5.3.2. Example: Merging Memories Width-Wise.       37         5.4. Example: Specifying Bank-Selection Bits for Local Memory Addresses.       39         6. Image: System of Tasks.       45         6.1. Image: Executing Multiple Loops in Parallel.       45         6.2. Image: Sharing an Expensive Compute Block.       46         6.3. Image: Avoiding Potential Performance Pitfalls.       46         7. Datatype Best Practices.       48         7.1. Avoid Implicit Data Type Conversions.       49 |  |  |  |  |  |

Contents

##

# **1. Intel<sup>®</sup> HLS Compiler Best Practices Guide**

The *Intel*<sup>®</sup> *HLS Compiler Best Practices Guide* provides techniques and practices that you can apply to improve the FPGA area utilization and performance of your HLS component. Typically, you apply these best practices after you verify the functional correctness of your component.

The features and devices supported by the Intel HLS Compiler depend on what edition of Intel Quartus<sup>®</sup> Prime you have. The following icons indicate content in this publication that applies only to the Intel HLS Compiler provided with a certain edition of Intel Quartus Prime:

Indicates that a feature or content applies only to Intel HLS Compiler Pro Edition.

Indicates that a feature or content applies only to Intel HLS Compiler Standard Edition.

In this publication, <quartus\_installdir> refers to the location where you installed Intel Quartus Prime Design Suite. The Intel High Level Synthesis (HLS) Compiler is installed as part of your Intel Quartus Prime Design Suite installation.

The default Intel Quartus Prime Design Suite installation location depends on your operating system and your Intel Quartus Prime edition:

| PRO | Windows | C:\intelFPGA_pro\19.1                                |

|-----|---------|------------------------------------------------------|

|     | Linux   | /home/ <username>/intelFPGA_pro/19.1</username>      |

| STD | Windows | C:\intelFPGA_standard\19.1                           |

|     | Linux   | /home/ <username>/intelFPGA_standard/19.1</username> |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **2. Best Practices for Coding and Compiling Your Component**

After you verify the functional correctness of your component, you might want to improve the performance and FPGA area utilization of your component. Learn about the best practices for coding and compiling your component so that you can determine which best practices can help you best optimize your component.

As you look at optimizing your component, apply the best practices techniques in the following areas, roughly in the order listed. Also, review the examples designs and tutorials provided with the Intel High Level Synthesis (HLS) Compiler to see examples of how some of these techniques can be implemented.

Interface Best Practices on page 6

With the Intel High Level Synthesis Compiler, your component can have a variety of interfaces: from basic wires to the Avalon Streaming and Avalon Memory-Mapped Master interfaces. Review the interface best practices to help you choose and configure the right interface for your component.

Loop Best Practices on page 20

The Intel High Level Synthesis Compiler pipelines your loops to enhance throughput. Review the loop best practices to learn techniques to optimize your loops to boost the performance of your component.

Memory Architecture Best Practices on page 31

The Intel High Level Synthesis Compiler infers efficient memory architectures (like memory width, number of banks and ports) in a component by adapting the architecture to the memory access patterns of your component. Review the memory architecture best practices to learn how you can get the best memory architecture for your component from the compiler.

Datatype Best Practices on page 48

The datatypes in your component and possible conversions or casting that they might undergo can significantly affect the performance and FPGA area usage of your component. Review the datatype best practices for tips and guidance how best to control datatype sizes and conversions in your component.

Alternative Algorithms

The Intel High Level Synthesis Compiler lets you compile a component quickly to get initial insights into the performance and area utilization of your component. Take advantage of this speed to try larger algorithm changes to see how those changes affect your component performance.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **3. Interface Best Practices**

With the Intel High Level Synthesis Compiler, your component can have a variety of interfaces: from basic wires to the Avalon Streaming and Avalon Memory-Mapped Master interfaces. Review the interface best practices to help you choose and configure the right interface for your component.

Each interface type supported by the Intel HLS Compiler has different benefits. However, the system that surrounds your component might limit your choices. Keep your requirements in mind when determining the optimal interface for your component.

#### **Demonstrating Interface Best Practices**

The Intel HLS Compiler comes with a number of tutorials that give you working examples to review and run so that you can see good coding practices as well as demonstrating important concepts.

Review the following tutorials to learn about different interfaces as well as best practices that might apply to your design:

| Tutorial                                                                                   | Description                                                                                                                                         |  |  |  |  |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| You can find these tutorials in the following location on your Intel Quartus Prime system: |                                                                                                                                                     |  |  |  |  |

| <guartus_installdir>/hls/examples/tutorials</guartus_installdir>                           |                                                                                                                                                     |  |  |  |  |

| interfaces/overview                                                                        | Demonstrates the effects on quality-of-results (QoR) of choosing different component interfaces even when the component algorithm remains the same. |  |  |  |  |

| best_practices/<br>parameter_aliasing                                                      | Demonstrates the use of therestrict keyword on component<br>arguments<br>Demonstrates the use of the restrict keyword on component<br>arguments.    |  |  |  |  |

| interfaces/<br>explicit_streams_buffer                                                     | Demonstrates how to use explicit stream_in and stream_out interfaces in the component and testbench.                                                |  |  |  |  |

| <pre>pro interfaces/ explicit_streams_packets_read y_empty</pre>                           | Demonstrates how to use the usesPackets, usesEmpty, and firstSymbolInHighOrderBits stream template parameters.                                      |  |  |  |  |

| <pre>interfaces/ explicit_streams_packets_read y_valid</pre>                               | Demonstrates how to use the usesPackets, usesValid, and usesReady stream template parameters.                                                       |  |  |  |  |

| explicit_streams_ready_latenc                                                              | Demonstrates how to achieve a better loop initiation interval (II) with stream write using the readyLatency stream template parameter.              |  |  |  |  |

|                                                                                            | continued                                                                                                                                           |  |  |  |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### 3. Interface Best Practices UG-20107 | 2019.04.01

| Tutorial                                     | Description                                                                                                                      |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| interfaces/<br>mm_master_testbench_operators | Demonstrates how to invoke a component at different indicies of an Avalon Memory Mapped (MM) Master (mm_master class) interface. |  |  |

| interfaces/mm_slaves                         | Demonstrates how to create Avalon-MM Slave interfaces (slave registers and slave memories).                                      |  |  |

| interfaces/<br>multiple_stream_call_sites    | Demonstrates the benefits of using multiple stream call sites.                                                                   |  |  |

| interfaces/pointer_mm_master                 | Demonstrates how to create Avalon-MM Master interfaces and control their parameters.                                             |  |  |

| interfaces/stable_arguments                  | Demonstrates how to use the stable attribute for unchanging arguments to improve resource utilization.                           |  |  |

#### **Related Information**

- Avalon Memory-Mapped Interface Specifications

- Avalon Streaming Interface Specifications

## **3.1.** Choose the Right Interface for Your Component

Different component interfaces can affect the quality of results (QoR) of your component without changing your component algorithm. Consider the effects of different interfaces before choosing the interface for your component.

The best interface for your component might not be immediately apparent, so you might need to try different interfaces for your component to achieve the optimal QoR. Take advantage of the rapid component compilation time provided by the Intel HLS Compiler and the resulting High Level Design reports to determine which interface gives you the optimal QoR for your component.

This section uses a vector addition example to illustrate the impact of changing the component interface while keeping the component algorithm the same. The example has two input vectors, vector a and vector b, and stores the result to vector c. The vectors have a length of  $\mathbb{N}$  (which could be very large).

The core algorithm is as follows:

```

#pragma unroll 8

for (int i = 0; i < N; ++i) {

c[i] = a[i] + b[i];

}</pre>

```

The Intel HLS Compiler extracts the parallelism of this algorithm by pipelining the loops if no loop dependency exists. In addition, by unrolling the loop (by a factor of 8), more parallelism can be extracted.

Ideally, the generated component has a latency of N/8 cycles. In the examples in the following section, a value of 1024 is used for N, so the ideal latency is 128 cycles (1024/8).

The following sections present variations of this example that use different interfaces. Review these sections to learn how different interfaces affect the QoR of this component.

You can work your way through the variations of these examples by reviewing the tutorial available in <quartus\_installdir>/hls/examples/tutorials/ interfaces/overview.

## 3.1.1. Pointer Interfaces

Software developers accustomed to writing code that targets a CPU might first try to code this algorithm by declaring vectors a, b, and c as pointers to get the data in and out of the component. Using pointers in this way results in a single Avalon Memory-Mapped (MM) Master interface that the three input variables share.

Pointers in a component are implemented as Avalon<sup>®</sup> Memory Mapped (Avalon-MM) master interfaces with default settings. For more details about pointer parameter interfaces, see Intel HLS Compiler Default Interfaces in Intel High Level Synthesis Compiler Reference Manual.

The vector addition component example with pointer interfaces can be coded as follows:

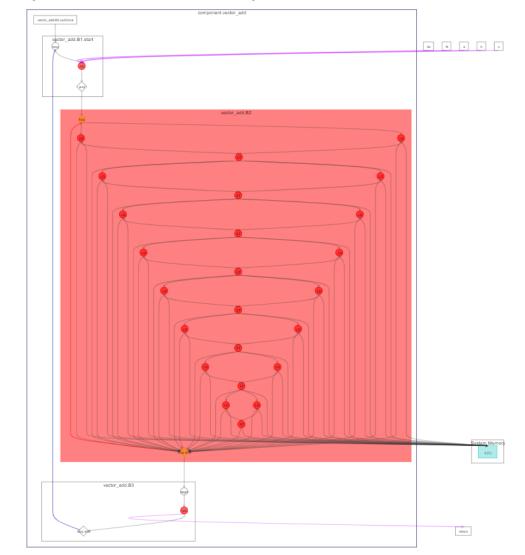

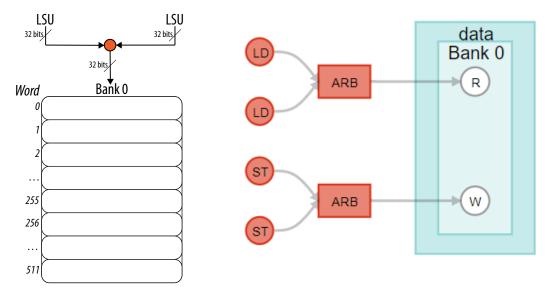

The following diagram shows the Component Viewer report generated when you compile this example. Because the loop is unrolled by a factor of 8, the diagram shows that vector\_add.B2 has 8 loads for vector a, 8 loads for vector b, and 8 stores for vector c. In addition, all of the loads and stores are arbitrated on the same memory, resulting in inefficient memory accesses.

#### Figure 1. Component View of vector\_add Component with Pointer Interfaces

The following Loop Analysis report shows that the component has an undesirably high loop initiation interval (II). The II is high because vectors a, b, and c are all accessed through the same Avalon-MM Master interface. The Intel HLS Compiler uses stallable arbitration logic to schedule these accesses, which results in poor performance and high FPGA area use.

In addition, the compiler cannot assume there are no data dependencies between loop iterations because pointer aliasing might exist. The compiler cannot determine that vectors a, b, and c do not overlap. If data dependencies exist, the Intel HLS Compiler cannot pipeline the loop iterations effectively.

| Loops analysis                                                               | Show fully unrolled loops |      |            |                                |

|------------------------------------------------------------------------------|---------------------------|------|------------|--------------------------------|

|                                                                              | Pipelined                 | П    | Bottleneck | Details                        |

| Component: vector_add<br>(part_1_pointers.cpp:8)                             |                           |      |            | Task<br>function               |

| vector_add.B1.start (Component invocation)                                   | No                        | n/a  | n/a        | Out-of-<br>order inner<br>loop |

| 8X Partially unrolled vector_add.B2 <sup>\</sup><br>(part_1_pointers.cpp:10) | Yes                       | ~508 | П          | Memory<br>dependency           |

|                                                                              |                           |      |            | Ţ                              |

Compiling the component with an Intel Quartus Prime compilation flow targeting an Intel Arria<sup>®</sup> 10 device results in the following QoR metrics, including high ALM usage, high latency, high II, and low  $f_{MAX}$ . All of which are undesirable properties in a component.

#### Table 1. QoR Metrics for a Component with a Pointer Interface<sup>1</sup>

| QoR Metric                          | Value   |

|-------------------------------------|---------|

| ALMs                                | 15593.5 |

| DSPs                                | 0       |

| RAMs                                | 30      |

| f <sub>MAX</sub> (MHz) <sup>2</sup> | 298.6   |

| Latency (cycles)                    | 24071   |

| Initiation Interval (II) (cycles)   | ~508    |

<sup>1</sup>The compilation flow used to calculate the QoR metrics used Intel Quartus Prime Pro Edition Version 17.1.

$^2 \text{The } f_{\text{MAX}}$  measurement was calculated from a single seed.

## 3.1.2. Avalon Memory Mapped Master Interfaces

By default, pointers in a component are implemented as Avalon Memory Mapped (Avalon-MM) master interfaces with default settings. You can mitigate poor performance from the default settings by configuring the Avalon-MM master interfaces.

You can configure the Avalon-MM master interface for the vector addition component example using the ihc::mm\_master class as follows:

```

component void vector_add(

ihc::mm_master<int, ihc::aspace<l>, ihc::dwidth<8*8*sizeof(int)>,

ihc::align<8*sizeof(int)> >& a,

```

The memory interfaces for vector  ${\tt a},$  vector  ${\tt b},$  and vector  ${\tt c}$  have the following attributes specified:

• The vectors are each assigned to different address spaces with the ihc::aspace attribute, and each vector receives a separate Avalon-MM master interface.

With the vectors assigned to different physical interfaces, the vectors can be accessed concurrently without interfering with each other, so memory arbitration is not needed.

- The width of the interfaces for the vectors is adjusted with the ihc::dwidth attribute.

- The alignment of the interfaces for the vectors is adjusted with the ihc::align attribute.

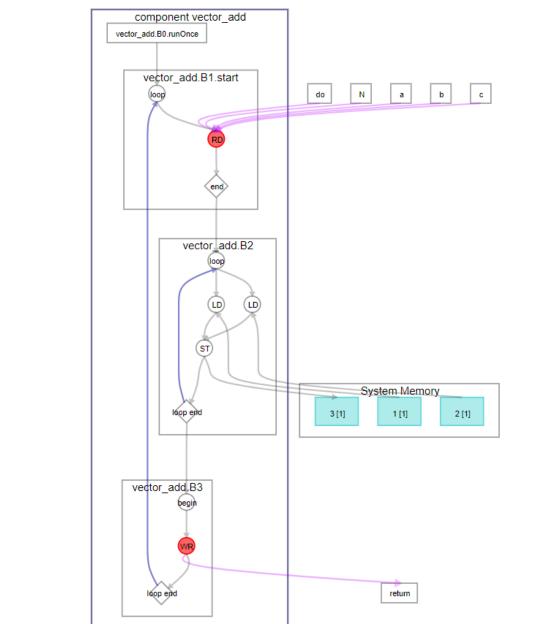

The following diagram shows the Component Viewer report generated when you compile this example.

#### Figure 2. Component View of vector\_add Component with Avalon-MM Master Interface

The diagram shows that vector\_add.B2 has two loads and one store. The default Avalon-MM Master settings used by the code example in Pointer Interfaces on page 8 had 16 loads and 8 stores.

By expanding the width and alignment of the vector interfaces, the original pointer interface loads and stores were coalesced into one wide load each for vector a and vector b, and one wide store for vector c.

Also, the memories are stall-free because the loads and stores in this example access separate memories.

Compiling this component with an Intel Quartus Prime compilation flow targeting an Intel Arria 10 device results in the following QoR metrics:

| QoR Metric                          | Pointer | Avalon-MM Master |

|-------------------------------------|---------|------------------|

| ALMs                                | 15593.5 | 643              |

| DSPs                                | 0       | 0                |

| RAMs                                | 30      | 0                |

| f <sub>MAX</sub> (MHz) <sup>2</sup> | 298.6   | 472.37           |

| Latency (cycles)                    | 24071   | 142              |

| Initiation Interval (II) (cycles)   | ~508    | 1                |

#### Table 2. QoR Metrics Comparison for Avalon-MM Master Interface<sup>1</sup>

<sup>1</sup>The compilation flow used to calculate the QoR metrics used Intel Quartus Prime Pro Edition Version 17.1.

$^2 \mbox{The } f_{\mbox{MAX}}$  measurement was calculated from a single seed.

All QoR metrics improved by changing the component interface to a specialized Avalon-MM Master interface from a pointer interface. The latency is close to the ideal latency value of 128, and the loop initiation interval (II) is 1.

*Important:* This change to a specialized Avalon-MM Master interface from a pointer interface requires the system to have three separate memories with the expected width. The initial pointer implementation requires only one system memory with a 64-bit wide data bus. If the system cannot provide the required memories, you cannot use this optimization.

## 3.1.3. Avalon Memory Mapped Slave Interfaces

Depending on your component, you can sometimes optimize the memory structure of your component by using Avalon Memory Mapped (Avalon-MM) slave interfaces.

When you allocate a slave memory, you must define its size. Defining the size puts a limit on how large a value of  $\mathbb{N}$  that the component can process. In this example, the RAM size is 1024 words. This RAM size means that  $\mathbb{N}$  can have a maximal size of 1024 words.

The vector addition component example can be coded with an Avalon-MM slave interface as follows:

```

component void vector_add(

hls_avalon_slave_memory_argument(1024*sizeof(int)) int* a,

hls_avalon_slave_memory_argument(1024*sizeof(int)) int* b,

hls_avalon_slave_memory_argument(1024*sizeof(int)) int* c,

int N) {

#pragma unroll 8

for (int i = 0; i < N; ++i) {

c[i] = a[i] + b[i];

}

}</pre>

```

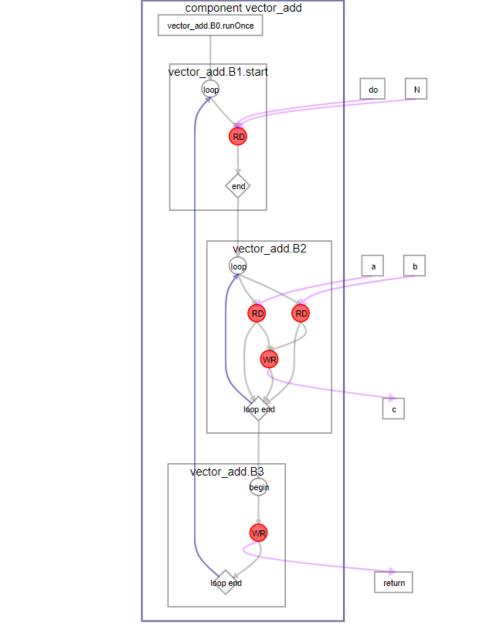

The following diagram shows the Component Viewer report generated when you compile this example.

## component vector\_add vector\_add.B0.runOnce vector\_add.B1.start do N loop RD vector\_add.B2 loop (LD) (LD) a LD/ST b LD/ST c LD/ST (ST) Local Memory óop er a [1] c [1] b [1] vector\_add.B3 begin loop en return

## Figure 3. Component View of vector\_add Component with Avalon-MM Slave Interface

Compiling this component with an Intel Quartus Prime compilation flow targeting an Intel Arria 10 device results in the following QoR metrics:

### Table 3. QoR Metrics Comparison for Avalon-MM Slave Interface<sup>1</sup>

| QoR Metric                          | Pointer | Avalon-MM Master | Avalon-MM Slave |

|-------------------------------------|---------|------------------|-----------------|

| ALMs                                | 15593.5 | 643              | 490.5           |

| DSPs                                | 0       | 0                | 0               |

| RAMs                                | 30      | 0                | 48              |

| f <sub>MAX</sub> (MHz) <sup>2</sup> | 298.6   | 472.37           | 498.26          |

| Latency (cycles)                    | 24071   | 142              | 139             |

| Initiation Interval (II) (cycles)   | ~508    | 1                | 1               |

<sup>1</sup>The compilation flow used to calculate the QoR metrics used Intel Quartus Prime Pro Edition Version 17.1.

$^2 \mbox{The } f_{MAX}$  measurement was calculated from a single seed.

The QoR metrics show by changing the ownership of the memory from the system to the component, the number of ALMs used by the component are reduced, as is the component latency. The  $f_{MAX}$  of the component is increased as well. The number of RAM blocks used by the component is greater because the memory is implemented in the component and not the system. The total system RAM usage (not shown) should not increase because RAM usage shifted from the system to the FPGA RAM blocks.

## 3.1.4. Avalon Streaming Interfaces

Avalon Streaming (Avalon-ST) interfaces support a unidirectional flow of data, and are typically used for components that drive high-bandwidth and low-latency data.

The vector addition example can be coded with an Avalon-ST interface as follows:

```

struct int_v8 {

int data[8];

};

component void vector_add(

ihc::stream_in<int_v8>& a,

ihc::stream_in<int_v8>& b,

ihc::stream_out<int_v8>& c,

int N) {

for (int j = 0; j < (N/8); ++j)

int_v8 av = a.read();

int_v8 bv = b.read();

int_v8 cv;

#pragma unroll 8

for (int i = 0; i < 8; ++i) {

cv.data[i] = av.data[i] + bv.data[i];

c.write(cv);

}

}

```

An Avalon-ST interface has a data bus, and ready and busy signals for handshaking. The struct is created to pack eight integers so that eight operations at a time can occur in parallel to provide a comparison with the examples for other interfaces. Similarly, the loop count is divided by eight.

The following diagram shows the Component Viewer report generated when you compile this example.

### Figure 4. Component View of vector\_add Component with Avalon-ST Interface

The main difference from other versions of the example component is the absence of memory.

The streaming interfaces are stallable from the upstream sources and the downstream output. Because the interfaces are stallable, the loop initiation interval (II) is approximately 1 (instead of exactly 1). If the component does not receive any bubbles (gaps in data flow) from upstream or stall signals from downstream, then the component achieves the desired II of 1.

If you know that the stream interfaces will never stall, you can further optimize this component by taking advantage of the usesReady and usesValid stream parameters.

Compiling this component with an Intel Quartus Prime compilation flow targeting an Intel Arria 10 device results in the following QoR metrics:

| QoR Metric                          | Pointer | Avalon-MM Master | Avalon-MM Slave | Avalon-ST |

|-------------------------------------|---------|------------------|-----------------|-----------|

| ALMs                                | 15593.5 | 643              | 490.5           | 314.5     |

| DSPs                                | 0       | 0                | 0               | 0         |

| RAMs                                | 30      | 0                | 48              | 0         |

| f <sub>MAX</sub> (MHz) <sup>2</sup> | 298.6   | 472.37           | 498.26          | 389.71    |

| Latency (cycles)                    | 24071   | 142              | 139             | 134       |

| Initiation Interval (II) (cycles)   | ~508    | 1                | 1               | 1         |

#### Table 4.QoR Metrics Comparison for Avalon-ST Interface1

<sup>1</sup>The compilation flow used to calculate the QoR metrics used Intel Quartus Prime Pro Edition Version 17.1.

$^2 \mbox{The } f_{\mbox{MAX}}$  measurement was calculated from a single seed.

Moving the vector\_add component to an Avalon-ST interface, further improved ALM usage, RAM usage, and component latency. The component II is optimal if there are no stalls from the interfaces.

## 3.1.5. Pass-by-Value Interface

For software developers accustomed to writing code that targets a CPU, passing each element in an array by value might be unintuitive because it typically results in many function calls or large parameters. However, for code targeting an FPGA, passing array elements by value can result in smaller and simpler hardware on the FPGA.

The vector addition example can be coded to pass the vector array elements by value as follows. A struct is used because we want to pass the entire array (of 8 data elements) by value.

This component takes and processes only eight elements of vector a and vector b, and returns eight elements of vector c. To compute 1024 elements for the example, the component needs to be called 128 times (1024/8). While in previous examples the component contained loops that were pipelined, here the component is invoked many times, and each of the invocations are pipelined.

Send Feedback

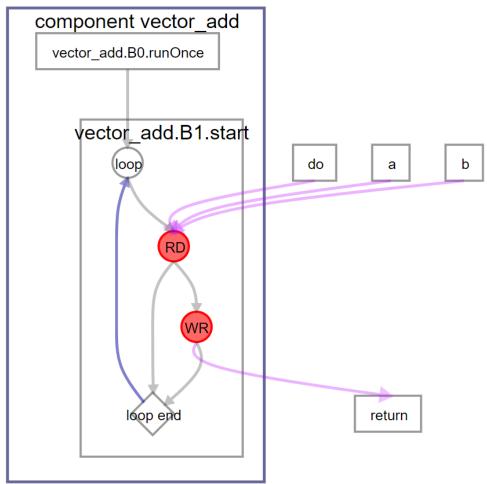

The following diagram shows the Component Viewer report generated when you compile this example.

## Figure 5. Component View of vector\_add Component with Pass-By-Value Interface

The latency of this component is one, and it has a loop initiation interval (II) of one.

Compiling this component with an Intel Quartus Prime compilation flow targeting an Intel Arria 10 device results in the following QoR metrics:

| Table 5. C | <b>DoR Metrics Com</b> | parison for Pass-b | y-Value Interface <sup>1</sup> |

|------------|------------------------|--------------------|--------------------------------|

|            |                        |                    |                                |

| QoR Metric                          | Pointer | Avalon-MM Master | Avalon-MM Slave | Avalon-ST | Pass-by-Value |

|-------------------------------------|---------|------------------|-----------------|-----------|---------------|

| ALMs                                | 15593.5 | 643              | 490.5           | 314.5     | 130           |

| DSPs                                | 0       | 0                | 0               | 0         | 0             |

| RAMs                                | 30      | 0                | 48              | 0         | 0             |

| f <sub>MAX</sub> (MHz) <sup>2</sup> | 298.6   | 472.37           | 498.26          | 389.71    | 581.06        |

| Latency (cycles)                    | 24071   | 142              | 139             | 134       | 128           |

| Initiation Interval (II) (cycles)   | ~508    | 1                | 1               | 1         | 1             |

<sup>1</sup>The compilation flow used to calculate the QoR metrics used Intel Quartus Prime Pro Edition Version 17.1.

$^2 \mbox{The } f_{MAX}$  measurement was calculated from a single seed.

The QoR metrics for the vector\_add component with a pass-by-value interface shows fewer ALM used, a high component  $f_{MAX}$ , and optimal values for latency and II. In this case, the II is the same as the component invocation interval. A new invocation of the component can be launched every clock cycle. With a initiation interval of 1, 128 component calls are processed in 128 cycles so the overall latency is 128.

## 3.2. Avoid Pointer Aliasing

Add a restrict type qualifier to pointer types whenever possible. By having restrictqualified pointers, you prevent the Intel HLS Compiler from creating unnecessary memory dependencies between nonconflicting read and write operations.

The restrict type qualifier to use depends on your edition of Intel Quartus Prime:

- The restrict type qualifier is \_\_\_\_\_restrict.

- SID The restrict type qualifier is restrict.

Consider a loop where each iteration reads data from one array, and then it writes data to another array in the same physical memory. Without adding the restrict type qualifier to these pointer arguments, the compiler must assume that the two arrays overlap. Therefor, the compiler must keep the original order of memory accesses to both arrays, resulting in poor loop optimization or even failure to pipeline the loop that contains the memory accesses.

For more details, review the parameter aliasing tutorial in the following location:

<quartus\_installdir>/hls/examples/tutorials/best\_practices/parameter\_aliasing

# **4. Loop Best Practices**

The Intel High Level Synthesis Compiler pipelines your loops to enhance throughput. Review the loop best practices to learn techniques to optimize your loops to boost the performance of your component.

The Intel HLS Compiler lets you know if there are any dependencies that prevent it from optimizing your loops. Try to eliminate these dependencies in your code for optimal component performance. You can also provide additional guidance to the compiler by using the available loop pragmas.

As a start, try the following techniques:

- Manually fuse adjacent loop bodies when the instructions in those loop bodies can be performed in parallel. These fused loops can be pipelined instead of being executed sequentially. Pipelining reduces the latency of your component and can reduce the FPGA area your component uses.

- Use the #pragma loop\_coalesce directive to have the compiler attempt to collapse nested loops. Coalescing loops reduces the latency of your component and can reduce the FPGA area overhead needed for nested loops.

### **Tutorials Demonstrating Loop Best Practices**

The Intel HLS Compiler comes with a number of tutorials that give you working examples to review and run so that you can see good coding practices as well as demonstrating important concepts.

Review the following tutorials to learn about loop best practices that might apply to your design:

| Tutorial                                                                                   | Description                                                                                                                                                                                    |  |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| You can find these tutorials in the following location on your Intel Quartus Prime system: |                                                                                                                                                                                                |  |  |  |  |

| <quartus_installdir>/hls/examples/tutorials</quartus_installdir>                           |                                                                                                                                                                                                |  |  |  |  |

| Dest_practices/                                                                            | Demonstrates the performance and resource utilization improvements of using <pre>loop_coalesce</pre> pragma on nested loops.                                                                   |  |  |  |  |

| best_practices/<br>loop_memory_dependency                                                  | Demonstrates breaking loop-carried dependencies using the $ivdep$ pragma.                                                                                                                      |  |  |  |  |

| best_practices/<br>resource_sharing_filter                                                 | <ul> <li>Demonstrates the following versions of a 32-tap finite impulse response (FIR) filter design:</li> <li>optimized-for-throughput variant</li> <li>optimized-for-area variant</li> </ul> |  |  |  |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## 4.1. Reuse Hardware By Calling It In a Loop

Loops are a useful way to reuse hardware. If your component function calls another function, the called function will be the top-level component. Calling a function multiple times results in hardware duplication.

For example, the following code example results in multiple hardware copies of the function foo in the component myComponent because the function foo is inlined:

```

int foo(int a)

{

return 4 + sqrt(a) /

}

component

void myComponent()

{

...

int x =

x += foo(0);

x += foo(1);

x += foo(2);

...

}

```

If you place the function foo in a loop, the hardware for foo can be reused for each invocation. The function is still inlined, but it is inlined only once.

```

component

void myComponent()

{

...

int x = 0;

#pragma unroll 1

for (int i = 0; i < 3; i++)

{

x += foo(i);

}

...

}

```

You could also use a switch/case block if you want to pass your reusable function different values that are not related to the loop induction variable i:

```

component

void myComponent()

{

int x = 0;

#pragma unroll 1

for (int i = 0; i < 3; i++)

{

int val = 0;

switch(i)

case 0:

val = 3;

break;

case 1:

val = 6;

break;

case 2:

val = 1;

break;

}

x += foo(val);

```

} ... }

You can learn more about reusing hardware and minimizing inlining be reviewing the resource sharing tutorial available in <quartus\_installdir>/hls/examples/tutorials/best\_practices/resource\_sharing\_filter.

## 4.2. Parallelize Loops

One of the main benefits of using an FPGA instead of a microprocessor is that FPGAs use a spatial compute structure. A design can use additional hardware resources in exchange for lower latency.

You can take advantage of the spatial compute structure to accelerate the loops by having multiple iterations of a loop executing concurrently. To have multiple iterations of a loop execute concurrently, unroll loops when possible and structure your loops so that dependencies between loop iterations are minimized and can be resolved within one clock cycle.

## 4.2.1. Pipeline Loops

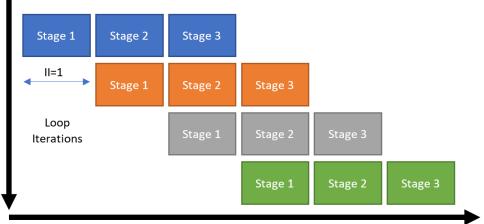

Pipelining is a form of parallelization where multiple iterations of a loop execute concurrently, like an assembly line.

Consider the following basic loop with three stages and three iterations. A loop stage is defined as the operations that occur in the loop within one clock cycle.

#### Figure 6. Basic loop with three stages and three iterations

Time

If each stage of this loop takes one clock cycle to execute, then this loop has a latency of nine cycles.

The following figure shows the pipelining of the loop from Figure 6 on page 22.

## Figure 7. Pipelined loop with three stages and four iterations

Time

The pipelined loop has a latency of five clock cycles for three iterations (and six cycles for four iterations), but there is no area tradeoff. During the second clock cycle, Stage 1 of the pipeline loop is processing iteration 2, Stage 2 is processing iteration 1, and Stage 3 is inactive.

This loop is pipelined with a loop initiation interval (II) of 1. An II of 1 means that there is a delay of 1 clock cycle between starting each successive loop iteration.

The Intel HLS Compiler attempts to pipeline loops by default, and loop pipelining is not subject to the same constant iteration count constraint that loop unrolling is.

Not all loops can be pipelined as well as the loop shown in Figure 7 on page 23, particularly loops where each iteration depends on a value computed in a previous iteration.

For example, consider if Stage 1 of the loop depended on a value computed during Stage 3 of the previous loop iteration. In that case, the second (orange) iteration could not start executing until the first (blue) iteration had reached Stage 3. This type of dependency is called a loop-carried dependency.

In this example, the loop would be pipelined with II=3. Because the II is the same as the latency of a loop iteration, the loop would not actually be pipelined at all. You can estimate the overall latency of a loop with the following equation:

$latency_{loop} = (iterations - 1) * II + latency_{body}$

where  $latency_{loop}$  is the number of cycles the loop takes to execute and  $latency_{body}$  is the number of cycles a single loop iteration takes to execute.

The Intel HLS Compiler supports pipelining nested loops without unrolling inner loops. When calculating the latency of nested loops, apply this formula recursively. This recursion means that having II>1 is more problematic for inner loops than for outer loops. Therefore, algorithms that do most of their work on an inner loop with II=1 still perform well, even if their outer loops have II>1.

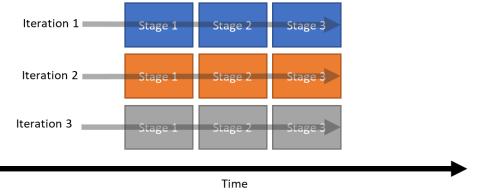

## 4.2.2. Unroll Loops

When a loop is unrolled, each iteration of the loop is replicated in hardware and executes simultaneously if the iterations are independent. Unrolling loops trades an increase in FPGA area use for a reduction in the latency of your component.

Consider the following basic loop with three stages and three iterations. Each stage represents the operations that occur in the loop within one clock cycle.

#### Figure 8. Basic loop with three stages and three iterations

Time

If each stage of this loop takes one clock cycle to execute, then this loop has a latency of nine cycles.

The following figure shows the loop from Figure 8 on page 24 unrolled three times.

#### Figure 9. Unrolled loop with three stages and three iterations

Three iterations of the loop can now be completed in only three clock cycles, but three times as many hardware resources are required.

You can control how the compiler unrolls a loop with the #pragma unroll directive, but this directive works only if the compiler knows the trip count for the loop in advance or if you specify the unroll factor. In addition to replicating the hardware, the compiler also reschedules the circuit such that each operation runs as soon as the inputs for the operation are ready.

For an example of using the #pragma unroll directive, see the best\_practices/ resource\_sharing\_filter tutorial.

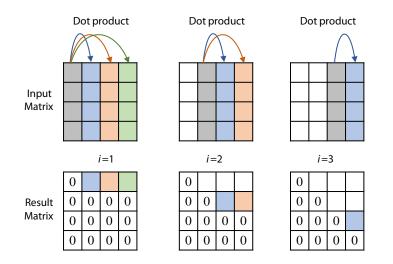

## 4.2.3. Example: Loop Pipelining and Unrolling

Consider a design where you want to perform a dot-product of every column of a matrix with each other column of a matrix, and store the six results in a different upper-triangular matrix. The rest of the elements of the matrix should be set to zero.

The code might look like the following code example:

```

1.

#define ROWS 4

2.

#define COLS 4

3.

component void dut(...)

4.

float a_matrix[COLS][ROWS]; // store in column-major format

5.

б.

float r_matrix[ROWS][COLS]; // store in row-major format

7.

8.

// setup...

9.

for (int i = 0; i < COLS; i++) {

10.

11.

for (int j = i + 1; j < COLS; j++) {

12.

float dotProduct = 0;

13.

for (int mRow = 0; mRow < ROWS; mRow++) {</pre>

14.

dotProduct += a_matrix[i][mRow] * a_matrix[j][mRow];

15.

16.

17.

r_matrix[i][j] = dotProduct;

}

18.

19.

}

20.

21.

// continue...

22.

}

23.

```

You can improve the performance of this component by unrolling the loops that iterate across each entry of a particular column. If the loop operations are independent, then the compiler executes them in parallel.

Floating-point operations typically must be carried out in the same order that they are expressed in your source code to preserve numerical precision. However, you can use the --fp-relaxed compiler flag to relax the ordering of floating-point operations. With the order of floating-point operations relaxed, all of the multiplications in this loop can occur in parallel. To learn more, review the tutorial: <quartus\_installdir>/hls/examples/ tutorials/best\_practices/ floating\_point\_ops

The compiler tries to unroll loops on its own when it thinks unrolling improves performance. For example, the loop at line 14 is automatically unrolled because the loop has a constant number of iterations, and does not consume much hardware (ROWS is a constant defined at compile-time, ensuring that this loop has a fixed number of iterations).

You can improve the throughput by unrolling the j-loop at line 11, but to allow the compiler to unroll the loop, you must ensure that it has constant bounds. You can ensure constant bounds by starting the j-loop at j = 0 instead of j = i + 1. You must also add a predication statement to prevent  $r_matrix$  from being assigned with invalid data during iterations 0,1,2,...i of the j-loop.

```

01: #define ROWS 4

02: #define COLS 4

03:

04: component void dut(...) {

05:

float a_matrix[COLS][ROWS]; // store in column-major format

float r_matrix[ROWS][COLS]; // store in row-major format

06:

07:

08:

// setup...

09:

10:

for (int i = 0; i < COLS; i++) {

11:

12: #pragma unroll

for (int j = 0; j < COLS; j++) {</pre>

13:

14:

float dotProduct = 0;

15:

16: #pragma unroll

for (int mRow = 0; mRow < ROWS; mRow++) {

dotProduct += a_matrix[i][mRow] * a_matrix[j][mRow];</pre>

17:

18:

19:

20:

21:

r_matrix[i][j] = (j > i) ? dotProduct : 0; // predication

22:

}

23:

}

}

24:

25:

// continue...

26:

27:

28: }

```

Now the j-loop is fully unrolled. Because they do not have any dependencies, all four iterations run at the same time.

```

Refer to the resource_sharing_filter tutorial located at

<quartus_installdir>/hls/examples/tutorials/best_practices/

resource_sharing_filter for more details.

```

You could continue and also unroll the loop at line 10, but unrolling this loop would result in the area increasing again. By allowing the compiler to pipeline this loop instead of unrolling it, you can avoid increasing the area and pay about only four more clock cycles assuming that the i-loop only has an II of 1. If the II is not 1, the Details pane of the Loops Analysis page in the high level design report (report.html) gives you tips on how to improve it.

The following factors are factors that can typically affect loop II:

loop-carried dependencies

```

See the tutorial at <quartus_installdir>/hls/examples/tutorials/

best_practices/loop_memory_dependency

```

- long critical loop path

- inner loops with a loop II > 1

## 4.3. Construct Well-Formed Loops

A well-formed loop has an exit condition that compares against an integer bound and has a simple induction increment of one per iteration. The Intel HLS Compiler can analyze well-formed loops efficiently, which can help improve the performance of your component.

The following example is a well-formed loop:

```

for(int i=0; i < N; i++)

{

//statements

}</pre>

```

Well-formed nested loops can also help maximize the performance of your component.

The following example is a well-formed nested loop structure:

```

for(int i=0; i < N; i++)

{

//statements

for(int j=0; j < M; j++)

{

//statements

}

}</pre>

```

## 4.4. Minimize Loop-Carried Dependencies

Loop-carried dependencies occur when the code in a loop iteration depends on the output of previous loop iterations. Loop-carried dependencies in your component increase loop initiation interval (II), which reduces the performance of your component.

The loop structure below has a loop-carried dependency because each loop iteration reads data written by the previous iteration. As a result, each read operation cannot proceed until the write operation from the previous iteration completes. The presence of loop-carried dependencies reduces of pipeline parallelism that the Intel HLS Compiler can achieve, which reduces component performance.

```

for(int i = 1; i < N; i++)

{

A[i] = A[i - 1] + i;

}</pre>

```

The Intel HLS Compiler performs a static memory dependency analysis on loops to determine the extent of parallelism that it can achieve. If the Intel HLS Compiler cannot determine that there are no loop-carried dependencies, it assumes that loop-dependencies exist. The ability of the compiler to test for loop-carried dependencies is impeded by unknown variables at compilation time or if array accesses in your code involve complex addressing.

To avoid unnecessary loop-carried dependencies and help the compiler to better analyze your loops, follow these guidelines:

#### **Avoid Pointer Arithmetic**

Compiler output is suboptimal when your component accesses arrays by dereferencing pointer values derived from arithmetic operations. For example, avoid accessing an array as follows:

```

for(int i = 0; i < N; i++)

{

int t = *(A++);

*A = t;

}</pre>

```

#### **Introduce Simple Array Indexes**

Some types of complex array indexes cannot be analyzed effectively, which might lead to suboptimal compiler output. Avoid the following constructs as much as possible:

• Nonconstants in array indexes.

For example, A[K + i], where i is the loop index variable and K is an unknown variable.

• Multiple index variables in the same subscript location.

For example, A[i + 2  $\times$  j], where i and j are loop index variables for a double nested loop.

The array index A[i][j] can be analyzed effectively because the index variables are in different subscripts.

• Nonlinear indexing.

For example, A[i & C], where i is a loop index variable and C is a nonconstant variable.

#### **Use Loops with Constant Bounds Whenever Possible**

The compiler can perform range analysis effectively when loops have constant bounds.

## 4.5. Avoid Complex Loop-Exit Conditions

If a loop in your component has complex exit conditions, memory accesses or complex operations might be required to evaluate the condition. Subsequent iterations of the loop cannot launch in the loop pipeline until the evaluation completes, which can decrease the overall performance of the loop.

Use the speculated\_iterations pragma to specify how many cycles the loop exit condition can take to compute.

#### **Related Information**

Loop Iteration Speculation (speculated\_iterations Pragma)

## 4.6. Convert Nested Loops into a Single Loop

To maximize performance, combine nested loops into a single loop whenever possible. The control flow for a loop adds overhead both in logic required and FPGA hardware footprint. Combining nested loops into a single loop reduces these aspects, improving the performance of your component.

The following code examples illustrate the conversion of a nested loop into a single loop:

| Nested Loop                                                                                                                                     | Converted Single Loop                                        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| <pre>for (i = 0; i &lt; N; i++) {     //statements     for (j = 0; j &lt; M; j++)     {         //statements         //statements     } }</pre> | <pre>for (i = 0; i &lt; N*M; i++) {     //statements }</pre> |  |  |

You can also specify the loop\_coalesce pragma to coalesce nested loops into a single loop without affecting the loop functionality. The following simple example shows how the compiler coalesces two loops into a single loop when you specify the loop\_coalesce pragma.

Consider a simple nested loop written as follows:

```

#pragma loop_coalesce

for (int i = 0; i < N; i++)

for (int j = 0; j < M; j++)

sum[i][j] += i+j;</pre>

```

The compiler coalesces the two loops together so that they run as if they were a single loop written as follows:

```

int i = 0;

int j = 0;

while(i < N){

sum[i][j] += i+j;

j++;

if (j == M){

j = 0;

i++;

}

}

```

For more information about the loop\_coalesce pragma, see "Loop Coalescing (loop\_coalesce Pragma)" in Intel High Level Synthesis Compiler Reference Manual.

## 4.7. Declare Variables in the Deepest Scope Possible

To reduce the FPGA hardware resources necessary for implementing a variable, declare the variable just before you use it in a loop. Declaring variables in the deepest scope possible minimizes data dependencies and FPGA hardware usage because the Intel HLS Compiler does not need to preserve the variable data across loops that do not use the variables.

Consider the following example:

The array  ${\rm a}$  requires more resources to implement than the array  ${\rm b}.$  To reduce hardware usage, declare array  ${\rm a}$  outside the inner loop unless it is necessary to maintain the data through iterations of the outer loop.

*Tip:* Overwriting all values of a variable in the deepest scope possible also reduces the resources necessary to represent the variable.

## **5. Memory Architecture Best Practices**

The Intel High Level Synthesis Compiler infers efficient memory architectures (like memory width, number of banks and ports) in a component by adapting the architecture to the memory access patterns of your component. Review the memory architecture best practices to learn how you can get the best memory architecture for your component from the compiler.

In most cases, you can optimize the memory architecture by modifying the access pattern. However, the Intel HLS Compiler gives you some control over the memory architecture.

#### **Tutorials Demonstrating Memory Architecture Best Practices**

The Intel HLS Compiler comes with a number of tutorials that give you working examples to review and run so that you can see good coding practices as well as demonstrating important concepts.

Review the following tutorials to learn about memory architecture best practices that might apply to your design:

| Tutorial                                                                                   | Description                                                                                                                                                                                 |  |  |  |  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| You can find these tutorials in the following location on your Intel Quartus Prime system: |                                                                                                                                                                                             |  |  |  |  |

| <quartus_installdir>/hls/examples/tutorials</quartus_installdir>                           |                                                                                                                                                                                             |  |  |  |  |

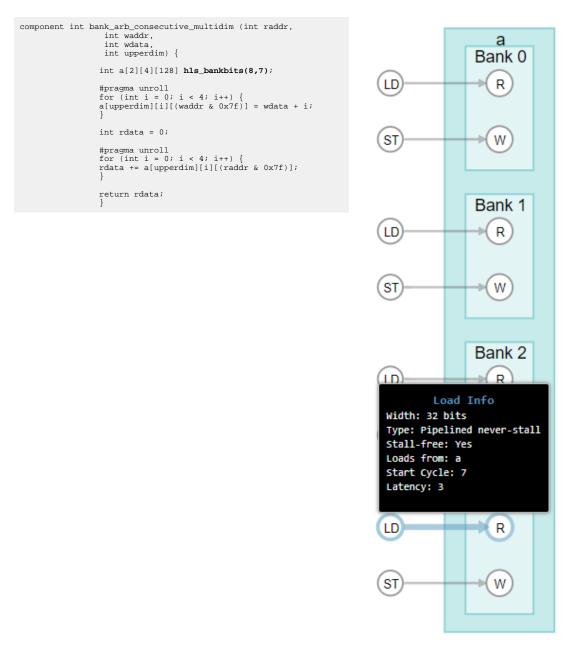

| component_memories/bank_bits                                                               | Demonstrates how to control component internal memory architecture for<br>parallel memory access by enforcing which address bits are used for banking.                                      |  |  |  |  |

| component_memories/<br>depth_wise_merge                                                    | Demonstrates how to improve resource utilization by implementing two logical memories as a single physical memory with a depth equal to the sum of the depths of the two original memories. |  |  |  |  |

| component_memories/<br>width_wise_merge                                                    | Demonstrates how to improve resource utilization by implementing two logical memories as a single physical memory with a width equal to the sum of the widths of the two original memories. |  |  |  |  |

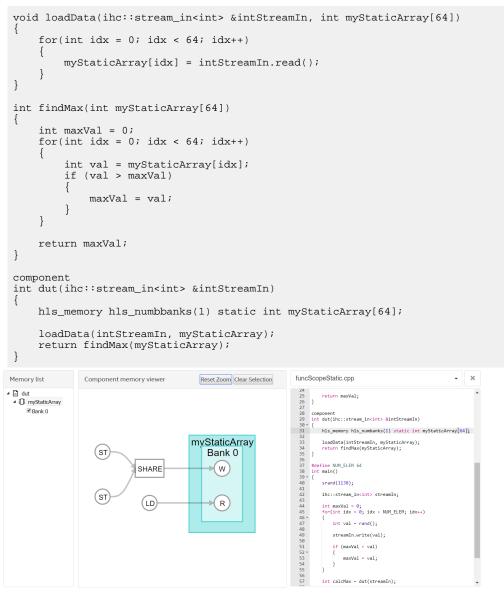

## **5.1. Example: Overriding a Coalesced Memory Architecture**

Using memory attributes in various combinations in your code allows you to override the memory architecture that the Intel HLS Compiler infers for your component.

The following code examples demonstrate how you can use the following memory attributes to override coalesced memory to conserve memory blocks on your FPGA:

- hls\_bankwidth(*n*)

- hls\_numbanks(n)

- hls\_singlepump

- hls\_numports\_readonly\_writeonly(m,n)

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

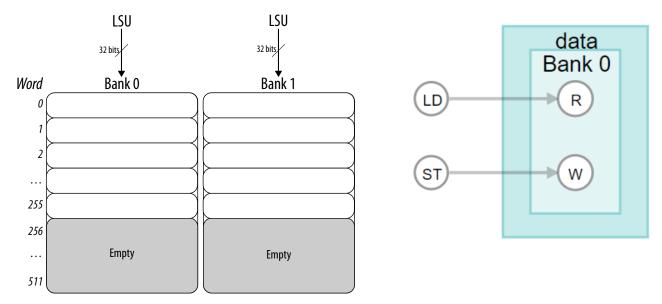

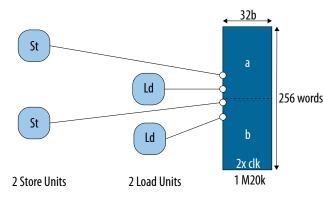

The original code coalesces memory to 256 locations deep by 64 bits wide (256x64 bits), that is, two on-chip memory blocks:

The following images show how the 256x64 bit memory for this code sample is structured, as well how the component memory structure is shown in the high-level design report (report.html)

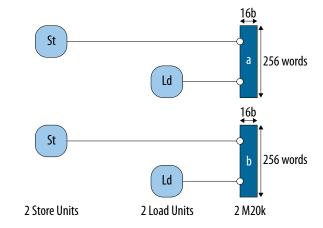

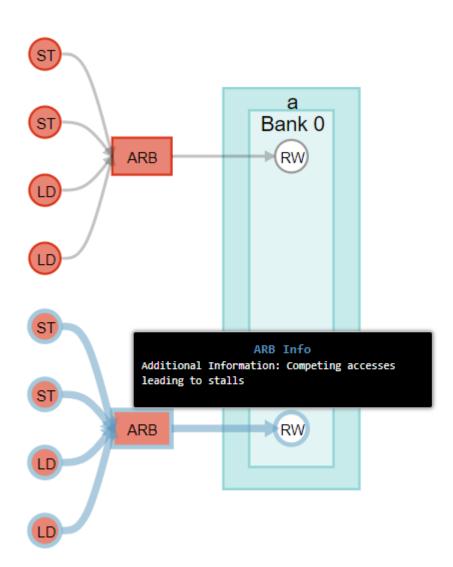

The modified code implements a simple dual-port on-chip memory block that is 512 locations deep by 32 bits wide (512x32 bits) with stallable arbitration:

*Tip:* Instead of specifying the hls\_singlepump and hls\_numports\_readonly\_writeonly(1,1) attributes, you can specify this configuration with the hls\_simple\_dual\_port\_memory attribute.

The following images show how the 512x32 bit memory with stallable arbitration for this code sample is structured, as well how the component memory structure is shown in the high-level design report (report.html).

While it might appear that you save hardware area by reducing the number of RAM blocks needed for the component, the introduction of stallable arbitration causes the amount of hardware needed to implement the component to increase. In the following table, you can compare the number ALMs and FFs required by the components.

| Quartus Fit Resource Utilization Summary |        |      |      |      |       |  |  |

|------------------------------------------|--------|------|------|------|-------|--|--|

|                                          | ALMs   | FFs  | RAMs | DSPs | MLABs |  |  |

| Full design (all components)             | 1164.5 | 1922 | з    | o    | 25    |  |  |

| mem_coalesce_override                    | 1074.5 | 1654 | 1    | 0    | 23    |  |  |

| mem_coalesce_default                     | 90     | 268  | 2    | 0    | 2     |  |  |

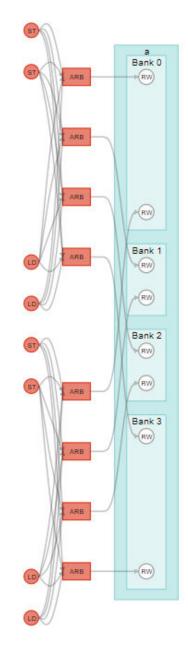

## 5.2. Example: Overriding a Banked Memory Architecture

Using memory attributes in various combinations in your code allows you to override the memory architecture that the Intel HLS Compiler infers for your component.

The following code examples demonstrate how you can use the following memory attributes to override banked memory to conserve memory blocks on your FPGA:

- hls\_bankwidth(n)

- hls\_numbanks(n)

- hls\_singlepump

- hls\_doublepump

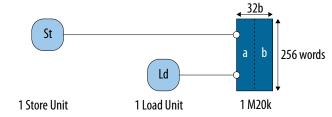

The original code creates two banks of single-pumped on-chip memory blocks that are 16 bits wide:

To save banked memory, you can implement one bank of double-pumped 32-bit wide on-chip memory block by adding the following attributes before the declaration of data[1024]. These attributes fold the two half-used memory banks into one fullyused memory bank that is double-pumped, so that it can be accessed as quickly as the two half-used memory banks.

```

hls_bankwidth(2) hls_numbanks(1)

hls_doublepump

unsigned short data[1024];

```

Alternatively, you can avoid the double-clock requirement of the double-pumped memory by implementing one bank of single-pumped on-chip memory block by adding the following attributes before the declaration of data[1024]. However, in this example, these attributes add stallable arbitration to your component memories, which hurts your component performance.

```

hls_bankwidth(2) hls_numbanks(1)

hls_singlepump

unsigned short data[1024];

```

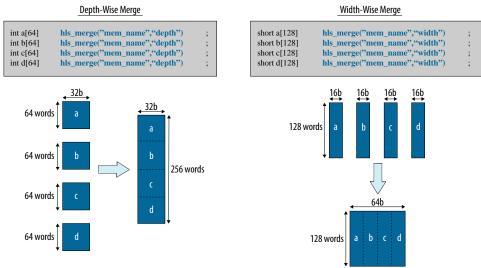

## **5.3. Merge Memories to Reduce Area**

In some cases, you can save FPGA memory blocks by merging your component memories so that they consume fewer memory blocks, reducing the FPGA area your component uses. Use the hls\_merge attribute to force the Intel HLS Compiler to implement different variables in the same memory system.

When you merge memories, multiple component variables share the same memory block. You can merge memories by width (width-wise merge) or depth (depth-wise merge). You can merge memories where the data in the memories have different datatypes.

#### Figure 12. Overview of width-wise merge and depth-wise merge

The following diagram shows how four memories can be merged width-wise and depth-wise.

## 5.3.1. Example: Merging Memories Depth-Wise

Use the hls\_merge("<mem\_name>","depth") attribute to force the Intel HLS Compiler to implement variables in the same memory system, merging their memories by depth.

All variables with the same <mem\_name> label set in their hls\_merge attributes are merged.

Consider the following component code:

```

component int depth_manual(bool use_a, int raddr, int waddr, int wdata) {

int a[128];

int b[128];

int rdata;

// mutually exclusive write

if (use_a) {

a[waddr] = wdata;

else

b[waddr] = wdata;

}

// mutually exclusive read

if (use_a)

rdata = a[raddr];

else {

}

rdata = b[raddr];

}

return rdata;

}

```

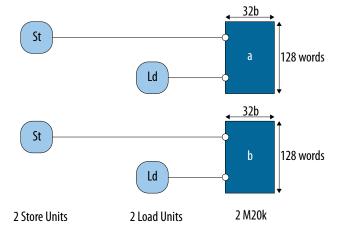

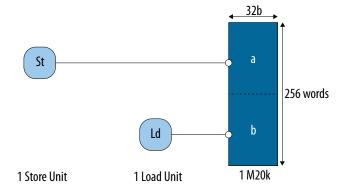

The code instructs the Intel HLS Compiler to implement local memories a and b as two on-chip memory blocks, each with its own load and store instructions.

Because the load and store instructions for local memories a and b are mutually exclusive, you can merge the accesses, as shown in the example code below. Merging the memory accesses reduces the number of load and store instructions, and the number of on-chip memory blocks, by half.

```

component int depth_manual(bool use_a, int raddr, int waddr, int wdata) {

int a[128] hls_merge("mem","depth");

int b[128] hls_merge("mem","depth");

int rdata;

// mutually exclusive write

if (use_a) {

a[waddr] = wdata;

} else

b[waddr] = wdata;

}

// mutually exclusive read

if (use_a) {

rdata = a[raddr];

} else {

rdata = b[raddr];

}

return rdata;

}

```

## Figure 14. Depth-Wise Merge of Local Memories for Component depth\_manual

There are cases where merging local memories with respect to depth might degrade memory access efficiency. Before you decide whether to merge the local memories with respect to depth, refer to the HLD report (<result>.prj/reports/ report.html) to ensure that they have produced the expected memory configuration with the expected number of loads and stores instructions. In the example below, the Intel HLS Compiler should not merge the accesses to local memories a and b because the load and store instructions to each memory are not mutually exclusive.

```

component int depth_manual(bool use_a, int raddr, int waddr, int wdata) {

int a[128] hls_merge("mem","depth");

int b[128] hls_merge("mem","depth");

int rdata;

// NOT mutually exclusive write

a[waddr] = wdata;

b[waddr] = wdata;

// NOT mutually exclusive read

rdata = a[raddr];

rdata += b[raddr];

return rdata;

}

```

In this case, the Intel HLS Compiler might double pump the memory system to provide enough ports for all the accesses. Otherwise, the accesses must share ports, which prevent stall-free accesses.

# Figure 15. Local Memories for Component depth\_manual with Non-Mutually Exclusive Accesses

### 5.3.2. Example: Merging Memories Width-Wise

Use the hls\_merge("<mem\_name>", "width") attribute to force the Intel HLS Compiler to implement variables in the same memory system, merging their memories by width.

All variables with the same <mem\_name> label set in their hls\_merge attributes are merged.

Consider the following component code:

```

component short width_manual (int raddr, int waddr, short wdata) {

short a[256];

short rdata = 0;

// Lock step write

a[waddr] = wdata;

b[waddr] = wdata;

// Lock step read

rdata += a[raddr];

rdata += b[raddr];

return rdata;

}

```

### Figure 16. Implementation of Local Memory for Component width\_manual