Document Number: LS1028ARDBRM Reference Manual Rev. b, 11/2018

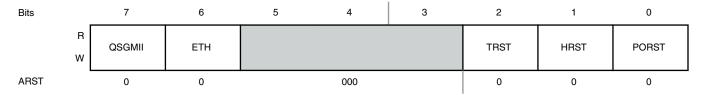

# **QorlQ LS1028A Reference Design Board Reference Manual**

## **Contents**

| Chapter 1 LS1028ARDB Overview                          | 4   |

|--------------------------------------------------------|-----|

| 1.1 Acronyms and abbreviations                         |     |

| 1.2 Related documentation                              |     |

| 1.3 Block diagrams                                     |     |

| 1.4 Board features.                                    |     |

|                                                        |     |

| Chapter 2 LS1028ARDB Functional Description            | 14  |

| 2.1 Processor                                          |     |

| 2.2 Power supplies                                     |     |

| 2.3 Clocks                                             |     |

| 2.4 DDR interface.                                     |     |

| 2.5 USB interface                                      |     |

| 2.6 DisplayPort                                        |     |

| 2.7 SerDes interface.                                  |     |

| 2.8 Ethernet controller interface                      |     |

| 2.9 Synchronous audio interface (SAI)                  |     |

| 2.10 M.2 connectors                                    |     |

| 2.11 DUART interface                                   |     |

| 2.12 CAN interface                                     |     |

| 2.13 I2C interface                                     |     |

| 2.14 XSPI interface.                                   |     |

| 2.15 JTAG port                                         |     |

| 2.16 eSDHC interface.                                  |     |

| 2.17 Mikro-click modules                               |     |

| 2.18 GPIOs.                                            |     |

| 2.19 Interrupt handling                                |     |

| 2.20 Temperature measurement                           |     |

| 2.21 System controller                                 |     |

| •                                                      |     |

| <b>Chapter 3 Board Configuration and Debug Support</b> | t51 |

| 3.1 Switch configuration                               |     |

| 3.2 LEDs                                               |     |

| 3.2 LLD3                                               |     |

| Chapter 4 Qixis Programming Model                      | 5.0 |

| 4.1 Register Conventions                               |     |

| 4.2 Resets.                                            |     |

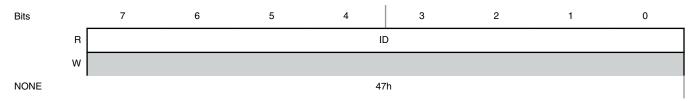

| 4.3 Identification Registers                           |     |

| 4.4 Identification (ID)                                |     |

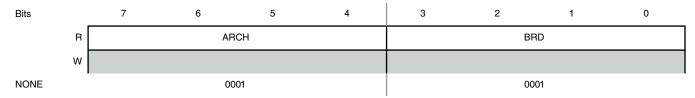

| 4.5 Board Version (VER)                                |     |

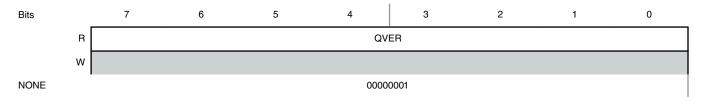

| 4.6 Qixis Version (QVER)                               |     |

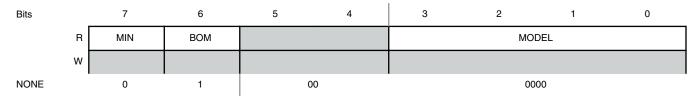

| 4.7 Programming Model (MODEL)                          |     |

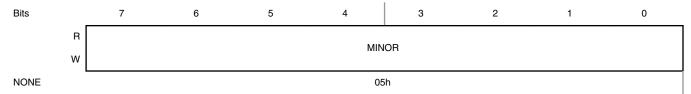

| 4.8 Minor Revision (MINOR)                             |     |

| 4.9 Control and Status Registers                       |     |

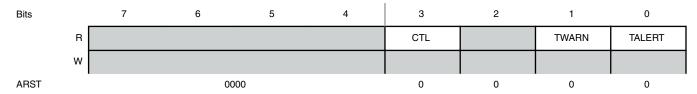

| 4.10 General Control (CTL)                             |     |

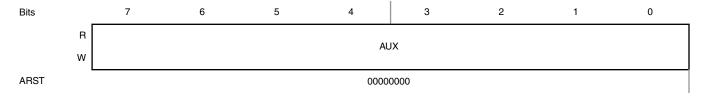

| 4.11 Auxiliary (AUX)                                   |     |

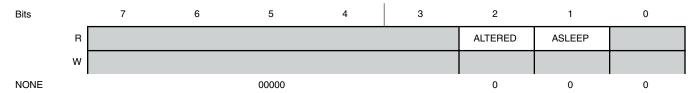

| 4.12 System Status (STAT_SYS)                          | 0/  |

| 4.13 Alarm (ALARM)                                     |     |

| 4.14 Presence Detect 1 (STAT_PRES1)                    |     |

| T. 1T   16361106 Detect   (OTAL_FILEST)                |     |

| 4.15 Presence Detect 2 (STAT_PRES2)  | 70  |

|--------------------------------------|-----|

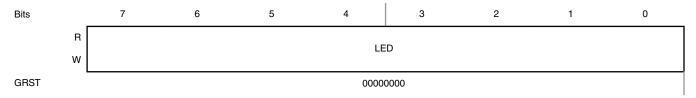

| 4.16 LED Control (LED).              |     |

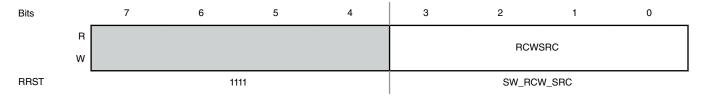

| 4.17 Reconfiguration Régisters       | 72  |

| 4.18 Reconfiguration Control (RCFG)  |     |

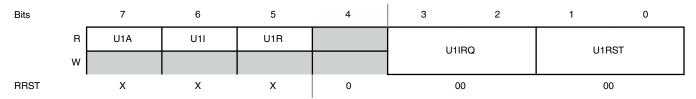

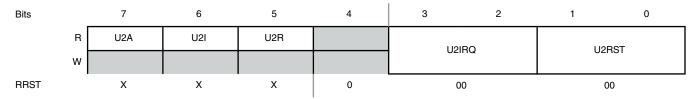

| 4.19 USB Control (USB_STAT)          | 73  |

| 4.20 USB Control (USB_CTL)           |     |

| 4.21 Watchdog (WATCH)                | 75  |

| 4.22 Power Control/Status Registers  |     |

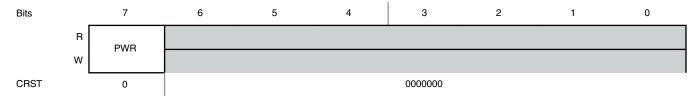

| 4.23 Power Control 2 (PWR_CTL2)      |     |

| 4.24 Power Status 0 (PWR_MSTAT)      | 77  |

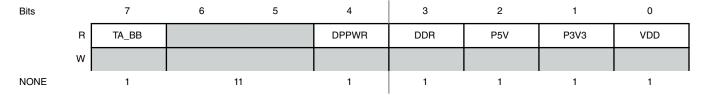

| 4.25 Power Status 1 (PWR_STAT1)      |     |

| 4.26 Clock Control Registers         |     |

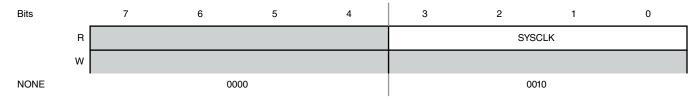

| 4.27 Clock Speed 1 (ČLK_SPD1)        |     |

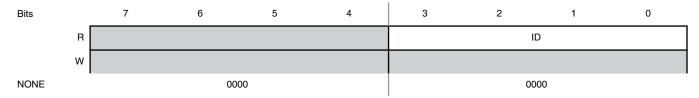

| 4.28 Clock ID/Status (CLK_ID)        |     |

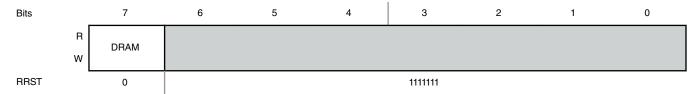

| 4.29 Reset Control Registers         |     |

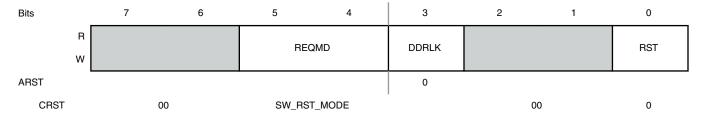

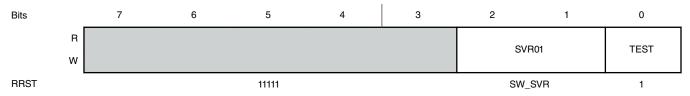

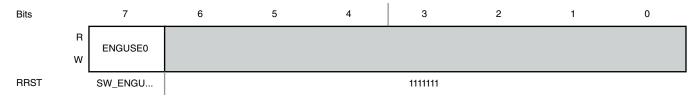

| 4.30 Reset Control (RST_CTL)         | 81  |

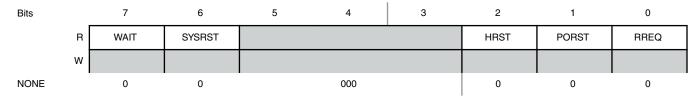

| 4.31 Reset Status (RST_STAT)         | 82  |

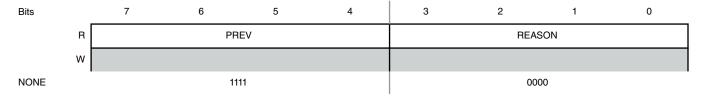

| 4.32 Reset Event Trace (RST_REASON)  | 84  |

| 4.33 Reset Force 1 (RST_FORCE1)      |     |

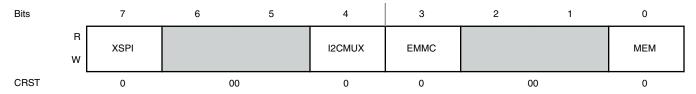

| 4.34 Reset Force 2 (RST_FORCE2)      | 86  |

| 4.35 Reset Force 3 (RST_FORCE3)      |     |

| 4.36 Reset Mask 1 (RST_MASK1)        | 88  |

| 4.37 Reset Mask 2 (RST_MASK2)        | 89  |

| 4.38 Reset Mask 2 (RST_MASK3)        | 90  |

| 4.39 Board Configuration Registers   | 90  |

| 4.40 Board Configuration 0 (BRDCFG0) | 91  |

| 4.41 Board Configuration 1 (BRDCFG1) | 92  |

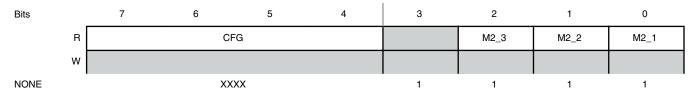

| 4.42 Board Configuration 2 (BRDCFG2) | 92  |

| 4.43 Board Configuration 3 (BRDCFG3) | 93  |

| 4.44 Board Configuration 4 (BRDCFG4) | 95  |

| 4.45 Board Configuration 5 (BRDCFG5) | 96  |

| 4.46 Board Configuration 6 (BRDCFG6) | 97  |

| 4.47 DUT Configuration Registers     |     |

| 4.48 DUT Configuration 0 (DUTCFG0)   |     |

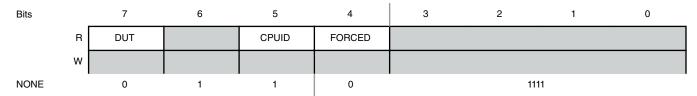

| 4.49 DUT Configuration 1 (DUTCFG1)   | 99  |

| 4.50 DUT Configuration 2 (DUTCFG2)   |     |

| 4.51 DUT Configuration 11 (DUTCFG11) |     |

| 4.52 GPIO Registers                  |     |

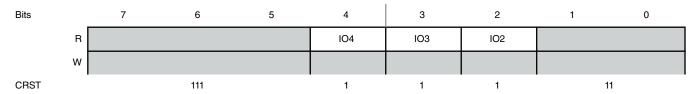

| 4.53 GPIO I/O (GPIO_IO)              | 102 |

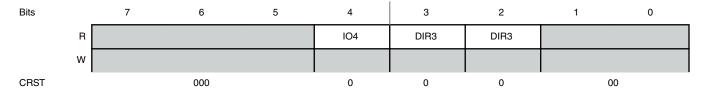

| 4.54 GPIO Direction (GPIO_DIR)       | 103 |

| 4.55 IRQ Status Registers            | 104 |

| 4.56 Interrupt Status 0 (IRQSTAT0)   |     |

| 4.57 Interrupt Status 1 (IRQSTAT1)   |     |

| 4.58 Interrupt Status 2 (IRQSTAT2)   |     |

| 4.59 Interrupt Drive 5 (IRQDRV5)     |     |

| 4.60 Core Management Space Registers |     |

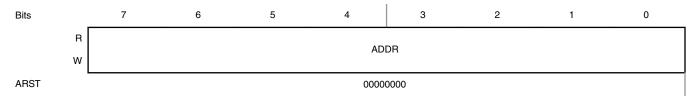

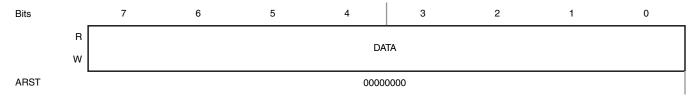

| 4.61 Core Management Address (CMSA)  |     |

| 4.62 Core Management Data (CMSD)     | 109 |

|                                      |     |

Appendix A Revision History......110

## Chapter 1 LS1028ARDB Overview

The QorlQ<sup>®</sup> LS1028A reference design board (LS1028ARDB) is a computing, evaluation, development, and test platform supporting the QorlQ LS1028A processor, which is a dual-core Arm<sup>®</sup> Cortex<sup>®</sup>-v8 A72 processor with frequency up to 1.3 GHz. The LS1028ARDB is optimized to support SGMII (1 Gbit/s), QSGMII (5 Gbit/s), PCIe x1 (8 Gbit/s), and SATA (6 Gbit/s) over high-speed SerDes ports, USB 3.0, DisplayPort, and also a high-bandwidth DDR4 memory.

The LS1028ARDB can be used to develop and demonstrate human machine interface systems, industrial control systems such as robotics controllers and motion controllers, and PLCs. The reference design also provides the functionality needed for Industrial IoT gateways, edge computing, industrial PCs, and wireless or wired networking gateways.

The board is lead-free and RoHS-compliant.

Developers using the LS1028ARDB can perform standard debugging tasks, such as:

- · Upload and run code

- · Set breakpoints

DQS

- · Display memory and registers

- · Connect and incorporate proprietary hardware into target systems using the LS1028A as a host processor

- Use the LS1028ARDB as a demonstration tool

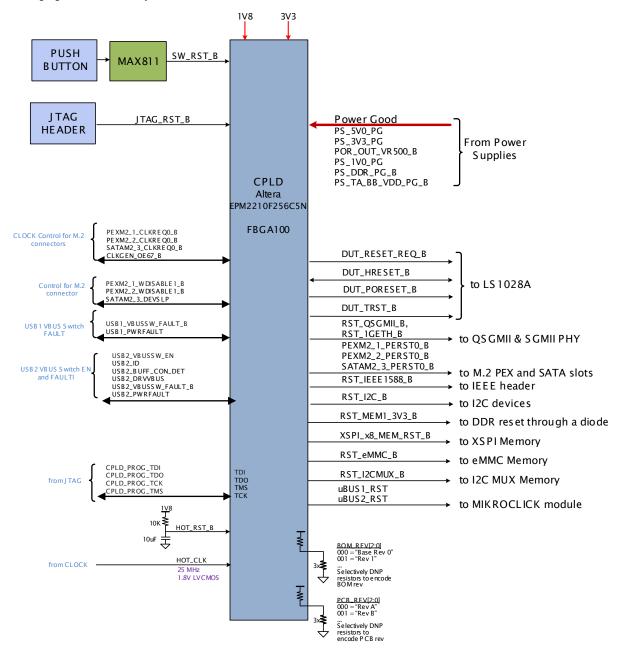

The board support package (BSP) is developed using the Linux operating system. The onboard CPLD provides startup configuration information for the U-Boot and Linux.

#### 1.1 Acronyms and abbreviations

The table below lists and explains the acronyms and abbreviations used in this document.

**Term** Description CAN Controller area network CCI Cache coherency interconnect **CPLD** Complex programmable logic device CTS Clear to send **DCM** Development system control monitor **DDR SDRAM** Double data rate synchronous dynamic random-access memory DIP Dual inline package **DPAA** Data path acceleration architecture

Table 1. Acronyms and abbreviations

Table continues on the next page...

Data strobe

Table 1. Acronyms and abbreviations (continued)

| Term      | Description                                                               |  |  |

|-----------|---------------------------------------------------------------------------|--|--|

| DUART     | Dual universal asynchronous receiver/transmitter                          |  |  |

| DUT       | Device under test                                                         |  |  |

| EC        | Ethernet controller                                                       |  |  |

| ECC       | Error correcting code                                                     |  |  |

| eDP       | Embedded DisplayPort                                                      |  |  |

| EMI       | Ethernet management interface                                             |  |  |

| ENETC     | Ethernet controller                                                       |  |  |

| eMMC      | Embedded multimedia card                                                  |  |  |

| eSDHC     | Enhanced secure digital host controller                                   |  |  |

| FET       | Field-effect transistor                                                   |  |  |

| FPGA      | Field-programmable gate array                                             |  |  |

| GbE       | Gigabit Ethernet                                                          |  |  |

| GPIO      | General purpose input/output                                              |  |  |

|           |                                                                           |  |  |

| GT/s HDLC | GigaTransfers/second                                                      |  |  |

|           | High-level data link control High-speed serial interface                  |  |  |

| HSSI      | Inter-integrated circuit                                                  |  |  |

| IZC       | Joint Test Action Group (IEEE <sup>®</sup> Standard 1149.1 <sup>™</sup> ) |  |  |

| JTAG      |                                                                           |  |  |

| LOS       | Loss of signal                                                            |  |  |

| OCM       | Offline configuration manager                                             |  |  |

| ОТС       | On-The-Go                                                                 |  |  |

| PBL       | Pre-boot loader                                                           |  |  |

| PLL       | Phase-locked loop                                                         |  |  |

| PMIC      | Power management multi-channel IC                                         |  |  |

| POR       | Power-on reset                                                            |  |  |

| PSU       | Power supply unit                                                         |  |  |

| PTP       | Precision time protocol                                                   |  |  |

| PWM       | Pulse width modulation                                                    |  |  |

| QSGMII    | Quad serial gigabit media independent interface                           |  |  |

| QSPI      | Quad serial peripheral interface                                          |  |  |

| RCW       | Reset configuration word                                                  |  |  |

| RTC       | Real time clock                                                           |  |  |

Table 1. Acronyms and abbreviations (continued)

| Term   | Description                                       |

|--------|---------------------------------------------------|

| RTS    | Request to send                                   |

| SATA   | Serial advanced technology attachment             |

| SDRAM  | Synchronous dynamic random-access memory          |

| SerDes | Serializer/deserializer                           |

| SGMII  | Serial gigabit media independent interface        |

| SPD    | Serial presence detect                            |

| SPI    | Serial peripheral interface                       |

| ss     | Spread spectrum                                   |

| SSC    | Spread spectrum clocking                          |

| тсхо   | Temperature compensated crystal (Xtal) oscillator |

| UART   | Universal asynchronous receiver/transmitter       |

| UDIMM  | Unbuffered dual inline memory module              |

| UFT    | Universal frequency translator                    |

| USB    | Universal serial bus                              |

| XSPI   | Octal serial peripheral interface                 |

## 1.2 Related documentation

The table below lists and explains the additional documents and resources that you can refer to for more information on the LS1028ARDB.

Some of the documents listed below may be available only under a non-disclosure agreement (NDA). To request access to these documents, contact your local field applications engineer or sales representative.

Table 2. Related documentation

| Document                          | Description                                                                                                                                                                             | Link/how to access                 |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| QorlQ LS1028A Product<br>Brief    | Provides a brief overview of the LS1028A processor                                                                                                                                      | Contact FAE / sales representative |

| QorlQ LS1028A Data Sheet          | Provides information about electrical characteristics, hardware design considerations, and ordering information                                                                         | Contact FAE / sales representative |

| QorlQ LS1028A Reference<br>Manual | Provides a detailed description about the LS1028A QorlQ multicore processor and its features, such as memory map, serial interfaces, power supply, chip features, and clock information | Contact FAE / sales representative |

| QorlQ LS1028A Chip Errata         | Lists the details of all known silicon errata for the LS1028A                                                                                                                           | Contact FAE / sales representative |

Table 2. Related documentation (continued)

| Document                                                                                   | Description                                                                                                                                                                                                                                           | Link/how to access                                                                         |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| QorlQ LS1028A Reference<br>Design Board Getting<br>Started Guide                           | Explains the LS1028ARDB settings and physical connections needed to boot the board                                                                                                                                                                    | Contact FAE / sales representative                                                         |

| QorlQ LS1028A Design<br>Checklist, AN12028                                                 | This document provides recommendations for new designs based on the LS1028A SoC. This document can also be used to debug newly designed systems by highlighting those aspects of a design that merit special attention during initial system start-up | Contact FAE / sales representative                                                         |

| Layerscape LS1028A BSP                                                                     | This document explains how to use the QorlQ LS1028A BSP, which is a Linux-based development kit, to evaluate and explore the features of the LS1028A SoC                                                                                              | Contact FAE / sales representative                                                         |

| CodeWarrior Development<br>Studio for QorlQ LS series -<br>ARM V8 ISA, Targeting<br>Manual | This manual explains how to use the CodeWarrior Development Studio for QorlQ LS series - ARM V8 ISA product                                                                                                                                           | CodeWarrior Development<br>Studio for QorlQ LS series -<br>ARM V8 ISA, Targeting<br>Manual |

| CodeWarrior TAP Probe<br>User Guide                                                        | Provides details of CodeWarrior® TAP, which enables target system debugging through a standard debug port (usually JTAG) while connected to a developer workstation through Ethernet or USB                                                           | CodeWarrior TAP Probe<br>User Guide                                                        |

## 1.3 Block diagrams

This section provides block diagrams showing major functional units of the LS1028A processor and LS1028ARDB.

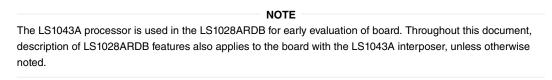

The figure below shows the LS1028A processor block diagram.

Figure 1. LS1028A block diagram

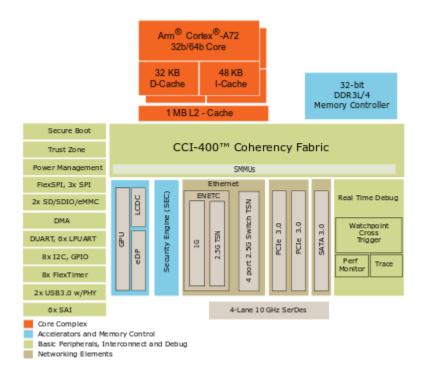

The figure below shows the LS1028ARDB block diagram.

Figure 2. LS1028ARDB block diagram

## 1.4 Board features

The table below lists the features of the LS1028ARDB.

Table 3. LS1028ARDB features

| LS1028ARDB feature               | Specification        | Description                                                                                                                                                                              |  |  |

|----------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Processor                        | Two-core processor   | Two Arm® Cortex®- A72 processor cores:                                                                                                                                                   |  |  |

|                                  |                      | Based on 64-bit ARMv8 architecture                                                                                                                                                       |  |  |

|                                  |                      | Up to 1.3 GHz operation                                                                                                                                                                  |  |  |

|                                  |                      | Single-threaded cores with 48 KB L1 instruction cache and 32 KB L1 data cache                                                                                                            |  |  |

|                                  |                      | Arranged as a single cluster of two cores sharing a single 1 MB L2 cache                                                                                                                 |  |  |

|                                  |                      | NOTE  For more details on the LS1028A processor, see QorlQ  LS1028A Family Reference Manual.                                                                                             |  |  |

| DDR memory                       | DDR4                 | Five onboard 1G x8 discrete memory modules (Four data byte lanes + ECC)                                                                                                                  |  |  |

|                                  |                      | 32-bit data and 4-bit ECC                                                                                                                                                                |  |  |

|                                  |                      | One chip select                                                                                                                                                                          |  |  |

|                                  |                      | Data transfer rates of up to 1.6 GT/s                                                                                                                                                    |  |  |

|                                  |                      | Single-bit error correction and double-bit error detection ECC (4-bit check word across 32-bit data)                                                                                     |  |  |

| High-speed serial ports (SerDes) | One four-lane SerDes | Lane 0: Supports one 1 GbE RJ45 SGMII, connected through the<br>Qualcomm AR8033 PHY                                                                                                      |  |  |

|                                  |                      | Lane 1: Supports four 1.25 GbE RJ45 QSGMII, each connected through the NXP F104S8A PHY                                                                                                   |  |  |

|                                  |                      | Lane 2: Connects to one PCIe M.2 Key-E slot to support PCIe Gen3     (8 Gbit/s) cards                                                                                                    |  |  |

|                                  |                      | • Lane 3: Connects to one PCIe M.2 Key-E slot or one SATA M.2 Key-B slot through a register mux to support either PCIe Gen 3 (8 Gbit/s) or SATA Gen 3 cards (6 Gbit/s) at a time         |  |  |

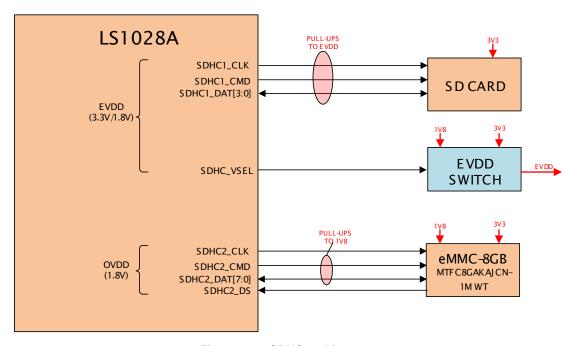

| eSDHC                            | eSDHC1               | Supports a secure digital (SD) connector for connecting an external SD 3.0 card                                                                                                          |  |  |

|                                  | eSDHC2               | Onboard 8 GB eMMC memory (MTFC8GAKAJCN) supporting                                                                                                                                       |  |  |

|                                  |                      | — x1, x4, and x8 I/Os                                                                                                                                                                    |  |  |

|                                  |                      | <ul> <li>— SDR/DDR modes up to 52 MHz clock speed</li> </ul>                                                                                                                             |  |  |

|                                  |                      | — HS200/HS400 modes                                                                                                                                                                      |  |  |

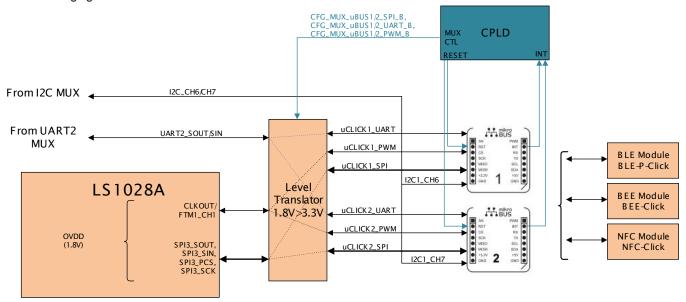

| SPI                              | SPI3                 | Connects to two mikroBUS <sup>™</sup> sockets to support mikro-click modules, such as Bluetooth 4.0, 2.4 GHz IEEE 802.15.4 radio transceiver, near field communications (NFC) controller |  |  |

Table 3. LS1028ARDB features (continued)

| LS1028ARDB feature              | Specification                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

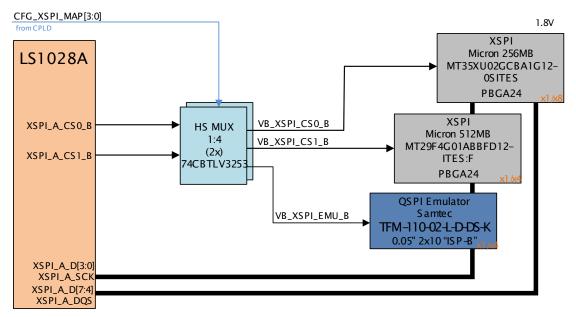

| Octal SPI (XSPI)                | One XSPI (XSPI A)                                                                                | One 256 MB onboard XSPI serial NOR flash memory     One 512 MB onboard XSPI serial NAND flash memory     Supports a QSPI emulator for offboard QSPI emulation                                                                                                                                                                                                                 |  |  |

| I2C                             | Six I2C interfaces                                                                               | <ul> <li>All system devices are accessed via I2C1, which is multiplexed on I2C multiplexer PCA9848 to isolate address conflicts and reduce capacitive load</li> <li>I2C1 is used for EEPROMs, RTC, INA220 current-power sensor, thermal monitor, PCIe/SATA M.2 connectors and mikro-click modules 1 and 2</li> </ul>                                                          |  |  |

| Serial ports                    | Two UART ports<br>(UART1 and UART2)                                                              | <ul> <li>UART1 supports RS-232 levels of up to 1 Mbit/s data rate on a DB9 male connector. LTC8204 RS232 transceiver is used for interface conversion. Hardware handshaking is not supported.</li> <li>UART2 can be used to interface with either mikro-click modules or RS-232 transceiver LTC2804 (similar to UART1). The selection can be controlled from FPGA.</li> </ul> |  |  |

| CAN                             | Two CAN ports (CAN1 and CAN2)                                                                    | The two CAN DB9 ports can support CAN FD fast phase at data rates of up to 5 Mbit/s.                                                                                                                                                                                                                                                                                          |  |  |

| Ethernet                        | SGMII (1 GB Ethernet port)  QSGMII (four 1 GB Ethernet ports)  IEEE 1588 <sup>™</sup>            |                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| USB 3.0                         | Two high-speed USB 3.0 ports with integrated PHYs                                                | <ul> <li>Supports super-speed (5 Gbit/s) operations</li> <li>USB 3.0 port 1 is configured as host with a Type A connector</li> <li>USB 3.0 port 2 is configured as downstream facing port (DFP) or upstream facing port (UFP) with a Type C connector</li> </ul>                                                                                                              |  |  |

| Serial audio interface<br>(SAI) | Audio transceiver<br>(used only on TX<br>signals) (not<br>supported by the<br>LS1043A processor) | Audio codec SGTL5000 provides headphone and audio LINEOUT for stereo speakers     IEEE1588 interface to support audio on SAI4                                                                                                                                                                                                                                                 |  |  |

| Display                         | DisplayPort (not<br>supported by the<br>LS1043A processor)                                       | <ul> <li>Supports display resolution of up to 4Kp60</li> <li>Supports link transfer rates of up to HBR2 (5.4 Gbit/s)</li> </ul>                                                                                                                                                                                                                                               |  |  |

| Clocks                          | Differential system clock (DIFF_SYSCLK)                                                          | 100 MHz                                                                                                                                                                                                                                                                                                                                                                       |  |  |

Table 3. LS1028ARDB features (continued)

| LS1028ARDB feature | Specification                     | Description                                                                                                                                                                             |  |

|--------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | SerDes clocks                     | REF_CLK1 and REF_CLK2 of 100 MHz                                                                                                                                                        |  |

|                    | Ethernet clocks                   | 125 MHz clock to Ethernet controller either from the IEEE 1588 port or an onboard oscillator                                                                                            |  |

|                    | Display Port clock<br>(DP_REFCLK) | 27 MHz                                                                                                                                                                                  |  |

|                    | FPGA CLK                          | 25 MHz clock to CPLD                                                                                                                                                                    |  |

| Power supplies     |                                   | 12 V input power from DC input adaptor                                                                                                                                                  |  |

|                    |                                   | • 5.0 V for USB1, USB2, CAN1, CAN2, and mikro-click modules                                                                                                                             |  |

|                    |                                   | 1.0 V (VDD) for core and platforms                                                                                                                                                      |  |

|                    |                                   | • Filtered 1.0 V / 0.9 V USB_SDVDD, USB_SVDD, DP_SVDD, SVDD                                                                                                                             |  |

|                    |                                   | <ul> <li>3.3 V for board components (SGMII PHY, M.2 connectors, SD card,<br/>eMMC, CAN transceivers, mikroBUS connectors, LEDs, DP port,<br/>CPLD IO and VDD, clockgen VDDO)</li> </ul> |  |

|                    |                                   | Filtered 3.3 V for USB_HVDD                                                                                                                                                             |  |

|                    |                                   | <ul> <li>1.8 V for board components (UART transceivers, XSPI memories,<br/>eMMC memory IO VDD, CPLD IO bank3)</li> </ul>                                                                |  |

|                    |                                   | 1.8 V clockgen VDD and VDDA                                                                                                                                                             |  |

|                    |                                   | • 1.8 V OVDD, TH_VDD                                                                                                                                                                    |  |

|                    |                                   | Filtered 1.35 V X1VDD, AVDD_SD1_PLL1, AVDD_SD1_PLL2                                                                                                                                     |  |

|                    |                                   | 2.5 V QSGMII PHY VDD25, VDD25A, and DDR4 memory VPP                                                                                                                                     |  |

|                    |                                   | 1.0 V QSGMII PHY VDD, VDDA                                                                                                                                                              |  |

|                    |                                   | • 1.2 V DRAM VDD                                                                                                                                                                        |  |

|                    |                                   | 0.6 V DRAM VTT, VREF                                                                                                                                                                    |  |

|                    |                                   | 3.3 V / 1.8 V EVDD for eSDHC                                                                                                                                                            |  |

|                    |                                   | • 0.9 V / 1.0 V TA_BB_VDD                                                                                                                                                               |  |

| Debug interface    |                                   | Arm Cortex 10-pin JTAG connector                                                                                                                                                        |  |

|                    |                                   | CPLD programming header                                                                                                                                                                 |  |

| Package            |                                   | Package type is Flip Chip, Plastic-ball, Grid Array (FC-PBGA), 17 mm     x 17 mm                                                                                                        |  |

|                    |                                   | Socket and heat sink are included                                                                                                                                                       |  |

#### Table 3. LS1028ARDB features (continued)

| LS1028ARDB feature | Specification | Description                                            |  |

|--------------------|---------------|--------------------------------------------------------|--|

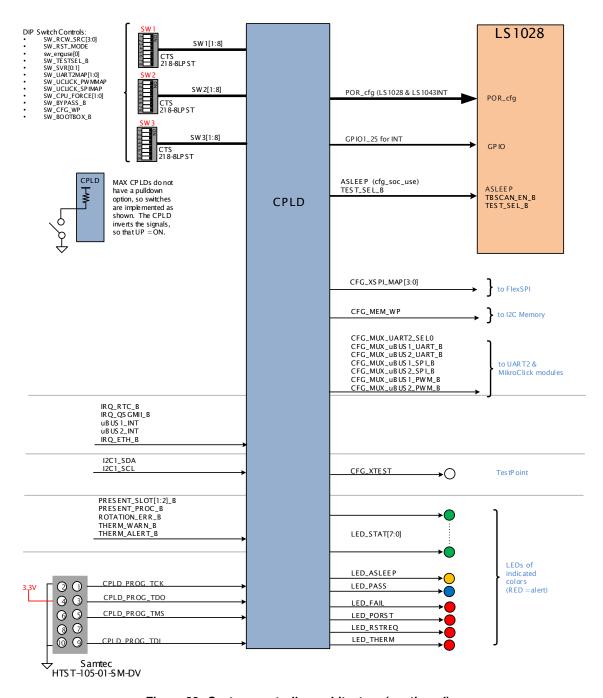

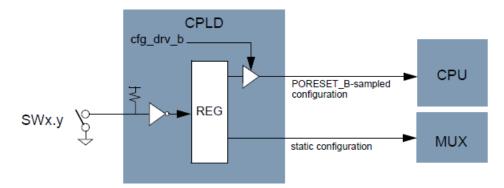

| System logic       | CPLD          | Manages the following:                                 |  |

|                    |               | System reset sequencing                                |  |

|                    |               | <ul> <li>SoC POR configuration at reset</li> </ul>     |  |

|                    |               | Implements registers for system control and monitoring |  |

|                    |               | General fault monitoring and logging                   |  |

# Chapter 2 LS1028ARDB Functional Description

This chapter explains all major functional components of the LS1028ARDB. The chapter is divided into the following sections:

- Processor

- Power supplies on page 15

- · Clocks on page 21

- DDR interface on page 23

- USB interface on page 24

- DisplayPort on page 26

- SerDes interface on page 26

- Ethernet controller interface on page 27

- M.2 connectors on page 31

- DUART interface on page 32

- CAN interface on page 33

- I2C interface on page 34

- XSPI interface on page 38

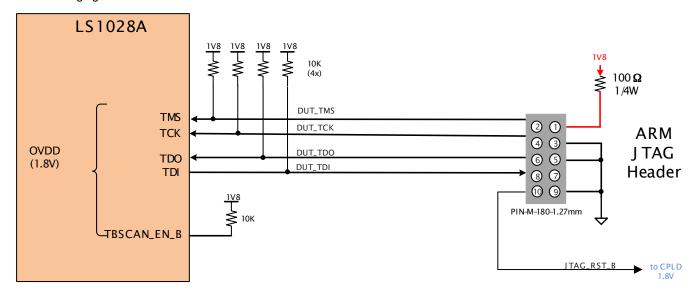

- JTAG port on page 40

- eSDHC interface on page 40

- Mikro-click modules on page 41

- GPIOs on page 43

- Interrupt handling on page 43

- Temperature measurement on page 44

- System controller on page 44

#### 2.1 Processor

The LS1028ARDB board is based on the QorlQ LS1028A processor having two Arm® Cortex®- A72 processor cores. The LS1028ARDB board supports as many features of the LS1028A as possible. In addition, the LS1028ARDB board supports an LS1043A interposer that allows early evaluation of the board with limited features and restrictions.

As a restriction, the following interfaces cannot be tested using the LS1043A interposer:

- DisplayPort

- SDHC2

- · Octal SPI (XSPI)

- CAN

- SPI3

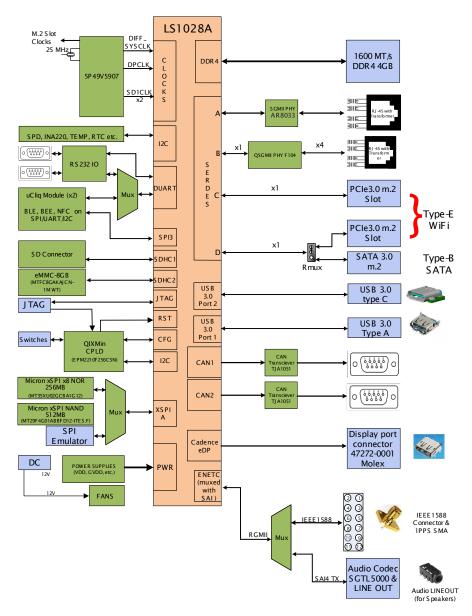

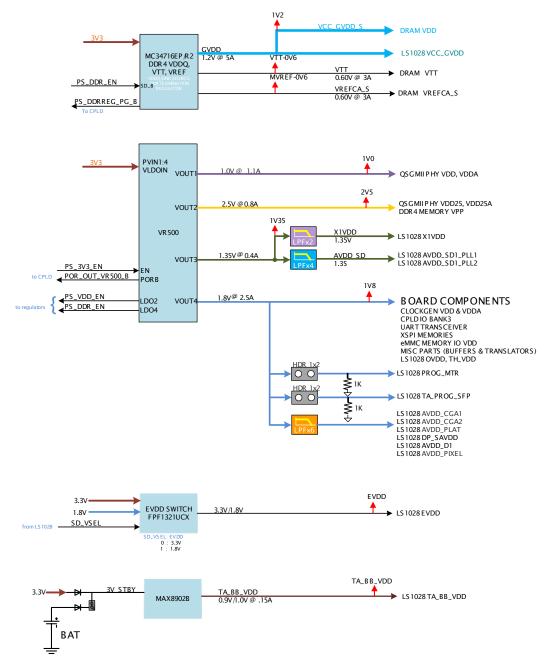

## 2.2 Power supplies

The LS1028ARDB generates all the voltages necessary for the correct operation of the LS1028A processor, DDR4, PHYs, and numerous other peripherals. All power is derived from an external 12 V DC power supply.

The following figures show the block diagram of LS1028ARDB power supplies:

Figure 3. Power supplies - Part 1

Figure 4. Power supplies - Part 2

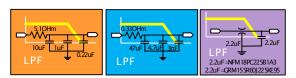

Note that several power supplies have onboard low-pass filters, to prevent board switching noise from coupling into sensitive analog supplies. The figure below shows the filters used.

Figure 5. Passive low pass filters

## 2.2.1 Primary power supply

The LS1028ARDB is powered up through an external 12 V DC power adapter. The specifications of the DC adapter are as follows:

- Input: 100 240 VAC, 50 60 Hz

- Output: 12 V, 0 5 A DC power supply adapter (160 W) Standard

- DC Jack (2 pin, 2.5 mm x 5.5 mm x 11 mm)

## 2.2.2 Secondary power supplies

The following table lists different power supply components used to generate various LS1028ARDB power supplies.

Table 4. Secondary power supplies

| Part<br>identifi<br>er | Manufacturing part number | Part<br>manufacturer  | Power supply | Specifications                        | Description                                                                                                                                                                                                                                                                                                                             |

|------------------------|---------------------------|-----------------------|--------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U1                     | LT8609SEV                 | Linear<br>Technology  | 5V0          | 5 V at 2 A                            | Supplies power to the board components:  • USB 1 and USB 2 connectors  • CAN transceivers  • Mikro-click modules                                                                                                                                                                                                                        |

| U2                     | LTC7151S                  | Linear<br>Technology  | VDD          | 1.0 V / 0.9 V at 20<br>A <sup>1</sup> | Supplies power to the LS1028A core supplies.  NOTE  Filtered VDD also powers USB (USB_SDVDD, USB_SVDD), Display Port (DP_SVDD), and SerDes (SVDD) power supplies of LS1028A.                                                                                                                                                            |

| U3                     | LTC7151S                  | Linear<br>Technology  | 3V3          | 3.3 V at 15 A                         | Supplies power to board components: CPLD IO and VDD, Display Port, SGMII PHY, M.2 connectors, SD card, eMMC memory, I2C EEPROMs, current monitor (INA220), Temperature monitor (SA56004ED), CAN transceivers, mikroBUS connectors, misc components (buffers and translators).  NOTE Filtered 3V3 also powers USB (USB_HVDD of LS1028A). |

| U4                     | MC34716EP                 | NXP<br>Semiconductors | 1V2          | 1.2 V at 4 A                          | DDR4 DRAM memories LS1028A DRAM controller core and I/O                                                                                                                                                                                                                                                                                 |

|                        |                           |                       | VTT_0V6      | 0.6 V at 3 A                          | Address and control bus termination supply                                                                                                                                                                                                                                                                                              |

Table 4. Secondary power supplies (continued)

| Part<br>identifi<br>er | Manufacturing part number | Part<br>manufacturer  | Power supply           | Specifications                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|---------------------------|-----------------------|------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                           |                       | MVREF                  | 0.6 V at 3 A                                                         | Reference voltage for DDR4 DRAM memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| U6                     | MC34VR500V9<br>ES         | NXP<br>Semiconductors | 1V0, 2V5,<br>1V35, 1V8 | • 1.0 V at 1.1 A • 2.5 V at 0.8 A • 1.35 V at 0.4 A • 1.8 V at 2.5 A | Multi-output DC/DC regulator with four switched outputs, two LDO outputs (VDD and DDR enable), and one reset control output to CPLD (RST_OUT). Four switched outputs are:  • SW1LX: 1.0 V for the QSGMII PHY VDD and VDDA  • SW2LX: 2.5 V for QSGMII PHY VDD25, VDD25A, and DDR4 memory VPP  • SW3LX: 1.35 V; Filtered 1.35 V is supplied to LS1028A X1VDD, AVDD_SD1_PLL1, and AVDD_SD1_PLL2  • SW4LX: 1.8 V for board components: UART transceiver, XSPI memories, eMMC memory IO, CPLD IO bank3, clockgen VDD and VDDA  NOTE  Filtered 1V8 also powers LS1028A power supplies: AVDD_CGA1, AVDD_CGA2, AVDD_PLAT, DP_SAVDD, AVDD_D1, and AVDD_PIXEL.  NOTE  Jumper-enabled 1V8 also powers PROG_MTR and PROG_SFP. |

Table 4. Secondary power supplies (continued)

| Part<br>identifi<br>er | Manufacturing part number | Part<br>manufacturer | Power supply  | Specifications             | Description                                                                                                                                                                                                   |

|------------------------|---------------------------|----------------------|---------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U7                     | FPF1321UCX                | ON<br>Semiconductor  | EVDD          | 3.3 V<br>1.8 V             | NOTE  EVDD boots up to 3.3 V and can be changed to 1.8 V depending upon the SD_VSEL pin state that is controlled from the LS1028A SDHC IP block.  NOTE  The FPF1321UCX is a power switch, not a power supply. |

| U8                     | MAX8902B                  | Maxim<br>Integrated  | TA_BB_V<br>DD | 0.9 V / 1.0 V at 0.15<br>A | Power supply for TA_BB_VDD.                                                                                                                                                                                   |

<sup>1.</sup> VDD is 1.0 V or 0.9 V depending upon the state of GPIO1\_DAT24 GPIO pin of LS1028A.

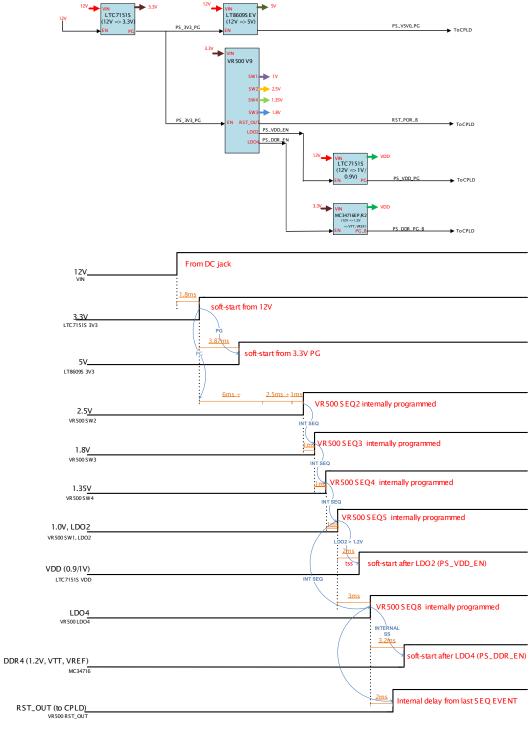

## 2.2.3 Power supply sequence

The LS1028ARDB board is configured to switch ON automatically when the 12 V power supply is switched ON and is connected to jack (J1) on the board.

The 12 V input can be subsequently power cycled using the following events:

- The power switch (push button) is pressed

- The register bit, PWR\_CTL2[PWR], is set to '1' using the I2C or JTAG/CCS communication paths

On the availability of 12 V supply to the power regulators, the orderly enable of all power supplies are sequenced using powergood of the regulators, as shown in the following figure.

## Sequence

Figure 6. Power up voltage sequence

NOTE

$\label{thm:continuous} The \ LS1028 ARDB \ follows \ the \ power \ supply \ sequencing \ requirements \ as \ detailed \ in \ \textit{QorIQ LS1028A Data Sheet}.$

#### 2.2.4 Current and power measurement

The LS1028ARDB implements onboard current and power measurements only for the VDD supply. The table below lists all measurable supplies.

Table 5. Power monitoring

| Power | Measurement device | Shunt resistor value | Notes                                                                                                                                    |

|-------|--------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| VDD   | INA220             | 0.001                | The VDD supply powers the LS1028A core (0.9 V / 1 V), USB (USB_SDVDD, USB_SVDD), DisplayPort (DP_SVDD) and SerDes (SVDD) power supplies. |

Power supplies not listed in the above table are considered as low-current/incidental supplies and are not instrumented for power measurement.

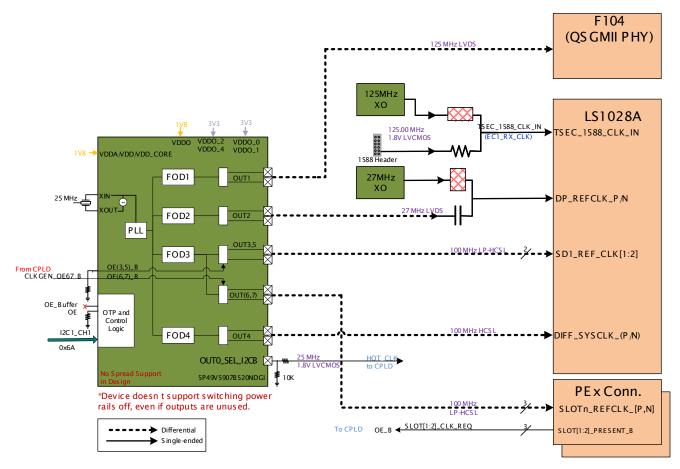

#### 2.3 Clocks

The LS1028ARDB provides all the clocks required for the processor and peripheral interfaces. The figure below shows the LS1028ARDB clock architecture.

Figure 7. LS1028ARDB clock architecture

The 5P49V5907B520NDGI is a programmable clock generator that generates most of the clocks. Clock configurations are stored in its one-time programmable (OTP) memory. The configuration in volatile memory can be changed through the I2C1\_CH1 interface. The device is accessible at 0x6A I2C 7-bit address. The frequencies are generated from a 25 MHz crystal (603-25-261 from FOX Electronics). The following table summarizes the specifications of each clock.

Table 6. LS1028ARDB clocks

| Part<br>identifier | Clock generator                                          | Clock                                                            | Specifications                                                                                                | Destination                                |

|--------------------|----------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| U9                 | IDT 5P49V5907B520NDGI                                    | VDD0: FPGA_CLK_25MHz                                             | <ul> <li>Frequency: 25 MHz</li> <li>Output type:<br/>LVCMOS</li> <li>Operating voltage:<br/>3.3 V</li> </ul>  | CPLD                                       |

|                    |                                                          | OUT3,5:<br>SD1_REF_CLK1_[P, N]<br>SD1_REF_CLK2_[P,N]             | Frequency: 100 MHz     Output type: LP-HCSL     Operating voltage: 1.8 V                                      | SerDes1<br>controller                      |

|                    |                                                          | OUT6, 7 <sup>1</sup> : PEXM2_1_REFCLK_[P,N] PEXM2_2_REFCLK_[P,N] | Frequency: 100 MHz     Output type: LP-HCSL     Operating voltage: 1.8 V                                      | M.2 connectors<br>1 and 2                  |

|                    |                                                          | OUT4:<br>DIFF_SYSCLK[P, N]                                       | <ul><li>Frequency: 100 MHz</li><li>Output type: HCSL</li><li>Operating voltage: 3.3 V</li></ul>               | DIFF_SYSCLK                                |

|                    |                                                          | OUT2:<br>DP_REFCLK_[P, N]                                        | <ul><li>Frequency: 27 MHz</li><li>Output type: LVDS</li><li>Operating voltage:<br/>3.3 V</li></ul>            | Display Port                               |

|                    |                                                          | OUT1:<br>125M0_LVDS_REF_CLK_[P,N]                                | <ul><li>Frequency: 125 MHz</li><li>Output type: LVDS</li><li>Operating voltage:<br/>3.3 V</li></ul>           | QSGMII PHY                                 |

| Y2 <sup>2</sup>    | 125 MHz crystal oscillator<br>(KC5032A125.000C1GE00<br>) | EC1_125MHz_CLK<br>(EC1_RX_CLK)                                   | <ul> <li>Frequency: 125 MHz</li> <li>Output type:<br/>LVCMOS</li> <li>Operating voltage:<br/>1.8 V</li> </ul> | Ethernet<br>controller / IEEE<br>1588 port |

Table 6. LS1028ARDB clocks (continued)

| Part identifier  | Clock generator | Clock                     | Specifications    | Destination  |

|------------------|-----------------|---------------------------|-------------------|--------------|

| U91 <sup>3</sup> | 27 MHz crystal  | DP_REFCLK_P DP_REFCLK_N   | Frequency: 27 MHz | Display port |

| Y3               | 25 MHz crystal  | ETH_XTALIN<br>ETH_XTALOUT | Frequency: 25 MHz | SGMII PHY    |

- 1. The enable/disable for 100 MHz clocks to the M.2 connectors (J16 and J18/J20) is controlled by CPLD. The CPLD detects the CARD presence on the M.2 slots and enables the OUT 6 and 7 of the clock generator accordingly. Since, both the outputs are controlled from the same OE, 100 MHz clocks to the M.2 slots are enabled even if only one of the M.2 slots is populated.

- 2. The Y2 oscillator provides an option for stable 125 MHz CLK\_IN to the 1588 block. The option can be enabled by mounting R388 and removing R387 that is mounted on the board by default.

- 3. The U91 oscillator provides an option for a low jitter clock input for Display interface. Clock from U91 can be enabled by removing C646, C647 and mounting C705, C706. The C646 and C647 capacitors are mounted by default.

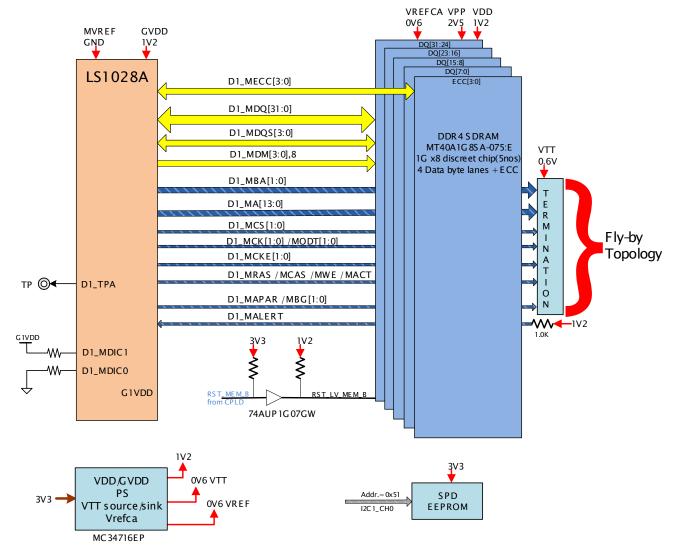

#### 2.4 DDR interface

The LS1028ARDB board supports four 1G x8 DDR4 SDRAM memory chips supporting data transfer rates of up to 1.6 GT/s and one 1G x8 DDR4 SDRAM memory chip for supporting ECC.

The address and control/command signals to the DDR4 SDRAM memory chips are routed in as per the Fly-by topology and are terminated to VTT (0.6 V). The data bus and associated signals, such as DM and DQS/DQS\_B have one-to-one byte wise connections to the individual x8 DDR4 memories. The ECC nibble goes to the fifth DDR4 memory. The part number of the SDRAM memory chips is MT40A1G8SA-075:E (from Micron Technology).

Following are the characteristics of the LS1028A DDR4 memory controller:

- Up to 1.6 GT/s

- Supports 32-bit operation (with ECC support)

- · Supports x8 devices

- Supports two chip selects, D1\_MCS0\_B and D1\_MCS1\_B; however, on board only D1\_MCS0\_B chip select is supported

- IOs powered by 1.2 V power supply from MC34716EP switch regulator

The MC34716EP switch regulator generates the following different power supplies for the DDR4 controller IO, memory devices, and terminations: VCC\_GVDD\_S (1.2 V), VTT (0.6 V) and VREFCA (0.6 V). The memory interface including all the necessary termination and I/O power are routed, as shown in the following figure.

Figure 8. DDR4 interface

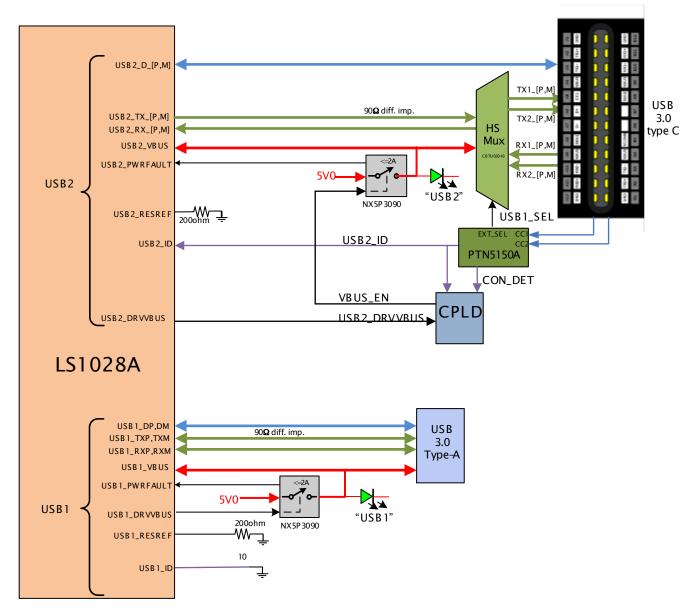

### 2.5 USB interface

The LS1028ARDB supports two USB 3.0 ports. The USB 1 port is connected to a Type A connector and is configured as host. Type A connector is always host only. The USB2 port is connected to a Type C connector and is configured as downstream facing port (DFP) or upstream facing port (UFP). Based on the configuration detected on the Type C port, the USB2 PHY can operate either in host or device mode. The following figure shows the architecture of the USB 3.0 interface.

Figure 9. USB architecture

The PTN5150A (from NXP) is a small low-power configuration channel logic chip that detects (through CC1 and CC2 pins) and indicates to the USB controller (through USB2\_ID signal) if the USB2 Type C connector is configured as a device or host. The PTN5150A is configured to operate the USB3 Type C port in DFP mode with default USB current capability (0.5 A / 0.9 A). To support higher current on the Type C (USB2) port, the hardware configuration of PTN5150 and NX5P3090UK VBUS switch should be changed. Refer to the device datasheet for more information.

The USBx\_DRVVBUS and USBx\_PWRFAULT pins of each USB controller are connected to a programmable-current USB switch, NX5P3090UK (from NXP), for individual port management. The USB switch is powered from +5 V USB power supply. To indicate power fault conditions, the USB switch sends PWRFAULT signals to the USB controller. For USB2 port, the USB switch drives USB2 VBUS (USB2\_VBUS) when USB2\_DRVVBUS=1, USB1\_ID = 0, and USB2\_CON\_DET=1, this logic is controlled by CPLD. For USB1 port, the USB switch drives USB1 VBUS (USB1\_VBUS) when USB1\_DRVVBUS=1.

The maximum allowed current consumption of a USB connected device is 900 mA per channel.

Both, USB1 and USB2 connectors have an LED nearby, USB1\_5V and USB2\_5V, respectively, which are active when the +5 V USB power supply is enabled to the connectors.

## 2.6 DisplayPort

The LS1028A processor supports and embedded DisplayPort (eDP) TX controller that connects to the DisplayPort connector on the board for digital display.

The controller supports the following:

- Supports DisplayPort 1.3 and eDP 1.4

- Supports link transfer rates of up to HBR2 (5.4 Gbit/s) and display resolution up to 4Kp60

The CONFIG1 and CONFIG2 pins of the DisplayPort are pulled down with 1  $M\Omega$  resistors to avoid any power driven on the DP\_PWR pin from a downstream device.

The DP\_PWR pin can provide 3.3 V up to 3 A inrush current through a power switch NX5P3090UK (controlled through the CPLD register).

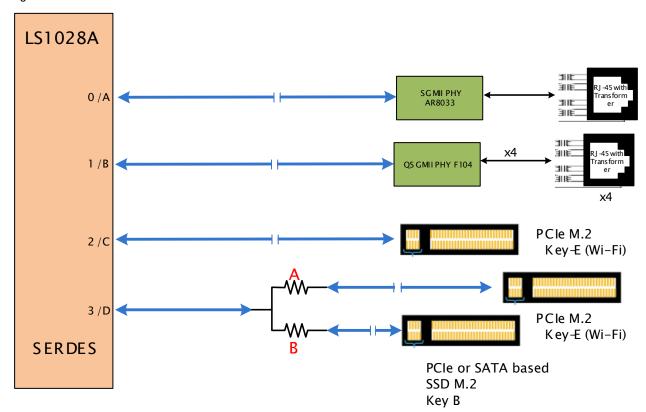

#### 2.7 SerDes interface

The LS1028A processor supports one SerDes LYNX36 module with four high-speed serial communication lanes to support various protocols, such as SGMII, QSGMII, PCIe, and SATA.

The figure below shows the LS1028ARDB SerDes architecture.

Figure 10. SerDes architecture

The LS1028A SerDes module support several protocols, which are assigned to dedicated functions on the LS1028ARDB, as shown in the table below.

Table 7. SerDes assignments

| SerDes<br>module | Lane  | Connectivity                                 | Port                                                                      |

|------------------|-------|----------------------------------------------|---------------------------------------------------------------------------|

| 1                | 0 / A | Qualcomm AR8033 1 GbE PHY                    | 1 x 1GbE RJ45 on SGMII MAC interface                                      |

|                  | 1 / B | NXP F104S8A QSGMII<br>Quad 1 GbE PHY         | 4 x 1GbE RJ45 on QSGMII MAC interface                                     |

|                  | 2/C   | PCIe Gen 3 (8 Gbit/s)                        | M.2 Key E slot for Wi-Fi cards                                            |

|                  | 3 / D | PCIe Gen 3 (8 Gbit/s) or SATA 3.0 (6 Gbit/s) | M.2 Key E slot for Wi-Fi cards or M.2 Key B slot for SATA based SSD cards |

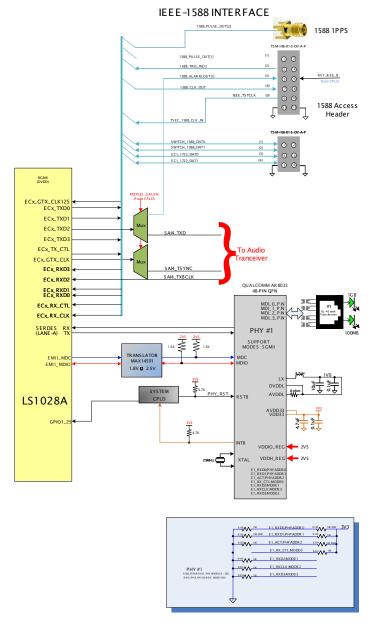

#### 2.8 Ethernet controller interface

The LS1028A processor supports one Ethernet controller (ENETC), which connects either to an onboard 1588 access header or to an audio transceiver (through TX signals only) and an SGMII port (over LYNX36 SerDes Lane A). The controller also supports QSGMII connectivity through the TSN switch and it is available over LYNX36 SerDes interface (Lane B).

The EMI1 MDIO/MDC signals control the SGMII and QSGMII PHY transceivers. EMI1 operates at OVDD (1.8 V) levels. The signals are bi-directionally shifted to 2.5 V for compatibility with both AR8033 (one-port SGMII) and F104S8A PHY (Four-port QSGMII).

#### 2.8.1 SGMII Ethernet

The onboard Ethernet PHY, Qualcomm AR8033 PHY (U23) connects to the ENETC of the LS1028A processor using SGMII protocol over LYNX36 SerDes lane A.

Figure 11. SGMII and IEEE 1588

Table 8. Hardware bootstrap settings for SGMII PHY

| Setting        | Description           |

|----------------|-----------------------|

| PHY_AD[2:0]    | PHY address = 0b00010 |

| MODE[3:0]=0001 | SGMII<=>UTP           |

#### 2.8.2 QSGMII Ethernet

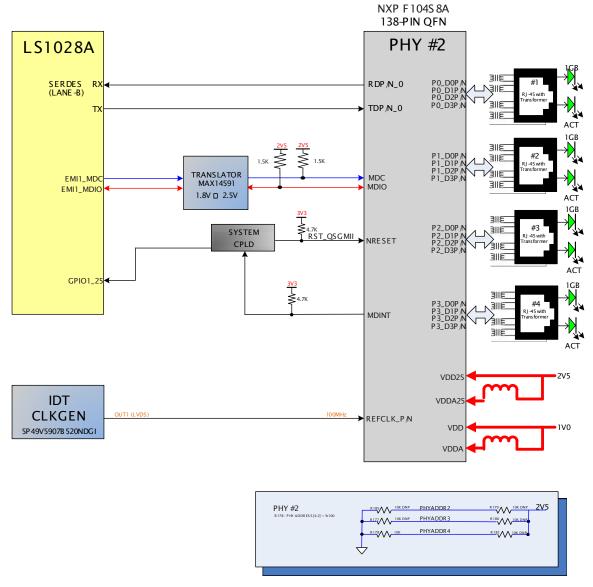

The onboard Ethernet PHY, NXP F104S8A PHY (U24), connects to the TSN switch of the LS1028 processor using QSGMII protocol over SerDes lane B.

The following figure shows the QSGMII interface.

Figure 12. QSGMII port

Table 9. Hardware bootstrap settings for QSGMII PHY

| Setting     | Description                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY_AD[4:2] | PHY address = 0b100                                                                                                                                  |

| MODE        | <ul> <li>REFCLK_SEL[1:0] = 00: 125 MHz is used as REFCLK.</li> <li>COMA_MODE = 0: PHY comes out of reset as soon as reset is de-asserted.</li> </ul> |

#### **2.8.3 IEEE 1588 interface**

The LS1028A processor provides support for the IEEE 1588<sup>™</sup> precision time protocol (PTP), which works in tandem with ENETC to time-stamp the incoming packets. A 12-pin header (J11) is provided on the board to allow support for 1588 protocol. The SMA connector (J12) is used to analyze time synchronization by measuring the pulse per second (PPS) signal. A 6-pin header (J13) is used to access TSN switch 1588 pins and IEEE 1722 pins.

The IEEE signals are multiplexed with the SAI4 signals (see Figure 11. on page 28) and LS1028ARDB uses the multiplexer 74LVC2G3157DPJ (U92, from Nexperia) to demux. The IEEE signals available on header J11 and J13 depend upon the RCW settings and the appropriate signal through the CPLD. For more information on the RCW settings, see *QorlQ LS1028A Reference Manual*.

Figure 11. on page 28 shows the architecture of the IEEE 1588 system.

The table below lists the testing options provided by the IEEE 1588 test header.

Table 10. IEEE 1588 port

| IEEE 1588 feature | Specifications        | Description                                                                                                                                                                |

|-------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks            | Input clock           | ETH reference clock (to processor) is driven from an onboard 125 MHz oscillator source. Under software configuration, it may be clocked from the IEEE 1588 header instead. |

| Signals           | Other related signals | All remaining IEEE 1588 signals are connected to the dedicated header pins                                                                                                 |

Table 11. IEEE1588 and IEEE1722 signals

| Signal name                   | Connector name and Designator        | Description                               | Availability with Audio |

|-------------------------------|--------------------------------------|-------------------------------------------|-------------------------|

| 1588_PULSE_OUT2               | 1PPS(IEEE1588) (J12)                 | SMA connector                             | Yes                     |

| 1588_CLK_OUT                  | IEEE1588 (J11)                       | IEEE1588 header                           | Yes                     |

| 1588_ALARM_OUT[1]             | IEEE1588 (J11)                       | IEEE1588 header                           | No                      |

| 1588_PULSE_OUT1 <sup>1</sup>  | IEEE1588 (J11)                       | IEEE1588 header                           | No                      |

| SWITCH_1588_DAT1 <sup>1</sup> | TSN Switch IEEE1588 & IEEE1722 (J13) | IEEE1588 signals from TSN switch          | No                      |

| SWITCH_1588_DAT0 <sup>1</sup> | TSN Switch IEEE1588 & IEEE1722 (J13) | IEEE1588 signals from TSN switch          | No                      |

| EC1_1722_DAT0 <sup>1</sup>    | TSN Switch IEEE1588 & IEEE1722 (J13) | IEEE1722 synchronization signal for audio | Yes                     |

| EC1_1722_DAT1 <sup>1</sup>    | TSN Switch IEEE1588 & IEEE1722 (J13) | IEEE1722 synchronization signal for audio | No                      |

| 1588_TRIG_IN1                 | IEEE1588 (J11)                       | IEEE1588 header                           | Yes                     |

| 1588_CLK_IN <sup>1</sup>      | IEEE1588 (J11)                       | IEEE1588 header                           | Yes                     |

<sup>1.</sup> This signal is available only when RCW field EC1\_SAI4\_5\_PMUX is set to 3'b101 (IEEE1588).

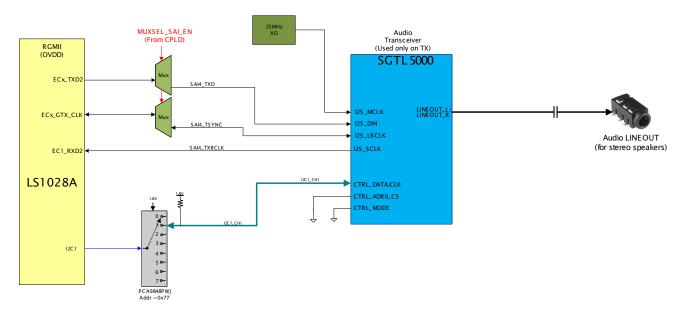

## 2.9 Synchronous audio interface (SAI)

The LS1028ARDB board supports audio through NXP SGTL5000-32QFN audio codec (U93). The board supports one audio LINEOUT (J34) for headphone and stereo speakers. The figure below shows the LS1028ARDB audio interface architecture.

The SGTL5000 has 25 MHz as MCLK input to generate the required SAI and internal clocks. The device can provide or take as input the TSYNC based on desired configuration.

The SAI4 signals are multiplexed with the IEEE signals (see Figure 11. on page 28) and LS1028ARDB uses the multiplexer 74LVC2G3157DPJ (U92, from Nexperia) to demux. Software must configure the appropriate signal through FPGA, to select the appropriate controller and interface.

Table 12. SAI4 configuration and setup

| Configuration signal | Controlled by | Description                                   |

|----------------------|---------------|-----------------------------------------------|

| MUXSEL_SAI_EN        | BRDCFG3[2]    | 0: IEEE signals connect to the IEEE header    |

|                      |               | 1: IEEE signals connect to the SAI4     CODEC |

## 2.10 M.2 connectors

The LS1028ARDB supports M.2 connectors (Key E and Key B) that are supported through SerDes lanes 2 and 3.

One M.2 Key E connector (J16) is connected through the LYNX36 SerDes lane 2. This connector supports only 1630 and 2230 PCIe Gen3 card types to provide wireless connectivity including Wi-Fi, Bluetooth, and NFC.

The other M.2 Key E connector (J18) is connected through the LYNX36 SerDes lane 3. However, lane 3 can also connect to the M.2 Key B connector (J20) as per the register settings mentioned in Table 13. Register configuration on page 31 to support solid state storage devices (SSD) ( SATA 3.0). The M.2 Key B connector supports 2230 and 2242 module card types.

The following table describes the three-pad arrangement that is required to select either Type E connector or Type B connector on the LYNX36 SerDes lane 3.

Table 13. Register configuration

| M.2 connector select | Signal name      | Mount register/capacitor | Values |

|----------------------|------------------|--------------------------|--------|

| Type E <sup>1</sup>  | PEXM2_2_REFCLK_P | R214                     | 0 Ω    |

Table 13. Register configuration (continued)

| M.2 connector select | Signal name      | Mount register/capacitor | Values       |

|----------------------|------------------|--------------------------|--------------|

|                      | PEXM2_2_REFCLK_N | R213                     | 0 Ω          |

|                      | PEXM2_2_PET_P    | C409                     | 0.22 μF ±10% |

|                      | PEXM2_2_PET_N    | C410                     | 0.22 μF ±10% |

|                      | PEXM2_2_PER_P    | R216                     | 0 Ω          |

|                      | PEXM2_2_PER_N    | R215                     | 0 Ω          |

| Туре В               | PEXM2_2_REFCLK_P | R223                     | 0 Ω          |

|                      | PEXM2_2_REFCLK_N | R222                     | 0 Ω          |

|                      | PEXM2_2_PET_P    | C423                     | 0.01 μF ±10% |

|                      | PEXM2_2_PET_N    | C422                     | 0.01 μF ±10% |

|                      | PEXM2_2_PER_P    | C420                     | 0.01 μF ±10% |

|                      | PEXM2_2_PER_N    | C421                     | 0.01 μF ±10% |

<sup>1.</sup> By default, registers and capacitors are mounted for the M.2 Key E connector (J18).

The M.2 Key E connectors J16 and J18 have 1x4-pin headers J17 and J19, respectively, for coexistence signals. Since, coexistence signal assignments on M.2 connectors is vendor dependant, refer to the vendor-specific documentation of M.2 modules for details.

## 2.10.1 Adapters

You can use adapters to convert M.2 connector to a PCIe slot for PCIe Gen 1 and Gen 2 compliant endpoints. For more detail on these adapters, click the following links.

- P11S-P11F M.2 (NGFF) to PCI-E Extender Board

- P11S-P11F Duo PCI-E to M.2 (NGFF) Extender Board

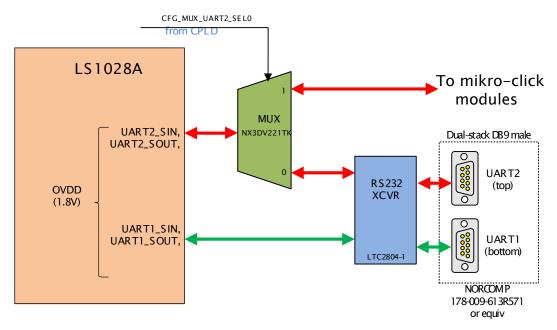

#### 2.11 DUART interface

The LS1028A device provides one instance of the DUART block, which support two 2-wire serial ports with no hardware flow control. On the LS1028ARDB board, the DUART ports connect to an RS-232 transceiver (Linear Technology LTC2804-1), which translates the UART1 and UART2 signals to RS-232 levels. The RS-232 signals of UART1 and UART2 are provided on dual DB9 male connector (DTE configuration) to provide convenient communication channels to both terminal and host computers.

It is recommended to use UART1 as a debug port. The LTC2804-1 transceiver can support 1 Mbit/s data rate on each of the serial ports.

The figure below shows the LS1028ARDB DUART connections.

Figure 14. DUART architecture

The UART2 signals can be used either to communicate with mikro-click modules or with RS232-compliant devices using the LTC2804-1 transceiver. The selection is done through a mux which is controlled through the CFG\_MUX\_UART2\_SEL0 signal by CPLD.

Configuration signal

Config register

DIP switch

Description

CFG\_MUX\_UART2\_SEL0

BRDCFG3[5:4]

SW2[5:6]

• 0x: UART2 on DB9 connector (default value)

• 10: UART2 on mikro-click module 1

• 11: UART2 on mikro-click module 2

Table 14. UART configuration and setup

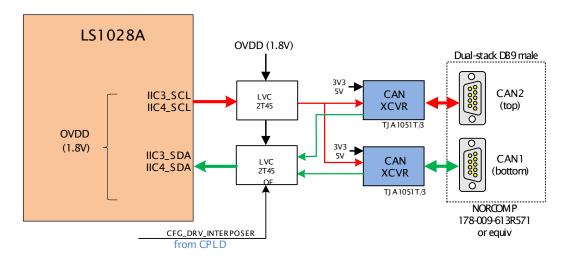

#### 2.12 CAN interface

The LS1028A processor supports two controller area network (CAN) modules, CAN1 and CAN2. On the LS1028ARDB, the CAN ports are available for external connection through a dual-port stacked DB9 male connector. Two high-speed CAN transceivers TJA1051T/3 from NXP (U54 and U56) provide an interface for the CAN ports to send and receive CAN signals to and from the processor. The TJA1052T/3 transceivers can support data rate of up to 5 Mbit/s in CAN with Flexible Data-Rate (CAN FD) phase.

The figure below shows the CAN architecture.

Figure 15. CAN architecture

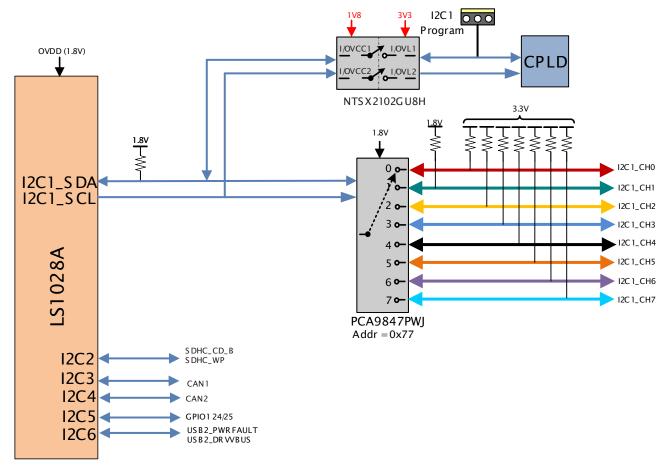

#### 2.13 I2C interface

The LS1028A processor supports up to six I2C buses. The I2C1 port is used for system setup and monitoring and the other ports should be programmed to be used for SDHC1 CD and WP, CAN 1 and 2 interfaces, GPIO, and USB2 PWRFAULT & DRVVBUS. These secondary functionalities should be enabled in the RCW field.

The I2C1 port is connected to a PCA9847PWJ I2C multiplexer to isolate address conflicts and to effectively manage the large number of I2C devices. The I2C1 port is connected to the level shifter device NTSX2102GU8H (from NXP) to enable bidirectional voltage level translation (1.8 V to 3.3 V and 3.3 V to 1.8 V) for CPLD and external I2C devices.

The figure below shows the I2C bus architecture.

Figure 16. I2C bus architecture

The multiplexer used for the I2C1 bus partitions the bus into eight sub-buses, called "channels." Software must program the multiplexer to access one of the eight I2C1 channels. All boot-software-dependant devices are placed on channel 0, or "I2C1\_CH0" as it is named. Channel 0 is the default selection upon reset so that software has immediate access to critical resources.

All channels on I2C1 are translated to 3V3 except channel 1, which operates at 1V8 (OVDD) power supply.

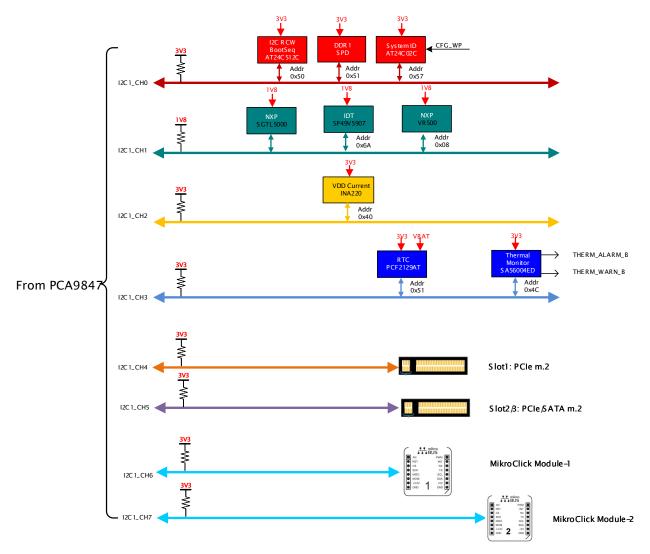

The I2C devices available on the I2C1 bus are shown in the figure below.

Figure 17. I2C1 channels

The following table describes the devices available on each of the eight I2C1 channels.

Table 15. I2C1 bus device map

| I2C bus  | 7-bit address | Device                                  | Description                   | Notes                                           |

|----------|---------------|-----------------------------------------|-------------------------------|-------------------------------------------------|

| (AII)    | -             | I2C master                              | LS1028ARDB                    |                                                 |

|          | 0x66          | I2C slave                               | CPLD                          | I2C access to CPLD BCSRs (registers).           |

|          | 0x77          | NXP PCA9847PWJ                          | I2C bus multiplexer (primary) | Converts I2C1 bus into eight channels           |

| I2C1_CH0 | 0x50          | Atmel AT24C512C-XHD-<br>B: 64 KB EEPROM | UEFI/ boot memory             | Provides I2C booting option. Write protectable. |

Table 15. I2C1 bus device map (continued)

| I2C bus  | 7-bit address                                                         | Device                                   | Description                           | Notes                                                                                                                                      |

|----------|-----------------------------------------------------------------------|------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|          | 0x51                                                                  | AT24C04C 512-byte<br>DDR4 SPD EEPROM     | SPD data                              | Stores SPD and temperature data for DDR4 SDRAM memory. Write protectable.                                                                  |

|          | 0x57                                                                  | Atmel AT24C02C-XHM-B:<br>256-byte EEPROM | System ID                             | Stores board-specific data, such as MAC addresses and serial number/errata. Write protectable.                                             |

| I2C1_CH1 | 0x0A                                                                  | SGTL5000 32QFN                           | Low-power stereo codec                | Audio transceiver providing audio LINEOUT for stereo speakers                                                                              |

|          | 0x6A                                                                  | IDT 5P49V5907                            | Programmable clock generator          | Generates differential<br>sysclk and reference<br>clocks for DP, LYNX36<br>SerDes and PEX M.2<br>connectors                                |

|          | 0x08                                                                  | NXP MC34VR500V9ES                        | PMIC switched outputs                 | Generates 1.8 V, 1.35 V, 1.0 V, and 2.5 V                                                                                                  |

| I2C1_CH2 | 0x40                                                                  | Texas Instruments<br>INA220              | VDD voltage/current/<br>power monitor | Reports voltage, current, and power data for VDD                                                                                           |

| I2C1_CH3 | 0x4C                                                                  | NXP SA56004ED                            | Thermal monitor                       | Monitors processor thermal diode                                                                                                           |

|          | 0x51                                                                  | NXP PCF2129AT                            | Battery-backed clock                  | Provides time and date functionality with battery backup option                                                                            |

| I2C1_CH4 | I2C address is<br>defined by the<br>plugged-in PCIe<br>card           | PCIe M.2                                 | Key E connector                       | I2C path for the M.2<br>connector (J16), which<br>supports Wi-Fi cards on<br>lane 2 of LYNX36<br>SerDes.                                   |

| I2C1_CH5 | I2C address is<br>defined by the<br>plugged-in PCIe/<br>SATA card     | PCIe M.2                                 | Key E / Key B connector               | I2C path for the J18 or<br>J20 M.2 connector which<br>supports Wi-Fi or SATA<br>SSD cards, respectively,<br>on lane 3 of LYNX36<br>SerDes. |

| I2C1_CH6 | I2C address is<br>defined by the<br>plugged-in mikro-<br>click module | MIKROE 1597                              | BLE / BEE / NFC                       | Provides I2C connectivity to mikro-click modules on connectors J29 and J30.                                                                |

Table 15. I2C1 bus device map (continued)

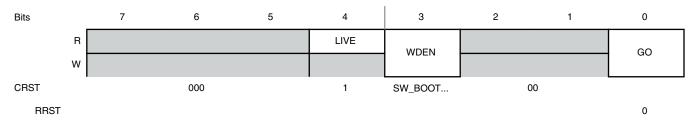

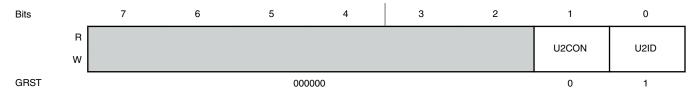

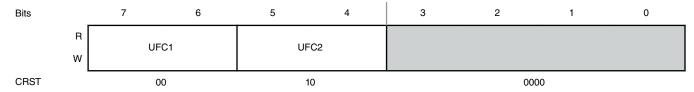

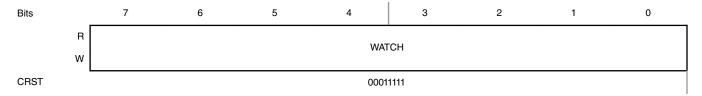

| I2C bus  | 7-bit address                                                         | Device      | Description     | Notes                                                                       |