# **AMD** AMD SP5100 Register Reference Guide

Technical Reference Manual Rev. 3.03

P/N: 44413\_sp5100\_rrg\_pub\_3.03

#### Trademarks

AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

PCI Express and PCIe are registered trademarks of PCI-SIG.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

# **Table of Contents**

| 1 | Introd   | uction                                                                                                                    | 6   |

|---|----------|---------------------------------------------------------------------------------------------------------------------------|-----|

|   | 1.1 Abc  | out this Manual                                                                                                           | 6   |

|   | 1.2 Nor  | menclature and Conventions                                                                                                | 6   |

|   | 1.2.1    | Recent Updates                                                                                                            | 6   |

|   | 1.2.2    | Numeric Representations                                                                                                   |     |

|   | 1.2.3    | Register Description                                                                                                      |     |

|   | 1.3 Bloc | ck Diagram                                                                                                                |     |

| 2 | Reaist   | ter Descriptions: PCI Devices                                                                                             | 9   |

|   | •        | TA Registers (Bus 0, Device 17, Function 0)                                                                               |     |

|   | 2.1.1    | PCI Configuration Registers                                                                                               |     |

|   | 2.1.2    | SATA I/O Register for IDE Mode                                                                                            |     |

|   | 2.1.2.1  |                                                                                                                           |     |

|   | 2.1.2.2  | BAR4 Registers                                                                                                            | 40  |

|   | 2.1.3    | SATA Memory Mapped Register for AHCI Mode                                                                                 | 41  |

|   | 2.1.3.1  | BAR5 Registers                                                                                                            | 41  |

|   | 2.1.3.2  | Generic Host Control                                                                                                      | 42  |

|   | 2.1.3.3  | Offset 00h: CAP – HBA Capabilities                                                                                        | 42  |

|   | 2.1.3.4  |                                                                                                                           |     |

|   | 2.1.3.5  |                                                                                                                           |     |

|   | 2.1.3.6  |                                                                                                                           |     |

|   | 2.1.3.7  |                                                                                                                           |     |

|   | 2.1.3.8  |                                                                                                                           |     |

|   | 2.1.3.9  |                                                                                                                           |     |

|   | 2.1.3.1  | <b>5</b> ( <b>1 1 /</b>                                                                                                   |     |

|   | 2.1.3.1  | - 0 1                                                                                                                     |     |

|   |          | CI USB 1.1 and EHCI USB 2.0 Controllers (Bus 0, Device 18/19/20)                                                          |     |

|   | 2.2.1    | OHCI Registers (Device 18/19/20)                                                                                          |     |

|   | 2.2.1.1  |                                                                                                                           |     |

|   | 2.2.1.2  |                                                                                                                           |     |

|   | 2.2.2    | USB3 (device-20, fun-5) OHCI PCI Configuration Registers                                                                  |     |

|   | 2.2.2.1  |                                                                                                                           |     |

|   | 2.2.3    | USB1, USB2 & USB3 (Device-18, 19 & Device-20 fun-5) OHCI Memory Mapped Registers                                          |     |

|   | 2.2.4    | USB1/ USB2 EHCI PCI Configuration Registers                                                                               |     |

|   | 2.2.5    | EHCI Memory Mapped Register                                                                                               |     |

|   | 2.2.5.1  | 1 5 6                                                                                                                     |     |

|   | 2.2.5.2  |                                                                                                                           |     |

|   | 2.2.5.3  | 5 5                                                                                                                       |     |

|   |          | Bus Module and ACPI Block (Device 20, Function 0)                                                                         |     |

|   | 2.3.1    | PCI Configuration Registers and Extended Registers                                                                        |     |

|   | 2.3.1.1  |                                                                                                                           |     |

|   | 2.3.1.2  |                                                                                                                           |     |

|   | 2.3.2    | SMBus Registers                                                                                                           |     |

|   | 2.3.3    | Legacy ISA and ACPI Controller                                                                                            |     |

|   | 2.3.3.1  |                                                                                                                           |     |

|   | 2.3.3    | 3.1.1       IO-Mapped Control Registers.         3.1.2       Client Management Registers (Accessed through C50h and C51h) |     |

|   |          | 3.1.2 Client Management Registers (Accessed through Coon and Com)                                                         |     |

|   | 2.0.0    |                                                                                                                           | 100 |

| 2.3.3.2                                                                      | Power Management (PM) Registers                                                                                                                                                                                                                     |                                                             |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 2.3.3.3                                                                      | ACPI Registers                                                                                                                                                                                                                                      | 216                                                         |

| 2.3.3.4                                                                      | Power Management (PM2) Block2 Registers                                                                                                                                                                                                             |                                                             |

| 2.3.4                                                                        | WatchDogTimer Registers                                                                                                                                                                                                                             | 226                                                         |

| 2.3.5                                                                        | ASF SMBus Host Interface Registers                                                                                                                                                                                                                  |                                                             |

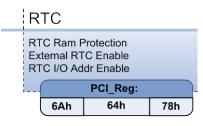

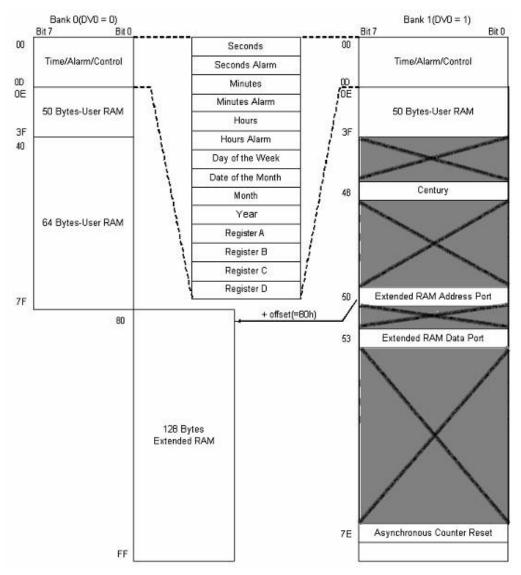

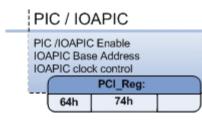

| 2.3.6                                                                        | RTC Extended Registers                                                                                                                                                                                                                              | 232                                                         |

| 2.4 IDE                                                                      | Controller (Device 20, Function 1)                                                                                                                                                                                                                  | 235                                                         |

| 2.4.1                                                                        | PCI Configuration Registers                                                                                                                                                                                                                         | 235                                                         |

| 2.4.2                                                                        | IDE I/O Registers                                                                                                                                                                                                                                   | 246                                                         |

| 2.5 HD                                                                       | Audio Controller Registers                                                                                                                                                                                                                          |                                                             |

| 2.5.1                                                                        | HD Audio Controller PCI Configuration Space Registers (Device 20 Function 2)                                                                                                                                                                        | 248                                                         |

| 2.5.2                                                                        | HD Audio Controller Memory Mapped Registers                                                                                                                                                                                                         | 255                                                         |

|                                                                              |                                                                                                                                                                                                                                                     |                                                             |

| 3 Regist                                                                     | er Descriptions: PCI Bridges                                                                                                                                                                                                                        | 272                                                         |

| •                                                                            | er Descriptions: PCI Bridges                                                                                                                                                                                                                        |                                                             |

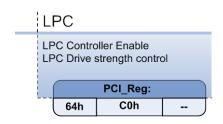

| 3.1 LPC                                                                      | SISA Bridge (Device 20, Function 3)                                                                                                                                                                                                                 | 272                                                         |

| 3.1 LPC<br>3.1.1                                                             | CISA Bridge (Device 20, Function 3)<br>Programming Interface                                                                                                                                                                                        |                                                             |

| 3.1 LPC<br>3.1.1<br>3.1.2                                                    | CISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers                                                                                                                                                         |                                                             |

| 3.1 LPC<br>3.1.1<br>3.1.2<br>3.1.3                                           | C ISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers<br>SPI ROM Controller Registers                                                                                                                        |                                                             |

| 3.1 LPC<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                  | C ISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers<br>SPI ROM Controller Registers<br>Features of the LPC Block                                                                                           | 272<br>272<br>272<br>272<br>290<br>293                      |

| 3.1 LPC<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2 Hos                       | C ISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers<br>SPI ROM Controller Registers<br>Features of the LPC Block<br>t PCI Bridge Registers (Device 20, Function 4)                                         |                                                             |

| 3.1 LPC<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2 Hos                       | C ISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers<br>SPI ROM Controller Registers<br>Features of the LPC Block                                                                                           |                                                             |

| 3.1 LPC<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2 Hos<br>3.3 Rea            | C ISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers<br>SPI ROM Controller Registers<br>Features of the LPC Block<br>t PCI Bridge Registers (Device 20, Function 4)                                         | 272<br>272<br>272<br>272<br>290<br>293<br>293<br>294<br>307 |

| 3.1 LPC<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2 Hos<br>3.3 Rea            | C ISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers<br>SPI ROM Controller Registers<br>Features of the LPC Block<br>at PCI Bridge Registers (Device 20, Function 4)<br>at Time Clock (RTC)                 | 272<br>272<br>272<br>290<br>293<br>294<br>307<br>314        |

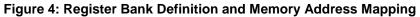

| 3.1 LPC<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2 Hos<br>3.3 Rea<br>3.4 IOX | C ISA Bridge (Device 20, Function 3)<br>Programming Interface<br>PCI Configuration Registers<br>SPI ROM Controller Registers<br>Features of the LPC Block<br>t PCI Bridge Registers (Device 20, Function 4)<br>I Time Clock (RTC)<br>APIC Registers | 272<br>272<br>272<br>290<br>293<br>294<br>307<br>314<br>314 |

# List of Tables

| Table 1-1: Register Description Table Notation—Example              | 6   |

|---------------------------------------------------------------------|-----|

| Table 2-1 Legacy Support Registers                                  |     |

| Table 2-2 Emulated Registers                                        |     |

| Table 2-3: IO Drive Strength Recommendations for Various Interfaces |     |

| Table 2-4: IO Drive Strength Recommendations for the IDE Interface  | 144 |

| Table 3-1 PCI-to-PCI Bridge Configuration Registers Summary         | 294 |

# 1 Introduction

### 1.1 About this Manual

This manual is a register reference guide for the AMD SP5100 (previously referred to by its code name "SB700S" in this guide).

AMD's SP5100 southbridge integrates the key I/O, communications, and audio features required in a stateof-the-art PC into a single device.

### **1.2 Nomenclature and Conventions**

#### 1.2.1 Recent Updates

Updates recent to each revision are highlighted in red.

#### 1.2.2 Numeric Representations

- Hexadecimal numbers are prefixed with "0x" or suffixed with "h," whenever there is a possibility of confusion. Other numbers are decimal.

- Registers (or fields) of an identical function are sometimes indicated by a single expression in which the part of the signal name that changes is enclosed in square brackets. For example, registers HOST\_DATA0 through to HOST\_DATA7 is represented by the single expression HOST\_DATA[7:0].

#### 1.2.3 Register Description

All registers in this document are described with the format of the sample table below. All offsets are in hexadecimal notation, while programmed bits are in either binomial or hexadecimal notation.

| Table 1-1: Register D | Description Table I | Notation—Example |

|-----------------------|---------------------|------------------|

|-----------------------|---------------------|------------------|

| Latency Timer – RW – 8 bits – [Offset: 0Dh] |      |         |                                                                                                                                                                                                                                                                              |  |  |

|---------------------------------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Field Name                                  | Bits | Default | Description                                                                                                                                                                                                                                                                  |  |  |

| Latency Timer (R/W)                         | 7:0  | 00h     | This bit field is used to specify the time in number of PCI clocks, the SATA controller as a master is still allowed to control the PCI bus after its GRANT_L is deasserted. The lower three bits [0A:08] are hardwired to 0 h, resulting in a time granularity of 8 clocks. |  |  |

| Latency Timer. Reset Value: 00h             |      |         |                                                                                                                                                                                                                                                                              |  |  |

| Register Information                                                                                                                                                                                                                                                                                       | Value/Content in the Example    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|

| Register name                                                                                                                                                                                                                                                                                              | Latency Timer                   |  |  |  |

| Read / Write capability<br>R = Readable<br>W = Writable<br>RW = Readable and Writable                                                                                                                                                                                                                      | RW                              |  |  |  |

| Register size                                                                                                                                                                                                                                                                                              | 8 bits                          |  |  |  |

| Register address(es)*                                                                                                                                                                                                                                                                                      | Offset: 0Dh                     |  |  |  |

| Field name                                                                                                                                                                                                                                                                                                 | Latency Timer (R/W)             |  |  |  |

| Field position/size                                                                                                                                                                                                                                                                                        | 7:0                             |  |  |  |

| Field default value                                                                                                                                                                                                                                                                                        | 00h                             |  |  |  |

| Field description                                                                                                                                                                                                                                                                                          | "This bit 8 clocks."            |  |  |  |

| Field mirror information                                                                                                                                                                                                                                                                                   |                                 |  |  |  |

| Brief register description                                                                                                                                                                                                                                                                                 | Latency Timer. Reset Value: 00h |  |  |  |

| <ul> <li>* Note: There maybe more than one address; the convention used is as follows:</li> <li>[aperName:offset] - single mapping, to one aperture/decode and one offset</li> <li>[aperName1, aperName2,, aperNameN:offset] - multiple mappings to different apertures/decodes but same offset</li> </ul> |                                 |  |  |  |

[aperName:startOffset-endOffset] - mapped to an offset range in the same aperture/decode

**Warning:** Do not attempt to modify values of registers or bit fields marked "Reserved." Doing so may cause the system to behave in unexpected manners.

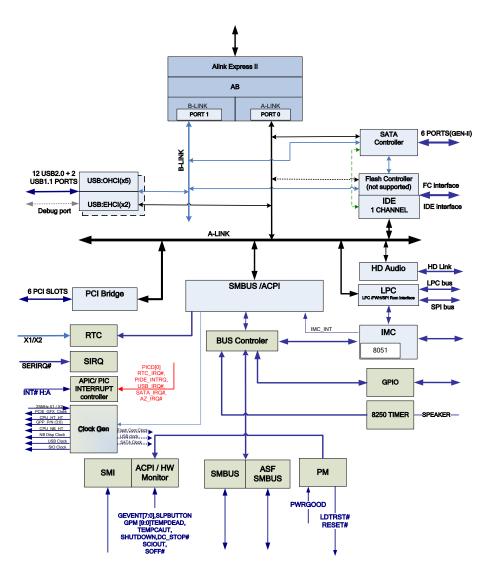

# 1.3 Block Diagram

This section contains a diagram for the SP5100. *Figure 1* below shows the SP5100 internal PCI devices and the major function blocks.

Figure 1 SP5100 PCI Internal Devices and Major Function Blocks

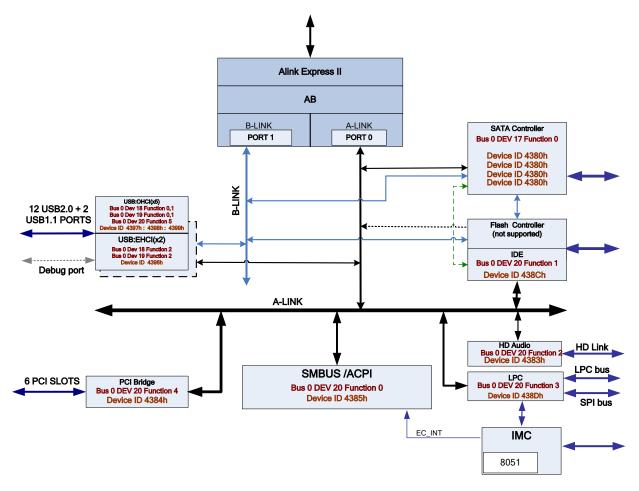

# 2 Register Descriptions: PCI Devices

Note: The SP5100 internal PCI devices are listed in *Figure 2* below. The sub-sections that follow provide descriptions of the PCI configuration space, the I/O space, and the memory space registers for each device. PCI configuration space registers are only accessible with configuration read or configuration write cycles and with the target device selected by settling its corresponding IDSEL bit in the configuration cycle address field.

Figure 2: SP5100 PCI Internal Devices

# 2.1 SATA Registers (Bus 0, Device 17, Function 0)

SATA registers are composed of PCI Config, Memory mapped I/O and I/O space registers. These registers are cleared by the PCIRST# signal; therefore, they will be cleared on a warm boot.

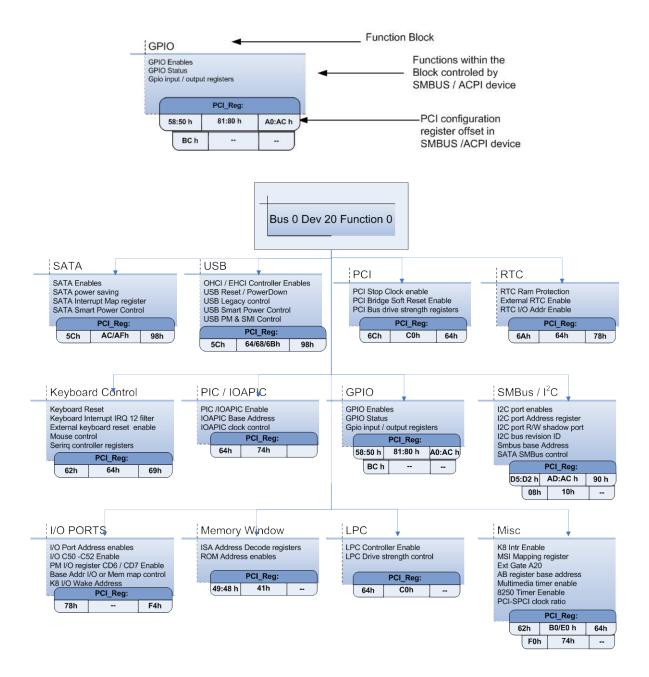

Note: Some SATA functions are controlled by, and associated with, certain PCI configuration registers in the SMBus/ACPI device. For more information refer to section 2.4: SMBus Module and ACPI Block (Device 20, Function 0). The diagram below lists these SATA functions and the associated registers.

| SATA                                                                                         |        |     |  |  |

|----------------------------------------------------------------------------------------------|--------|-----|--|--|

| SATA Enables<br>SATA power saving<br>SATA Interrupt Map register<br>SATA Smart Power Control |        |     |  |  |

| PCI_Reg:                                                                                     |        |     |  |  |

| 5Ch                                                                                          | AC/AFh | 98h |  |  |

|                                                                                              |        |     |  |  |

#### 2.1.1 PCI Configuration Registers

These registers are accessible only when the SATA controller detects a Configuration Read or Write operation, with its IDSEL asserted, on the 32-bit PCI bus.

| Register Name                        | Offset Address |

|--------------------------------------|----------------|

| Vendor ID                            | 00h            |

| Device ID                            | 02h            |

| Command                              | 04h            |

| Status                               | 06h            |

| Revision ID/Class Code               | 08h            |

| Cache Link Size                      | 0Ch            |

| Master Latency Timer                 | 0Dh            |

| Header Type                          | 0Eh            |

| BIST Mode Type                       | 0Fh            |

| Base Address 0                       | 10h            |

| Base Address 1                       | 14h            |

| Base Address 2                       | 18h            |

| Base Address 3                       | 1Ch            |

| Bus Master Interface Base Address    | 20h            |

| AHCI Base Address                    | 24h            |

| Subsystem ID and Subsystem Vendor ID | 2Ch            |

| Capabilities Pointer                 | 34h            |

| Interrupt Line                       | 3Ch            |

| Interrupt Pin                        | 3Dh            |

| Min_gnt                              | 3Eh            |

| Max_latency                          | 3Fh            |

| Misc control                         | 40h            |

| Watch Dog Control And Status         | 44h            |

| Watch Dog Counter                    | 46h            |

| Blink Control                        | 48h            |

| MSI Control                          | 50h            |

| MSI Address                          | 54h            |

| MSI Upper Address                    | 58h            |

| MSI Data                             | 5Ch            |

| Power Management Capability ID       | 60h            |

| Power Management Capability          | 62h            |

| Power Management Control And Status  | 64h            |

| Serial ATA Capability Register 0     | 70h            |

| Serial ATA Capability Register 1     | 74h            |

| Register Name                      | Offset Address |

|------------------------------------|----------------|

| IDP Index                          | 78h            |

| IDP Data                           | 7Ch            |

| PHY Test In                        | 80h            |

| PHY Test Out                       | 82h            |

| PHY Mode                           | 84h            |

| PHY Global Control                 | 86h            |

| PHY Port0 Control                  | 88h            |

| PHY Port1 Control                  | 8Ch            |

| PHY Port2 Control                  | 90h            |

| PHY Port3 Control                  | 94h            |

| PHY Port4 Control                  | 98h            |

| PHY Port5 Control                  | 9Ch            |

| PHY Port0 GENII Control            | A0h            |

| PHY Port1 GENII Control            | A2h            |

| PHY Port2 GENII Control            | A4h            |

| PHY Port3 GENII Control            | A6h            |

| PHY Port4 GENII Control            | A8h            |

| PHY Port5 GENII Control            | AAh            |

| Port0 BIST Error Count             | ACh            |

| Port0 BIST Control/Status          | B0h            |

| Reserved                           | B2h            |

| Port1 BIST Error Count             | B4h            |

| Port1BIST Control/Status           | B8h            |

| Reserved                           | BAh            |

| Port2 BIST Error Count             | BCh            |

| Port2 BIST Control/Status          | C0h            |

| Reserved                           | C2h            |

| Port3 BIST Error Count             | C4h            |

| Port3 BIST Control/Status          | C8h            |

| Reserved                           | CAh            |

| Port4 BIST Error Count             | CCh            |

| Port4 BIST Control/Status          | D0h            |

| Reserved                           | D2h            |

| Port5 BIST Error Count             | D4h            |

| Port5 BIST Control/Status          | D8h            |

| Reserved                           | DAh            |

| BIST pattern Count                 | DCh            |

| PCI Target Control TimeOut Counter | E0h            |

| T-Mode BIST Transit Pattern DW1    | E4h            |

| T-Mode BIST Transit Pattern DW2    | E8h            |

| BIST Transmit Pattern Definition   | ECh            |

| Reserved                           | EE-EFh         |

| 20-BIT BIST Transmit Pattern       | F0             |

| Reserved                           | F3h-FFh        |

| Vendor ID - R - 16 bits - [PCI_Reg:00h] |      |         |                                                                                                                                   |  |

|-----------------------------------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Field Name                              | Bits | Default | Description                                                                                                                       |  |

| Vendor ID                               | 15:0 | 1002h   | This register holds a unique 16-bit value assigned to a vendor.<br>And combined with the device ID, it identifies any PCI device. |  |

| Device ID - R - 16 bits - [PCI_Reg:02h] |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----------------------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Field Name                              | Bits | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Device ID                               | 15:0 | 4390h   | This register holds a unique 16-bit value assigned to a device.<br>When used with the combination of base class and sub-class,<br>the correct functionality of the SATA mode will be enabled by<br>hardware and software.<br>Note: To make Device ID 4394h, software will program an<br>unlock bit (PCI_CFG 0x40[24]) to 1'b1. Once programmed,<br>Device ID becomes read-only. This bit supersedes the<br>bonding option and the writing of the Device ID field. That is to<br>say, in order to make Device ID 4390h or 4391h, PCI_CFG<br>0x40[24] must be programmed to 1'b0 (default). |  |  |

Note: The SP5100 SATA controller supports multiple Device IDs to accommodate different SATA configurations. The following configurations are supported through BIOS programming:

- IDE (IDE emulation mode) ٠

- AHCI mode ٠

- RAID 0 / RAID 1 and RAID 10

The SP5100 Device IDs and sub-class codes are assigned as follows:

| Mode                                                         | Device ID            | Sub-Class Code | PCI_CFG 0x40[24] |  |  |  |

|--------------------------------------------------------------|----------------------|----------------|------------------|--|--|--|

| IDE                                                          | 4390h                | 01h            | 0                |  |  |  |

| AHCI <sup>1</sup>                                            | 4391h                | 06h            | 0                |  |  |  |

| RAID 0, 1, 10 <sup>3</sup>                                   | 439 <mark>2</mark> h | 04h            | 0                |  |  |  |

| AHCI <sup>2</sup>                                            | 4394h                | 06h            | 1                |  |  |  |

| Note 1: For Microsoft <sup>®</sup> inbox AHCI driver support |                      |                |                  |  |  |  |

Note 2: For AMD inbox AHCI driver support (Recommended) Note 3: RAID driver support (from third party. AMD does not provide RAID driver)

|                                       | Command - RW - 16 bits - [PCI_Reg:04h] |         |                                                                                                                                                               |  |  |

|---------------------------------------|----------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Field Name                            | Bits                                   | Default | Description                                                                                                                                                   |  |  |

| I/O Access Enable                     | 0                                      | Ob      | This bit controls access to the I/O space registers. When this bit is 1, it enables SATA controller to response to PCI IO space access.                       |  |  |

| Memory Access Enable                  | 1                                      | Ob      | This bit controls access to the memory space registers. When<br>this bit is 1, it enables SATA controller to response to PCI<br>memory space access           |  |  |

| Bus Master Enable                     | 2                                      | 0b      | Bus master function enable.<br>1: Enable<br>0: Disable.                                                                                                       |  |  |

| Special Cycle<br>Recognition Enable   | 3                                      | 0b      | Read Only.<br>Hard-wired to '0' indicates that there is no special support.                                                                                   |  |  |

| Memory Write and<br>Invalidate Enable | 4                                      | 0b      | Read Only.<br>Hard-wired to '0' indicates that memory write and invalidate<br>command is not supported.                                                       |  |  |

| VGA Palette Snoop<br>Enable           | 5                                      | 0b      | Read Only.<br>Hard-wired to '0' indicates the SATA host controller does not<br>need to snoop VGA palette cycles.                                              |  |  |

| PERR- Detection Enable                | 6                                      | Ob      | If set to 1, the IDE host controller asserts PERR- when it is the agent receiving data AND it detects a parity error. PERR- is not asserted if this bit is 0. |  |  |

| Wait Cycle Enable                     | 7                                      | Ob      | Read Only.<br>Hard-wired to '0' indicates the SATA controller does not need<br>to insert a wait state between the address and data on the AD<br>lines.        |  |  |

| Command - RW - 16 bits - [PCI_Reg:04h] |               |           |                                                                                                                                                        |  |

|----------------------------------------|---------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field Name                             | Bits          | Default   | Description                                                                                                                                            |  |

| SERR- Enable                           | 8             | Ob        | If set to 1 and bit 6 is set, the SATA controller asserts SERR-<br>when it detects an address parity error. SERR- is not asserted<br>if this bit is 0. |  |

| Fast Back-to-Back<br>Enable            | 9             | Ob        | Read Only.<br>Hard-wired to '0' indicates that fast back to back to the same<br>agent are allowed only.                                                |  |

| Interrupt Disable                      | 10            | 0b        | (Complies to PCI 2.3 spec.)                                                                                                                            |  |

| Reserved                               | 15:11         | 00h       | Reserved.                                                                                                                                              |  |

| Reset Condition: PCI Rese              | t, or Power I | Managemen | t State transition from D3 to D0.                                                                                                                      |  |

|                              | St           | atus - RW | - 16 bits - [PCI_Reg:06h]                                                           |  |

|------------------------------|--------------|-----------|-------------------------------------------------------------------------------------|--|

| Field Name                   | Bits         | Default   | Description                                                                         |  |

| Reserved                     | 2:0          | 0h        | Reserved.                                                                           |  |

| Interrupt Status             | 3            | 0b        | Interrupt status bit. It complies with the PCI 2.3 specification.                   |  |

| Capabilities List            | 4            | 1b        | Read Only.                                                                          |  |

|                              |              |           | Default to 1 to indicate that the Capabilities Pointer is located                   |  |

|                              |              |           | at 34h.                                                                             |  |

| 66MHz Support                | 5            | 1b        | 66MHz capable. This feature is supported in the SATA                                |  |

| _                            |              |           | controller.                                                                         |  |

| Reserved                     | 6            | 0b        | Reserved.                                                                           |  |

| Fast Back-to-Back            | 7            | 0b        | Read Only.                                                                          |  |

| Capable                      |              |           | Hard-wired to '0' indicates that Fast Back-to-Back incapable.                       |  |

| Data Parity Error            | 8            | 0b        | Data Parity reported. Set to 1 if the SATA controller detects                       |  |

|                              |              |           | PERR- asserted while acting as PCI master (whether PERR-                            |  |

|                              |              |           | was driven by SATA controller or not.) Write '1' clears this bit.                   |  |

| DEVSEL- Timing               | 10:9         | 01b       | Read only.                                                                          |  |

|                              |              |           | These bits indicate DEVSEL- timing when performing a                                |  |

|                              |              |           | positive decode.                                                                    |  |

|                              |              |           | Since DEVSEL- is asserted to meet the medium timing, these bits are encoded as 01b. |  |

| Signaled Target Abort        | 11           | 0b        | Signaled Target Abort. This bit is set to 1, when the SATA                          |  |

| Signaled Target Abort        | 11           | 00        | controller signals Target Abort. Write '1' clears this bit.                         |  |

| Received Target Abort        | 12           | 0b        | Received Target Abort. This bit is set to 1 when the SATA                           |  |

| Received Target Abolt        | 12           | 00        | controller generated PCI cycle (SATA controller is the PCI                          |  |

|                              |              |           | master) is aborted by a PCI target. Cleared by writing a 1 to it.                   |  |

| Received Master Abort        | 13           | 0b        | Received Master Abort Status. Set to 1 when the SATA                                |  |

| Status                       | 10           | 05        | controller acting as a PCI master, aborts a PCI bus memory                          |  |

| Olaldo                       |              |           | cycle. Cleared by writing a 1 to this bit. Write '1' clears this bit.               |  |

|                              |              |           |                                                                                     |  |

| SERR- Status                 | 14           | 0b        | SERR- status. This bit is set to 1 when the SATA controller                         |  |

|                              |              |           | detects a PCI address parity error. Write '1' clears this bit.                      |  |

| Detected Parity Error        | 15           | 0b        | Detected Parity Error. This bit is set to 1 when the SATA                           |  |

| _                            |              |           | controller detects a parity error. Write '1' clears this bit.                       |  |

| Bit [15:8] are read/write. H |              |           |                                                                                     |  |

| Reset Condition: PCI Rese    | et, or Power | Managemen | t State transition from D3 to D0.                                                   |  |

|                              |              |           |                                                                                     |  |

| Revision ID/Class Code- R - 32 bits - [PCI_Reg:08h] |     |     |                                                                                  |  |

|-----------------------------------------------------|-----|-----|----------------------------------------------------------------------------------|--|

| Field Name Bits Default Description                 |     |     |                                                                                  |  |

| Revision ID                                         | 7:0 | 00h | These bits are default to 00h to indicate the revision level of the chip design. |  |

|                                                        | Revision I                                                      | D/Class C                  | ode- R - 32 bits - [PCI_Reg:08h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------|-----------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field Name                                             | Bits                                                            | Default                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Operating Mode<br>Selection                            | 15:8                                                            | 8Fh                        | RW<br>Programmable I/F.<br>Bit [15]: Master IDE Device. Always 1.<br>Bits [14:12]: Reserved. Always read as 0's.<br>Bit [11]: Programmable indicator for Secondary. Always 1 to<br>indicate that both modes are supported.<br>Bit [10]: Operating Mode for Secondary.<br>1: Native PCI-mode.<br>0: Compatibility Mode<br>Bit [9]: Programmable indicator for Primary. Always 1 to<br>indicate that both modes are supported.<br>Bit [8]: Operating Mode for Primary.<br>1: Native PCI-mode.<br>0: Compatibility mode<br>0: Compatibility mode<br>See *Note 1 |

| Sub-Class Code                                         | 23:16                                                           | 01h                        | Sub-Class Code. 01h to indicate an IDE Controller. See *Note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Class Code                                             | 31:24                                                           | 01h                        | Class Code. These 8 bits are read only and wired to 01h to indicate a Mass-Storage Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *Note 2: This field is on<br>Sub-Class Code P<br>01 8F | G 40h[0] ==0.<br>ly write-able whe<br>Program Interfac<br>- IDE | en PCI_Reg<br>e: Controlle | h[0] is 1. In IDE mode (sub class code ==01) bits [11:8] are<br>:40h[0] is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 06 01<br>04 00                                         | ) RA                                                            | •••                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Reset Condition: PCI R                                 | eset.                                                           |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cache Line Size - RW - 8 bits - [PCI_Reg:0Ch]                                          |               |            |                                 |  |  |

|----------------------------------------------------------------------------------------|---------------|------------|---------------------------------|--|--|

| Field Name Bits Default Description                                                    |               |            |                                 |  |  |

| Reserved                                                                               | 3:0           | 0h         | Reserved                        |  |  |

| Cache Line Size Register 7:4 0h If the value is 1, cache line size is 16 DW (64 byte). |               |            |                                 |  |  |

| Reset Condition: PCI Rese                                                              | t, or Power I | Management | State transition from D3 to D0. |  |  |

| Master Latency Timer - RW - 8 bits - [PCI_Reg:0Dh] |                                                                                 |     |                                                                                                                                                   |  |  |

|----------------------------------------------------|---------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Field Name Bits Default Description                |                                                                                 |     |                                                                                                                                                   |  |  |

| Reserved                                           | 2:0                                                                             | 0h  | Reserved                                                                                                                                          |  |  |

| Master Latency Timer                               | 7:3                                                                             | 00h | Master Latency Timer. This number in units of PCICLKs represents the guaranteed time slice allowed to IDE host controller for burst transactions. |  |  |

| Reset Condition: PCI Res                           | Reset Condition: PCI Reset, or Power Management State transition from D3 to D0. |     |                                                                                                                                                   |  |  |

| Header Type - R - 8 bits - [PCI_Reg:0Eh] |      |         |                                                                                                                                                                                                                      |  |

|------------------------------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field Name                               | Bits | Default | Description                                                                                                                                                                                                          |  |

| Header Type                              | 7:0  | 00h     | Header Type. Since the IDE host controller is a single-function device, this register contains a value of 00h. Bit [7] is writable when PCI configuration register 40h[0] is set. This applies to ASIC Revision A12. |  |

| BIST Mode Type - RW - 8 bits - [PCI_Reg:0Fh] |      |         |                                                                                                      |  |

|----------------------------------------------|------|---------|------------------------------------------------------------------------------------------------------|--|

| Field Name                                   | Bits | Default | Description                                                                                          |  |

| Completion Code                              | 3:0  | 0h      | Read Only.<br>Indicates the completion code status of BIST. A non-zero<br>value indicates a failure. |  |

| BIST Mode Type - RW - 8 bits - [PCI_Reg:0Fh]                                    |            |              |                                                           |  |  |

|---------------------------------------------------------------------------------|------------|--------------|-----------------------------------------------------------|--|--|

| Field Name Bits Default Description                                             |            |              |                                                           |  |  |

| Reserved                                                                        | 5:4        | 0h           | Reserved                                                  |  |  |

| Start BIST                                                                      | 6          | 0b           | Since bit [7] is 0, programming this bit takes no effect. |  |  |

| BIST Capable                                                                    | 7          | 0            | Read Only.                                                |  |  |

| Hard-wired to '0' Indicates no HBA related BIST function                        |            |              |                                                           |  |  |

| Reset Condition: PCI Reset, or Power Management State transition from D3 to D0. |            |              |                                                           |  |  |

| Note: This does not indicat                                                     | e SATA BIS | T capability |                                                           |  |  |

|                                 | Base Address 0 - RW - 32 bits - [PCI_Reg:10h] |                |                                                                                                                                           |  |

|---------------------------------|-----------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field Name                      | Bits                                          | Default        | Description                                                                                                                               |  |

| Resource Type Indicator         | 0                                             | 1b             | RTE (Resource Type Indicator). This bit is wired to 1 to indicate that the base address field in this register maps to I/O space.         |  |

| Reserved                        | 2:1                                           | 0h             | Reserved.                                                                                                                                 |  |

| Primary IDE CS0 Base<br>Address | 31:3                                          | 0000_<br>0000h | Base Address for Primary IDE Bus CS0. This register is<br>used for native mode only. Base Address 0 is not used<br>in compatibility mode. |  |

| Reset Condition: PCI Rese       | t, or Power I                                 | Managemen      | t State transition from D3 to D0.                                                                                                         |  |

| Base Address 1 - RW - 32 bits - [PCI_Reg:14h] |               |            |                                                                   |  |

|-----------------------------------------------|---------------|------------|-------------------------------------------------------------------|--|

| Field Name                                    | Bits          | Default    | Description                                                       |  |

| Resource Type Indicator                       | 0             | 1b         | RTE (Resource Type Indicator). This bit is wired to 1 to          |  |

|                                               |               |            | indicate that the base address field in this register maps to I/O |  |

|                                               |               |            | space.                                                            |  |

| Reserved                                      | 1             | 0b         | Reserved.                                                         |  |

| Primary IDE CS1 Base                          | 31:2          | 0000_      | Base Address for Primary IDE Bus CS1. This register is used       |  |

| Address                                       |               | 0000h      | for native mode only. Base Address 1 is not used in               |  |

|                                               |               |            | compatibility mode.                                               |  |

| Reset Condition: PCI Rese                     | t, or Power I | Management | t State transition from D3 to D0.                                 |  |

| Base Address 2 - RW - 32 bits - [PCI_Reg:18h] |                |           |                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------------------|----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Field Name                                    | Bits           | Defaul    | Description                                                                                                                                                                                                                                                                                                       |  |  |

| Resource Type Indicator                       | 0              | 1b        | RTE (Resource Type Indicator). This bit is wired to 1 to<br>indicate that the base address field in this register maps to I/O<br>space for IDE mode.<br>When flash controller is enabled (PM_Reg_59, bit 1), this bit is<br>'0' to indicate that the base address field in this register maps<br>to memory space. |  |  |

| Reserved                                      | 2:1            | 0h        | Reserved.                                                                                                                                                                                                                                                                                                         |  |  |

| Secondary IDE CS0                             | 31:3           | 0000_     | Under IDE mode, this serves as the base Address for                                                                                                                                                                                                                                                               |  |  |

| Base Address<br>or                            | (See Note)     | 0000h     | Secondary IDE Bus CS0. This register is used for native mode<br>only. Base Address 2 is not used in compatibility mode.<br>When flash controller is enabled (PM_Reg_59, bit 1), this                                                                                                                              |  |  |

| Flash Controller base address                 |                |           | register serves as the base address for the flash controller<br>Note: When this register serves as the base address for the<br>flash controller, bits [16:3] are read-only.                                                                                                                                       |  |  |

| Reset Condition: PCI Rese                     | t, or Power Ma | inagement | t State transition from D3 to D0.                                                                                                                                                                                                                                                                                 |  |  |

| Base Address 3 - RW - 32 bits - [PCI_Reg:1Ch] |      |         |                                                                                                                                   |

|-----------------------------------------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| Field Name                                    | Bits | Default | Description                                                                                                                       |

| Resource Type Indicator                       | 0    | 1b      | RTE (Resource Type Indicator). This bit is wired to 1 to indicate that the base address field in this register maps to I/O space. |

| Reserved                                      | 1    | 0b      | Reserved.                                                                                                                         |

| Base Address 3 - RW - 32 bits - [PCI_Reg:1Ch]                                   |      |                |                                                                                                                                       |  |

|---------------------------------------------------------------------------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Field Name                                                                      | Bits | Default        | Description                                                                                                                           |  |

| Secondary IDE CS1<br>Base Address                                               | 31:2 | 0000_<br>0000h | Base Address for Secondary IDE Bus CS1. This register is used for native mode only. Base Address 3 is not used in compatibility mode. |  |

| Reset Condition: PCI Reset, or Power Management State transition from D3 to D0. |      |                |                                                                                                                                       |  |

| Bus Master Interface Base Address - RW - 32 bits - [PCI_Reg:20h] |               |            |                                                                                                                                         |  |

|------------------------------------------------------------------|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Field Name                                                       | Bits          | Default    | Description                                                                                                                             |  |

| Resource Type Indicator                                          | 0             | 1b         | RTE (Resource Type Indicator). This bit is wired to 1 to<br>indicate that the base address field in this register maps to I/O<br>space. |  |

| Reserved                                                         | 3:1           | 0h         | Reserved.                                                                                                                               |  |

| Bus Master Interface                                             | 31:4          | 000_       | Base Address for Bus Master interface registers and                                                                                     |  |

| Register Base Address                                            |               | 0000h      | correspond to AD[15:4].                                                                                                                 |  |

| Reset Condition: PCI Rese                                        | t, or Power N | Management | t State transition from D3 to D0.                                                                                                       |  |

| AHCI Base Address - RW - 32 bits - [PCI_Reg:24h] |                                                                                 |         |                                                          |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------|---------|----------------------------------------------------------|--|--|

| Field Name                                       | Bits                                                                            | Default | Description                                              |  |  |

| Resource Type Indicator                          | 0                                                                               | 0b      | RTE (Resource Type Indicator). This bit is wired to 0 to |  |  |

|                                                  |                                                                                 |         | indicate a request for register memory space.            |  |  |

| Reserved                                         | 9:1                                                                             | 000h    | Reserved.                                                |  |  |

| AHCI Base Address                                | 31:10                                                                           | 00_0000 | Base address of register memory space. This represents a |  |  |

|                                                  |                                                                                 | h       | memory space for support of 4 ports.                     |  |  |

| Reset Condition: PCI Rese                        | Reset Condition: PCI Reset, or Power Management State transition from D3 to D0. |         |                                                          |  |  |

| Subsystem ID and Subsystem Vendor ID - RW - 32 bits - [PCI_Reg:2Ch] |       |         |                                                            |  |

|---------------------------------------------------------------------|-------|---------|------------------------------------------------------------|--|

| Field Name                                                          | Bits  | Default | Description                                                |  |

| Subsystem Vendor ID                                                 | 15:0  | 0000h   | Subsystem Vendor ID. Can only be written once by software. |  |

| Subsystem ID                                                        | 31:16 | 0000h   | Subsystem ID. Can only be written once by software.        |  |

| Write once and read only.                                           |       |         |                                                            |  |

| Reset Condition: PCI Rese                                           | t.    |         |                                                            |  |

| Capabilities Pointer - R - 8 bits - [PCI_Reg:34h] |     |     |                                        |  |

|---------------------------------------------------|-----|-----|----------------------------------------|--|

| Field Name Bits Default Description               |     |     |                                        |  |

| Capabilities Pointer                              | 7:0 | 60h | The first pointer of Capability block. |  |

| Interrupt Line - RW - 8 bits - [PCI_Reg:3Ch]                                    |      |         |                                                                                                                                                             |  |

|---------------------------------------------------------------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field Name                                                                      | Bits | Default | Description                                                                                                                                                 |  |

| Interrupt Line                                                                  | 7:0  | 00h     | Identifies which input on the interrupt controller the function's<br>PCI interrupt request pin (as specified in its Interrupt Pin<br>register) is routed to |  |