# 11 Ways to Protect Your Power Path

Design Tips and Tradeoffs Using TI's Power Switches

**TEXAS INSTRUMENTS**

# **Table of Contents**

| Introduction: Basics of Power Switches 3 | Chapter 6: Overvoltage Protection               |

|------------------------------------------|-------------------------------------------------|

| Chapter 1: Inrush Current Control        | Chapter 7: Thermal Shutdown                     |

| Chapter 2: Adjustable Current Limit      | Chapter 8: Current Monitoring                   |

| Chapter 3: Short-Circuit Protection      | Chapter 9: Power-Good Signal                    |

| Chapter 4: Reverse Current Blocking 28   | Chapter 10: Safely Driving an Inductive Load 52 |

| Chapter 5: Reverse Polarity Protection   | Chapter 11: Automotive Load Dump 58             |

#### **Application Report**

SLVA927A–November 2017–Revised April 2019 Authors: Arthur Huang, Emily Roth

#### Abstract

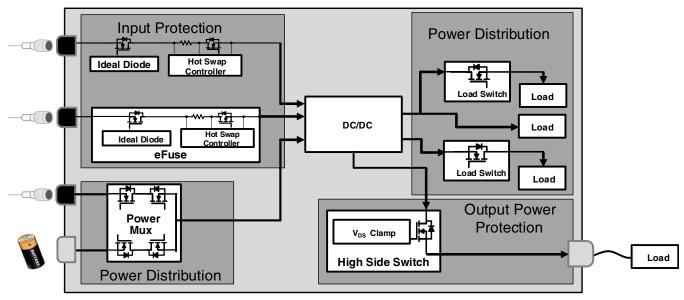

A *Power Switch* provides an electrical connection from a voltage source or ground to a load. It saves power across multiple voltage rails and protects subsystems from damage. It also provides enhanced component protection, inrush current protection, and minimizes printed-circuit board (PCB) size.

There are several power switch topologies with different functions that address different applications. *Load Switches* establish the power switch foundation by providing safe and reliable distribution of power. Applications typically using load switches include power distribution, power sequencing, inrush current control, and reduced current leakage. Integrated *Power MUX* devices are similar to load switches but allow for multiple input sources. This set of electronic switches is used to select and transition between two or more input power paths to a single output while also providing input power protection.

*eFuses* and *Hot Swap* controllers provide additional input power path protection functions such as current sense monitoring, current limiting, undervoltage and overvoltage protection, and thermal shutdown. This makes these devices ideal for hot-plug and transient events that would otherwise damage system components. These benefits help reduce system maintenance costs and maximize equipment uptime.

Ideal diode, ORing controllers provide protection against reverse-polarity conditions by monitoring an external FET, significantly reducing power loss, and blocking reverse current. Whenever a transient event occurs, the controller monitors and adjusts the external FET to prevent damage to upstream components.

Smart high-side switches are for off-board load protection. They provide additional diagnostic telemetry that monitors the output load current and detects shortcircuit and open-load events. Smart high-side switches have adjustable current limits, allowing more reliable integration into applications with either large inrush current startup profiles or low peak currents. Adding a smart high-side switch to a design leads to a smarter and more robust solution for driving capacitive, inductive, and LED loads.

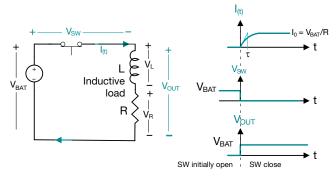

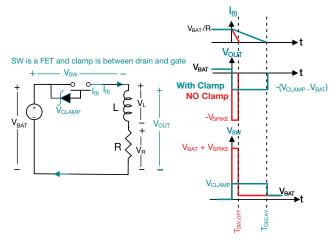

*Low-side switches* connect the load to ground instead of providing a connection between a power supply and the load. By including an integrated flyback diode, *lowside switches* help eliminate inductive load transients by dissipating current in a circular loop. This allows them to drive inductive loads such as solenoids, relays, and motors.

This application report highlights the different topologies within the power switch portfolio, and provides suggestions in choosing the correct solution for a faster design time.

|                              | POWER DIS        | STRIBUTION                          | INPUT POWER PROTECTION  |                            | OUTPUT POWER<br>PROTECTION         |                            |                    |

|------------------------------|------------------|-------------------------------------|-------------------------|----------------------------|------------------------------------|----------------------------|--------------------|

|                              | Load Switch      | Power MUX<br>(2 input, 1<br>output) | eFuse<br>(Internal FET) | Hot Swap<br>(External FET) | Ideal Diode<br>ORing<br>Controller | Smart High-<br>Side Switch | Low-Side<br>Switch |

| Voltage Range                | 0 V to 18 V      | 2.8 V to 22 V                       | 2.7 V to 60 V           | ±80 V                      | ±75 V                              | 6 V to 40 V                | 0 V to 100 V       |

| Max Operating Current        | 15 A             | 4.5 A                               | 15 A                    | N/A                        | N/A                                | 12 A                       | 1 A                |

| Functions                    |                  |                                     |                         |                            |                                    |                            |                    |

| Inrush Current Control       | 1                | 1                                   | √                       | 1                          |                                    | 1                          |                    |

| Adjustable Current Limit     |                  | 1                                   | √                       | 1                          |                                    | 1                          |                    |

| Reverse Current Blocking     | 1                | 1                                   | √                       | 1                          | √                                  |                            |                    |

| Current Sense Monitoring     |                  |                                     | √                       | 1                          |                                    | 1                          |                    |

| Short-Circuit Protection     | ✓ <sup>(1)</sup> | 1                                   | 1                       | √                          |                                    | √                          |                    |

| Overvoltage Protection       |                  | 1                                   | 1                       | √                          |                                    |                            |                    |

| Reverse Polarity Protection  |                  | 1                                   | 1                       | √                          | 1                                  | √                          |                    |

| Power Good Signal            | 1                |                                     | 1                       | 1                          |                                    |                            |                    |

| Inductive Load Compatibility |                  |                                     |                         |                            |                                    | √                          | 1                  |

| Load-Dump Compatibility      |                  |                                     | 1                       | 1                          | 1                                  | √                          | 1                  |

| Thermal Shutdown             | 1                | 1                                   | √                       | 1                          |                                    | √                          |                    |

<sup>(1)</sup> Self protected load switch

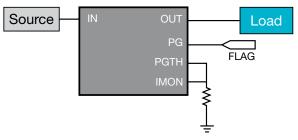

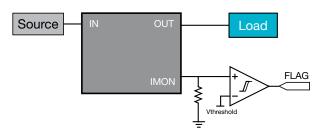

### 1 Load Switches

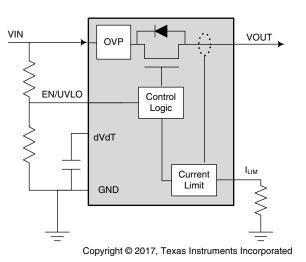

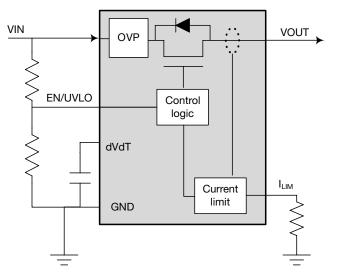

Figure 2. Load Switch Block Diagram

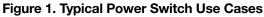

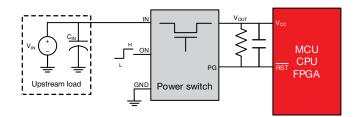

Integrated load switches are electronic switches that turn power rails on and off. When the internal FET turns on, current flows from the input to output and passes power to the downstream circuitry. When the device is enabled, the rise time of the output voltage ( $V_{OUT}$ ) can be controlled by adjusting the capacitance on an external pin (CT pin). When the device is disabled, the fall time of  $V_{OUT}$  is controlled through the quick output discharge (QOD). QOD pulls the output to ground whenever the device is turned off, preventing the output from *floating* or entering an undetermined state.

Some common functions of load switches include power savings, power sequencing, and inrush current control. Power savings is important in applications looking to minimize current dissipation and maximize power efficiency. By disconnecting the supply from a load or subsystem, the switch minimizes power drawn from inactive loads. Power sequencing is important in applications where individual voltage rails need to be turned on and off in a specific order. By configuring the CT and QOD pins, the ramp-up and power-down timing can be adjusted. Inrush current control protects systems that contain large bulk capacitors near the load. When power is initially applied to the system, charging these capacitors can result in a large inrush current that exceeds the nominal load current. If left unaddressed, this can cause voltage rails to fall out of regulation due to the drop, resulting in the system entering an undesired state. Load switches can mitigate the inrush current by using the CT pin to manage the rise time of the power rail. This leads to a linear output slew rate with no voltage dips or external regulators required.

| DESCRIPTION                                                                  | DEVICES  | VOLTAGE<br>RANGE | MAX<br>CURRENT | TYPICAL Ron | PACKAGE |

|------------------------------------------------------------------------------|----------|------------------|----------------|-------------|---------|

| Adjustable rise time, adjustable QOD                                         | TPS22918 | 1 V to 5.5 V     | 2 A            | 52 mΩ       | SOT     |

|                                                                              | TPS22810 | 2.7 V to 18 V    | 2 A            | 79 mΩ       | SOT     |

| Space-constrained applications                                               | TPS22915 | 1.05 V to 5.5 V  | 2 A            | 37 mΩ       | CSP     |

|                                                                              | TPS22916 | 1 V to 5.5 V     | 2 A            | 60 mΩ       | CSP     |

| Self protected with controlled rise time                                     | TPS22919 | 1.6 V to 5.5 V   | 1.5 A          | 90 mΩ       | SOT     |

| Lowest ON-resistance, Power Good indication                                  | TPS22990 | 1 V to 5.5 V     | 10 A           | 3.9 mΩ      | SON     |

| Fast turn-on time (≤ 65 µs), Power Good indication,<br>QOD, Thermal shutdown | TPS22971 | 0.65 V to 3.6 V  | 3 A            | 6.7 mΩ      | DSBGA   |

#### Table 2. Load Switch Examples<sup>(1)</sup>

<sup>(1)</sup> For more information about load switches, visit *TI.com/LoadSwitches*.

### 2 Power Multiplexing

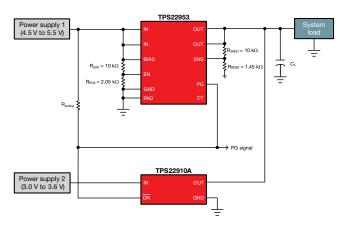

Figure 3. Power MUX Block Diagram

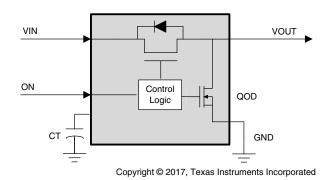

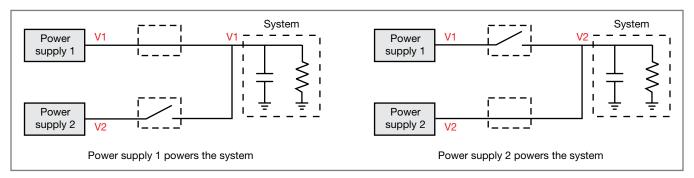

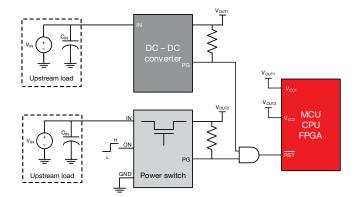

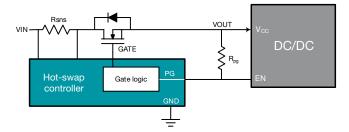

Integrated *Power MUX* devices allow a system to transition between different power sources seamlessly. If the main power supply fails, power multiplexing allows the system to switch to a backup power supply, such as a battery, to preserve operating conditions. Power multiplexing can also provide switching between two different voltage levels for subsystems that operate at two different voltages. In this scenario, to prevent reverse current flow from  $V_{OUT}$  into one of the  $V_{IN}$  channels, reverse current protection (RCP) blocks current from flowing back through the body diode. Power multiplexing also contains adjustable current limits. If the current exceeds the threshold set by the switch, the switch clamps the channel and prevent current from exceeding the limit. Furthermore, if the current limit forces the device to reach higher temperatures, thermal shutdown will turn off the switch until it can operate at safe conditions again. Similar to load switches, power MUX switches also contain inrush current control to prevent large transient current events.

*Power MUX* devices can switch between different power rails in three general ways: manually, automatically, or both. Manual switchovers occur with an external GPIO. Whenever the user wants to switch between power rails, the enable pin is toggled and the output is powered by the other power rail. Automatic switchover occurs whenever the primary power supply fails or is disconnected. When the device detects the voltage drop, it automatically switches to the backup power rail. There are some Power MUX solutions which offer the flexibility to be used in an automatic configuration and be controlled by a manual control signal. This method can have a default (automatic) priority, but then be overridden by an external microcontroller if needed.

| DESCRIPTION                                                                              | DEVICE  | RECOMMENDED<br>VOLTAGE RANGE | MAX CURRENT         | TYPICAL<br>R <sub>on</sub> | PACKAGE |

|------------------------------------------------------------------------------------------|---------|------------------------------|---------------------|----------------------------|---------|

| Automatic priority and manual override, adjustable current limit                         | TPS2120 | 2.8 V to 22 V                | 3 A, each channel   | 62 mΩ                      | CSP     |

| Automatic priority and manual override, fast output switchover, adjustable current limit | TPS2121 | 2.8 V to 22 V                | 4.5 A, each channel | 56 mΩ                      | QFN     |

<sup>(1)</sup> For more information about power multiplexing, visit *TI.com/PowerMux*.

#### 3 eFuses

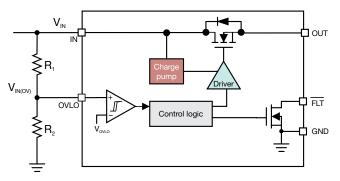

Figure 4. eFuse Block Diagram

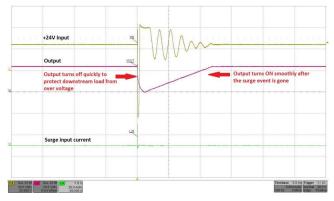

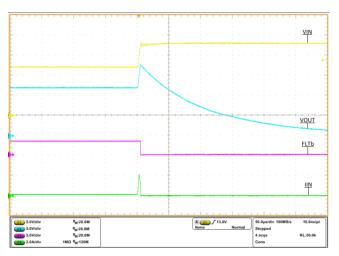

*eFuses* are integrated power protection switches that provide voltage and current protection during fault events. These include short-circuit, overcurrent, overvoltage, undervoltage, and temperature events that might otherwise damage downstream loads. During a short-circuit transient event, the current through the *eFuse* increases very rapidly. The *eFuse* enables a fast-trip current threshold that terminates this rapid increase in less than 200 ns, protecting the supply. If an overvoltage event occurs on the input (VIN), the *eFuse* monitors the voltage across the internal FET and clamps the output voltage until the input falls below the overvoltage threshold. *eFuses* also come with built-in overtemperature protection that shuts down the FET if the junction temperature exceeds 150°C (typical). The *eFuse* either remains off (latch-off version) or attempts to restart (auto retry version) the device after the junction temperature decreases. *eFuses* offer many additional features similar to load switches including adjustable inrush current control and reverse current protection.

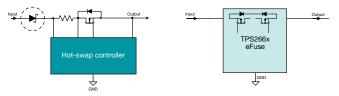

Managing current flow from an active power bus to a subsidiary system can be a challenging task. As a device is inserted or removed from a live supply, it is possible to see a very large spike in current during the initial capacitor charging. An *eFuse* or Section 4 hot-swap controller ensures the safe insertion and operation of these systems. Unlike hot swap controllers, *eFuses* contain an integrated FET which minimizes total solution size. This allows *eFuses* to be used in applications such as power multiplexing. By using two *eFuses*, each *eFuse* can control a power rail while providing reverse current protection for its respective supply. *eFuses* are also UL 2367 certified, cutting down on system testing time.

| DESCRIPTION                                                                                        | DEVICE    | RECOMMENDED<br>VOLTAGE<br>RANGE | MAX<br>CURRE<br>NT | TYPICA<br>L R <sub>on</sub> | PACKAGE        |

|----------------------------------------------------------------------------------------------------|-----------|---------------------------------|--------------------|-----------------------------|----------------|

| Overvoltage or undervoltage protection, QOD using FLT pin, adjustable current limit                | TPS2595   | 2.7 V to 18 V                   | 4 A                | 34 mΩ                       | SON            |

| Lowest Ron circuit-breaker device, accurate load monitoring, adjustable transient fault management | TPS25982  | 2.5 V to 24 V                   | 15 A               | $3 \text{ m}\Omega$         | QFN            |

| Back to back FETs, status monitoring, thermal shutdown, internal reverse current blocking          | TPS25942A | 2.7 V to 18 V                   | 5 A                | 42 mΩ                       | QFN            |

| Reverse polarity protection, current sense output, adjustable current limit                        | TPS2660   | 4.2 V to 55 V                   | 2 A                | 150 mΩ                      | SOP and<br>QFN |

| Power limiting, overvoltage cut-off or voltage clamping functionality                              | TPS1663   | 4.5 V to 60 V                   | 6 A                | 31 mΩ                       | SOP and<br>QFN |

| Power limiting, reverse current blocking, reverse polarity protection                              | TPS2663   | 4.5 V to 60 V                   | 6 A                | 31 mΩ                       | SOP and<br>QFN |

Table 4. eFuse Examples<sup>(1)</sup>

<sup>(1)</sup> For more information about eFuses, visit *www.ti.com/efuses*.

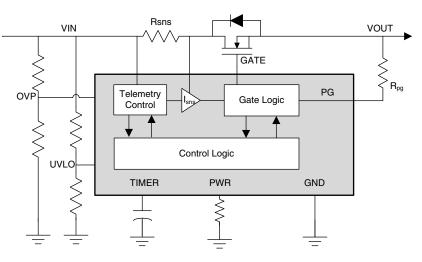

### 4 Hot Swap

Copyright © 2017, Texas Instruments Incorporated

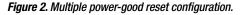

Figure 5. Hot Swap Block Diagram

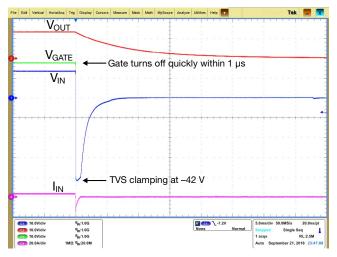

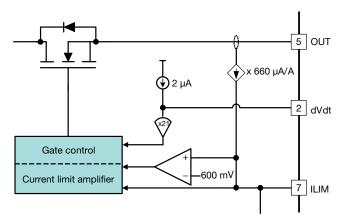

*Hot Swap* controllers drive an external MOSFET that protects the system against hot swap events. *Hot Swap* controllers do not integrate a MOSFET as eFuses do. The external MOSFET allows *hot swap* controllers to operate at higher voltages and currents than eFuse devices. The controller monitors the gate voltage of the external FET and adjusts the voltage depending on the situation. When the device is inserted into a live power system, the controller measures the inrush current across  $R_{SNS}$ . If the value exceeds the programable current limit, the gate voltage is lowered and limits the current passing downstream. If the power dissipated across the FET exceeds the programmable power limit, then the gate voltage is reduced to lower the current flowing through  $R_{SNS}$ . The overvoltage and undervoltage pins also cut off the output voltage whenever the input voltage is not within specified thresholds.

To ensure that the external MOSFET remains within safe operating area (SOA), the *hot swap* controller regulates the current limit at higher  $V_{DS}$  voltages. The device also includes an assortment of telemetry that monitors the operating conditions. The Power Good (PG) signal turns on whenever the power rail reaches regulation, and some *hot swap* controllers contain PMBus monitoring that allows real-time feedback on the device status.

Since *hot swap* controllers operate by controlling an external  $R_{SNS}$  and MOSFET, they do not contain an innate current limit. The external components allow the user to customize the solution size and power requirements to fit their application.

| DESCRIPTION                                                                                                      | DEVICE                | RECOMMENDED VOLTAGE RANGE | PACKAGE    |

|------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|------------|

| 18-V analog devices, small footprint, easy-to-use                                                                | TPS247xx              | 2.5 V to 18 V             | SOP or QFN |

| Meets 240-V requirements for high-end applications, similar to TPS247xx                                          | TPS2477x              | 2.5 V to 18 V             | QFN        |

| PMBus and I2C communication, balance between efficiency and accuracy                                             | LM25066A,<br>LM25066I | 2.9 V to 17 V             | QFN        |

| Higher voltage applications, PMBus and I2C communication, external FET temperature and failure sensing           | LM5066                | 10 V to 80 V              | PWP        |

| Higher voltage applications, SOA protection, current limit                                                       | LM5069                | 9 V to 80 V               | SOP        |

| Negative voltage support, SOA protection, PMBus and I2C communication                                            | LM5064                | -10 V to -80 V            | SOP        |

| Negative voltage support with dual current limit, soft-start disconnect,<br>ORing support, –200 V maximum rating | TPS2352x              | –10 V to –80 V            | SOP        |

| Circuit breaker function for severe current events, programmable fault timer, PG output                          | LM5067                | -9 V to -80 V             | SOP        |

<sup>(1)</sup> For more information about Hot Swap controllers, visit *www.ti.com/hotswap*.

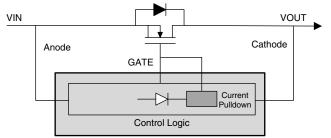

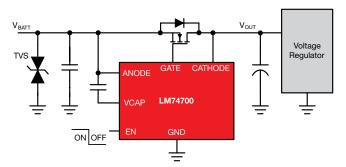

# 5 Ideal Diode, ORing Controllers

Copyright © 2017, Texas Instruments Incorporated

Figure 6. Ideal Diode Block Diagram

*Ideal diode* controllers control an external FET and, similar to a regular diode, can block reverse current whenever a reverse voltage event occurs. Whenever one of these events occur, the controller shuts off the FET and uses the body diode to prevent any transients from damaging upstream components. The controller can also prevent against ground shorts at the input (VIN) by using the same method.

*Ideal diode* controllers can also protect against reverse polarity conditions, commonly caused by connecting a battery incorrectly or mis-wiring a power supply. If the user accidentally switches the polarity on VIN, an additional diode from the controller to GND can be included to prevent damage to the IC or the power source. The controller also significantly lowers power dissipation normally found across diodes. By driving the external FET instead of a diode, the voltage drop typically found across diode solutions can be minimized.

*Ideal diodes* can also act as ORing controllers. Basic power redundancy architecture contains two or more power supplies connected to a single load. ORing solutions allow the system to switch between power sources if one were to fail, and can even connect power sources in parallel. This allows for uninterrupted power and saves on redundant power supply costs.

| DESCRIPTION                                        | DEVICE     | RECOMMENDED<br>VOLTAGE<br>RANGE | TYPICAL<br>QUIESCENT<br>CURRENT | FORWARD<br>VOLTAGE<br>THRESHOLD | PACKAGE      |

|----------------------------------------------------|------------|---------------------------------|---------------------------------|---------------------------------|--------------|

| Fast turnoff, voltage sensing                      | TPS241x    | 3 V to 16.5 V                   | N/A                             | 10 mV                           | SOP and SOIC |

| Automotive qualified, low Iq, high efficiency      | LM74700-Q1 | 3.2 V to 65 V                   | 80 µA                           | 20 mV                           | SOT          |

| Low side ORing controller, FET diagnostics         | LM5051     | -6 V to -100 V                  | 69 µA                           | 45 mV                           | SOIC         |

| Low Iq, reverse current protection, integrated FET | LM66100    | 1.5 V to 5.5 V                  | 0.2 µA                          | 79 mV <sup>(2)</sup>            | SC-70        |

# Table 6. Ideal Diode Controller Examples <sup>(1)</sup>

<sup>(1)</sup> For more information about *Ideal diode* controllers, visit *www.ti.com/idealdiode*.

<sup>(2)</sup> Typical forward voltage at lout = 1 A.

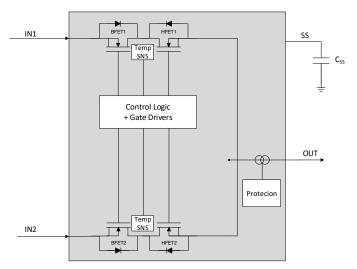

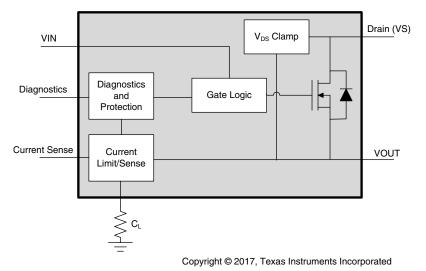

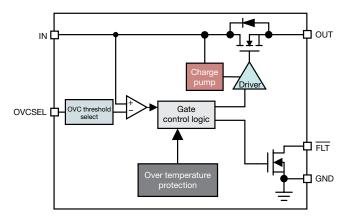

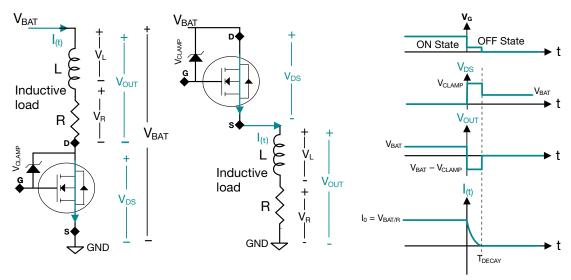

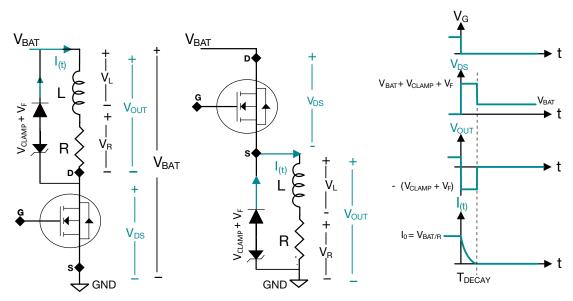

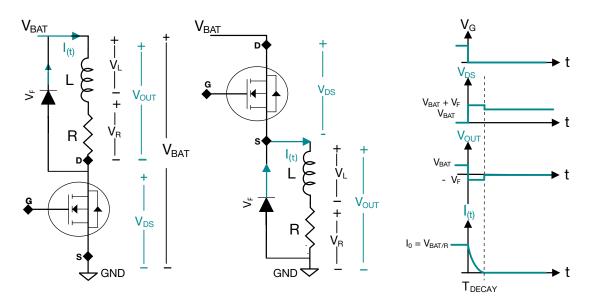

# 6 Smart High-Side Switches

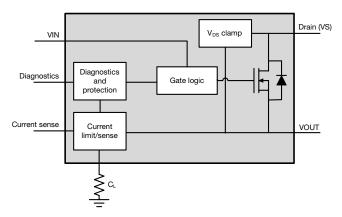

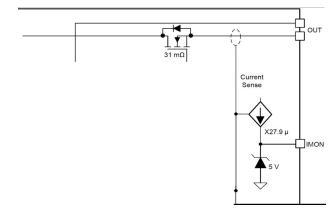

Figure 7. Smart High-side Switch Block Diagram

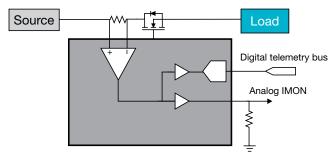

*Smart high-side* switches reliably drive off-board loads. These switches contain highly-adjustable and selectable current limits that enable a system to be optimally designed for specific loads. By connecting an external resistor to set the current-limit threshold, the switch protects the load and power supply from overstressing during short-circuits to GND events or power-up conditions. This enables more reliable designs by minimizing transient currents and supply droops. When the threshold is reached, a closed loop activates and clamps the output current to the set value. A fault is then reported on the CS pin.

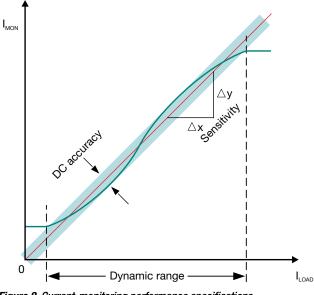

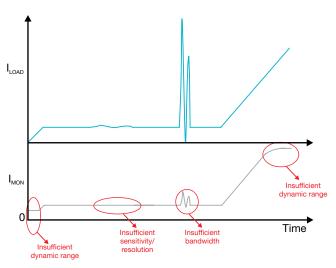

These switches also offer highly-accurate current sensing to provide real-time diagnostics to the system. A current mirror sources current from VIN, reflecting this as voltage on the Current Sense (CS) pin. The CS pin does not need to be calibrated, and can serve as a diagnostics report pin. Whenever an open load or short happens, the voltage on the CS pin falls to 0 V. Whenever a current limit, thermal event, or an open load or short in the off state occurs, the voltage is pulled up to its maximum threshold. High-accuracy current monitoring and adjustable current limit are ideal for industrial applications like programmable logic controllers, motor valves, servo drives and control units.

Another functionality of *smart high-side* switches is load-dump compatibility, which allows these devices to connect directly to a 12-V battery without concerns about typical voltage and current transients. Additional protection includes mitigation of large inrush current events that would otherwise damage downstream components.

*Smart high-side* switches can be AEC-Q100 certified, allowing full integration into many automotive applications that require a low on-resistance and high voltage tolerances to accommodate voltage spikes and inrush current events. Some of these applications include front and rear lighting, seat heating, infotainment, cluster, powertrain, and ADAS.

| DESCRIPTION                                                                                            | DEVICE      | RECOMMENDED<br>VOLTAGE<br>RANGE | CURRENT<br>SENSE<br>ACCURA<br>CY | CONTINUOUS LOAD<br>CURRENT | TYPICA<br>L R <sub>on</sub> | PACKA<br>GE |

|--------------------------------------------------------------------------------------------------------|-------------|---------------------------------|----------------------------------|----------------------------|-----------------------------|-------------|

| Selectable current limit for design flexibility, low $R_{\text{ON}},$ small footprint, thermal sensing | TPS1HA08-Q1 | 3 V to 40 V                     | ±5% at 1 A                       | 0 A to 12 A                | 8 mΩ                        | SOP         |

| Low standby current, highly accurate current sense,                                                    | TPS1H100-Q1 | 3.5 V to 40 V                   | ±3% at 1 A                       | 0 A to 4 A                 | 100 mΩ                      | SOP         |

| thermal shutdown                                                                                       | TPS27S100   | 3.5 V to 40 V                   | ±3% at 1 A                       | 0 A to 4 A                 | 80 mΩ                       | SOP         |

| Multi-channel support, fast hardware interrupts, low standby current, loss of GND diagnostics          | TPSxH160-Q1 | 3.4 V to 40 V                   | ±3% at 1 A                       | 0 A to 1.8 A per channel   | 160 mΩ                      | SOP         |

Table 7. Smart High-Side Examples (1) (2)

$^{(1)}$   $\,$  Additional devices in various typical  $R_{ON}$  values are available.

<sup>(2)</sup> For more information about smart high-side switches, see *ti.com/smarthighsideswitch*.

| DESCRIPTION                                                                             | DEVICE      | RECOMMENDED<br>VOLTAGE<br>RANGE | CURRENT<br>SENSE<br>ACCURA<br>CY | CONTINUOUS LOAD<br>CURRENT | TYPICA<br>L R <sub>on</sub> | PACKA<br>GE |

|-----------------------------------------------------------------------------------------|-------------|---------------------------------|----------------------------------|----------------------------|-----------------------------|-------------|

| Dual-channel, programmable current limit                                                | TPS2HB08-Q1 | 3 V to 28 V                     | +3/-8% at<br>1 A                 | 0 A to 8 A per channel     | 8 mΩ                        | SOP         |

| Inductive load negative clamp with optimized slew rate, global fault report             | TPSxH000-Q1 | 3.4 V to 40 V                   | -                                | 0 A to 1A                  | 1 Ω                         | SOP         |

| Highly accurate current limit, supports full diagnostics with the digital status output | TPS1H200-Q1 | 3.4 V to 40 V                   | -                                | 0 A to 2.5 A               | 200 mΩ                      | SOP         |

# Table 7. Smart High-Side Examples <sup>(1) (2)</sup> (continued)

# 7 Low-Side Switches

Copyright © 2017, Texas Instruments Incorporated

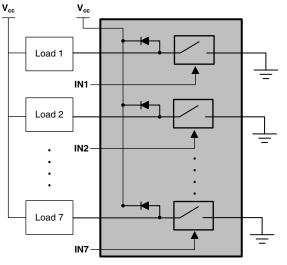

Figure 8. Low-Side Switch Block Diagram

*Low-side* switches are used to connect and disconnect ground from a load, unlike the rest of the power switch topologies. This configuration allows *low-side* switches to drive inductive loads; an internal flyback diode prevents inductive transients from damaging the circuit and components. Whenever the switch is opened, the inductive transients flow through the flyback diode and dissipate throughout the load. This makes these devices ideal for motors, solenoids, and relays.

*Low-side* switches consists of two designs: Darlington pair arrays and low-side MOSFET solutions. Darlington pair solutions can support higher voltage applications due to the higher voltage ratings of the integrated BJTs, while the MOSFET solutions have lower on-resistances and lower leakage currents. Most of the *low-side* switches contain seven channels, which can be tied in parallel to support higher current operation.

| DESCRIPTION                                                                       | DEVICE    | RECOMMENDED<br>VOLTAGE RANGE | MAX<br>CURRENT        | NUMBER OF<br>CHANNELS | PACKAGE                           |

|-----------------------------------------------------------------------------------|-----------|------------------------------|-----------------------|-----------------------|-----------------------------------|

| Darlington pair BJTs, higher voltage support                                      | ULN2003A  | 0 V to 50 V                  | 500 mA per<br>channel | 7                     | SOIC, SOP,<br>and DIP<br>Packages |

| Darlington pair BJTs, 8-channel support                                           | ULN2803A  | 0 V to 50 V                  | 500 mA per<br>channel | 8                     | SOIC                              |

| Low-side MOSFET solutions, low on-resistance and current leakage, power efficient | TPL7407LA | 0 V to 30 V                  | 600 mA per<br>channel | 7                     | SOIC or SOP                       |

#### Table 8. Low-side Switch Examples

### 8 References

- 1. Texas Instruments, Basics of Load Switches Application Report

- 2. Texas Instruments, What is an eFuse? Application Report

- 3. Texas Instruments, Robust Hot Swap Design Application Report

- 4. Texas Instruments, Adjustable Current Limit of Smart High Side Switch Application Report

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Original (November 2018) to A Revision Pa | age |

|----|-------------------------------------------------------|-----|

| •  | Changed content in abstract                           | 1   |

| •  | Changed headings, row 3, and row 7 in table 1         | 2   |

| •  | Added table notes to table 1.                         | 2   |

| •  | Changed row 3 in table 2.                             | 3   |

| •  | Changed content in section 2                          |     |

| •  | Changed row 1 and 2 in table 3.                       | 4   |

| •  | Changed rows 2, 5, and 6 in table 4.                  | 5   |

| •  | Changed title and row 1, 2, and 4 in table 6.         |     |

| •  | Changed content in section 6                          |     |

| •  | Changed rows 4, 5, and 6 in table 7.                  |     |

#### Author: Alex Triano

#### Abstract

When a subsystem turns on, current initially flows to any capacitors or inductance at the load. This current is often referred to as inrush current. If a switch turns on quickly (such as without slew-rate control), then the current may be large enough to interrupt other subsystems connected to the same input rail. In some cases, inrush current during a short period of time can irreversibly damage surrounding components or even the switch itself. It is possible to manage inrush current in several ways, although all techniques result in a reduction of the speed at which the output voltage rises.

### The Dangers of Inrush Current

Inrush current may cause an upstream supply voltage to dip. If this voltage is supplying power to other subsystems, those components may experience misbehavior or a reset.

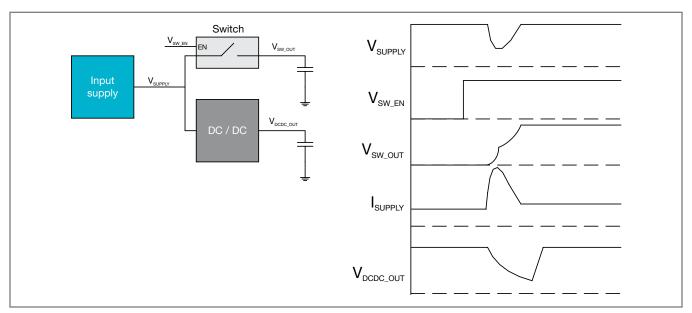

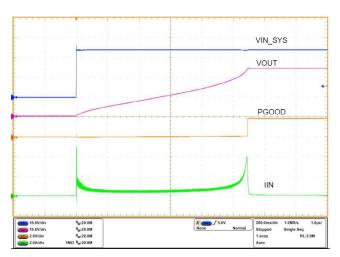

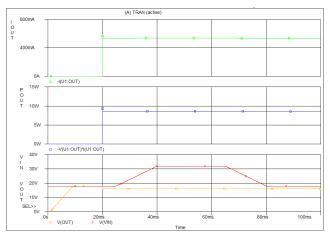

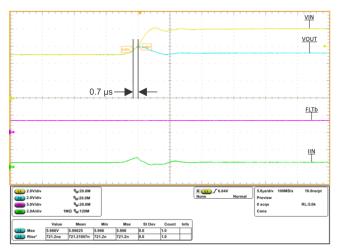

In **Figure 1**, the switch is enabled, which causes a fast transient voltage (dv/dt) and a large current spike on the input supply. This leads to a V<sub>SUPPLY</sub> voltage dip, which is visible while V<sub>SW\_OUT</sub> continues to turn on. The voltage dip on V<sub>SUPPLY</sub> causes DC/DC converters to shut down; V<sub>OUT</sub> decays until V<sub>SUPPLY</sub> recovers within the normal operating range. This scenario demonstrates how inrush current on one load can cause other loads to experience a reset.

Some systems have restrictions on how much current they can draw from the input. These restrictions may be set by safety standards, cable/connector ratings or the need to stay below the current rating of a fast-blow fuse. A failure to manage inrush current can exceed restrictions and lead to compliance failures or damaged cables, connectors or fuses.

A power switch that uses a metal-oxide semiconductor field-effect transistor (MOSFET) to turn power on and off can exceed the FET's safe operating area (SOA) and damage the switch itself. Most power FET manufacturers include a graph listing how much current the switch can handle at a given drain-to-source voltage ( $V_{DS}$ ), ambient temperature and specified pulse duration. If a FET turns on quickly, into a large load capacitance, the total energy passing through the FET is one-half capacitance-voltage-squared (CV<sup>2</sup>) during the turn on-time ( $t_{ON}$ ) duration. This value can exceed the FET's SOA curve and damage the FET. If that same amount of energy is spread over a longer  $t_{ON}$ , then the FET has more time to dissipate that heat and could be designed to survive.

#### **Common Techniques to Control Inrush Current**

There are three traditional approaches and one newer approach to controlling inrush current. The first is to use a passive element such as a series resistor or a negative temperature coefficient (NTC) thermistor to slowly charge the output. The second is to use a switch and manage

Figure 1: Inrush current on  $V_{SW OUT}$ , causing a supply dip and reset on  $V_{DCDC OUT}$ .

the slew rate at which the output voltage is rising. The third is to use a current limiter or a device designed to provide a constant current until the switch is fully on. The newest approach is to use thermal regulation, which provides maximum current while regulating the temperature of the switch to prevent failure.

# Passive

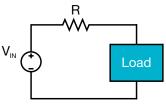

Adding resistance in series with the supply limits current to the load. A pure resistor would limit the peak inrush current to  $V_{IN}/R$ , and then the current would begin decreasing as the output becomes fully charged. This technique will dissipate power through the resistor as well as limit the current that the load can draw once powered. But because of poor efficiency, this technique is usually limited to low-current applications (often much less than 1 A). **Figure 2** shows a series resistor to limit inrush current.

Figure 2: Series resistor to limit inrush current.

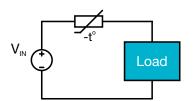

If adding an NTC, the resistance will start off high when the switch is cool and power has not flowed through it. As power is applied, the high resistance will allow a small amount of current through to the output. This will begin to self-heat the device and cause the resistance to drop, gradually allowing more and more current through to the load until the NTC is fully on. Since NTC performance relies heavily on ambient temperature, it may not be suitable for applications needing a wide operating temperature range. **Figure 3** shows how to use a series NTC thermistor to limit inrush current.

Figure 3: Using a series NTC thermistor to limit inrush current.

# **Slew-Rate Control**

I

Controlling the rate at which the switch turns on directly controls the rate at which the output voltage rises. **Equation 1** calculates the inrush current as:

$$_{\rm INRUSH} = C_{\rm LOAD} \times \frac{dV_{\rm OUT}}{dt}$$

(1)

Slowing the switch speed (dV\_{OUT}/dt) reduces  $\rm I_{\rm INRUSH}$  for a given, fixed  $\rm C_{\rm LOAD}.$

# **RC Time Constant**

For a discrete power switch, one common method to manage inrush current is to install a resistor-capacitor (RC) that slows down the MOSFET switching speed, as shown in **Figure 4**.

Figure 4: A discrete MOSFET with an RC rise time to limit inrush current.

This is a simple method to control the switch speed through an RC time constant. While the speed can be reduced and the total turn-on time increased, note that the dv/dt speed is nonlinear; therefore, the inrush current is nonlinear. The switch will start to turn on slowly and will exponentially increase as the switch becomes fully on. See **Figure 5** for RC-based inrush current.

Figure 5: RC-based inrush current.

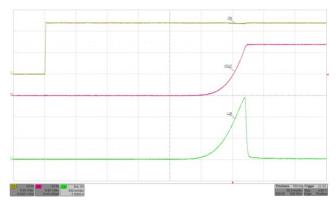

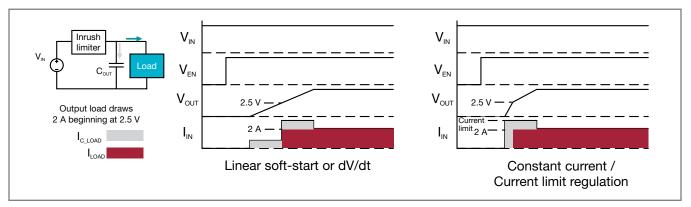

#### Linear Soft Start or dV/dt

Many integrated power switches have a method of controlling the output voltage rise time linearly. These switches may come with a fixed or adjustable rise time. In all cases, controlling the output voltage rise time linearly means controlling a constant  $dV_{OUT}/dt$  rate. In this case, if  $C_{LOAD}$  is constant and  $dV_{OUT}/dt$  is a constant speed, then  $I_{INRUSH}$  will also be a constant, as shown in **Figure 6**.

Figure 6: Linear dv/dt to limit inrush current using the Texas Instruments <u>TPS22975 load switch</u>.

Linear soft start has a couple of advantages over an RC time constant approach, including simple and precise calculations for inrush current. There may be situations where you have both a maximum inrush current restriction and a maximum turn-on time requirement. In these cases, if an RC time constant would either take too long to turn on or have too high of an inrush current, then a linear control scheme offers the best chance to satisfy both requirements. If you can't satisfy **Equation 2**, then there is no solution other than changing the design architecture to remove these restrictions, or moving to a smaller  $C_{LOAD}$  or a lower  $V_{OUT}$ :

$$I_{\text{INRUSH}_{MAX}} = C_{\text{LOAD}} \times \frac{V_{\text{OUT}}}{t_{\text{ON}}}$$

(2)

#### **Constant Current/Current Limit Regulation**

Similar to a linear soft-start scheme, a constant current method of controlling inrush current would yield the same result if powering a purely capacitive load. If you charge with a constant  $I_{INRUSH}$ , then for a given  $C_{LOAD}$ , you will be charging at a constant dv/dt.

The difference is the linear soft start was regulating voltage, whereas a current limiter is regulating current. The approaches will differ once you begin introducing loads outside of a capacitor. If you have an integrated circuit that activates before the output voltage is fully on, then the linear soft-start method will have that current superimposed. The constant current method will change its slew rate, since some current is now going to the load instead of to the output capacitor.

In **Figure 7**, linear soft start is maintaining a constant slew rate for the output, whereas the constant current limit will change its slew rate when the load turns on at 2.5 V.

Constant current limit during startup can be helpful for situations where loads may turn on while the switch is still turning on. Constant-current-limit devices often provide protection against events such as an output short circuit. We will discuss current-limiting techniques in more detail in the next chapter, but it is important to understand that it is one form of managing inrush current during startup.

#### **Thermal Regulation**

In order to turn on as quick as possible but maintain protection for the switch, there is a final technique using thermal regulation. This can be useful in situations with

Figure 7: Linear dv/dt versus constant-current-limit regulation.

a large or unknown output capacitance (such as driving an offboard load). Once the junction temperature rises to a specified level, the device starts controlling the inrush current profile in order to maintain a regulated junction temperature. This will continue until the load capacitors are fully charged, or until a timeout. To learn more about a switch with a thermal regulation loop, see the TPS2663 eFuse (or electronic fuse), also highlighted in Figure 8.

Figure 8: Thermal regulation loop using the TPS2663 with 24-V  $V_{\rm IN}$  and 30 mF of output capacitance.

#### Authors: Rakesh Panguloori and Lokesh Ghulyani

#### Abstract

Current limiting is essential in many systems to restrict transient overload currents to permissible levels. Traditional current-limiting solutions such as discrete resettable fuse circuits are inferior in performance due to their inaccuracy, slower response, and a lack of configurability and repeatability. This chapter discusses how integrated power switch solutions overcome the limitations of discrete current-limiting solutions.

Integrated power switch solutions provide accurate and adjustable current limit that helps limit overload currents precisely, thereby reducing front-stage power budgets and the size of passive components, cables and printed circuit board (PCB) traces. In addition, their accurate current-limiting (or output power-limiting) function simplifies system design by complying with critical safety standards.

#### The Need for Current Limiting

The semiconductor components, passive filters, PCB traces and interfacing cables found inside electronic equipment all have an inherent maximum current capability that when exceeded will cause them to overheat, possibly to an unrecoverable state. To overcome this, some kind of current-limiting device restricts fault currents within the maximum current-rating limits and brings the system back to normal operation once the fault is cleared.

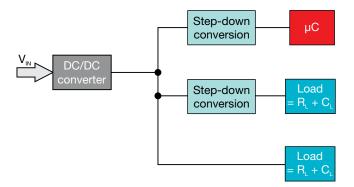

In the example shown in **Figure 1**, a DC/DC converter is supplying power to various internal subsystems, each requiring a specific voltage for proper operation. An overload event in any one of these subsystems can

Figure 1: Power distribution in typical electronic equipment.

affect the operation of system-critical loads connected to the same power distribution bus, leading to an erroneous system function or system reset.

To overcome such a scenario, you can use currentlimiting devices in each of the power paths to manage overload and short-circuit events, and to guard sensitive circuitry for reliable system operation.

These parameters determine the performance of a current-limiting device:

- Accuracy.

- Adjustability.

- Repeatability.

- Response time.

#### **Traditional Ways to Implement Current Limiting**

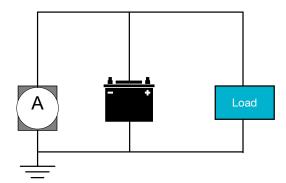

Fuses are traditionally considered protection devices, isolating overload or short-circuit faults from the main system. While fuses are an inexpensive solution, they can fall short of many of the protection requirements imposed on modern electronic equipment. The overload current needs to be exceedingly higher (500%) than the rated fuse current in order to produce a response within milliseconds. This makes it extremely difficult to predict the precise overcurrent level at which the fuse will open. A conservative fuse current rating selection may lead to a fuse blowup during inrush current events. In addition, once the fuse blows during an overload event, it has to be physically replaced, which increases system downtime and maintenance costs. **Figure 2** shows such a scenario.

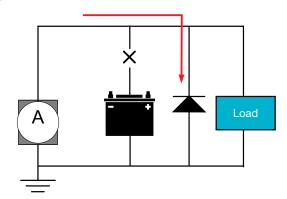

Figure 2: A blown fuse needs to be physically replaced every time in order to resume normal operation.

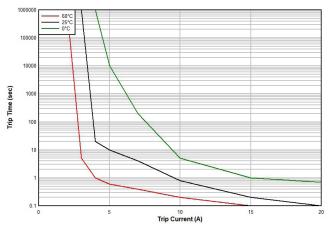

A resettable fuse is a positive temperature coefficient (PTC) device that increases its on-resistance with temperature. During an overload event, the excessive load current increases power loss, thereby increasing its on-resistance. The higher on-resistance helps limit the overload current and protects the circuit. Unlike a physical fuse, PTCs allow current to flow after the fault is cleared without replacing the device.

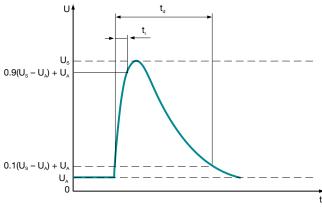

Because PTCs are actuated by the heating effect of an overcurrent load, their reaction time is limited to several milliseconds, as they have a natural dependency on the ambient temperature, as shown in **Figure 3**. Another property of a resettable fuse is that its on-resistance increases after every reset, which raises concerns about achieving repeatable performance over time.

Figure 3: Trip time vs. trip current temperature dependency.

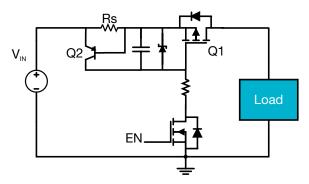

# **Discrete Current-Limiting Circuits**

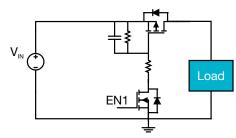

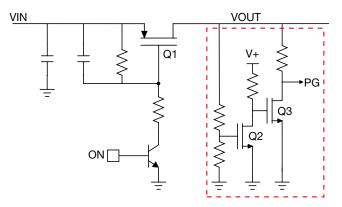

**Figure 4** shows an example of a current-limit circuit using discrete components. The resistor-capacitor components around discrete power switch Q1 slow down the metal-oxide semiconductor field-effect transistor switching speed and provide inrush current control. In this implementation, the combination of series

Figure 4: Active current-limiting circuit using discrete components.

sense resistor Rs and P-channel N-channel P-channel transistor Q2 provide active current limiting.

In steady-state operation, Q1 is fully turned on and load current flows through the series sense resistor Rs and discrete power switch Q1. The voltage drop across Rs generates bias voltage VBE for Q2, which is used to control Q1 in a closed-loop form. When the load current reaches high enough to bias Q2 on, Q2 reduces the gate-to-source voltage of Q1 to limit the load current to VBE/Rs.

The response time of this discrete approach is much better than a fuse or PTC, but still suffers from poor accuracy. Current-limiting accuracy can be in the range of 30% considering the variation of VBE voltage over temperature. Another disadvantage is the power loss in the sense resistor; for a 5-A application, dissipation would be as high as  $3.25 \text{ W} (0.65 \text{ V} \times 5 \text{ A} = 3.25 \text{ W})$ . It is possible to reduce the power loss by using either a current-sense amplifier or a fast comparator to disable pass switch Q1 in the event of overload, but this adds complexity and cost. Discrete current-limiting circuits do not incorporate thermal protection, so these solutions need careful selection of the pass field-effect transistor (FET) and prudent thermal design to keep the pass FET within safe operating area limits under extreme fault conditions. All of these limitations often lead to a tradeoff between accuracy, cost, complexity, PCB size and power loss.

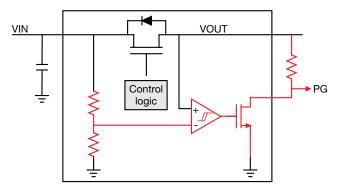

### eFuses

An <u>eFuse</u> is an active current protection device with an integrated FET used to limit currents to safe levels during fault conditions. The common elements of an eFuse are a power switch to modulate the load current, a current-sensing element and control logic. As shown in **Figure 5** on the following page, the current-limit threshold can be set to a desired value through external resistor  $R_{LIM}$  at the  $I_{LIM}$  pin of the eFuse, providing system flexibility in adjusting the current limit to a wide range.

In a steady-state condition, the integrated power switch is fully turned on (just like a discrete switch) to minimize voltage drop in the power path. If at any point the load current reaches the set current-limit level,  $I_{LIM}$ , the gate control transitions the integrated power switch into linear mode. This increases the on-resistance and corresponding voltage drop across the eFuse to provide a constant output current.

Figure 5: Block diagram of an eFuse.

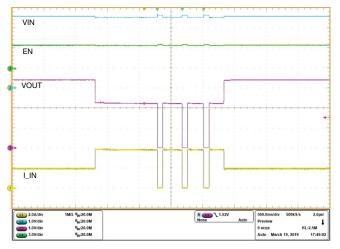

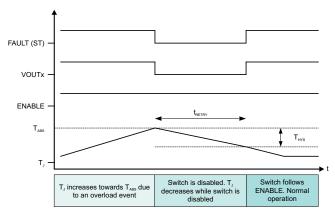

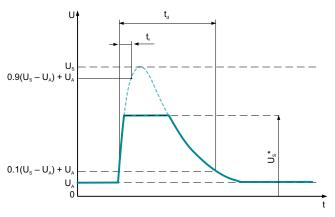

**Figure 6** shows the overload response of an eFuse with the current limit set at 4 A. As you can see, the eFuse responds quickly to an overload event (typically hundreds of microseconds) and regulates the output current to  $I_{LIM}$ . Once the fault is removed, the eFuse recovers back to normal operation smoothly.

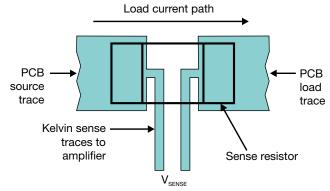

An eFuse uses a current mirror circuit to measure the path current without the need for an external sense resistor (like Rs in **Figure 4**). This approach not only saves board space but also eliminates the loss in sense resistors and provides better current-limiting accuracy over discrete approaches—in the range of  $\pm 5\%$  to  $\pm 8\%$ .

Another major advantage of eFuse devices is their integrated overtemperature protection. The device shuts

*Figure 6:* Transient overload current limiting and recovery with the TPS2595 eFuse.

off the integrated power switch for junction temperatures above 150°C to ensure robust protection.

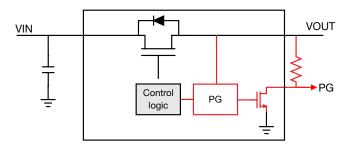

# **High-Side Switches**

Smart power switches offer robust protection against overload and short-to-ground events through overcurrent protection and are available in Automotive Electronics Council (AEC)-Q100 options. These devices provide a current-limiting function similar to eFuses but differ in their ability to drive inductive offboard loads.

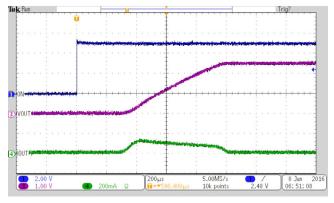

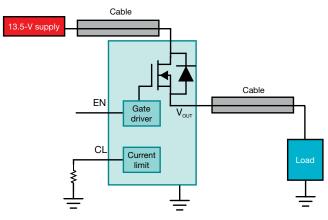

As shown in **Figure 7**, smart power switches have options to use either an internal, fixed high current limit (when the  $C_L$  pin is ground) or an external lower current-limit value (when the  $C_L$  pin is tied to ground through external resistor  $R_{CL}$ ). The adjustable low current limit greatly reduces the fault energy that the internal power switch has to handle during a fault, in turn reducing stress on the power switch and improving system reliability.

Figure 7: Block diagram of a high-side switch.

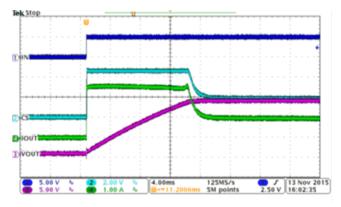

The lower current limit also helps clamp the inrush currents to a much lower value, as shown in **Figure 8** on the following page. Lower fault currents save systemlevel costs by minimizing PCB trace widths and cable sizes, along with lower connector ratings and component tolerances. For more information on the benefits of adjustable current limiting with smart power switches, see the application report, "<u>Adjustable Current Limit of</u> <u>Smart High-Side Switches</u>."

Figure 8: Inrush current clamping with the TPS1H100-Q1 high-side switch.

# **Power Limiting**

Power limiting is usually required to limit the power delivered to the load. For power supplies with a narrow voltage range, a current-limiting device would be sufficient to limit power. But for power supplies with a wider voltage range, a power-limiting device is required. **Figure 9** illustrates a typical implementation for limiting power.

Figure 9: Typical power limiting.

# The Need for Power Limiting

In most applications, it's possible to achieve power limiting with current limiting, but certain applications need to precisely limit the energy or power delivered into the load. Industrial systems such as programmable logic controllers have a wide operating voltage range, from 18 V to 36 V. In telecommunication systems, the operating voltage range varies from 36 V to 72 V, thus may require power limiting as well as current limiting.

Limiting current for a fixed output voltage or a smaller variation in voltage can achieve power limiting. But larger variations in voltage require an additional control loop in order to limit power. This additional current loop adjusts the current limit with voltage to maintain constant power. TI's <u>Precision Power Limiting</u> <u>Solution</u> reference design provides an example of this additional control loop.

There are safety and compliance standards such as International Electrotechnical Commission (IEC) 61010-1 for industrial equipment power and energy limiting. Complying with these standards means that precise power limiting is also required.

Certain power supplies are inherently power-limited; these power supplies come under National Electrical Code (NEC) Class 2 or IEC 60950 standards. Achieving power limiting in these power supplies requires an additional power-limiting circuit.

# Implementing Power Limiting Using an eFuse

To precisely limit power, such as in industrial applications, TI's TPS2663 and TPS1663 eFuses offer an integrated solution. These eFuses have an additional power-limiting control loop, and the output power limit is configurable through the P<sub>LIM</sub> pin. The <u>TPS2663</u> and <u>TPS1663</u> can limit output power with an accuracy of  $\pm 6\%$  up to 150 W. These devices also support load transients by enabling current twice the programmed current limit (two times the pulse current) to pass to the transient load.

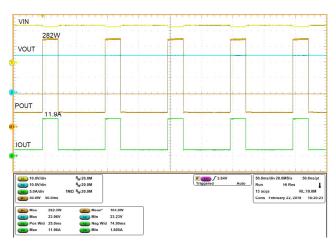

**Figure 10** shows the power-limiting response of the TPS2663. The output power limit is set to 100 W by the resistor on the  $P_{LIM}$  pin; the device allows a pulse current of 12 A and a pulse power of 282 W for a duration of 25 ms to support the load transients. For more details on power limiting with TPS2663 devices, see the <u>data sheet</u>.

**Figure 10:** Power limiting with the TPS26633 (two times the pulse current support,  $I_{LM} = 6 A$ ,  $V_{IN} = 24 V$ ).

# Implementing Power Limiting with an External Control Loop

It is possible to use current limiting to achieve power limiting for power supplies with a narrow input-voltage range. Achieving power limiting in wider-voltage-range power supplies requires an additional control loop for precise power limiting that adjusts the current limit based on the output voltage.

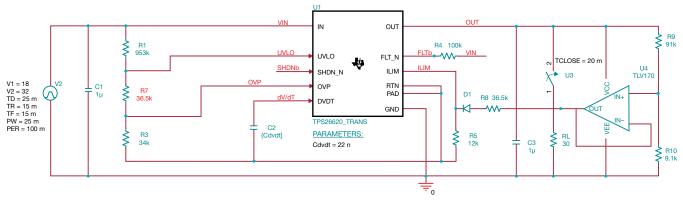

**Figure 11** shows an implementation of the TPS2662 for power limiting. The additional control loop uses a TLV170 amplifier to inject current proportional to the output voltage into the  $I_{LIM}$  pin for power limiting. **Figure 12** provides the PSpice simulation results for the circuit shown in **Figure 11**. For this simulation, the input voltage varies from 18 V to 32 V. The TLV170 adjusts its current limit and the output power is limited to less than 10 W.

Figure 12: Simulation results for power limiting with the TPS2662.

# Conclusion

Current limiting is a basic protection requirement in most modern electronic equipment. Although discrete components work, they require more board space, are less efficient and can generally be less cost effective. TI integrated solutions, eFuses and high-side switches, provide accurate current limiting, faster response times and can repair themselves without user intervention.

# Chapter 3 Short-Circuit Protection

#### Author: Alec Forbes

#### Abstract

Short-circuit protection is critical to ensuring robust reliability for output power protection, as short-circuit failures can cause supply failures or even damage to systems. The most common implementation of shortcircuit protection is through the use of a current-limited output; however, it is important to understand the impact of current limit on short-circuit reliability.

Short-circuit behavior and protection requirements vary based on the output impedance, ranging from terminal shorts to a partial resistive short. Depending on the short-circuit impedance and load profile, the current and energy profile will take different forms.

#### What is a Short Circuit?

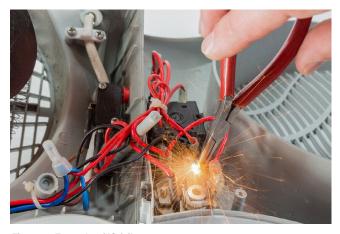

In personal electronics, industrial, automotive and communication applications, short-circuit protection is a safety requirement for all power distribution outputs. Short circuits occur whenever a charged conductor makes physical contact to a grounded element in the system. During a short circuit, the electrical short between power supply and ground can create a very low impedance path, causing a high, uncontrolled sustained current flow. This type of flow is extremely dangerous for systems and can cause integrated circuit (IC) failure, as seen in **Figure 1**. Thus, any systems with a risk of shortcircuit events must implement robust protection.

Figure 1: Example of IC failure.

The risk of a short circuit becomes higher in systems that contain some or all of these characteristics:

- Output cables. Over time, cabling can wear down and present exposed metal, which can make contact with connectors.

- Debris-filled environments. A common cause of short circuits is metallic debris shorting pins or traces.

- Maintenance requirements. Any possibility of exposure to metal tools during maintenance increases the risk of an accidental short-circuit event.

- **Strong voltage supplies.** The more energy that a power supply can provide, the higher the risk of a short-circuit event causing a health hazard.

Automotive systems, for example, regulate output shortcircuit protection through the Automotive Electronics Council (AEC)-Q100-012 standard, which mandates that systems should be capable of surviving thousands of repetitive short-circuit events. The application report, "AEC-Q100-012 Short-Circuit Reliability Test Results for Smart High-Side Switches," documents TI's test process for high-side switches.

#### **Protection Against Short Circuits**

The primary danger during a short-circuit event is the sustained high current flow caused by low output impedance. So in order to protect against short circuits, the system must have output power protection that can recognize a short-circuit event and then shut the system off quickly and safely.

The best way to implement this type of protection is to use a current-limiting switch on the output. This switch will provide protection against a sustained uncontrolled short-circuit current and shut off, protecting the output circuitry. Because the output impedance is unknown and often has an inductive element, the switch must be able to safely demagnetize the inductance, and thus needs a flyback mechanism. **Figure 2** on the following page shows the typical setup that has potential for short circuit.

There are three primary short-circuit conditions that a system must be able to withstand: terminal short circuits, cable short circuits and resistive short circuits.

Figure 2: Typical setup with potential for short circuit.

# Terminal Short Circuit

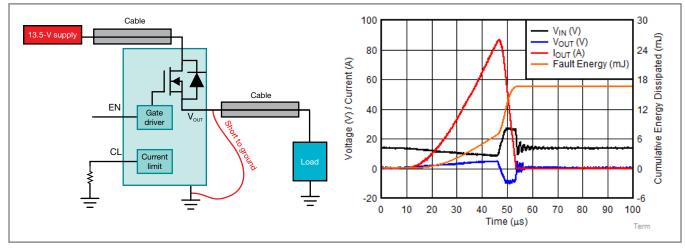

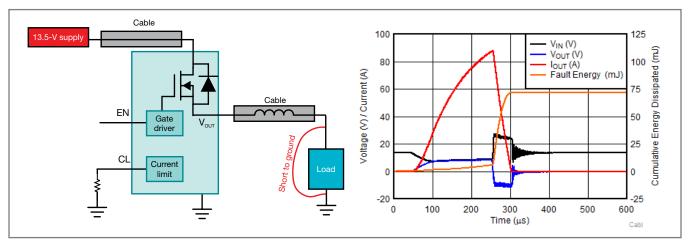

The simplest type of short circuit is the terminal short circuit, illustrated in **Figure 3** with a TI high-side switch providing an output protection stage. The output current increases quickly until it hits a 90-A current limit, at which point the switch recognizes a short-circuit event and turns the switch off, preventing dangerous current flow.

Because this is a terminal short circuit, there is minimal series impedance, and the current-limiting output is easily able to protect the system from the short circuit. The rise and fall times of the short-circuit current are very quick, and the entire event is over in less than 50 µs.

To understand the short circuit, take a look at the total cumulative fault energy, which occurs in two portions:

- As the short-circuit current ramps up, the current causes resistive power losses in the field-effect transistor (FET); however, they are low, as the FET is in saturation mode and the resistance is very small.

- After the switch hits its current limit and turns off, small trace inductive elements in the short circuit create a negative voltage spike that causes the voltage clamp in the switch to engage and the drainto-source voltage ( $V_{DS}$ ) to rise to 40 V. While the inductance demagnetizes, this high  $V_{DS}$  requires the dissipation of more fault energy.

Because of the short length of the pulse, the total fault energy is kept to a relatively safe 18 mJ, despite the high current limit. This case is the easiest short circuit to survive, as there are no series impedances that will impact the output protection.

# Cable Short Circuit

In the event of a short circuit through a cable, accounting for the cable series impedance increases the difficulty of protection. The waveform in **Figure 4** on the following page shows a TI high-side switch short-circuited; however, this time the short circuit occurs at the load side of a  $5-\mu$ H cable (a standard value for a 5-m cable).

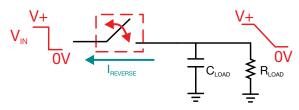

Figure 3: Terminal short on output.

Figure 4: Cable short circuit across the load.

The extra series inductance significantly slows down the current rise and fall times, so the pulse takes 10 times longer and the total fault energy is 75 mJ—four times higher than the terminal short circuit. Energy dissipation occurs in two portions similar to the terminal short-circuit case—but now that the output inductance is 5  $\mu$ H rather than just parasitics (typically less than 10 nH), the inductor demagnetization contains a much higher percentage of the cumulative fault energy.

The energy dissipated in the fault can be very large due to the high current, so the inductive clamp must be rated high enough to dissipate this energy. **Equation 1** calculates the energy dissipated while discharging an inductive element through a series clamp:

$$E = \frac{1}{2} \times L \times I_{PK}^{2} \times \left(\frac{V_{IN}}{V_{CLAMP} - V_{IN}}\right)$$

(1)

The high-side switch parameter,  $V_{CLAMP}$ , is devicedependent, but it's usually 40 V to 60 V. Therefore, with even a small 5-µH cable inductance, a high current limit can create a large demagnetization energy that the output protection stage must absorb. The input voltage can also increase during demagnetization because of the input inductance, increasing the total fault energy that must be dissipated. Most high-side switches list the inductive load energy peak, so make sure that the calculated energy from the maximum cable length and maximum current is below the rated energy. **Figure 5** below shows these values for a TI high-side switch.

# Resistive Short Circuit

A resistive short circuit occurs when debris or corrosion causes a partial short circuit or a load failure. In the short circuits described above, a low series resistance causes the current to increase until it hits the current limit. When there is some series resistance with a high current limit, there is a risk that the current will saturate before hitting the current limit. In the event of a series resistance, the output protection must have a low-enough current limit to register the short circuit as a fault event.

**Figure 6** on the following page shows a case where the series resistance limits the short-circuit current to below the output protection current limiter, so the device does not turn off the output and current flows indefinitely.

During this time, there is a high, uncontrolled current flow until the system hits thermal shutdown or a secondary method of current monitoring turns the system off. For reliability against resistive short circuits, you must either design the overall system to manage the transient

| Energy dissipation during turnoff, $E_{\text{TOFF}}$   | Single pulse, $L_{OUT} = 5$ mH, $T_{J,start} = 125^{\circ}C$     | 200 mJ |

|--------------------------------------------------------|------------------------------------------------------------------|--------|

| Energy dissipation during turnoff, $E_{\mathrm{TOFF}}$ | Repetitive pulse, $L_{OUT} = 5$ mH, $T_{J,start} = 125^{\circ}C$ | 80 mJ  |

Figure 5: Inductive energy dissipation of a TI high-side switch.

Figure 6: Resistive short circuit.

current pulse or ensure that it will shut off by minimizing the output protection current limit.

# The "<u>Improved Automotive Short Circuit Reliability</u> <u>Through Adjustable Current Limiting</u>" application note describes this event in greater detail.

### **System Interruption**

The previous sections covered how to ensure that the system will survive a short-circuit event. But even if the system does survive without damage, a short-circuit event should cause as minimal of an interruption to the system as possible.

During a short-circuit event, high current can overload the input supply and create an undervoltage lockout event for the entire system. To prevent this, it's important that the short circuit is registered as quickly as possible so to facilitate the implementation of shortcircuit protection with solutions that have a very fast response time.

To minimize the response time, many protection devices implement a fast-trip response that triggers within nanoseconds of an overcurrent event. If the fast-trip threshold is hit, the device instantly turns off to protect the supply, and then slowly ramps up the output current safely to the chosen current limit. This keeps overshoot during the short circuit from having an adverse effect on the supply.

# **Protection Considerations**

To protect against short circuits, it's best practice to use an output protection stage with an integrated current limit and inductive clamp. Typically, this protection is implemented through a high-side switch with an integrated output clamp, or through an eFuse or load switch IC with an external flyback diode.

When designing short-circuit protection, consider:

- Minimizing the current-limiting value. Lowering the current limit minimizes the energy that must be dissipated in a short circuit. Because this energy is a function of the square of current, minimizing the peak current significantly decreases the risk of failure. Keep the current limit as close to the maximum working current as possible.

- Confirming that the output protection can dissipate the required fault energy. Calculate the maximum short-circuit energy expected based on cable lengths and current limits, and check that the output protection stage will be able to safely dissipate that energy.

- Limiting input and output inductances. Inductances in series with the short circuit significantly increase the demagnetization time and total fault energy that must be dissipated.

- Guaranteeing the registration of a resistive short circuit. In the event of a resistive short circuit, ensure that either the current limit is low enough to recognize a partial fault or that there is an alternative method

of overcurrent detection (like a microcontroller) continuously monitoring the load current.

Understanding protection response times. In the event that a short circuit causes an overcurrent, there is a response time before the I<sub>LIM</sub> circuitry is able to limit the current, during which there is some overshoot. Understand how the response time will impact the maximum possible current.

By designing an output protection stage around these principles, you can safely protect an output from a short circuit and minimize the risk of damage.

#### Author: Alek Kaknevicius

#### Abstract

Reverse current occurs when current travels from output to input rather than from input to output. This chapter explains where reverse current comes from, why it can be harmful to systems and how to modify a design to protect against reverse current.

### What is Reverse Current?

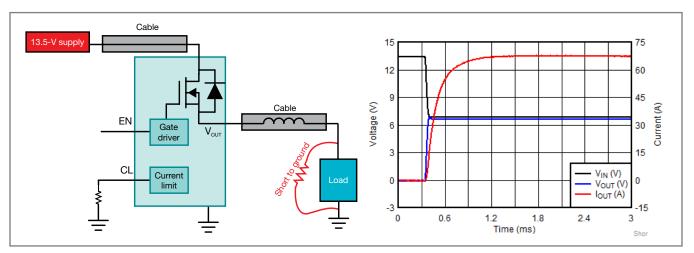

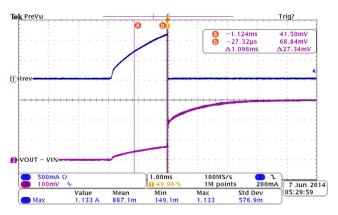

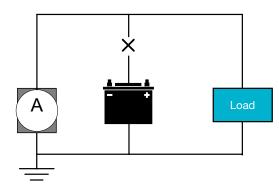

Reverse current is when there is a higher voltage at the output of a system than at the input, causing current to flow backwards through the system. There are two common sources of reverse voltage: the first is when power is disconnected from a system and the input voltage suddenly drops. During this time, a higher voltage can be left at the output, which temporarily produces reverse current. See **Figure 1**.

Figure 1: Reverse current caused by a sudden loss of power.

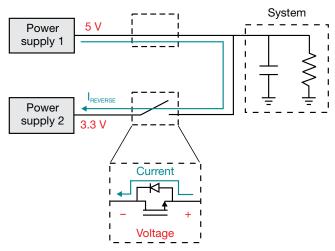

The other cause of reverse current is when a metal-oxide semiconductor field-effect transistor (MOSFET) is used for a load-switching application and the body diode becomes forward-biased.

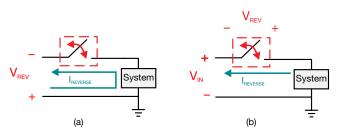

The output of a switch with a higher voltage than the input causes a reverse voltage, which is what causes reverse current. Don't confuse this with negative voltage, also known as reverse polarity. A negative voltage occurs in situations where the positive and negative terminals of a power supply are switched. In this case, what should be connected to ground actually has a voltage from the positive input to the system, as shown in **Figure 2**. This causes a different current phenomenon through the device than reverse polarity. For more information on reverse polarity protection, see <u>Chapter 5</u>.

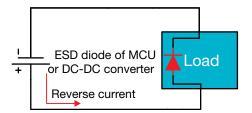

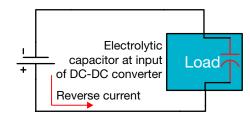

### Why Do You Need to Block Reverse Current?

Reverse current can damage internal circuitry and power supplies. Depending on the path from output

Figure 2: Reverse polarity (a); reverse voltage (b).

to input, reverse current spikes can also damage cables and connectors. If you are using a MOSFET for load-switching applications, reverse current can travel backwards through its body diode if it becomes forward-biased, because the FET output voltage is greater than the input voltage. This causes a linear rise in power dissipation across the body diode, expressed by **Equation 1**:

$$P = IV: P_D = I_{REV} \times V_{DROP}$$

(1)

where  $\mathsf{P}_{\mathsf{D}}$  is the power dissipated across the body diode,  $\mathsf{I}_{\mathsf{REV}}$  is reverse current through the device and  $\mathsf{V}_{\mathsf{DROP}}$  is the voltage drop across the body diode.

If the heat generated by the power dissipation through the device exceeds the thermal rating of the device, then combustion can occur. Therefore, it is essential to limit reverse current flow, or reverse voltage.

### When Do You Need to Block Reverse Current?

There are several applications where blocking reverse current is necessary.

### Power Multiplexing

Power multiplexing is the practice of using a switching circuit to choose one of multiple power supplies for a system, with the ability to switch between them. **Figure 3** on the following page shows this configuration.

If one of the power-supply voltages is higher than the other, then it's possible for reverse current to occur even when the other power rail has an "open" switch— one example is when using FETs to switch the power supplies. The higher voltage at the output of the open FET causes reverse current to flow from the higher-voltage power supply, through the FET body diode and into the lower-voltage power supply. **Figure 4** on the following page shows the application of 5 V to a system while the switch for the 3.3-V rail is open.

Figure 3: Power multiplexing configuration.

You can see in **Figure 4** that with a simple FET solution for the switch, reverse current is able to flow through the FET body diode, even when the switch is open.

Figure 4: Reverse current caused by power multiplexing.

# ORing

ORing is similar to power multiplexing, except that rather than selecting one supply to power the system, the highest voltage always powers the system. Reverse current blocking is also necessary here, because each ORing switch sees reverse current when the other switch is closed.

# Sudden Loss of Input Power

When a closed switch suddenly loses power on its input, there is the potential for reverse current. If the capacitance on the output of the switch is larger than the input, then the voltage on the output will decay more slowly. This means that while power is decaying, the voltage on the output of the switch will fall more slowly than the input. During this period, the voltage on the output of the switch will be larger than the input, so reverse current will flow across the switch. To avoid this, you should have a switch with reverse current blocking, or a larger input than output capacitance.

In some systems, a supercapacitor holds up the output when the input supply drops. This is sometimes referred to as a "last gasp" circuit, which allows the system to safely power down. It's also a good idea to have reverse current protection here in order to protect any upstream supplies or components.

# How Do You Block Reverse Current?

There are several ways to block reverse current.

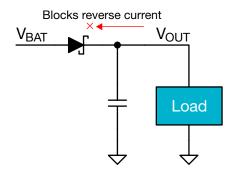

# Diodes

Diodes are great for high-voltage, low-current applications. However, diodes cause a forward-voltage drop that increases the total power dissipation in the system and drops the power supply by 0.6 V to 0.8 V. This can cause decreased efficiency in the system and a shortened battery life. A popular alternative is the use of a Schottky diode. They have lower forward-voltage drops, but are more expensive and have higher reverse current leakage, which could cause problems for the system such as supply or battery damage.

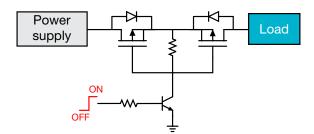

# Back-to-Back MOSFETs

Using back-to-back MOSFETs is a powerful option, since it offers current blocking in both directions when the MOSFETs are turned off. In comparison to the diode solution, there is a lower voltage drop from the power supply to the load. However, this implementation takes up a larger amount of space on the board, requiring several components to build, as shown in **Figure 5** on the following page.

Aside from the large solution size and bill-of-materials count, this solution also doubles the on-resistance of a single MOSFET solution and does not provide

Figure 5: Reverse current blocking with back-to-back MOSFETs disabled.

any reverse current blocking when the MOSFETs are turned on.

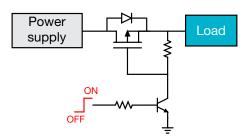

# Backwards MOSFET

If a MOSFET is positioned so that the body diode is facing from input to output, then there will be no reverse current flow when the MOSFET is switched off (open) (see Figure 6).

Figure 6: Reverse current blocking using a single MOSFET disabled.

The disadvantage with this solution is that it is not possible to switch the supply off, since there is always a diode path between the source and the load. This is a preferable status for diode ORing but not so much for power multiplexing because you may need to prioritize a lower voltage supply, such as when the main supply for a system is a lower voltage but the backup battery is a higher voltage.

With an ORing circuit, the battery will power the system until the voltage has been drained to below the main supply voltage. A power multiplexing circuit will prevent the battery from being used until the system decides to switch over to the backup battery.

# Switching the MOSFET Body Terminal

To block reverse current with a single MOSFET, the body terminal must either be biased to the highest supply or ground, depending on if the FET is P-channel or N-channel. This is usually not possible for a discrete MOSFET, since the body terminal is not typically accessible.

# Power Switches that Block Reverse Current

Several types of power switches are capable of blocking reverse current.

# Load Switches

Load switches integrate reverse current blocking by switching the body terminal of the internal MOSFET. This allows the device to have a low on-resistance while still providing protection to the supply. If the load switch is off, then reverse current is always blocked.

Some devices offer always-on reverse current blocking, which will turn off the device if the output voltage is greater than the input voltage by a certain voltage threshold. The disadvantage with an always-on reverse current blocking scheme is that the output voltage needs to be greater than the input voltage before the device turns off, so some amount of reverse current will flow through the device before this occurs. **Figure 7** shows an example of the expected reverse current through a load switch before reverse current blocking is enabled.

**Figure 7:** Full-time reverse current protection ( $V_{IN} = 3.0$  V,  $V_{OUT}$  ramp up from 3.0 V to 3.3 V).

# eFuses

With eFuses, a back-to-back MOSFET implementation is most common due to the MOSFETs' higher voltage capability. In some devices, both MOSFETs are integrated into the device, but in others, there is a pin for driving an external second FET to create a back-toback configuration. Similar to load switches, there are some eFuses that come with always-on reverse current blocking by monitoring the difference between  $V_{\rm OUT}$  and  $V_{\rm IN}$ , while others only provide reverse current blocking when turned off.

### Power Multiplexers

Integrated power multiplexers safely handle power multiplexing applications so that reverse current does not flow from one supply into the other. Current power multiplexers adopt both the back-to-back and body terminal configurations, and all power multiplexers have reverse current blocking.

# Ideal Diodes

Ideal diodes are controllers that drive an external MOSFET with the body diode facing from supply to load. These devices will automatically detect the input and output voltage difference to always enable reverse current blocking while maintaining a low on-resistance.

# Conclusion

Applications such as power multiplexing or a loss of power can lead to a reverse voltage event that will induce reverse current. This can cause damage to both power supply and system. A TI power switch is both a size- and cost-effective solution helping prevent damage from reverse current. The TI power-switch portfolio has a variety of devices with different specifications for reverse current protection, making them a good fit for a wide variety of applications.

#### Author: Karikalan Selvaraj

#### Abstract

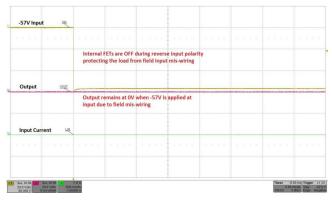

Many front-end power system designs require protection from damage caused by a reverse-connected input power supply, a reversed battery connection or miswiring of field power-supply lines.

Schottky diodes are the traditional choice for protection against reverse polarity conditions, but the associated power loss from the forward conduction requires careful thermal management, leading to increased system cost and space. Plus, increased demand for higher power density necessitates better and more efficient reverse polarity protection methods.

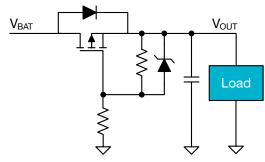

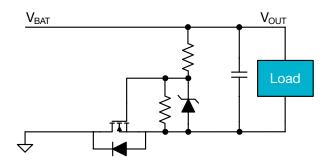

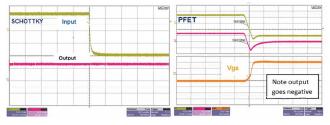

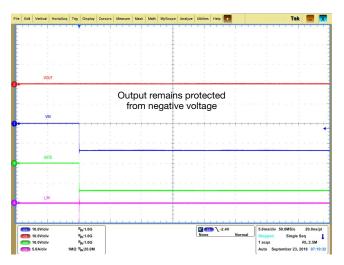

#### **Reverse Polarity Protection Overview**