# Freescale Semiconductor Users Guide

MPC5121EQRUG Rev. 6, 09/2010

# MPC5121e Hardware Design Guide

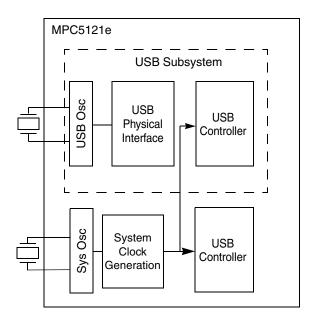

This document is a collection of application examples and practical information that relate to hardware design issues for the MPC5121e and other microprocessors in this family of devices. This document covers use of the onboard DRAM controller, practical information on Universal Serial Bus issues, and a description of the method used to initially configure the microcontroller at the release of reset.

Configuring the microcontroller for proper operation at the release of reset is done by reading the external bus while reset is released. This section explains how the values read set up the initial memory map, the configuration of the external memory bus and various clock speeds.

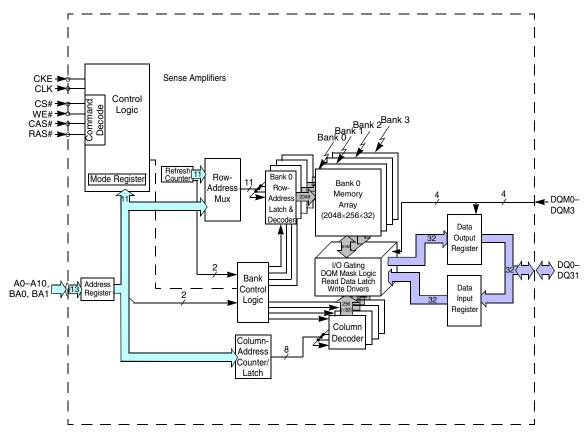

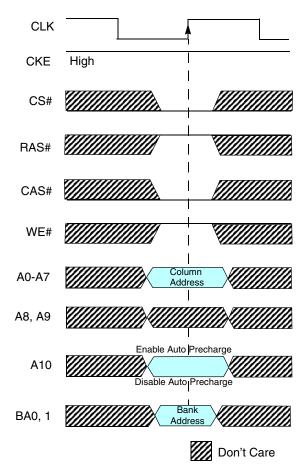

The DRAM controller section explains how to set up the timing of the high speed memory interface to the Synchronous DRAM memory. Also, this section handles the protocol between the SDRAM memory and the microcontroller.

The USB section covers hardware issues related to external physical interfaces, how the physical interfaces are connected to the microprocessor, and PC board layout issues related to USB signals.

In-depth material about using the MPC5121e is also available in Freescale's reference manual. See the Freescale Web site: http://freescale.com

#### **Topic Reference**

| MPC5121e Hardware Design Guide                    |   |

|---------------------------------------------------|---|

| MPC5121e Clocks                                   | 3 |

| Understanding the Reset Configuration Word for th | e |

| MPC5121e                                          | į |

| MPC5121e DRAM Controller 4                        |   |

| MPC5121E USB9                                     | į |

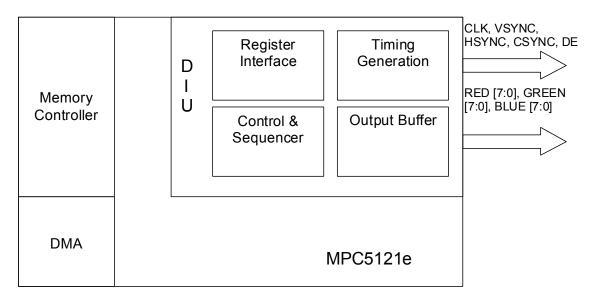

| MPC5121e DIU Hardware Interface 10                | 9 |

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com

# **Revision History**

| Date    | Revision<br>Level | Description                                                                                                                                                                                                                                                                                      | Page<br>Number(s) |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 11/2008 | 0                 | Initial release.                                                                                                                                                                                                                                                                                 | N/A               |

| 12/2008 | 1                 | Added reset configuration word section.                                                                                                                                                                                                                                                          | N/A               |

| 02/2009 | 2                 | Added DRAM controller and USB sections.                                                                                                                                                                                                                                                          | N/A               |

| 03/2009 | 3                 | Updated DRAM controller section.                                                                                                                                                                                                                                                                 | 63–64, 84–86      |

| 04/2009 | 4                 | Added DIU section.                                                                                                                                                                                                                                                                               | N/A               |

| 06/2009 | 5                 | Added information about use of DRAM Controller Initialization Tool.  Corrected information in 2.5.2, "RST_CONF_PCIARB," in same section.                                                                                                                                                         | 85–90<br>33       |

| 09/2010 | 6                 | Corrected information in "Understanding the Reset Configuration Word for the MPC5121e," section 2.2, "Boot Interface Control," about reset parameter RST_CONF_ROMLOC.  Same changes in "Understanding the Reset Configuration Word for the MPC5121e," Appendix A: table 5, table 6, and table 7. | 29<br>36, 37, 39  |

#### **Freescale Semiconductor**

#### **User Guide**

# MPC5121e Clocks

by: Rakesh Chennamadhavuni MSG Applications Engineering

This section discusses the clock structure, relationships between various clocks, and how different module clocks are derived on the MPC5121e.

## 1 Introduction

The wide range of applications supported by the MPC5121e require a complex clocking structure with different primary clock domains derived from four separate oscillator sources. Internal PLLs and clock dividers allow generation of a wide range of clock references. Each peripheral clock may be individually controlled; in other words, gated individually or scaled in frequency to minimize total power consumption of the device. The MPC5121e system requires a system-level clock input: SYS\_XTALI. This clock input may be driven directly from an external oscillator or with a crystal using the internal oscillator. The SYS\_PLL is programmed at reset by the reset configuration word (RST\_CONFIG) sampled at the rising edge

#### **Contents**

| 1   | Intro  | duction                                            | . 3 |

|-----|--------|----------------------------------------------------|-----|

| 2   | Initia | lization and Configuration                         | . 6 |

|     | 2.1    | Reset Sequences                                    | . 6 |

|     | 2.2    | Enable/Disable Clock to Individual Modules         | . 8 |

|     | 2.3    | Changing the Frequency of the Clock                | . 8 |

| 3   | Mea    | surements                                          | . 9 |

| 4   | PSC    | Clock Structure                                    | 10  |

|     | 4.1    | PSC in UART Mode                                   | 10  |

|     | 4.2    | PSC in Codec Mode                                  | 11  |

|     | 4.3    | Introduction                                       |     |

|     | 4.4    | Configuring and Observing PSC_MCLK_OUT             | 12  |

| 5   | PSC    | in AC97 Mode                                       | 14  |

| 6   | PSC    | in SPI Mode                                        | 15  |

| 7   | CAN    | Module Clock                                       | 15  |

| 8   | Gen    | eral Clock and Power Circuitry Layout Guidelines . | 17  |

|     | 8.1    | Clock Circuitry                                    | 17  |

|     | 8.2    | Power Circuitry                                    | 17  |

|     | 8.3    | Ferrite Beads in Filtering                         | 19  |

| App | endix  | A                                                  | 20  |

|     | A.1    | Example Code for Pin Multiplexing of I/O Pads      | 20  |

|     | A.2    | I/O Control Register Table for Clocks              | 20  |

|     | A.3    | Block Diagram of Various Clock Structures in       |     |

|     |        | MPC5121e                                           | 22  |

| App | endix  | B References                                       | 23  |

#### Introduction

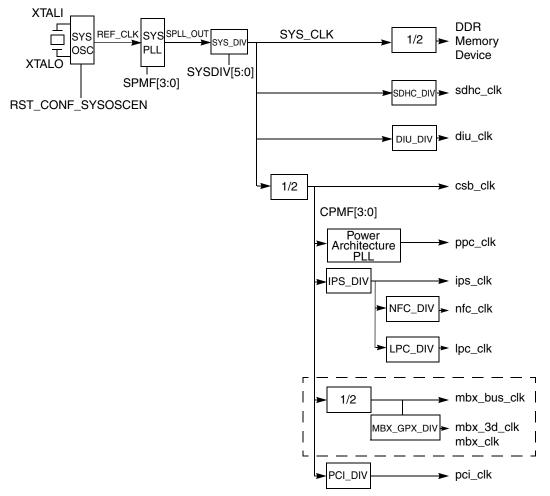

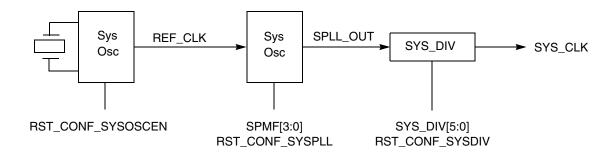

(de-assertion) of power-on reset. The SYS\_PLL clock is then divided (SYS\_DIV) and used as a reference to the MPC5121e cores and peripherals.

The system oscillator may be disabled so that an externally generated clock may be used as a reference. This can be performed by setting the RST\_CONF\_SYSOSCEN in the reset configuration word (RST\_CFG) at reset. There is a separate oscillator for the independent real-time clock (RTC) system. The USB PHY contains its own oscillator with the input USB\_XTALI and an embedded PLL. The SATA PHY contains its own oscillator with the input SATA XTALI and an embedded PLL.

#### The four oscillator sources are:

- 1. XTAL for system: This clock input may be driven directly from an external oscillator or with a crystal using the internal oscillator. This is selected by RST\_CONFIG\_SYSOGEN in the reset configuration word.

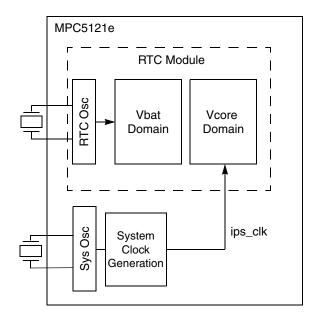

- 2. RTC oscillator clock: The RTC module contains circuitry on two clock and voltage domains. The  $V_{bat}$  voltage domain circuitry operates from a 32.768 kHz oscillator input. The  $V_{Core}$  domain or programming interface operates from the IPS CLK.

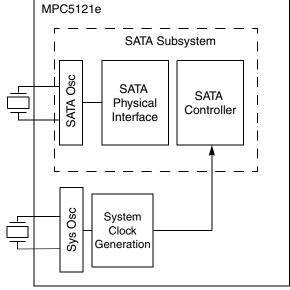

- 3. SATA oscillator clock: The SATA interface requires a 25 MHz crystal input that is independent of the system oscillator. The 1.5 GHz clock required by the SATA physical interface is generated by this 25 MHz input.

- 4. USB oscillator clock: The USB 2.0 specification requires a clock operating at up to 480 MHz. This clock is derived from a dedicated oscillator input of 24 MHz and multiplied within the USB physical interface for USB transmission. The USB-OTG controller operates from the IPS\_CLK interface

- Note: A 24 MHz clock is used for internal PHY in this case. External PHYs may have a different value.

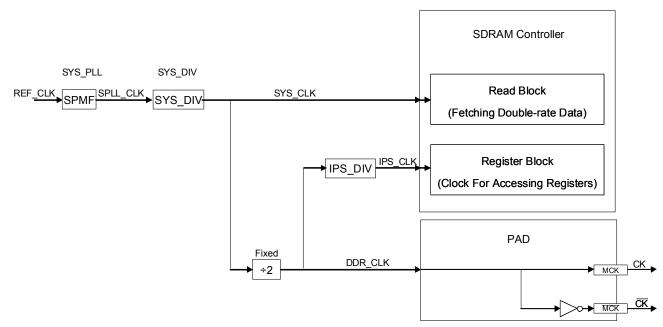

Figure 1. Diagram of Clock Structure

Below is a table of the modules connected to each individual clock.

**Table 1. Clocks and Associated Modules**

| Module Reference Clock | Module(s)                                                                                                                                                                                    |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSB_CLK                | AXE, CFM, CSBARB, DMA, MEM, PPC_PLL, PCI <sup>1</sup> , PCI_DMA, PCI_IOS                                                                                                                     |

| IPS_CLK                | BDLC, DIU <sup>1</sup> , EMB <sup>1</sup> , FEC, FIFOC, FUSE, GPIO, I2C, IPIC, MSCAN <sup>1</sup> , PATA, PMC, RTC <sup>1</sup> , SAP <sup>1</sup> , SATA, SDHC, SPDIF, TPM, USB0, USB1, WDT |

| LPC_CLK                | EMB <sup>1</sup> , LPC                                                                                                                                                                       |

| NFC_CLK                | EMB <sup>1</sup> , NFC                                                                                                                                                                       |

| PPC_CLK                | E300                                                                                                                                                                                         |

| REF_CLK                | MSCAN <sup>1</sup> , SYS_PLL                                                                                                                                                                 |

| MBX_CLK                | MBX                                                                                                                                                                                          |

| MBX_3D_CLK             | MBX                                                                                                                                                                                          |

MPC5121e Clocks, Rev. 0

#### **Initialization and Configuration**

Table 1. Clocks and Associated Modules (continued)

| Module Reference Clock | Module(s)        |

|------------------------|------------------|

| DDR_CLK                | MDDRC, PRIMAN    |

| PCI_CLK                | PCI <sup>1</sup> |

| RTC_CLK                | RTC              |

| SATA_OSC               | SATA_PHY         |

| USB_OSC                | USB_PHY          |

Indicates that the module has more than one reference clock.

# 2 Initialization and Configuration

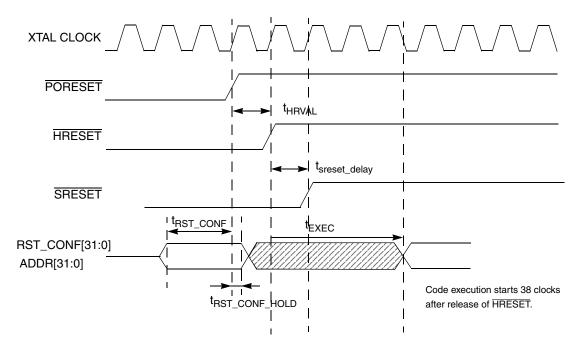

## 2.1 Reset Sequences

- 1. The PORESET will sample the reset configuration word.

- 2. The HRESET is qualified with respect to power-on reset after a certain number of clock cycles has passed (see Table 2).

- a) HRESET provides a mechanism to initialize all clocks and peripherals to the initial values.

- b) This flow does not sample the reset configuration word.

- 3. SRESET provides a mechanism to shorten the boot flow by bypassing initialization of boot peripherals and clocks.

During the power-up sequence the PORESET pin must be asserted by an external device for a minimum of 32 XTAL clock cycles. The oscillator input (XTALI) must be stable prior to PORESET de-assertion. After PORESET has been qualified and released, the HRESET flow is started.

Figure 2. Power-On Reset Behavior

**Table 2. Reset Option Clock Cycles**

| Symbol                     | Description                                                                | Value<br>(clock<br>cycles) |

|----------------------------|----------------------------------------------------------------------------|----------------------------|

| t <sub>HRVAL</sub>         | Time HRESET is asserted after it has been qualified                        | 26800                      |

| t <sub>RST_CONF</sub>      | Time reset configuration must be asserted prior to de-assertion of PORESET | 16                         |

| t <sub>RST_CONF_HOLD</sub> | Reset configuration hold time                                              | 4                          |

| t <sub>EXEC</sub>          | Time between de-assertion and core execution                               | TBD                        |

| tSRESET_DELAY              | Time delay between de-assertion of HRESET and the de-assertion of SRESET   | 16                         |

The default modules to which clocks should be enabled after reset are: CFG, LPC, NFC, TPR, PCI, DDR, MEM, and MBX\_BUS. The clocks CFG, LPC, NFC, DDR, and MEM should be enabled at all times for correct operation. TPR must be set for all normal user modes.

The reset configuration word controls the values (frequencies) of the default clocks after boot-up. Some of the very important clock configuration fields that reset configuration word controls are mentioned in Table 3. Refer also to the reset values of the SCFR1 and SCFR2 registers, to calculate the initial frequencies.

#### **Initialization and Configuration**

| Table 3. I | Reset | Configuration | Word |

|------------|-------|---------------|------|

|------------|-------|---------------|------|

| Reset Parameter    | Signal                   | Description                 |

|--------------------|--------------------------|-----------------------------|

| RST_CONFIG_COREPLL | EMB_AD[13:10]            | Core PLL Multiply Factor    |

| RST_CONFIG_SYSPLL  | EMB_AD[26:23]            | System PLL Multiply Factor  |

| RST_CONFIG_SYSOGEN | EMB_AX02                 | Oscillator Bypass Mode      |

| RST_CONFIG_SYSDIV  | LPC_AX[3], EMB_AD[31:27] | System PLL Divider          |

| RST_CONFIG_PCI66EN | EMB_AD[7]                | Enable 66 MHz PCI Operation |

See the Reset chapter in the MPC5121e reference manual for more information. Also see the Reset section of this document (this section is in progress and will be added soon).

#### 2.2 Enable/Disable Clock to Individual Modules

The clocks to some individual modules can be enabled or disabled. This can be done by either setting (for enable) or clearing (for disable) the corresponding bit in the SCCR1 or SCCR2 register.

Example: If you want to disable the clock to the I<sup>2</sup>C module, then clear the bit I2C\_EN in the SCCR2 register. If you want to enable the clock to the I<sup>2</sup>C module, then set the bit I2C\_EN in SCCR2.

#### Example Code:

```

// Enable the I2C clock (this field is in SCCR2 register):

SET (I2C_EN) in IMMR+CLOCK_MODULE_BASE+SCCR2 i.e.

Write 1 in I2C_EN field at IMMR + 0x000_0F00+ 0x0000_0008.

// Disable the I2C clock.

CLEAR (I2C_EN) in IMMR+CLOCK_MODULE_BASE+SCCR2 i.e.

Write 0 in I2C EN field at IMMR + 0x000 0F00+ 0x0000 0008.

```

#### NOTE

Disabling the clock to a module will only disable the clock to that module — it does not have any effect on the clock itself. For the chip to operate correctly some clocks have to be enabled at all times.

#### NOTE

SCCR1 and SCCR2 registers are in the Clocks module (refer to the MPC5121e Reference manual).

# 2.3 Changing the Frequency of the Clock

The frequency of the basic clocks can be changed by programming the corresponding fields in the SCFR1, SCFR2, and SPMR registers. Module-derived clock frequencies such as PSC\_MCLK\_OUT and MSCAN\_CLK can be modified by registers in these modules.

Example: If you want to divide the IPS\_CLK by 4 write 100'b into the IPS\_DIV field in the SCFR1 register —

Example Code:

Write 4 (in IPS\_DIV field) in IMMR+CLOCK\_MODULE\_BASE+SCFR1 i.e. Write 4 in IPS DIV field at IMMR + 0x0000 0F00+ 0x0000 000C.

**Table 4. Register Fields and Associated Clocks**

| Register | Field          | Туре       | Input Clock | Output Clock   |

|----------|----------------|------------|-------------|----------------|

| SPMR     | SPMF           | Multiplier | REF_CLK     | SPLL_OUT       |

| SPMR     | CPMF           | Multiplier | (SYS_CLK/2) | PPC_CLK        |

| SCFR2    | SYS_DIV        | Divider    | SPLL_OUT    | SYS_CLK        |

| SCFR1    | IPS_DIV        | Divider    | (SYS_CLK/2) | IPS_CLK        |

| SCFR1    | PCI_DIV        | Divider    | (SYS_CLK/2) | PCI_CLK        |

| SCFR1    | MBX_GPX_DIV    | Divider    | MBX_BUS_CLK | MBX_(3D)_CLK   |

| SCFR1    | LPC_DIV        | Divider    | IPS_CLK     | LPC_CLK        |

| SCFR1    | NFC_DIV        | Divider    | IPS_CLK     | NFC_CLK        |

| SCFR1    | DIU_DIV        | Divider    | SYS_CLK     | DIU_CLK        |

| SCFR2    | SDHC_DIV       | Divider    | SYS_CLK     | SHDC_CLK       |

| PnCCR    | PSCn_MCLK_DIV  | Divider    | 1           | PSC_MCLK_OUT   |

| MnCCR    | MSCANn_CLK_DIV | Divider    | 1           | CAN_SOURCE_CLK |

<sup>&</sup>lt;sup>1</sup> The input clock in this case depends on the multiplexer fields in those registers.

## 3 Measurements

Refer to the section "Understanding the Reset Configuration Word for the MPC5121e" in this document for more information. *This section has not yet been published*.

#### NOTE

Special note on observing the PPC core clock: the internal PPC clock can be brought out on one of the TPA pins.

Apart from the common pin muxing procedure, there is an additional step needed to bring the PPC clock out. Depending on what you want to observe, set ECLK or SBCLK accordingly in HID0.

Table 5. Using HID0[ECLK] and HID0[SBCLK] to Configure CLK\_OUT

| HRESET   | ECLK | SBCLK | CLK_OUT                                                 |

|----------|------|-------|---------------------------------------------------------|

| Asserted | X    | Х     | Bus clock (small pulse for every rising edge of SYSCLK) |

| Negated  | 0    | 0     | Clock output off                                        |

|          | 0    | 1     | Core clock divided by two                               |

|          | 1    | 0     | Core clock                                              |

|          | 1    | 1     | Bus clock                                               |

HID0 is a special purpose register and can only be changed in supervisor mode via special instructions. The clock\_out\_1 and clock\_out\_2 signals are further divided down before they go to the TPA pads. Refer

MPC5121e Clocks, Rev. 0

Freescale Semiconductor

#### **PSC Clock Structure**

to the TPA select table in appendix A. Refer to Freescale document MPCFPE32B, *Programming Environments Manual for 32-Bit Implementations of the PowerPC*<sup>TM</sup> *Architecture*, for more information about the special commands to be used.

A brief explanation of observing PSC\_MCLK\_OUT is mentioned in Section 4, "PSC Clock Structure."

#### 4 PSC Clock Structure

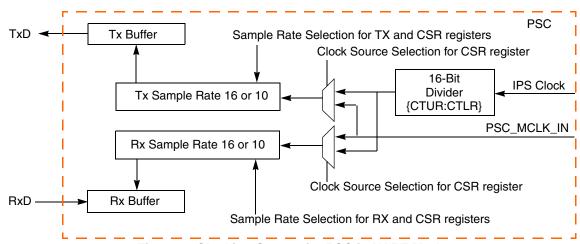

#### 4.1 PSC in UART Mode

The transmit and receive baud rate for the PSC in UART mode can be generated from either the internal or external clock.

- The source of the internal clock is IPS CLK.

- The source of the external clock is PSC MCLK IN.

Both clocks are divided by the prescaler. In addition, the ips\_clk is further divided by the 16-bit timer/counter. As shown in Figure 3 the ips\_clk is divided by the timer/counter and then by a prescaler of 16 or 10, whereas the PSC\_MCLK\_IN is divided only by a prescaler of 10. Transmit and receive clocks are independent of each other. The transmit clock is independent from the receive clock and vice versa. In other words, you can choose the internal clock for the transmitter and the external clock for the receiver. The clock source and prescaler for both transmitter and receiver are selected by setting the appropriate bits in the RCS and TCS fields in the Clock Select Register (CSR) in the PSC module.

Figure 3. Clocking Source for PSC in UART Mode

The baud rate depends on the CSR register and the CTR register. The baud rate of the TX signal is calculated as follows:

**Table 6. TCS Baud Rate Calculation**

| Transmit Clock Select | Baud Rate                 |

|-----------------------|---------------------------|

| 0000-1101             | ips_clk / (16 × CT[0:15]) |

| 1111                  | ips_clk / (10 × CT[0:15]) |

| 1110                  | psc_mclk_in / 10          |

MPC5121e Clocks, Rev. 0

| Table 7 | RCS | Raud | Rate | Calculation | า |

|---------|-----|------|------|-------------|---|

|         |     |      |      |             |   |

| Receive Clock Select | Baud Rate                 |

|----------------------|---------------------------|

| 0000–1101            | ips_clk / (16 × CT[0:15]) |

| 1111                 | ips_clk / (10 × CT[0:15]) |

| 1110                 | psc_mclk_in / 10          |

#### NOTE

Transmit clock and receive clock are independent of each other. CSR, CTUR and CTLR registers are in the PSC module (refer to the MPC5121e reference manual).

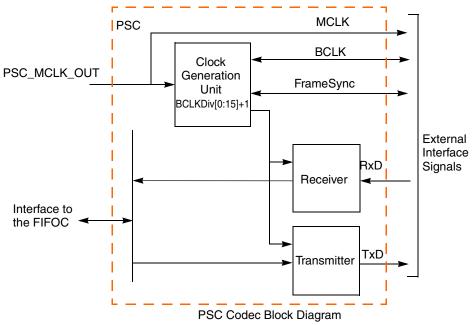

#### 4.2 PSC in Codec Mode

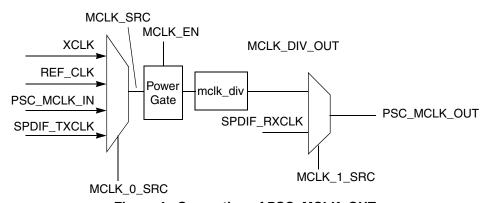

PSC in codec mode uses PSC\_MCLK\_OUT. A brief introduction to PSC\_MCLK\_OUT is given below.

Figure 4. Generation of PSC\_MCLK\_OUT

#### 4.3 Introduction

The PSC\_MCLK\_OUT can be generated from five clock sources. The generation of the clocks is divided into two stages.

- 1. First is the divider stage, where one of four clock sources is selected by the MCLK\_0\_SRC field in PnCCR. Then this clock is further divided by the divider, if that clock is enabled by MCLK\_EN. If MCLK\_EN has been cleared, then the clock is disabled and the input clock source will not reach the divider.

- 2. In the second stage either the divided clock source or spdif\_rxclk can be selected as the final PSC\_MCLK\_OUT, depending on the value of MCLK\_1\_SRC. SPDIF\_RXCLK bypasses the divider.

SPDIF\_TXCLK and PSC\_MCLK\_IN are external clocks and SPDIF\_RXCLK is generated by the SPDIF module. External clocks should be provided if these are used as clock sources for generation of PSC\_MCLK\_OUT. External clock sources can be provided from the appropriate pads. Pin muxing for the pads should be done so that these clocks can reach internally into the chip. See appendix A for pin muxing details about SPDIF\_TXCLK and PSC\_MCLK\_IN, and example code for pin muxing.

#### **PSC Clock Structure**

# 4.4 Configuring and Observing PSC\_MCLK\_OUT

Below is the simplest procedure to observe PSC MCLK OUT.

Configuring and observing PSC MCLK OUT is a seven step process:

- 1. Select the proper clock source by configuring MCLK 0 SRC field in the PnCCR register.

- 2. Clear the MCLK EN field in the PnCCR register.

- 3. Write the appropriate divide value into the PSC MCLK DIV field in the PnCCR register.

- 4. Set the MCLK EN field in the PnCCR register.

- 5. Choose the proper clock source by configuring the MCLK 1 SRC field in the PnCCR register.

- 6. Write 0x0100 8100 to the SICR register in the PSCn module.

- 7. Perform pin muxing for signal 4 in the selected PSC. Now the PSC\_MCLK\_OUT can be observed at pin PSCn 4.

Refer to appendix A for pin muxing details. In the above case it is assumed that all clock sources are provided.

Example code for PSC0 (this is a simple way of observing the clock; depending on the mode of implementation, there may be several other ways):

Assumptions in this example: Using SYS CLK in the first stage and MCLK DIV in the second stage.

```

// Pin muxing (selecting function) psc0 4 from PSC0 4 I/O Pad.

Write 0 in FuncMux field in IMMR+IOCTL BASE ADDRESS+IOCTL PSCO 4 i.e

Write 0 in FuncMux field in IMMR+0x0A000+0x0304.

// Select one from four clock sources in first stage. (Here sys_clk is used)

Write 0 in MCLK 0 SRC in IMMR+CLOCKS MODULE ADDRESS+POCCR i.e.

Write 0 in MCLK 0 SRC field at IMMR+0x0000 0F00+0X0000 001C.

// The divider value should be changed after disabling the mclk en

Clear (MCLK 0 EN) in IMMR+CLOCKS MODULE ADDRESS+POCCR i.e.

Write 0 in MCLK 0 EN field at IMMR+0x0000 0F00+0X0000 001C.

// Changing the divider value

Write (divider value in PSC0 MCLK DIV field) in IMMR+CLOCKS MODULE ADDRESS+POCCR i.e.

Write (divider value in PSC0_MCLK_DIV) at IMMR+0x0000_0F00+0X0000_001C.

// Enabling the mclk en

SET (MCLK 0 EN) in IMMR+CLOCKS MODULE ADDRESS+POCCR i.e.

Write 1 in MCLK 0 EN field at IMMR+0x0000 0F00+0X0000 001C.

// Select one from two clock sources in second stage.

Write 0 in MCLK_1_SRC in IMMR+CLOCKS_MODULE ADDRESS+POCCR i.e.

Write 0 in MCLK_1_SRC field at IMMR+0x0000_0F00+0X0000 001C.

// Perform this operation.

Write 0x01008100 into IMMR+ PSC0 BASE ADDRESS+ PSC SICR i.e.

Write 0x0100 8100 into IMMR+ 0x0001 1000+0x0000 0040.

```

MPC5121e Clocks, Rev. 0

12

Freescale Semiconductor

#### NOTE

PnCCR registers are in the Clocks module (refer to the MPC5121e reference manual).

Figure 5. Block Diagram and Signal Definition for Codec Mode

Depending on the value of the GENCLK field in the SICR register in the PSC module:

- The serial BCLK and the FrameSync can be inputs that come from an external codec device.

- They can be internally generated by the PSC and provided as outputs to the external device, under control of bit SICR[GenClk].

If the bit GenClk in the SICR register is set to zero:

• The BCLK and the FrameSync are inputs. In this case the FrameSync width can be anything from one BCLK period up to the total FrameSync length/period minus one BCLK.

If the bit GenClk in the SICR register is set to one:

• If the GenClk bit is set to one, the PSC generates the BCLK and the FrameSync signal. The source for the internal clock generation is the PSC\_MCLK\_OUT provided by the clock module.

The PSC provides the MCLK\_OUT clock to the external codec divided independently, no matter whether the PSC is configured as a master (provide BCLK and FrameSync) or as a slave (receive the clock signals). Therefore there is no need for an external crystal for the external device.

Each PSC consists of a CCR register to generate a BCLK and a FrameSync signal. If the PSC is configured as a master and MCLK is available, the PSC generates both clock signals, independent of whether the transmitter or receiver is enabled or not. If the PSC is configured as SPI master mode, the BCLK is only generated if the transmitter and receiver are enabled and TX data is available in the TX FIFO.

$$BCLK = \frac{MCLK}{BCLKDiv[0:15] + 1}$$

MPC5121e Clocks, Rev. 0

FrameSync Length = Frame SyncDiv[0:7]+1

When the FrameSync is an output, the CTUR register can program the pulse width. This register defines the number of BCLK cycles while the FrameSync signal is active. The default reset value for this register is 0x00. Therefore, the default FrameSync width is one BCLK.

Frame sync width = CTUR[0:7] + 1

#### NOTE

FrameSync width CTUR: Defines the number of BCLK while the FrameSync is active.

FrameSync length CCR[FrameSyncDiv]: Defines the number of BCLK until the next frame starts.

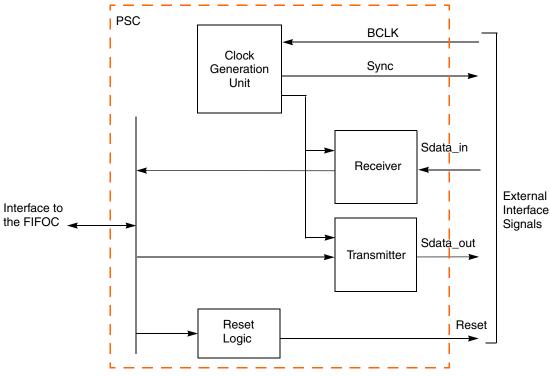

# 5 PSC in AC97 Mode

Figure 6. PSC AC97 Block Diagram

The PSC receives the BCLK from the external AC97 codec and provides the associated frame signal. In AC97 mode, the clock and frame relations are fixed.

- The BCLK is an input from the external codec.

- The PSC divides BCLK by 256 to generate a frame pulse (Sync) that is high for 16 BCLK cycles.

Therefore, the CCR register and the SICR[GenClk] bit are not used.

## 6 PSC in SPI Mode

In SPI master mode:

- The BCLK (SCLK) frequency is generated by dividing down the MCLK frequency.

- The DSCLK defines the delay between the SS going active and the first BCLK (SCK) clock pulse transition. The DSCLK delay is created by dividing down the MCLK frequency. The delay between consecutive transfers is created by dividing down the IPS CLK clock frequency.

- DTL stands for length of delay after transfer. The counter/timer determines the length of time the PSC delays after each serial transfer (the length of time that SS stays high/inactive between consecutive transfers).

Delay after transfer can be used to ensure that the deselect time requirement is met (for peripherals that have such a requirement). Some peripherals must be deselected for a minimum period of time between consecutive serial transfers.

$$DSCKL Delay = \frac{CCR[0:7] + 1}{MCLK}$$

$$DTL = \frac{CT[0:15] + 2}{IPS\_CLK Frequency} + \frac{3}{MCLKFrequency}$$

where CT[0:7] = CTUR[0:7]CT[8:15] = CTLR[0:7]

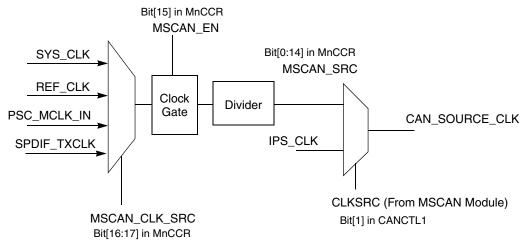

## 7 CAN Module Clock

The CAN\_SOURCE\_CLK can be generated from five clock sources. The generation of the clocks is divided into two stages.

- 1. The first stage is the divider stage, where one of four clock sources is selected by the MSCAN\_CLK\_SRC field from the MnCCR register. Then this clock is further divided by the divider, as long as that clock is enabled by MSCAN\_EN. If the clock is disabled by clearing MSCAN\_EN then the input clock source will not reach the divider.

- 2. In the second stage either the divided clock source or IPS\_CLK can be selected as the final CAN\_SOURCE\_CLOCK based on the CLKSRC bit in the CANCTL1 register in the MSCAN module. IPS\_CLK bypasses the divider.

SPDIF\_TXCLK and PSC\_MCLK\_IN are external clocks. External clocks should be provided if these are used as clock sources for the generation of PSC\_MCLK\_OUT. External clock sources can be provided from the appropriate pads. Pin muxing for the pads should be done so that these clocks can reach internally into the chip. Refer to Section 4, "PSC Clock Structure," for example code for pin muxing PSC\_MCLK\_IN and SPDIF\_CLK.

#### **NOTE**

The MnCCR register is in the clock module while the CANCTL1 register is in the MSCAN module.

#### **CAN Module Clock**

MnCCR: MSCAN Clock Control Register (Clocks Module) CANCTL1: MSCAN Control Register 1 (MSCAN Module)

Bit numbering is according to the Power PC notation.

psc\_mclk\_in is an external clock. spdif\_txclk is generated by SPDIF module.

Figure 7. CAN Module Clock

# 8 General Clock and Power Circuitry Layout Guidelines

# 8.1 Clock Circuitry

- The crystal oscillator is sensitive to noise from other signals and also to stray capacitances. In order to reduce the coupling between the clock traces and other high speed traces, and therefore decrease the crosstalk, it is recommended to keep the crystal oscillator away from signals with fast rise and/or fall times (< 3 ns). A separation of at least three times the trace width (five times is better) will in most cases keep the crosstalk to acceptable levels.

- In order to decrease the effect of the resonant current that flows in the circuit, the IC pins, load capacitor, crystal, and resistors should be placed close to each other, so that a smaller loop area is achieved.

- In order to minimize the board skew and achieve a reliable timing, it is recommended to use a single routing plane to route the clock traces. This routing plane must be adjacent to a solid reference plane.

- Every via has parasitic capacitance and inductance associated with it which degrades the signal quality due to impedance discontinuities and signal reflections. Usually it is the series parasitic inductance that creates the most problems. This also affects the rising edge of the signals. Therefore vias should be avoided on clock traces.

- The preferred characteristics of the load capacitor are low leakage, low effective series resistance (ESR), and stability across temperature.

- To minimize the radiations it is usually a good practice not to route traces near the edges of the PCB. Also, as a trace approaches the edge of a reference plane the impedance changes this will impact signal integrity.

# 8.2 Power Circuitry

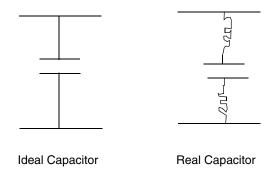

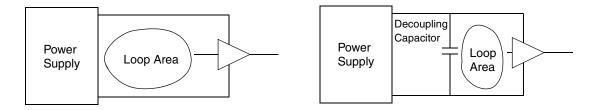

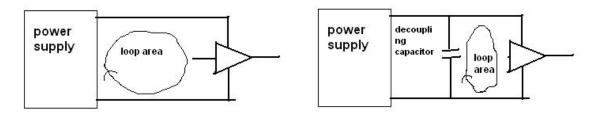

The power supply noise, if not properly controlled, causes unpredictable behavior in the circuit. The common method used to suppress this noise is to use a capacitor near each load (IC), providing a low impedance path to ground. Use of power and ground planes will greatly reduce the impedance of the power nets.

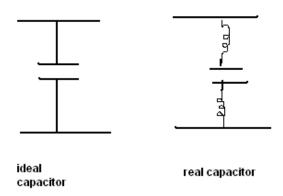

Also, a large bypass capacitor is usually placed in parallel to the power supply. In this way the problem of wiring inductance of supply traces at higher frequencies can to a certain extent be overcome. This capacitor provides a low impedance path between power and ground. But it should be noted that the capacitors are not perfect. Figure 8 shows the difference between the ideal capacitor and the real capacitor.

- 1. The real capacitor includes inductance in series on both ends. This will become a problem at higher frequencies.

- 2. Therefore it is recommended to use an array of other smaller capacitors which cover low, medium, and high frequencies. This array provides a low impedance path from power to ground over a wide range of frequency bands. (The reason it helps to use multiple small capacitors is because the inductances are then in parallel, thus lowering the inductance. Also, smaller physical parts especially SMT parts have lower inductance.)

- 3. Common problems such as power drooping can also be mitigated using this approach.

#### **General Clock and Power Circuitry Layout Guidelines**

- 4. The bypass capacitors must be placed close to the chip, so that the overall loop area is less. This will decrease the series inductance that the signal sees and also decrease the EMI.

- 5. If possible use shorter and wider traces for traces from V<sub>CC</sub> and GND. This will decrease the series inductance. (It is better to use planes.)

- 6. Common characteristics like low ESR should be considered while choosing the bypass capacitors. (It is necessary to be aware of ESR on larger capacitors as most MLC bypass capacitors already have low ESR.) Some of the factors that should be considered while calculating the value of the bypass capacitors are:

- Maximum step change in the supply current

- Maximum noise that can be tolerated

- Maximum common path impedance

- Series inductance of the supply trace

Figure 8. Ideal and Real Capacitors

Figure 9. Loop Area

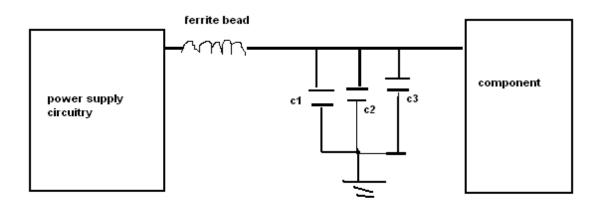

Figure 10. Circuit with Series of Arrays

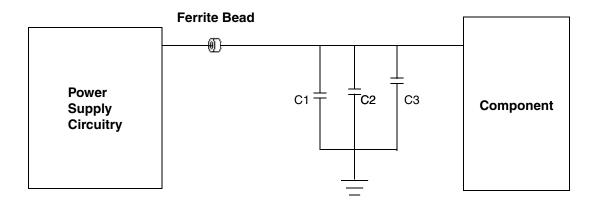

Usually a combination of ferrite beads and capacitors provides ideal filtering on supply lines.

# 8.3 Ferrite Beads in Filtering

Ferrite beads are used to suppress high frequency noise in electronic circuits. The fundamental mechanism behind this is that beads provide very low impedance at DC and relatively high impedance over a range of frequencies (which is dependent on physical characteristics).

The beads are passive components, and it should be noted that the beads don't enhance the signal quality by themselves but will suppress and isolate the noise, as well as decrease the EMI radiation. The magnetic field is contained within the beads and they cannot be detuned by external magnetic fields.

The characteristics of beads that determine their properties are:

- The frequency range that can be effectively suppressed this is determined by the type of ferrite material used.

- The level of attenuation this is determined by the physical size and shape of the bead.

Usually the impedance is directly proportional to the length of the ferrite beads.

The effectiveness of the bead deteriorates rapidly once it crosses the Curie temperature. This temperature depends on the material and may vary from 120 °C to 500 °C.

# **Appendix A**

# A.1 Example Code for Pin Multiplexing of I/O Pads

- 1. Select the desired signal.

- 2. Look up the pad I/O control register table in the manual and select the required pad.

- It should be noted that some signals are multiplexed to multiple pads. Therefore the required pad must be carefully selected.

- Pads belong to certain categories which determine the variables that can be controlled and thus their properties. All the pads contain FUNCMUX and slew rate select fields as basic fields.

- 3. Write the binary value of the desired signal in the FUNCMUX field in the chosen pad register.

Which individual fields in the pad are to be selected depends on the implementation that is being used.

It is recommended to use the maximum slew rate possible to ensure a good signal.

#### Example Code:

- 1. PSC MCLK IN is the desired signal for which pin multiplexing is done.

- 2. Looking into the I/O control register table it is observed that this signal is multiplexed in

- NFC CE0 pad

- PSC MCLK IN pad

- 3. NFC CE0 pad is chosen for pin multiplexing in this example.

- 4. Write 01 in FUNCMUX field in IMMR+IOCTL BASE ADDRESS+ IOCTL NFC CE0.

- 5. Write 01 in FUNCMUX field in IMMR+0x0A000+0X01C.

Other fields in this register are chosen depending on the specific application.

## A.2 I/O Control Register Table for Clocks

Note: This is only a subset of the entire table. Please refer to the MPC5121e reference manual (chapter I/O control) for the entire table. The Type column in the following table shows the type of the pad register. Each register type has its own configurable parameters. FuncMux and slew rate are common to all the register types. Refer to the manual for more information on the configurable parameters, their definitions, and their values.

Table 8. Pin I/O Control Register Table for Clocks

| Pin Name   | Signal Name | FuncMux<br>(FieldValue) | Туре |

|------------|-------------|-------------------------|------|

| LPC_CLK    | LPC_CLK     | 00                      | STD  |

| PATA_IOR_B | SDHC_CLK    | 01                      | STD  |

| NFC_WP_B   | SDHC_CLK    | 01                      | STD  |

| PSC8_4     | SDHC_CLK    | 01                      | STD  |

<sup>1.</sup> The number of bits for this field differs by register type.

MPC5121e Clocks, Rev. 0

#### **General Clock and Power Circuitry Layout Guidelines**

#### Table 8. Pin I/O Control Register Table for Clocks

| Pin Name    | Signal Name | FuncMux<br>(FieldValue) | Туре      |

|-------------|-------------|-------------------------|-----------|

| PSC3_4      | VIU_PIX_CLK | 10                      | STD       |

| I2C0_SCL    | I2C0_SCL    | 00                      | STD_ST    |

| I2C1_SCL    | I2C1_SCL    | 00                      | STD_ST    |

| I2C2_SCL    | I2C2_SCL    | 00                      | STD_ST    |

| SPDIF_TXCLK | SPDIF_TXCLK | 00                      | STD_ST    |

| IRQ1        | SPDIF_TXCLK | 01                      | STD_ST    |

| PSC_MCLK_IN | PSC_MCLK_IN | 00                      | STD_ST    |

| PSC0_2      | FEC_TX_CLK  | 01                      | STD_ST    |

| PSC2_4      | FEC_RXCLK   | 01                      | STD_ST    |

| PSC2_0      | USB0_CLK    | 10                      | STD_ST    |

| PSC5_0      | USB1_CLK    | 01                      | STD_ST    |

| PSC6_0      | DIU_CLK     | 10                      | STD_ST    |

| NFC_CE0_B   | PSC_MCLK_IN | 10                      | STD_PU_ST |

| LPC_CS1_B   | SPDIF_TXCLK | 01                      | STD_PU_ST |

| PCI_AD07    | FEC_TX_CLK  | 10                      | PCI       |

| PCI_AD04    | VIU_PIX_CLK | 01                      | PCI       |

| PCI_CLK     | PCI_CLK     | 00                      | PCI       |

| PCI_AD31    | USB0_CLK    | 01                      | PCI_ST    |

| PCI_AD19    | USB1_CLK    | 10                      | PCI_ST    |

| PCI_AD09    | FEC_RX_CLK  | 10                      | PCI_ST    |

| CKSTP_OUT_B | TPA         | 01                      | STD       |

| LPC_CLK     | TPA         | 01                      | STD       |

**General Clock and Power Circuitry Layout Guidelines**

# A.3 Block Diagram of Various Clock Structures in MPC5121e

**RTC Clock Generation**

SATA Clock Generation

**USB Clock Generation**

# **Appendix B References**

MPC5121e Reference Manual Rev. 3, MPC5121ERM, Freescale Semiconductor, 2008.

*High-Speed Digital Design: A Handbook of Black Magic*, Howard W. Johnson and Martin Graham, Prentice Hall, 1993.

"Effects of Plane Splits on High-Speed Signals," Dr. Abe Riazi, *Printed Circuit Design & Fab.* http://pcdandf.com/cms/content/view/3413/95/

"High Speed PCB Design," Jack Horgan, *EDAcafe*. http://www10.edacafe.com/nbc/articles/view\_weekly.php?section=Magazine&articleid=209218

#### THIS PAGE IS INTENTIONALLY BLANK

#### **Freescale Semiconductor**

**User Guide**

# Understanding the Reset Configuration Word for the MPC5121e

by: Mark Ruthenbeck Microcontroller System Group

# 1 Introduction

The MPC5121e supports a multitude of boot options, such as what interface to fetch the boot code from, at what speeds the system PLL will run, etc. In this section of this quick reference user guide we will discuss and describe the reset configuration word on the MPC5121e/5123.

#### 1.1 Abstract

This document describes the functions and clarifies the reset configuration selections for the MPC5121e/5123.

# 2 Detailed Description

The reset configuration word consists of signals inputted on the EMB bus from EMB[31..0] and the EMB AX AX[3].

The RST\_CONF word is latched when the PORESET becomes qualified. This controls the boot configuration

#### Contents

|    | intro  | oduction                                    |

|----|--------|---------------------------------------------|

|    | 1.1    | Abstract                                    |

| 2  | Det    | ailed Description                           |

|    | 2.1    | Clocking Modes and Speeds                   |

|    | 2.2    | Boot Interface Control                      |

|    | 2.3    | NOR Flash Configurations30                  |

|    | 2.4    | NAND Flash Configurations                   |

|    | 2.5    | PCI Bus Configuration33                     |

|    | 2.6    | Other System Functions                      |

| 3  | Ref    | erences                                     |

| 4  | Rev    | rision History                              |

| Αp | pendix | A Reset Configuration Word Tables           |

| Αp | pendix | B Non-Mux Mode Addressing Pin Assignment 41 |

| Αp | pendix | C Mux Mode Addressing Pin Assignments 43    |

| Ap | pendix | D NAND Flash Pin Connections 46             |

of the device. Each RST\_CONF pin must be driven appropriately to ensure that the device enters the desired mode of operation. The value latched into the device at reset may be verified by access to the RCWLR and RCWHR registers (IMMRBAR+ 0x0e00, IMMRBAR + 0x0e04).

These configuration inputs control the way the system behaves beginning at boot time. These items include:

- 1. Clocking modes and clock speeds

- 2. Boot configurations in other words, what interface to boot from, how the boot is to be handled, what address to boot from, etc.

- 3. Flash configurations for both NOR and NAND flash

- 4. PCI bus configuration

- 5. Miscellaneous items such as test modes, little endian modes, etc.

## 2.1 Clocking Modes and Speeds

**Table 1. Clocking Reset Configuration**

| Reset Parameter   | Signal                      | Description                                                                     |

|-------------------|-----------------------------|---------------------------------------------------------------------------------|

| RST_CONF_SYSOSCEN | EMB_AX02                    | Oscillator bypass mode 0 System Oscillator bypass mode 1 System Oscillator mode |

| RST_CONF_SYSPLL   | EMB_AD[26:23]               | System PLL multiply factor See, "MPC5121e Clocks," for programming options.     |

| RST_CONF_SYSDIV   | LPC_AX[3],<br>EMB_AD[31:27] | System PLL divider See, "MPC5121e Clocks," for programming options.             |

| RST_CONF_COREPLL  | EMB_AD[13:10]               | Core PLL multiply factor<br>See, "MPC5121e Clocks," for programming options.    |

#### 2.1.1 RST\_CONF\_SYSOSEN

Starting from the clock source, the RST\_CONF\_SYSOSCEN bit tells the chip if the oscillator is to be used or not. If the system is being driven from an external oscillator and not a crystal, then this bit needs to be set to 0. If the system is being driven by a crystal, then this bit must be set to 1 (enabling the oscillator).

## 2.1.2 RST\_CONF\_SYSPLL/SYS\_CONV\_SYSDIV

The RST\_CONF\_SYSPLL bit sets up the PLL multiplier, and then the RST\_CONF\_SYSDIV divides the PLL output. This output becomes the SYS\_CLK. The maximum clock speed for SYS\_CLK is 400 MHz.

Figure 1. System Clocking

Eqn. 1

$$f_{SPLL} = SPMF \times f_{REF\ CLK}$$

The system PLL multiplier factor values are shown in Table 2.

**Table 2. System PLL Multiplier Factor**

| System PLL Multiplier Factor (SPMF) | SPMF Value[3:0] |

|-------------------------------------|-----------------|

| Bypass mode — used for testing      | 0001            |

| 12                                  | 0010            |

| 16                                  | 0011            |

| 20                                  | 0100            |

| 24                                  | 0101            |

| 28                                  | 0110            |

| 32                                  | 0111            |

| 36                                  | 1000            |

| 40                                  | 1001            |

| 44                                  | 1010            |

| 48                                  | 1011            |

| 52                                  | 1100            |

| 56                                  | 1101            |

| 60                                  | 1110            |

| 64                                  | 1111            |

| 68                                  | 0000            |

The SYS\_CLK output is finally determined by the SYS\_DIV factor, as shown in Table 3.

**Table 3. System Divide Values/Factors**

| Divide Factor | SYS_DIV[5:0] Value |

|---------------|--------------------|

| 2             | 000000             |

| 2.5           | 000001             |

| 3             | 000010             |

| 3.5           | 000011             |

| 4             | 000100             |

| 4.5           | 000101             |

| 5             | 000110             |

| 6             | 001000             |

| 7             | 000111             |

| 8             | 001001             |

| 9             | 001010             |

| 10            | 001100             |

| 11            | 001011             |

| 12            | 001101             |

| 13            | 001110             |

| 14            | 010000             |

| 15            | 001111             |

| 16            | 010001             |

| 17            | 010010             |

| 18            | 010100             |

| 19            | 010011             |

| 20            | 010101             |

| 21            | 010110             |

| 22            | 011000             |

| 23            | 010111             |

| 24            | 011001             |

| 25            | 011010             |

| 26            | 011100             |

| 27            | 011011             |

| 28            | 011101             |

| 29            | 011110             |

| 30            | 100000             |

| 31            | 0111111            |

| 32            | 100001             |

| 33            | 100010             |

Understanding the Reset Configuration Word for the MPC5121e, Rev. 1

All other settings are reserved.

The SYS\_CLK or system clock is used as the primary clock source for the rest of the chip. This clock cannot exceed 400 MHz. The equation for this is:

SYS\_CLK =

$$(SPMF \times f_{REF\ CLK})/(Divide\ Factor)$$

Eqn. 2

#### 2.2 Boot Interface Control

| Reset Parameter | Signal      | Description                                                                                                             |

|-----------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| RST_CONF_ROMLOC | EMB_AD[1:0] | Selects boot device 00 LPC boot 01 NAND (NFC) boot 10 Reserved 11 NAND (NFC) boot see also definition of ST_CONF_NFC_PS |

| RST_CONF_BMS    | EMB_AD[5]   | Boot mode select Selects e300 boot vector and configures default value for LPC CS0 or NFC base address.                 |

Setting these configuration bits selects which interface the system uses for the boot code. See Section 2.4, "NAND Flash Configurations," for details about other bits that configure the balance of the interface.

#### 2.2.1 RST\_CONF\_ROMLOC

These configuration bits select the boot device. The choices are simply between the LPC (NOR flash) or NAND flash. These bits, in conjunction with RST\_CONF\_NFC\_PS, also help define the type of NAND flash.

When these bits are set for LPC, the MPC5121e selects the device that is on CS0 (chip select 0) during boot mode. Otherwise the boot sequence will be done via the NAND flash device.

| Reset Parameter | Signal | Description                                                                                                               |

|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| RST_CONF_ROMLOC |        | Selects boot device 00 LPC boot 01 NAND (NFC) boot 10 Reserved 11 NAND (NFC) boot — see also definition of ST_CONF_NFC_PS |

# 2.2.2 RST\_CONF\_BMS

| Reset Parameter | Signal    | Description                                                                                             |

|-----------------|-----------|---------------------------------------------------------------------------------------------------------|

| RST_CONF_BMS    | EMB_AD[5] | Boot mode select Selects e300 boot vector and configures default value for LPC CS0 or NFC base address. |

This bit is the boot mode select (BMS) pin and defines the boot mode vector — in other words, the memory location for CS0 or for NFC base address. See the table below for the choices of boot memory locations.

| Boot Device | Boot Mode Select | Definition | Boot Start Address/Boot Vector |

|-------------|------------------|------------|--------------------------------|

| LPC (CS0)   | 0                | Boot low   | 0x00000000/0x00000100          |

| LPC (CS0)   | 1                | Boot high  | 0xFFF00000/0xFFF00100          |

| NAND        | 0                | Boot low   | 0x00000000                     |

| NAND        | 1                | Boot high  | 0xFFF00000                     |

# 2.3 NOR Flash Configurations

| Reset Parameter  | Signal        | Description                                                                                                                                                                                                                                                                   |

|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_CONF_LPC_AX  | EMB_AD[9:8]   | LPC address extension mode 00 No LPC Address Extension 01 Use LPC_AX[pata] 10 Use LPC_AX[nfc] 11 Reserved                                                                                                                                                                     |

| RST_CONF_LPC_MX  | EMB_AD[16]    | LPC mux mode configuration 0 Non-multiplexed mode 1 Multiplexed mode                                                                                                                                                                                                          |

| RST_CONF_LPC_WA  | EMB_AD[17]    | LPC word/byte addressing 0 Byte addressing 1 Word addressing                                                                                                                                                                                                                  |

| RST_CONF_LPC_DBW | EMB_AD[19:18] | LPC data port size 00 8-bit 10 Reserved 01 16-bit 11 32-bit                                                                                                                                                                                                                   |

| RST_CONF_NFC_PS  | EMB_AD[20]    | NAND flash page size if RST_CONF_ROMLOC = 01 then RST_CONF_NFC_PS defines the page size: 0 512-byte page size 1 2 KB page size if RST_CONF_ROMLOC = 11 then RST_CONF_NFC_PS defines the spare size with a fixed page size of 4K: 0 64 bytes spare size 1 218 bytes spare size |

# 2.3.1 RST\_CONF\_LPC\_AX

This bit defines which set of pins have the LPC\_AX[] signals.

| LPC_AX[] | Ball Number<br>RST_LPC_AX [01] | Ball/Pin Number<br>RST_LPC_AX [10] |

|----------|--------------------------------|------------------------------------|

| LPC_AX04 | H2                             | G2                                 |

| LPC_AX05 | J4                             | G3                                 |

| LPC_AX[] | Ball Number<br>RST_LPC_AX [01] | Ball/Pin Number<br>RST_LPC_AX [10] |

|----------|--------------------------------|------------------------------------|

| LPC_AX06 | J3                             | H5                                 |

| LPC_AX07 | J2                             | H4                                 |

| LPC_AX08 | K5                             | H1                                 |

| LPC_AX09 | NA                             | G4                                 |

When using the non-mux mode addressing, these bits are required to be set. See Section Appendix B, "Non-Mux Mode Addressing Pin Assignment," for details on the pin/signal assignments for non-mux mode addressing.

#### 2.3.2 RST\_CONF\_MX

This bit defines the local plus (CS0) address/data mode. The choices are multiplexed (mux) or non-multiplexed. For the multiplexed addressing mode there is an address tenure, followed by an ALE, then the data tenure. For non-multiplexed mode, the address and data tenure are concurrent. The non-multiplexed mode is, in general, a faster method of accessing data in the flash.

Refer to Section Appendix B, "Non-Mux Mode Addressing Pin Assignment," and Section Appendix C, "Mux Mode Addressing Pin Assignments," for package pin assignments for these two modes.

| Reset Parameter | Signal | Description                                                          |

|-----------------|--------|----------------------------------------------------------------------|

| RST_CONF_LPC_MX |        | LPC mux mode configuration 0 Non-multiplexed mode 1 Multiplexed mode |

## 2.3.3 RST\_CONF\_DBW

This bit selects whether the local plus bus controller is in word or byte addressing mode.

| Reset Parameter | Signal | Description                                                  |

|-----------------|--------|--------------------------------------------------------------|

| RST_CONF_LPC_WA |        | LPC word/byte addressing 0 Byte addressing 1 Word addressing |

Byte addressing uses the lowest significant address line as A0 from the MPC5121e. If the system is set up for 16-bit data bus, then A0 is a no connect. A1 from the MPC5121e would be connected to A0 of the memory (or peripheral) device. In word addressing mode, internal to the MPC5121e, the address lines are shifted and A0 would then be connected to A0 of the memory (or peripheral) device.

# 2.3.4 RST\_CONF\_DPW

These sets of bits select the data port width (DPW) for the LPC (CS0) during boot. This is applicable for both mux and non-mux addressing modes.

| Reset Parameter  | Signal | Description                                                 |

|------------------|--------|-------------------------------------------------------------|

| RST_CONF_LPC_DBW |        | LPC data port size 00 8-bit 10 Reserved 01 16-bit 11 32-bit |

See Section Appendix B, "Non-Mux Mode Addressing Pin Assignment," for details on the pin/signal assignments for non-mux mode addressing and Section Appendix C, "Mux Mode Addressing Pin Assignments," for details on the pin/signal assignments for mux mode.

## 2.4 NAND Flash Configurations

# 2.4.1 RST\_CONF\_NFC\_PS

These sets of bits select the NAND flash page size (NFC\_PS) and, in conjunction with RST\_CONF\_ROMLOC, the 4K page size and spare bytes.

Table 4. NFC Page Size

| Reset Parameter | Signal     | Description                                                                                                                                                                                                                                                                   |

|-----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_CONF_NFC_PS | EMB_AD[20] | NAND flash page size if RST_CONF_ROMLOC = 01 then RST_CONF_NFC_PS defines the page size: 0 512-byte page size 1 2 KB page size if RST_CONF_ROMLOC = 11 then RST_CONF_NFC_PS defines the spare size with a fixed page size of 4K: 0 64 bytes spare size 1 218 bytes spare size |

## 2.4.2 RTS\_CONF\_NFC\_DBW

This bit sets the data port width (size) for the NAND flash controller.

| Reset Parameter  | Signal | Description                          |

|------------------|--------|--------------------------------------|

| RST_CONF_NFC_DBW |        | NFC data port size 0 8-bit 1 16 -bit |

See Section Appendix D, "NAND Flash Pin Connections," for pin assignments for the NAND flash connections.

# 2.5 PCI Bus Configuration

| Reset Parameter  | Signal | Description                                           |

|------------------|--------|-------------------------------------------------------|

| RST_CONF_PCI66EN |        | Enable 66 MHz PCI operation 0 PCI 33 MHz 1 PCI 66 MHz |

| RST_CONF_PCIARB  |        | Internal PCI arbiter signals 0 Disabled 1 Enabled     |

#### 2.5.1 RST\_CONF\_PCI66EN

This bit sets the proper PCI bus timing, although you still need to set the clock speed appropriately. This bit in conjunction with the PCI\_DIV System Clock Frequency Register 1 (IMMRBAR+ 0x0f0c) will provide proper PCI bus timing. See chapter 5 of MPC5121ERM, MPC5121e Microcontroller Reference Manual, for PCI DIV details.

| Reset Parameter  | Signal | Description                                           |

|------------------|--------|-------------------------------------------------------|

| RST_CONF_PCI66EN |        | Enable 66 MHz PCI operation 0 PCI 33 MHz 1 PCI 66 MHz |

#### 2.5.2 RST\_CONF\_PCIARB

This bit directs whether the PCI is enabled or not. This essentially disables the PCI bus completely. When this configuration is selected, PCI GNT0 (ball E25) must be tied high—inactive.

| Reset Parameter | Signal     | Description                                       |

|-----------------|------------|---------------------------------------------------|

| RST_CONF_PCIARB | EMB_AD[15] | Internal PCI arbiter signals 0 Disabled 1 Enabled |

## 2.6 Other System Functions

| Reset Parameter | Signal    | Description                                            |

|-----------------|-----------|--------------------------------------------------------|

| RST_CONF_SWEN   | EMB_AD[2] | Enables watchdog timer at reset  0 Disabled  1 Enabled |

| Reset Parameter  | Signal     | Description                                                                               |

|------------------|------------|-------------------------------------------------------------------------------------------|

| RST_CONF_TPR     | EMB_AD[3]  | Factory test mode  0 Disabled (normal operation)  1 Enabled (Freescale factory test only) |

| RST_CONF_COREDIS | EMB_AD[4]  | Core disable mode 0 Disabled (normal operation) 1 Enabled (Freescale factory test only)   |

| RST_CONF_TLE     | EMB_AD[6]  | Endian mode  0 Big endian mode  1 Little endian mode                                      |

| RST_CONF_CKS_IN  | EMB_AD[22] | Checkstop  O Checkstop input disabled  Checkstop input enabled                            |

#### 2.6.1 RST\_CONF\_SWEN

| Reset Parameter | Signal    | Description                                            |

|-----------------|-----------|--------------------------------------------------------|

| RST_CONF_SWEN   | EMB_AD[2] | Enables watchdog timer at reset  0 Disabled  1 Enabled |

This bit enables the software watchdog timer. The default time for this timer is the maximum count. It is driven by the input oscillator. For an input frequency of 33 MHz, the watchdog timer will time out in about 128 seconds.

#### 2.6.2 RST\_CONF\_TPR

This bit is used for the factory test mode. For normal operation, this signal must be set to low.

| Reset Parameter | Signal | Description                                                                               |

|-----------------|--------|-------------------------------------------------------------------------------------------|

| RST_CONF_TPR    |        | Factory Test Mode  0 Disabled (normal operation)  1 Enabled (Freescale factory test only) |

# 2.6.3 RST\_CONF\_CORE\_DIS

This bit is used for factory testing of the SOC. For normal operation, this signal must be tied low. The pin is called "Core Disable," so it's a double negative. In other words, you need to disable the disable signal to have an enable.

| Reset Parameter  | Signal | Description                                                                               |

|------------------|--------|-------------------------------------------------------------------------------------------|

| RST_CONF_COREDIS | ,      | Core disable mode  0 Disabled (normal operation)  1 Enabled (Freescale factory test only) |

Understanding the Reset Configuration Word for the MPC5121e, Rev. 1

#### 2.6.4 RST\_CONF\_TLE

| Reset Parameter | Signal    | Description                                        |

|-----------------|-----------|----------------------------------------------------|

| RST_CONF_TLE    | EMB_AD[6] | Endian mode 0 Big endian mode 1 Little endian mode |

This bit directs the e300 core to operate in true little endian mode. The true little endian mode is another enhanced capability of the e300 core. The true little endian mode actually operates on true little endian instructions and data from memory.

For most applications, this bit will normally be set to 0, big endian mode. This bit has no other effects on the SOC itself.

#### 2.6.5 RST\_CONF\_CKS\_IN

| Reset Parameter | Signal | Description                                                    |

|-----------------|--------|----------------------------------------------------------------|

| RST_CONF_CKS_IN |        | Checkstop  O Checkstop input disabled  Checkstop input enabled |

This bit sets the pin multiplexing on this pin AA to (CHSTP) checkstop in as the default value. With this bit set, the checkstop is now the default pin setting.

#### 3 References

- 1. MPC5121ERM, MPC5121e Microcontroller Reference Manual

- 2. E300CORERM, e300 Power Architecture  $^{TM}$  Core Family Reference Manual

# 4 Revision History

| Revision         | Date              | Comments                                                                                                                                       |

|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Original release | 16 September 2008 | M. Ruthenbeck (MAR) – Original Version                                                                                                         |

| Version 0.1      | 19 September 2008 | MAR – revised based on feedback from M. Capistran                                                                                              |

| Version 1        | 21 September 2010 | Corrected information for reset parameter RST_CONF_ROMLOC. Value of binary 10 was = LPC boot (and 4K NFC page size). Changed to 10 = Reserved. |

# **Appendix A Reset Configuration Word Tables**

**Table 5. Reset Configuration Word (Alphabetically by Parameter)**

| Reset Parameter   | Signal        | Description                                                                                                                                                                                                                                                                   |

|-------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_CONF_BMS      | EMB_AD[5]     | Boot mode select<br>Selects e300 boot vector and configures default value for LPC CS0<br>or NFC base address                                                                                                                                                                  |

| RST_CONF_CKS_IN   | EMB_AD[22]    | Checkstop 0 Checkstop input disabled 1 Checkstop input enabled                                                                                                                                                                                                                |

| RST_CONF_COREDIS  | EMB_AD[4]     | Core disable mode 0 Disabled (normal operation) 1 Enabled (Freescale factory test only)                                                                                                                                                                                       |

| RST_CONF_COREPLL  | EMB_AD[13:10] | Core PLL multiply factor<br>See clock module for programming options                                                                                                                                                                                                          |

| RST_CONF_EMB_AD14 | EMB_AD[14]    | Reserved — must be connected to 1                                                                                                                                                                                                                                             |

| RST_CONF_LPC_AX   | EMB_AD[9:8]   | LPC address extension mode 00 No LPC address extension 01 Use LPC_AX[pata] 10 Use LPC_AX[nfc] 11 Reserved                                                                                                                                                                     |

| RST_CONF_LPC_DBW  | EMB_AD[19:18] | LPC data port size 00 8-bit 10 Reserved 01 16-bit 11 32-bit                                                                                                                                                                                                                   |

| RST_CONF_LPC_MX   | EMB_AD[16]    | LPC mux mode configuration 0 Non-multiplexed mode 1 Multiplexed mode                                                                                                                                                                                                          |

| RST_CONF_LPC_WA   | EMB_AD[17]    | LPC word/byte addressing 0 Byte addressing 1 Word addressing                                                                                                                                                                                                                  |

| RST_CONF_NFC_DBW  | EMB_AD[21]    | NFC data port size 0 8-bit 1 16-bit                                                                                                                                                                                                                                           |

| RST_CONF_NFC_PS   | EMB_AD[20]    | NAND flash page size if RST_CONF_ROMLOC = 01 then RST_CONF_NFC_PS defines the page size: 0 512-byte page size 1 2 KB page size if RST_CONF_ROMLOC = 11 then RST_CONF_NFC_PS defines the spare size with a fixed page size of 4K: 0 64 bytes spare size 1 218 bytes spare size |

| RST_CONF_PCI66EN  | EMB_AD[7]     | Enable 66 MHz PCI operation 0 PCI 33MHz 1 PCI 66MHz                                                                                                                                                                                                                           |

Table 5. Reset Configuration Word (Alphabetically by Parameter) (continued)

| Reset Parameter   | Signal                      | Description                                                                                                                   |

|-------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| RST_CONF_PCIARB   | EMB_AD[15]                  | Internal PCI arbiter signals 0 Disabled 1 Enabled                                                                             |

| RST_CONF_ROMLOC   | EMB_AD[1:0]                 | Selects boot device  00 LPC boot  01 NAND (NFC) boot  10 Reserved  11 NAND (NFC) boot (see also definition of ST_CONF_NFC_PS) |

| RST_CONF_SWEN     | EMB_AD[2]                   | Enables watchdog timer at reset 0 Disabled 1 Enabled                                                                          |

| RST_CONF_SYSDIV   | LPC_AX[3],<br>EMB_AD[31:27] | System PLL divider See, "MPC5121e Clocks," for programming options.                                                           |

| RST_CONF_SYSOSCEN | EMB_AX02                    | Oscillator bypass mode 0 System oscillator bypass mode 1 System oscillator mode                                               |

| RST_CONF_SYSPLL   | EMB_AD[26:23]               | System PLL multiply factor See, "MPC5121e Clocks," for programming options.                                                   |

| RST_CONF_TLE      | EMB_AD[6]                   | Endian mode 0 Big endian mode 1 Little endian mode                                                                            |

| RST_CONF_TPR      | EMB_AD[3]                   | Factory test mode  0 Disabled (normal operation)  1 Enabled (Freescale factory test only)                                     |

Table 6. Reset Configuration Word (By Signal EMB\_AD[])

| Signal      | Reset Parameter  | Description                                                                                                              |

|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| EMB_AD[1:0] | RST_CONF_ROMLOC  | Selects boot device1 00 LPC boot 01 NAND (NFC) boot 10 Reserved 11 NAND (NFC) boot see also definition of ST_CONF_NFC_PS |

| EMB_AD[2]   | RST_CONF_SWEN    | Enables watchdog timer at reset 0 Disabled 1 Enabled                                                                     |

| EMB_AD[3]   | RST_CONF_TPR     | Factory test mode 0 Disabled (normal operation) 1 Enabled (Freescale factory test only)                                  |

| EMB_AD[4]   | RST_CONF_COREDIS | Core disable modes 0 Disabled (normal operation) 1 Enabled (Freescale factory test only)                                 |

| EMB_AD[5]   | RST_CONF_BMS     | Boot mode select<br>Selects e300 boot vector and configures default value for LPC<br>CS0 or NFC base address."           |

### Understanding the Reset Configuration Word for the MPC5121e, Rev. 1

Table 6. Reset Configuration Word (By Signal EMB\_AD[]) (continued)

| Signal                           | Reset Parameter   | Description                                                                                                                                                                                                                                                                   |

|----------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMB_AD[6]                        | RST_CONF_TLE      | Endian mode 0 Big endian mode 1 Little endian mode                                                                                                                                                                                                                            |

| EMB_AD[7]                        | RST_CONF_PCI66EN  | Enable 66 MHz PCI operation 0 PCI 33 MHz 1 PCI 66 MHz                                                                                                                                                                                                                         |

| 00 No LF<br>01 Use L<br>10 Use L |                   | LPC address extension mode 00 No LPC address extension 01 Use LPC_AX[pata] 10 Use LPC_AX[nfc] 11 Reserved                                                                                                                                                                     |

| EMB_AD[13:10]                    | RST_CONF_COREPLL  | Core PLL multiply factor<br>See, "MPC5121e Clocks," for programming options.                                                                                                                                                                                                  |

| EMB_AD[14]                       | RST_CONF_EMB_AD14 | Reserved — must be connected to 1                                                                                                                                                                                                                                             |

| EMB_AD[15]                       | RST_CONF_PCIARB   | Internal PCI arbiter signals 0 Disabled 1 Enabled                                                                                                                                                                                                                             |

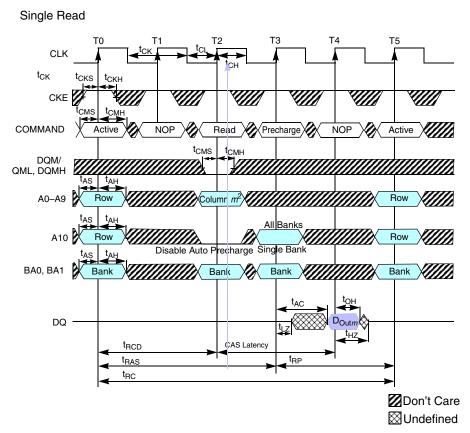

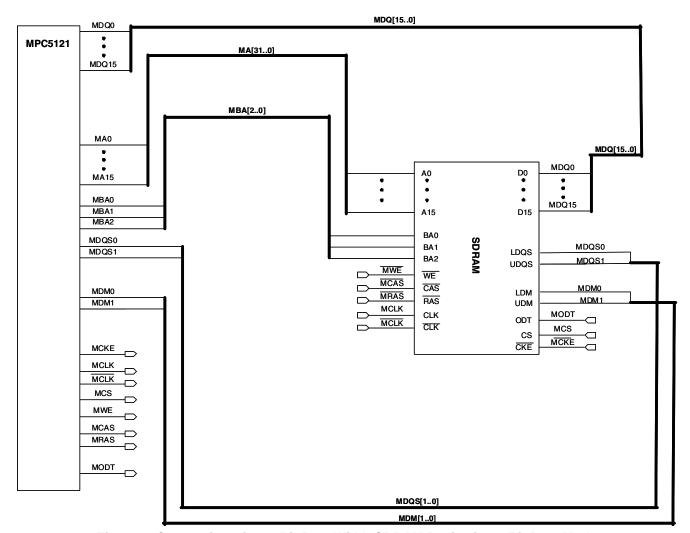

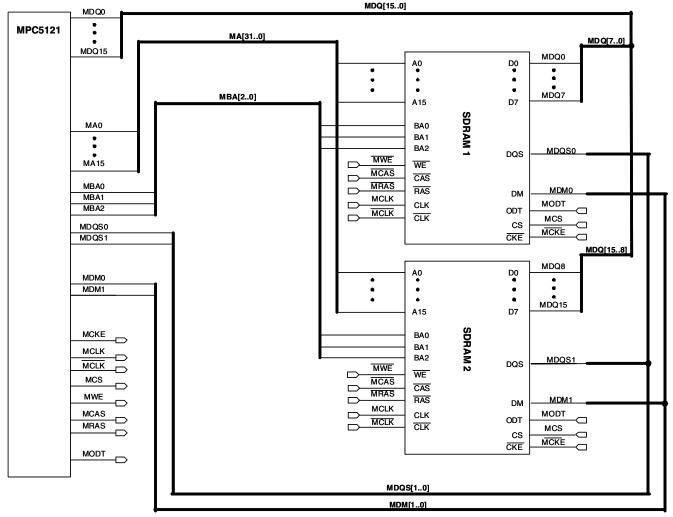

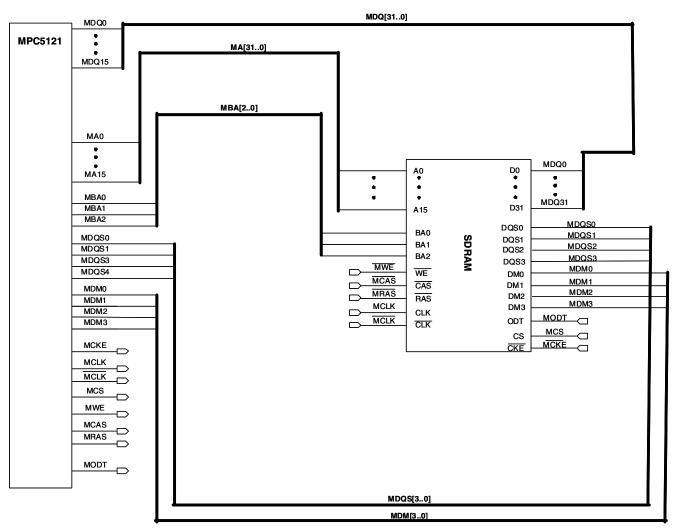

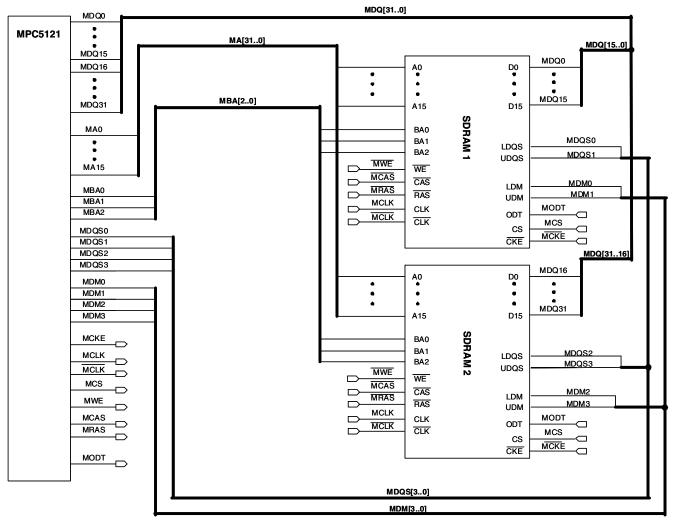

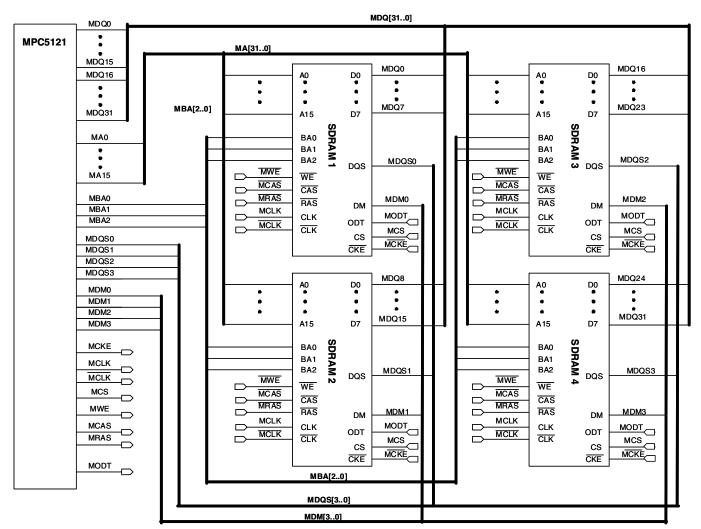

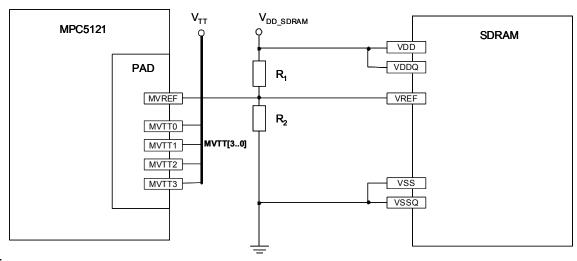

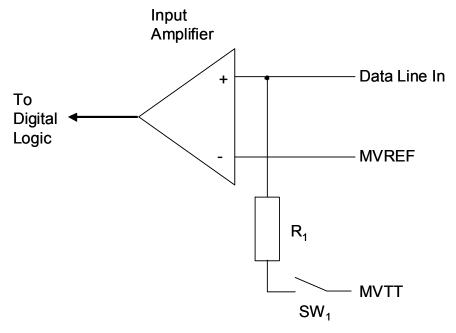

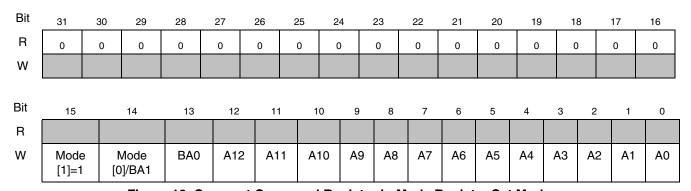

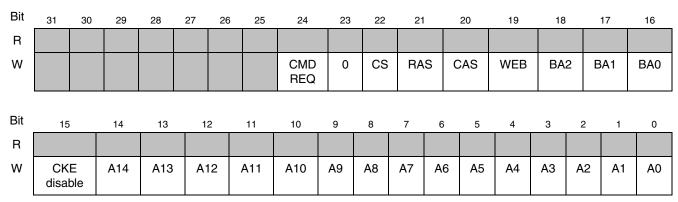

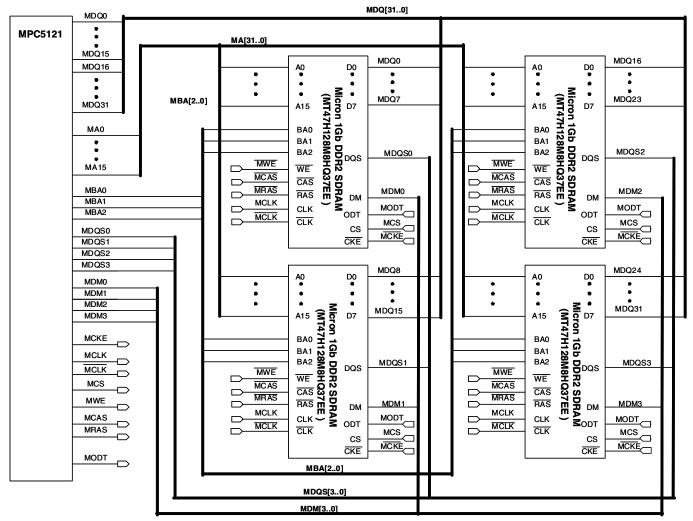

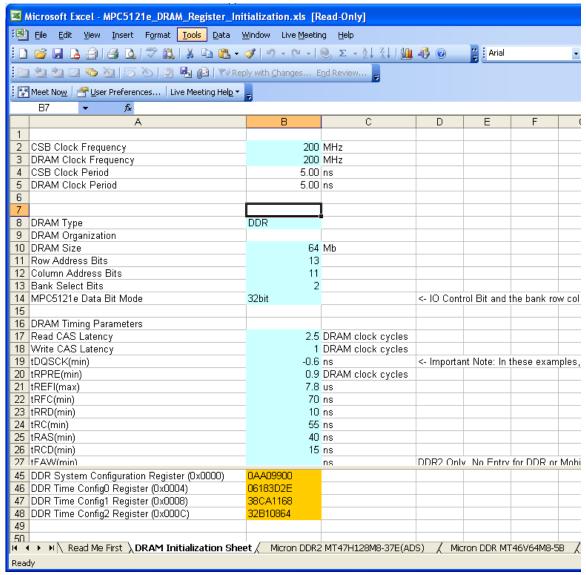

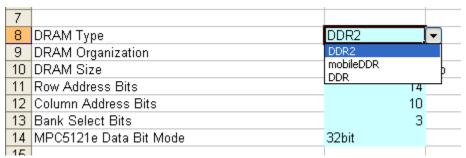

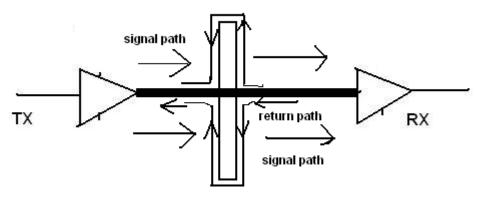

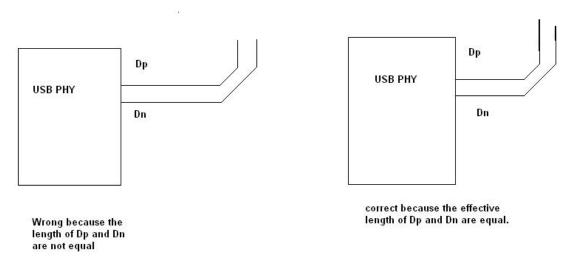

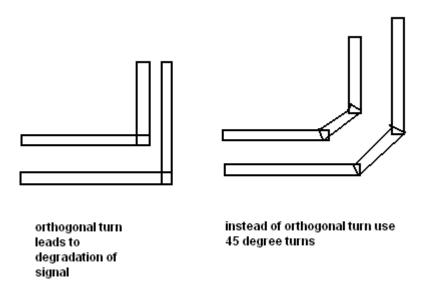

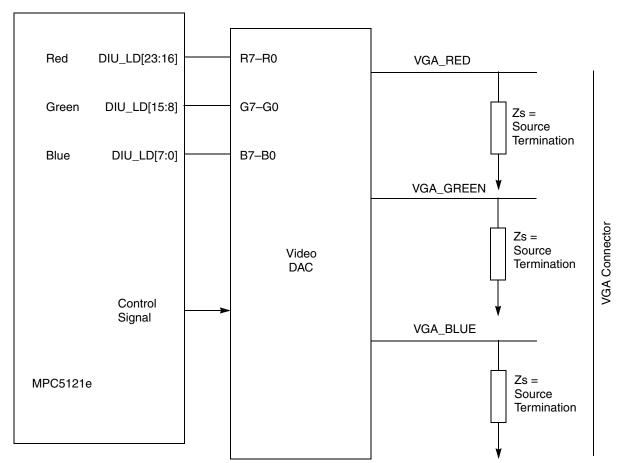

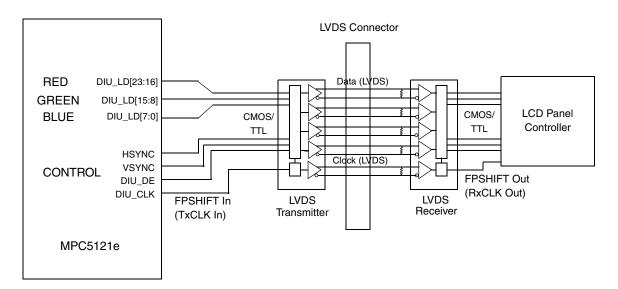

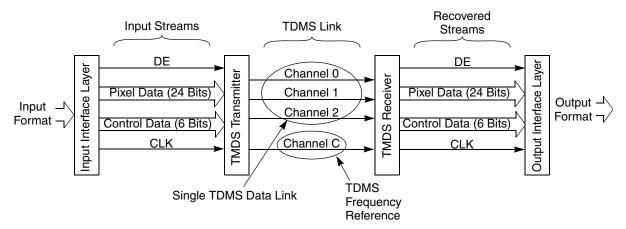

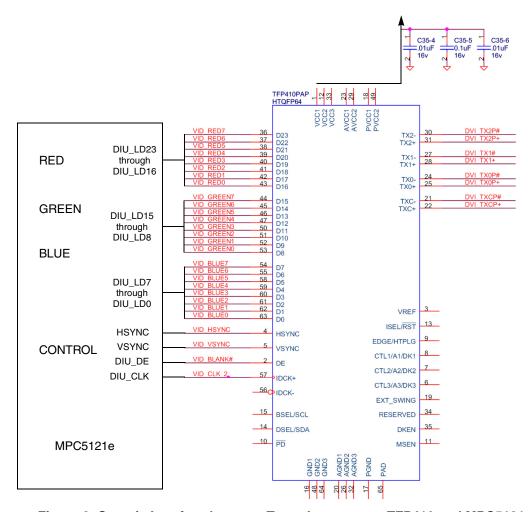

| EMB_AD[16]                       | RST_CONF_LPC_MX   | LPC mux mode configuration 0 Non-multiplexed mode 1 Multiplexed mode                                                                                                                                                                                                          |