Aoc P N 41A50 144 Users Manual

P/N : 41A50-144 0707161359060306365001184565546

PN : 41A50-144 to the manual 783f9621-d35a-9074-01c0-6af872800a4a

2015-02-02

: Aoc Aoc-P-N-41A50-144-Users-Manual-393020 aoc-p-n-41a50-144-users-manual-393020 aoc pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 82

SERVICE MANUAL

SPECTRUM Series

LCD Monitor

LM-700/LM-700A

P/N : 41A50-144

1

THESE DOCUMENTS ARE FOR REPAIR SERVICE INFORMATION ONLY. EVERY

REASONABLE EFFORT HAS BEEN MADE TO ENSURE THE ACCURACY OF THIS

MANUAL; WE CANNOT GUARANTEE THE ACCURACY OF THIS INFORMATION

AFTER THE DATE OF PUBLICATION AND DISCLAIMS RE LIABILITY FOR CHANGES,

ERRORS OR OMISSIONS,

MANUFACTURE DATA : JULY. 2001

REVISE 7 SEP 2001

2

TABLE OF CONTENTS

PAGE

1. SPECIFICATIONS .................................................................................................... 3

1-1 GENERAL SPECIFICATIONS ...................................................….............. 3

1-2 LCD MONITOR DESCRIPTION .................................................................. 4

1-3 INTERFACE CONNECTOR .................................................................……. 4

2. PRECAUTION AND NOTICES ................................................................................ 5

2-1 ASSEMBLY PRECAUTION ......................................................................... 5

2-2 OPERATIONG PRECAUTION ..................................................................... 5

2-3 STORAGE PRECAUTION …........................................................................ 5

2-4 HIGH VOLTAGE WARNING ....................................................................... 5

3. OPERATING INSTRUCTIONS ................................................................................ 6

4. ADJUSTMENT .......................................................................................................... 7

4-1 ADJUSTMENT CONDITIONS AND PRECAUTIONS ............................... 7

4-2 ADJUSTMENTS METHOD .& DESCRIPTION......................... 7-8

4-3 FRONT PANEL CONTROL KNOBS ............................................................ 9

5. CIRCUIT & SOFTWARE DESCRIPTION ................ 10

5-1 THE DIFFERENT BETWEEN EACH PANEL ……………………………. 10

5-2 SPECIAL FUNCTION WITH PRESS KEY ……………………………….. 10

5-3 THE OPTIONAL ON MAINBOARD USING SHUTTLE & 4 KEY.. 10

5-4 THE OPTIONAL ON MAINBOARD OR OTHER ACCESSORY USING

DIFFERENT PANEL 10

5-5 SIMPLE INTRODUCTION ABOUT LM500 CHIPSET …………………... 11

5-6 SOFTWARE FLOW-CHART 12

6. A). INTERFACE-BOARD TROUBLE SHOOTING CHART .................... 14

B). INVERTER - MODULE TROUBLE SHOOTING CHART .................... 23

I. CHI-MEI-inverter spec & trouble shooting chart 23

C). ADAPTER TROUBLE SHOOTING CHART & BOM....... 50

D). AUDIO TROUBLE SHOOTING CHART & BOM

E). Main-chip GMZAN1 specifications 54

7. MECHANICAL OF CABINET FRONT DIS-ASSEMBLY...................................... 64

8. PARTS LISTING .........................................................................................………... 65

9. POWER SYSTEM AND CONSUMPTION CURRENT............................................ 73

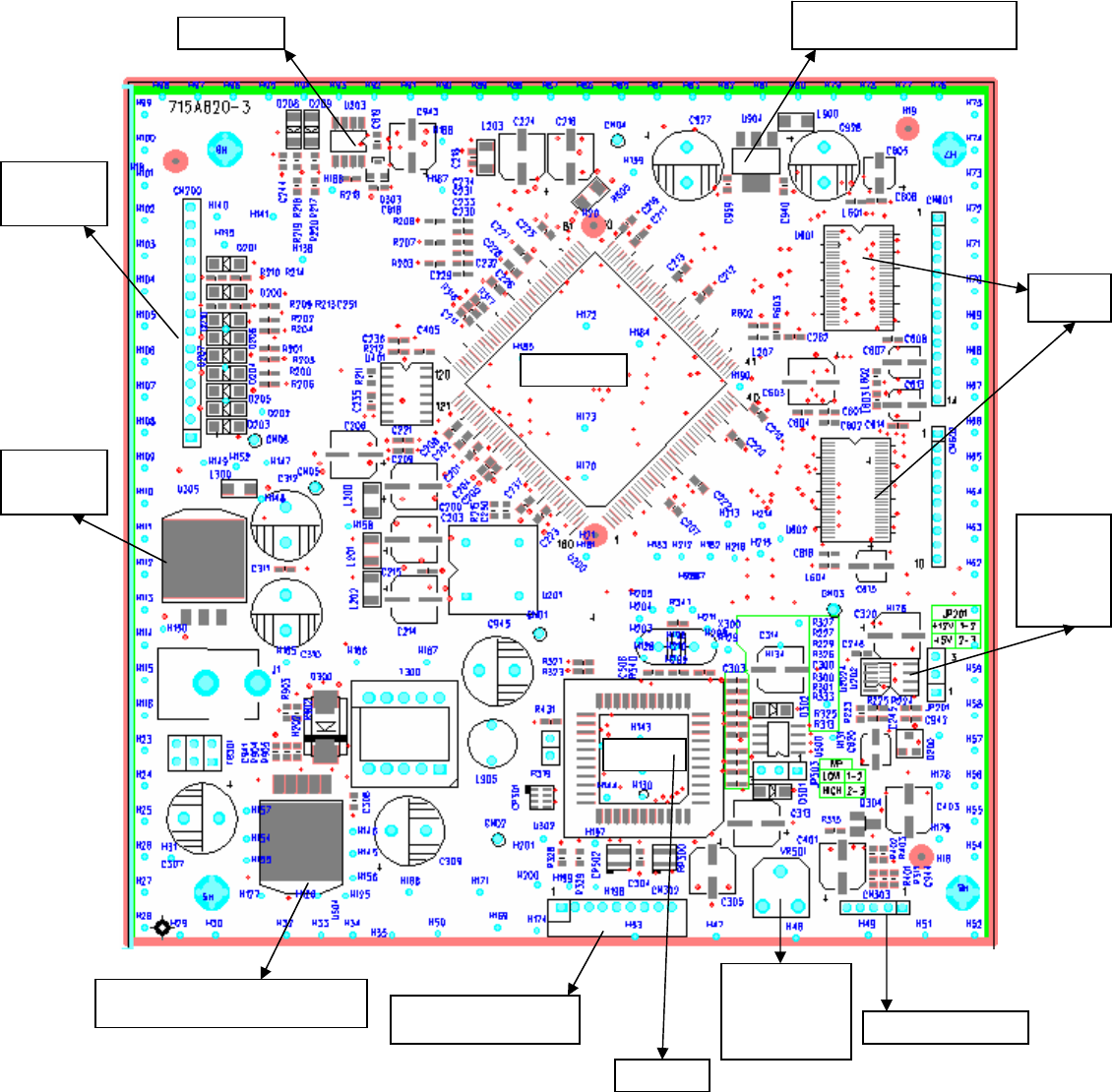

10. PCB LAYOUT .....................................................................………………………... 74

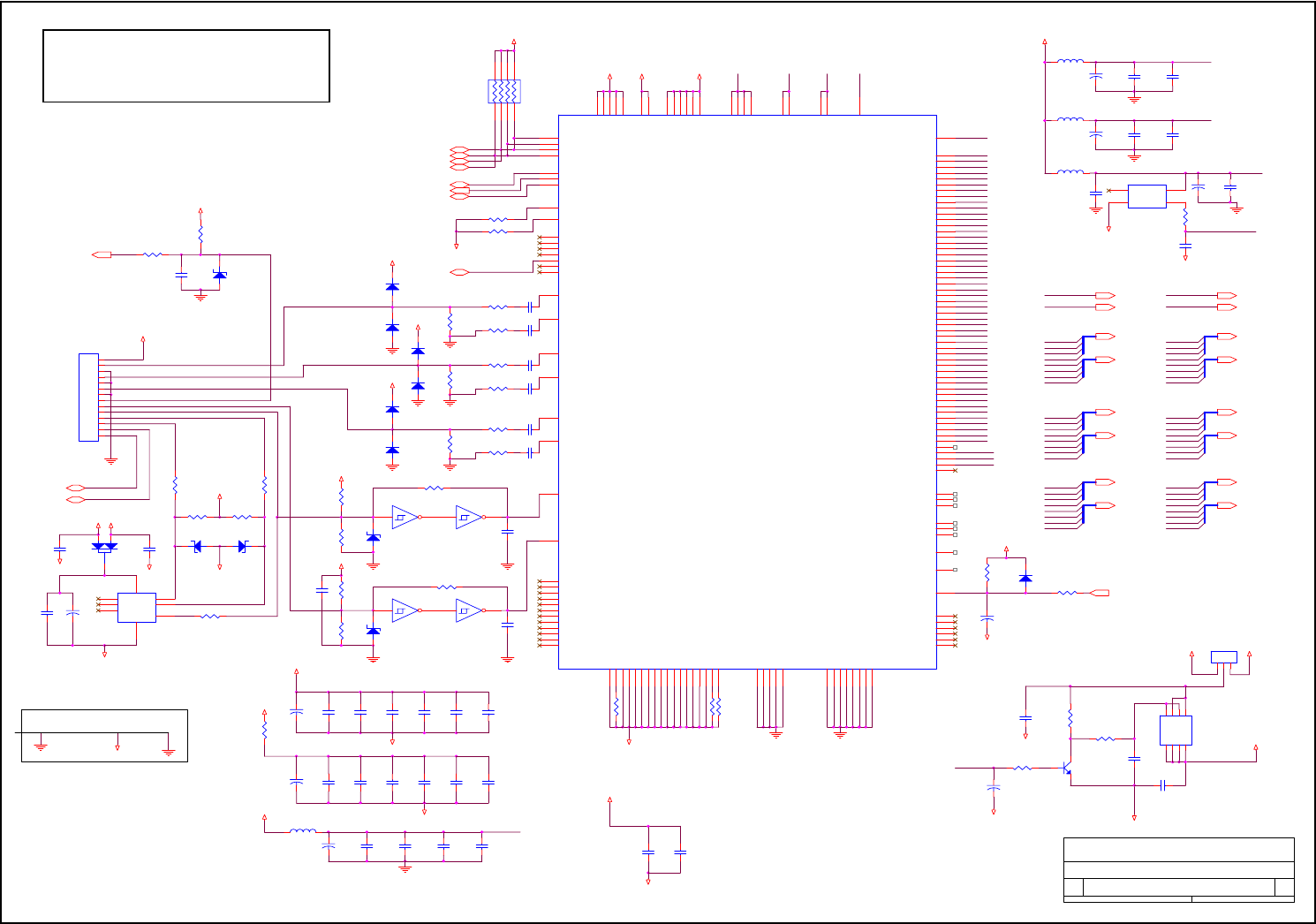

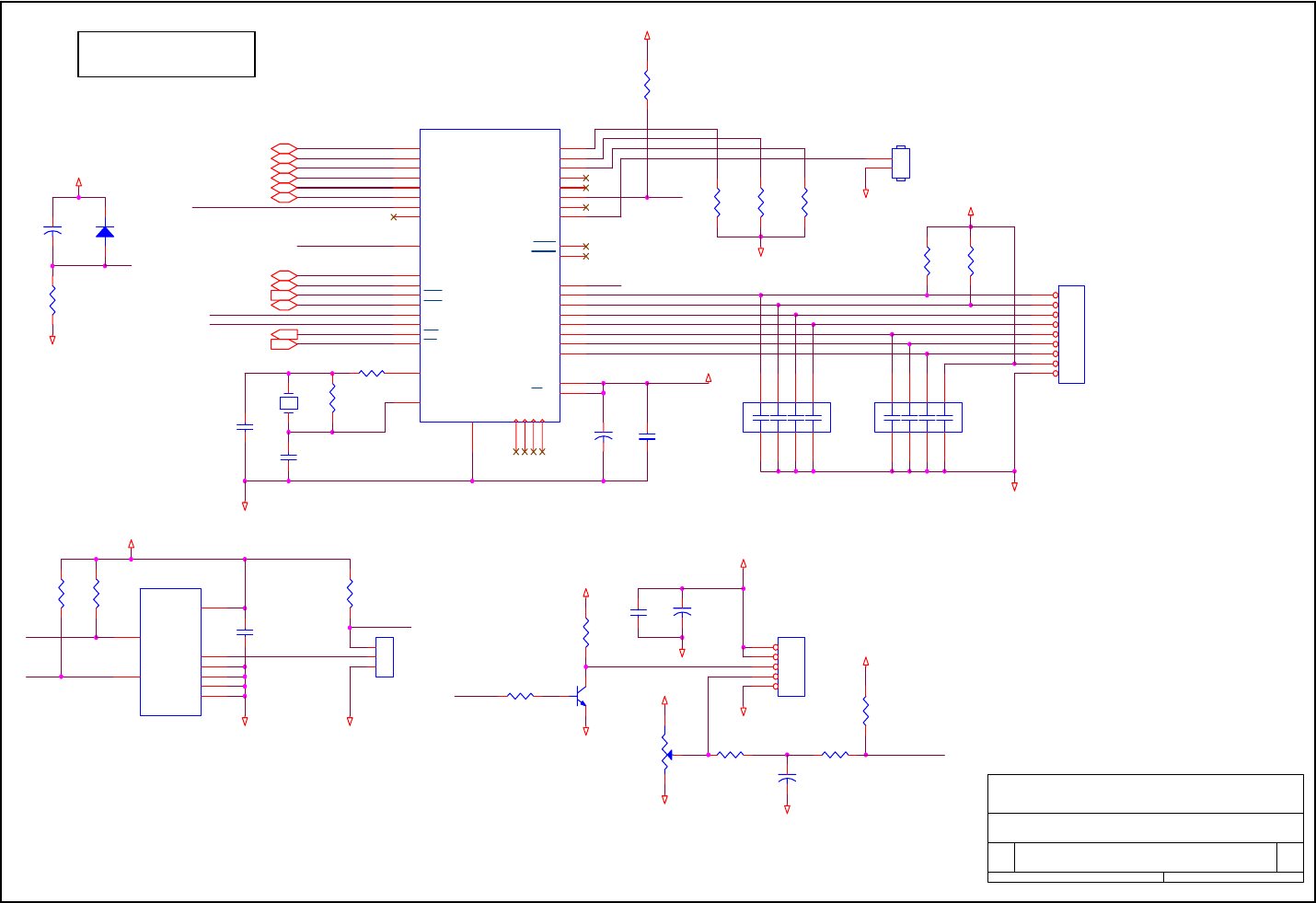

11. MAINBOARD SCHEMATIC DIAGRAM …............................................... 75

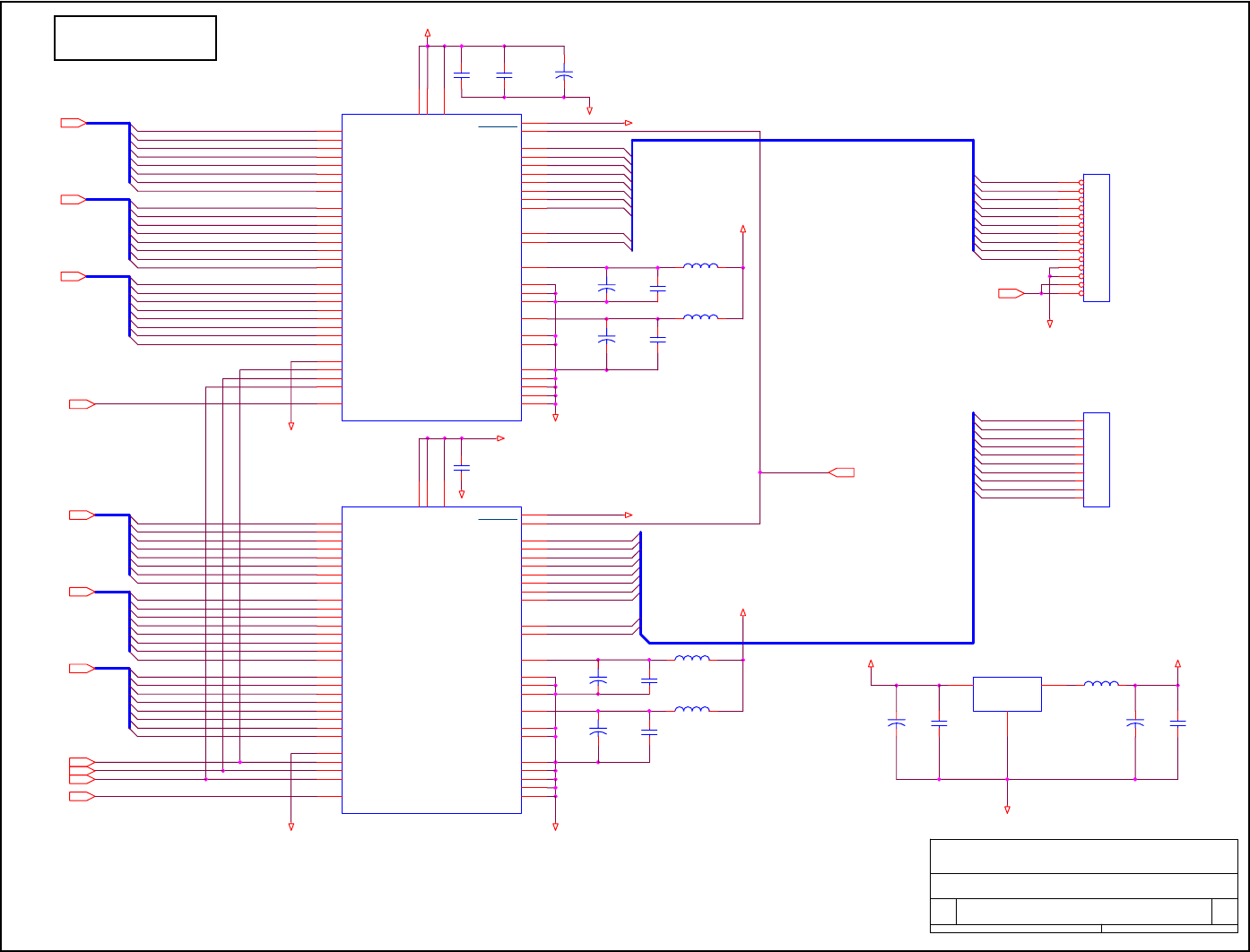

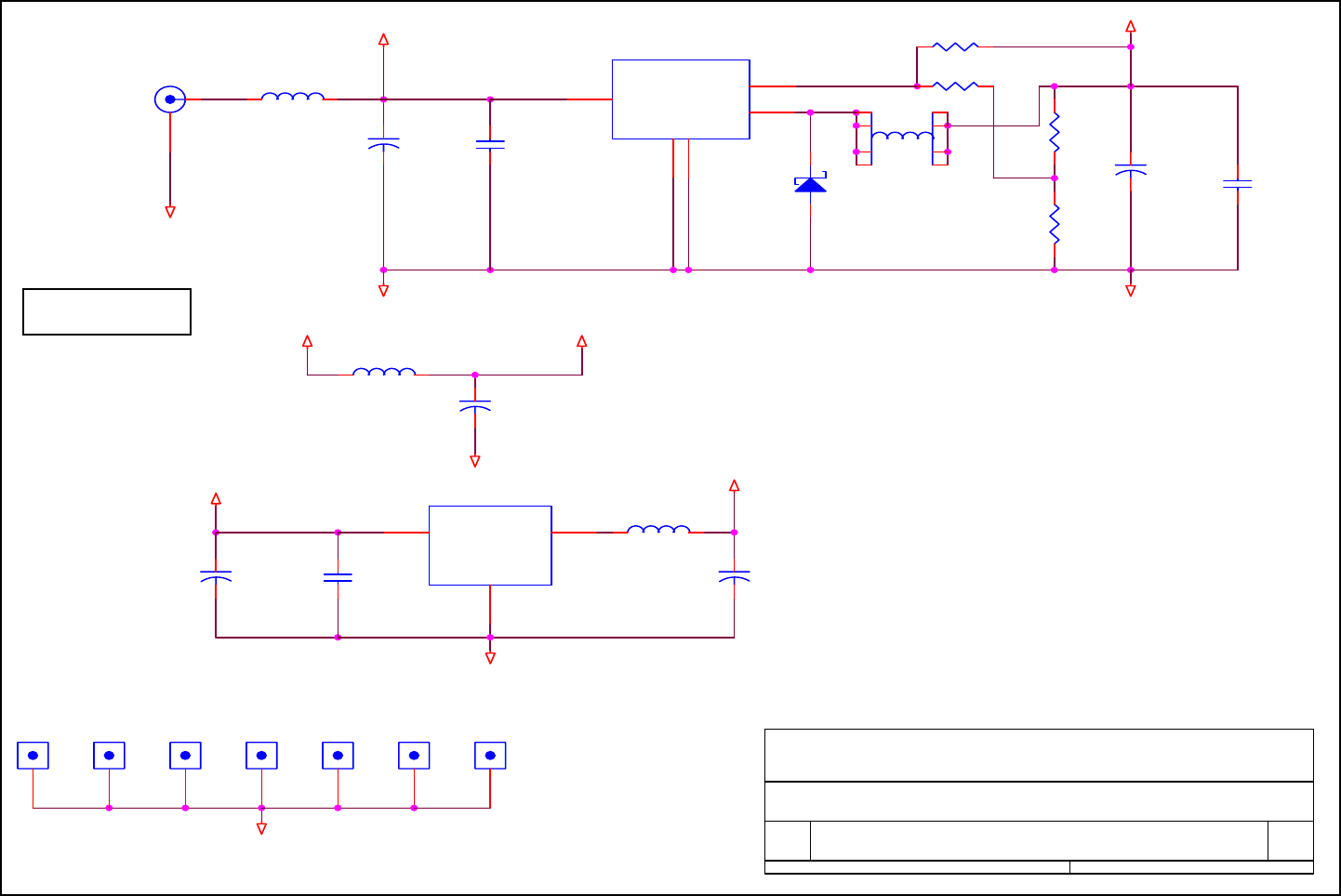

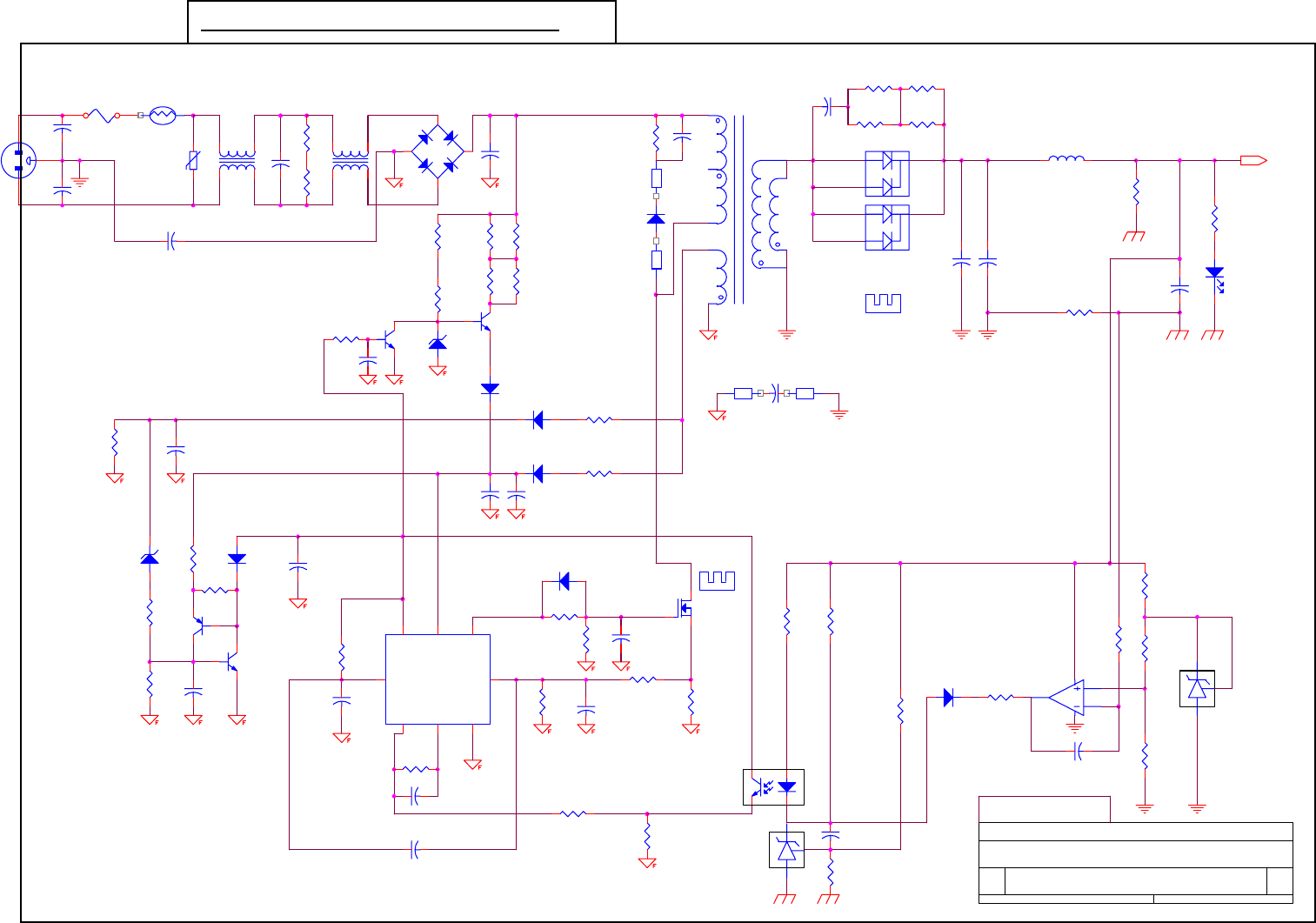

12. ADAPTER SCHEMATIC DIAGRAM

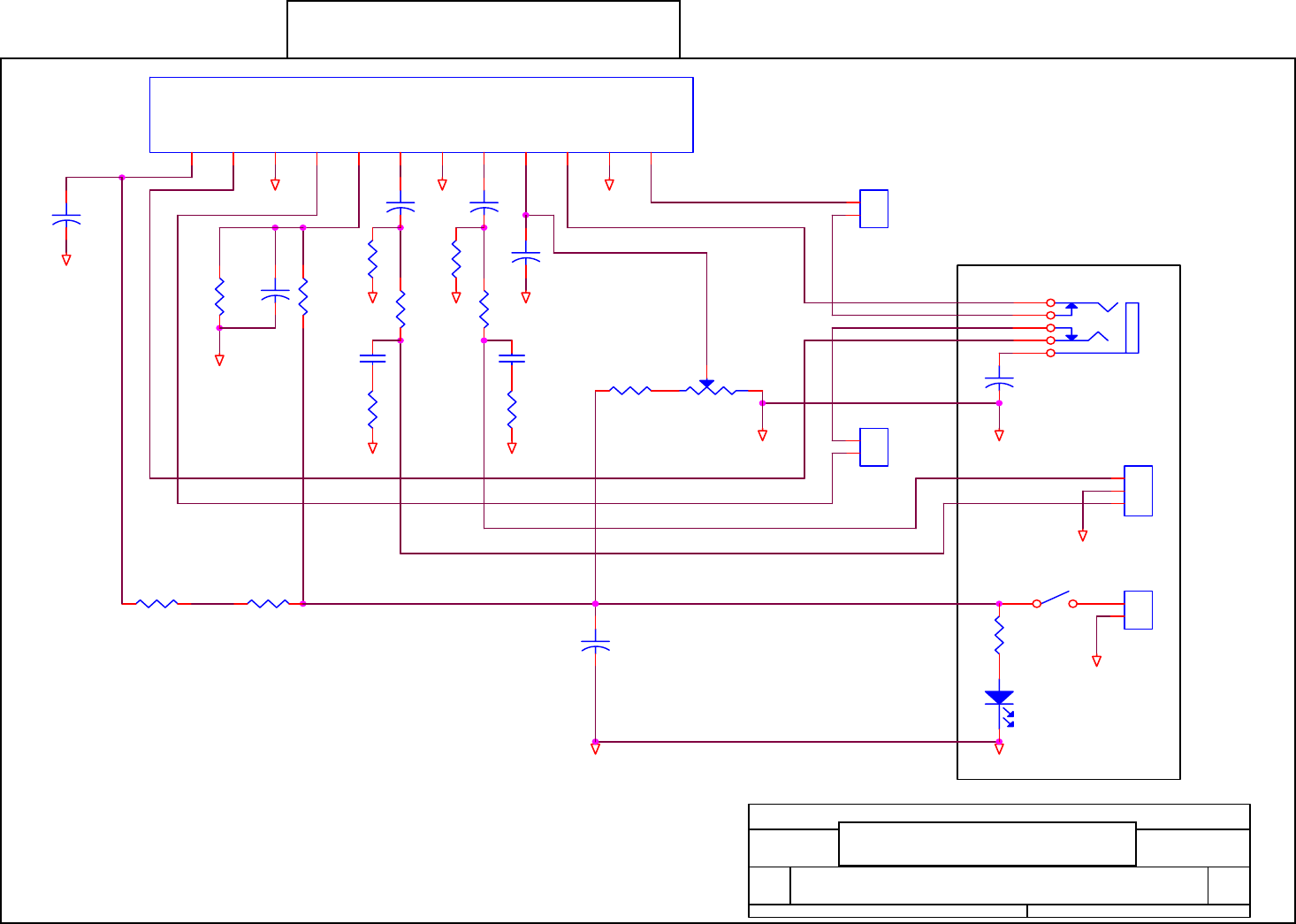

13.AUDIO SCHEMATIC DIAGRAM

3

1. SPECIFICATIONS FOR LCD MONITOR

1-1 General specifications

1. LCD-PANEL :

Active display area 17 inches diagonal

Pixel pitch 0.264 mm x 0.264 mm

Pixel format 1280 x 1024 RGB vertical stripe arrangement

2. Display Color :

8-bit, 16.7 million colors

3. ●External Controls :

Power On/Off, Auto key, Left key, Right key ( for 4-key )

●OSD menu Controls

Contrast, Brightness, Focus, Clock,H-position, V-position, Language, Recall-7800, Recall-6500, Reset,

Exit-osd, Red, Green, Blue, Selected Dos-resolution

4. Input Video Signal :

Analog-signal 0.7Vpp

Video signal termination impedance 75 OHM

5. Scanning Frequencies :

Horizontal: 29 KHz - 80 KHz

Vertical: 55 Hz – 75 Hz

Pixel clock: 135 MHz

6. Factory Preset Timing : 18

User Timings : 19

Input signal tolerance : H tolerance ±1 K, V tolerance ±1 Hz

7. Power Source :

Switching Mode Power Supply

AC 100 – 240 V, 50/60 Hz Universal Type

8. Operating Temperature : 0℃ - 50℃ Ambient

Non-operating Temperature : -20℃ - 60℃

9. Humidity :

Operating : 20% to 80% RH (non-condensing)

Non Operating : 5% to 95%RH (38.7℃ maximum wet bulb temperature)

10. Weight :

5.5 kg

11. External Connection : 15Pin D-type Connector, AC power-Cord

12. View Angle : x-axis right/left = 60, y-axis up/down = 40 ,60

13. Outside dimension : Width x Height x Thickness = 422x 449 x 215 mm

14. Plug and Play : VESA DDC1/DDC2B

15. Power saving : VESA DPMS

4

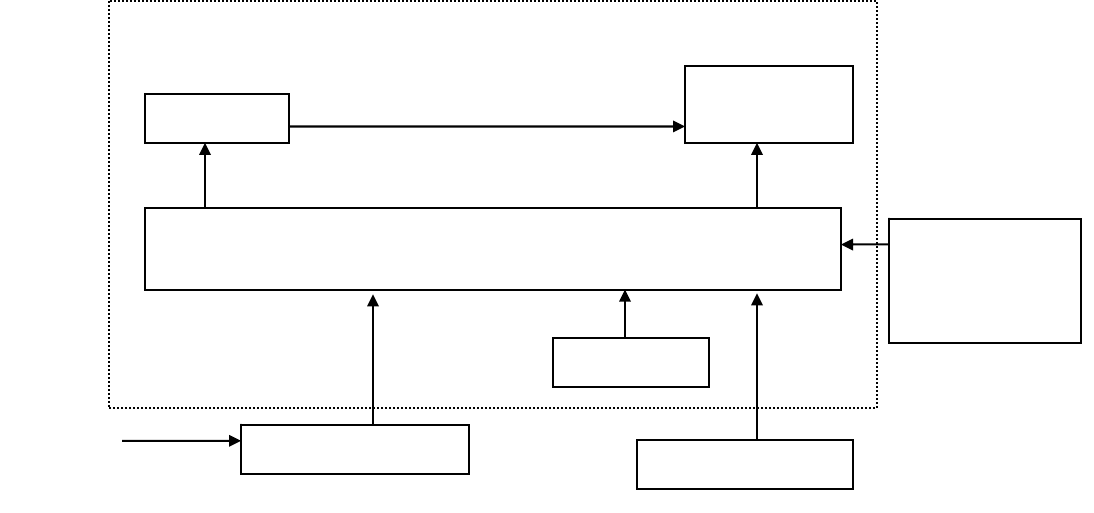

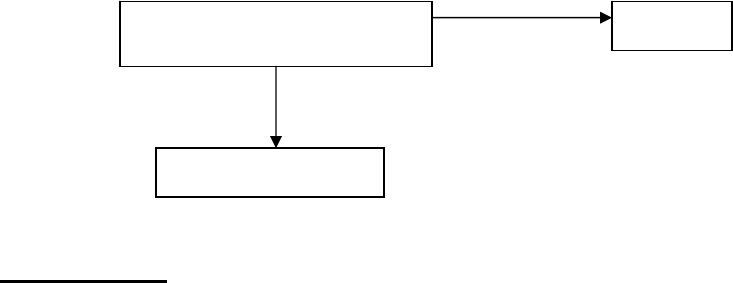

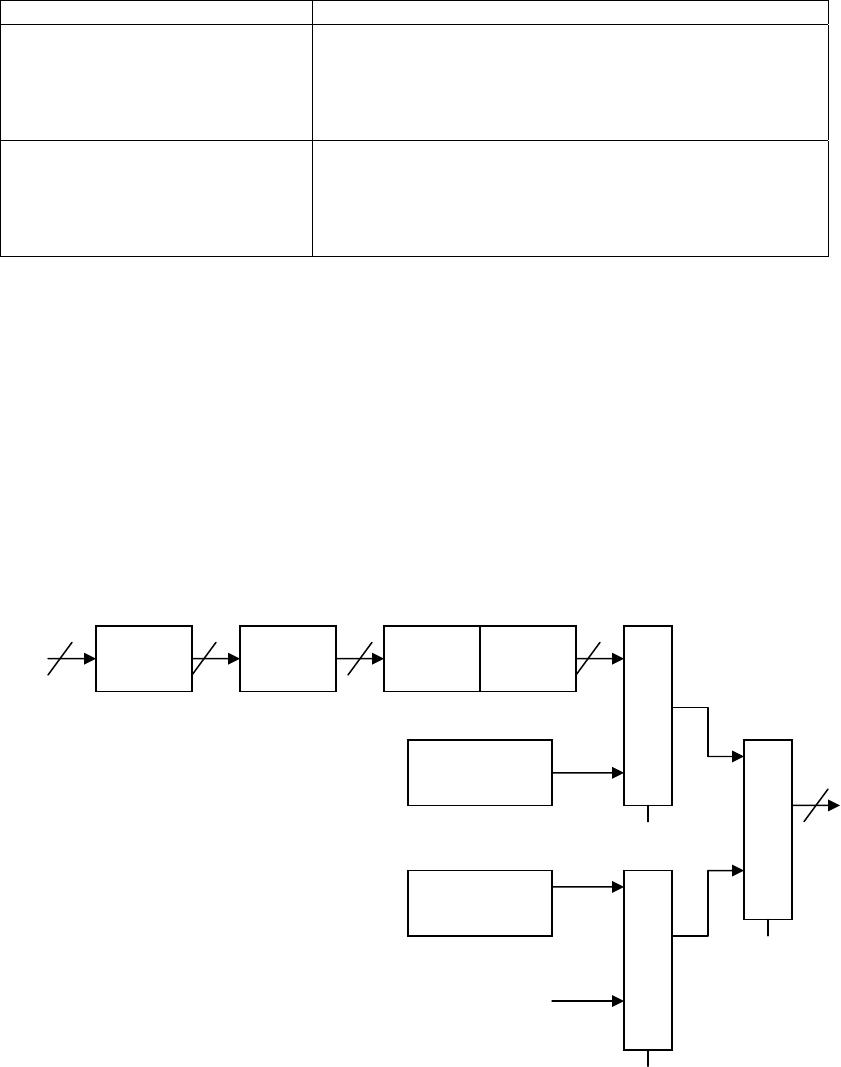

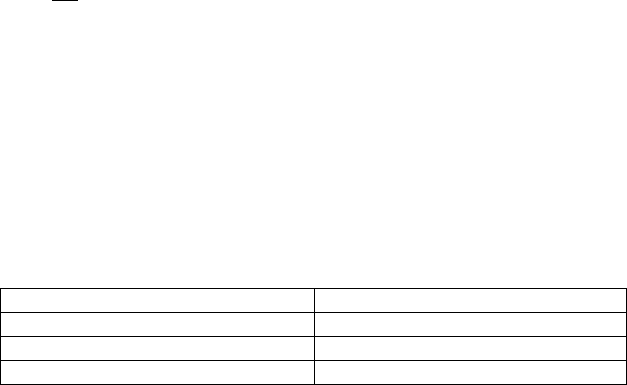

1-2 LCD MONITOR DESCRIPTION

The LCD MONITOR will contain an main board, an Inverter module, keyboard and External Adapter which

house the flat panel control logic, brightness control logic, DDC and DC-DC conversion

The Inverter module will drive the backlight of panel .

The Adapter will provides the 12V DC-power 5 Amp to Main-board and Inverter module .

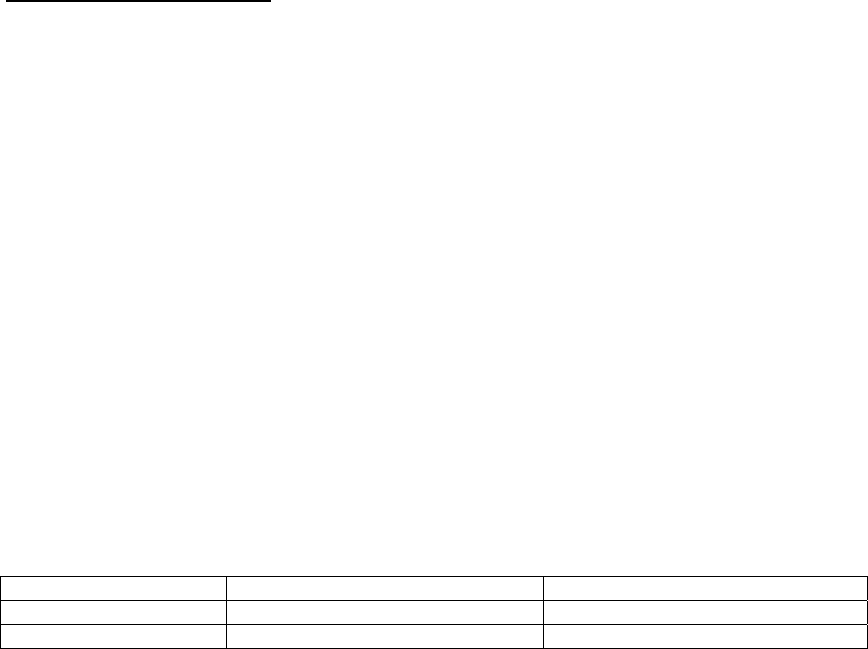

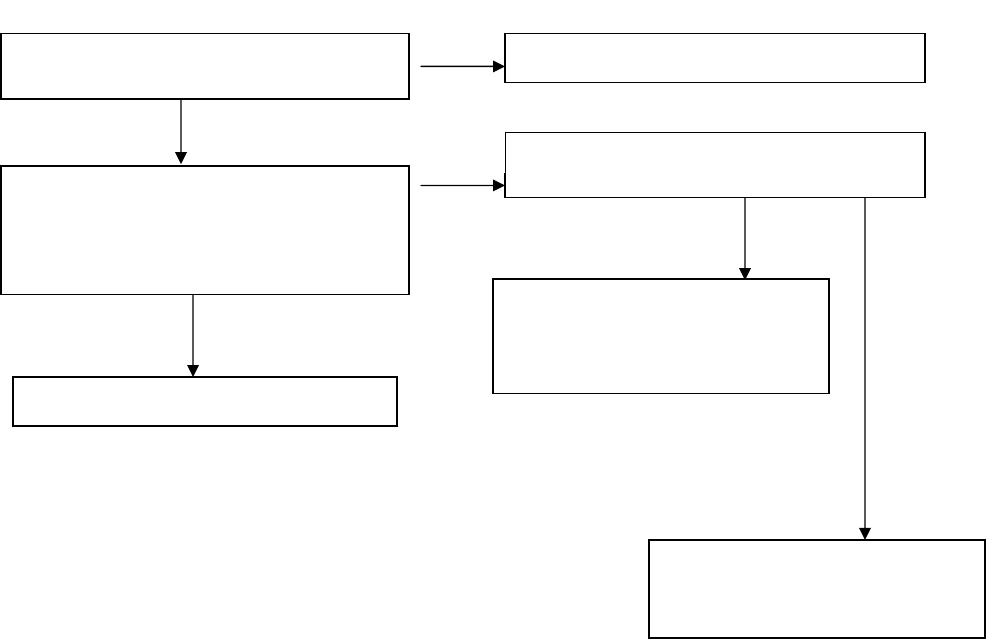

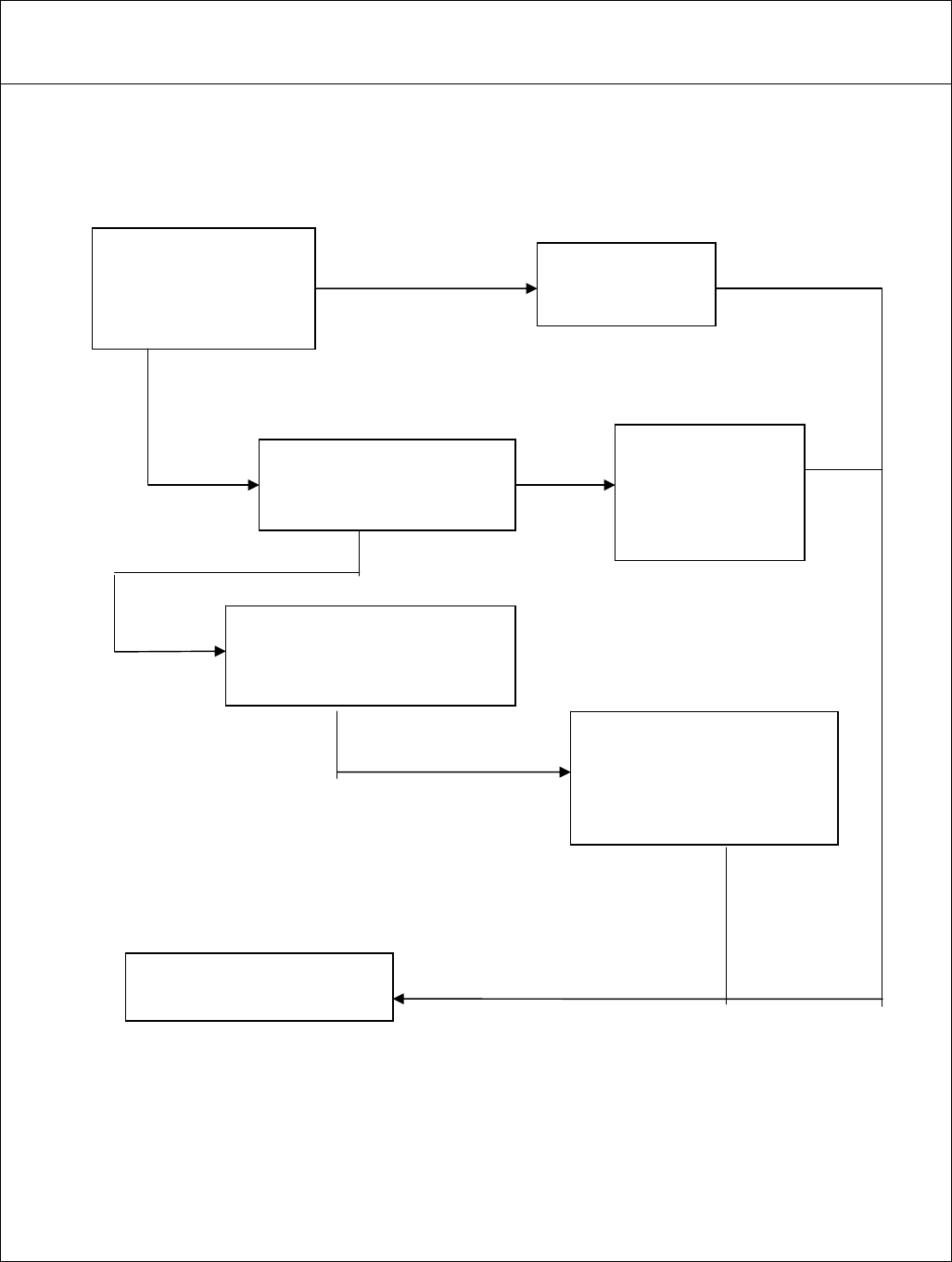

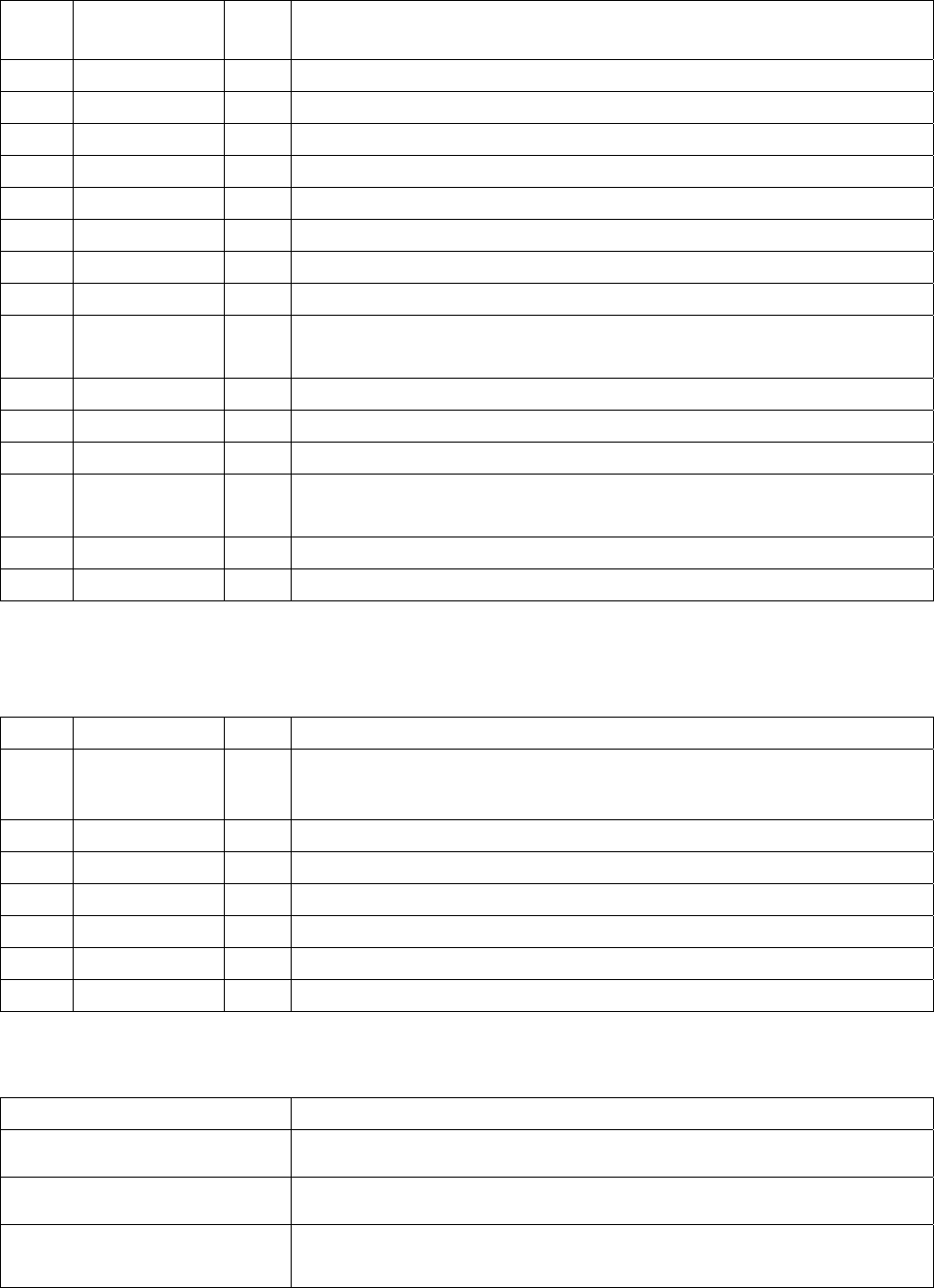

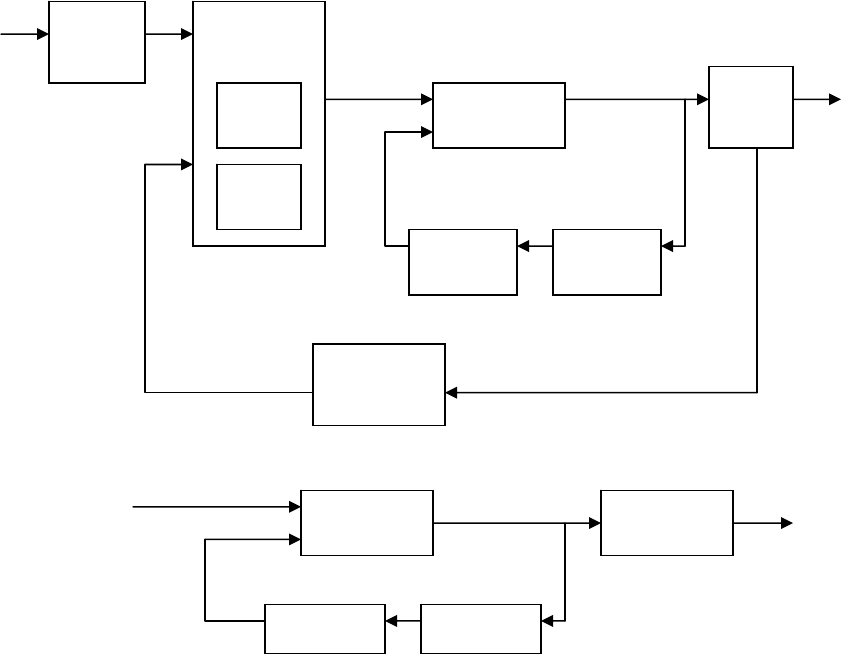

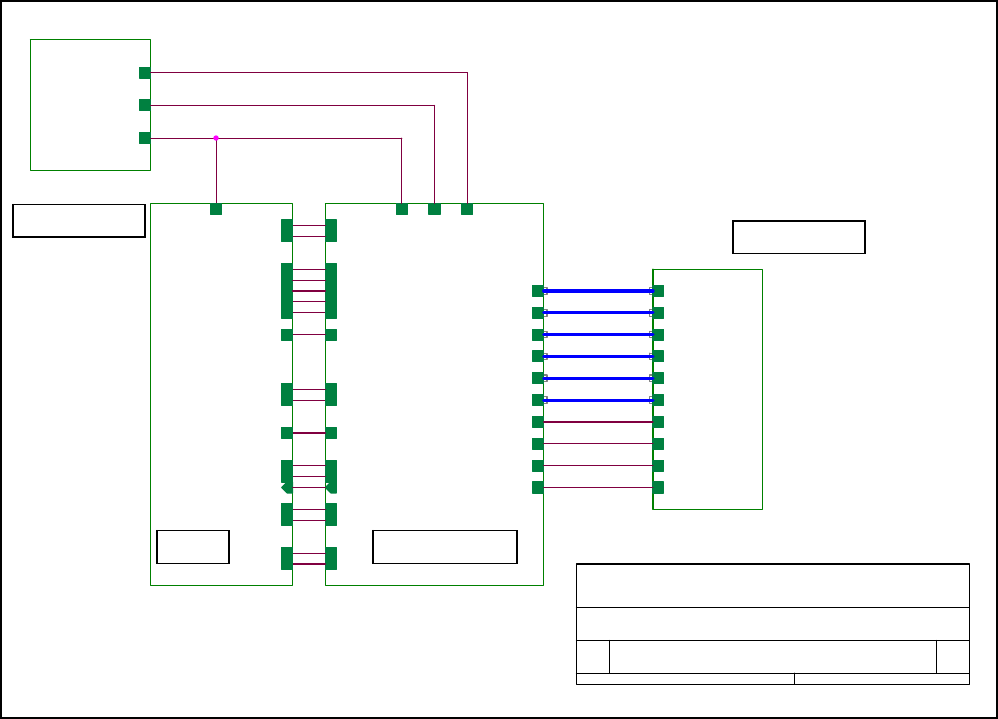

Monitor Block Diagram

1-3 Interface Connectors

(A) AC-Power Cable

(B) Video Signal Connectors and Cable

(C) External Adapter

Inverter

Flat Panel and

CCFL backlight

Main Board or Interface Board

Keyboard

RS232 Connector

For white balance

adjustment in

factory mode

ADAPTER HOST Computer

CCFT Drive.

AC-IN

100v-240v Video signal, DDC

5

2. PRECAUTIONS AND NOTICES

2-1 ASSEMBLY PRECAUTION

(1) Please do not press or scratch LCD panel surface with anything hard. And do not soil LCD panel surface

by touching with bare hands (Polarizer film, surface of LCD panel is easy to be flawed)

In the LCD panel, the gap between two glass plates is kept perfectly even to maintain display

characteristic and reliability. If this panel is subject to hard pressing, the following occurs :

(a) Uniform color (b) Orientation of liquid crystal becomes disorder

(2) Please wipe out LCD panel surface with absorbent cotton or soft cloth in case of it being soiled.

(3) Please wipe out drops of adhesive like saliva and water in LCD panel surface immediately.

They might damage to cause panel surface variation and color change.

(4) Do not apply any strong mechanical shock to the LCD panel.

2-2 OPERATING PRECAUTIONS

(1) Please be sure to unplug the power cord before remove the back-cover. (be sure the power is turn-off)

(2) Please do not change variable resistance settings in MAIN-BOARD, they are adjusted to the most suitable

value. If they are changed, it might happen LUMINANCE does not satisfy the white balance spec.

(3) Please consider that LCD backlight takes longer time to become stable of radiation characteristic in low

temperature than in room temperature.

(4) Please pay attention to displaying the same pattern for very long-time. Image might stick on LCD.

2-3 STORAGE PRECAUTIONS

(1) When you store LCD for a long time, it is recommended to keep the temperature between 0℃-40℃

without the exposure of sunlight and to keep the humidity less than 90% RH.

(2) Please do not leave the LCD in the environment of high humidity and high temperature such as 60℃

90%RH.

(3) Please do not leave the LCD in the environment of low temperature; below -15℃.

2-4 HIGH VOLTAGE WARNING

The high voltage was only generated by INVERTER module, if carelessly contacted the transformer on this

module, can cause a serious shock. (the lamp voltage after stable around 600V, with lamp current around 8mA,

and the lamp starting voltage was around 1500V, at Ta=25℃)

6

3. OPERATING INSTRUCTIONS

This procedure gives you instructions for installing and using the LM700 LCD monitor display.

1. Position the display on the desired operation and plug–in the power cord into External Adapter AC outlet.

Three-wire power cord must be shielded and is provided as a safety precaution as it connects the chassis

and cabinet to the electrical conduct ground. If the AC outlet in your location does not have provisions for

the grounded type plug, the installer should attach the proper adapter to ensure a safe ground potential.

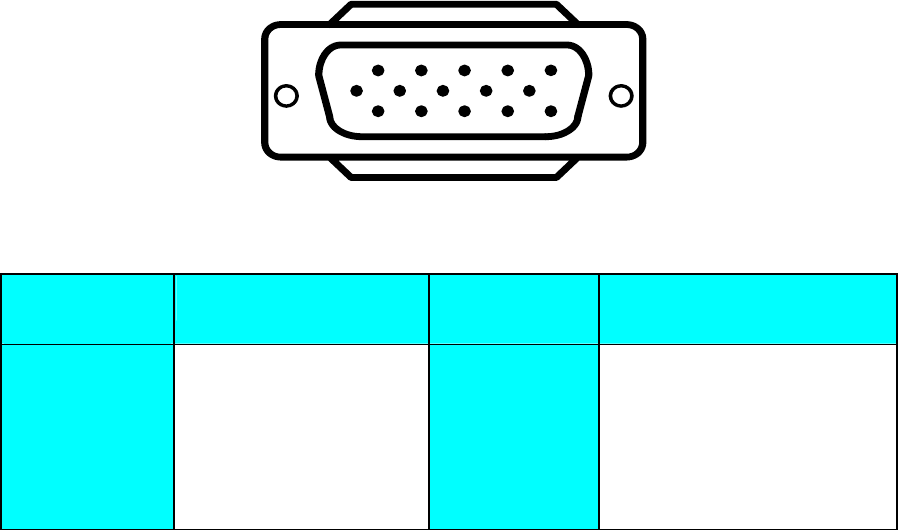

2. Connect the 15-pin color display shielded signal cable to your signal system device and lock both screws

on the connector to ensure firm grounding. The connector information is as follow:

15 - Pin Color Display Signal Cable

PIN NO.

DESCRIPTION

PIN NO.

DESCRIPTION

1. RED 9. 5V power from VGA-card

2. GREEN 10. GND

3. BLUE 11. SYNC. GND

4. GND 12. SDA

5. GND 13. HORIZ. SYNC

6. GND-R 14. VERT. SYNC

7. GND-G 15. SCL

8. GND-B

3. Apply power to the display by turning the power switch to the "ON" position and allow about thirty

seconds for Panel warm-up. The Power-On indicator lights when the display is on.

4. With proper signals feed to the display, a pattern or data should appear on the screen, adjust the brightness

and contrast to the most pleasing display, or press auto-key to get the best picture-quality.

5. This monitor has power saving function following the VESA DPMS. Be sure to connect the signal cable

to the PC.

6. If your LM700 LCD monitor requires service, it must be returned with the power cord & Adapter.

1

6

11 15

5

10

7

4. ADJUSTMENT

4-1 ADJUSTMENT CONDITIONS AND PRECAUTIONS

Adjustments should be undertaken only on following function : contrast, brightness focus, clock, h-position,

v-position, red, green, blue since 6500 color & 7800 color.

4-2 ADJUSTMENT METHOD

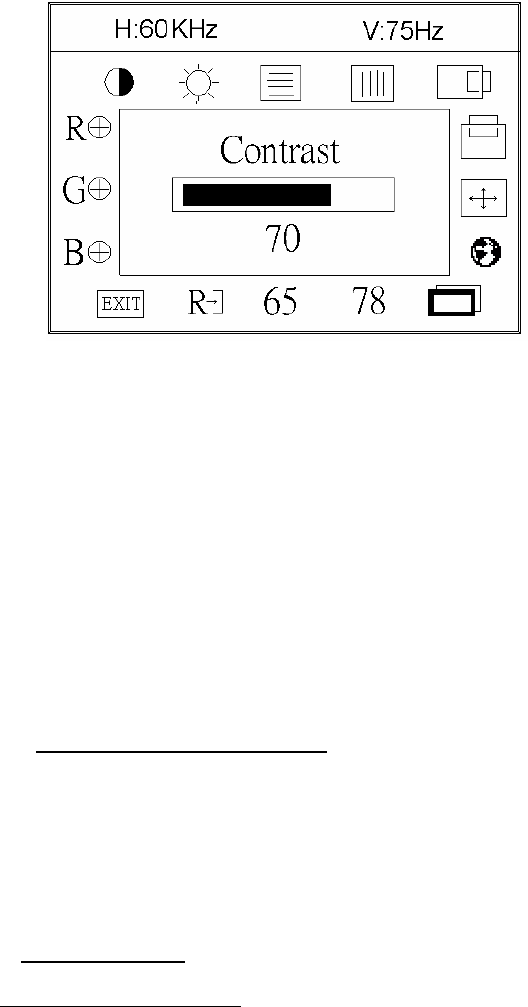

Press MENU button to activate OSD Menu or make a confirmation on desired function, Press Left/Right button

to select the function or done the adjustment.

1. White-Balance, Luminance adjustment

Approximately 30 minutes should be allowed for warm up before proceeding white balance

adjustment.

Before started adjust white balance ,please setting the Chroma-7120 MEM. Channel 5 to 7800 color and

MEM. channel 6 to 6500 color, ( our 7800 parameter is x = 296 ±10, y = 311 ±10, Y = 160 ±5cd/m2

and 6500 parameter is x = 313 ±10, y = 329 ±10, Y = 160 ±5 cd/m2)

How to setting MEM.channel you can reference to chroma 7120 user guide or simple use “ SC” key and

“ NEXT” key to modify xyY value and use “ID” key to modify the TEXT description

Following is the procedure to do white-balance adjust

Press MENU button during 2 seconds along with plug in the DC-power cord will activate the factory

mode, and the OSD screen will located at left top of panel.

I. Bias (Low luminance) adjustment :

1. Press “ AUTO” button , and wait for message “ Pass” ,check the Blacklevel value on

OSD should be large than 30, if less than 30 that means the offset calculation FAIL,

please manual adjust the blacklevel to value 43

2. set the contrast and brightness on OSD window to maximal value , RGB to “50”

3. adjust the VR501 on INTERFACE board until chroma 7120 measurement reach the

value Y=240 cd/m2 ±5 cd/m2

II. Gain adjustment :

a. adjust 7800 color-temperature

4. Set the Contrast of OSD function to 40, Brightness to 48

5. Switch the chroma-7120 to RGB-mode (with press “MODE” button )

6. switch the MEM.channel to Channel 05 ( with up or down arrow on chroma 7120 )

7. The lcd-indicator on chroma 7120 will show x = 296 ±10, y = 311 ±10, Y = 160 ±5

cd/m2

8. Adjust the RED on OSD window until chroma 7120 indicator reached the value

R=100

8

9. adjust the GREEN on OSD, until chroma 7120 indicator reached G=100

10. adjust the BLUE on OSD, until chroma 7120 indicator reached B=100

11. repeat above procedure ( item 8,9,10) until chroma 7120 RGB value meet the tolence

=100±2

12. switch the chroma-7120 to xyY mode With press “MODE” button

13. Adjust the Contrast on OSD window until the Y measurement on chroma 7120 reached

the value Y= 180 cd/m2

14. Press 78 on OSD window to save the adjustment result

b. adjust 6500 color-temperature

1 Set the Contrast of OSD function to 40, Brightness to 48

2 Switch the chroma-7120 to RGB-mode (with press “MODE” button )

3 switch the MEM.channel to Channel 06 ( with up or down arrow on chroma 7120 )

4 The lcd-indicator on chroma 7120 will show x = 313 ±10, y = 329 ±10, Y = 160 ±5

cd/m2

5 Adjust the RED on OSD window until chroma 7120 indicator reached the value R=100

6 adjust the GREEN on OSD, until chroma 7120 indicator reached G=100

7 adjust the BLUE on OSD, until chroma 7120 indicator reached B=100

8 repeat above procedure ( item 5,6,7) until chroma 7120 RGB value meet the tolence =100

±2

9 switch the chroma-7120 to xyY mode With press “MODE” button

10 Adjust the Contrast on OSD window until the Y measurement on chroma 7120 reached

the value Y= 180 cd/m2

11 Press 65 on OSD window to save the adjustment result

Turn the POWER-button off to on to quit from factory mode ( in USER-mode, the OSD window

location was placed at middle of screen)

9

2. Clock adjustment

Set the Chroma at pattern 63 (cross-talk pattern) or WIN98/95 shut-down mode (dot-pattern).

Adjust until the vertical-Stripe-shadow as wide as possible or no visible.

This function is adjust the PLL divider of ADC to generate an accurate pixel clock

Example : Hsyn = 31.5KHz Pixel freq. = 25.175MHz (from VESA spec)

The Divider number is (N) = (Pixel freq. x 1000)/Hsyn

From this formula, we get the Divider number, if we fill this number in ADC register (divider register),

the PLL of ADC will generate a clock which have same period with above Pixel freq.(25.175MHz) the

accuracy of this clock will effect the size of screen.(this clock was called PIXEL-CLOCK)

3. Focus adjustment

Set the Chroma at pattern 63 (cross talk pattern) or WIN98/95 shut down mode (dot-pattern).

Adjust the horizontal interference as less as possible

This function is adjust the phase shift of PIXEL-CLOCK to acquire the right pixel data .

If the relationship of pixel data and pixel clock not so match, we will see the horizontal interference on

screen ,we only find this phenomena in crosstalk pattern or dot pattern , other pattern the affect is very

light

4. H/V-Position adjustment

Set the Chroma to pattern 1 (crosshatch pattern) or WIN98/95 full-white pattern confirm above item 2 & 3

functions (clock & focus) was done well, if that 2 functions failed, the H/V position will be failed too.

Adjust the four edge until all four-edges are visible at the edge of screen.

5. MULTI-LANGUAGE function

There have 5 language for selection, press “MENU” to selected and confirm , press “ LEFT” or “ RIGHT”

to change the kind of language ( English , Deutch , Francais, Espanol, Italian)

6. Reset function

Clear each old status of auto-configuration and re-do auto-configuration ( for all mode)

This function also recall 7800 color-temperature , if the monitor status was in “ Factory-mode” this reset

function will clear Power-on counter ( backlight counter) too.

7. OSD-LOCK function

Press Left & Right key during switching on the monitor, the access to the OSD is locked, user only has

access to “ Contrast, Brightness, Auto-key “.

If the operator pressed the Left & Right during switching on the monitor again , the OSD is unlocked.

8. View Power-on counter and reset the Power-on counter( if not necessary , no suggest to entry factory

mode)

The Power-on counter was used to record how long the backlight of panel already working, the backlight

life time was guarantee minimal 25000 hours, the maintainer can check the record only in factory mode.

Press MENU button for 2 seconds along with plug-in DC power cord will be in factory mode, and the

OSD screen will located at left top of panel but take cautions don’t press icon “78” & “65”, if you

press 78/65 , your white-balance data will overlap with the new-one, and you must perform the white-

balance process again.

The result of counter was place at top of OSD, the maximal of record memory was 65000 hours, if exceed

65000 hours the counter will keep in 65000 hours until press “ RESET” at osd-menu in factory mode.

The “ RESET” function in factory mode will execute following function:

1. clear the Power-on counter to zero hours

2. clear old auto-configuration status for all mode , so the monitor will automatically re-do auto-config

when change to next mode or power on-off

4-3 FRONT PANEL CONTROL KNOBS

Power button : Press to switch on or switch off the monitor.

Auto button : to perform the automatic adjustment from CLOCK, FOCUS, H/V POSITION, but no affect the

color-temperature

Left/Right button : select function or do an adjustment.

MENU button : to activate the OSD window or to confirm the desired function

10

5. CIRCUIT-DESCRIPTION

5-1 SPECIAL FUNCTION with PRESS-KEY

A). press Menu button during 2 seconds along with plug-in the DC Power cord:

That operation will set the monitor into “Factory- mode”, in Factory mode we can do the White balance

adjustment with RS232 , and view the Backlight counter (this counter is use to record the panel activate

hours ,for convenient the maintainer to check the panel backlight life time)

In Factory mode, OSD-screen will locate in left top of screen.

Press POWER-button off to on once will quit from factory mode and back to user-mode.

B). Press both Left & Right button along with Power button off to on once will activate the OSD-LOCK

function, repeat this procedure will disable OSD-LOCK

In OSD-LOCK function, all OSD function will be lock , except Contrast and Brighness

OSD-INDEX EXPLANATION

1. CABLE NOT CONNECTED: Signal-cable not connected.

2. INPUT NOT SUPPORT:

a. INPUT frequency out of range: H > 81kHz, v > 75Hz or H < 28kHz, v < 55Hz

b. INPUT frequency out of VESA-spec. (out of tolerance too far)

3. UNSUPPORT mode, try different Video-card Setting:

Input frequency out of tolerance, but still can catch-up by our system (if this message show, that means, this

is new-user mode, AUTO-CONFIG will disable)

5-2 THE Different on MAINBOARD or other ACCESSORY when using different PANEL type

1). The MCU software should be change

example : for CHI-MEI panel , the MCU part-number is 56A-1125-61-M

for Hyundai panel , the MCU part-number is 56A-1125-61-Y

and the other ACCESSORY when use different panel type should be change as following:

1). The INVERTER module for CHI-MEI panel part-number is 79AL17-1-S

for Hyundai panel the INVERTER part number is 79A-L17-3-S

2). The cable to Panel side for CHI-MEI panel part number is 95A8018-30-1

for HYUNDAI panel is 95A8018-30-3

3). The Dsub cable for CHI-MEI is 89A-174D-5BF-GLF,

for Hyundai is 89A-174-L17-3.

4). The Mechanical accessory is change or adding as follow;

CHI-MEI PANEL M170E1 Hyundai PANELHT17E11-100

MAIN-FRAME 15A5684-1 15A5705-1

Panel 750ALCD170-3 750ALCD170-4

11

5-3 SIMPLE-INTRODUCTION about LM700 chipset

1. GMZAN1 ( all-in-one chip solution for ADC, OSD, scalar and interpolation) :

USE for computer graphics images to convert analog RGB data to digital data with interpolation process,

zooming, generated the OSD font , perform overlay function and generate drive-timing for LCD-PANEL.

2. M6759 (ALI- MCU, type 8052 series with 64k Rom-size and 512 byte ram) :

Use for calculate frequency, pixel-dot , detect change mode, rs232-communication, power-consumption

control, OSD-index warning , …etc.

3. 24LC21 (MicroChip IC) :

EePROM type, 1K ROM-SIZE, for saving DDC-CONTENT.

4. 24C04 (ATMEL IC) :

EePROM type, 4K ROM-SIZE, for saving AUTO-config data, White-balance data, and Power-key status

and Backlight-counter data.

5. LM2569S( NS brand switching regulator 12V to 5V with 3A load current) .

6. AIC 1084-33CM (AIC brand linear regulator 5V to 3.3V)

7. LVDS ( use NOVATEK NT7181F)

Convert the TTL signal to LVDS signal

The advantage of LVDS signal is : the wire can be lengthen and eliminate wire number , low EMI .

LVDS signal is high frequency but low voltage, only 0.35 VPP ,the frequency is seven times higher than TTL

MODULE-TPYE COMPONENT :

1. ADAPTER : CONVERSION-module to convert AC 110V-240V to 12VDC, with 5.0 AMP

2. INVERTER : CONVERSION-module to convert DC 12V to High-Voltage around 1600V, with frequency

30K-80Khz, 7mA-9Ma

12

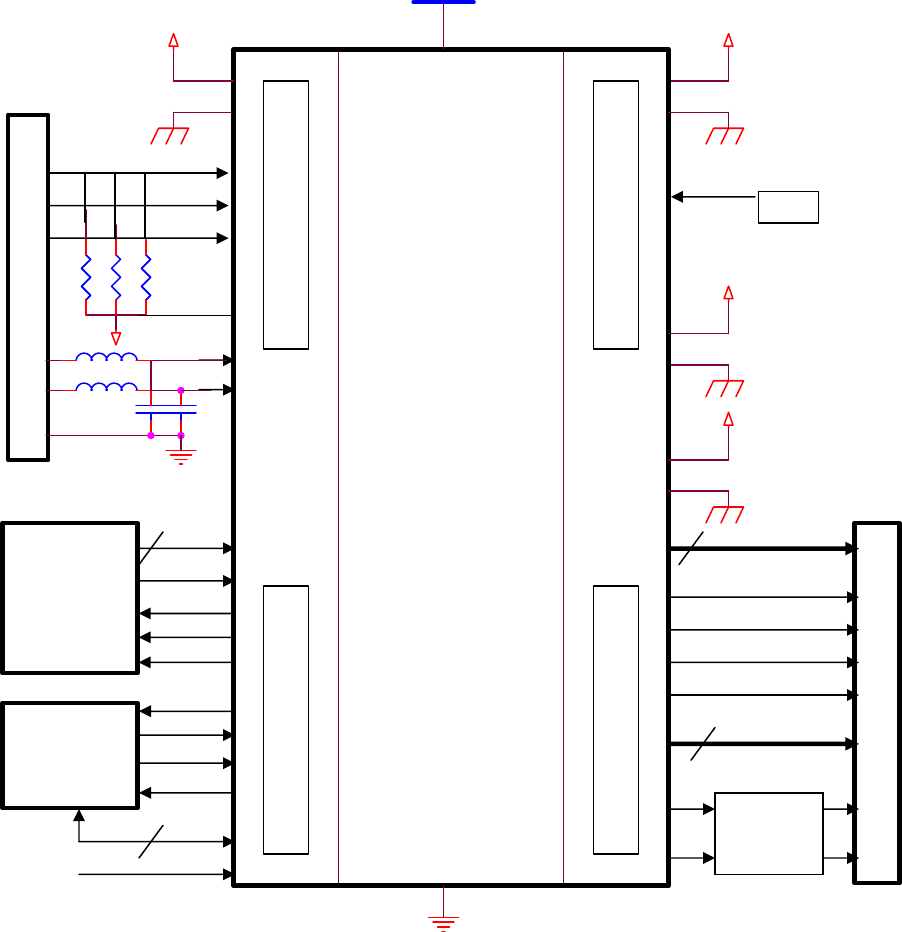

GMZAN1 (U200)

LVDS chip (U601,

U602)

Panel-Power Control

(U202)

MCU ( U302 )

Data Digital RGB

Panel Control Signal:

Dhs, Dvs, Dclk

Panel Power 5V

Communication signal:

Hclk,Hfs,Hdata0

Input analog RGB &

H,V,& ddc signal &

Rs232 communication

Oscillator 50 mhz

Cr

y

stal 20

m

hz

DDC-chi

p

PANEL

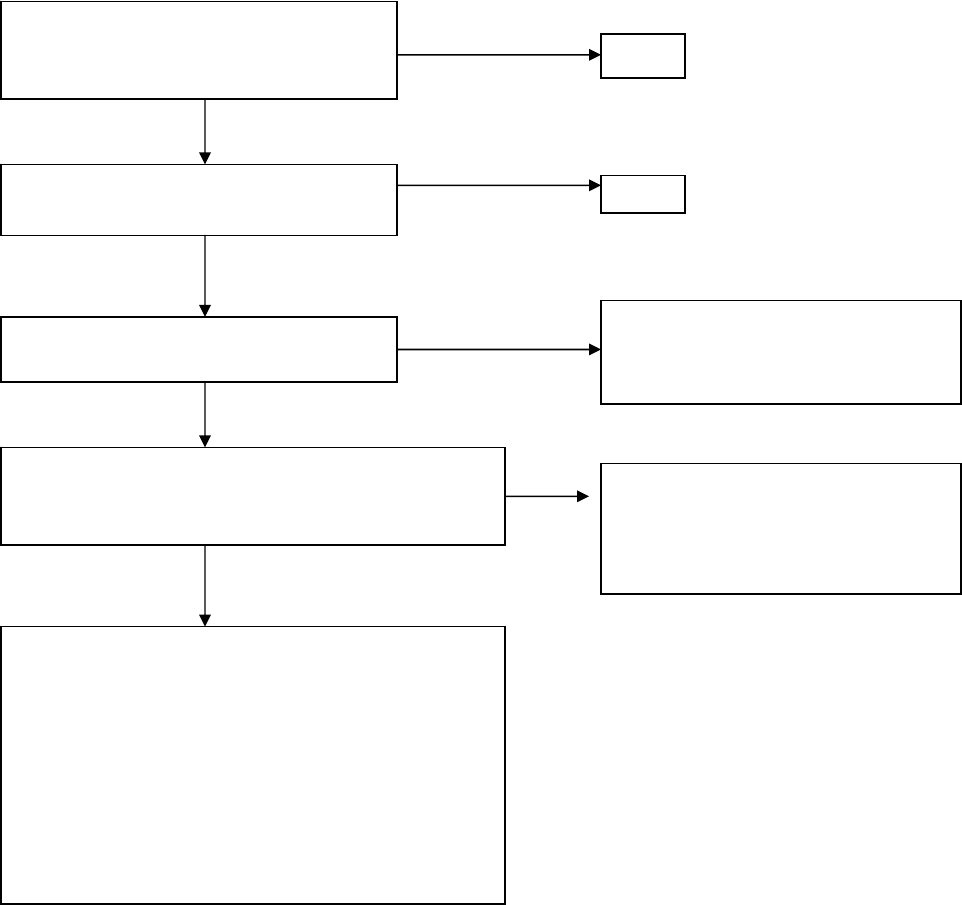

Main-board Block diagram

INVERTER module

Keyboard module

EXTERNAL-

ADAPTER

DC 12V 5Amp

13

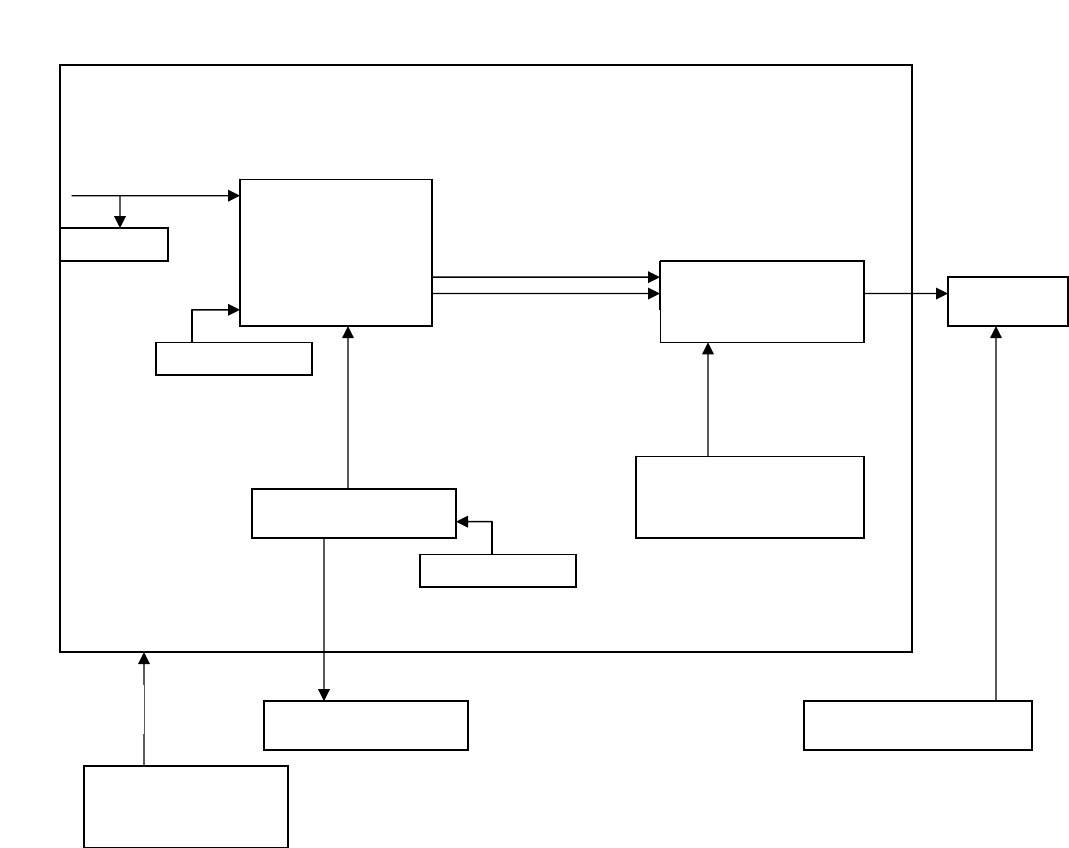

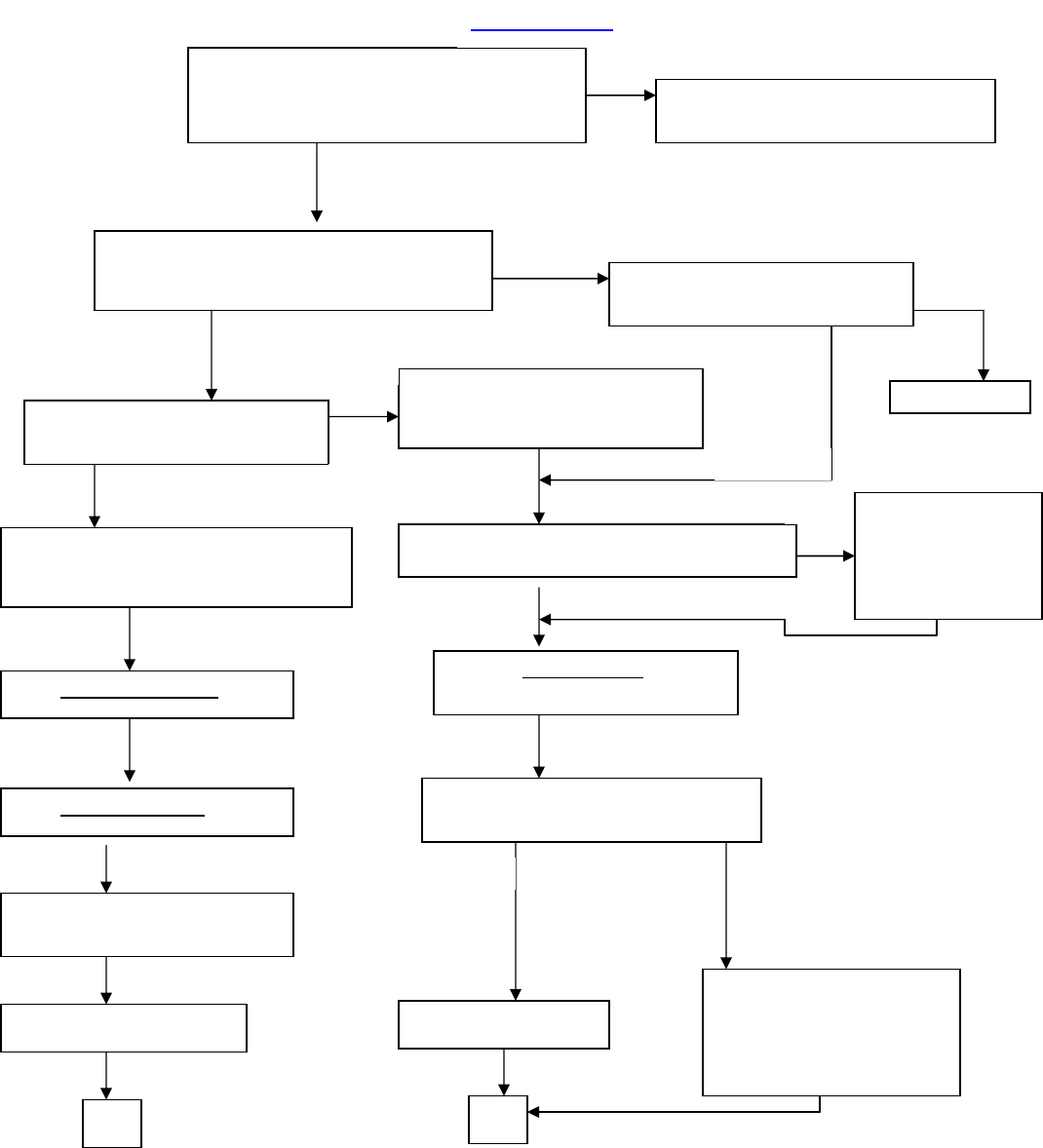

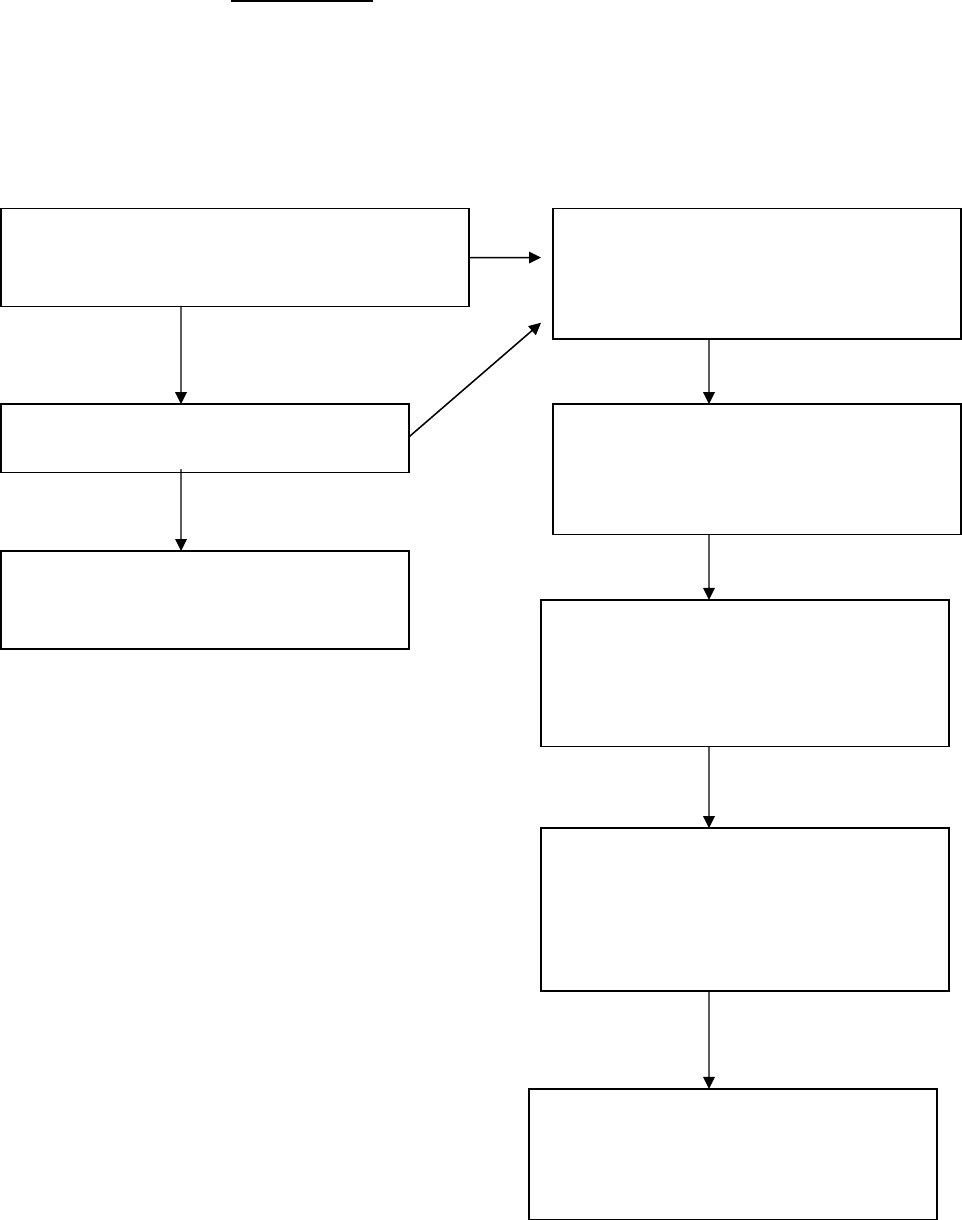

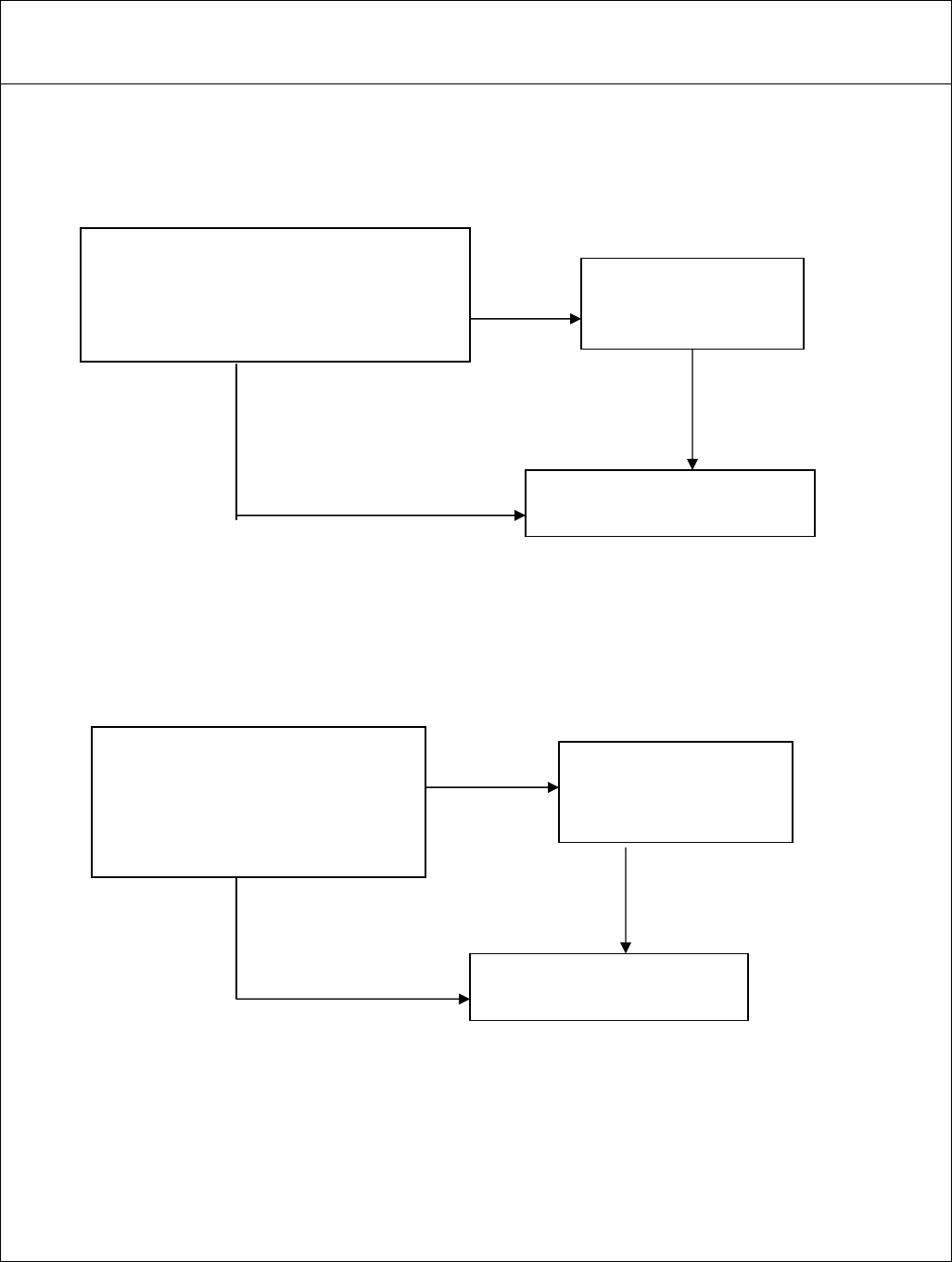

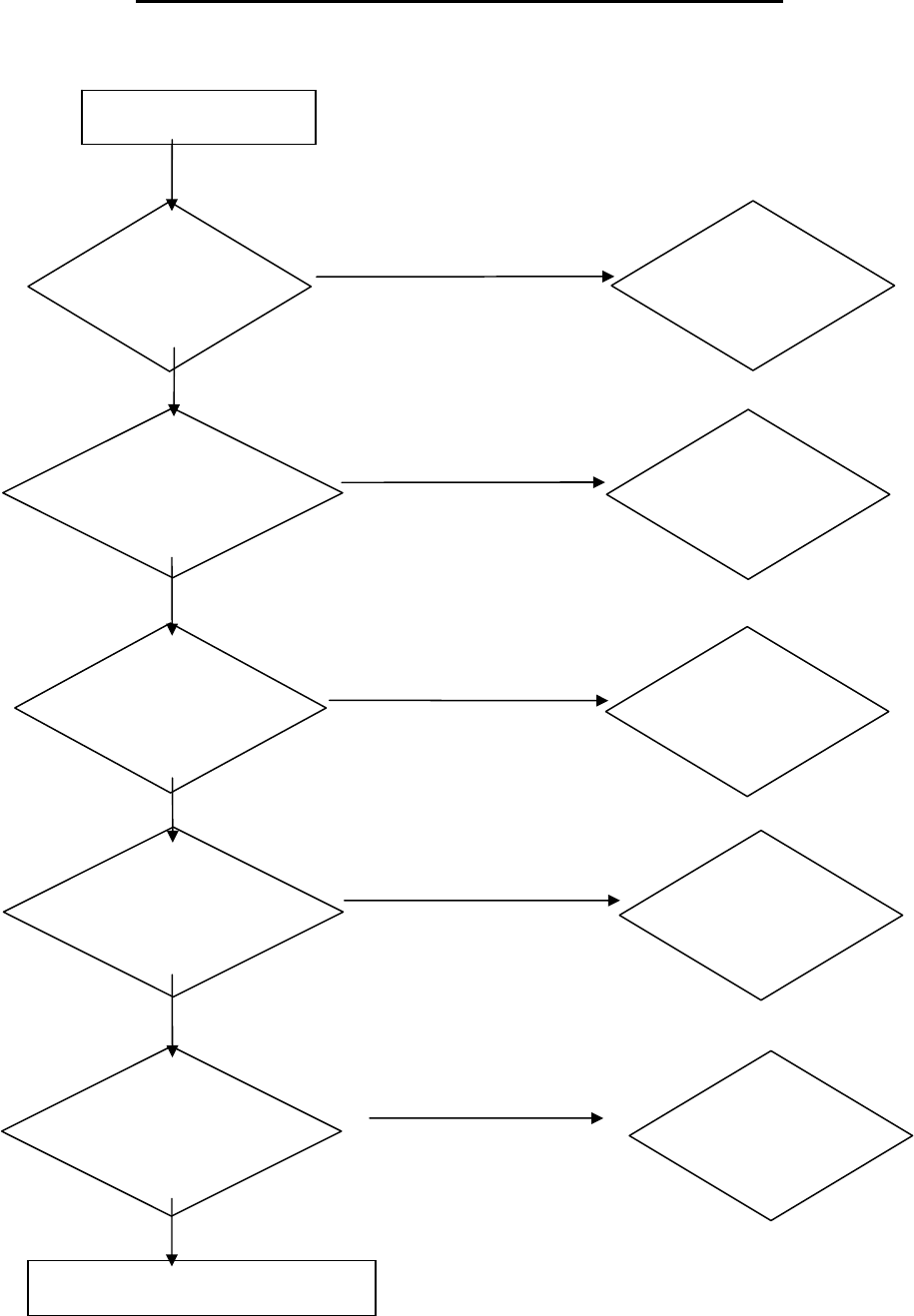

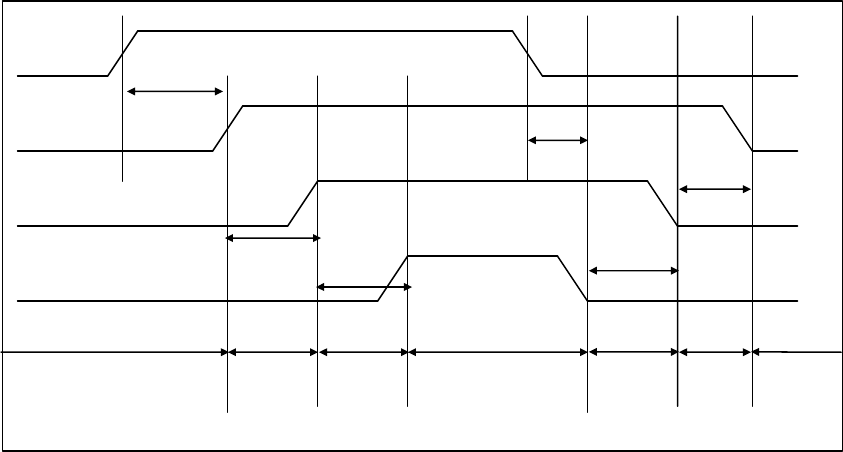

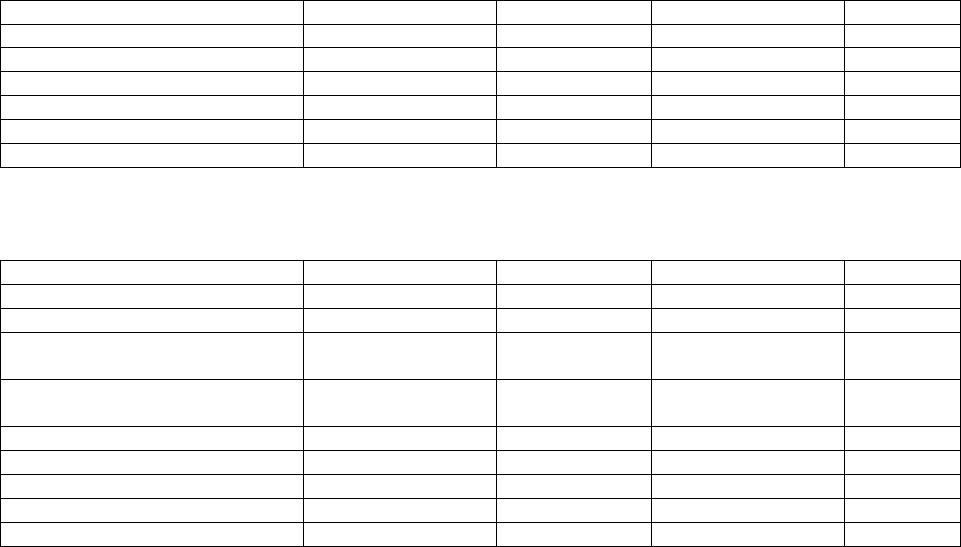

5-4 SOFTWARE FLOW CHART

I. Power-On Subrotine CHART

OK

Check White-balance data(6500 & 7800) same with the

backup data ?

Check POC( backlight counter) data same with the backup

data ?

IF not same, overwrite the data with backup value.

Initial GMZAN1

Yes

POWER-ON START

Initial MCU I/O, Interrupt vector & Ram

Initial 1.POC (backlight counter)

2. Clr all mode value

Yes

Check if in Factory mode?(when power-on,press the

MENU Button will be in FACTORY mode) SET factor

y

mode fla

g

Check Previous power-switch status from Eeprom, & other system status

MAIN-SUBROTINE LOOP

No

Check Eeprom is empty ?

Clear factor

y

mode fla

g

No

14

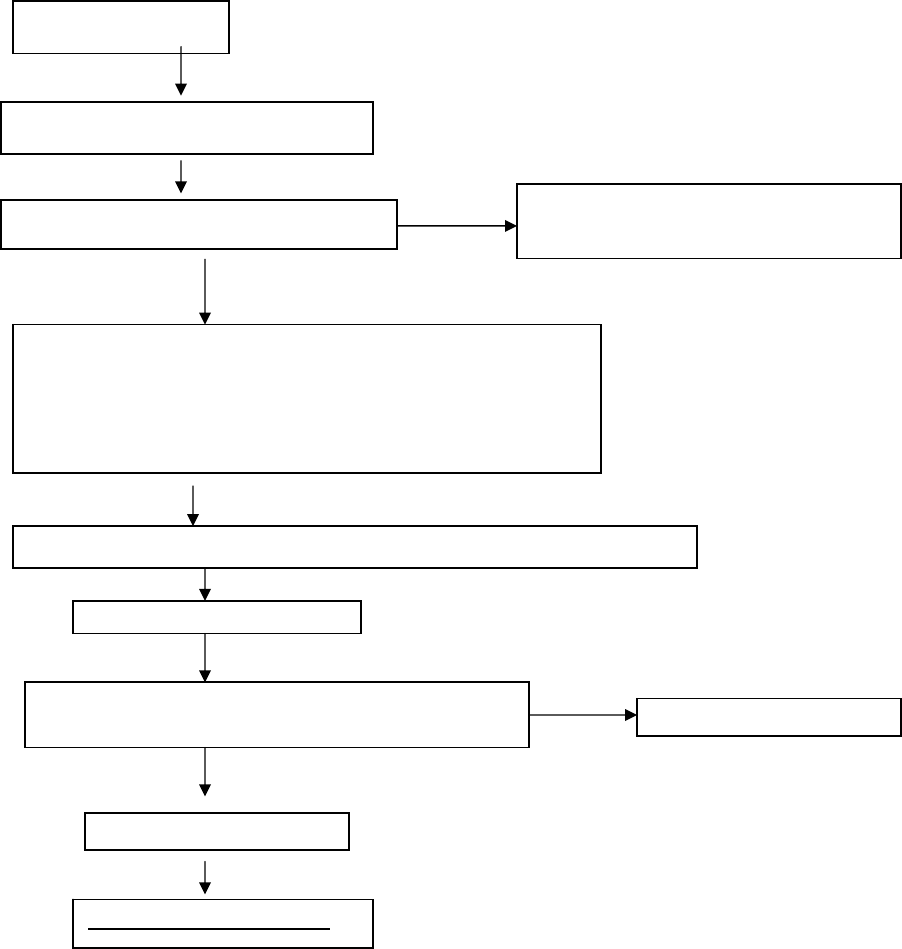

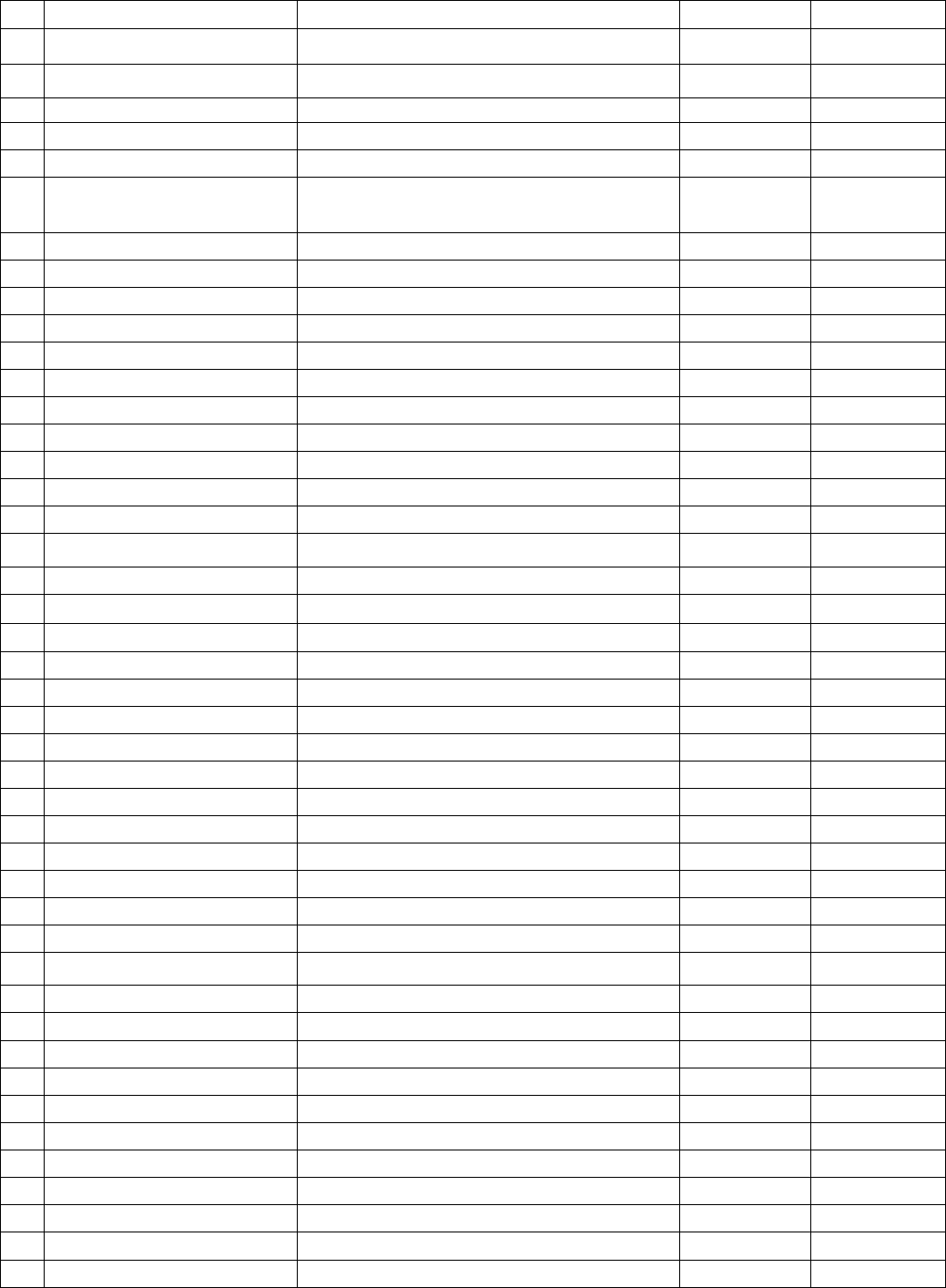

II. MAIN SUBROTINE LOOP

)

Main loop start

Process Power-saving status ( according to below flow-chart result)

Check GMZAN IFM status .is change or not.

And check Signal cable status ( cable not connected or not )

** IFM is the register which measured the HSYN & Vsyn status

Is current system status in Power-saving ?

Yes, IFM have change Wake-up GMZAN1

(because GMZAN1 was in

partial sleeping state)

Yes

Check the IFM result is in the standard

Mode table ?

No

Check the IFM result is in the user mode

table ?

Out of range ( input not support) be

confirm

Set mode index & parameter

Set change mode flag

No

No

Yes

Yes

confirm the frequency ( Hsyn or Vsyn) from IFM already

been changed ? ( check the change mode flag)

Process ( turn off OSD , setting GMZAN1according to

above parameter,set LED status, set backlight status)

Check Auto-config mode flag already been set?

No

Do Auto-config

automatically

Read Key status and Process on OSD-screen

Check Factory mode flag= 1

No

Yes , freq had been change

Monitoring the time-out of osd status ( if no key input persist for

10 sec , the osd time-out counter will trigger )

No

if the RS232 buffer is full,

process the command( while

adjust white-balance in factory

mode)

Yes

No

Yes

15

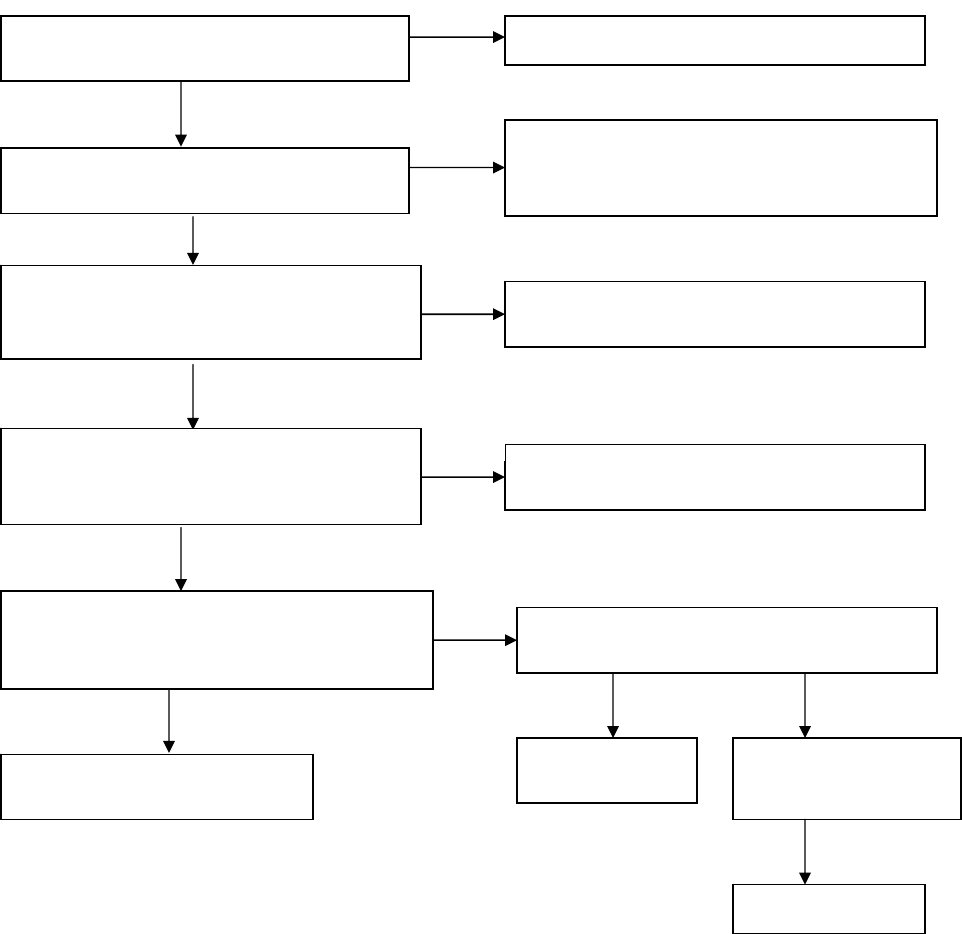

6. A). Interface-Board Trouble-Shooting chart

*Use the PC Win 98 white pattern, with some icon on it, and Change the Resolution to 640x480 60 Hz / 31 KHz

**NOTICE : The free-running freq. of our system is 48 KHz / 60 Hz, so we recommend to use another

resolution to do trouble shooting, this trouble shooting is proceed with 640x480 @60Hz 31Khz

I. NO SCREEN APPEAR

Note: 1. if Replace “MAIN-BOARD” , Please re-do “DDC-content” programmed & “WHITE-Balance”.

2. if Replace “ INVERTER” only, Please re-do “ WHITE-Balance”

Disconnected the Signal cable( Loose the

Signal cable ),Is the screen show “Cable Not

Connected” ?

Connected the Signal cable again,

Check LED status.

No

,

nothin

g

is show

Yes, there have OSD show

Connected the Signal cable again,

Check LED status.

Check the Wire-Harness from CN601,CN602

was tight enough?,

check the Wire connection to panel side too

OK,Wire tight enough

Led Green

Check Panel-Power Circuit Block

Check U200 Data-output Block

OK,Panel Power OK

Replace Inverter and Check

Inverter control relative circuit

Re-do White balance adjust

OK, U200 data OK

Check Power switch is in Power-on

status , and check if Power switch had

been stuck ?

Measured RGB (r200,r201,r202) H,V Input at U401

p

in 9

,

4

,

was there have si

g

nal ?

Measured Oscillator Block

Oscillator U201 & Crystal X300

Check communication pin between U200 &

MCU pin 2,6,7. , is it have transition?

Led Oran

g

e

Replace U200 (Gmzan1)

OK

,

Ke

y

board no stuc

k

OK

,

in

p

ut Normal

OK

,

clock normal

OK

,

Mcu have transition

Replace U302 (MCU)

& check Reset pin 10

must be change from High to

low when first AC power plug-

in

NG

,

no transition

Led oran

g

e

OK OK

R

ep

la

ce

M

CU

Led Green

Measured Input DC-voltage ( J1)= 12 V?

Measured U305 AIC 1084 pin 2 = 3.3V?

Measured U904 LT1117 pin 2= 3.3V?

Yes

,

all DC level exist

Check Correspondent component.

Is there any shortage or cold solder?

DC-Power Part

Check Correspondent

component short/open

( Protection Diode )

and Signal cable

bad ?

NG

16

PANEL-POWER CIRCUIT

INVERTER Control Relative Circuit

OSCILLATOR BLOCK

U200-DATA OUTPUT

OK,R225 have response

check R225 should have response from 12V to 0V

When we switch the power switch from on to off

Check the PPWR panel power relative circuit,

R223, Q200,U202(pin 5,6,7,8)

In normal operation, when LED =green, R223

should =0 v,

If PPWR no-response when the power switch

Turn on and turn off, replace the U200-GMZAN1

NG

Measured the U202 pin 5,6,7,8= 5 V? Replace U202 ( Nmos, SI9933

)

NG

,

no Volta

g

e

OK

Replace INVERTER-module

& Re-do white balance

Replace INVERTER to new-one, and

Check the screen is normal ??

Measured the inveter connector CN303

Pin 1=12V, pin 3 on/off control=5V (on)

NG, still no screen

Check the Bklt-On relative circuit, R315, Q304, R311,

In normal operation, when LED =green,

R315 Bklt-On should =0 v,

If Bklt-On no-response when the power switch turn on-off,

Re

p

lace the MCU

NG

NG

O

K

OK

Measured U201 Oscillator output R215= 50mhZ ? Replace Oscillator U201

NG,no trans

ition

OK, has transition

Measured X300 Crystal output R340= 20mhZ ? Replace Crystal X300

NG,no transition

OK

Measured PCLK(L207)

PVS,PHS (pin 73,74 from U200 )

Is there have any transition?

Pclk around 47MHz to 57MHZ ,

PVS=60.09Hz , PHS around 67 KHz ??(refer to

input signal=640x480@60 Hz 31k, and LED is

green)

Replace GMZAN1 (U200) or replace

MAINBOARD.

NG , no transition

OK

If MainBoard being replace , please

do the DDC – content reprogrammed

Check U202 pin 1,2,3,4= 5V

Yes

Check U304 relative circuit.(R905,T300..)

NG

17

II (a) THE SCREEN is Abnormal , stuck at white screen, OSD window can’t appear, but

keyboard & LED was normal operation.

At general, this symtom is cause by missing panel data or panel power, so we must check our

wire-harness which connected to panel or the panel power controller (U202)

II. (b)The screen had the Vertical Straight Line, might be stuck in Red, Green, Blue

That symptom is cause by bad Panel issue ( might be the Source IC from Panel is cold solder or

open loop ) so REPLACE THE PANEL TO NEW ONE.

Check if the Wire harness from CN601 & CN602 loose?

Check the wire on both Panel-side and Mainboard side.

Check the Panel-Power circuit as above (page 15)

U202 pin 5,6,7,8 ,must be 5V

Yes, tight enough

Yes, Voltage normal

Check the LVDS-Power L603,L604,L601,L602,L900= 3.3V ?

Check the both U601 & U602 LVDS-Input pin 31= 45mhz –

65mhz, and pin 27 = Vsyn freq, pin 28 = 45khz- 65 khz

Yes, Voltage normal

Yes, Frequency normal

Replace both LVDS chip ( U601 & U602)

Tighten it.

NG

Check U904,which convert the 5V to

3.3V

Check U200 DATA-OUPUT block as

above ( page 15)

NG

Check OSCILLATOR Block as

above ( page 15)

NG,no data output

Replace U302 MCU and check it RESET

pin 10 ,must be turn high to low when first

AC

p

owe

r

-on

OK,all clock is normal

Replace U200 GMZAN1

OK

,

reset is normal

Check U200 DATA-OUTPUT block again

NG

,

still no data out

18

KEYBOARD BLOCK check

OK

Check U302 pin 38 (LED green) will have

transition from hi to low or low to hi when we

press the power key??

Press power key and check U302 pin 43

= low (0V) ?

OK

Replace Tact-switch SW105 at keyboard if still

no work replace U302 MCU at main-board and

check MCU relative reset circuit, and crystal

OK

Check U302 MCU pin 43,42,41,40,39 at

High state(5V)? without press any key Mechanical was stuck, Check !

NG

NG

If still no Led green indicator, check Q102,

R106 & LED at keyboard !! cold solder or bad

NG, MCU no response

Check U302 pin 20= 20MHz ? and pin 44

(VDD)=5V ? and pin 10 (reset)=0V ? at normal

condition

If one of this item was NG, check the relative

circuit

NG

Without press key and change mode, Check U302

pin 16,17(sda,scl)= hi 5V ? or keep transition ?

OK

Check U300 eeprom 24LC04 relative circuit,

check U300 pin 7 = low?

Keep transition, that means eeprom no response

Check JP202 is

connect ?

NG

NG

Check U300 pin 8

(vdd)= 5V, and check

R300

,

R301 cold solde

r

OK

Replace eeprom

Replace U302 MCU

OK, no keep transition

19

POWER-BLOCK check

**Note : the Waveform of U304 pin 2 can determined the power situation

1. stable rectangle waveform with equal duty, freq around 150K-158KHz

that means all power of this interface board is in normal operation

,and all status of 5V & 3.3V is working well

2. unstable or uneven rectangle waveform without same duty, that means ABNORMAL operation was

happened, check 3.3V or 5V ,if short-circuit or bad component

3. rectangle waveform with large spike & harmonic pulse on front side , means all 3.3v is no load, U200

Gmzan1 was shut-down, and only U302 MCU still working , that means the monitor is in power saving

status , all power system is working well .

OK

Check U304 pin 2 is a stable rectangle wave?

Around 150k-158kHz stable rectangle wave

with equal duty without any spike or harmonic

pulse?

OK

NG, with

harmonic

p

ulse

Check U304 pin 2 is a unstable rectangle wave ?

The interface board power is good

Measure input power at U304 LM2596 pin 1=

12V ? Check ADAPTER and connector if loose?

NG

NG

Check all 3.3V & 5V power, there is

short circuit or bad component was

happened

OK

,

unstable wave

The interface board is in power-

saving state, press power key to wake

up & check your signal input

20

III.ALL SCREEN HAS INTERFERENCES OR NOISE, CAN’T BE FIXED BY AUTO KEY

** NOTE: There is so many kind of interferences, 1). One is cause by some VGA-CARD that not meet VESA spec or

power grounding too bad that influence our circuit

2).other is cause by external interferences, move the monitor far from electronic equipment.( rarely

happened)

Use DOT-pattern, or win98/99 shut-down

mode pattern, press “AUTO” key, was the

interferences disappear ??

Adjust “FOCUS” step by step, until the

horizontal interferences disappear

Does your signal-cable have an additional

cable for extension ??

END

END

Put away the additional cable

May be the additional cable grounding is

not quite well

Does your noise only exist in one mode only?

(ex: only at 1280x1024 @ 75 Hz, other is normal)

OK

OK

Yes, has extension

NG, interferences s

till exist

NG

NO additional extension cable

That was cause by you VGA-CARD setting, your VGA

card timing backporch/frontporch exceed vesa timing too

far, for some new AGP-VGA-CARD such situation

always happened

So in your control-panel icon ,select monitor ,setting ,

advance ,screen-adjust,at

Size icon, increase step by step slowly, press “”AUTO”

key every step you increase the SIZE . repeat the

procedure( increase/decrease SIZE one-step and press

AUTO) until the interferences disappear, press “APPLY”

to save in your VGA

Yes, only happened on one mode

Change the Signal-cable to new-one or

Try other brand VGA-CARD

(make sure just only that brand VGA-

CARD has this problem ,contact RD-

tai

p

ei

)

NO, all mode

21

There is an interferences in DOS MODE

NOTE :the criteria of doing AUTO-CONFIGURATION : must be a full-size screen, if the screen not full , the auto-

configuration will fail. So in dos mode ,just set your “CLOCK” in OSD-MENU to zero or use some EDITOR

software which can full fill the whole screen (ex: PE2, HE) and then press “AUTO”

Or you can use “DOS1.EXE” which attached in your Driver disk to optimize DOS mode performance

V. THE PANEL LUMINANCE WAS DOWN

Use white pattern and resolution 1280x1024 @ 60Hz , CHROMA 7120 measured the center of panel

Set Contrast, brightness =maximal, RGB= 50

Quit from OSD-screen, measured Y(luminance)

With chroma 7120, check Y= 240±10 CD/M2 ?

Adjust VR201 until maximal, measured Y =

240±10 cd/m2 ?

NG

NG

If the Y less than 160 cd/m2 (after the VR201=

MAX, contrast, brightness = max) then change the

LAMP of panel

If Y can reach >190 cd/m2 that means

The lamp still working well, so we just re-do the

white-balance process

As following procedure

OK

Use white-pattern, press MENU button along

with AC power-plug in ( you will in factory

mode) The OSD-menu will be at left-top of

screen,

press AUTO button to automatically adjust

blacklevel value, you will see the sign PASS ,if

FAIL , manual adjust the blacklevel until value 43 !

Set contrast, brightness to max, and turn the VR201

to max , wait for 20 minutes until the luminance Y

stable

The Y should be larger than 200 cd/m2

(for panel which already use for a year, the Y

luminance might be a little down, around 180

cd/m2, there is acceptable too)

Follow this manual page 7 item 4-2 method to

more detail procedure for do a white-balance

adjust

OK

22

6 B). Inverter –MODULE Spec &Trouble Shooting Chart

In LM700 model , we use CHI-MEI panel, and the INVERTER PROVIDER is SAMPO-

CORPORATION

SAMPO CORPORATION

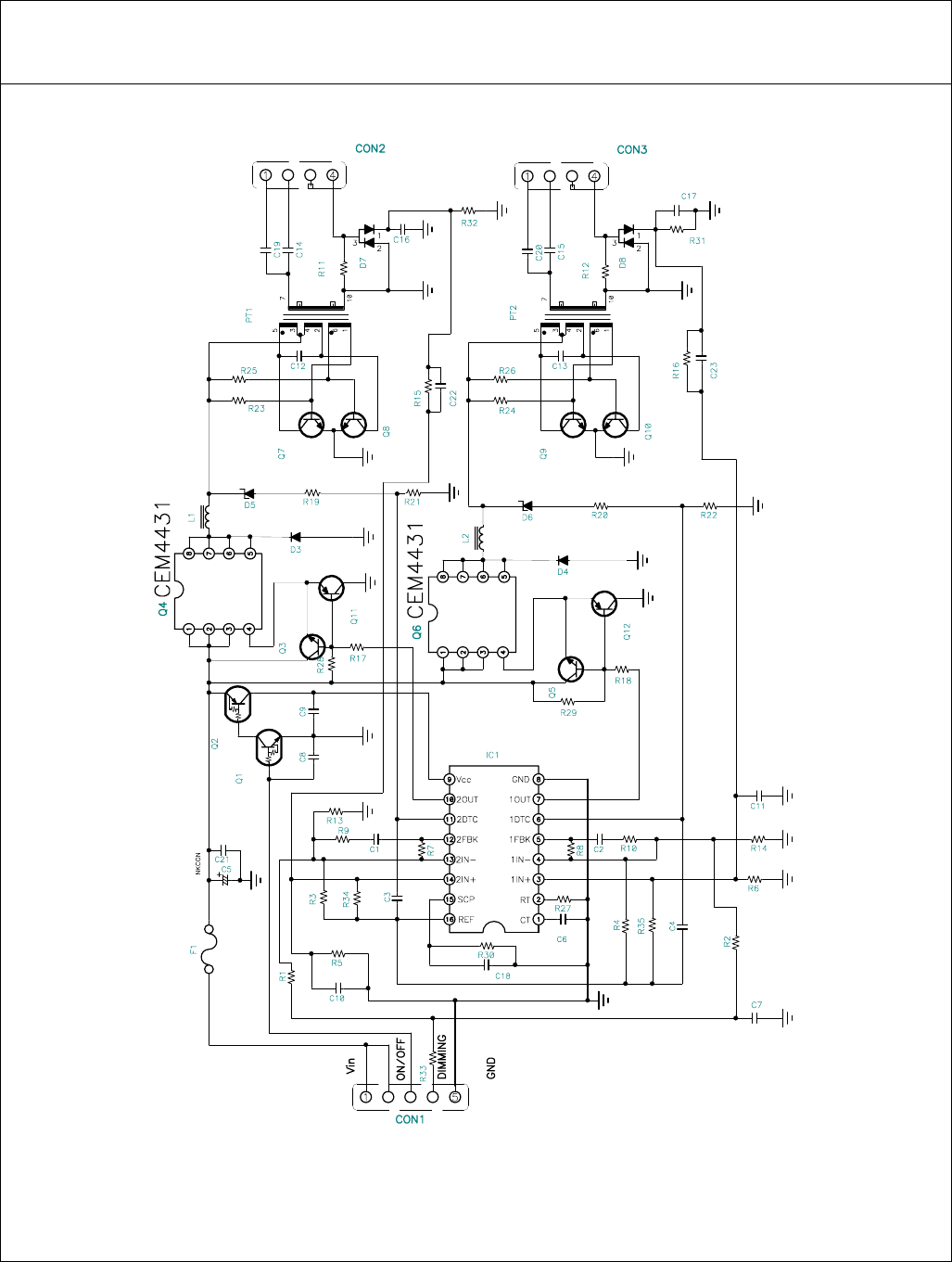

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

1.SAMPO PART NO .: L0037 ,AOC PART NO.: 79AL17-1-S

2.SCOPE : this is to specify the requirements of the subject parts used in

CHI-MEI (M170E1) 17 inch (4 C.C.F.L.) LCD monitor.

3.CONNECTOR PIN ASSIGMENT:

4-1. CON1: INPUT

MODEL NO.: S5B-PH-SM3-TB

4-2. CON2,CON3 : OUTPUT

MODEL NO. : SM04(4.0)B-BHS-1-TB

PIN SYMBOL DESCRIPTION

1 Vin Input voltage: 12V

2 Vin Input voltage: 12V

3 ON/OFF ON: 3V OFF:0V

4 Dimming Dimming range (0V~+5.0V)

5 GND GND

PIN SYMBOL DESCRIPTION

1 HV OUTPUT Input H.V to lamps

2 HV OUTPUT Input H.V to lamps

3 N.C. N.C.

4 RETURN Return to control

I.) TROUBLE SHOOTING OF CHI-MEI INVERTER (part no : 79AL17-1-S)

TYPE: L0037 FOR CHI-MEI 17”PANEL

23

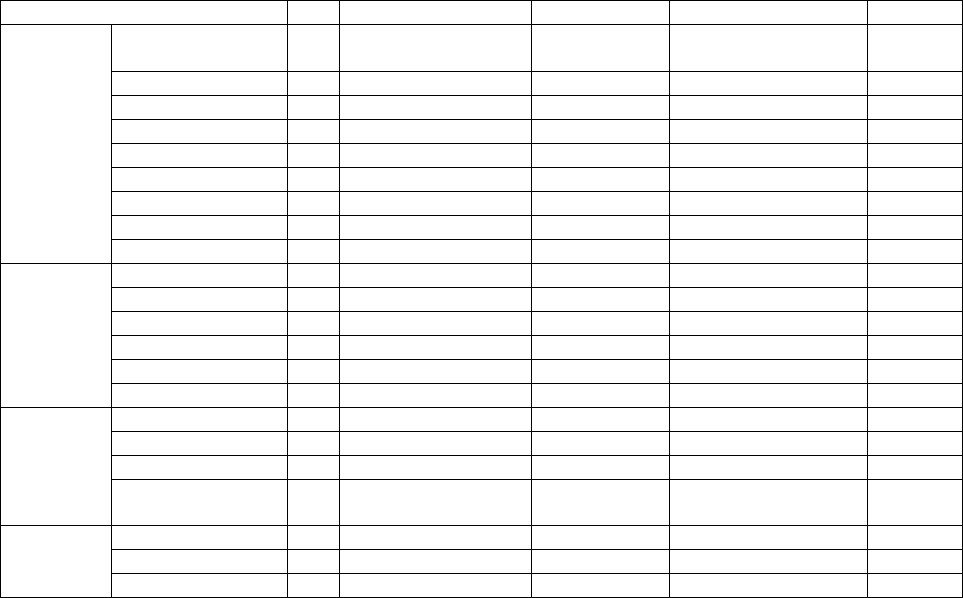

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

5.FUNCTION SPECIFICATIONS:

The data test with the set of SAMPO, and the test circuit is as below.

6. FUNCTION LOAD CIRCUIT:

ITEM SYMBOL MIN. TYP. MAX. UNIT REMARK

Input voltage Vin 10.8 12 13.2 V

Input current Iin -- 2200 2500 mA

output current

adj:0v( min.)

Iout

(min)

2.1

2.6

3.1

mA

FOR 1 CCFL

LOAD:120KΩ

Output current

adj.:5 v(max.)

Iout

(max)

5.5

6.0

6.5

mA

FOR 1 CCFL

LOAD:120KΩ

Frequency F 40 50 60 KHZ

H.V open Vopen 1400 1500 1600 Vrms

NO LOAD

H.V Load Vload 630 730 830 Vrms

RL=120KΩ

CON1

12345

PIN SYMBOL

1 Vin 12V

2 Vin 12V

3 ON/OFF

4 Dimming

5 GND

120KΩ

120KΩ

120KΩ

120KΩ

10Ω

10Ω 10Ω

10Ω

TV

1

2

4

4

2

1

TV TV

TV

24

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

7.CIRCUIT DIAGRAM:

GD

D

D

D

S

S

S

GD

D

D

D

S

S

S

25

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

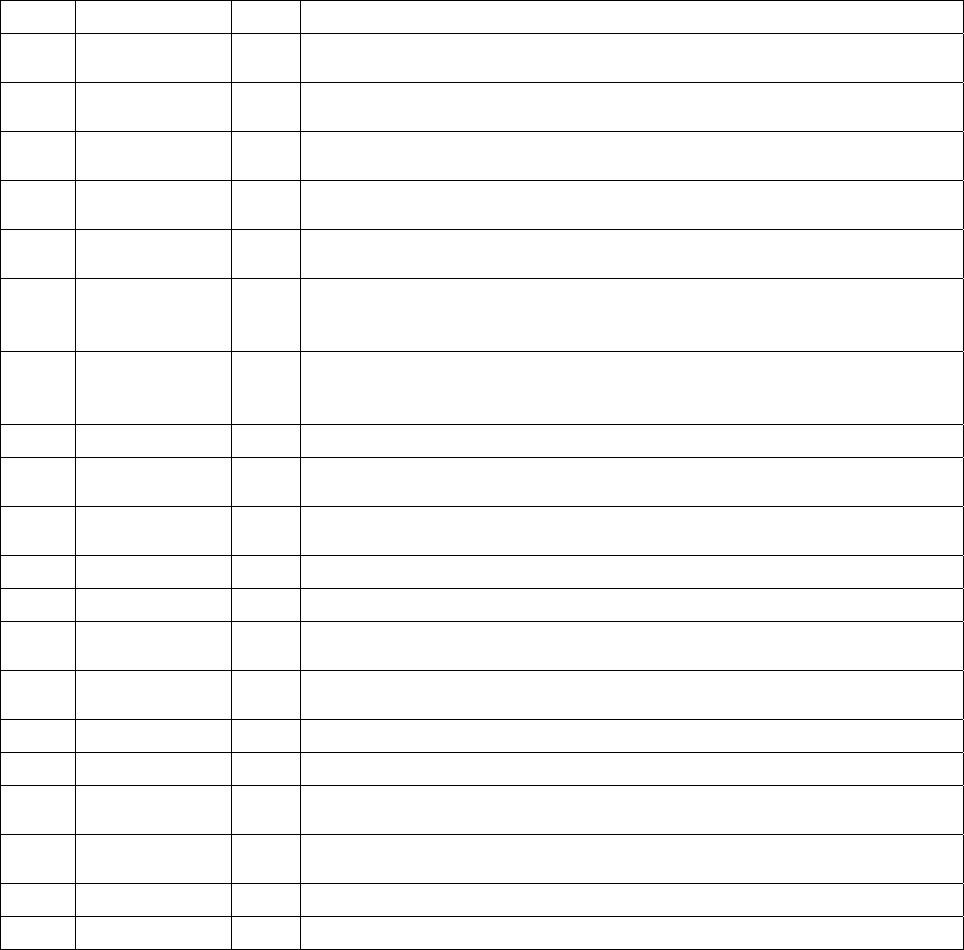

8.PART LIST

8-1 COMPONENTS LIST:

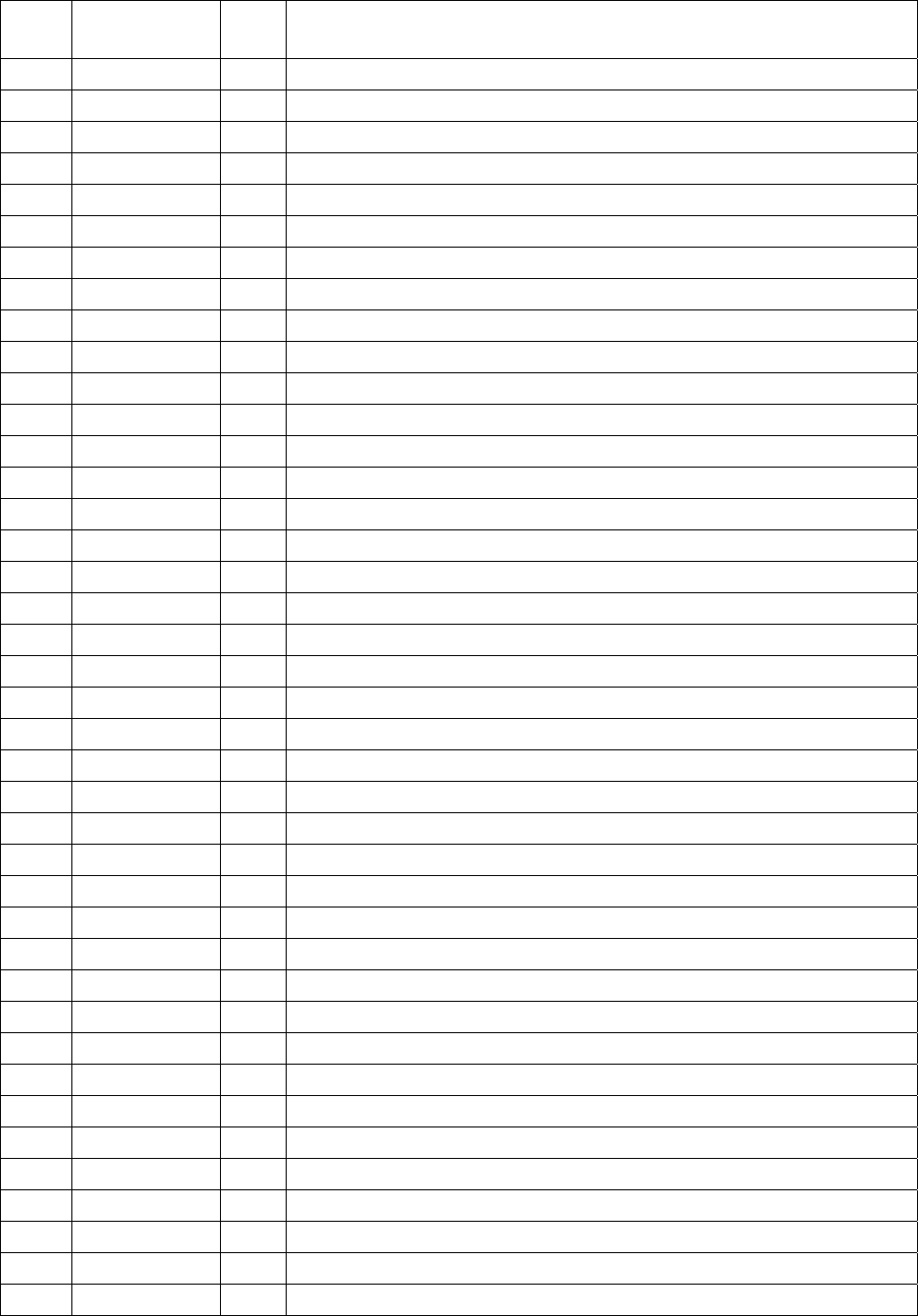

NO. REF. PART NAME PART NUMBER QTY DESCRIPTION SUPPLIER REMARK

1. CON1 CONNECTOR VCNCP0015-EJSTA 1 S5B-PH-SM3-TB JST

2. CON2,3 〃 VCNCP0014-PJSTA

VCNCP0014-ZGLEA

2 SM04(4.0)B.BHS-1-TB

GL SM02(4.0)-WH2

JST

GEAN-LEA

3. R1,2 RESISTOR VRMHNVA--103J-A 2

SMD 0603 10KΩ 5% YAGEO

4. R3,4 〃 VRMHNVA--683J-A 2

SMD 0603 68KΩ 5% YAGEO

5. R5,6 〃 VRMHNVA--912J-A 2

SMD 0603 9.1KΩ 5% YAGEO

6. R7,8 〃 VRMHNVA--274J-A 2

SMD 0603 270KΩ 5% YAGEO

7. R9,10 〃 VRMHNVA--R00J-A 2

SMD 0603 0Ω 5% YAGEO

8. R11,12,

31,32 〃 VRMCNV8--102F-A 4 SMD 0805 1KΩ 1% YAGEO

9. R13,14 〃 VRMHNVA--752J-A 2

SMD 0603 7.5KΩ 5% YAGEO

10. R15,16 〃 VRMHNVA--433J-A 2

SMD 0603 43KΩ 5% YAGEO

11. R17,18 〃 VRMHNVA--271J-A 2

SMD 0603 270Ω 5% YAGEO

12. R27 〃 VRMHNVA--472J-A 1 SMD 0603 4.7KΩ 5% YAGEO

13. R28,29, 〃 VRMHNVA--392J-A 2 SMD 0603 3.9KΩ 5% YAGEO

14. R23,24,

25,26 〃 VRMBNV4--102F-A 4

SMD 1206 1KΩ 1% YAGEO

15. R19,20 〃 VRMCNV8--183F-A 2 SMD 0805 18KΩ 1% YAGEO

16. R21,22 〃 VRMCNV8--133F-A 2 SMD 0805 13KΩ 1% YAGEO

17. R33 〃 VRMHNVA--363J-A 1

SMD 0603 36KΩ 5% YAGEO

18. Q1 TRANSIST0R VSTDTC144WKA--A 1 SMD DTC144WKA ROHM

19. Q2 〃 VSTDTA144WKA--A 1 SMD DTA144WKA ROHM

20. Q3,5 〃 VSTSST3904----A

VSTMMBT3904-A 2 SMD SST3904-T116

SMD MMBT3904

ROHM

MOTOROLA

21. Q4,6 〃 VSTCEM9435A-----A 2 SMD CEM9435A CET

22. Q7,8,9,

10 〃 VST2SD2150----A 4 SMD 2SD2150 ROHM

23. C1,2 CAPACITOR VCLFCN1EY224Z-A 2 SMD 0805 0.22 µF/25V TDK

24. C3,4,,9 〃 VCLRCN1EB104K-A 3 SMD 0805 0.1 µF/25V TDK

25. C5 VCEATU1EC336M--

VCEATU1VC476M--

1 DIP UGX 33 µF/25V

DIP UGX 47 µF/35V

SANYO

26

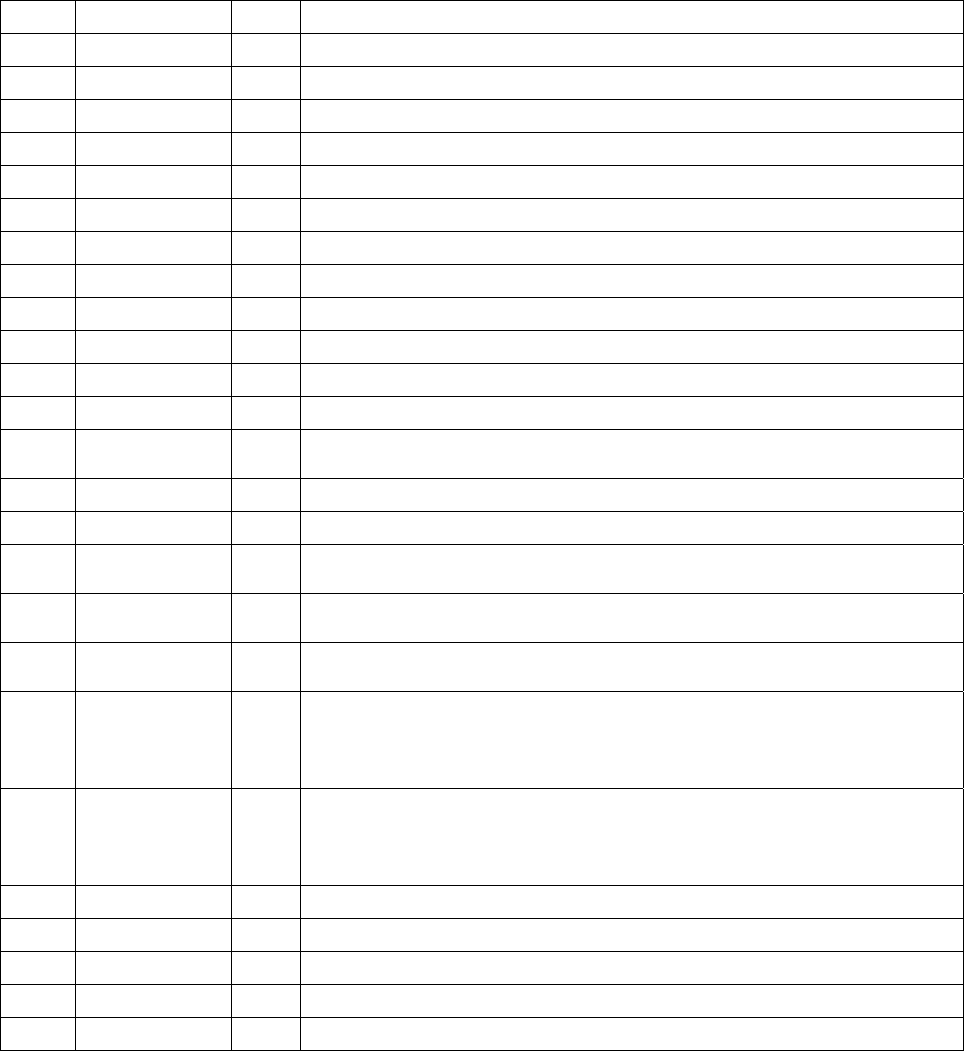

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

8-2 COMPONENTS LIST:

NO. REF. PART

NAME PART NUMBER QTY DESCRIPTION SUPPLIER REMARK

26. C6 〃 VCLRCN1HB102K-A 1 SMD 0805

1000PF/50V TDK

27. C10,11 〃 VCLRCN1EB333K-A 2 SMD 0805 0.033

µF/25V TDK

28. C12,13 〃 VCMEBF2AB184J-P

VCMECF2AC184J-P

2 DIP 0.18µF/100V

DIP 0.18µF/100V

ARCO

THOMSON

29 C14,15,19,

20 CAPACITOR VCDSEU3SL220K-- 4 DIP 22PF/3KV 10% TDK

30. C7,16,17 〃 VCLFCN1EY105Z-A 3 SMD 0805 1 µF/25V TDK

31. C18 〃 VCLFCN1CY225Z-A 1 SMD 0805 2.2 µF/16V TDK

32. C21 〃 VCLFBN1CY475Z-A 1 SMD 0805 4.7 µF/16V TDK

33. D1,2 DIODE VSDRLS4148----A 2 SMD RLS4148 ROHM

34. D3,4 〃 VSDRB160L40---A

VSDSMA160-----A

2 SMD RB160L40

SMD SMA160

ROHM

TPC

35. D5,6 〃 VSZRLZ8.2B-----A 2 SMD RLZ8.2B ROHM

36. D7,8 〃 VSDDA204K-----A 2 SMD DA204K ROHM

37. I.C I.C VSITL1451ACNS-A 1 SMD TL1451ACNS TEXAS

38. F1 FUSE QFS-N302FIDZD-A

QFS-Z302FIDZD-A

1 SMD FUSE 3.0A/63

SMD FUSE 3.0A/63

LITTLE

BUSSMANN

Attachment

(FEC1Q2)

40. L1,2 COIL RCHOL0007ID151A

RCHOL0007ID151-

2 DIP 150µH 10%

DIP 150µH 10%

YST

竑 赫

Attachment 1

41. PT1,2 TRANS RCVT-1207ID-Z-A

RCVT-1207ID-Z-C

2 SMD YST-1207

SMD WT-1207

YST

WT

Attachment 2

Attachment 2-1

42. PCB PCB QPWBGL983IDLF3- 1 QPWBGL983IDLF3- EISO

LONGMAW

千友

27

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

9. TROUBLE SHOOTING

9-1 NO POWER:

. FAIL

PASS FAIL

PASS

FAIL

PASS

CHECK ON FUSE

F1 Vin=12 TO CHANGE

F1= 4.0A/63V

TO CHECK ON Q4&Q6

Vout = 9V

TO CHANGE

L: Q4&Q3&

R: Q5&Q6&

TO CHECK ON L1&L2

INPUT 9V TO L1 OR L2

TO CHANGE

L: Q7&Q8&C12&PT1

R: Q9&Q10&C13&PT2

FUNCTION TEST OK!

TO CHANGE

L: Q4&Q3&Q11

R: Q5&Q6&Q12

28

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

9-2 HIGHT VOLTAGE PROTECTION:

FAIL

PASS

9-3 OUTPUT CURRENT ABNORMALITY:

FAIL

PASS

1. SHORT R30 OPEN LOAD

2. TEST C14 INPUT POINT

VOLTAGE Vh=1600 ±100V rms TO CHANGE ON

PT1 OR PT2

FUNCTION TEST OK!

1 CHECK ON C6 FREQUNCY

&CHIP&IC CPIP

2 OSCILLATOR FREQUNCY

RANGE = 100 ~ 250 KHZ

TO CHANGE ON C6

CHIP OR IC CHIP

FUNCTION TEST OK!

29

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

9-4. ENBALE ABNORMALITY:

FAIL

PASS

9-5 DIMMING CONTROL ABNORMALITY:

FAIL

PASS

IF ENBALE ABNORMALITY

1. TO CHECK IC PIN 9 TURN NO

HAVE 12 VOLTAGES TO CHANGE ON Q1&Q2

FUNCTION TEST OK!

IF DIMMING ABNORMALITY TO

CHECK R1&R2&C6 HAVR BREAK TO CHANGE ON R1 OR R2 OR

C6&R33

FUNCTION TEST OK!

IF DIMMING ABNORMALITY TO

CHECK R1&R2&C6&R33 HAVE BREAK

30

- 9 -

SAMPO CORPORATION

TROUBLE SHOOTING OF CHI-MEI INVERTER ( DIVTL0037-D42- -)

9-6 TRANSFORMER ABNORMALITY:

FAIL

PASS

10. INSTRUMENTS FOR TEST:

1. DC POWER SUPPLY GPS-3030D

2. AC VTVM VT:-181E

3. DIGITAL MULTIMERTER MODEL-34401

4. HIGHTVOLT PROB MODEL-1137A

5.SCOPE MODEL-V-6545

6. AC mA METER MODEL-2016 (YOKOGAWA)

IF TRANSFORMER ABNORMALITY TO

CHECK C3&C4 CHIP OUTLINE OR

TRANSFORMER

TO CHANGE ON C3&C4

OR TRANSFORMER

FUNCTION TEST OK!

31

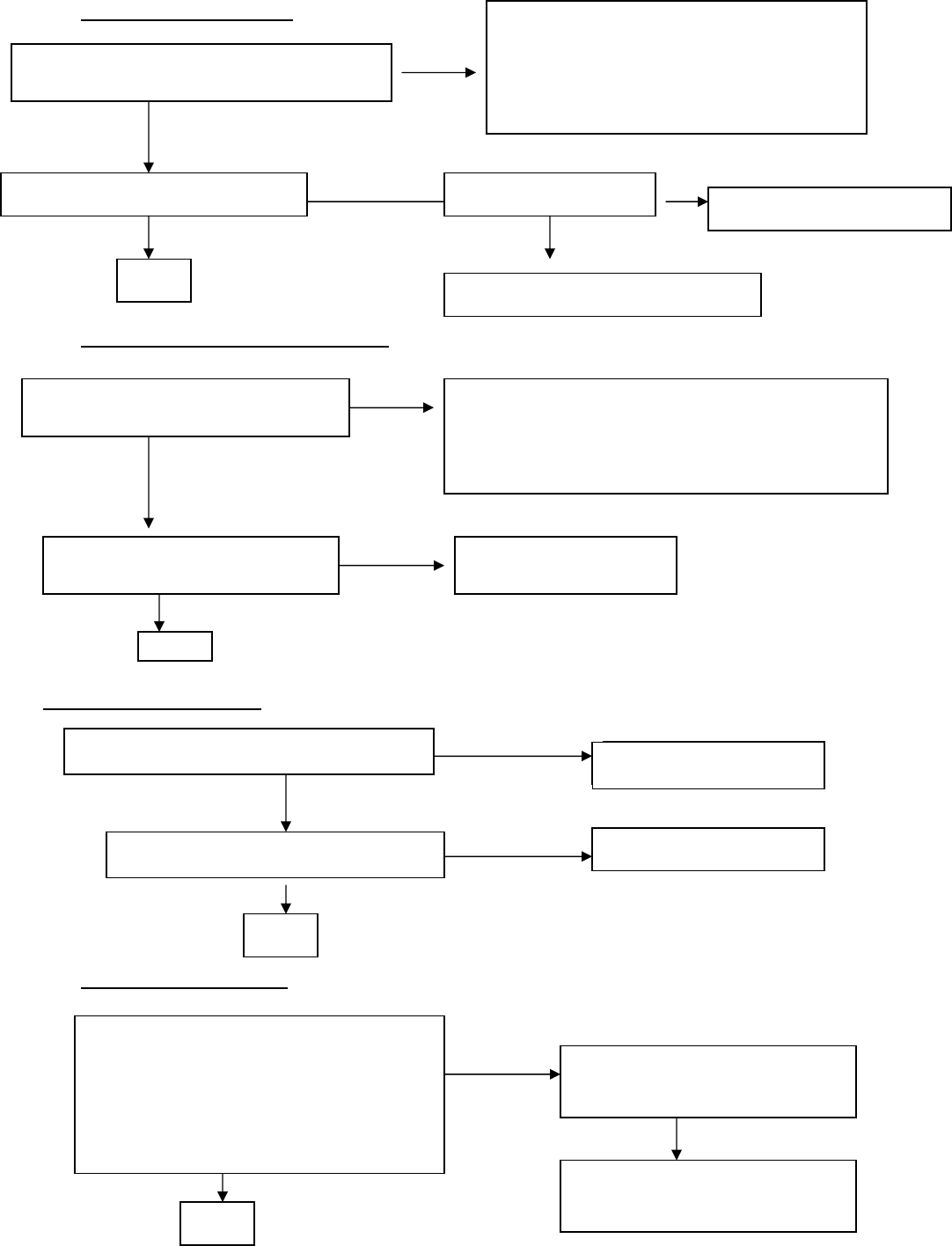

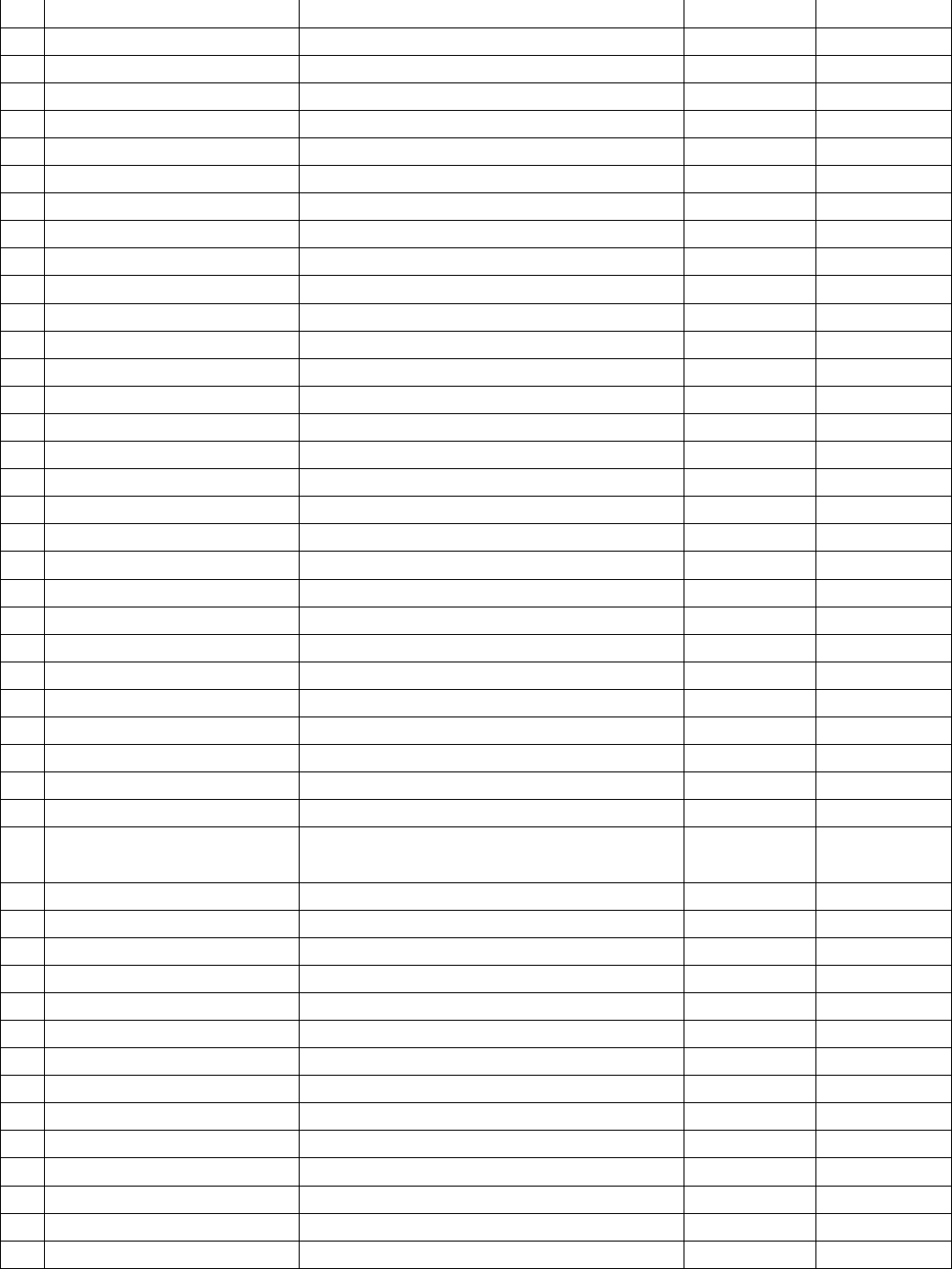

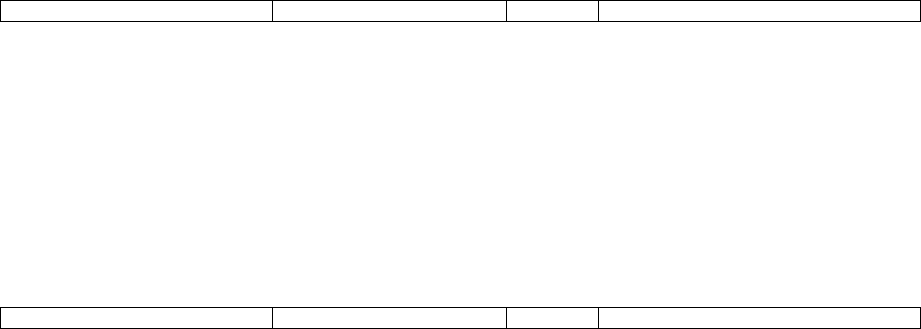

6 C). ADAPTER-MODULE Trouble shooting chart

The following spec & block-diagram is offer by CHI-SAM –COMPANY, for External Adapter

part number : 80AL17-1-CH ( Black), 80AL17-2-CH ( White)

AC ADAPTER CH-1205 TROUBLE SHOOTING

NO VOLTAGE O/P

CHECK BD101

AC VOLT. I/P OK ?

CHECK BD101

DC VOLT. O/P OK ?

CHECK U101 PIN7

12~15Vdc OK ?

CHECK U101 PIN4

FREQ. (50~70KHZ)

OK ?

CHECK Q101

PIN G & PIN D WAVE

OK ?

OK?

CHECK D106, D107, U102, U103

REPLACE

F101

REPLACE

BD101

CHECK

R115,D103,U101

NG ?

CHECK

C110,U101

NG ?

CHECK Q101

NG

NO

NO

NO

NO

NO

YES

YES

YES

YES

YES

32

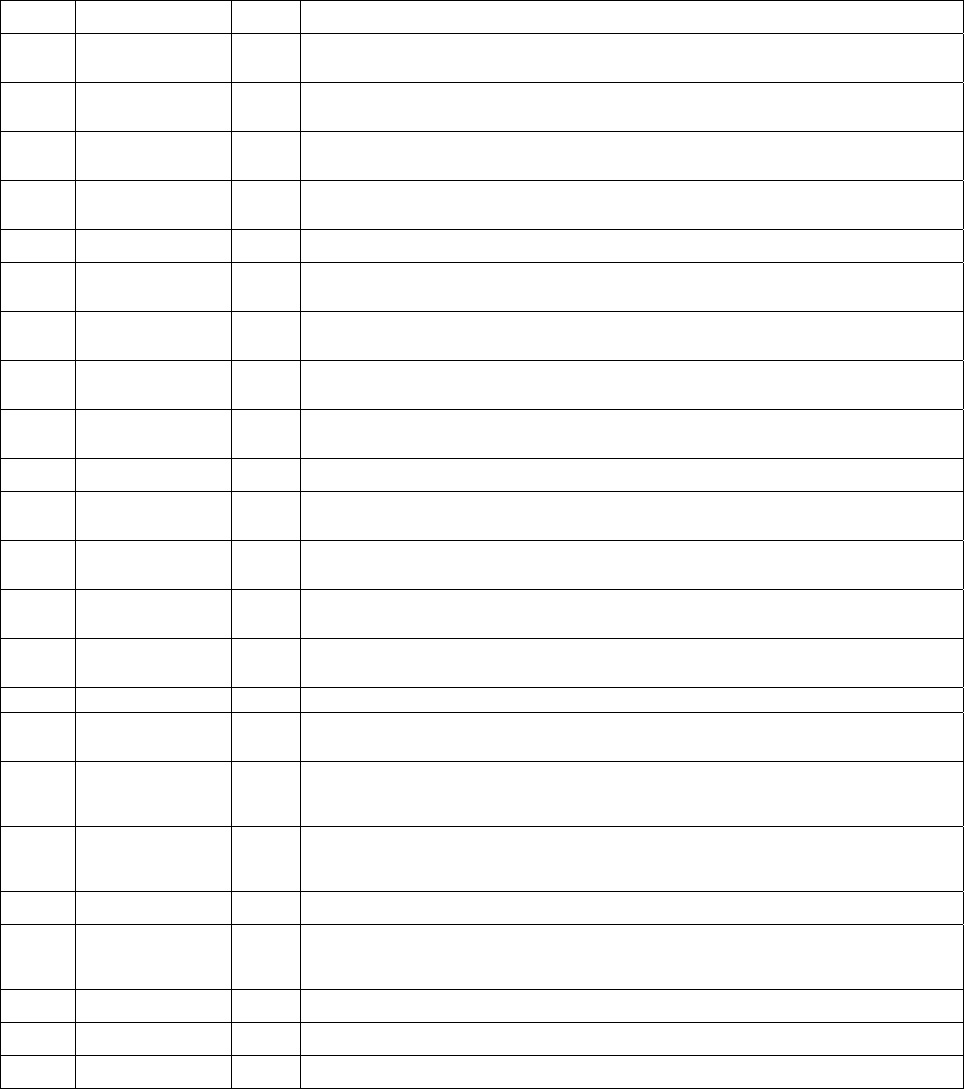

I.) Adapter Schematic CH-1205

Please see the ADAPTER-SCHEMATIC in the end of this Document ( page 75)

33

IV. ADAPTER BOM LIST ( PART no. 80AL15-2-LI)

Item Reference Part Quantity Cat.NO.

1 BD101 DIODE BRIDGE KBL405G 600V/4A 1 PCS 15D7L405G6

2 CN101 AC POWER SOCKET 1 PCS 64P21-0001

3 BEAD1,BEAD2,BEAD3,BEAD4 BEAD 3.5*3.2*1.6mm 4 PCS 62C-353216

4 C116 CAP CER 102P/500V +-10% Y5P 1 PCS 99426A1025

5 C105 CAP CER 103P/500V +80-20% Z5V 1 PCS 99459F1033

6 C107,C108,C109,

C121,C122,C123 CAP CER 104P/50V +-10% X7R SMD(0805) 6 PCS 99B26D104D

7 C112 CAP CER 271P/50V +-5% NPO SMD(0805) 1 PCS 99B15E271D

8 C113 CAP CER 301P/50V +-5% NPO SMD(0805) 1 PCS 99B15E301D

9 C110,C111 CAP CER 332P/50V +-10% X7R SMD(1206) 2 PCS 99B26D332E

10 C114 CAP CER 102P/50V +-10% X7R SMD(0805) 1 PCS 99B26D102D

11 C117,C118 CAP ELEC 1000U/16V +-20% 105℃(LOW ESR) 2 PCS 28D37-1021

12 C104 CAP ELEC 120U/400V +-20% 105℃ 650mA 18*36 1 PCS 281D701211

13 C106 CAP ELEC 150U/25V +-20% 105℃ 1 PCS 28147-1511

14 C119 CAP ELEC 470U/16V +-20% 105℃(LOW ESR) 1 PCS 28D37-4711

15 C103 CAP X1 0.47U/300Vac +-10% P=22.5 1 PCS 42A96-474G

16 C124 CAP Y2 102P/250Vac +-20% P=7.5,長腳 1 PCS 42D77-102F

17 C101,C102,C115 CAP Y2 222P/250Vac +-20% P=7.5 3 PCS 42D77-222F

18 L103 COIL CHOKE 5uH 5*20(RD005) 1 PCS 45M56-509C

19 D104,D105,D108,D109 DIODE 1N4148 75V/150mA(SMD) 4 PCS 15A2N41480

20 D102,D103 DIODE RLS245(SMD) 2 PCS 15AHLS2450

21 D106,D107 DIODE SCHOTTKY MBR20100CT 100V/20A 2 PCS 15B3100CT6

DIODE SCHOTTKY MBRF20100CT 100V/20A 15B3201006

DIODE SCHOTTKY FCH20A10 100V/20A 15B320A106

DIODE SCHOTTKY SS20FJK10L 100V/20A 15B3JK10L6

22 D101 DIODE UF4005G 600V/1A 1 PCS 15A74005G2

23 ZD102 DIODE ZENER RLZ18C(SMD) 1 PCS 15Z35Z18C0

24 ZD101 DIODE ZENER RLZ20B(SMD) 1 PCS 15Z35Z20B0

25 FOR COVER SCREW PHM3-20*10 2 pcs 6721A30101

26 F101 FUSE T2A/250Vac SLOW BLOW 1 PCS 49F54-202A

27 U105 IC AP431W*D 85℃ SMD(SOT-23) 1 PCS 171AP431WD

28 U104A IC BA10358F(SMD) 1 PCS 171A10358F

29 U101 IC CM3842 1 PCS 1700CM3842

30 U103 IC CM431 1 PCS 17000CM431

31 U102 IC H11A817C 1 PCS 17011A817C

32 J101 JUMPER 0.6ψ 8*12.5mm 1 PCS 54JB5-0005

34 J104 JUMPER 0.6ψ 8*22.5mm 1 PCS 54JB5-0009

35 J103,J105,J106 JUMPER 0.6ψ 8*5mm 3 PCS 54JB5-0002

36 J102 JUMPER 0.6ψ 8*7.5mm 1 PCS 54JB5-0003

37 LED101 LED L-34GD TYPE GREEN 1 PCS 1903112011

38 L102 LINE FILTER 18mH UU15.7(RD002) 1 PCS 47E10-0010

39 Q101 MOS FET 2SK2996 600V/10A 1 PCS 14K1SK2996

MOS FET2SK2761-01MR 600V//10A 14K1SK2761

MOS FET 2SK2843 600V/10A 14K1SK2843

40 R101 NTCR 3 OHM/5A 10ψ +-15% 1 PCS 26B2L50011

34

41 PCB PCB FOR CH-1205 REV:D 1 PCS 11S43-0030

42 R117 RES 100 1/8W +-5% SMD(0805) 1 PCS 2242510000

43 J109,J110 RES 0 OHM 1/4W +-5% SMD(1206) 2 PCS 2243500000

44 R143 RES 1.8K 1/8W +-5% SMD(0805) 1 PCS 2242518010

45 R114 RES 100 1/4W +-5% SMD(1206) 1 PCS 2243510000

46 R124,R127 RES 10K 1/8W +-5% SMD(0805) 2 PCS 2242510020

47 R136 RES 113K 1/8W +-1% SMD(0805) 1 PCS 2242111330

48 R145 RES 12K 1/4W +-5% SMD(1206) 1 PCS 2243512020

49 R128 RES 13K 1/8W +-5% SMD(0805) 1 PCS 2242513020

50 R115 RES 15 1/4W +-5% SMD(1206) 1 PCS 2243515090

51 R123 RES 150 1/4W +-5% SMD(1206) 1 PCS 2243515000

52 R107,R108,R109,R110 RES 180K 1/4W +-5% SMD(1206) 4 PCS 2243518030

53 R142 RES 2.4K 1/8W +-1% SMD(0805) 1 PCS 2242124010

54 R130,R131,R132, R133 RES 24 1/4W +-5% SMD(1206) 4 PCS 2243524090

55 R141 RES 270 1/4W +-5% SMD(1206) 1 PCS 2243527000

56 R129 RES 3.6K 1/8W +-5% SMD(0805) 1 PCS 2242536010

57 R137 RES 3.74K 1/8W +-1% SMD(0805) 1 PCS 2242137410

58 R139 RES 330 1/4W +-5% SMD(1206) 1 PCS 2243533000

59 R105,R106 RES 3M 1/4W +-5% SMD(1206) 2 PCS 2243530040

60 R104,R116 RES 4.7K 1/4W +-5% SMD(1206) 2 PCS 2243547010

61 R118,R144,R120,R134 RES 4.7K 1/8W +-5% SMD(0805) 4 PCS 2242547010

62 R102,R103 RES 470K 1/4W +-5% SMD(1206) 2 PCS 2243547030

63 R122 RES 47K 1/8W +-5% SMD(0805) 1 PCS 2242547020

64 R126 RES 510 1/8W +-5% SMD(0805) 1 PCS 2242551000

65 R138 RES 680 1/8W +-1% SMD(0805) 1 PCS 2242168000

66 R121 RES 8.2K 1/8W +-1% SMD(0805) 1 PCS 2242182010

67 R140 RES 9.31K 1/8W +-1% SMD(0805) 1 PCS 2242193110

68 R119 RES CF 4.7 K 1/8W +-5% 1 PCS 2222547011

69 R135 RES CuNi 10mΩ +-1%(錳銅線) 1 PCS 24911-0189

70 R111 RES MOF 43K 3W +-5% 立式(小型化),不打KINK 1 PCS 2376543029

71 R125 RES W.W. 0.39 OHM 2W +-5% NKNP TYPE 立式 ,不

打KINK 1 PCS 24735-398B

72 FOR C124 SRK TUBE 1ψ*17mm 1 PCS 57701-0170

73 FOR CN101 RING TERMINAL *70mm 1 PCS 54B2310705

74 FOR PCB SCREW M3*6 ISO/SW ZNC 2 PCS 6720530051

75 FOR Q101,D107,D106 SPRING SK-7 3 PCS 76455-0010

76 FOR CN101 SRK TUBE 5ψ*0.9cm 1 PCS 57705-0090

77 FOR Q101,D107,D106 SRK TUBE 6ψ*16mm 3 PCS 57706-0160

78 FOR C105 SRK TUBE 8ψ*15mm 1 PCS 57708-0150

79 FOR R125 SRK TUBE 8ψ*22mm 1 PCS 57708-0220

80 L101 Toroidal choke coil 2mH TN12.7*7.9*3.5(RD009) 1 PCS 45M36-502L

81 Q102 TR NPN 2SC4505 400V/0.1A (SMD) 1 PCS 14D2SC4505

82 Q103,Q105 TR NPN C2412K 50V/0.15A(SMD) 2 PCS 14C2C2412K

83 Q104 TR PNP A1037AK -50V/-0.15A(SMD) 1 PCS 14A21037AK

84 VAR101 VARISTOR SAS-471KD07 7ψ 1 PCS 27111-0001

85 T101 X'FORMER PWR PQ2620 FOR CH-1205(RD010) 1 PCS 47S10-0040

35

86 FOR FRONT HEATSINK 導熱墊片 TCR- 05 15*25-ASAHI 1 PCS 85011-0001

87 FOR FRONT HEATSINK 導熱墊片 TCR- 10 10*20-ASAHI 1 PCS 85100-0001

88 3M擋牆膠帶#44 1L 35*40mm 1 PCS 80400-0001

89 FRONT COVER 129.3*63.8*19.34mm 1 PCS 0810400020

90 BASE COVER 129.3*63.8*18.7mm 1 PCS 0820400020

91 DC OUTPUT POWER CABLE UL1185#18AWG ψ5.5*ψ2.5

*20.5,(音叉&車溝,黑),L=80CM 1 PCS 56L1807811

92 FRONT HEATSINK FOR CH-1205 1 PCS 75170-0060

93 BOTTOM HEATSINK FOR CH-1205 REV:C 1 PCS 75170-005C

94 FRPP FOR CH-1205 BOTTOM HEATSINK 1 PCS 80300-0020

95 LED HOLDER 5*10 1 PCS 71720-0010

96 RATING FOR 捷聯 CH-1205 REV:C 1 PCS 0643C00026

97 15*4mm OK標籤 FOR 捷聯 CH-1205 REV:A 1 PCS 0643000031

98 FOR D106,D107 SILICON RUBBER COVER (TO-220ST-B) 2 PCS 80100-0001

36

6 D). AUDIO-MODULE Trouble shooting chart

I.) NO VOICE OUTPUT

]

Use OHM-METER measure U1 pin 2, 4

(channel-A ) is speaker well connected?

Measure U1 pin 10,12 ( channel B) is speaker

well connected ?

Plug-out the DC power , make sure

the monitor is in OFF status .

Check J1,J2 is well connected?

Measured J2 pin 4,5 & 2,3 is

well connected ?

Check is speaker open circuit ?

Plug-in the DC power, set the monitor

ON status .

Check R10,R11 & J5, S1 is open

circuit?

Check U1 pin 1 = VCC 12V

Check U1 is work properly?

Check U1 pin 5 standby-bias

voltage around 4 V ? Check R4 is open circuit?

Check U1 pin 9 volume-bias

around 1 V ? Check R7 , VR1

Check Audio cable and J4 is well connected

NG

YES

YES

NG

NG

NG

YES

YES

YES

37

II.) SOUND DISTORTION

AUDIO BOM

Bill Of Materials September 7,2001 18:09:14 Page1

Item Quantity Reference Part

______________________________________________

1 3 C1,C2,C4 1uF

2 1 C3 2200uF/25V

3 1 C5 10uF/50V

4 2 C6,C7 0.047uF

5 1 C8 100uF/16V

6 1 C9 100uF/25V

7 1 D1 LED

8 2 J1,J3 CON2

9 1 J2 EAR PHONE

10 1 J4 AUDIO IN

11 1 J5 DC IN

12 3 VR1,R1,R2 10K

13 1 R3 33K

14 1 R4 68K

15 2 R5,R6 15K

16 1 R7 130K

17 2 R9,R8 3K

18 2 R11,R10 1(3W)

19 1 R12 680

20 1 S1 SW SPST

21 1 U1 AN7522

Check U1 pin 2, 4 10, 12 is the

voltage output = VCC / 2 . ? Check U1

CHECK SPEAKER

NG

YES

38

GMZAN1

The gmZAN1device utilizes Genesis’ patented third-generation Advanced Image Magnification technology as well as

a proven integrated ADC/PLL to provide excellent image quality within a cost effective SVGA/XGA LCD monitor

solution.

As a pin-compatible replacement for the gmB120, the gmZAN1 incorporates all of the gmB120 features plus many

enhanced features; including 10-bit gamma correction, Adaptive Contrast Enhancement (ACE) filtering, Sync On

Green (SOG), and an enhanced OSD.

1.1 Features

z Fully integrated 135MHz 8-bit triple-ADC, PLL, and pre-amplifier

z GmZ2 scaling algorithm featuring new Adaptive Contrast Enhancement (ACE)

z On-chip programmable OSD engine

z Integrated PLLs

z 10-bit programmable gamma correction

z Host interface with 1 or 4 data bits

z Pin-compatible with gmB120

Integrated Analog Front End

z Integrated 8-bit triple ADC

z Up to 135MHz sampling rates

z No additional components needed

z All color depths up to 24-bits/pixel are supported

High-Quality Advanced Scaling

z Fully programmable zoom

z Independent horizontal / vertical zoom

z Enhanced and adaptive scaling algorithm for optimal image quality

z Recovery Mode / Native Mode

Input Format

z Analog RGB up to XGA 85Hz

z Support for Sync On Green (SOG)

z Support for composite sync modes

Output Format

z Support for 8 or 6-bit panels (with high quality dithering)

z One or two pixel output format

Built In High-Speed Clock Generator

z Fully programmable timing parameters

z On-chip PLLs generate clocks for the on-chip ADC and pixel clock from a single reference oscillator

Auto-Configuration / Auto-Detection

z Phase and image positioning

z Input format detection

Operation Modes

z Bypass mode with no filtering

z Multiple zoom modes:

With filtering

With adaptive (ACE) filtering

Integrated On-Screen Display

z On-chip character RAM and ROM for better customization

z External OSD supported for greater flexibility

z Supports both landscape and portrait fonts

z Many other font capabilities including: blinking, overlay and transparency

39

1.3 Pin Description

Unless otherwise stated, unused input pins must be tied to ground, and unused output pins left open.

Table 1 : Analog-to-Digital Converter

PIN # Name I/O Description

77 ADC_VDD2

Digital power for ADC encoding logic. Must be bypassed with 0.1uF capacitor to

pin 78 (ADC_GND2)

78 ADC_GND2

Digital GND for ADC encoding logic. Must be directly connected to the digital

system ground plane.

79 ADC_VDD1

Digital power for ADC clocking circuit. Must by passed with 0.1uF capacitor to

pin 80 (ACD_GND1).

80 ADC_GND1

Digital GND for ADC clocking circuit. Must be directly connected to the digital

system ground plane.

81 SUB_GNDA

Dedicated pin for substrate guard ring that protects the ADC reference system.

Must be directly connected to the analog system ground plane.

82 ADC_GNDA

Analog ground for ADC analog blocks that are shared by all three channels.

Includes bandgap reference, master biasing and full scale adjust. Must be directly

connected to analog system ground plane.

84 ADC_VDDA

Analog power for ADC analog blocks that are shared by all three channels.

Includes bandgap reference, master biasing and full scale adjust. Must be

bypassed with 0.1uF capacitor to pin 82 (ADC_GNDA).

83 Reserved

For internal testing purpose only. Do not connect.

85 ADC_BGNDA

Analog ground for the blue channel. Must be directly connected to the analog

system ground plane.

88 ADC_BVDDA

Analog power for the blue channel. Must be bypassed with 0.1uF capacitor to pin

85(BGNDA).

86 BLUE- I

Negative analog input for the Blue channel.

87 BLUE+ I

Positive analog input for the Blue channel.

89 ADC_GGNDA

Analog ground for the green channel. Must be directly connected to the analog

system ground plane.

92 ADC_GVDDA

Analog power for the green channel. Must be bypassed with 0.1uF capacitor to

pin 89 (ADC_GGNDA).

90 GREEN- I

Negative analog input for the Green channel.

91 GREEN+ I

Positive analog input for the Green channel.

93 ADC_RGNDA

Analog ground for the red channel. Must be directly connected to the analog

system ground plane.

96 ADC_RVDDA

Analog power for the red channel. Must be bypassed with 0.1uF capacitor to pin

93 (ADC_RGNDA).

94 RED- I

Negative analog input for the Red channel.

95 RED+ I

Positive analog input for the Red channel.

40

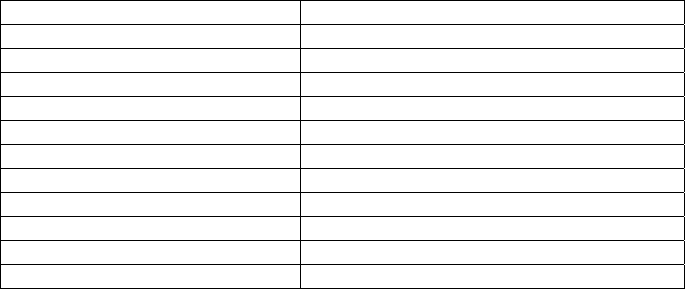

Table 2 : Host Interface (HIF) / External On-Screen Display

PIN # Name I/O Description

98 HFS I

Host Frame Sync. Frames the packet on the serial channel.

103 HCLK I

Clock signal input for the 3-wire serial communication.

99 HDATA I/O

Data signal for the 3-wire serial communication.

100 RESETn I

Resets the gmZAN1 chip to a known state when low.

101 IRQ O

Interrupt request output.

115 OSD-HREF O

HSYNC output for an external OSD controller chip.

116 OSD-VREF O

VSYNC output for an external OSD controller chip.

117 OSD-Clk O

Clock output for an external OSD controller chip.

118 OSD-Data0 I

Data input 0 from an external OSD controller chip.

119 OSD-Data1 I

Data input 1 from an external OSD controller chip.

120 OSD-Data2 I

Data input 2 from an external OSD controller chip.

121 OSD-Data3 I

Data input 3 from an external OSD controller chip.

122 OSD-FSW I

External OSD window display enable. Displays data from external OSD

controller when high.

123 MFB11 I/O

Multi-Function Bus 11. One of twelve multi-function signals MFB[11:0].

124 MFB10 I/O

Multi-Function Bus 10. One of twelve multi-function signals MFB[11:0].

102 MFB9 I/O

Multi-Function Bus 9. One of twelve multi-function signals MFB[11:0].

Also used as HDATA3 in a 4-bit host interface configuration.

104 MFB8 I/O

Multi-Function Bus 8. One of twelve multi-function signals MFB[11:0].

Also used as HDATA2 in a 4-bit host interface configuration.

105 MFB7 I/O

Multi-Function Bus 7. One of twelve multi-function signals MFB[11:0].

Also used as HDATA1 in a 4-bit host interface configuration.

106 MFB6 I/O

Multi-Function Bus 6. One of twelve multi-function signals MFB[11:0].

Internally pulled up. When externally pulled down (sampled at reset ) the host

interface is configured for 4 bits wide. In this configuration, MFB9:7 are used as

HDATA 3:1.

107 MFB5 I/O

Multi-Function Bus 5 One of twelve multi-function signals MFB[11:0].

Internally pulled up. When externally pulled down (sampled at reset ) the chip

uses an external crystal resonator across pins 141 and 142, instead of an

oscillator.

109 MFB4 I/O

Multi-Function Bus 4. One of twelve multi-function signals MFB[11:0].

110 MFB3 I/O

Multi-Function Bus 3. One of twelve multi-function signals MFB[11:0].

111 FMB2 I/O

Multi-Function Bus 2. One of twelve multi-function signals MFB[11:0].

112 MFB1 I/O

Multi-Function Bus 1. One of twelve multi-function signals MFB[11:0].

113 MFB0 I/O

Multi-Function Bus 0. One of twelve multi-function signals MFB[11:0].

41

Table 3 : Clock Recovery / Time Base Conversion

PIN # Name I/O Description

125 DVDD

Digital power for Destination DDS (direct digital synthesizer). Must be bypassed

with a 0.1uF capacitor to digital ground plane.

127 DAC_DGNDA Analog ground for Destination DDS DAC. Must be directly connected to the

analog system ground plane.

128 DAC_DVDDA Analog power for Destination DDS DAC. Must be bypassed with a 0.1uF

capacitor to pin 127 (DAC_DGNDA).

129 PLL_DVDDA

Analog power for the Destination DDS PLL. Must be bypassed with a 0.1uF

capacitor to pin 131 (PLL_DGNDA).

130 Reserved

For testing purposes only. Do not connect.

131 PLL_DGNDA

Analog ground for the Destination DDS PLL. Must be directly connected to the

analog system ground plane.

132 SUB_DGNDA Dedicated pin for the substrate guard ring that protects the Destination DDS.

Must be directly connected to the analog system ground plane.

133 SUB_SGNDA

Dedicated pin for the substrate guard ring that protects the Source DDS. Must be

directly connected to the analog system ground plane.

134 PLL_SGNDA

Analog ground for the Source DDS PLL. Must be directly connected to the

analog system ground.

135 Reserved

For testing purposes only. Do not connect.

136 PLL_SVDDA

Analog power for the Source DDS DAC. Must be bypassed with a 0.1uF

capacitor to pin 134 (PLL_SGNDA)

137 DAC_SVDDA Analog power for the Source DDS DAC. Must be by passed with a 0.1uF

capacitor to pin 138 (DAC_SGNDA)

138 DAC_SGNDA Analog power for the Source DDS DAC. Must be directly connected to the

analog system ground.

139 SVDD

Digital power for the Source DDS. Must be bypassed with a 0.1uF capacitor to

digital ground plane.

141 TCLK I Reference clock(TCLK) input from the 50 MHz crystal oscillator

142 XTAL O If using an external oscillator, leave this pin floating. If using an external crystal,

connect crystal between TCLK(141) and XTAL(142). See MFB5(pin 107).

143 PLL_RVDDA Analog power for the Reference DDS PLL. Must be bypassed with a 0.1uF

capacitor to pin 144(PLL_RGNDA)

144 PLL_RGNDA Analog ground for the Reference DDS PLL. Must be directly connected to the

analog system ground plane.

145 Reserved For testing purposes only. Do not connect.

146 SUB_RGNDA Dedicated pin for the substrate guard ring that protects the Reference DDS. Must

be directly connected to the analog system ground plane.

148 VSYNC I CRT Vsync input. TTL Schmitt trigger input.

149 SYN_VDD Digital power for CRT Sync input.

150 HSYNC/CSYNC I CRT Hsync or CRT composite sync input. TTL Schmitt trigger input.

42

Table 4. TFT Panel Interface

PIN # Name I/O Description

2pxl/clk 2pxl/clk 1pxl/clk 1pxl/clk

8bit 6-bit 8-bit 6-bit TFT

6 PD47 O OB1 - - -

7 PD46 O OB0 - - -

9 PD45 O OG1 - - -

10 PD44 O OG0 - - -

13 PD43 O OR1 - - -

14 PD42 O OR0 - - -

15 PD41 O EB1 - B1 -

16 PD40 O EB0 - B0 -

17 PD39 O EG1 - G1 -

19 PD38 O EG0 - G0 -

20 PD37 O ER1 - R1 -

22 PD36 O ER0 - R0 -

23 PD35 O OB7 OB5 - -

24 PD34 O OB6 OB4 - -

25 PD33 O OB5 OB3 - -

26 PD32 O OB4 OB2 - -

27 PD31 O OB3 OB1 - -

28 PD30 O OB2 OB0 - -

29 PD29 O OG7 OG5 - -

31 PD28 O OG6 OG4 - -

32 PD27 O OG5 OG3 - -

34 PD26 O OG4 OG2 - -

35 PD25 O OG3 OG1 - -

36 PD24 O OG2 OG0 - -

37 PD23 O OR7 OR5 - -

38 PD22 O OR6 OR4 - -

39 PD21 O OR5 OR3 - -

42 PD20 O OR4 OR2 - -

46 PD19 O OR3 OR1 - -

47 PD18 O OR2 OR0 - -

48 PD17 O EB7 EB5 B7 B5

50 PD16 O EB6 EB4 B6 B4

51 PD15 O EB5 EB3 B5 B3

52 PD14 O EB4 EB2 B4 B2

53 PD13 O EB3 EB1 B3 B1

54 PD12 O EB2 EB0 B2 B0

55 PD11 O EG7 EG5 G7 G5

56 PD10 O EG6 EG4 G6 G4

57 PD9 O EG5 EG3 G5 G3

62 PD8 O EG4 EG2 G4 G2

43

PIN # Name I/O Description

2pxl/clk 2pxl/clk 1pxl/clk 1pxl/clk

8bit 6-bit 8-bit 6-bit TFT

63 PD7 O EG3 EG1 G3 G1

64 PD6 O EG2 EG0 G2 G0

66 PD5 O ER7 EG5 R7 R5

67 PD4 O ER6 ER4 R6 R4

68 PD3 O ER5 ER3 R5 R3

69 PD2 O ER4 ER2 R4 R2

70 PD1 O ER3 ER1 R3 R1

71 PD0 O EG2 ER0 R2 R0

43 PdispE O This output provides a panel display enable signal that is active when flat panel

data is valid.

74 PHS O This output provides the panel line clock signal.

73 PVS O This output provides the frame start signal.

44 PCLKA O This output is used to drive the flat panel shift clock.

45 PCLKB O Same as PCLKA above.

The polarity and the phase of this signal are independently programmable.

75 Pbias O This output is used to turn on/off the panel bias power or controls backlight.

76 Ppwr O This output is used to control the power to a flat panel.

Table 5. Test Pins

PIN # Name I/O Description

3 PSCAN I

Enable automatic PCB assembly test. When this input is pulled high, the

automatic PCB assembly test mode is entered. An internal pull-down resistor

drives this input low for normal operation.

155 SCAN_IN1 I

Scan input 1 used for automatic PCB assembly tesing.

157 SCAN_IN2 I

Scan input 2 used for automatic PCB assembly tesing.

159 SCAN_OUT1 O Scan output 1 used for automatic PCB assembly tesing.

160 SCAN_OUT2 O Scan output 2 used for automatic PCB assembly tesing.

153 Reserved

154 Reserved

Table 6. VDD / VSS for Core Circuitry, Host Interface, and Panel/Memory Interface

PIN # Description

65, 40, 33, 12 PVDD4~PVDD1 for panel / memory interface. Connect to +3.3V.

Must be the same voltage as the CVDD’s

149, 108, 58, 21, 11 SRVDD2-1, CVDD4, CVDD2-1 for core circuitry. Connect to +3.3V.

Must be the same voltage as the PVDD’s.

158, 151, 140, 126, 114, 72, 61,

49, 41, 30, 18, 8, 1 Digital grounds for core circuiry and panel / memory interface.

44

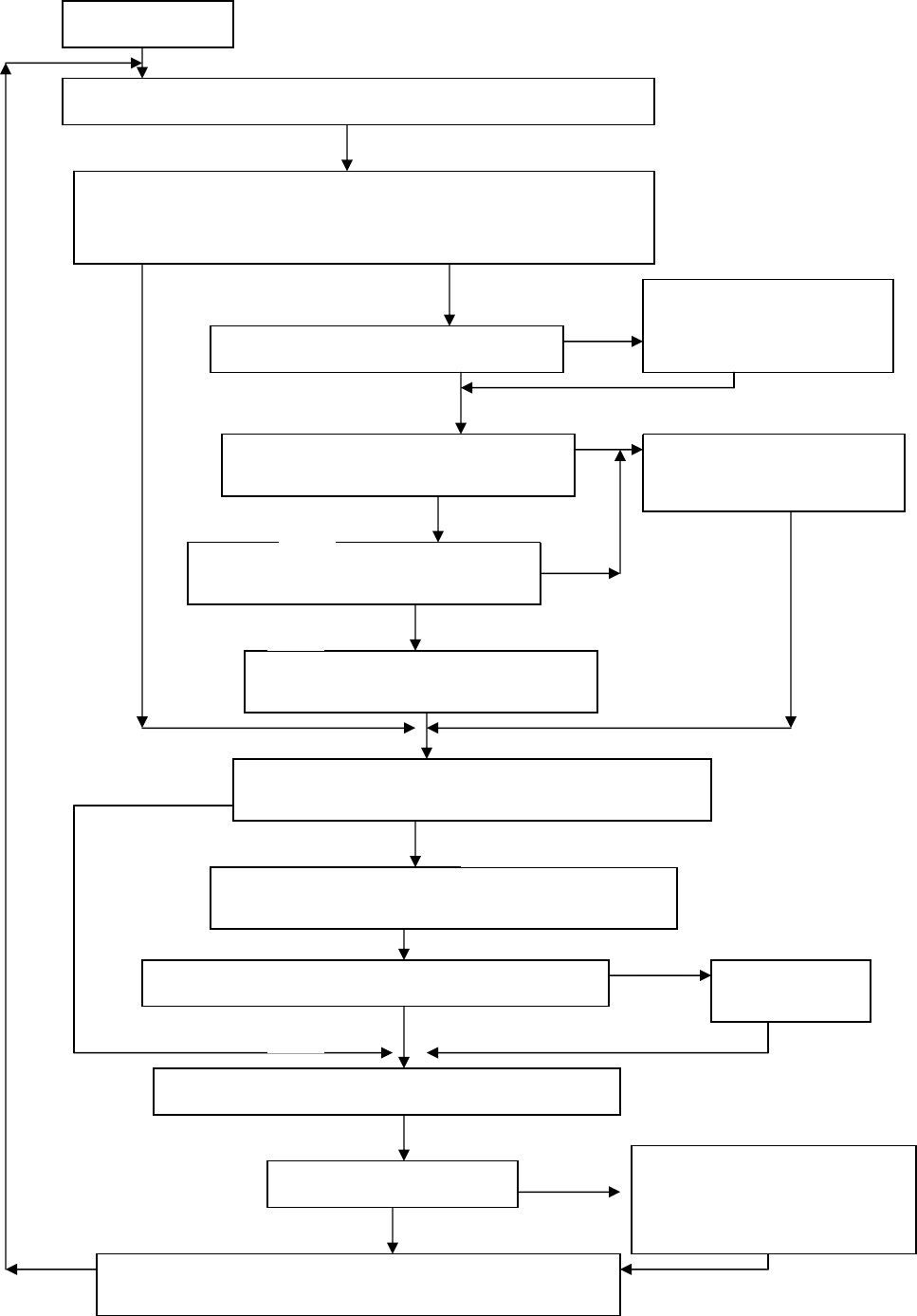

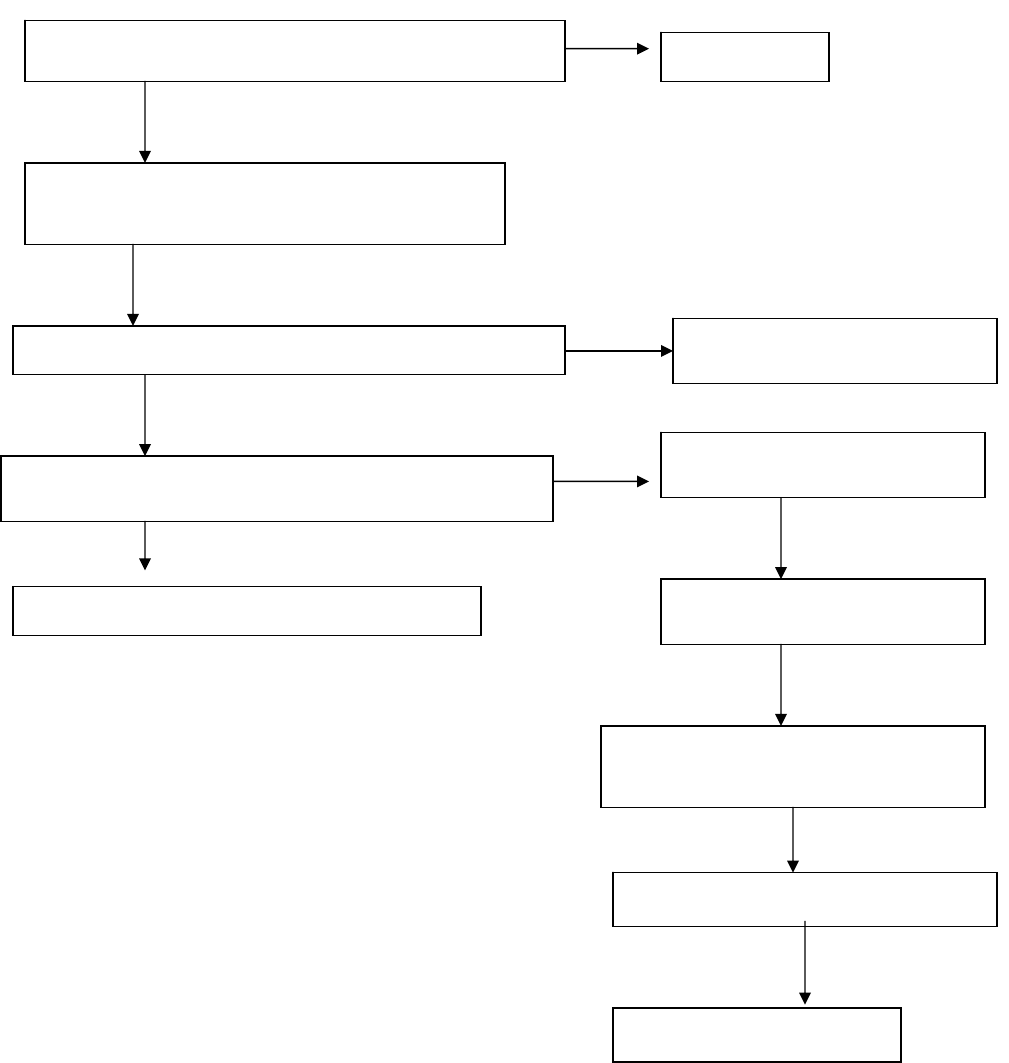

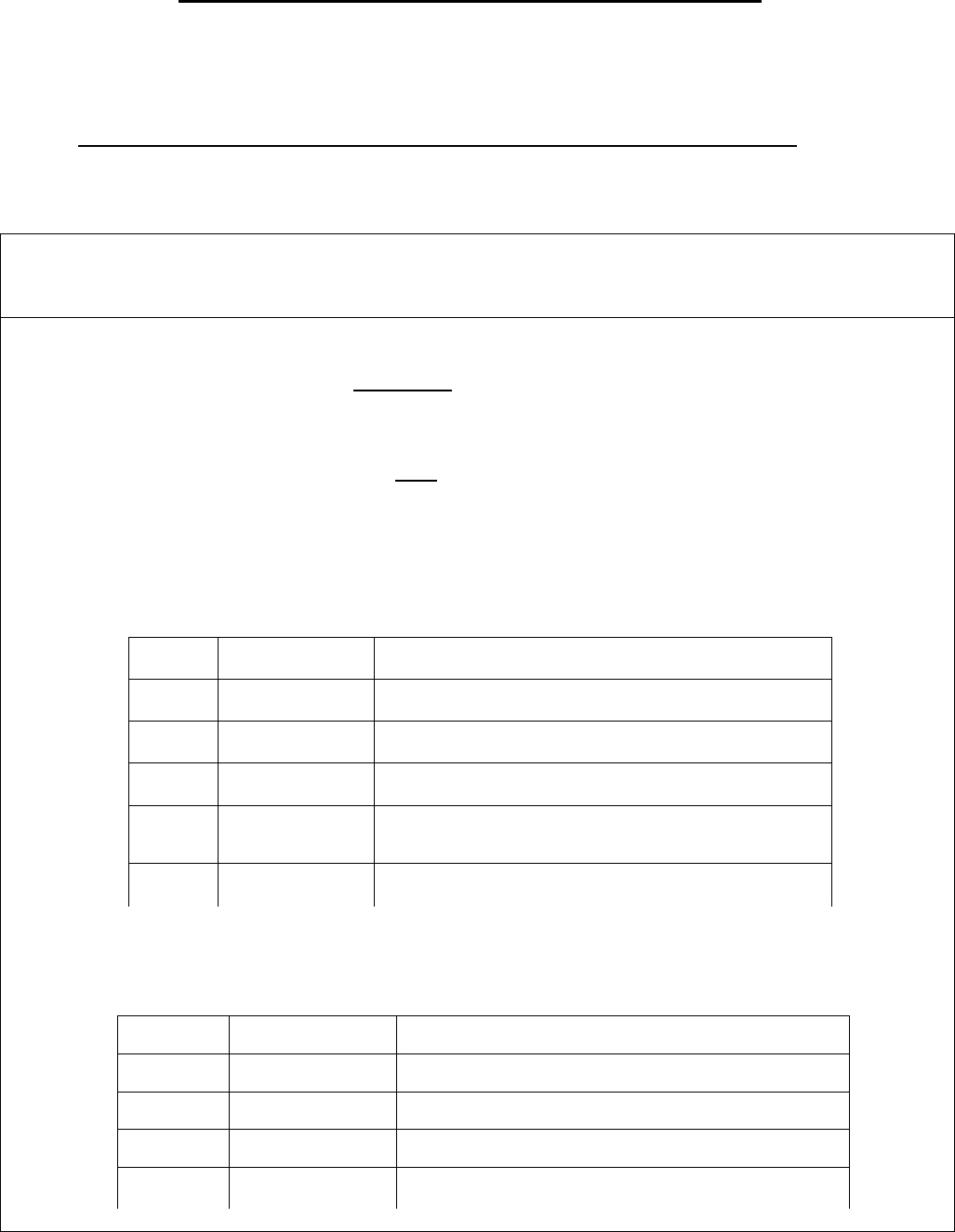

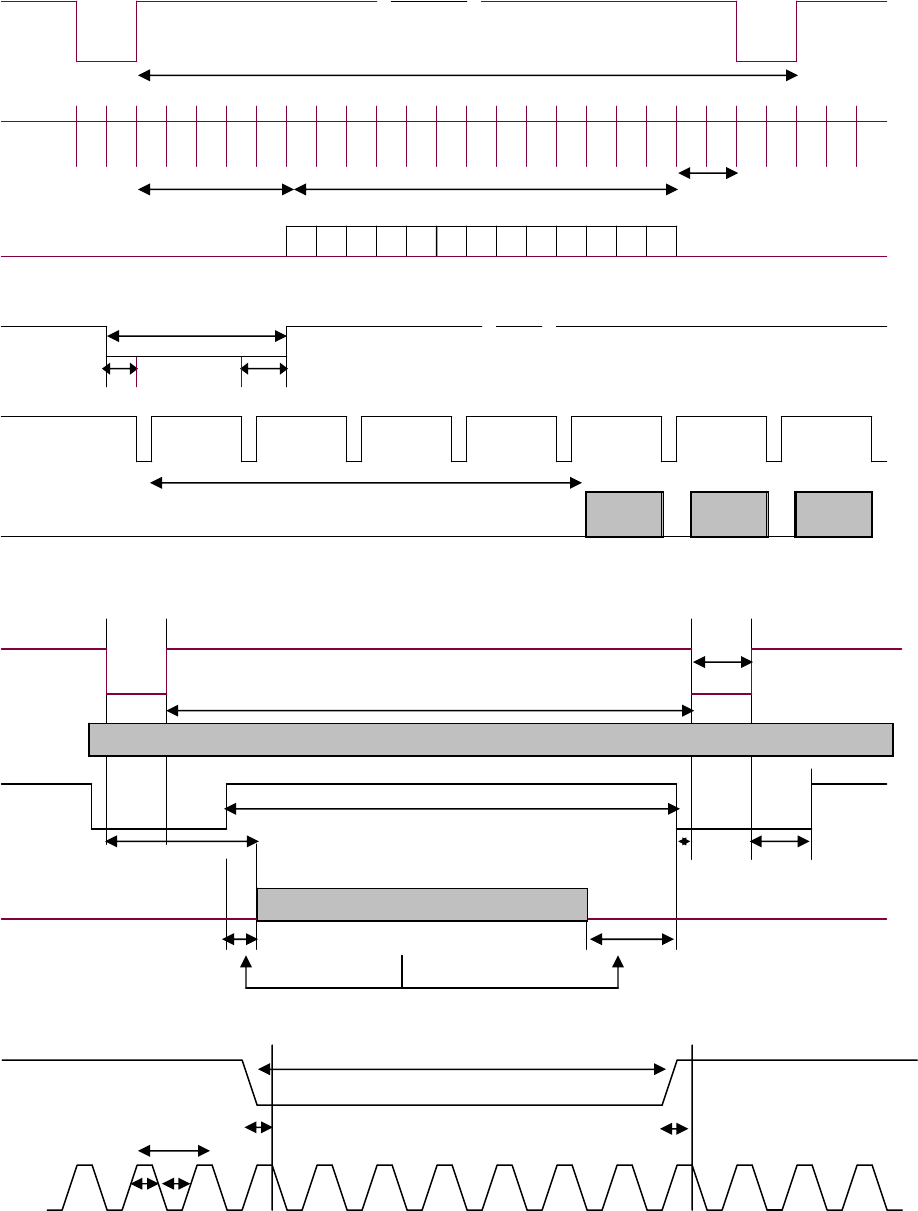

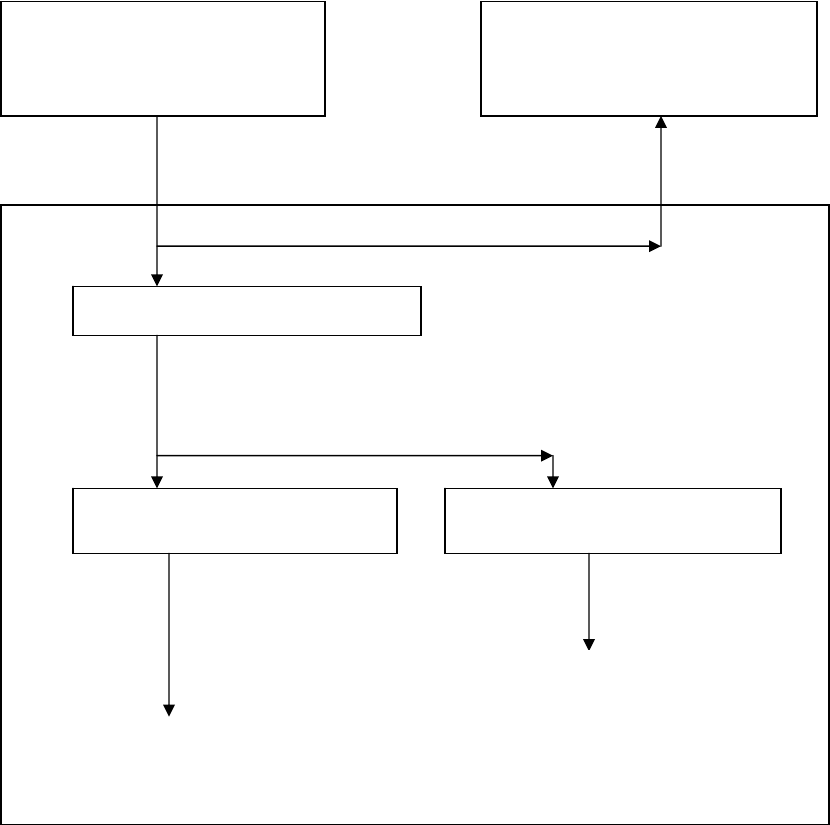

1.4 System-level Block Diagram

Figure 2. Typical Stand-alone Configuration

DVDDA

Panel Interface

SVDDA

SGNDA

OSC

ADC

RVDDA

Host Interface

DGNDA

Clock Generator

ADC_VDD

gmZAN1 Core

ADC_GND

ADC

RGNDA

TCLK

R1

R

R1

R

RVDDA

R1

R

R1

RR1

R

Video Connector

C1

C

L2

Vsync

C2

C

L1

Hsync

CVDD

Red

Blue

Green

On-Screen

Display

Controller

MPU with

EPROM

R+,G+,B+

OSD-FSW OSD-FSW

OSD-CLK

OSD-HREF

OSD-VREF

4

IRQ

HES

HCLK

HDATA

12

MFBs

RESETn

CVSS

TFT Panel

24

Even Data

PCLKA

PHS

PVS

PDISPE

Odd Data

24

Power

Switching

Module

Pbias Power

Switching

Module

Pbias

+12V

+5/3.3V

To Clock

Generator

45

1.5 Operating Modes

The Source Clock (also called SCLK in this document) and the Panel Clock are defined as follows:

z The Source Clock is the sample clock regenerated from the input Hsync timing (called clock recovery) by

SCLK DDS (direct digital synthesis) and the PLL.

z The Panel Clock is the timing clock for panel data at the single pixel per clock rate. The actual PCLK to the

panel may be one-half of this frequency for double-pixel panel data format. When its frequency is different from

that of source clock, the panel clock is generated by Destination Clock (or DCLK) DDS/PLL.

There are six display modes: Native, Slow DCLK, Zoom, Downscaling, Destination Stand Alone, and Source Stand

Alone.

Each mode is unique in terms of:

z Input video resolution vs. panel resolution

z Source Clock frequency / Panel Clock frequency ratio

z Source Hsync frequency / Panel Hsync frequenc ratio

z Data source (analog RGB, panel background color, on-chip pattern generator

1.5.1 Native

Panel Clock frequency = Source Clock frequency

Panel Hsync frequency = Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution and the input data clock frequency is

within the panel clock frequency specification of the panel being used.

1.5.2 Slow DCLK

Panel Clock frequency < Source Clock frequency

Panel Hsync frequency = Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution, but the input data clock frequency is

exceeds the panel clock frequency specification of the panel being used. The panel clock is scaled to the Source Clock,

and the internal data buffers are used to spread out the timing of the input data by making use of the large CRT

blanking time to extends the panel horizontal display time.

1.5.3 Zoom

Panel Clock frequency > Source Clock frequency

Panel Hsync frequency > Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is less than the panel resolution. The input data clock is then locked to the

pnael clock, which is at a higher frequency. The input data is zoomed to the panel resolution.

46

1.5.4 Downscaling

Panel Clock frequency < Source Clock frequency

Panel Hsync frequency < Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is greater than the panel resolution, to provide enough of a display to

enable the user to recover to a supported resolution. The input clock is operated at a frequency less than that of the

input pixel rate(under-sampled horizontally) and the scaling filter is used to drop input lines. In this mode, zoom

scaling must be disabled

1.5.5 Destination Stand Alone

Panel Clock = DCLK in open loop (not locked)

Panel Hsync frequency = DCLK frequency / (Destination Htotal register value)

Panel Vsync frequency = DCLK frequency / (Dest. Htotal register value * Dest. Vtotal register

value)

This mode is used when the input is changing or not available. The OSD may still be used as in all other display

modes and stable panel timing signals are produced. This mode may be automatically set when the gmZAN1 detects

input timing changes that could cause out- of-spec operation of the panel.

1.5.6 Source Stand Alone

Panel Clock = DCLK in open loop (not locked to input Hsync)

Panel Hsync frequency = SCLK frequency / (Source Htotal register value)

Panel Vsync frequency = SCLK frequency / (Source Htotal register value *Source Vtotal

register value)

This mode is used to display the pattern generator data. This mode may be useful for testing an LCD panel on the

manufacturing line (color temperature calibration, etc.).

47

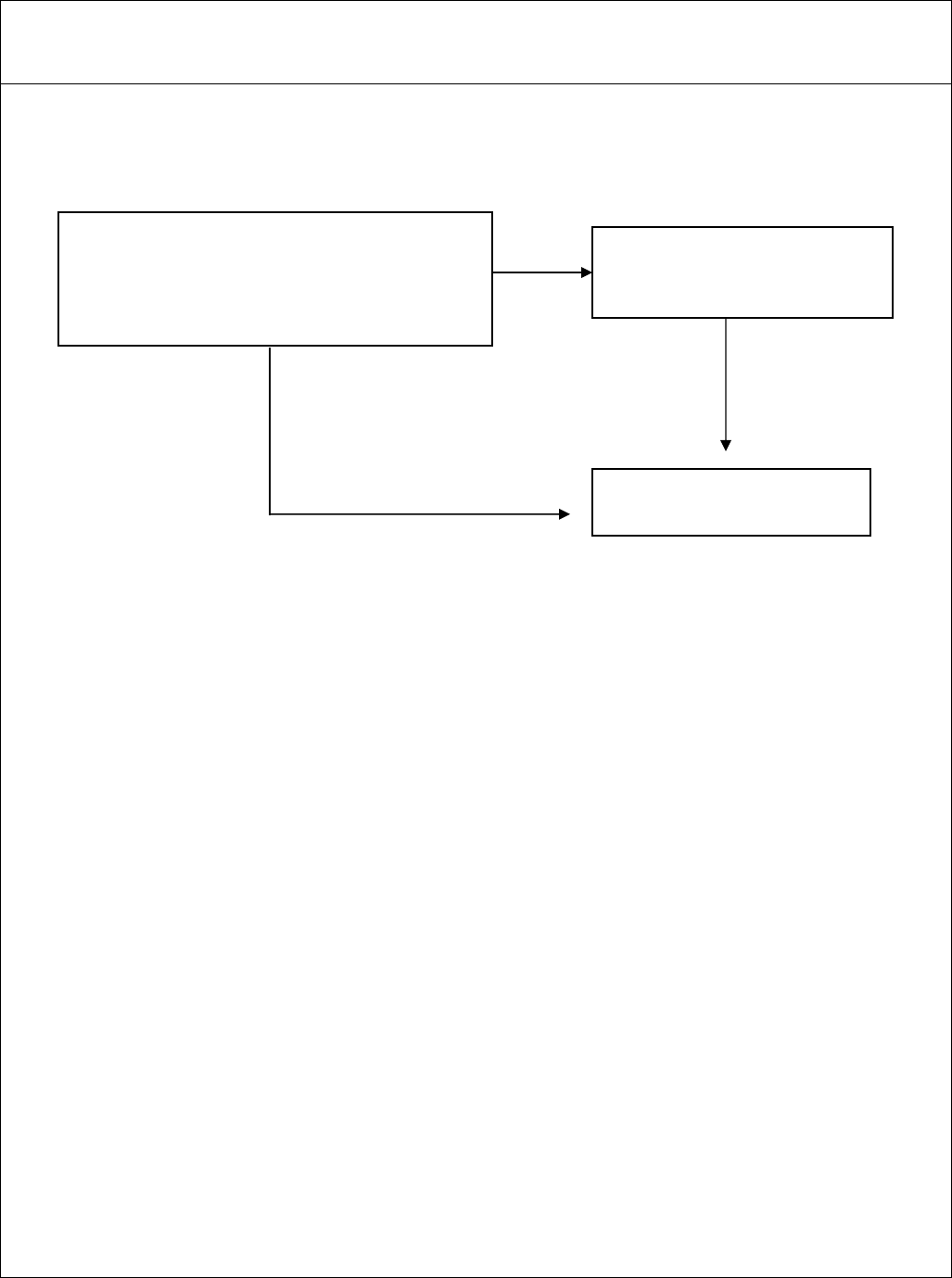

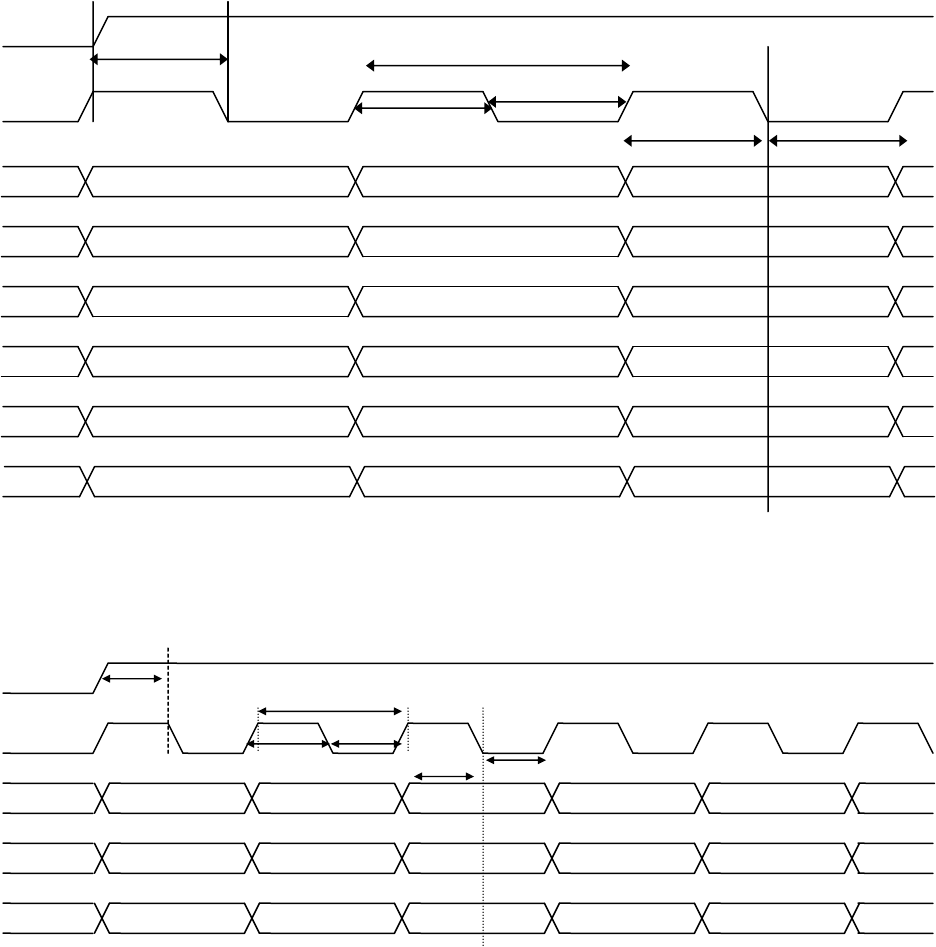

2. FUNCTIONAL DESCRIPTION

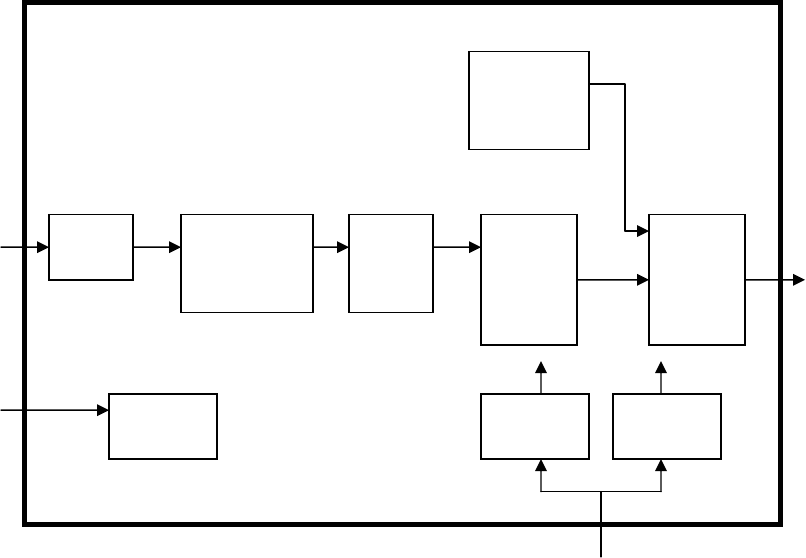

Figure 3 below shows the main functional blocks inside the gmZAN1

2.1 Overall Architecture

Figure 3. Block Diagram for gmZAN1

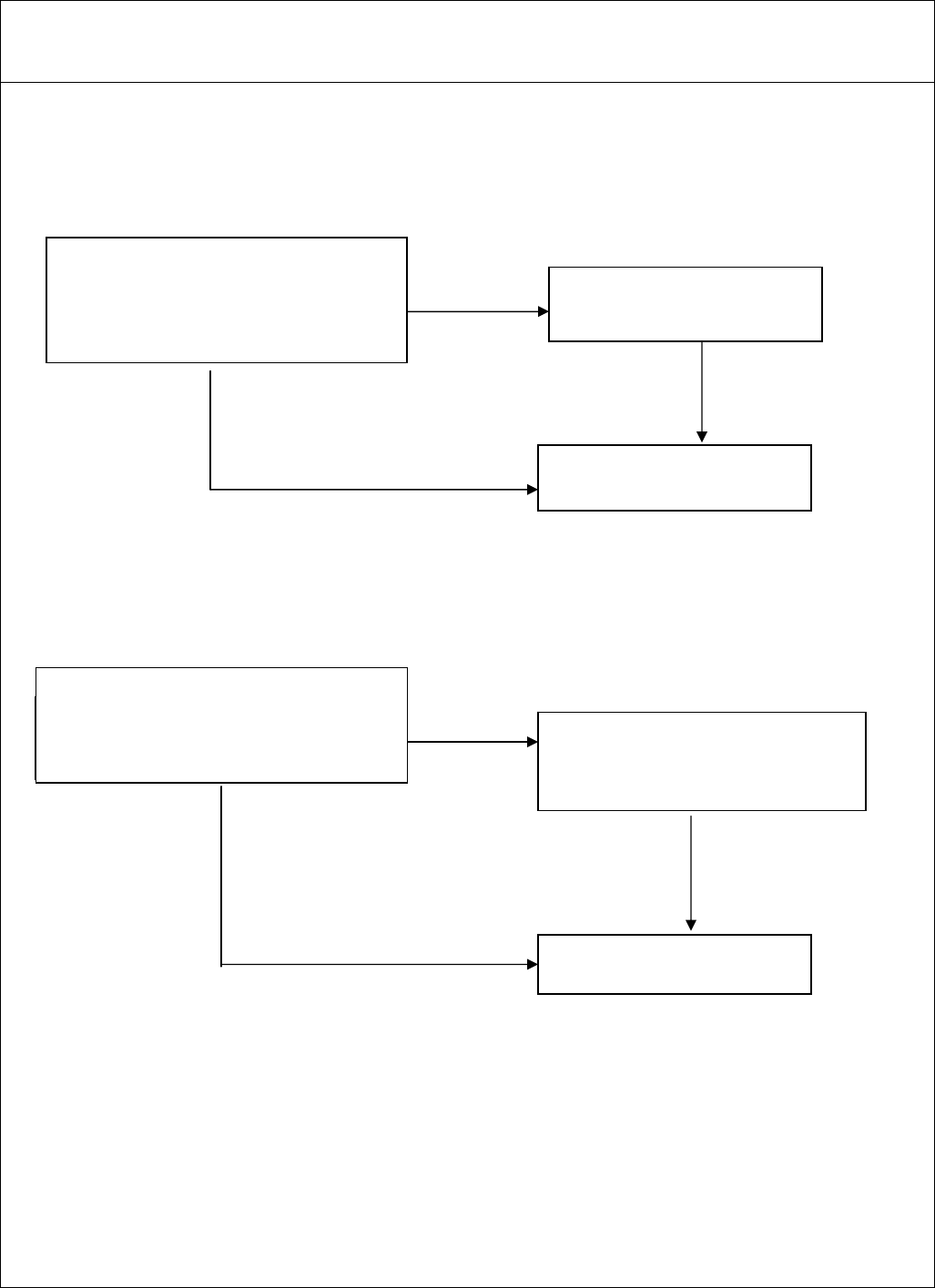

2.2 Clock Recovery Circuit

The gmZAN1 has a built-in clock recovery circuit. This circuit consists of a digital clock synthesizer and an analog

PLL. The clock recovery circuit generates the clock used to sample analog RGB data (SCLK or source clock). This

circuit is locked to the HSUNC of the incoming video signal. The RCLK generated from the TCLK input is used as a

reference clock.

The clock recovery circuit adjusts the SCLK period so that the feedback pulse generated every SCLK period

multiplied by the Source Horizontal Total value (as programmed into the registers) locks to the rising edge of the

Hsync input. Even though the initial SCLK frequency and the final SCLK frequency are as far apart as 60MHz ,

locking can be achieved in less than 1ms across the operation voltage/temperature range.

Triple

ADC Source

Timing

Measurement

/ Generation

Scaling

Engine Gamma

Control

(CLUT)

+

Dither

Panel

Timing

Control

On-Screen

Display

Control

Host

Interface Clock

Recovery

Pixel

Clock

Generator

Analog

RGB

MCU

Panel

Clock

Reference

48

The SCLK frequency (1/SCLK period) can be set to the range of 10-to-135 MHz. Using the DDS (direct digital

synthesis) technology the clock recovery circuit can generate any SCLK clock frequency within this range.

The pixel clock (DCLK or destination clock) is used to drive a panel when the panel clock is different from SCLK (or

SCLK/2). It is generated by a circuit virtually identical to the clock recovery circuit. The difference is that DCLK is

locked to SCLK while SCLK is locked to the Hsync input. DCLK frequency divided by N is locked to SCLK

frequency divided by M. The value M and N are calculated and programmed in the register by firmware. The value M

should be close to the Source Htotal value.

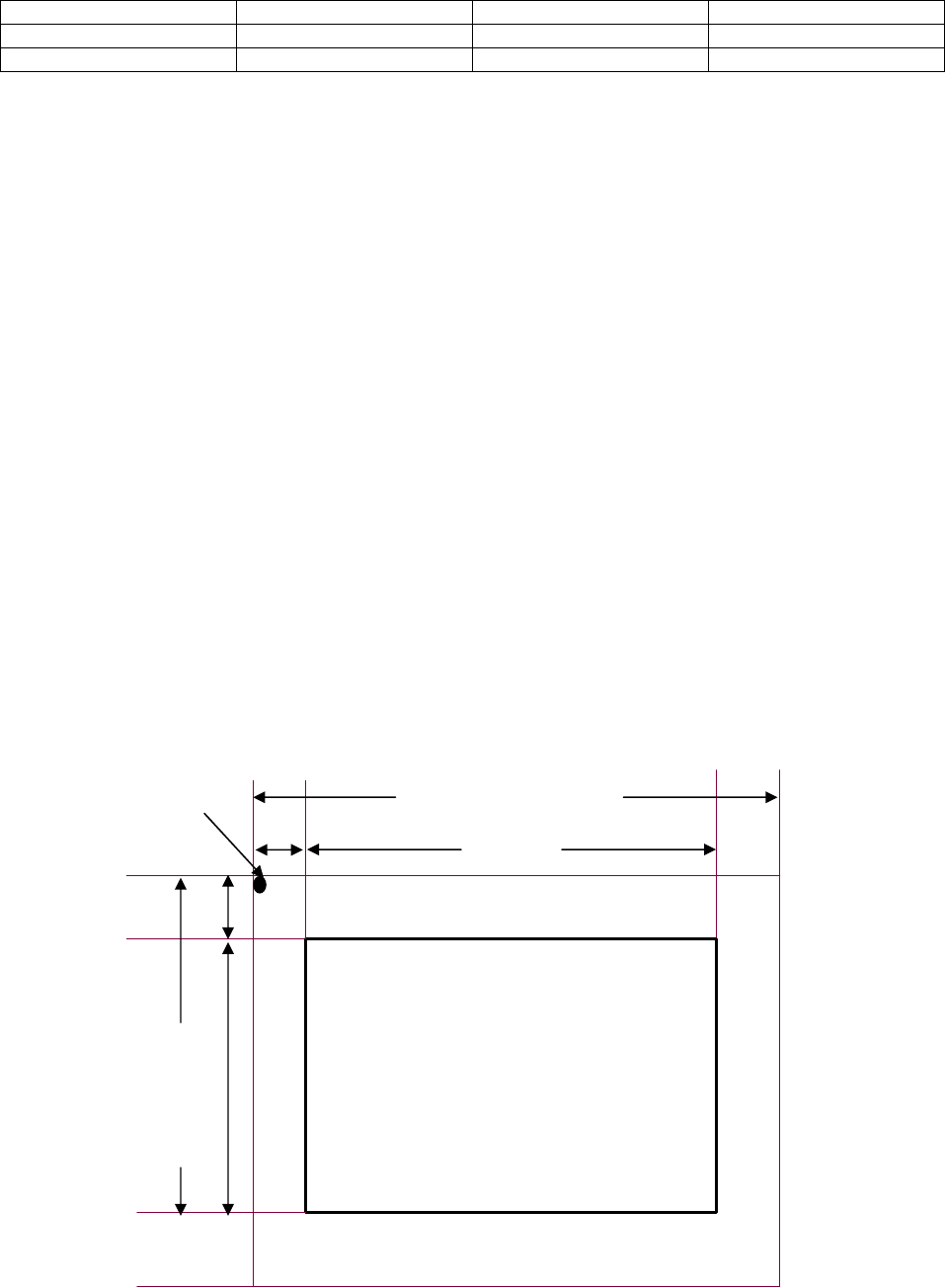

Figure 4. Clock Recovery Circuit

Sample

Phase

Delay

DDS Digital

Clock

Synthesis

Course

Adjust

Fine

Adjust

Analog

PLL & VCO

Clock

Divider

÷ n

PLL

Divider

÷

m

Prescaler

÷ 2 (or 1)

Source

Horizontal

Total Divider

Hsync

DDS Output VCO

Out

p

ut SCLK

Analog

PLL & VCO

Post Scale

÷ 2 (or 1)

PLL Divider

÷

n(2to8)

PLL Divider

÷

2 (or 1)

RCLK

TCLK

49

The table below summarizes the characteristics of the clock recovery circuit.

Table 7. Clock Recovery Characteristics

Minimum Typical Maximum

SCLK Frequency 10MHz 135 MHz

Sampling Phase Adjustment 0.5 ns/step, 64 steps

Patented digital clock synthesis technology makes the gmZAN1 clock circuits very immune to temperature/voltage

drift.

2.2.1 Sampling Phase Adjustment

The ADC sampling phase is adjusted by delaying the Hsync input at the programmable delay cell inside the gmZAN1.

The delay value can be adjusted in 64 steps, 0.5 ns/step. The accuracy of the sampling phase is checked by the

gmZAN1 and the “score” can be read in a register. This feature will enable accurate auto-adjustment of the ADC

sampling phase.

2.2.2 Source Timing Generator

The STG module defines a capture window and sends the input data to the data path block. The figure below shows

how the window is defined.

For the horizontal direction, it is defined in SCLKs (equivalent to a pixel count). For the vertical direction, it is

defined in lines.

All the parameters in the figure that begin with “Source” are programmed into the gmZAN1 registers.

Note that the vertical total is solely determined by the input.

The reference point is as follows:

z The first pixel of a line: the pixel whose SCLK rising edge sees the transition of the HSYNC polarity from low

to high.

z The first line of a frame: the line whose HSYNC rising edge sees the transition of the VSYNC polarity from low

to high.

The gmZAN1 also supports the use of analog composite sync and digital sync signals as described in Section 2.3.2

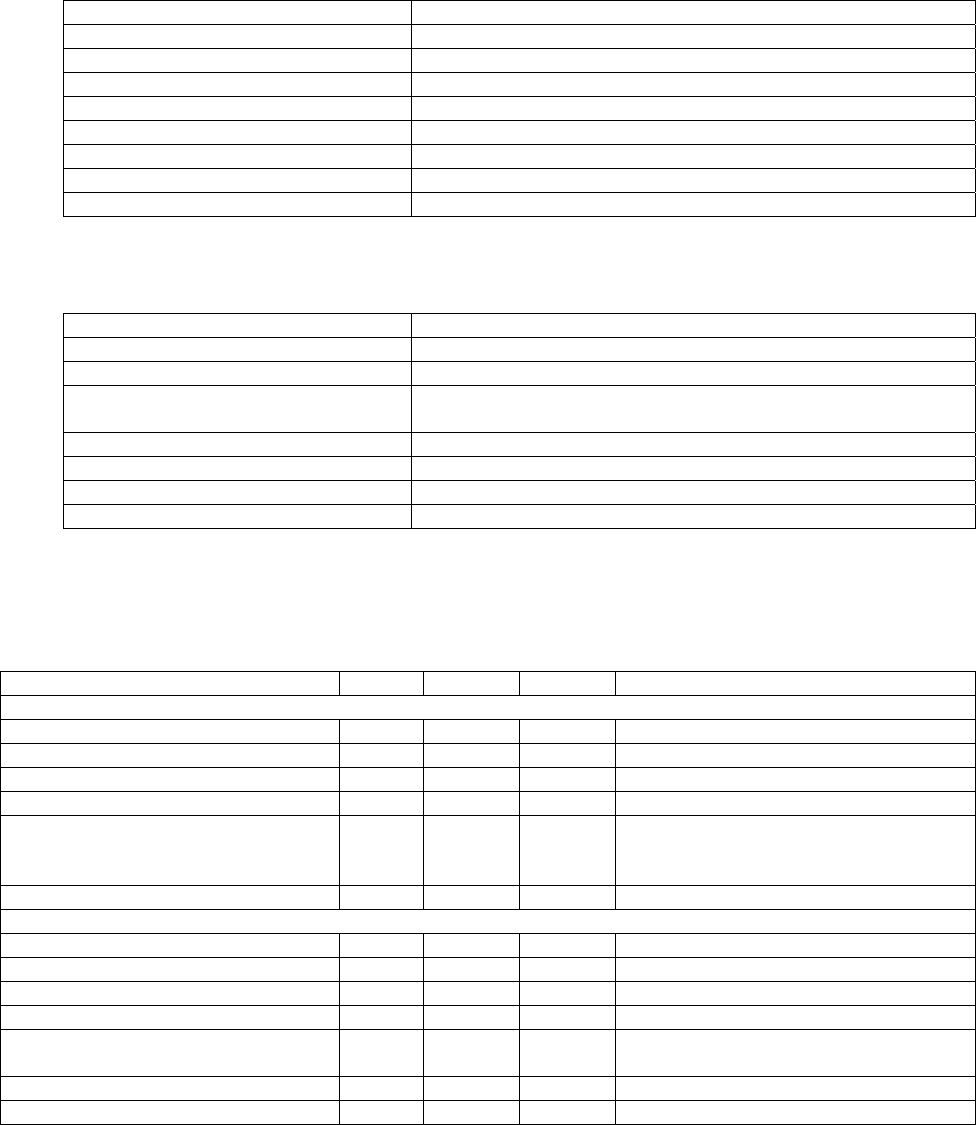

Figure 5. Capture Window

Capture Window

Source Vertical Total (lines)

Source

Hstart

Source Height

Reference

Point

Source

Vstart

Source Horizontal Total (pixels)

Source Width

50

2.3 Analog-to-Digital Converter

2.3.1 Pin Connection

The RGB signals are to be connected to the gmZAN1 chip as described in Table 8 and Table 9.

Table 8. Pin Connection for RGB Input with Hsync/Vsync

GmZAN1 Pin Name (Pin Number) CRT Signal Name

Red+(#95) Red

Red- (#94) N/A (Tie to Analog GND for Red on the board)

Green+(#91) Green

Green- (#90) N/A (Tie to Analog GND for Green on the board)

Blue+(#87) Blue

Blue- (#86) N/A (Tie to Analog GND for Blue on the board)

HSYNC/CS (#150) Horizontal Sync

VSYNC (#148) Vertical Sync

Table 9. Pin Connection for RGB Input with Composite Sync