Cypress Semiconductor 0737 This product is a Bluetooth wireless EZ-BT WICED SIP Module User Manual CYW20737S 0514

Cypress Semiconductor This product is a Bluetooth wireless EZ-BT WICED SIP Module CYW20737S 0514

Contents

- 1. User Manual_CYW20732S - 0514

- 2. User Manual_CYW20736S - 0514

- 3. User Manual_CYW20737S - 0514

User Manual_CYW20737S - 0514

CYW20737S

Bluetooth Low Energy

System-in-Package (SiP) Module

Cypress Semiconductor Corporation • 198 Champion Court • San Jose,CA 95134-1709 • 408-943-2600

Document Number: 002-14888 Rev. *C Revised April 21, 2017

The CYW20737S is a compact, highly integrated Bluetooth Low Energy (BLE) system-in-package (SiP) module. The CYW20737S

SiP includes an embedded BLE antenna, 24 MHz clock, and 512 Kb EEPROM, so only a minimal set of external components is

needed to create a standalone BLE device.

The CYW20737S is designed to accelerate time to market. The Bluetooth stack and several application profiles are built into the

module, allowing customers to focus on their core applications. To further reduce application development time, the CYW20737S

includes integrated software support, with one-click installation of the complete environment and a one-click compile/build/link/load

cycle. All this, coupled with an ultrasmall form factor and support for a wide voltage range, makes the CYW20737S well suited for

virtually any Bluetooth Smart application.

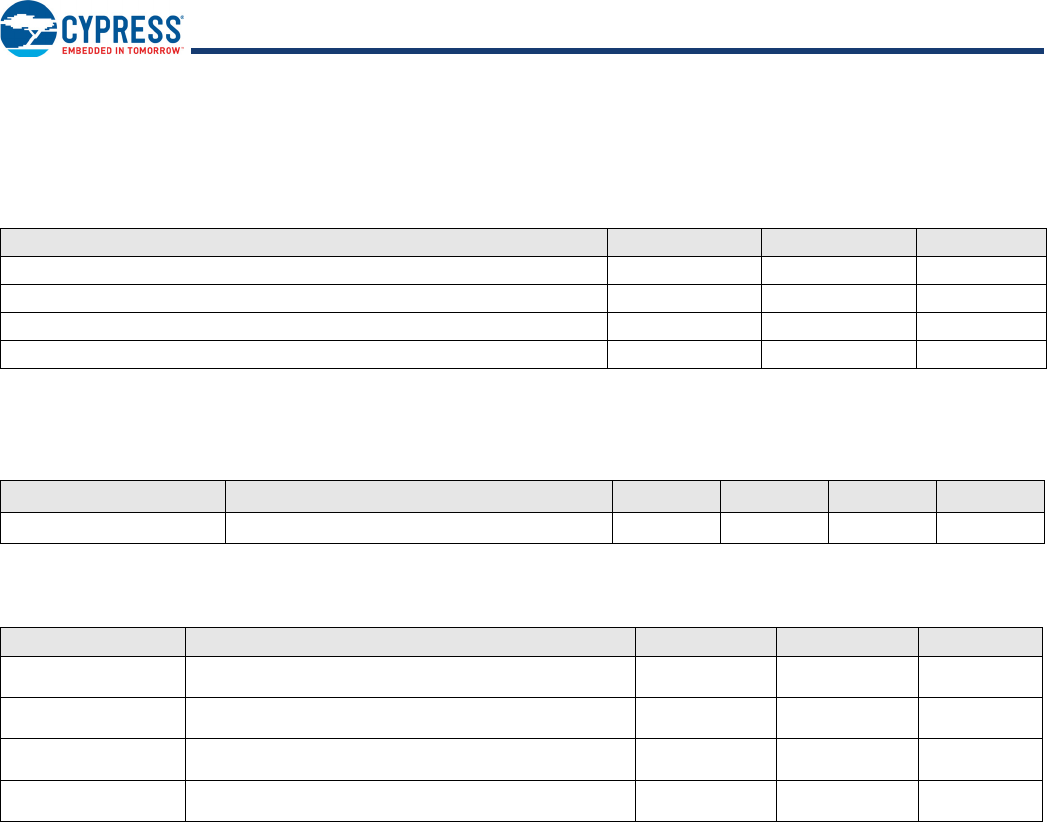

Cypress Part Numbering Scheme

Cypress is converting the acquired IoT part numbers from Broadcom to the Cypress part numbering scheme. Due to this conversion,

there is no change in form, fit, or function as a result of offering the device with Cypress part number marking. The table provides

Cypress ordering part number that matches an existing IoT part number.

Features

■ARM Cortex-M3 microcontroller unit (MCU)

■Embedded 512 Kb EEPROM

■Broadcom Serial Control (BSC), SPI, and UART interfaces

■FCC and CE compliant

■RoHS compliant, certified lead- and halogen-free

■Moisture Sensitivity Level (MSL) 3 compliant

■6.5 mm × 6.5 mm × 1.2 mm Land Grid Array (LGA) 48-pin

package

Applications

Profiles supported in ROM:

■Battery status

■Blood pressure monitor

■Find me

■Heart rate monitor

■Proximity

■Thermometer

■Weight scale

■Time

■Blood glucose monitor

■Support for RSA security library

■Support for LE Audio

■Support for pairing using NFC tags

Additional profiles supported in RAM:

■Blood glucose monitor

■Temperature alarm

■Location

■Other custom profiles

Table 1. Mapping Table for Part Number between Broadcom and Cypress

Broadcom Part Number Cypress Part Number

BCM20737S CYW20737S

Document Number: 002-14888 Rev. *C Page 2 of 24

CYW20737S

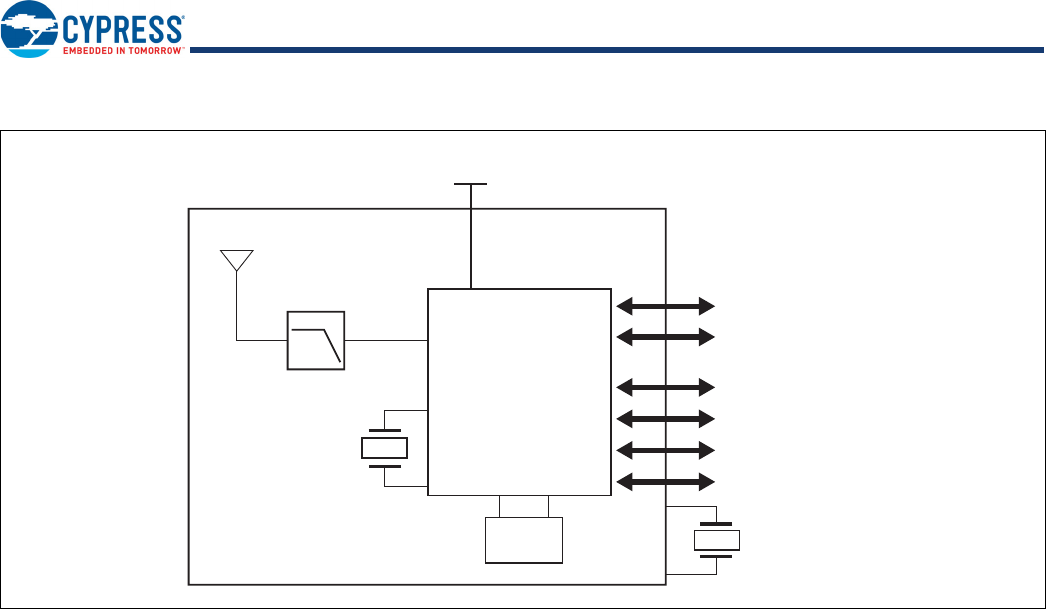

Figure 1. CYW20737S BLE SiP Block Diagram

IoT Resources

Cypress provides a wealth of data at http://www.cypress.com/internet-things-iot to help you to select the right IoT device for your

design, and quickly and effectively integrate the device into your design. Cypress provides customer access to a wide range of

information, including technical documentation, schematic diagrams, product bill of materials, PCB layout information, and software

updates. Customers can acquire technical documentation and software from the Cypress Support Community website

(http://community.cypress.com/).

VBAT/VDDIO

BCM20737S

Bluetooth Low Energy

System-on-Chip with

ARM ® Cortex™ M3-based

Microprocessor Core

Antenna

Bandpass

Filter UART

SPI/I2C

Infrared

ADC

GPIOs

PWM

32.768 kHz

Oscillator

(optional)

24 MHz

XTAL

EEPROM

512 Kb I2C

BCM20737S

CYW20737S

CYW20737S

Document Number: 002-14888 Rev. *C Page 3 of 24

CYW20737S

Contents

1. Functional Description .................................................4

1.1 External Reset .......................................................4

1.2 32.768 kHz Oscillator ............................................ 4

2. Pin Map and Signal Descriptions ................................5

3. Electrical Specifications ............................................ 10

4. RF Specifications ....................................................... 11

5. ADC Specifications .................................................... 12

6. Timing and AC Characteristics .................................13

6.1 SPI Timing ...........................................................13

6.2 BSC Interface Timing ..........................................14

6.3 UART Timing ....................................................... 15

7. PCB Design and Manufacturing Recommendations 16

7.1 Pad and Solder Mask Opening Dimensions ........ 16

7.2 PCB Layout Recommendations .......................... 16

7.3 PCB Stencil ............................................................... 17

7.4 Solder Reflow ...................................................... 17

8. Packaging and Storage Information ......................... 18

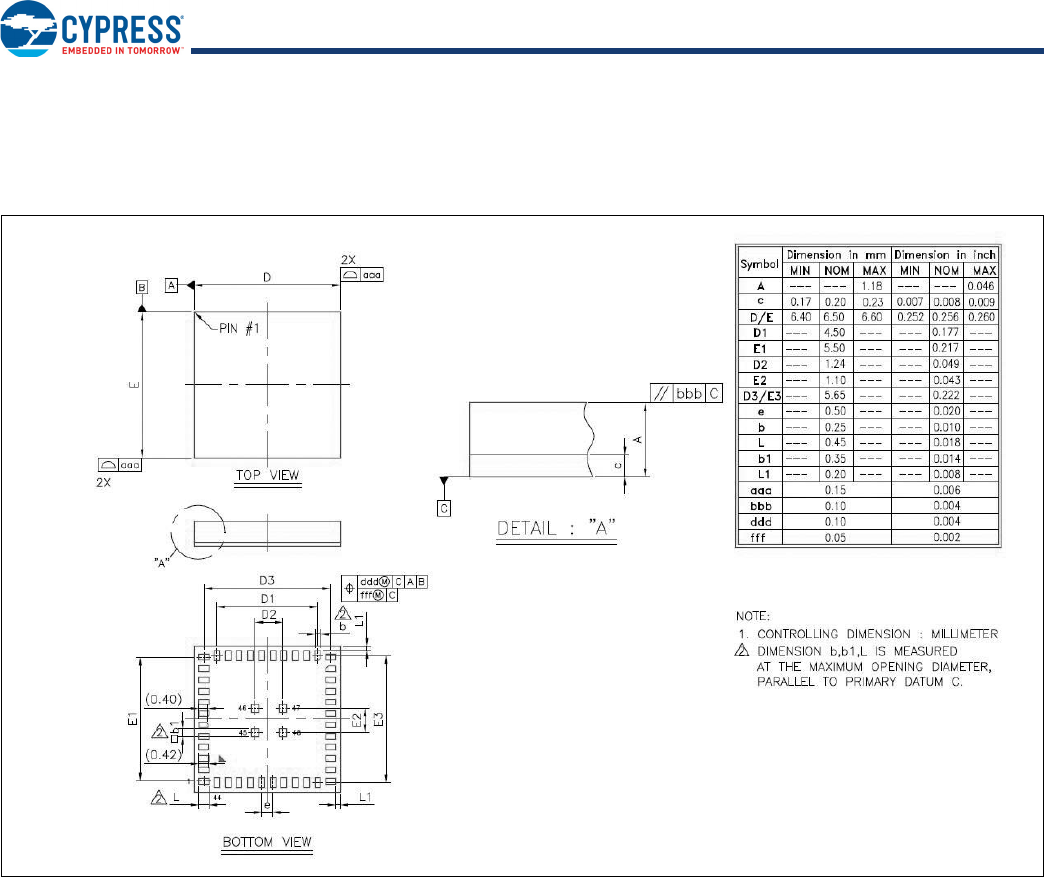

9. Mechanical Information ............................................. 20

10. Ordering Information ................................................ 22

Document History .......................................................... 23

Document Number: 002-14888 Rev. *C Page 4 of 24

CYW20737S

1. Functional Description

1.1 External Reset

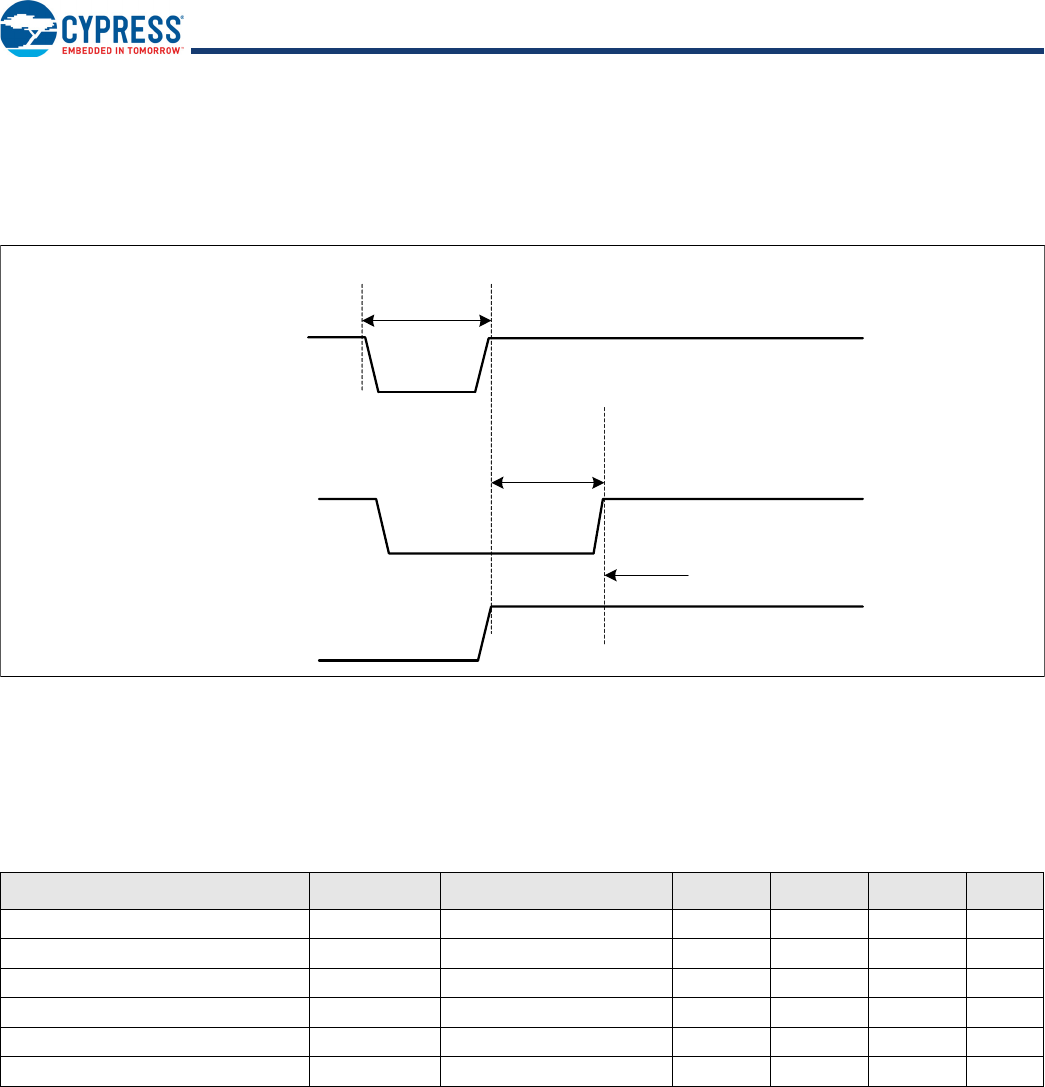

External reset timing for the CYW20737S is illustrated in Figure 2.

Figure 2. External Reset Timing

1.2 32.768 kHz Oscillator

The CYW20737S includes a standard Pierce oscillator. The oscillator circuit includes a comparator with hysteresis on the output to

create a single-ended digital output. The hysteresis eliminates chatter when the input is near the comparator threshold (~100 mV).

The oscillator circuit can is designed for a 32 kHz or 32.768 kHz crystal oscillator, and can also be driven by an external clock input

with a similar frequency. Characteristics for a 32 kHz oscillator are defined in Ta b l e 2 .

Table 2. 32 kHz Crystal Oscillator Characteristics

Parameter Symbol Conditions Min. Typ. Max. Unit

Output frequency Foscout – – 32.768 – kHz

Frequency tolerance Ftol Crystal-dependent – 100 – ppm

Start-up time Tstartup – – – 500 µs

Crystal drive level Pdrv For crystal selection 0.5 – – µW

Crystal series resistance Rseries For crystal selection – – 70 k

Crystal shunt capacitance Cshunt For crystal selection – – 1.3 pF

RESET_N

Pulsewidth

>20µs

CrystalEnable

BasebandReset

StartreadingEEPROMand

firmwareboot

Crystal

warm‐up

delay:

~5ms

Document Number: 002-14888 Rev. *C Page 5 of 24

CYW20737S

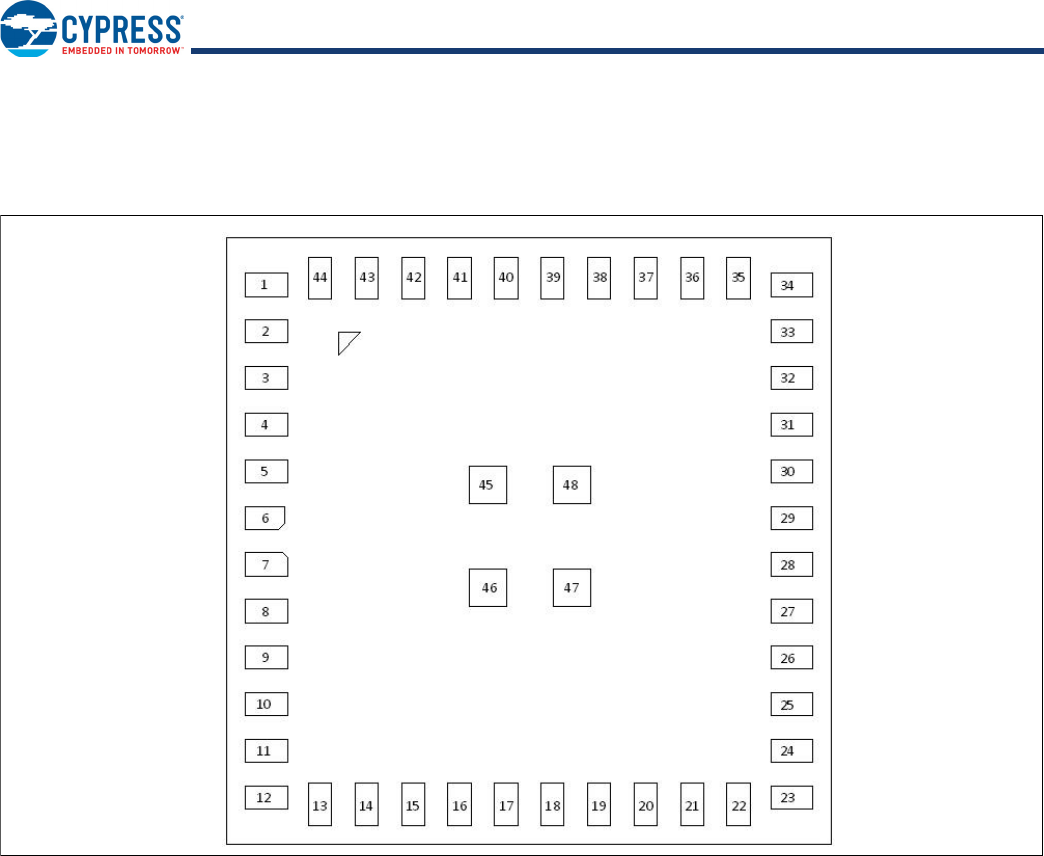

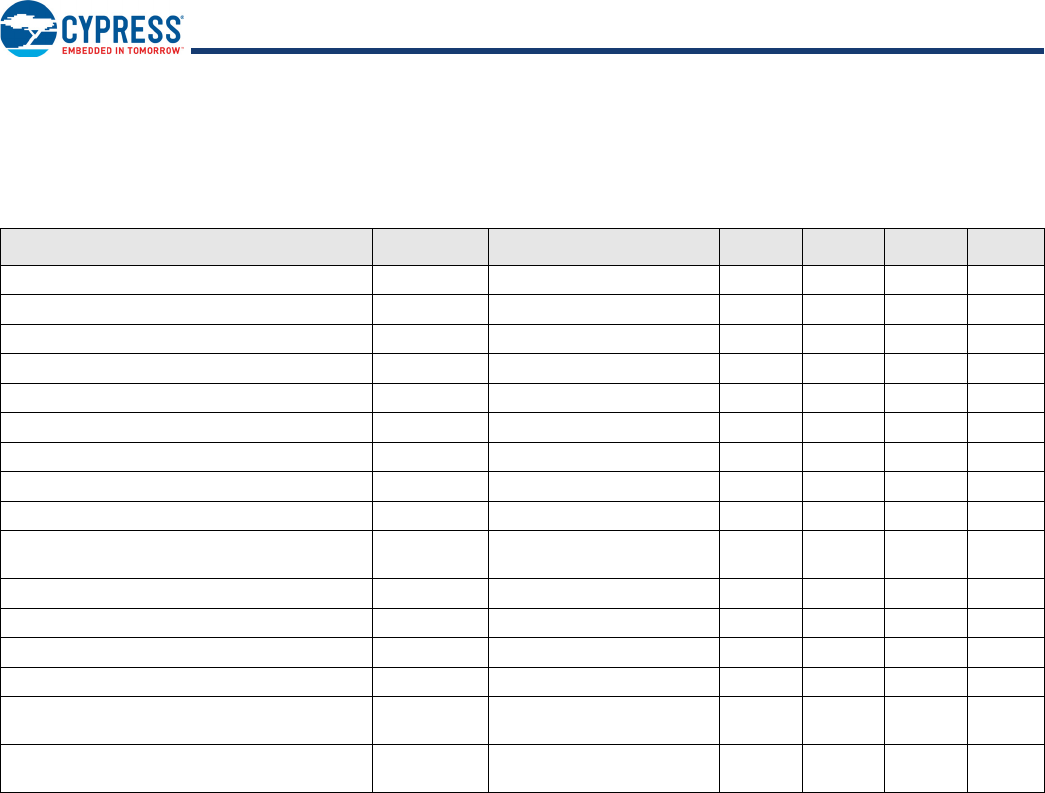

2. Pin Map and Signal Descriptions

The CYW20737S pin map is shown in Figure 3.

Figure 3. CYW20737S (TOP View)

The signal name, type, and description of each pin in the CYW20737S is listed in Table 3 on page 6. The symbols shown under

I/O Type indicate pin directions (I/O = bidirectional, I = input, O = output) and the internal pull-up/pull-down characteristics (PU = weak

internal pull-up resistor and PD = weak internal pull-down resistor), if any.

Document Number: 002-14888 Rev. *C Page 6 of 24

CYW20737S

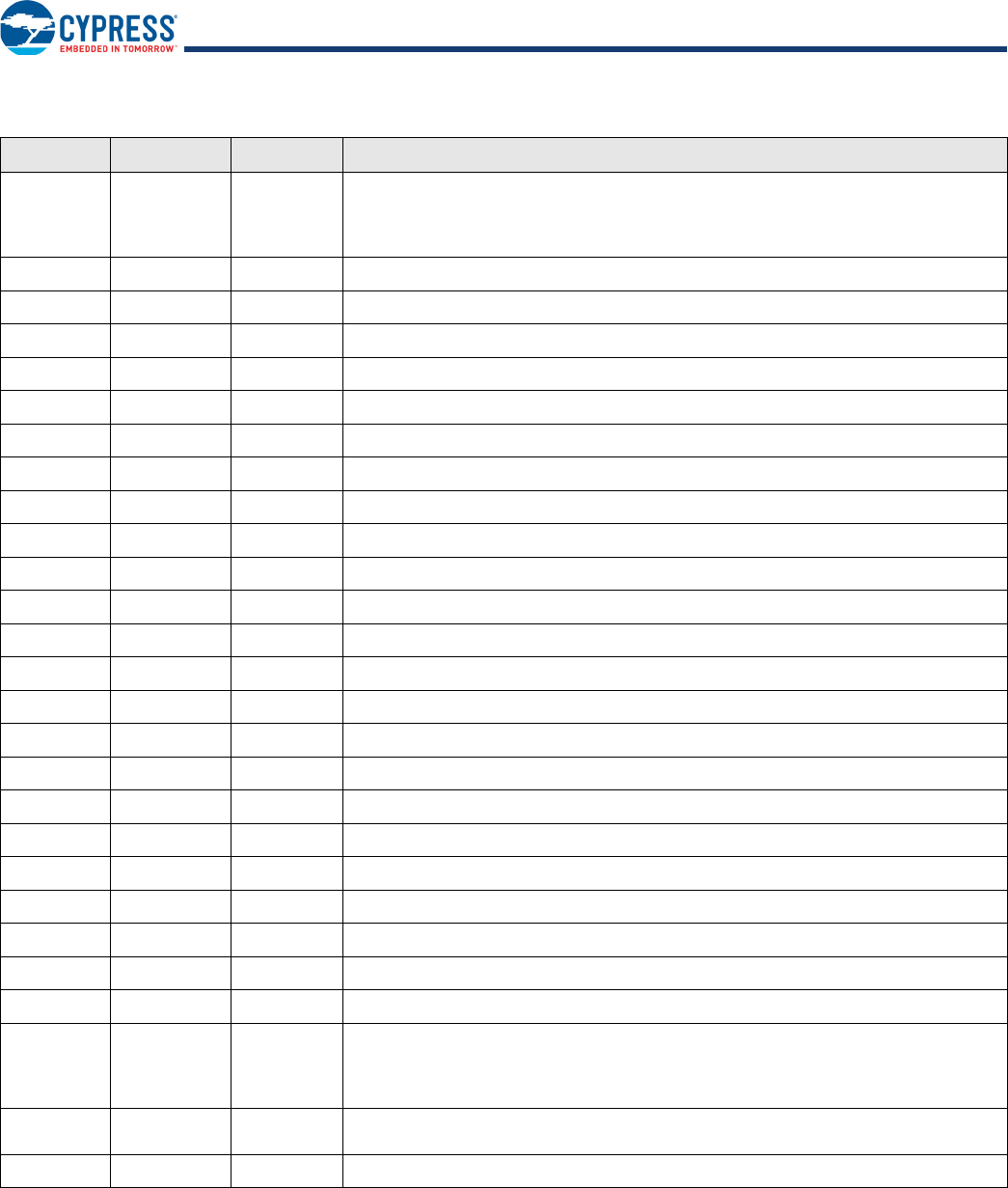

Table 3. Pin Descriptions

Pin Name I/O Type Description

1GPIO: P27

PWM1 I

Default direction: Input.

After POR state: Input floating.

Drain current: 16 mA

Alternate function: MOSI (master and slave) for SPI_2

2 GND GND GND

3 VBAT I Battery supply input.

4 GND GND GND

5 GND GND GND

6 GND GND GND

7 GND GND GND

8 GND GND GND

9 GND GND GND

10 Reserved – Leave floating

11 GND GND GND

12 GND GND GND

13 GND GND GND

14 GND GND GND

15 GND GND GND

16 GND GND GND

17 GND GND GND

18 UART_RX I UART_RX. This pin is pulled low through an internal 10 k resistor.

19 UART_TX O, PU UART_TX

20 GND GND GND

21 SCL I/O, PU SCL I/O, PU clock signal for an external I2C device

22 SDA I/O, PU SDA I/O, PU data signal for an external I2C device

23 GND GND GND

24 GND GND GND

25 GPIO: P1 I

Default direction: Input.

After POR state: Input floating.

This pin is tied to the WP pin of the embedded EEPROM.

Requires an external 10K pull-up

26 TMC I Test mode control. Pull this pin high to invoke test mode; leave it floating if not used.

This pin is connected to GND through an internal 10 k resistor.

27 RESET_N I/O PU Active-low system reset with open-drain output

Document Number: 002-14888 Rev. *C Page 7 of 24

CYW20737S

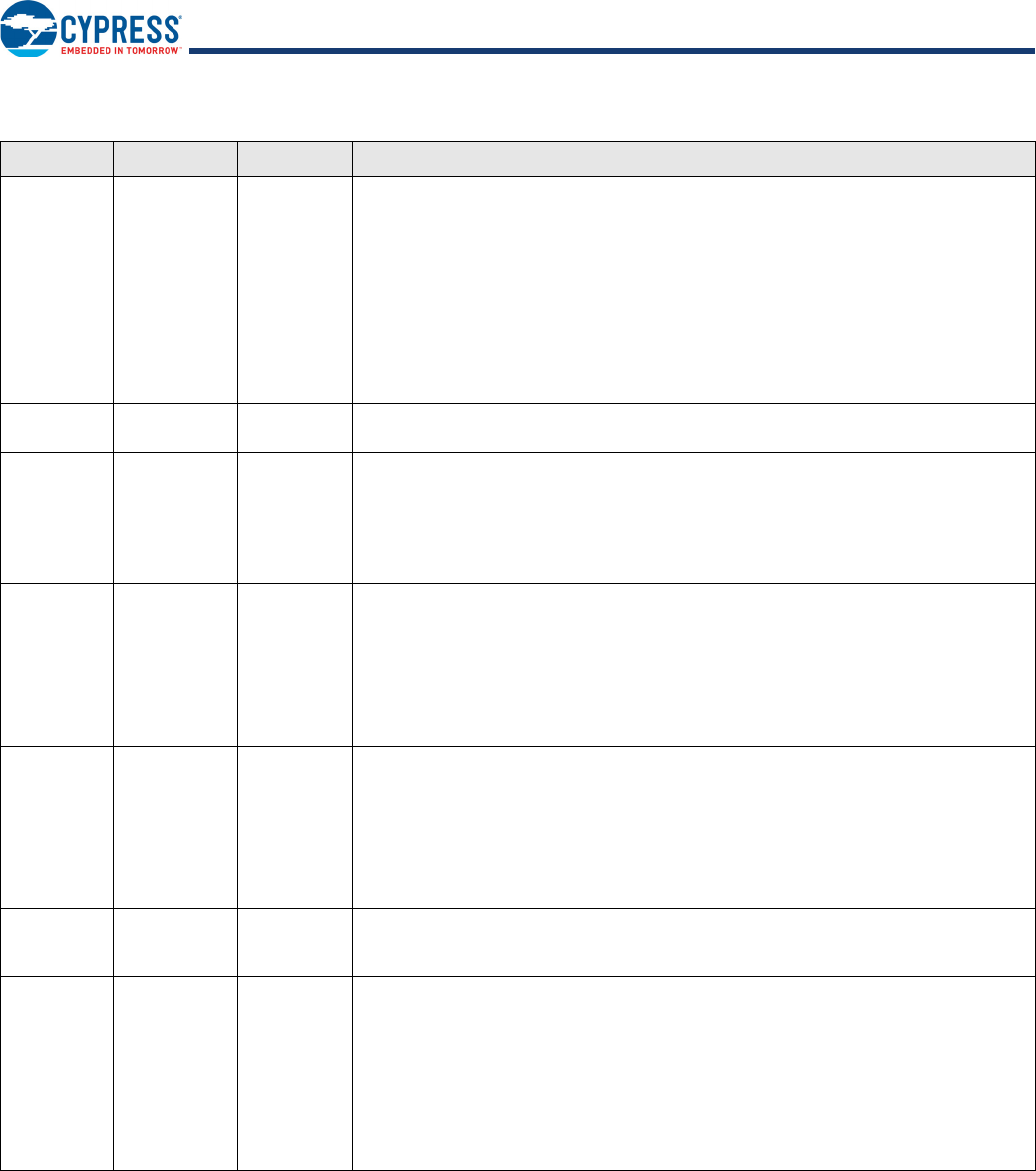

28 GPIO: P0 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■A/D converter input

■Peripheral UART TX (PUART_TX)

■MOSI (master and slave) for SPI_2

■IR_RX

■60Hz_main

29 GND GND GND

30 GPIO: P3 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■Peripheral UART CTS (PUART_CTS)

■SPI_CLK (master and slave) for SPI_2

31 GPIO: P2 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■Peripheral UART RX (PUART_RX)

■SPI_CS (slave only) for SPI_2

■SPI_MOSI (master only) for SPI_2

32 GPIO: P4 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■Peripheral UART RX (PUART_RX)

■MOSI (master and slave) for SPI_2.

■IR_TX

33 GPIO: P8 I

Default direction: Input.

After POR state: Input floating.

Alternate functions: A/D converter input.

34 GPIO: P33 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■A/D converter input

■MOSI (slave only) for SPI_2

■Auxiliary clock output (ACLK1)

■Peripheral UART RX (PUART_RX)

Table 3. Pin Descriptions (Cont.)

Pin Name I/O Type Description

Document Number: 002-14888 Rev. *C Page 8 of 24

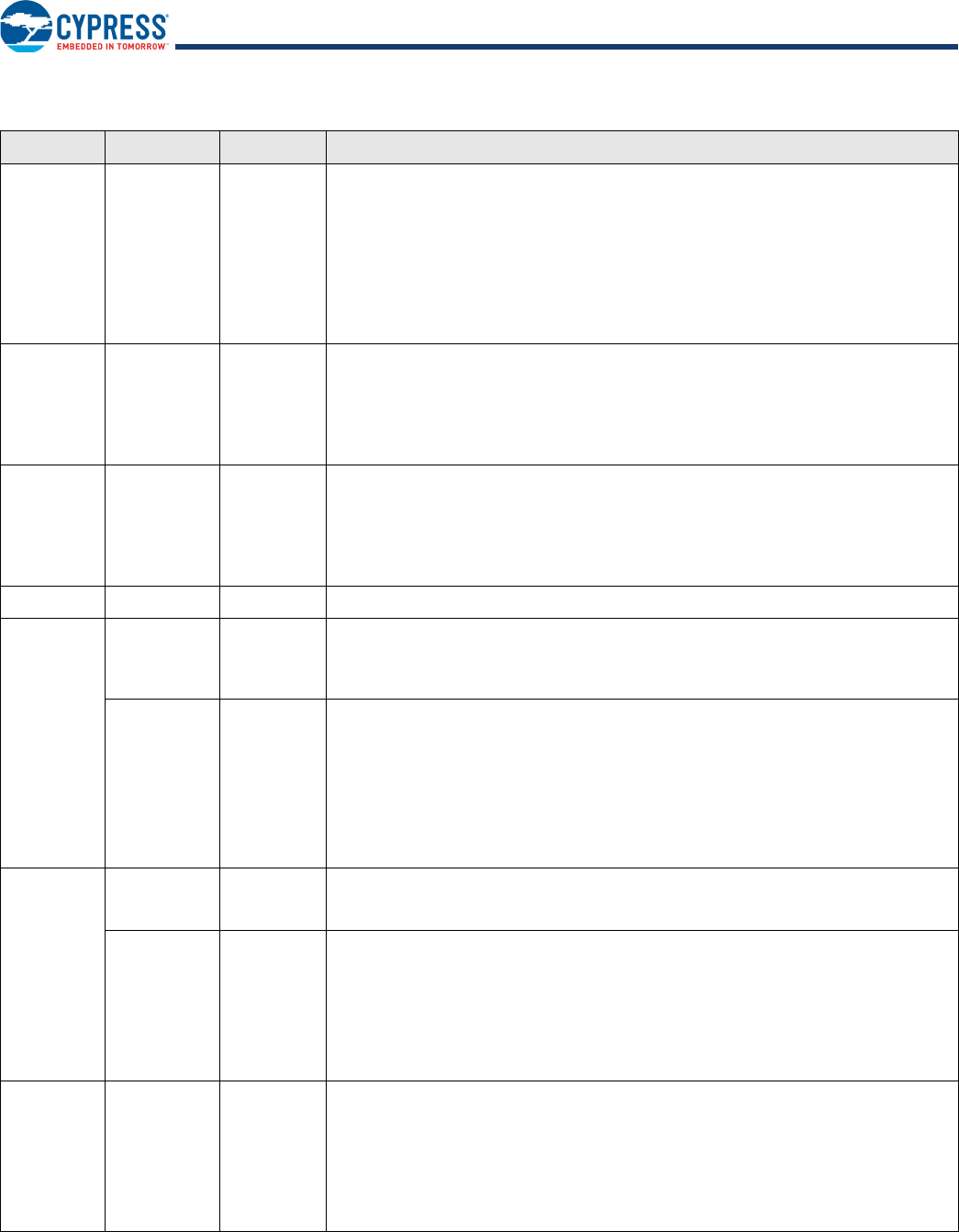

CYW20737S

35 GPIO: P32 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■A/D converter input

■SPI_CS (slave only) for SPI_2.

■Auxiliary clock output (ACLK0)

■Peripheral UART TX (PUART_TX)

36 GPIO: P25 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■MISO (master and slave) for SPI_2

■Peripheral UART RX (PUART_RX)

37 GPIO: P24 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■SPI_CLK (master and slave) for SPI_2

■Peripheral UART TX (PUART_TX)

38 NC NC No Connection (N/C).

39

GPIO: P13

PWM3 I

Default Direction: Input

After POR State: Input Floating

Drain current: 16 mA

Alternate function: A/D converter input

GPIO: P28

PWM2 I

Default direction: Input.

After POR state: Input floating.

Drain current: 16 mA

Alternate functions:

■A/D converter input

■LED1

■IR_TX

40

GPIO: P14

PWM2 I

Default direction: Input.

After POR state: Input floating.

Alternate function: A/D converter input

GPIO: P38 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■A/D converter input

■MOSI (master and slave) for SPI_2

■IR_TX

41 GPIO: P15 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■A/D converter input

■IR_RX

■60 Hz_main

Table 3. Pin Descriptions (Cont.)

Pin Name I/O Type Description

Document Number: 002-14888 Rev. *C Page 9 of 24

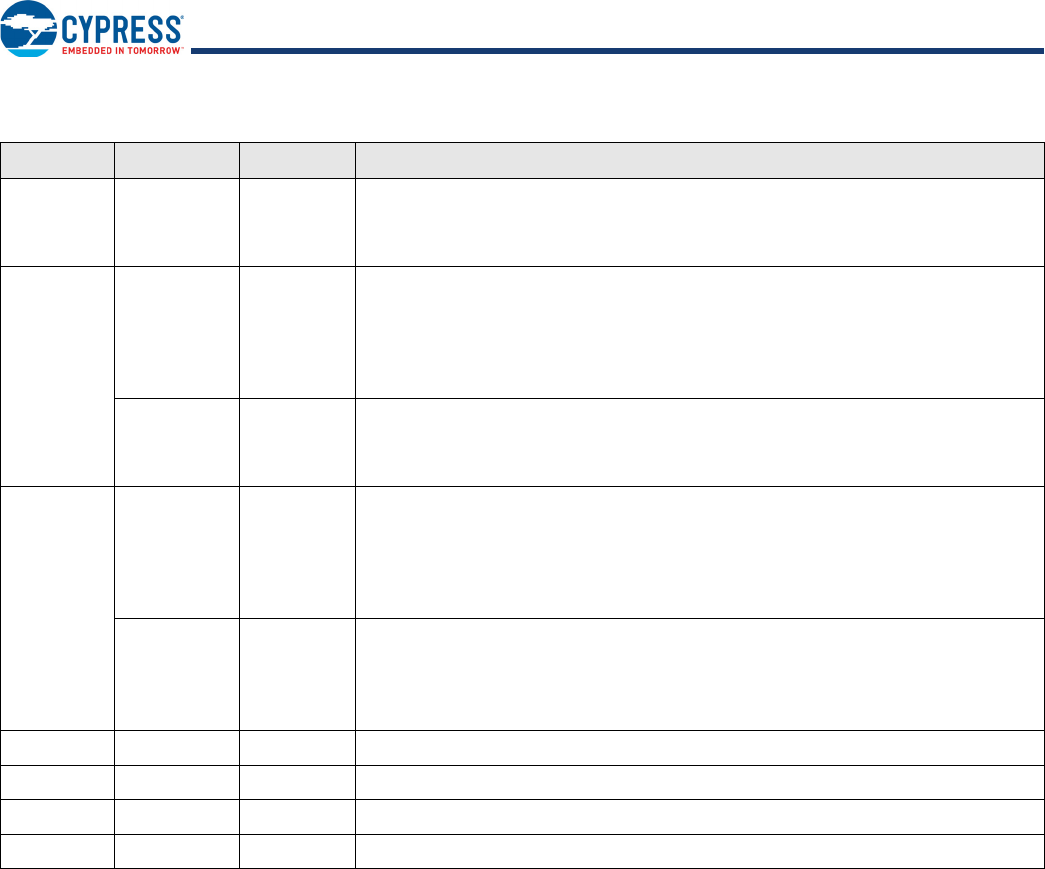

CYW20737S

42 GPIO: P26

PWM0 I

Default direction: Input.

After POR state: Input floating.

Drain current: 16 mA

Alternate function: SPI_CS (slave only) for SPI_2

43

GPIO: P12 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■A/D converter input

■XTALO32K

XTALO32K O

Low-power oscillator (LPO) output.

Alternate functions:

P12

P26

44

GPIO: P11 I

Default direction: Input.

After POR state: Input floating.

Alternate functions:

■A/D converter input

■XTALI32K

XTALI32K I

Low-power oscillator (LPO) input.

Alternate functions:

■P11

■P27

45 GND GND GND

46 GND GND GND

47 GND GND GND

48 GND GND GND

Table 3. Pin Descriptions (Cont.)

Pin Name I/O Type Description

Document Number: 002-14888 Rev. *C Page 10 of 24

CYW20737S

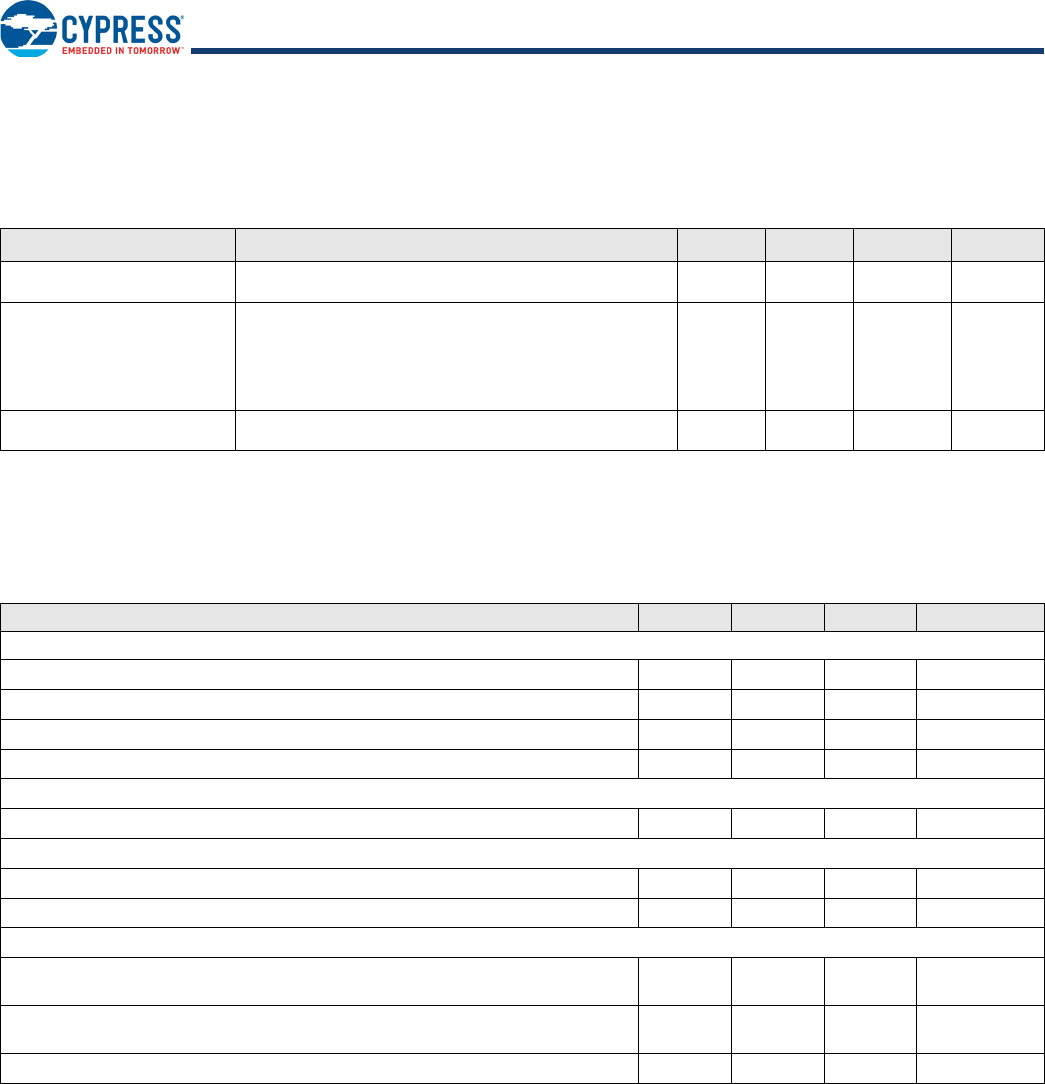

3. Electrical Specifications

Absolute maximum ratings are defined in Table 4.

Power for the CYW20737S module is provided by the host through the power pins.

Based on the current measurements in Table 6 on page 10, CYW20737S peak power values are:

■RX: 101.6 mW

■TX: 101.6 mW

■Sleep mode: 217.8 µW

■Deep Sleep mode: 9.1 µW

Table 4. Absolute Maximum Ratings

Parameter Min. Max. Unit

Supply power NA 3.63 V

Storage temperature –40 125 °C

Voltage ripple 0 ±2 %

Power supply (VBAT absolute maximum rating) 1.62 3.63 V

Table 5. Voltage

Symbol Parameter Min. Typ. Max. Unit

VBAT Battery voltage 1.62 – 3.63 V

Table 6. Current Consumption

Operating Mode Condition Nominal Maximum Unit

Receive Receiver and baseband are both operating, 100% 24.0 28.0 mA

Transmit Transmitter and baseband are both operating, 100% 24.0 28.0 mA

Sleep Wake in < 5 ms 55.0 60.0 µA

Deep Sleep Wake on interrupt 2.0 2.5 µA

Note: All measurements taken at 25°C

Document Number: 002-14888 Rev. *C Page 11 of 24

CYW20737S

4. RF Specifications

CYW20737S receiver specifications are defined in Ta b le 7.

RF transmitter specifications are defined in Table 8.

Table 7. Receiver Specifications

Parameter Mode and Conditions Min. Typ. Max. Unit

Frequency range – 2402 – 2480 MHz

RX sensitivity (standard) Packets: 200

Payload: PRBS 9

Length: 37 Bytes

Dirty Transmitter: off.

PER: 30.8%

– –94 – dBm

Maximum input – –10 – – dBm

Note: All measurements taken at 3.0V (default voltage)

Table 8. Transmitter Specifications

Parameter Min. Typ. Max. Unit

Transmitter

Frequency rangea

a. This parameter is taken from the Bluetooth 4.0 specification.

2402 – 2480 MHz

Output power adjustment range –20 – 4 dBm

Output power – 2 – dBm

Output power variation – 2.5 – dB

LO Performance

Initial carrier frequency tolerance – – ±150 kHz

Frequency Drift

Frequency drift – – ±50 kHz

Drift rate – – 20 kHz/50 µs

Frequency Deviation

Average deviation in payload

(sequence: 00001111)

225 – 275 kHz

Average deviation in payload

(sequence: 10101010)

185 – – kHz

Channel spacing – 2 – MHz

Document Number: 002-14888 Rev. *C Page 12 of 24

CYW20737S

5. ADC Specifications

CYW20737S ADC specifications are defined in Ta ble 9.

Table 9. ADC Specifications

Parameter Symbol Conditions Min. Typ. Max. Unit

Number of input channels – – – 9 – -

Channel switching rate fch –––133.33Kch/s

Input signal range Vinp –0–3.63V

Reference settling time – Charging refsel 7.5 – – µs

Input resistance Rinp Effective, single-ended – 500 – k

Input capacitance Cinp –––5pF

Conversion rate Fc– 5.859 – 187 kHz

Conversion time Tc– 5.35 – 170.7 µs

Resolution R – 16 Bits

Absolute voltage measurement error – Using on–chip ADC

firmware driver

–±2–%

Current I Iavdd1p2 + Iavdd3p3 ––1mA

Power P – – 1.5 – mW

Leakage Current Ileakage T = 25°C – – 100 nA

Power-up time Tpowerup –––200µs

Integral nonlinearity INL In the guaranteed

performance range

–1 – 1 LSBa

a. LSBs are expressed at the 10-bit level.

Differential nonlinearity DNL In the guaranteed

performance range

–1 – 1 LSBa

Document Number: 002-14888 Rev. *C Page 13 of 24

CYW20737S

6. Timing and AC Characteristics

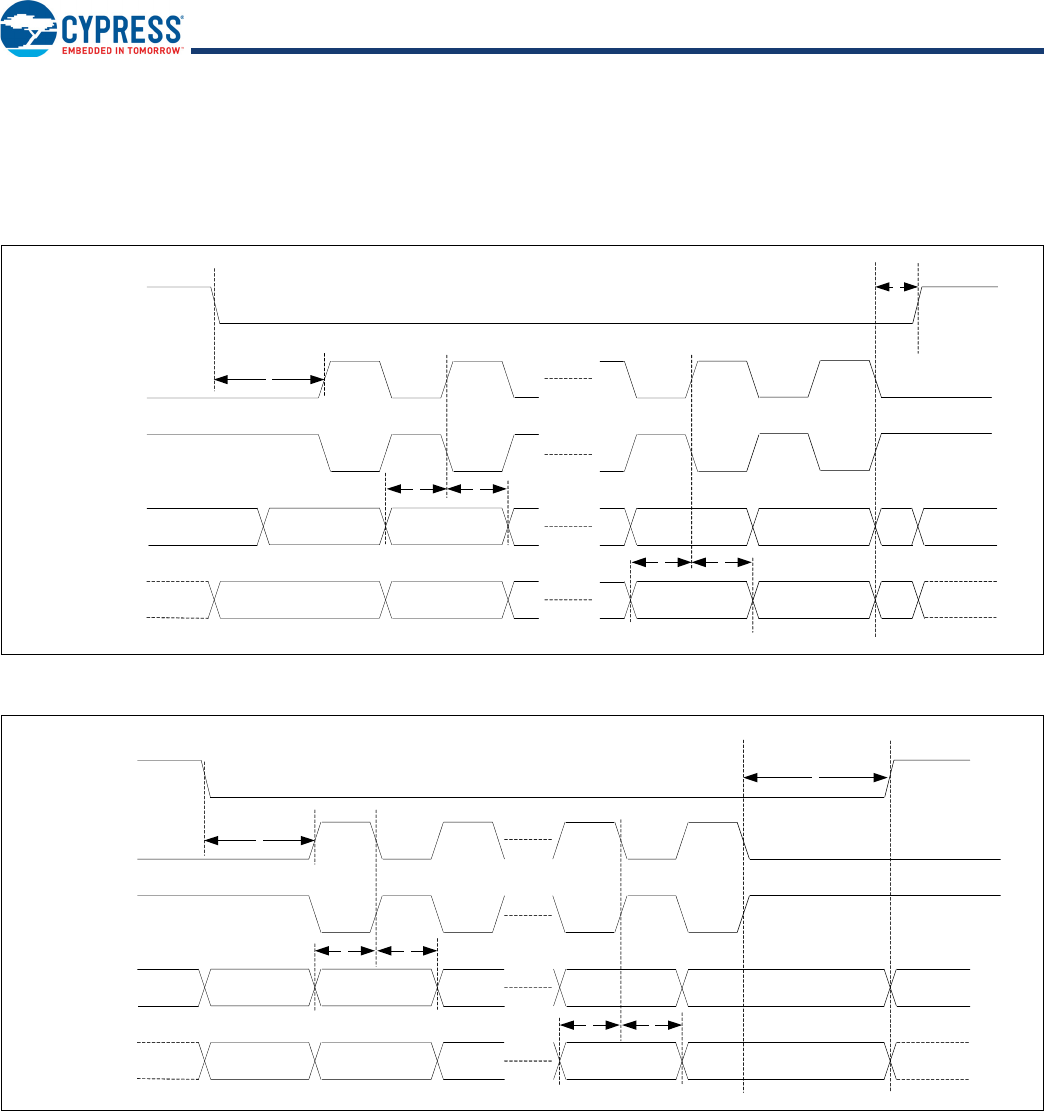

6.1 SPI Timing

SPI interface timing is illustrated in Figure 4 and Figure 5 and defined in Table 10 on page 14.

Figure 4. SPI Timing—Modes 0 and 2

Figure 5. SPI Timing—Modes 1 and 3

3

SPI_CSN

SPI_CLK

(Mode0)

SPI_MOSI ‐FirstBit

SPI_MISO NotDriven FirstBit

SecondBit

SecondBit

Lastbit

Lastbit

1

2

6

SPI_CLK

(Mode2)

NotDriven

‐

54

3

SPI_CSN

SPI_CLK

(Mode1)

SPI_MOSI ‐Invalidbit

SPI_MISO NotDriven Invalidbit

Firstbit

Firstbit

Lastbit

Lastbit

1

2

6

‐

NotDriven

SPI_CLK

(Mode3)

54

Document Number: 002-14888 Rev. *C Page 14 of 24

CYW20737S

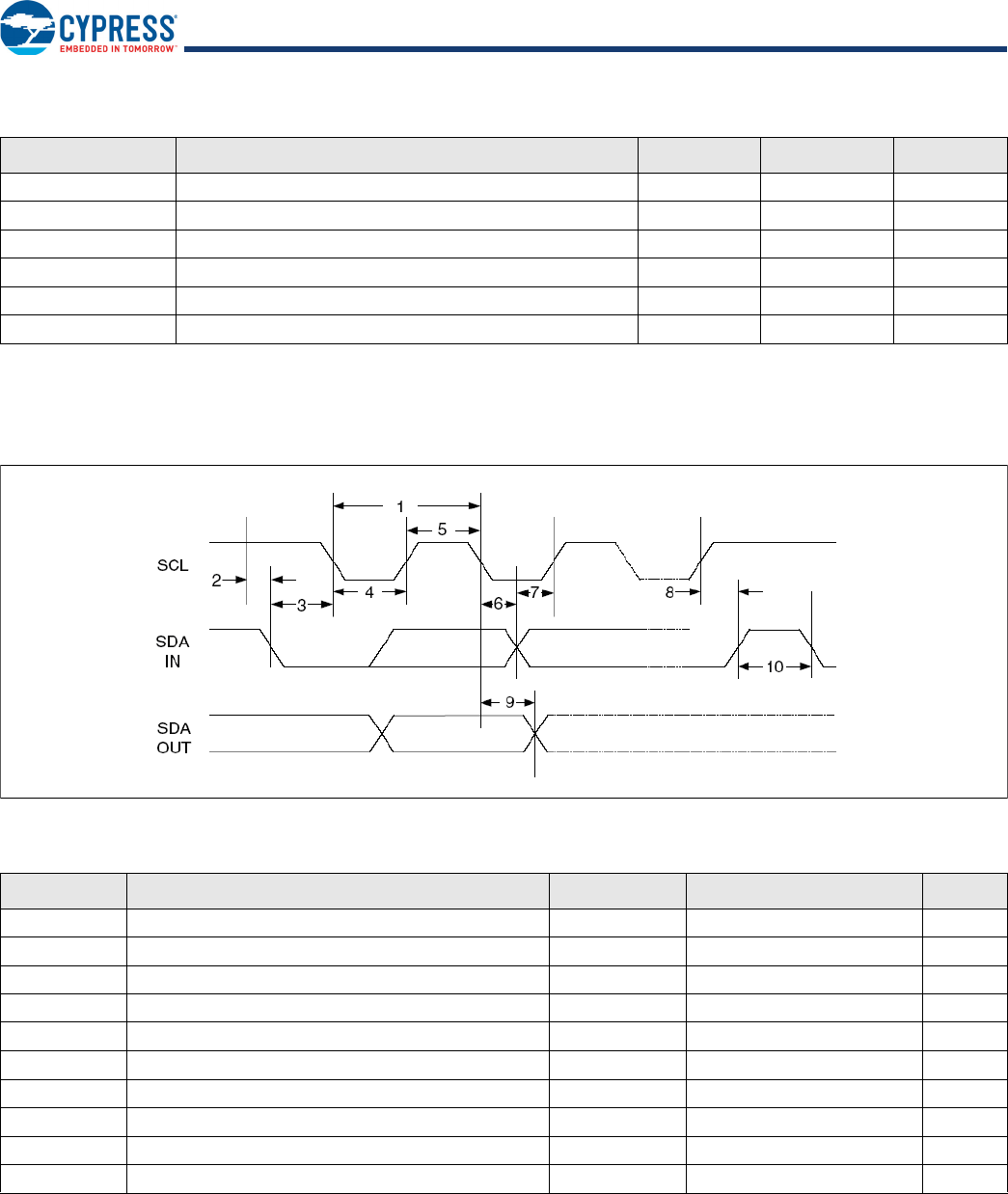

6.2 BSC Interface Timing

BSC interface timing is illustrated in Figure 6 and is defined in Tabl e 11 .

Figure 6. BSC Interface Timing

Table 10. SPI Interface Timing Specifications

Reference Characteristics Min. Typ. Max.

1 Time from CSN asserted to first clock edge 1 SCK 100

2 Master setup time – 1/2SCK –

3 Master hold time 1/2SCK - –

4 Slave setup time – 1/2 SCK –

5 Slave hold time 1/2 SCK – –

6 Time from last clock edge to CSN deasserted SCK 10 SCK 100

Table 11. BSC Interface Timing Specifications

Reference Characteristics Min. Max. Unit

1 Clock frequency – 100, 400, 800, 1000 kHz

2 START condition setup time 650 – ns

3 START condition hold time 280 – ns

4 Clock low time 650 – ns

5 Clock high time 280 – ns

6 Data input hold time 0 – ns

7 Data input setup time 100 – ns

8 STOP condition setup time 280 – ns

9 Output valid from clock – 400 ns

10 Bus free time 650 – ns

Document Number: 002-14888 Rev. *C Page 15 of 24

CYW20737S

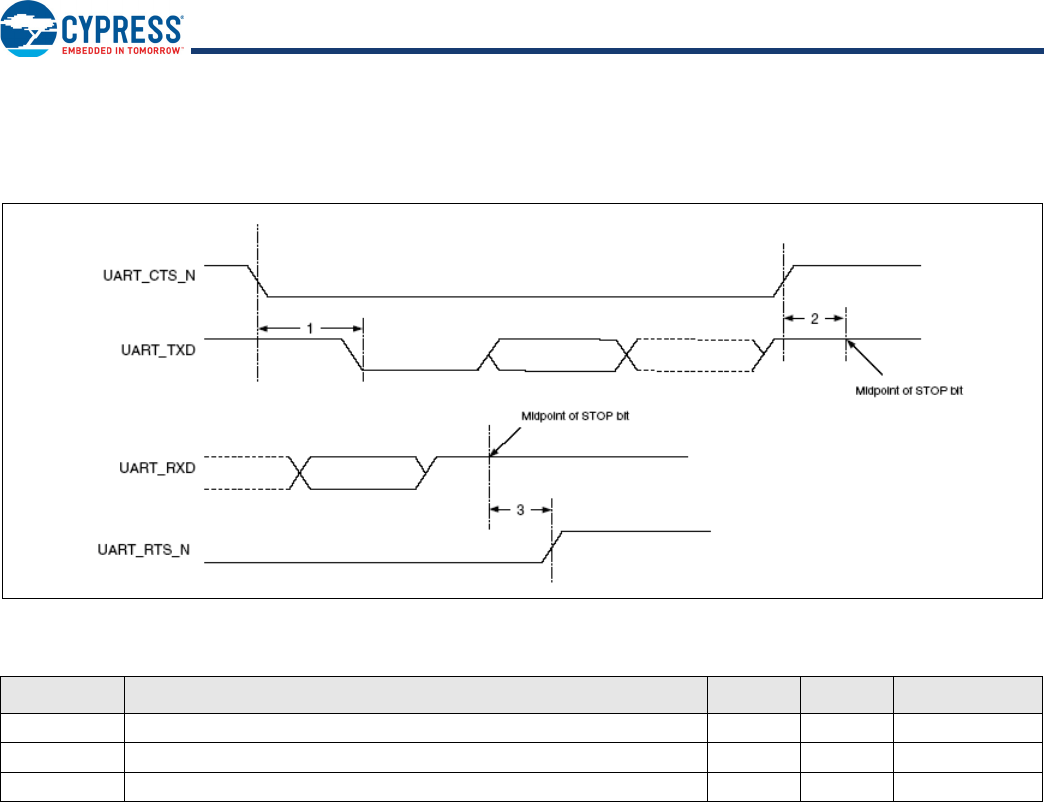

6.3 UART Timing

UART timing is illustrated in Figure 7 and defined in Table 12.

Figure 7. UART Timing

Table 12. UART Timing Specifications

Reference Characteristics Min. Max. Unit

1 Delay time, UART_CTS_N low to UART_TXD valid – 24 Baudout cycles

2 Setup time, UART_CTS_N high before midpoint of stop bit – 10 ns

3 Delay time, midpoint of stop bit to UART_RTS_N high – 2 Baudout cycles

Document Number: 002-14888 Rev. *C Page 16 of 24

CYW20737S

7. PCB Design and Manufacturing Recommendations

7.1 Pad and Solder Mask Opening Dimensions

CYW20737S pad and solder mask opening dimensions are defined in Table 13.

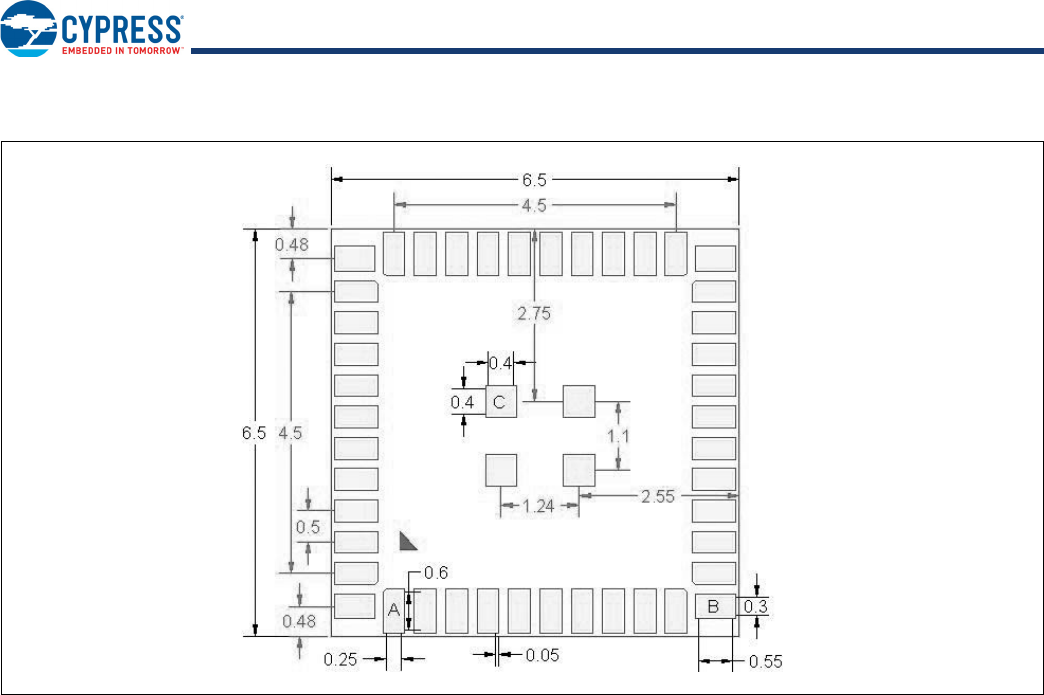

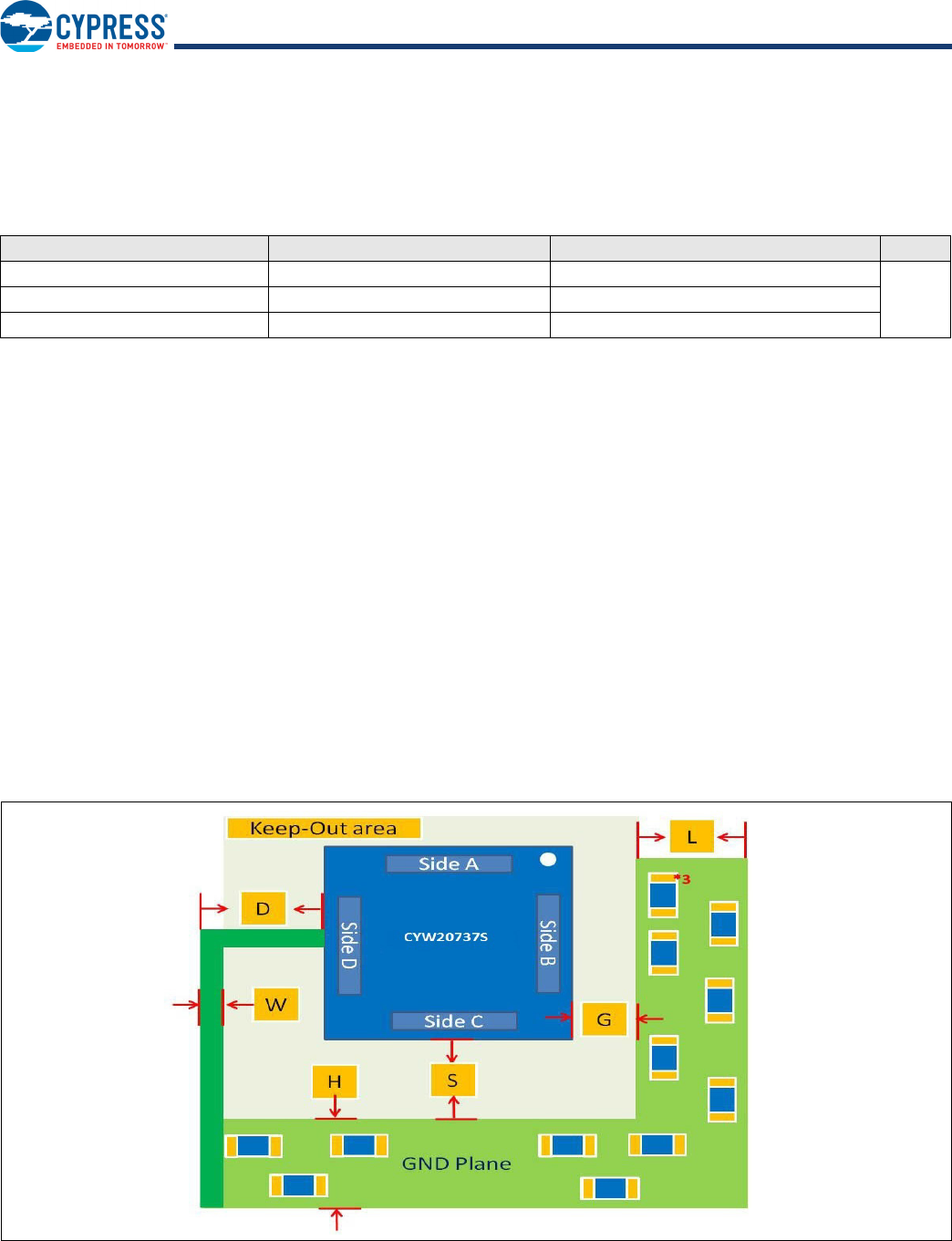

7.2 PCB Layout Recommendations

The following layout recommendations are referenced to Figure 8 on page 16.

■Connect to system ground from side D of the module (pins 13–22).

■The L-shaped ground plane is required for the embedded BLE antenna. Keep the GND continuous. Do not cut off the GND shape

to accommodate trace routes.

■An L-shaped ground plane is required. If the L-shaped GND plane is located on the top layer of the PCB, do not place components

on the ground plane. If this cannot be avoided, move the L-shaped ground plane to another layer.

■Antenna efficiency of 31–41% can be achieved based on the layout in Figure 8 on page 16 and the dimensions listed below.

Following these layout recommendations is expected to yield 50+ meters of usable range; deviating from these recommendations

may reduce the range of the antenna.

❐D: 4.5 mm (typical)

❐G, H, S: 3 mm (typical)

❐L: 3 mm (minimum)

❐W: 0.4 mm (typical)

■Route signal traces out of the module from side C (between pins 27 and 30) or side D (between pins 16 and 19) of the module.

Traces can be overlapped to avoid routing through the keep-out area.

■Do not route traces from side A or side B.

Figure 8. PCB Layout Example

Table 13. Pad and Solder Mask Dimensions

Pad Type Pad Dimensions Solder Mask Opening Dimensions Unit

Type A 0.6 × 0.25 0.7 × 0.35

mmType B 0.55 × 0.3 0.65 × 0.4

Type C 0.4 × 0.4 0.5 × 0.5

Document Number: 002-14888 Rev. *C Page 17 of 24

CYW20737S

7.3 PCB Stencil

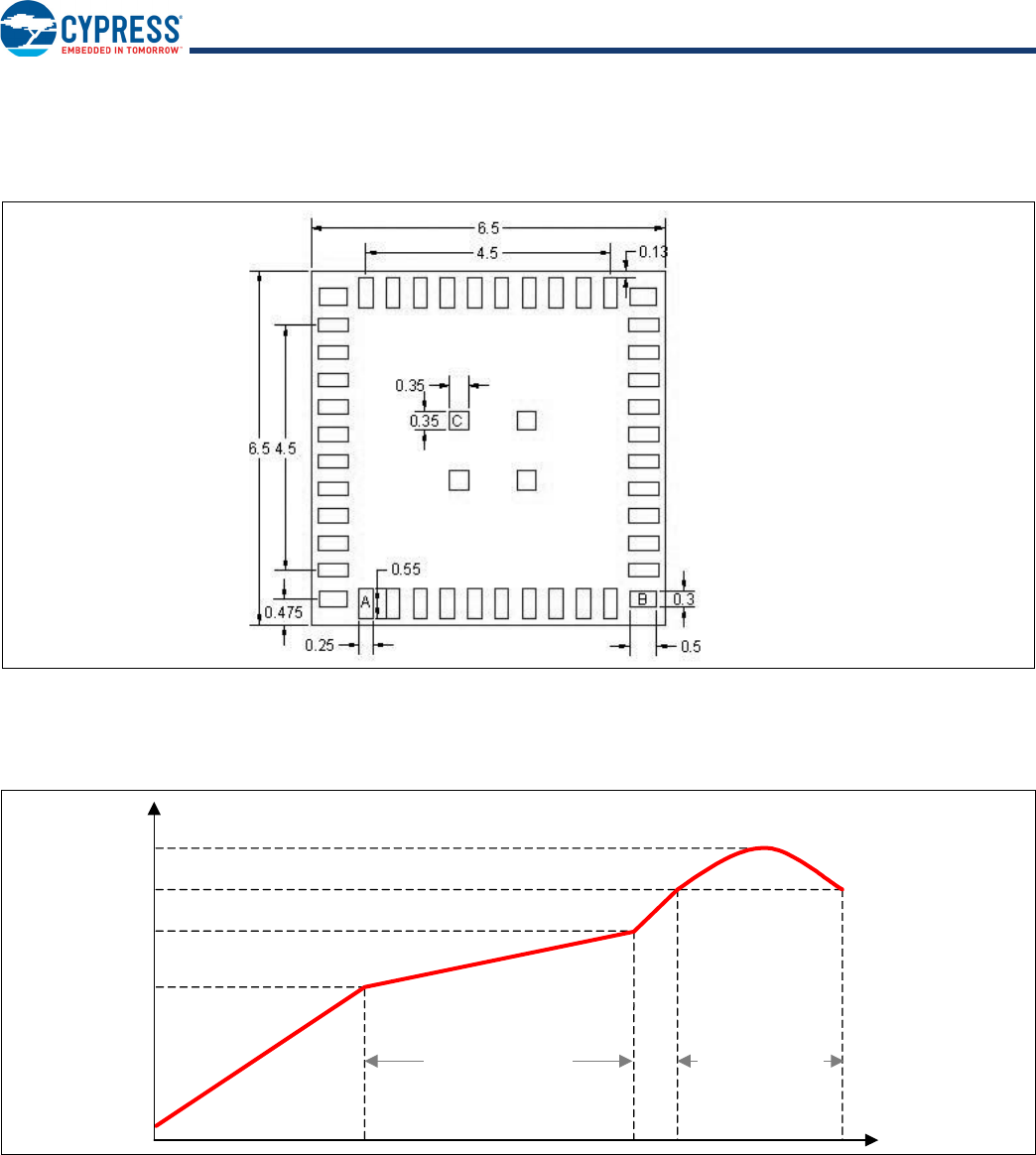

The recommended PCB stencil is shown in Figure 9 (all measurements in mm). Use an unsolder mask to set the module footprint.

Figure 9. CYW20737S Stencil (Bottom View)

7.4 Solder Reflow

The recommended solder reflow profile for the CYW20737S is defined in Figure 10.

Figure 10. Solder Reflow Profile

245°C

217°C

200°C

150°C

Ti

Temperature

Pre‐Heating:90~120sec. Soldering:60~90sec.

Document Number: 002-14888 Rev. *C Page 18 of 24

CYW20737S

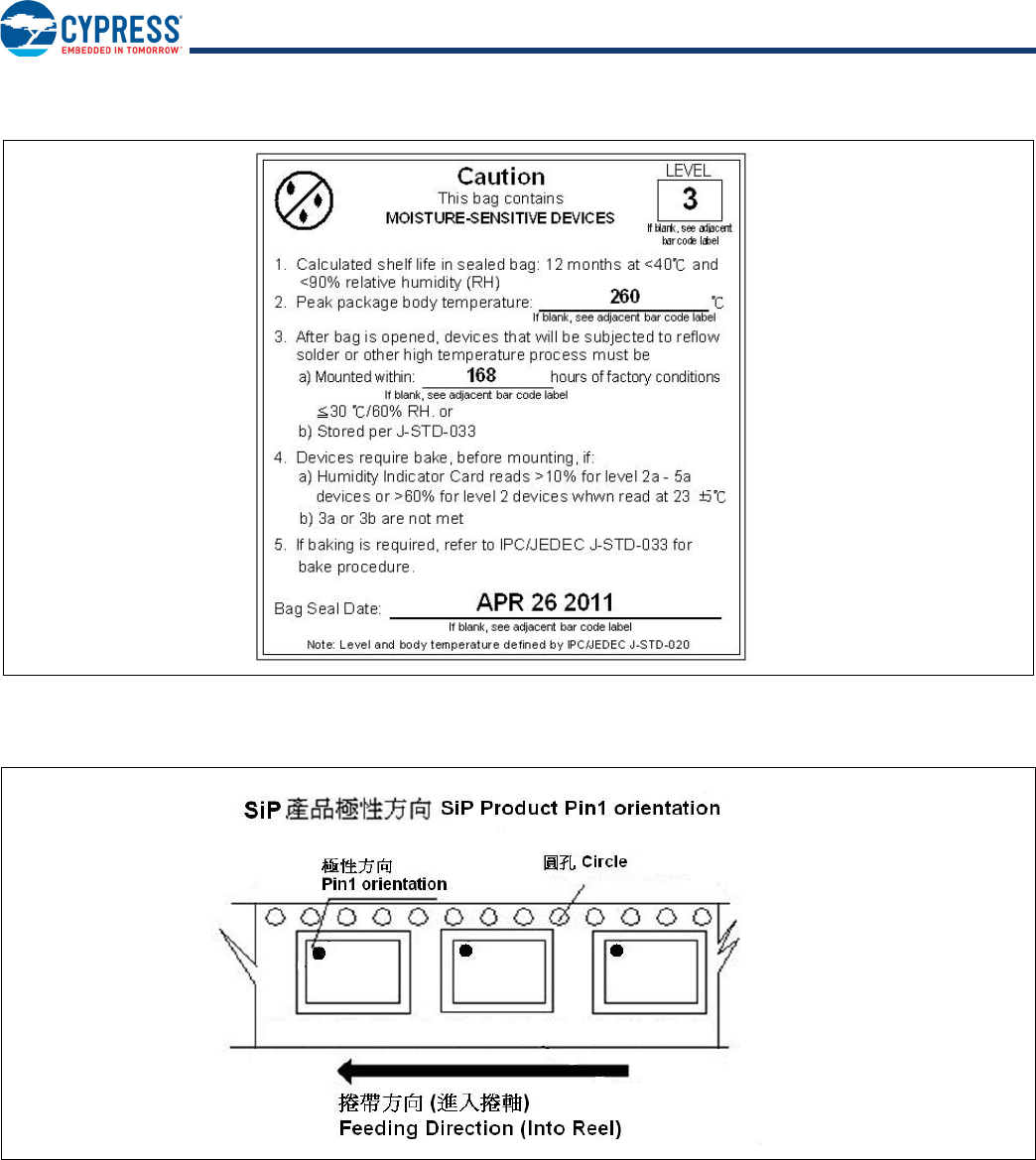

8. Packaging and Storage Information

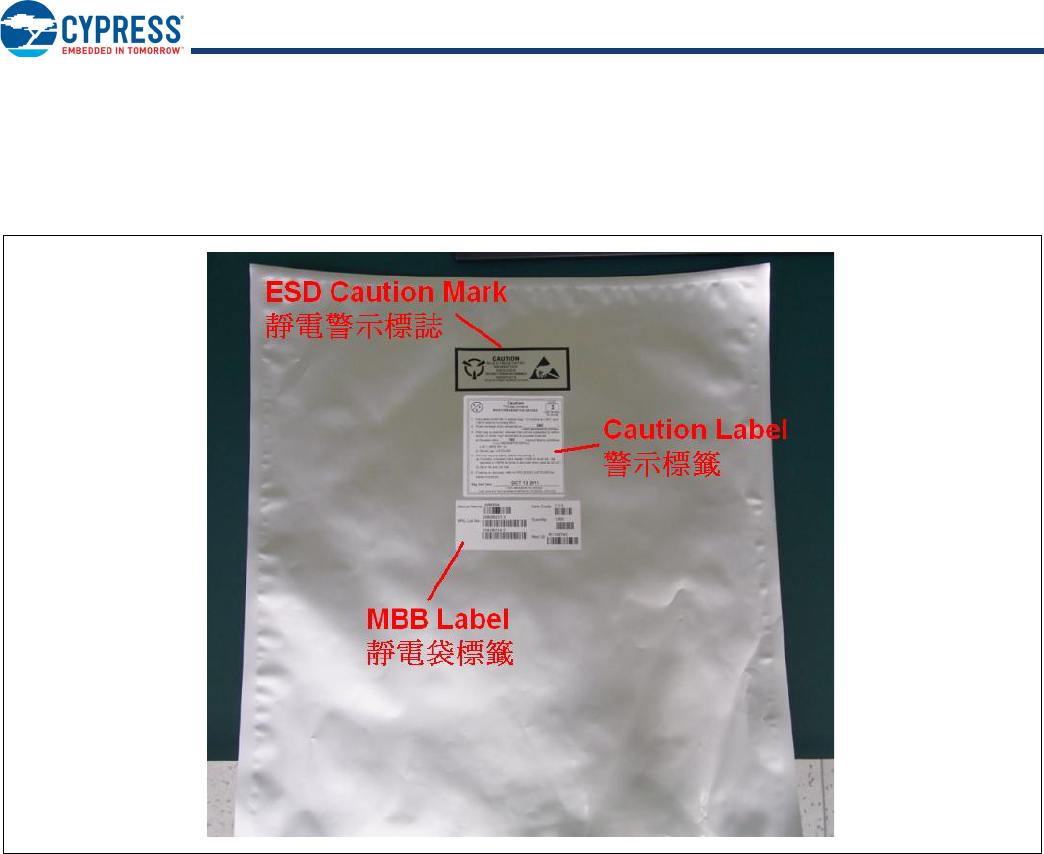

The CYW20737S is available in a tape and reel package and is shipped in an ESD-protected moisture-resistant (MSL-3) bag as shown

in Figure 11. The storage temperature range is –40°C to +125°C.

Figure 11. CYW20737S ESD/Moisture Packaging

The moisture sensitivity label on the CYW20737S shipping bag is shown in Figure 12 on page 19.

PRELIMINARY

'RFXPHQW1XPEHU5HY$ 3DJHRI

5HJXODWRU\,QIRUPDWLRQ

)&&

)&&127,&(

WKH)&&5XOHV7KHGHYLFHPHHWVWKHUHTXLUHPHQWVIRUPRGXODUWUDQVPLWWHU

DSSURYDODVGHWDLOHGLQ)&&SXEOLF1RWLFH'$WUDQVPLWWHU2SHUDWLRQLVVXEMHFWWRWKHIROORZLQJWZRFRQGLWLRQV7KLVGHYLFH

PD\QRWFDXVHKDUPIXOLQWHUIHUHQFHDQG7KLVGHYLFHPXVWDFFHSWDQ\LQWHUIHUHQFHUHFHLYHGLQFOXGLQJLQWHUIHUHQFHWKDWPD\FDXVH

XQGHVLUHGRSHUDWLRQ

&$87,21

7KH)&&UHTXLUHVWKHXVHUWREHQRWLILHGWKDWDQ\FKDQJHVRUPRGLILFDWLRQVPDGHWRWKLVGHYLFHWKDWDUHQRWH[SUHVVO\DSSURYHGE\

&\SUHVV6HPLFRQGXFWRUPD\YRLGWKHXVHUVDXWKRULW\WRRSHUDWHWKHHTXLSPHQW

7KLVHTXLSPHQWKDVEHHQWHVWHGDQGIRXQGWRFRPSO\ZLWKWKHOLPLWVIRUD&ODVV%GLJLWDOGHYLFHSXUVXDQWWR3DUWRIWKH)&&5XOHV

7KHVHOLPLWVDUHGHVLJQHGWRSURYLGHUHDVRQDEOHSURWHFWLRQDJDLQVWKDUPIXOLQWHUIHUHQFHLQDUHVLGHQWLDOLQVWDOODWLRQ7KLVHTXLSPHQW

JHQHUDWHVXVHVDQGFDQUDGLDWHUDGLRIUHTXHQF\HQHUJ\DQGLIQRWLQVWDOOHGDQGXVHGLQDFFRUGDQFHZLWKWKHLQVWUXFWLRQVrPD\FDXVH

KDUPIXOLQWHUIHUHQFHWRUDGLRFRPPXQLFDWLRQV+RZHYHUWKHUHLVQRJXDUDQWHHWKDWLQWHUIHUHQFHZLOOQRWRFFXULQDSDUWLFXODULQVWDOODWLRQ

,IWKLVHTXLSPHQWGRHVFDXVHKDUPIXOLQWHUIHUHQFHWRUDGLRRUWHOHYLVLRQUHFHSWLRQZKLFKFDQEHGHWHUPLQHGE\WXUQLQJWKHHTXLSPHQW

RIIDQGRQWKHXVHULVHQFRXUDJHGWRWU\WRFRUUHFWWKHLQWHUIHUHQFHE\RQHRUPRUHRIWKHIROORZLQJPHDVXUHV

n5HRULHQWRUUHORFDWHWKHUHFHLYLQJDQWHQQD

n,QFUHDVHWKHVHSDUDWLRQEHWZHHQWKHHTXLSPHQWDQGUHFHLYHU

n&RQQHFWWKHHTXLSPHQWLQWRDQRXWOHWRQDFLUFXLWGLIIHUHQWIURPWKDWWRZKLFKWKHUHFHLYHULVFRQQHFWHG

n&RQVXOWWKHGHDOHURUDQH[SHULHQFHGUDGLR79WHFKQLFLDQIRUKHOS

/$%(/,1*5(48,5(0(176

7KH2ULJLQDO(TXLSPHQW0DQXIDFWXUHU2(0PXVWHQVXUHWKDW)&&ODEHOOLQJUHTXLUHPHQWVDUHPHW7KLVLQFOXGHVDFOHDUO\YLVLEOH

ODEHORQWKHRXWVLGHRIWKH2(0HQFORVXUHVSHFLI\LQJWKHDSSURSULDWH&\SUHVV6HPLFRQGXFWRU)&&LGHQWLILHUIRUWKLVSURGXFWDVZHOO

DVWKH)&&1RWLFHDERYH7KH)&&LGHQWLILHULV)&&,'

,QDQ\FDVHWKHHQGSURGXFWPXVWEHODEHOHGH[WHULRUZLWK&RQWDLQV)&&,'

$17(11$:$51,1*

7KLVGHYLFHLVWHVWHGZLWKDVWDQGDUG60$FRQQHFWRUDQGZLWKWKHDQWHQQDVOLVWHGEHORZ:KHQLQWHJUDWHGLQWKH2(0VSURGXFWWKHVH

IL[HGDQWHQQDVUHTXLUHLQVWDOODWLRQSUHYHQWLQJHQGXVHUVIURPUHSODFLQJWKHPZLWKQRQDSSURYHGDQWHQQDV$Q\DQWHQQDQRWLQWKH

IROORZLQJWDEOHPXVWEHWHVWHGWRFRPSO\ZLWK)&&6HFWLRQIRUXQLTXHDQWHQQDFRQQHFWRUVDQG6HFWLRQIRUHPLVVLRQV

5)(;32685(

7RFRPSO\ZLWK)&&5)([SRVXUHUHTXLUHPHQWVWKH2ULJLQDO(TXLSPHQW0DQXIDFWXUHU2(0PXVWHQVXUHWRLQVWDOOWKHDSSURYHG

DQWHQQDLQWKHSUHYLRXV

7KHSUHFHGLQJVWDWHPHQWPXVWEHLQFOXGHGDVD&$87,21VWDWHPHQWLQPDQXDOVIRUSURGXFWVRSHUDWLQJZLWKWKHDSSURYHGDQWHQQDV

LQ7DEOHRQSDJHWRDOHUWXVHUVRQ)&&5)([SRVXUHFRPSOLDQFH$Q\QRWLILFDWLRQWRWKHHQGXVHURILQVWDOODWLRQRUUHPRYDO

LQVWUXFWLRQVDERXWWKHLQWHJUDWHGUDGLRPRGXOHLVQRWDOORZHG

7KHUDGLDWHGRXWSXWSRZHURI DQWHQQD)&&,' LVIDUEHORZWKH)&&UDGLRIUHTXHQF\

H[SRVXUHOLPLWV1HYHUWKHOHVVXVH VXFKDPDQQHUWKDWPLQLPL]HVWKHSRWHQWLDOIRUKXPDQFRQWDFWGXULQJQRUPDO

RSHUDWLRQ

(QGXVHUVPD\ QRW EHSURYLGHG ZLWKWKH PRGXOH LQVWDOODWLRQLQVWUXFWLRQV 2(0LQWHJUDWRUVDQGHQG XVHUV PXVW EHSURYLGHGZLWK

WUDQVPLWWHURSHUDWLQJFRQGLWLRQVIRUVDWLVI\LQJ5)H[SRVXUHFRPSOLDQFH

The device complies with part 15 of

WAP-0737

WAP-0737

the device with the PCB WAP-0737

the device

PRELIMINARY &<%7

&HUWLILFDWLRQ

LVOLFHQVHGWRPHHWWKHUHJXODWRU\U HTXLUHPHQWVRI,QGXVWU\&DQDGD,&

/LFHQVH,&

0DQXIDFWXUHUVRIPRELOHIL[HGRUSRUWDEOHGHYLFHVLQFRUSRUDWLQJWKLVPRGXOHDUHDGYLVHGWRFODULI\DQ\UHJXODWRU\TXHVWLRQVDQGHQVXUH

FRPSOLDQFH IRU 6$5 DQGRU 5) H[SRVXUH OLPLWV 8VHUV FDQ REWDLQ &DQDGLDQ LQIRUPDWLRQ RQ 5) H[SRVXUH DQG FRPSOLDQFH IURP

ZZZLFJFFD

7KLVGHYLFHKDVEHHQGHVLJQHGWRRSHUDWHZLWKWKHDQWHQQDVOLVWHGLQ7DEOHRQSDJHKDYLQJDPD[LPXPJDLQRI QQDV

QRWLQFOXGHGLQWKLVOLVWRUKDYLQJDJDLQJUHDWHU G%LDUHVWULFWO\SURKLELWHGIRUXVHZLWKWKLVGHYLFH7KHUHTXLUHGDQWHQQD

LPSHGDQFHLVRKPV7KHDQWHQQDXVHGIRUWKLVWUDQVPLWWHUPXVWQRWEHFRORFDWHGRURSHUDWLQJLQFRQMXQFWLRQZLWKDQ\RWKHUDQWHQQD

RUWUDQVPLWWHU

,&127,&(

7KH GHYLFHLQFOXGLQJ WKH EXLOWLQ WUDFH DQWHQQD FRPSOLHV ZLWK &DQDGD 566*(1 5XOHV 7KHGHYLFH PHHWV WKH

UHTXLUHPHQWVIRUPRGXODUWUDQVPLWWHUDSSURYDODVGHWDLOHGLQ566*(12SHUDWLRQLVVXEMHFWWRWKHIROORZLQJWZRFRQGLWLRQV7KLV

GHYLFHPD\QRWFDXVHKDUPIXOLQWHUIHUHQFHDQG7KLVGHYLFHPXVWDFFHSWDQ\LQWHUIHUHQFHUHFHLYHGLQFOXGLQJLQWHUIHUHQFHWKDW

PD\FDXVHXQGHVLUHGRSHUDWLRQ

,&5$',$7,21(;32685(67$7(0(17)25&$1$'$

7KLVGHYLFHFRPSOLHVZLWK,QGXVWU\&DQDGDOLFHQFHH[HPSW566VWDQGDUGV2SHUDWLRQLVVXEMHFWWRWKHIROORZLQJWZRFRQGLWLRQV

WKLVGHYLFH PD\ QRW FDXVHLQWHUIHUHQFHDQG WKLV GHYLFH PXVWDFFHSWDQ\LQWHUIHUHQFHLQFOXGLQJ LQWHUIHUHQFH WKDW PD\FDXVH

XQGHVLUHGRSHUDWLRQRIWKHGHYLFH

/HSUpVHQWDSSDUHLOHVWFRQIRUPHDX[&15G,QGXVWULH&DQDGDDSSOLFDEOHVDX[DSSDUHLOVUDGLRH[HPSWVGHOLFHQFH/H[SORLWDWLRQHVW

DXWRULVpHDX[GHX[FRQGLWLRQVVXLYDQWHVODSSDUHLOQHGRLWSDVSURGXLUHGHEURXLOODJHHWOXWLOLVDWHXUGHODSSDUHLOGRLWDFFHSWHU

WRXWEURXLOODJHUDGLRpOHFWULTXHVXELPrPHVLOHEURXLOODJHHVWVXVFHSWLEOHGHQFRPSURPHWWUHOHIRQFWLRQQHPHQW

/$%(/,1*5(48,5(0(176

7KH2ULJLQDO(TXLSPHQW0DQXIDFWXUHU2(0PXVWHQVXUHWKDW,&ODEHOOLQJUHTXLUHPHQWVDUHPHW7KLVLQFOXGHVDFOHDUO\YLVLEOHODEHO

RQWKHRXWVLGHRIWKH2(0HQFORVXUHVSHFLI\LQJWKHDSSURSULDWH&\SUHVV6HPLFRQGXFWRU,&LGHQWLILHUIRUWKLVSURGXFWDVZHOODVWKH,&

1RWLFHDERYH7KH,&LGHQWLILHULV ,QDQ\FDVHWKHHQGSURGXFWPXVWEHODEHOHGLQL WVH[WHULRUZLWK&RQWDLQV,&

(XURSHDQ577('HFODUDWLRQRI&RQIRUPLW\

+HUHE\&\SUHVV6HPLFRQGXFWRUGHFODUHVWKDWWKH%OXHWRRWKPRGXOHFRPSOLHVZLWKWKHHVVHQWLDOUHTXLUHPHQWVDQG

RWKHUUHOHYDQWSURYLVLRQVRI'LUHFWLYH(&$VDUHVXOWRIWKHFRQIRUPLW\DVVHVVPHQWSURFHGXUHGHVFULEHGLQ$QQH[,,,RIWKH

'LUHFWLYH(&WKHHQGFXVWRPHUHTXLSPHQWVKRXOGEHODEHOHGDVIROORZV

$OOYHUVLRQVRIWKH UHIHUHQFHGHVLJQFDQEHXVHGLQWKHIROORZLQJFRXQWULHV$XVWULD%HOJLXP&\SUXV

&]HFK5HSXEOLF'HQPDUN(VWRQLD)LQODQG)UDQFH*HUPDQ\*UHHFH+XQJDU\,UHODQG,WDO\/DWYLD/LWKXDQLD/X[HPERXUJ0DOWD

3RODQG3RUWXJDO6ORYDNLD6ORYHQLD6SDLQ6ZHGHQ7KH1HWKHUODQGVWKH8QLWHG.LQJGRP6ZLW]HUODQGDQG1RUZD\

ISED

The device

7922A-0737

-1.5dBi, ante

than -1.5

(3) No SAR evaluation is required since maximum transmitter Pout is below IC threshold

(3) Aucune évaluation SAR n'est requise étant donné que la puissance maximale de l'émetteur est inférieure au seuil IC.

7922A-0737

7922A-0737

device in the specified

Document Number: 002-14888 Rev. *C Page 23 of 24

CYW20737S

Document History

Document Title: CYW20737S Bluetooth Low Energy System-in-Package (SiP) Module

Document Number: 002-14888

Revision ECN Orig. of

Change

Submission

Date Description of Change

** – – 09/26/2014 20737S-DS100-R:

Initial release

*A – UTSV 11/06/2015

20737S-DS101-R:

Updated

•Table 5 on page 14

*B 5444054 UTSV 09/23/2016 Updated to Cypress Template

*C 5688156 AESATMP7 04/21/2017 Updated Cypress Logo and Copyright.

Document Number: 002-14888 Rev. *C Revised April 21, 2017 Page 24 of 24

CYW20737S

© Cypress Semiconductor Corporation, 2014-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC (“Cypress”). This document,

including any software or firmware included or referenced in this document (“Software”), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries

worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other

intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress

hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to

modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users

(either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as

provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation

of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE

OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent

permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any

product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is

the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products

are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or

systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the

device or system could cause personal injury, death, or property damage (“Unintended Uses”). A critical component is any component of a device or system whose failure to perform can be reasonably

expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim,

damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other

liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in

the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Sales, Solutions, and Legal Information

Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer’s representatives, and distributors. To find the office

closest to you, visit us at Cypress Locations.

Products

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Internet of Things cypress.com/iot

Memory cypress.com/memory

Microcontrollers cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

PSoC®Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

Cypress Developer Community

Forums | WICED IoT Forums | Projects | Video | Blogs |

Training | Components

Technical Support

cypress.com/support

24