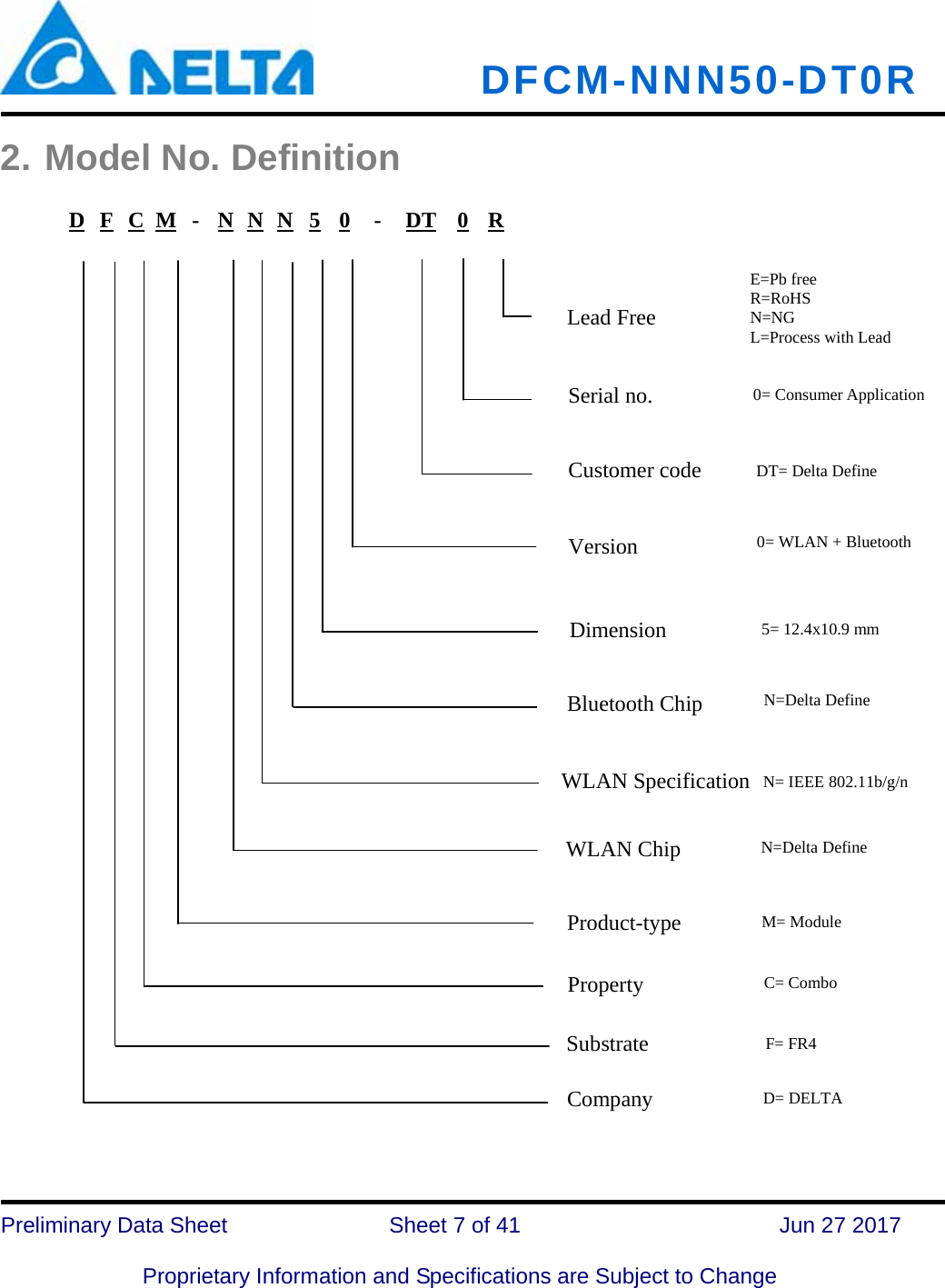

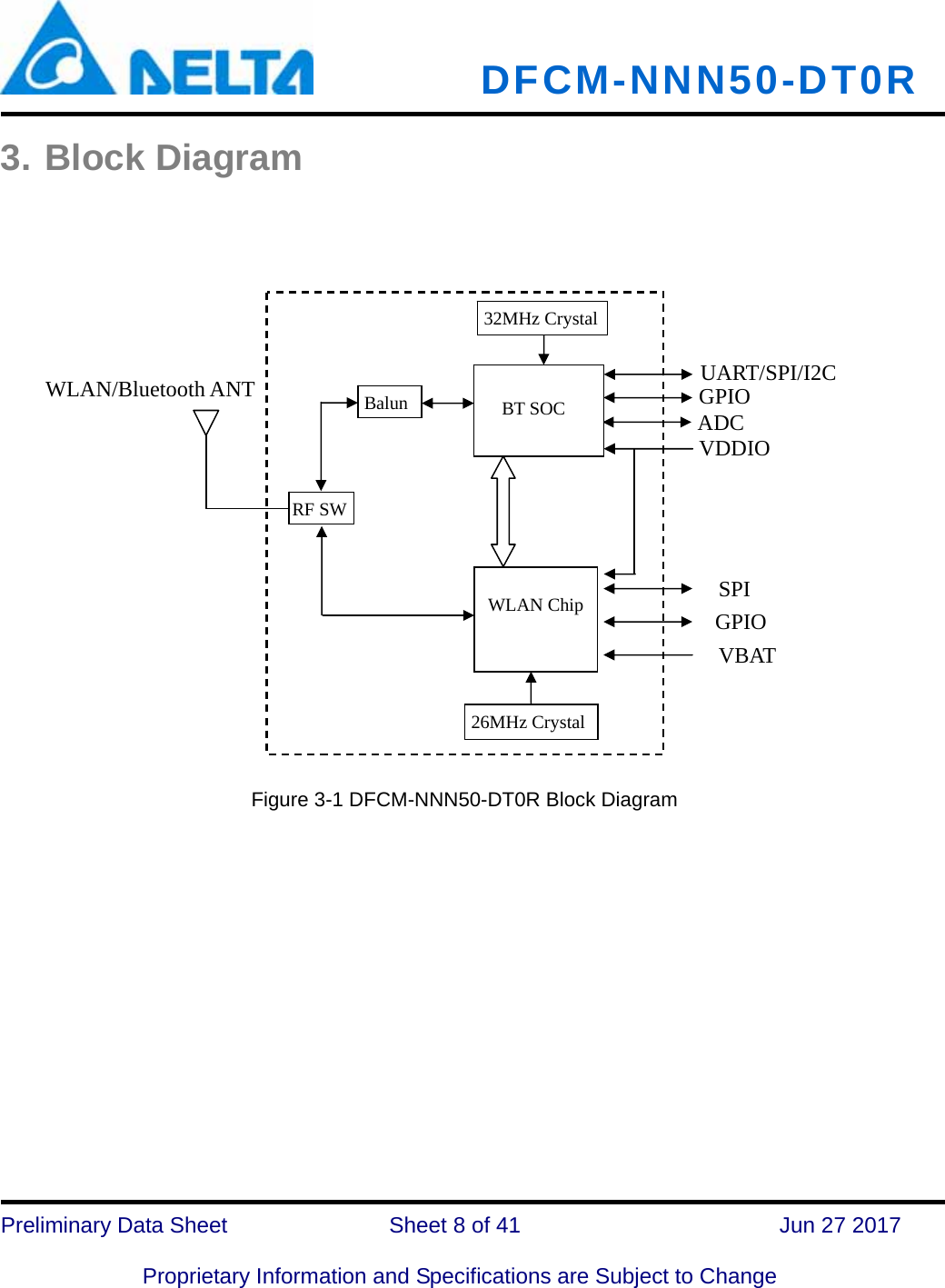

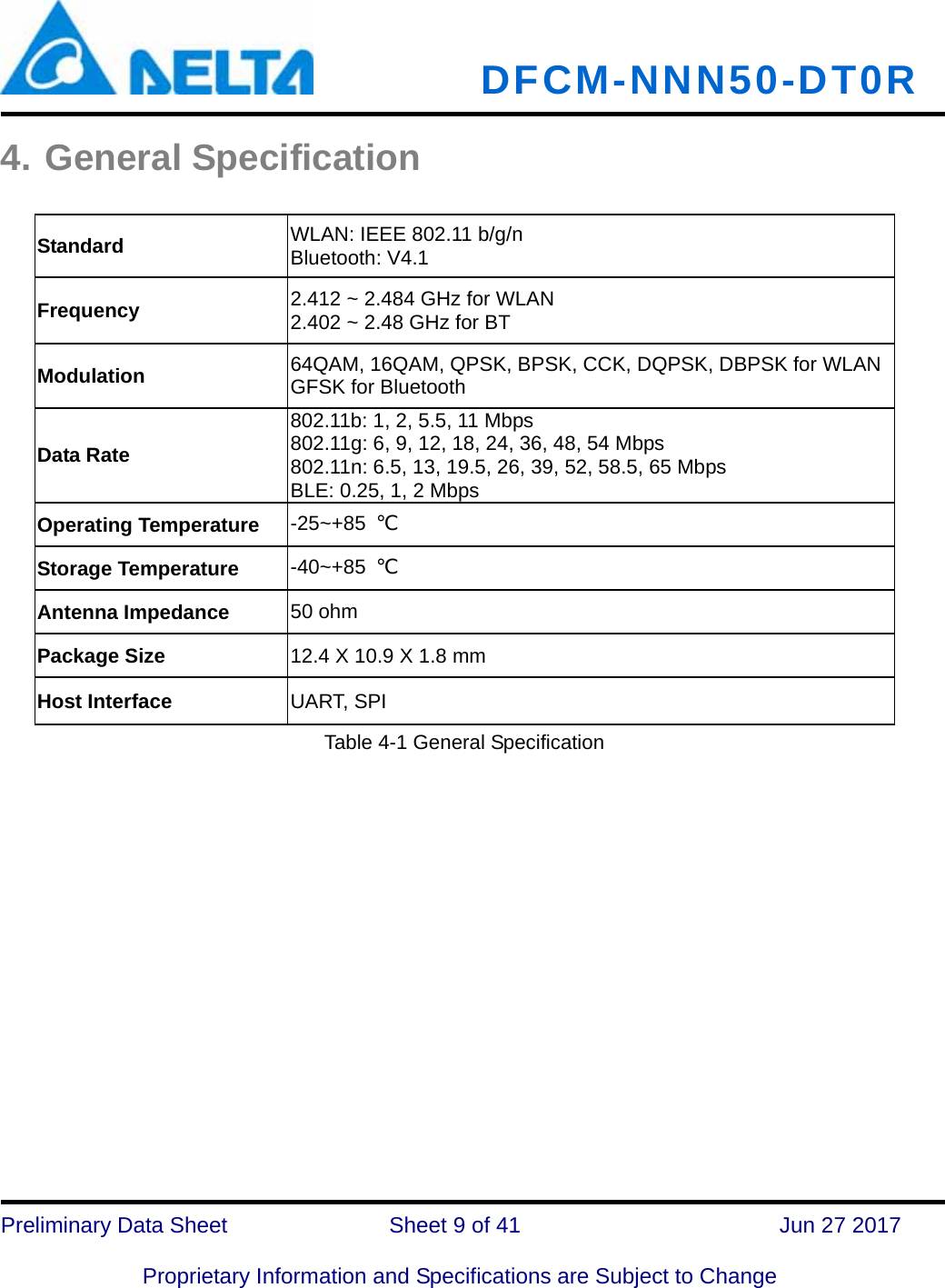

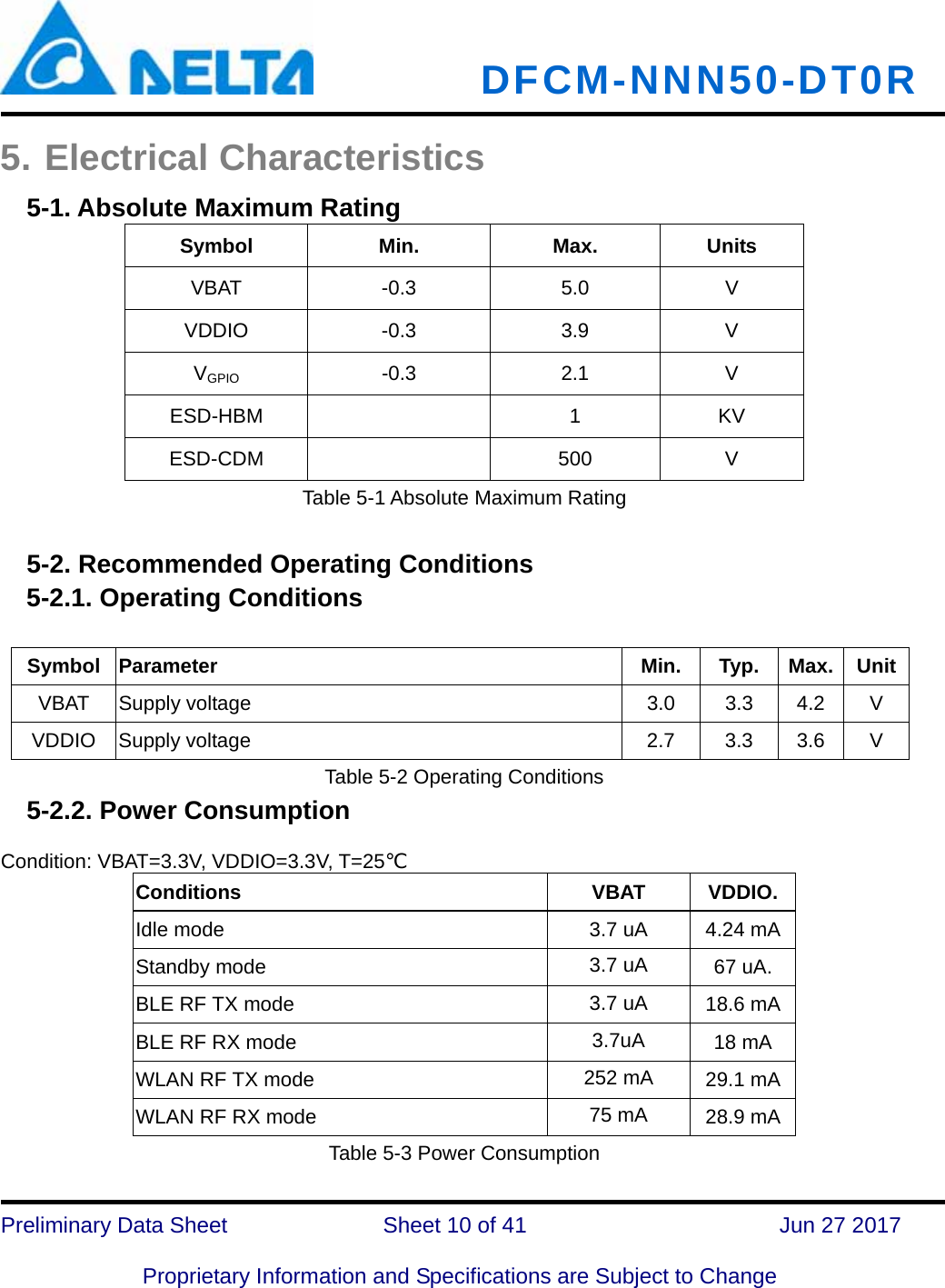

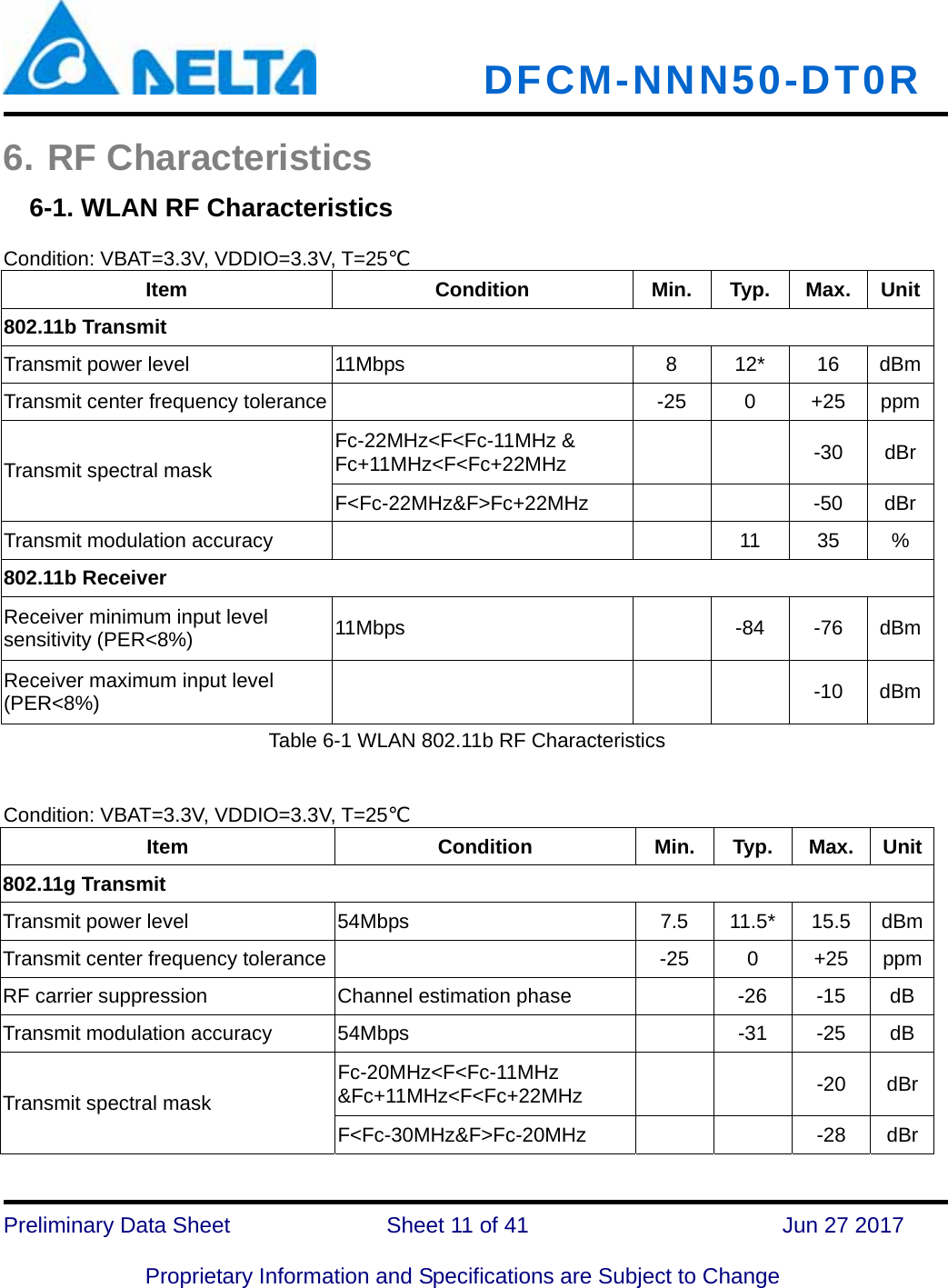

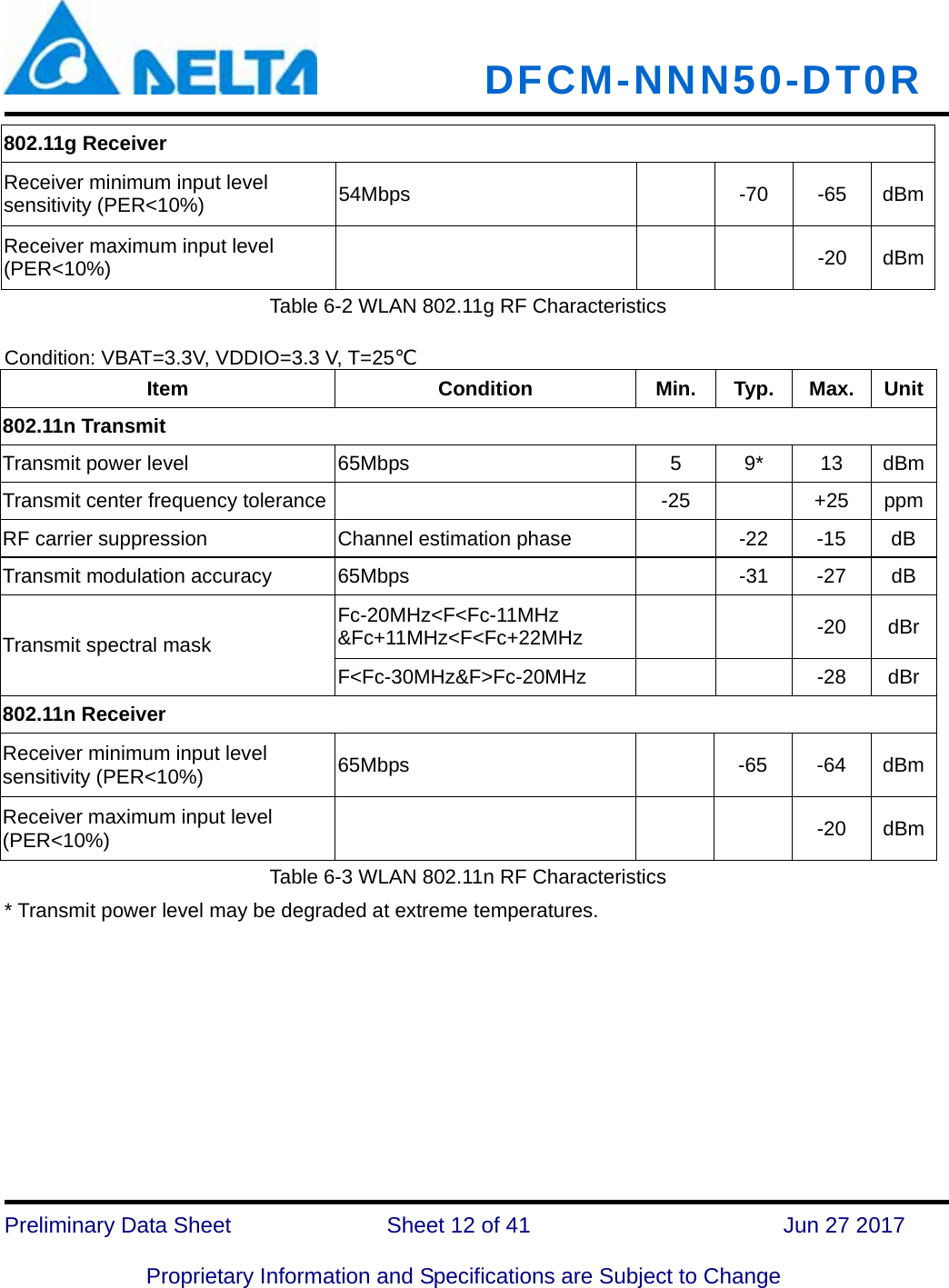

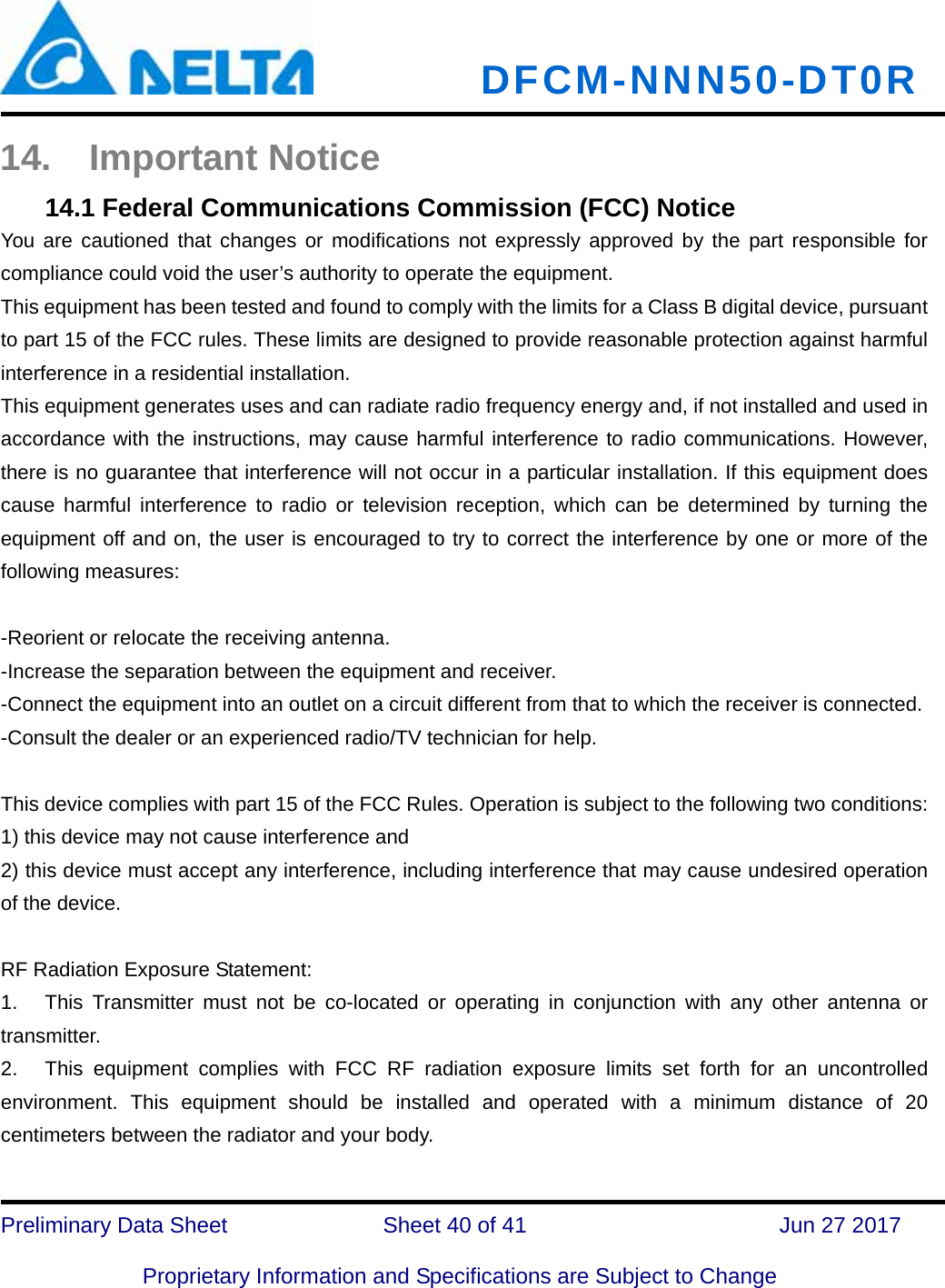

Delta Electronics orporated DFCM-NNN50 IEEE 802.11b/g/n Wireless LAN Plus Bluetooth Low Energy System On Chip Combo Module. User Manual

Delta Electronics Incorporated IEEE 802.11b/g/n Wireless LAN Plus Bluetooth Low Energy System On Chip Combo Module.

Users Manual