227 5977 1_1131_Computing_System_FEMM 1 1131 Computing System FEMM

227-5977-1_1131_Computing_System_FEMM 227-5977-1_1131_Computing_System_FEMM

User Manual: 227-5977-1_1131_Computing_System_FEMM

Open the PDF directly: View PDF ![]() .

.

Page Count: 66

I

~ ~

~@

Computing

System

Field Engineering

Maintenance Manual

N

N

'-I

I

Ul

\0

'-I

'-I

I

....

Field Engineering

Maintenance Manual

Issued

to:

____________

_

Branch Office:

___________

_

Department:

___________

_

Address:

____________

_

If

this

manual

is

misplaced, it

should

be

returned

to

the

above

address.

TI

TI

~@

Computing

System

PREFACE

This

manual

contains

all

maintenance

procedures

required

to

service

the

IBM 1130

Data

Processing

System.

This

manual

assumes

that

the

CE

has

limited

experience

and/or

training

on

the

system

and

is

fa-

miliar

with

the

material

contained

in

the

Field

Engi-

neering

Theory

of

Operation

(Instruction

Manual)

manuals

listed

in

the

Bibliography

(Appendix

A).

The

users

of

this

manual

are

cautioned

that

specifications

are

subject

to

change

at

any

time

and

without

prior

notice

by IBM.

Wiring

diagrams

(logics)

at

the

engineering

change

level

of

that

spec-

ific

machine

are

included

in

each

machine

shipment.

This

manual

(Form

227-5977-1)

is a

major

revision

of

Form

227-5977-0.

The

latter

is

made

obsolete

by

this

revision.

Copies

of

this

and

other

IBM

publications

can

be

obtained

through

IBM

Branch

Ofiices.

A

form

has

been

provided

at

the

back

of

this

publication

for

readers'

comments.

If

the

form

has

been

detached,

comments

may

be

directed

to

:

IBM,

Product

Publications

Department,

San

Jose,

Calif.

95114

@)

International

Business

Machines

Corporation,1966.

ii

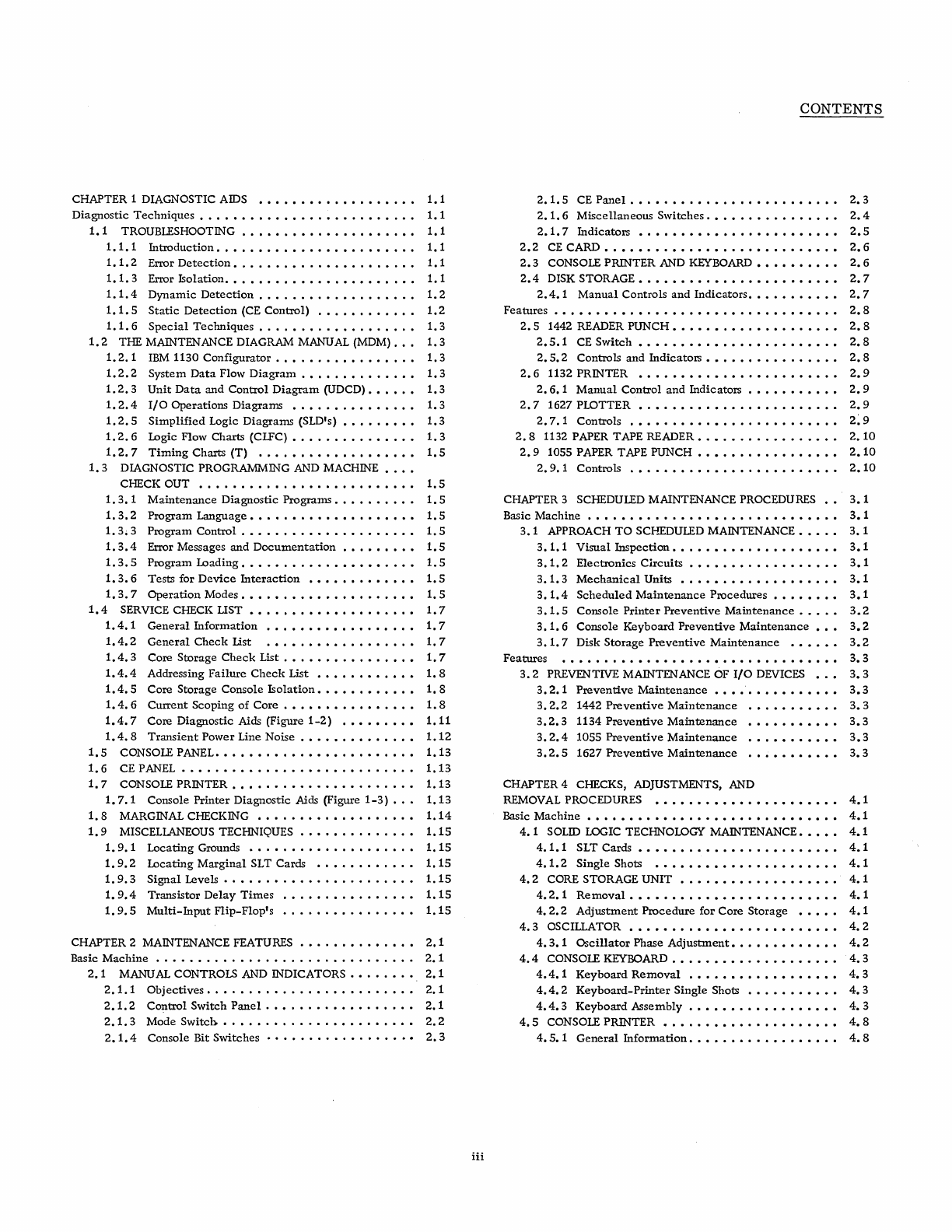

CHAPTER 1 DIAGNOSTIC AIDS

•••••••••••••••••••

1.

1

Diagnostic

Techniques.

• • • • • • • • • • • • • • • • • • • • • • .

••

1.1

1.

1

TROUBLESHOOTING.....................

1.

1

1.

1.

1

Introduction........................

1. 1

1.

1.2

Error

Detection.

. • . • • • • • . • • • • • • • • • .

.•

1.

1

1.1.3

Error

Isolation.

• • • • • • • . • • • • • • • • • • • •

••

1.1

1.1.4

Dynamic

Detection

•.•.•••••••••••••••

1.2

1.

1.5

Static

Detection

(CE

Control)

.•.••••••.••

1.2

1.

1.

6

Special

Techniques

• . • . • • • . . • • • • • . . •

.•

1. 3

1.2

THE MAINTENANCE DIAGRAM MANUAL (MDM) .

•.

1.

3

1.

2. 1

IBM

1130

Configurator

• • • . • • . • • • • • • • .

.•

1.

3

1.

2.2

System

Data

Flow

Diagram

. • • • • • • • • • . •

••

1.

3

1.

2.3

Unit

Data

and

Control

Diagram

(UDCD) . • • •

.•

1.

3

1.2.4

I/O

Operations

Diagrams

••••.•.••••••••

1. 3

1.

2.

5

Simplified

Logic

Diagrams

(SLD's) • . • • • • •

••

1.

3

1.

2.

6 Logic Flow Charts (CLFC) • • • • • • • • • . • • •

••

1.3

1.2.7

Timing

Charts (T)

..•••••••••.•••••••

1.5

1.3

DIAGNOSTIC PROGRAMMING AND MACHINE

••••

CHECK OUT

••••.•.•.•.•••.•••••••••••

1.5

1.

3.1

Maintenance

Diagnostic

Programs.

• • • • • • •

•.

1.

5

1.

3.

2

Program

Language.

• . • • • • • • • • • • • • • • •

••

1.

5

1.3;

3

Program

Control.

• • • • • • • • • • • • • • • • • •

••

1.5

1.

3.

4 Error Messages

and

Documentation

. • • • • • •

••

1.

5

1.

3.

5

Program

Loading.

• • . • • • . • • • • • • • • • • •

••

1.

5

1.

3.

6 Tests for

Device

Interaction

•••••••••••••

1.5

1.3.7

Operation

Modes.

• • • • • • • • • • • • • • • • . •

••

1.5

1.4

SERVICE CHECK LIST • • • • • • • • • • • • • • • • • •

••

1.7

1.4.1

General

Information

.••••••••••••••

•

••

1.7

1.4.2

General

Check

List

••••••••••••••••••

1.7

1.4.3

Core Storage

Check

List • • • • • • • • • • • • • •

••

1.

7

1.4.4

Addressing

Failure

Check

List

••••••••••••

1.

8

1.4.

5 Core Storage Console

Isolation.

• • • • • • • • •

••

1. 8

1.4.6

Current

Scoping

of

Core.

• • • • • • • • • • • • •

••

1.8

1.4.7

Core Diagnostic Aids (Figure

1-2)

•••••••••

1.

11

1.4.8

Transient

Power

Line

Noise.

• • • • • • • • • • •

••

1.12

1.5

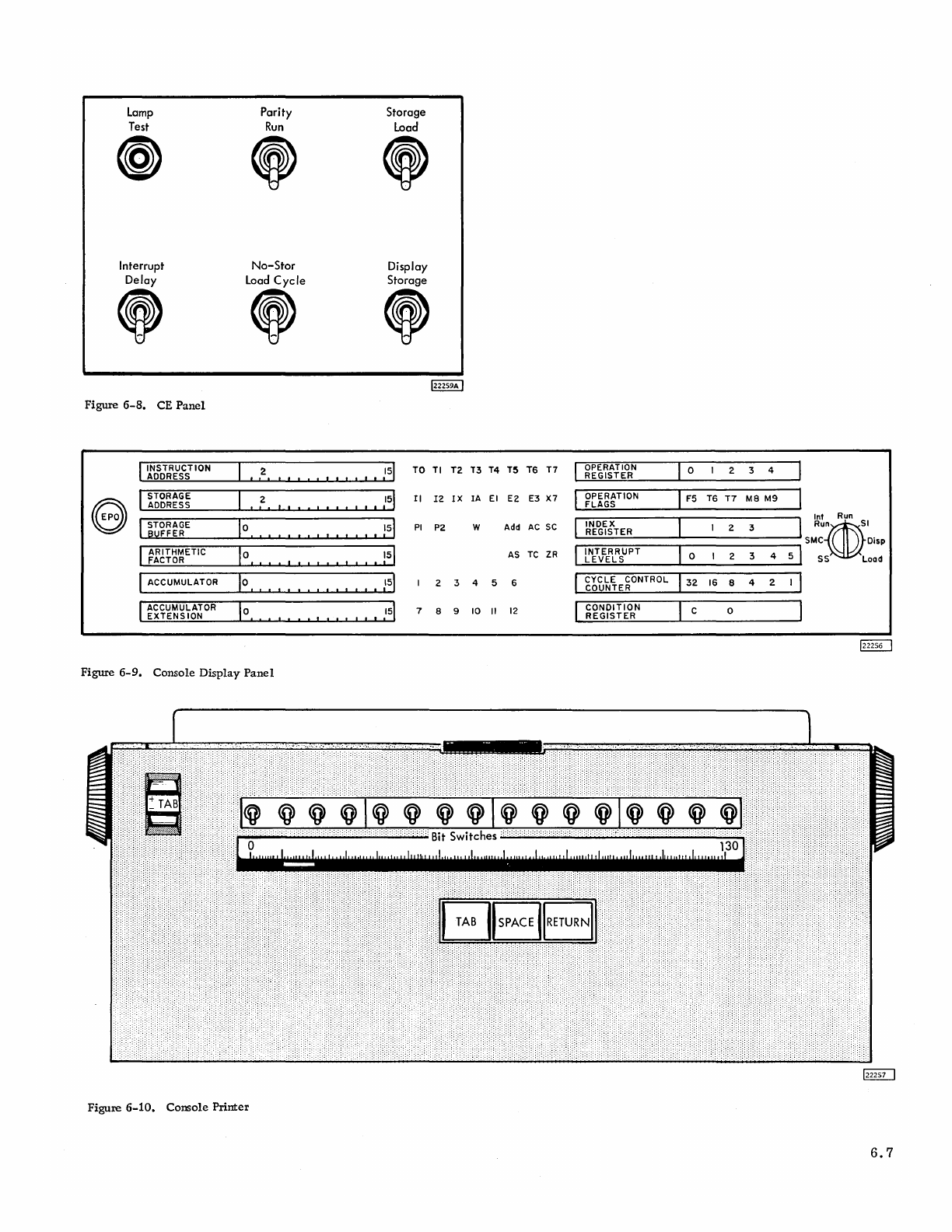

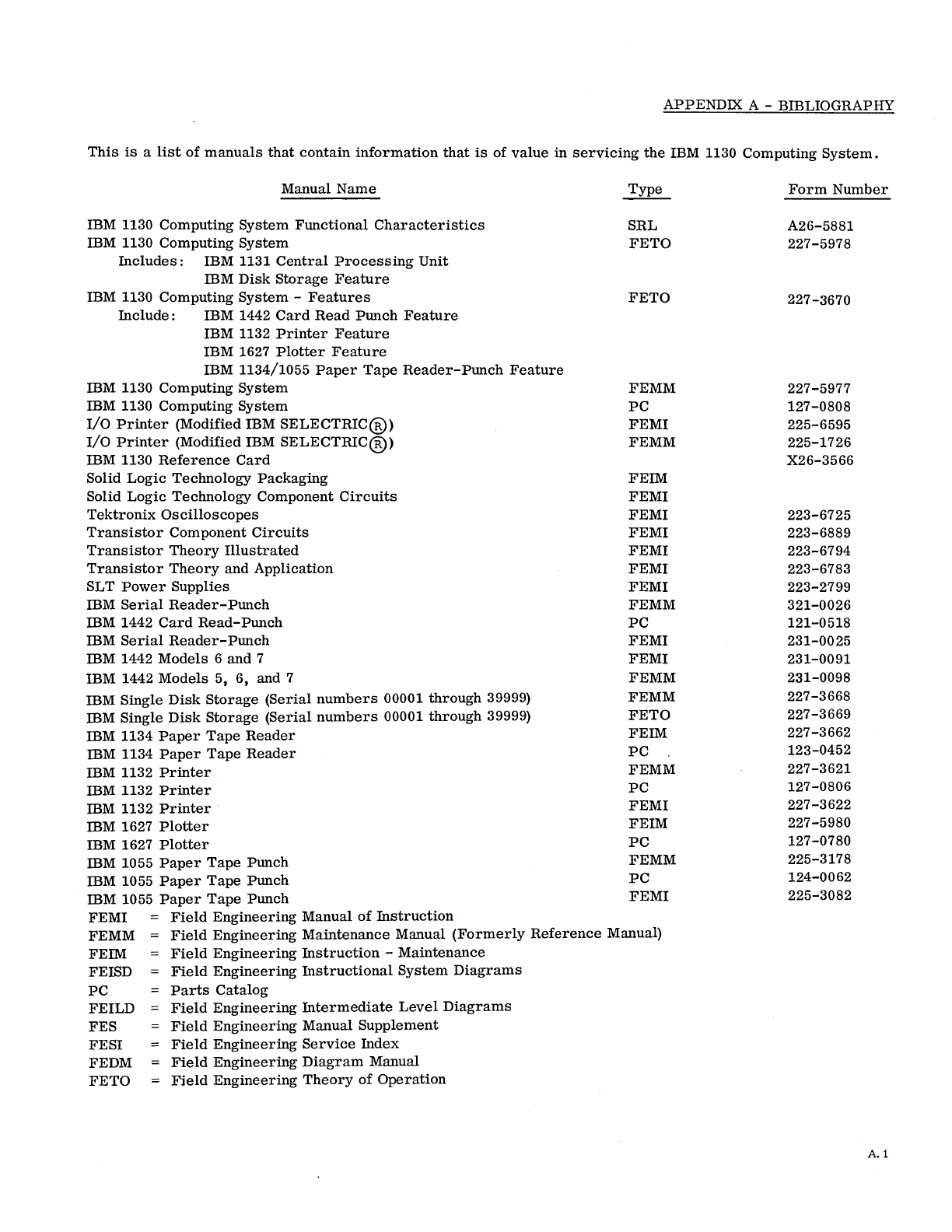

CONSOLE PANEL. • • • • • • • • • • • • • • • • • • • • •

••

1.13

1.6

CE

PANEL.

• • • . • • • • • • • • • • • • • • • • • • • • •

••

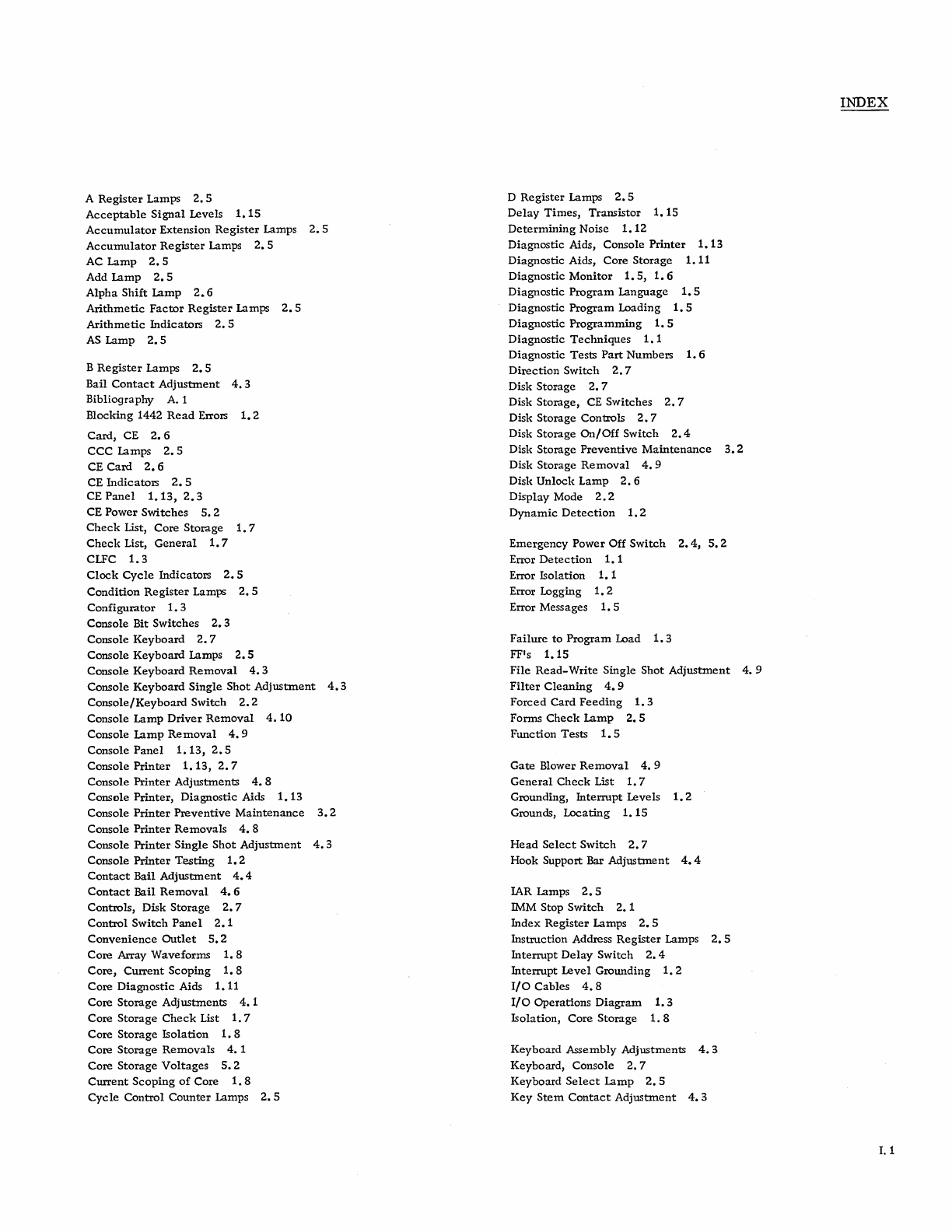

1.13

1.7

CONSOLE

PRINTER.

• • • • • • • • • . • . • • . • . . .

••

1.13

1.

7.

1 Console

Printer

Diagnostic

Aids (Figure

1-3)

•

••

1. 13

1.8

MARGINAL CHECKING

•••••••••••••••••.•

1.14

1.9

MISCELLANEOUS

TECHNIQUES.

• • • • • • • • . . •

.•

1.15

1.9.1

Locating

Grounds

••.•••••••••••••••.•

1.15

1.

9.2

Locating

Marginal

SLT Cards

••••••••.•.•

1.15

1.9.3

Signal

Levels.

• • • • • • • • • • • • • • . • • . • •

••

1.15

1.9.4

Transistor

Delay

Times

••.•••••••••••••

1.15

1.9.5

Multi-Input

Flip-Flop's

•..•.•••.•••••••

1.15

CHAPTER 2 MAINTENANCE FEATURES

.••.••••••••••

2.1

Basic

Machine

• . • • • • . . . . • . . . . • . . . . . • . • • . • . •

..

2.

1

2.1

MANUAL CONTROLS AND

INDICATORS.

• • • • •

••

2.1

2.1.1

Objectives.........................

2.1

2.1.

2

Control

Switch

Panel.

• • . • • . • • • • • • • • .

••

2.1

2.1.3

Mode

Switch. • • • • • . • . . . . . • • • • • • • • •

••

2.2

2.1.4

Console Bit Switches

••

• • • • • • . • • . • • • •

••

2.3

iii

CONTENTS

2.1.5

CE

Panel.

• . • • • • . • • • • • • • • • • • • • • •

••

2.3

2.1.

6

Miscellaneous

Switches.

• • • • • • • • • • • • •

••

2.4

2.1.7

Indicators

••••••••••••••••••••••••

2.5

2.2

CE

CARD.

• • • • • • • • • • • • • • • • • • • • • • • • •

••

2.6

2.3

CONSOLE PRINTER AND KEYBOARD. • • • • • • •

••

2.6

2.4

DISK

STORAGE.

• • • • • • • • • • • • • • • • • • • • •

••

2.7

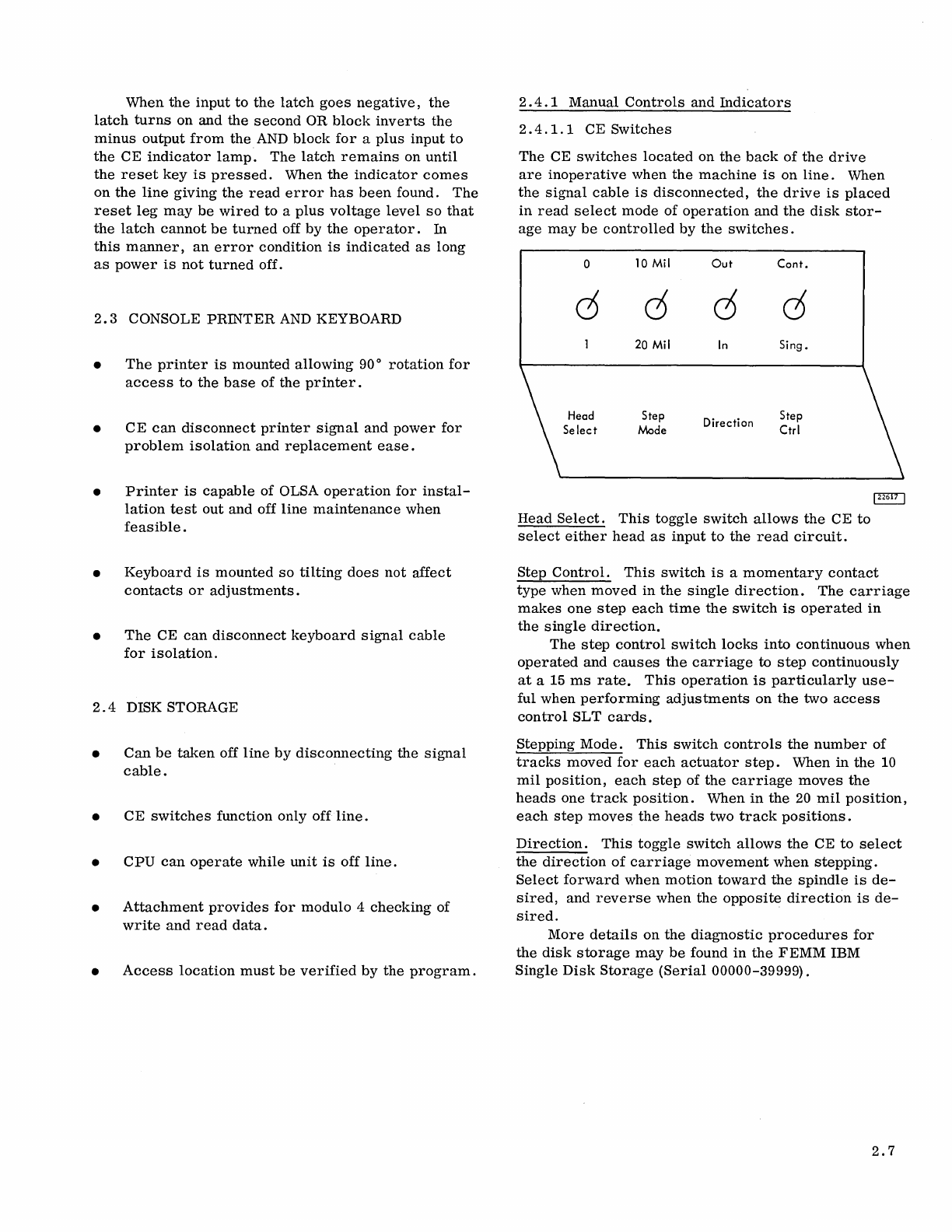

2.4.1

Manual

Controls

and

Indicators.

• • • • • • • •

••

2.7

Features • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • •

••

2.8

2.5

1442 READER

PUNCH.

• • • • • • • • • • • • • • • • •

••

2.8

2.5.1

CE

Switch.

• • • • • • • • • • • • • • • • • • • • •

••

2.8

2.5.2

Controls

and

Indicators.

• • • • • • • • • • • • •

••

2.8

2.6

1132 PRINTER

••••••••••••••••••••••••

2.9

2.6.1

Manual

Control

and

Indicators • • • • • • • • •

••

2.9

2.7

1627 PLOTTER • . • • • • • • • • • • • • • • • • • • • •

••

2.9

2.7.1

Controls

•••••••••••••••••••••••••

2~9

2.8

1132 PAPER TAPE

READER.

• • . • • • • • • • • • • •

••

2.10

2.9

1055 PAPER TAPE

PUNCH.

• • • • • • • • • • • • • •

••

2.10

2.9.1

Controls

•••••••••••••••••••••••••

2.10

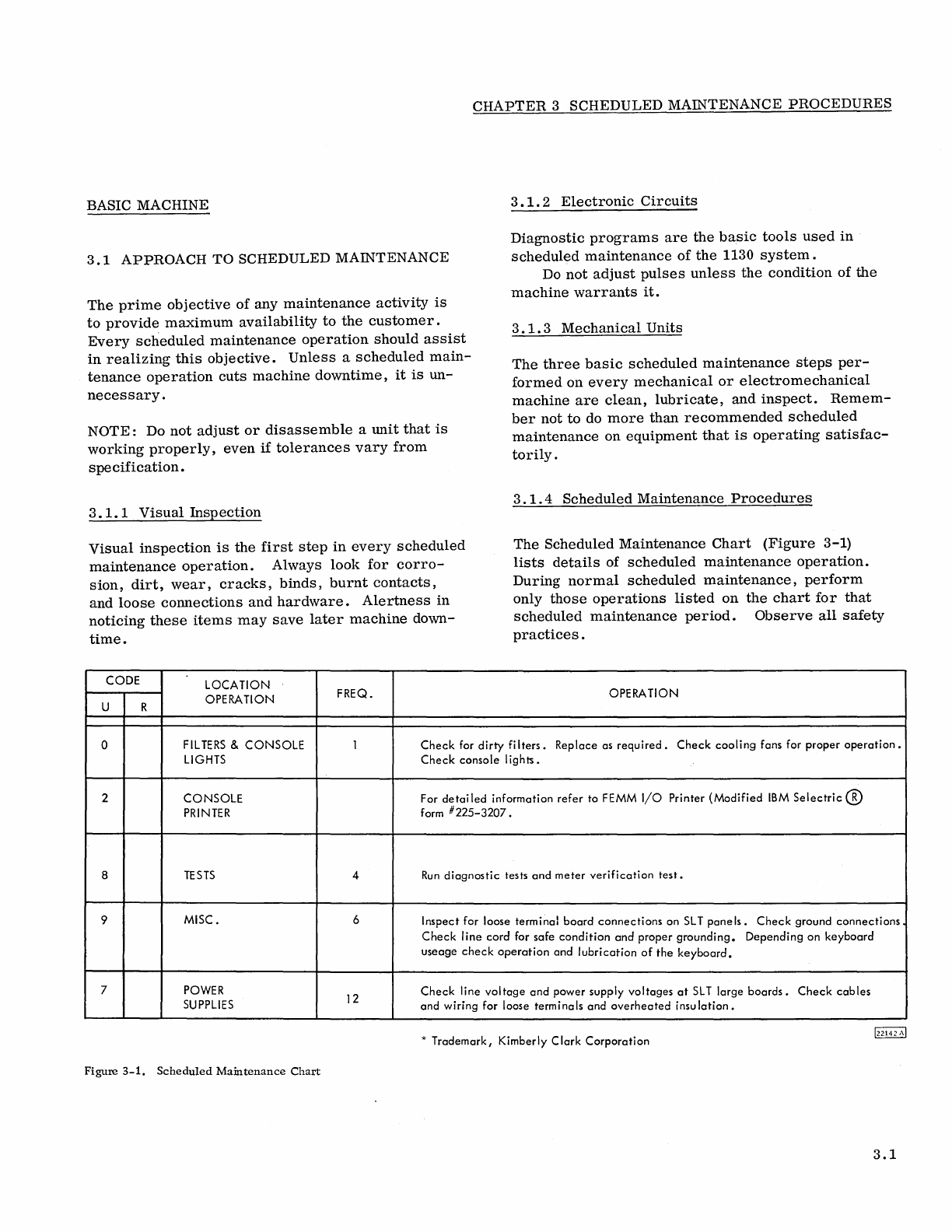

CHAPTER 3 SCHEDULED MAINTENANCE

PROCEDURES..

3.1

Basic

Machine

• • • • • • • • . • . • • • • • • • • • • • • • • • • •

••

3.

1

3.1

APPROACH

TO

SCHEDULED MAINTENANCE. • •

••

3.

1

3.

1. 1

Visual

Inspection.

• • • • • • • • • • • • • • • • •

••

3.

1

3.1.

2

Electronics

Circuits

• • • • • • • • • • • • • • • •

••

3.1

3.1.

3

Mechanical

Units

.••••••••••••••••••

3.1

3.1.4

Scheduled

Maintenance

Procedures • • • • • •

••

3.1

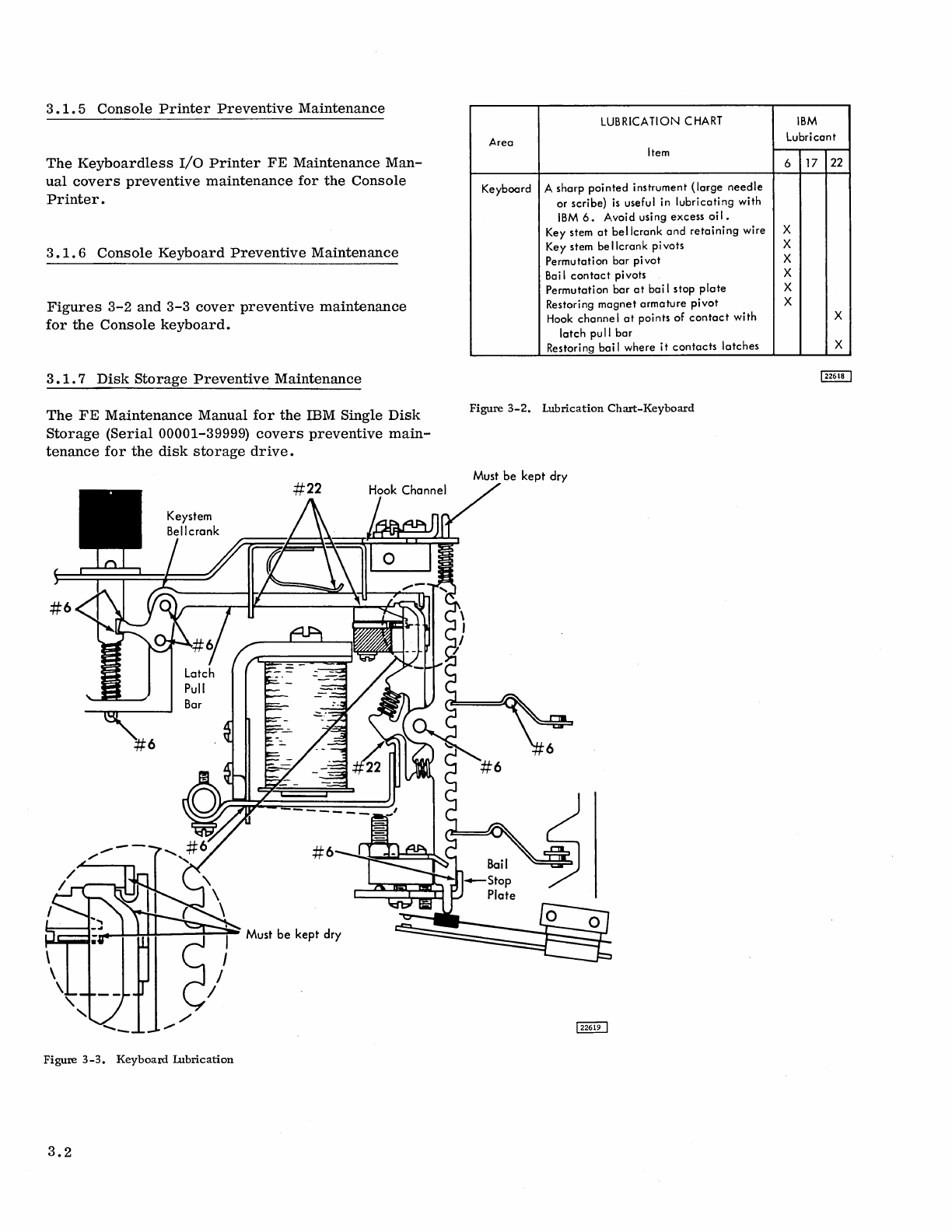

3.

1.5

Console

Printer

Preventive

Maintenance

• • •

••

3.2

3.1.

6 Console

Keyboard

Preventive

Maintenance

•

••

3.2

3.1.7

Disk

Storage

Preventive

Maintenance

••••••

3.2

Features

3.3

3.2

PREVENTIVE MAINTENANCE OF

I/O

DEVICES

•••

3.3

3.2.1

Preventive

Maintenance

••

• • • • • • • • • • •

••

3.3

3.2.2

1442

Preventive

Maintenance

•••••••••••

3.3

3.2.3

1134

Preventive

Maintenance

3.2.4

1055

Preventive

Maintenance

3.2.5

1627

Preventive

Maintenance

CHAPTER 4 CHECKS, ADJUSTMENTS, AND

3.3

3.3

3.3

REMOVAL PROCEDURES

••••••••••••••••••••••

4.1

Basic

Machine

• • • • • • • • • • • • • • • • • • • • • • • • • • • •

••

4.1

4.

1 SOLID LOGIC TECHNOLOGY MAINTENANCE. • •

••

4.1

4.1.1

SLT Cards • • • • • • • • • • • • • • • • • • • • • •

••

4.1

4.1.2

Single

Shots

••••••••••••••••••••••

4.1

4.2

CORE STORAGE

UNIT

• • • • • • • • • • • • • • • • •

••

4.

1

4.2.

1

Removal.........................

4.

1

4.2.2

Adjustment

Procedure

for

Core

Storage

•••••

4.1

4.3

OSCILLATOR.........................

4.2

4.3.

1

Oscillator

Phase

Adjustment.

• • • • • • • • • •

••

4.

2

4.4

CONSOLE KEYBOARD • • • • • • • • • • • • • • • • • •

••

4.

3

4.4.

1

Keyboard

Removal

••••••••••••••••••

4.

3

4.4.

2

Keyboard-Printer

Single Shots

•••••••••••

4.

3

4.4.

3

Keyboard

Assembly

• • • • • • . • • • • • • • • •

••

4.

3

4.

5 CONSOLE PRINTER • • • • • • • • • • • • • • • • • • •

••

4.

8

4.5.

1

General

Information.

• • • • • • • • • • • • • • •

••

4.

8

4.5.2

Service

Checks

••.••••••••••••••••••

4.5.3

Removal

•••••••••••••••••••••••••

4.6

I/O

CABlES

••••••••••••.•••••••••••••

4.

7 DISK STORAGE

UNIT

•••••••••••••••••••

4.

7.

1

Removal

•••••••••••••••••••••••••

4.7.2

File

Read-Write

Single

Shot

••••••••••••

4.

8 MISCELLANEOUS UNITS

••••••••••••••••••

4.

8.1

Table

Top

••••••••••••••••••••••••

4.

8.

2

Gate

Blowers

••••••••••••••••••••••

4.8.3

Filters

••••••••••••••••••••••••••

4.

8.4

Console Lamps

•••••••••••••••••••••

4.

8.5

Status

Indicator

Panel

••••••••••••••••

Features

••••••••••••••••••••••••••••••••••

4.9

1442

ATTACfWENT

••••••••••••••••••••

4.9.1

Read

Single

Shot

.••••••••••••••••••

4.

9.2, Punch

Gate

Single

Shot·

•••••••••••••••

4.10

PAPER TAPE ATTACHMENT

•••••••••••••••

4.

10.

1

Paper

Tape

Reader

Single

Shot

•••••••••••

4.10.2

Paper

Tape

Punch

•••••••••••••••••••

4.10.3

1134

Attachment

Oscillator

•••••••••••••

4.11

1132 PRINTER ATTACHMENT

•••••••••••••

4.12

1627 PLOTTER ATTACHMENT

•••••••••••••

4.13

1132 PRINTER

••••••••••••••••••••••••

4.14

1627 PLOTTER

•••••••••••••••••••••••

4.8

4.8

4.8

4.9

4.9

4.9

4~9

4.9

4.9

4.9

4.9

4.10

4.11

4.11

4.11

4.11

4.11

4.11

4.11

4.11

4.11

4.11

4.11

4.11

iv

4.15

1134

PAPER TAPE

READER'

• • • • • • • • • •

••

4.11

4.16

1055

PAPER TAPE PUNCH

•••••••••••••

4.11

4.17

1442 SERIAL READER

PUNCH.

• • • • • • • •

••

4.11

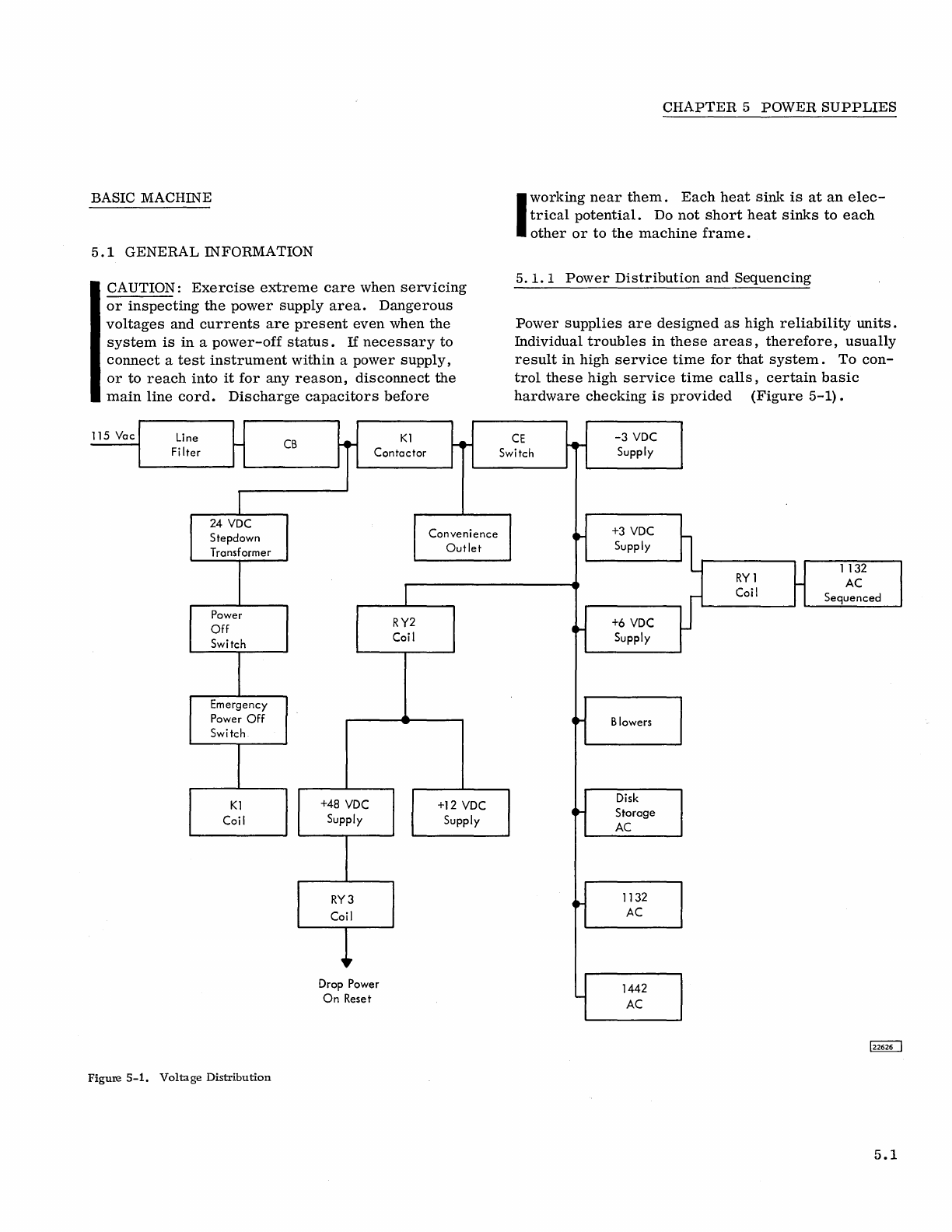

CHAPTER 5 POWER SUPPLIES. • • • • • • • • • • • • • • • • • • •

5.

1

Basic

Machine

• • • • • • • • • • • • • • • • • • • • • • • • • • • •

••

5.

1

5.1

GENERAL...........................

5.

1

5.1.1

Power

Distribution

and

Sequencing.

• • • • •

••

5.1

5.1.2

Switches.........................

5.2

S. 1. 3 CE Power Switches

••••••••••••••••••

5.2

5.1.4

Indicators • • • • • • • • • • • • • • • • • • • • • • • •

5.2

5.1.5

Voltage

Variation.

• • • • • • • • • • • • • • • •

••

5.2

S. 1. 6

Convenience

Outlet

•••••••••••••••••

5.2

5.1.7

Voltages

Present

Under

Normal

Power Off

Conditions.

• • • • • • • • • • • • • • • • • • • • • • • S. 2

S. 1. 8

Input

Power

Specifications

••

• • • • • • • • • • •

5.2

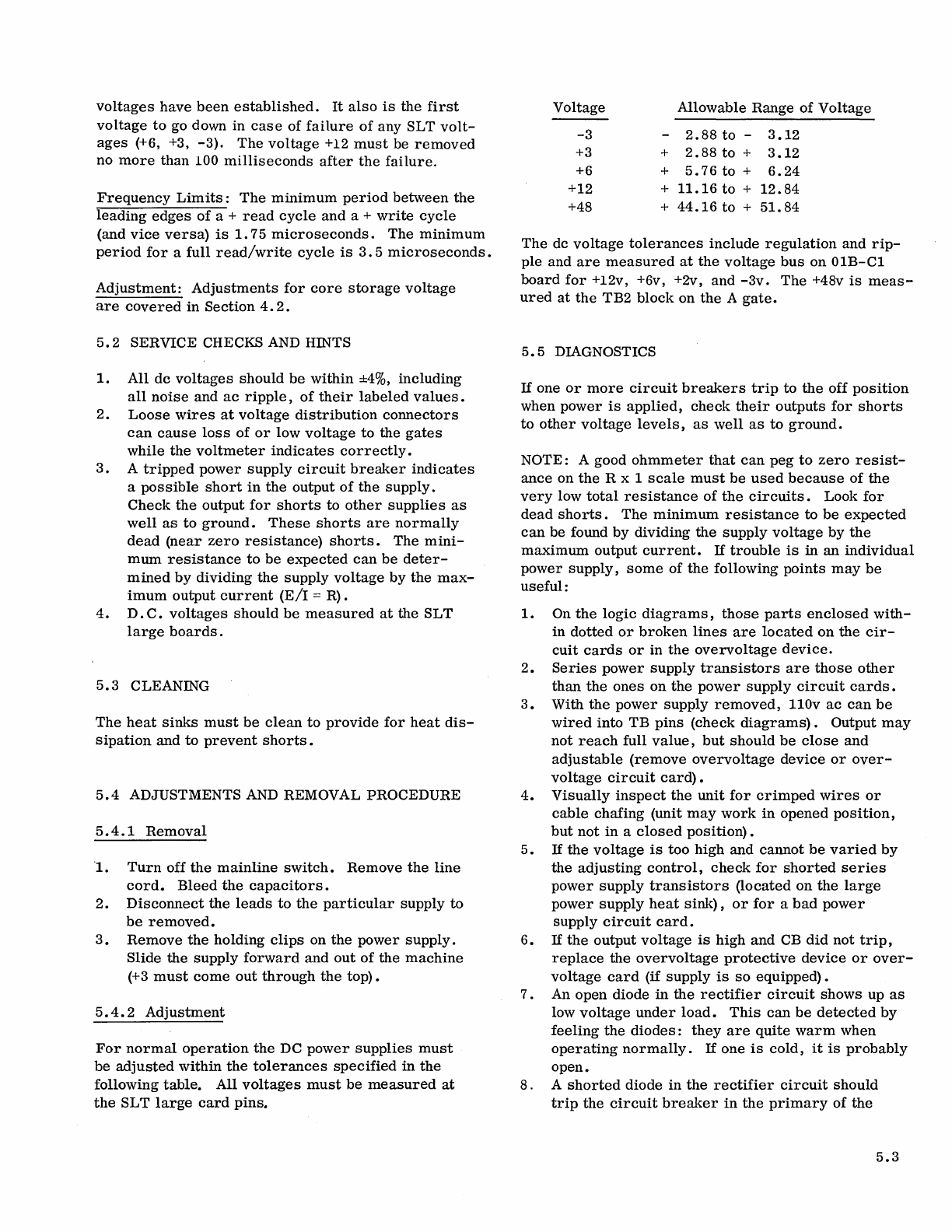

5.1.9

Individual

Power

Supplies.

• • • • • • • • • • • • •

5.2

5.1.10

Core

Storage

Voltages

• • • • • • • • • • • • • • • •

5.2

5.

2 SERVICE CHECKS AND HINTS

•••••••••••••

5.

3

5.3

ClEANING...........................

5.3

5.4

ADJUSTMENTS AND REMOVAL PROCEDURE • • • •

5.3

S.

4.

1

Removal

••••••••••••••••••••••••

S. 3

S. 4. 2

Adjustment.......................

S. 3

5.5

DIAGNOSTICS........................

5.3

5.5.1

Power Supply

Trouble

Symptom

Analysis

Chart

5.4

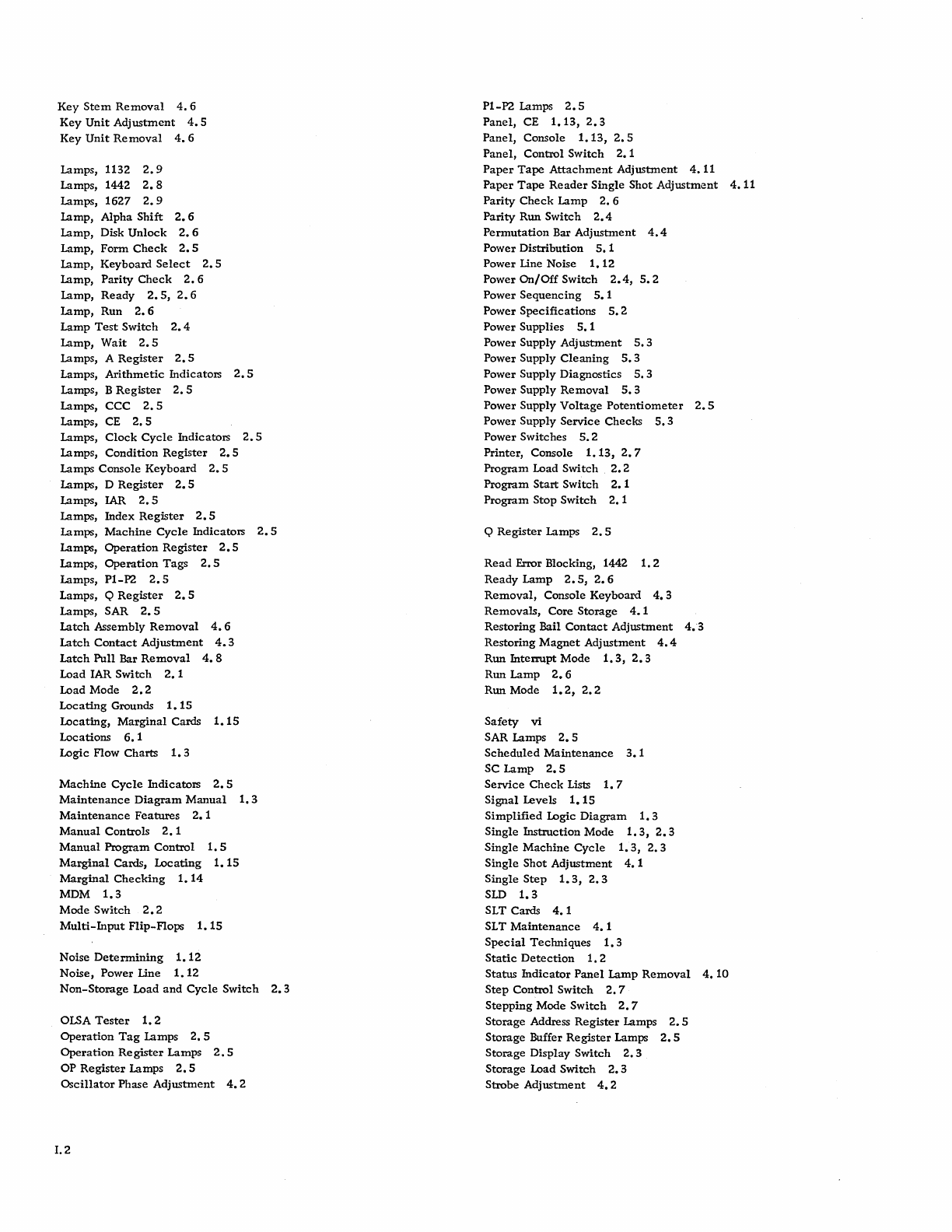

APPENDIX A - BIBLIOGRAPHY. . . . . . . . . . . . . .

..

A. 1

WARNINGS

Core

Storage

Be

extremely

cautious

when

working

around

the

core

array.

Avoid

disturbing

individual

planes.

Sense

and

select

wires

are

welded

to

pins

at

the

perimeter

of

the

array.

Bending

these

pins

can

fracture

welds

or

cause

shorts

between

adjacent

pins.

Use

the

han-

dles

provided

and

exercise

care

to

prevent

the

sides

from

striking

the

frame

of SL T

cards

whenever

it

is

necessary

to

remove

the

array.

Do

not

leave

core

storage

unit

unattended

when

covers

are

removed.

Oscilloscope

Core

Storage

Direct

probing

of

the

core

planes

is

not

advised.

Because

core

is

a

current

device,

no

valuable

infor-

mation

can

be

obtained

with

voltage

measurements

in

this

area

and

considerable

damage

could

result.

Due

to

physical

construction

of

the

core

array

the

current

probe

cannot

be

used

directly.

Techniques

for

obtaining

current

and

voltage

wave

shapes

are

detailed

in

section

1.4.

6

of

this

manual.

General

The

SLT

probe

tip

should

be

used

when

scoping

to

prevent

shorting

of

voltage

pins.

Probing

with

alli-

gator

clips

or

uninsulated

tips

should

be

avoided.

Power

Supplies

When

the

system

is

in

a

power-off

status,

24

vac

is

present

in

the

power

supply

area.

SLT

Components

Turn

off

power

whenever

an

SLT

card

is

removed

or

replaced.

Turn

off

power

to

the

sy

stem

when

v

wrapping

or

unwrapping

wire

or

when

testing

for

continuity.

Avoid

operating

the

system

for

prolonged

periods

of

time

with

the

SLT

card

covers

removed.

Servicing

Clear

core

storage

after

servicing

the

processor

to

prevent

returning

the

system

to

the

customer

with

an

invalid

word

in

core

storage.

An

invalid

word

re-

sults

in

a

data

error

when

the

word

is

read

from

core.

Tying

input

and

output

logic

functions

to

the

ground

or

to 0

volt

level

can

be

helpful

in

troubleshooting.

Exercise

care

in

the

disk

storage

unit

to

prevent

des-

troying

disk

storage

data

when tying

lines

to

the

0

volt

level.

Some

logic

blocks

can

be

tied

to

the

+ 3

volt

level.

It

is

necessary

to

evaluate

the

physical

con-

struction

of

the

component

circuits,

both

input

and

output,

on

a

line

before

it

can

be

determined

whether

the

+ 3

volt

level

will

be

effective.

Information

about

the

component

circuits

is

not

now

available

in

the

field.

In

general,

use

a 0

volt

level

and

work

back

to

an

input

or

an

output

which

gives

the

required

+ 3

volt

level.

Power

supply

voltages

are

present

on

some

pins.

Exercise

care

not

to

ground

these

pins.

NOTE:

Insert

a

470Q

resistor

to

act

as

a

load

limit-

ing

resistor

in

the

jumper

used

for

tying

down

lines.

Card

Reader

I/O

Run

all

cards

out

of

the

card

reader

punch

before

powering

down.

Powering

down

the

card

reader

punch

when

the

card

punch

is

loaded

with

cards

results

in

a

card

laced

in

column

one.

Use

the

pro-

vided

diagnostic

tests

as

masters

and

reproduce

the

deck

before

uSIng

the

deck

to

reduce

exposure

to

having

to

re-keypunch

cards.

Make

customer

aware

of

the

lacing

of

cards.

SAFETY

Personal

safety

cannot

be

over-emphasized.

To

ensure

your

own

safety,

make

it

an

every

day

practice

to

follow

safety

precautions

at

all

times.

Become

familiar

with

and

use

the

safety

practices

outlined

in

the

pocket-size

cards,

IBM

Forms

124-0002

and

MO

4-8401,

issued

to

all

Customer

Engineers.

Voltages

Potential

difference

within

the

electronic

gates,

printed

cards,

and

display

back

panel

is

+48v

dc

to

-3v

dc.

Do

not

remove

or

replace

circuit

cards

when

dc

power

is

on.

Do

not

short

out

or

bypass

safety

features.

Power

Supplies

Extreme

care

must

be

exercised

when

servicing

or

inspecting

the

power

supply

even

though

the

voltage

range

on

the

machine

is

low.

Dangerous

voltages

and

currents

are

present

even

when

the

system

is

in

a

power-off

status.

If

it

is

necessary

to

connect

a

test

instrument

within

the

power

supply,

or

to

reach

into

it

for

any

reason,

disconnect

the

main-

line

cord.

Discharge

capacitors

before

working

near

them.

Each

heat

sink

is

at

an

electrical

poten-

tial.

Do

not

short

heat

sinks

to

each

other

or,

to

the

machine

frame.

Grounding

Convenience

outlets

for

Customer

Engineers

are

provided

in

the

1131, 1132,

and

1442.

Machine

grounding

is

required.

Three-wire

grounded

power

cords

are

provided.

The

third

wire

is

for

grounding

and

must

not

carry

current

from

any

source.

IT

IS IMPORTANT

TO

THE

SAFETY

OF

PERSONNEL

THAT

IF

ANY

MACHINE

OF

A GROUP

IS GROUNDED,

ALL

OTHER

EQUIPMENT

OF

THE

GROUP MUST

BE

GROUNDED.

Grounded

machines

must

be

placed

so

that

it

is

not

possible

for

a

person

to

touch

both

a

grounded

machine

and

any

ungrounded

metal

equipment.

Grounded

machines

do

not

present

vi

a

hazard

in

themselves;

the

real

hazard

is

from

un-

grounded

electrical

equipment.

Console

Printer

(Modified IBM

SELECTRIC

® )

Working

in

certain

areas

of

the

typewriter

is

particu-

lar

ly

hazardous

due

to

the

positive

action

of

the

type-

writer.

Follow

safe

working

practices.

Because

it

is

not

possible

to

foresee

each

individual

area

of

exposure,

the

following

general

rules

serve

as

a

guide

when

working

on

this

equipment.

1.

At

the

completion

of

a

service

call,

replace

gear

guards

and

dust

shields.

These

safety

guards

are

installed

to

prevent

the

operator

from

placing

his

hands

too

near

moving

parts.

Because

most

operators

do

not

have

a

complete

knowledge

of

the

mechanical

workings

of

the

machine,

the

only

way

they

can

be

adequately

protected

is

to

place

guards

over

the

exposed

areas.

Be

cautious

when

servicing

this

machine

during

the

time

the

rear

guards

and

dust

shields

are

removed.

2.

When

lubricating,

replacing

parts,

etc.,

make

sure

the

machine

is

turned

off.

It

is

a good

idea

to

remove

the

motor

plug

from

the

socket

after

turning

the

switch

to

the

off

position.

3.

Exercise

caution

when

handling

the

motor.

The

shaded-pole

motor

used

in

this

machine

runs

considerably

hotter

than

the

capacitor

type

motor

used

in

the

Model

B

typewriter.

4.

Be

particularly

careful

to

avoid

injury

to

the

hands

from

sharp

edges

on

stamped

parts,

springs,

links,

etc.

when

picking

up

and

handling

all

types

of

machines.

Although

the

safety

of

the

operator

and

the

CE

is

one

of

the

prime

consider-

ations

in

the

design

of

the

product,

mass

pro-

duction

techniques

do

not

permit

separate

opera-

tions

on

each

part

to

provide

a

smooth

edge.

5.

Wear

safety

glasses

when

performing

any

work

that

could

result

in

parts,

lubricants,

cleaning

solvents,

or

any

other

materials

contacting

the

eyes.

NOTE:

The

word

CAUTION

is

used

in

this

manual

to

indicate

procedures

that

require

extra

precautions

to

ensure

personal

safety.

DIAGNOSTIC TECHNIQUES

1.

1 TROUBLESHOOTING

1. 1.

1

Introduction

The

service

philosophy

of

the

1130

system

is

based

on

the

effective

use

of

diagnostic

programs

and

techniques.

These

programs

and

techniques

depend

heavily

on

the

multiple

modes

of

operation

of

the

processor

and

of

the

console

indicators

to

define

problem

areas.

It

must

be

recognized

that

the

pro-

grams

and

techniques

carmot

always

eliminate

the

need

for

detailed

pulse

and

voltage

checking,

but

they

are

designed

to

reduce

this

detailed

evaluation

to a

minimum.

When a

failure

occurs,

note

all

pertinent

infor-

mation.

Record

the

contents

of

all

registers

and

console

panel

indicators

on a

check

sheet

for

later

reference.

Try

to

localize

the

failure

before

re-

moving

the

machine

from

productive

work.

The

+12

and

+48

volt

supplies

do

not

power

down

the

system

if

either

has

a

power

failure.

The

sys-

tem

does

not

run

if

these

voltages

are

missing

and

the

supplies

should

be

checked

first

to

determine

their

condition.

The

increased

realiability

of

electronic

com-

ponents

suggests

that

the

majority

of

general

service

problems

are

electro-mechanical

in

nature.

These

problems

are

caused

by

mechanical

adjustments,

mechanical

wear,

electrical

timing,

and

loose

connections.

Diagnostic

procedures

have

been

provided

to

assist

in

isolating

troubles

between

the

electronics

of

the

processor

and

the

functions

of

electro-

mechanical

peripheral

devices.

Keep

in

mind

two

other

problem

sources,

pro-

gram

troubles

and

electrical

noise

troubles.

Be-

cause

the

1131

processor

depends

completely

on

programming

for

all

input

and

output

functions

as

well

as

for

processing,

program

timing

errors

and

incorrect

data

can

appear

as

electronic

processor

or

I/o

problems.

The

diagnostic

programs

are

designed

to

exercise

and

examine

the

fWlCtions

of

the

processor

and

I/o

devices.

In

general,

the

tests

provide

the

assurance

needed

to

guide

problem

analysis

to

the

machine

or

the

program.

Electrical

noise

can

be

a

problem

due to

the

low

level

signals

used

in

this

and

other

solid

state

systems.

Critical

evaluation

during

test

assures

that

the

system

is

CHAPTER

1 - DIAGNOSTIC AIDS

free

from

electrical

noise

interference

anticipated

in

most

environments.

Suppression

circuits

have

been

designed

into

the

system

to

reduce

exposure

to

both

internal

and

external

interference.

However,

there

is

always

the

possibility

of

unique

external

conditions

or

of

the

failure

of

grounding

or

suppres-

sion

circuits.

While

there

are

no

unique

tests

or

tools

available

to

pinpoint

electrical

noise,

the

diagnostic

section

of

this

manual

does

provide

some

analYSis

procedures

which

can

assIst

trouble

analysis

when

electrical

interference

is

suspected.

Note:

For

problems

that

do

not

seem

to

lend

themselves

to

analysis,

check

that

all

cards

and

interboard

connectors

are

in

place

and

seated.

1. 1.

2

Error

Detection

All

data

entering

core

storage

has

odd

parity

added

to

each

half

word.

The

parity

is

checked

when

reading

out

of

core

storage.

A

parity

error

in

core

results

in

the

processor

stopping

at

the

end

of

the

core

storage

cycle

in

which

the

parity

error

con-

dition

is

detected.

Parity

bypass

is

under

CE

switch

control,

not

under

program

control.

The

I/o

devices

have

checking

circuits

with

error

checks

which

can

be

recognized

by

programmed

interrogation

of

the

corresponding

Device

Status

Word

(DSW);

Disk

Storage,

1132

Printer,

and

1442-6

or

7

Card

Reader-Punch.

Each

of

these

devices,

except

Disk

Storage,

uses

a

visual

indicator

to

alert

the

operator

to

the

fact

that

an

error

has

occurred.

System

diagnostic

programs

provide

for

error

handling

techniques

for

program

recognizable

input

data

errors,

and

supply

printouts

to

aid

in

diagnosing

troubles.

1.

1. 3

Error

Isolation

The

CE

switches

under

the

right

hand

top

cover

pro-

vide

specific

functions

for

processor

error

isolation.

Bit

switch

data

can

be

written

into

core

and

then

read

back

for

parity

verification.

Bit

switch

data

can

be

cycled

through

the

processor

and

registers

without

reference

to

storage.

Interrupt

request

can

be

in-

hibited.

Indicator

lamps

can

be

mass

tested.

In

addition

to

the

CE

switches,

four

modes

of

operation

(single

step,

single

cycle,

single

instruc-

tion,

and

interrupt

run)

are

available

at

the

console.

These

modes

are

described

in

detail

in

section

1. 1.

5.

1.1

To

further

assist

error

isolation,

the

single

disk

storage

can

be

disconnected

from

the

system

and

operated

in

the

read

mode

under

CE

switch

con-

trol.

The

processor

can

also

be

operated

independ-

ently

of

the

disk

storage

when

it

has

been

discon-

nected

from

the

system.

The

I/o

devices

are

capable

of

limited

mechan-

ical

operation

independently

of

the

processor.

In

general,

independent

mechanical

operation

of

the

devices

cannot

be

performed

without

affecting

pro-

cessor

performance.

It

is

possible

to

remove

the

devices

from

the

system

by

disconnecting

their

signal

connectors.

In

some

cases

it

is

necessary

to

ground

interrupt

level

lines

to

permit

operation

of

the

processor

with

the

device

removed.

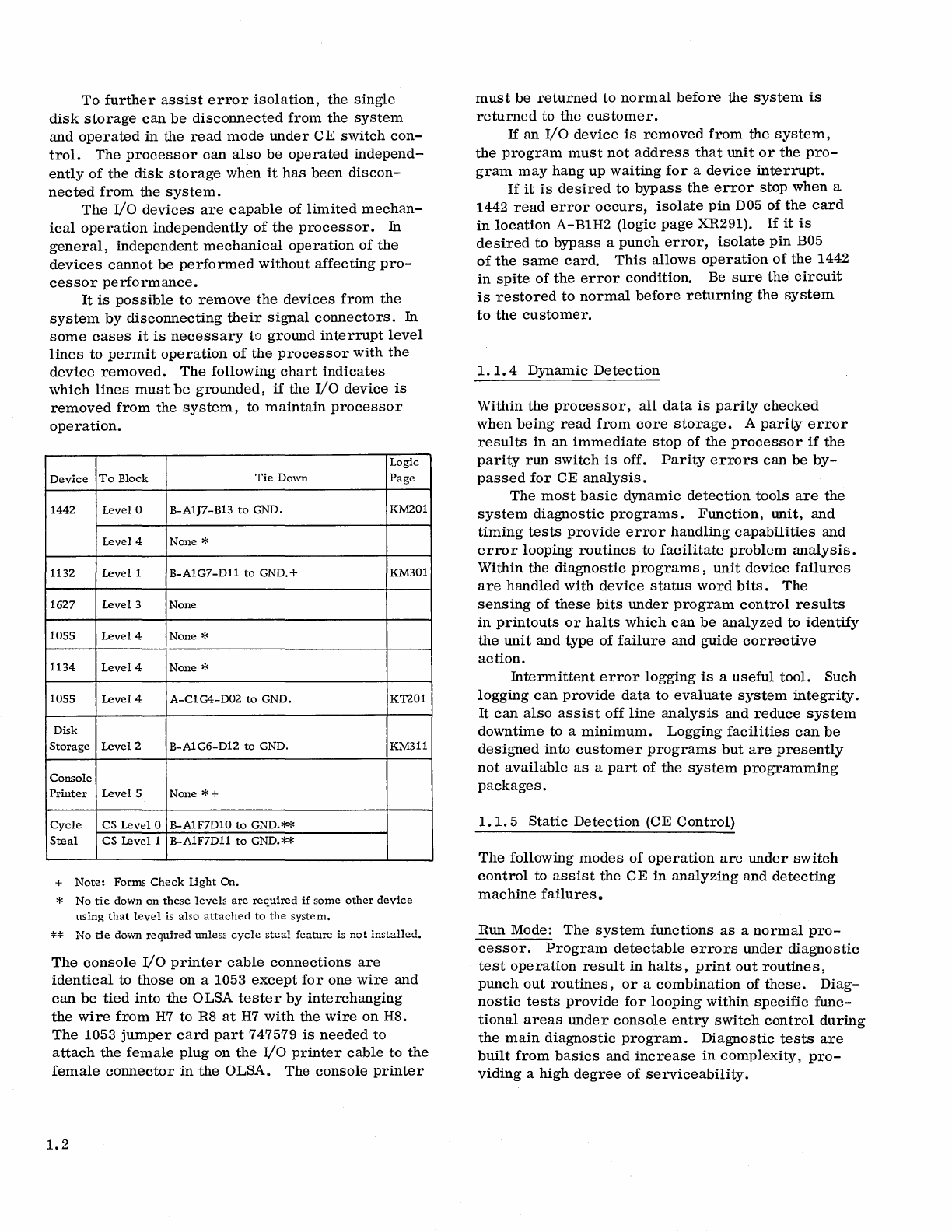

The

following

chart

indicates

which

lines

must

be

grounded,

if

the

I/O

device

is

removed

from

the

system,

to

maintain

processor

operation.

Logic

Device

To

Block

Tie

Down

Page

1442

Level

a

B-AIJ7-B13

to

GND. KM201

Level

4

None

*

1132

Levell

B-AIG7-D11

to

GND.+

KM301

1627

Level

3

None

lOSS

Level

4

None

*

1134

Level

4

None

*

lOSS

Level

4

A-CIG4-D02

to

GND. KT201

Disk

Storage

Level

2

B-AIG6-D12

to

GND. KM311

Console

Printer

levelS

None

*+

Cycle

CS

Level

0

B-AIF7DlO

to

GND.**

Steal

CS

Levell

B-AIF7D11

to

GND.**

+

Note:

Forms

Check

Light

On.

* No

tie

down

on

these

levels

are

required

if

some

other

device

using

that

level

is

also

attached

to

the

system.

......

No

tie

dovvi1

required

unless

cycle

steal

feature

is

not

installed.

The

console

I/o

printer

cable

connections

are

identical

to

those

on

a 1053

except

for

one

wire

and

can

be

tied

into

the

OLSA

tester

by

interchanging

the

wire

from

H7

to R8

at

H7

with

the

wire

on

H8.

The

1053

jumper

card

part

747579

is

needed

to

attach

the

female

plug

on

the

I/o

printer

cable

to

the

female

connector

in

the

OLSA. The

console

printer

1.2

must

be

returned

to

normal

before

the

system

is

returned

to

the

customer.

If

an

I/O

device

is

removed

from

the

system,

the

program

must

not

address

that

unit

or

the

pro-

gram

may

hang

up

waiting

for

a

device

interrupt.

If

it

is

desired

to

bypass

the

error

stop

when

a

1442

read

error

occurs,

isolate

pin

D05

of

the

card

in

location

A-B1H2 (logic

page

XR291).

If

it

is

desired

to

bypass

a

punch

error,

isolate

pin

B05

of

the

same

card.

This

allows

operation

of

the

1442

in

spite

of

the

error

condition. Be

sure

the

circuit

is

restored

to

normal

before

returning

the

system

to

the

customer.

1.1.4

Dynamic

Detection

Within

the

processor,

all

data

is

parity

checked

when

being

read

from

core

storage.

A

parity

error

results

in

an

immediate

stop

of

the

processor

if

the

parity

run

switch

is

off.

Parity

errors

can

be

by-

passed

for

CE

analysis.

The

most

basic

dynamic

detection

tools

are

the

system

diagnostic

programs.

Function,

unit,

and

timing

tests

provide

error

handling

capabilities

and

error

looping

routines

to

facilitate

problem

analysis.

Within

the

diagnostic

programs,

unit

device

failures

are

handled

with

device

status

word

bits.

The

sensing

of

these

bits

under

program

control

results

in

printouts

or

halts

which

can

be

analyzed

to

identify

the

unit

and

type

of

failure

and

guide

corrective

action.

Intermittent

error

logging

is

a

useful

tool.

Such

logging

can

provide

data

to

evaluate

system

integrity.

It

can

also

assist

off

line

analysis

and

reduce

system

downtime

to a

minimum.

Logging

facilities

can

be

designed

into

customer

programs

but

are

presently

not

available

as

a

part

of

the

system

programming

packages.

1.1.

5

Static

Detection

(CE

Control)

The

following

modes

of

operation

are

under

switch

control

to

assist

the

CE

in

analyzing

and

detecting

machine

failures

0

Run Mode:

The

system

functions

as

a

normal

pro-

cessor.

Program

detectable

errors

under

diagnostic

test

operation

result

in

halts,

print

out

routines,

punch

out

routines,

or

a

combination

of

these.

Diag-

nostic

tests

provide

for

looping

within

specific

func-

tional

areas

under

console

entry

switch

control

during

the

main

diagnostic

program.

Diagnostic

tests

are

built

from

basics

and

increase

in

complexity,

pro-

viding

a

high

degree

of

serviceability.

Run

Interrupt

Mode: A

level

five

interrupt

occurs

after

each

main

line

instruction.

This

mode

can

be

used

for

tracing

main

line,

branch,

or

sub-routine

operations.

Single

Instruction

Mode:

The

processor

stops

after

each

instruction

is

executed.

The

start

key

controls

the

advance.

Single

Machine

Cycle:

The

processor

executes

a

single

clock

cycle

TO-T7,

E,

I,

IX, IA,

etc.

,

under

control

of

the

start

key.

SMC

can

be

used

to

investi-

gate

CPU

functions

with

every

cycle

taken

by

memory.

Single

Step:

The

processor

executes

a

single

clock

step,

i.

e.

,

Tl

under

control

of

the

start

key.

Pressing

the

single

step

key

results

in

the

generation

of

an

A

pulse,

the

release

of

the

key

results

in

a

B

pulse.

Exercise

care

when

using

single

step

because

core

data

can

be

destroyed

if

the

processor

is

reset

or

if

the

mode

switch

is

changed

between

TO

and

T6

time.

1.

1.

6

Special

Techniques

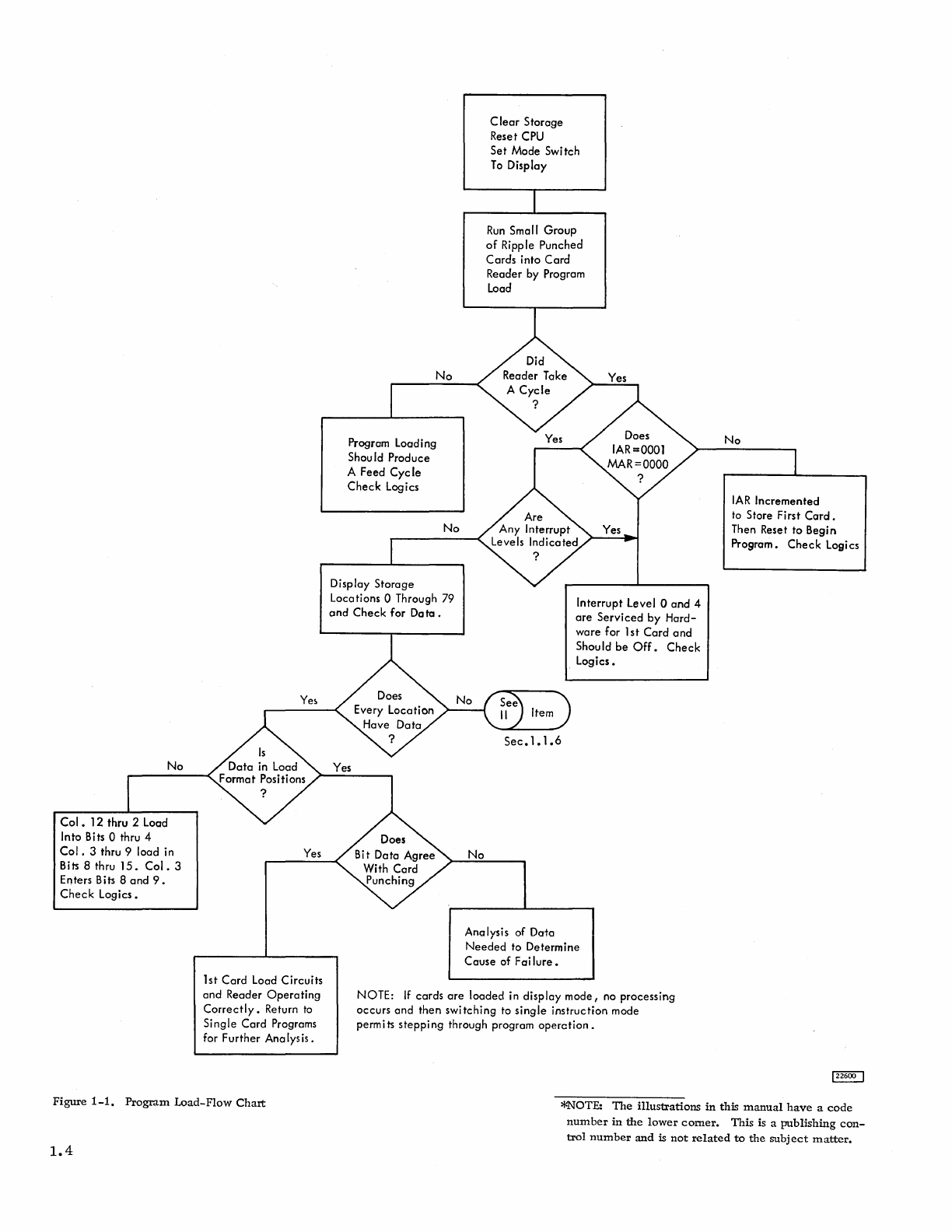

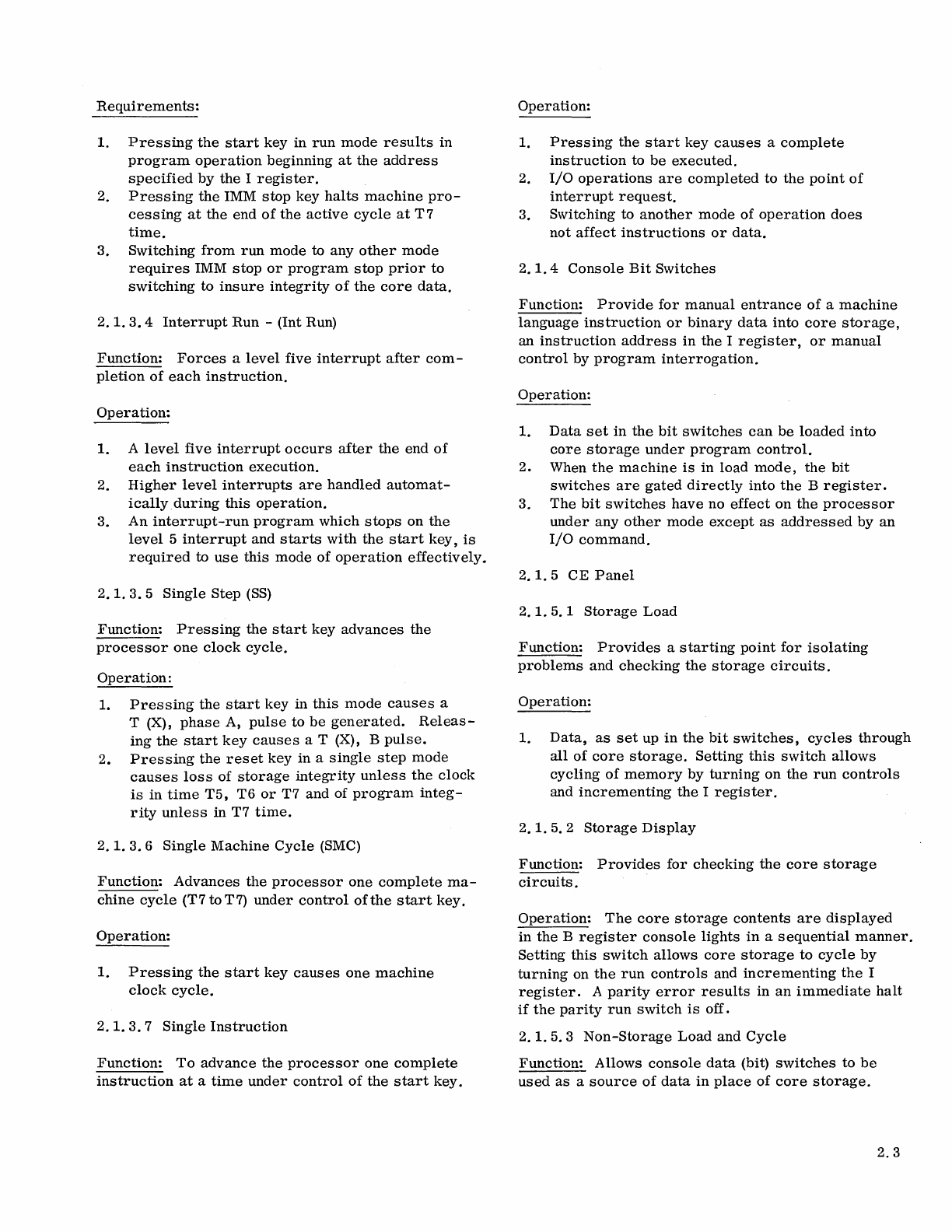

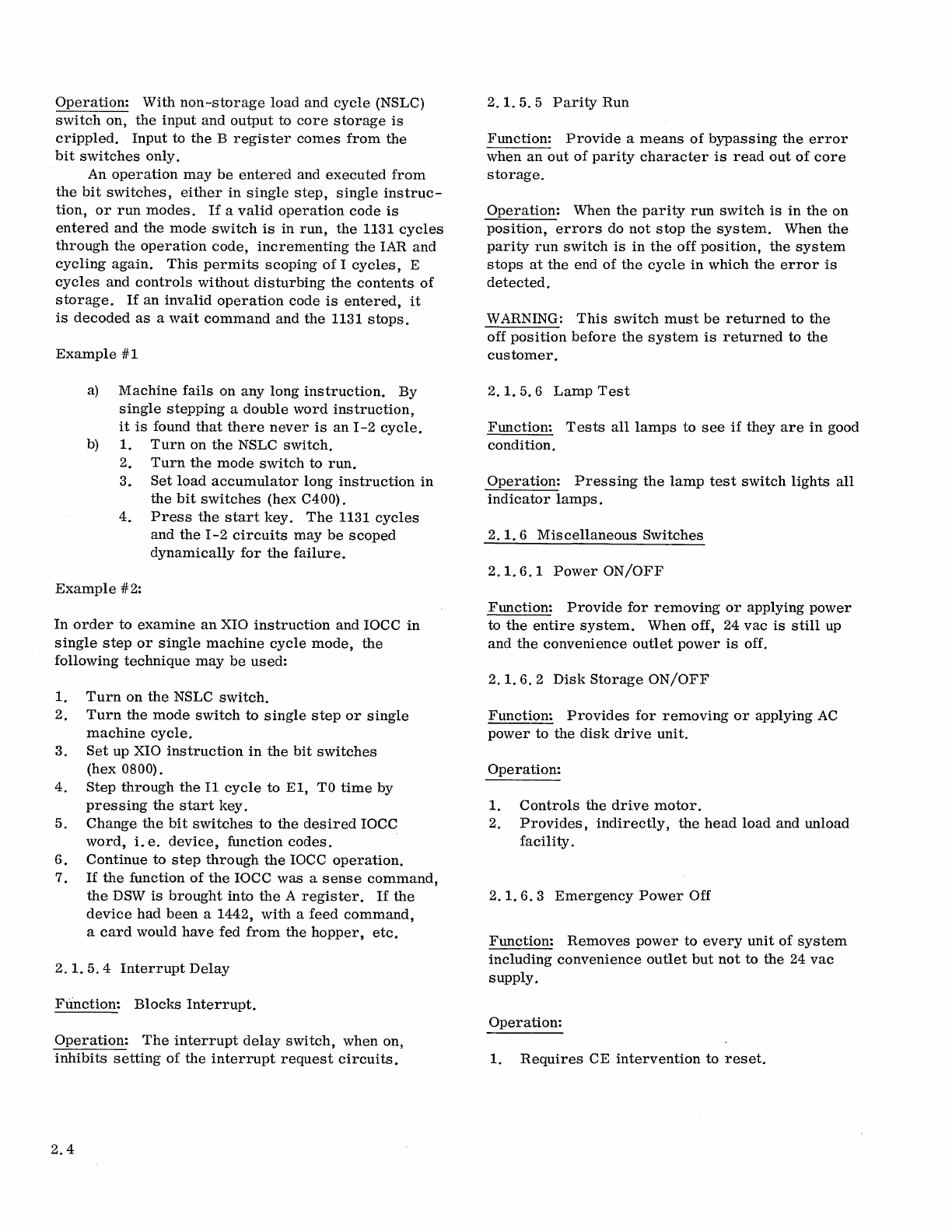

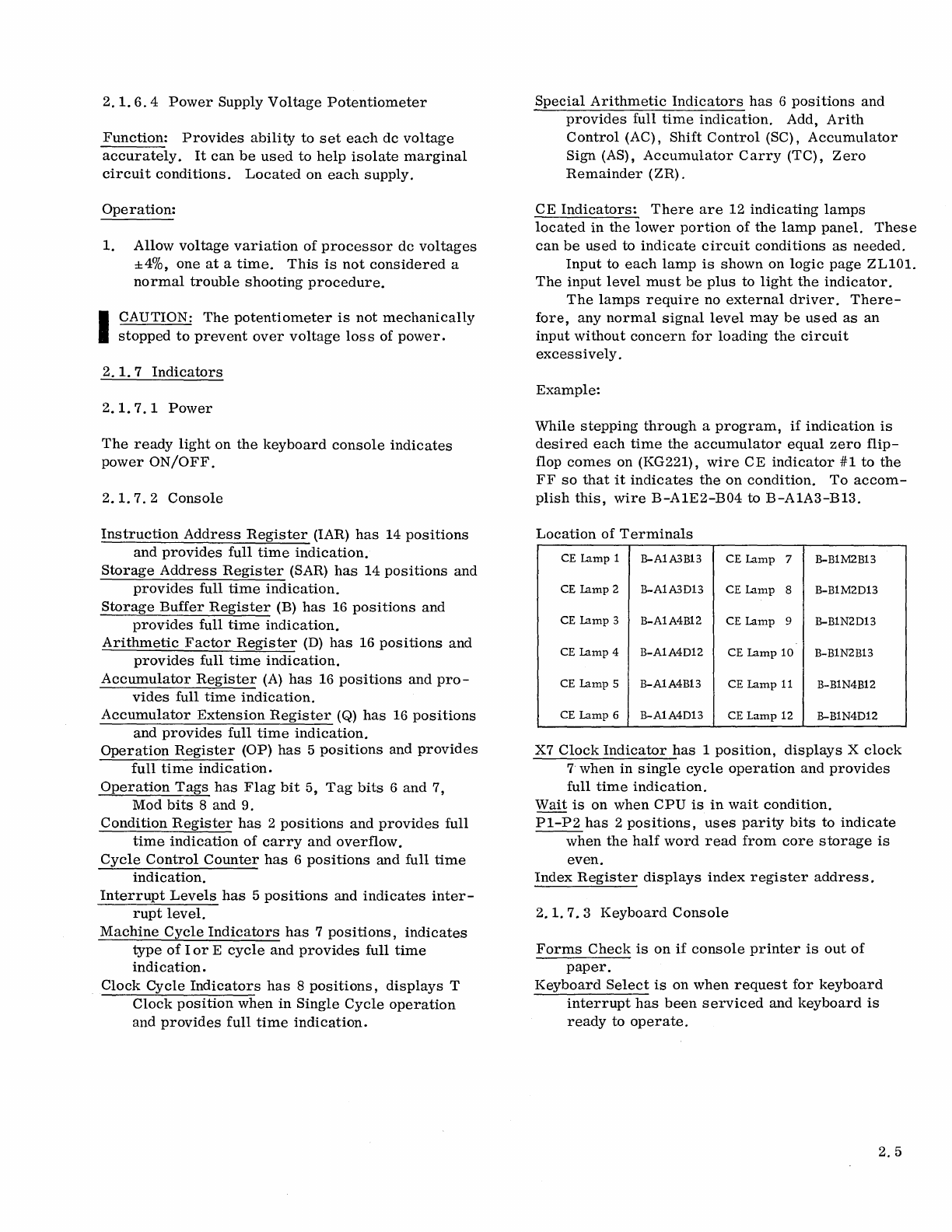

Failure

to

Program

Load

(card

system):

(Figure

1-1)

The

initial

problem

is

to

define

whether

the

card

reader

or

the

processor

is

at

fault.

The

following

procedure

can

assist

diagnosis:

1.

Try

one

card

programs.

If

these

do

not

lead

to

an

immediate

fault

location,

load

core

with

hex

7000 (MDX)

using

the

bit

switches

and

the

storage

load

switch.

Press

reset

and

start

the

program

by

pressing

the

start

key.o

This

causes

the

processor

to

perform

a

no-op

operation.

By

changing

the

displacement

through

core,

the

instruction

operates

as

a

branch.

If

the

MDX

instruction

operates

properly,

enter

hex

COOO

(load

accumulator)

in

location

0000.

Enter

hex

DOOO

(store

accumulator)

in

location

0001.

Reset

the

CPU

and

press

the

start

key.

This

simple

routine

loops

and

sets

hex

DOOO

in

every

core

location.

If

these

routines

run,

check

the

system

using

the

following flow

chart.

2.

An

incorrectly

adjusted

read

emitter

causes

intermittent

loss

of

interrupts.

In

this

case

the

last

words

in

the

read

in

area

are

blank

and

the

data

read

is

in

adjacent

positions.

Failure

to

read

a

column

(assuming

an

interrupt

occurs)

results

in

blank

words

within

the

SO-word

field

causing

a

read

register

check

or

a

feed

check.

Double

incrementing

of

the

I

counter

on

pro-

gram

load

causes

blank

words

in

core

on

program

load.

Card

Feeding

(no

program):

A

technique

for

causing

the

1442 to

feed

cards

without

a

program

in

the

machine

is

sometimes

needed.

This

technique

is

1.

Load

the

read

hopper

with

cards.

2.

Turn

the

mode

switch

to

single

step.

3.

Press

the

program

load

key.

Cards

continue

to

feed

as

long

as

the

program

load

key

is

held.

The

program

load

key

may

be

blocked

down

and

the

feeding

controlled

by

the

1442

start

and

stop

keys.

1.

2

THE

MAINTENANCE DIAGRAM MANUAL (MDM)

The

following

paragraphs

define

the

organization

and

contents

of

this

manual.

1.

2.1

IBM 1130

Configurator

•

Defines

the

maximum

system

configuration.

1.2.2

System

Data

Flow

Diagram

• Shows

over-all

data

flow

of

the

1130.

• Shows

exits

and

entries

to

I/O.

1.

2. 3 Unit

Data

and

Control

Diagram

(UDCD)

•

Expands

each

unit

contained

within

the

system

data

flow

diagram

to

include

major

controls.

1.

2.4

I/o

Operations

Diagrams

• Shows

the

over-all

functions

of

I/o

operations

in

positive

logic

diagrams.

1.

2.5

Simplified

Logic

Diagrams

(SLDs)

•

Contains

logic

diagrams,

arranged

in

an

under-

standable

manner,

of

those

complex

areas

of

the

system

where

an

additional

level

of

logic

is

desired

for

clarity.

1.

2.6

Logic

Flow

Charts

(CLFC)

• Shows

in

condensed

form,

the

concept

of

a

particular

operation.

1.3

Col.

12 thru 2 Load

Into Bits 0 thru 4

Col.

3 thru 9 load in

Bits 8 thru

15.

Col.

3

Enters Bits 8

and

9.

Check

Logics.

Yes

1

st

Card

Load

Circui

ts

and

Reader

Operating

Correctly.

Return to

Single

Card

Programs

for

Further

Analysis.

Figure

1-1.

Program

Load-Flow

Chart

1.4

No

Program Load i ng

Shou

Id

Produce

A

Feed

Cycle

Check

Logics

No

Display

Storage

Locations 0 Through

79

and

Check

for

Data.

No

C

lear

Storage

Reset CPU

Set

Mode Switch

To

Display

Run

Small

Group

of

Ripple

Punched

Cards

into

Card

Reader by Program

Load

Interrupt

Level 0

and

4

are

Serviced

by

Hard-

ware

for 1

st

Card

and

Should

be

Off.

Check

Logics.

Analysis

of

Data

Needed

to

Determine

Cause

of

Fai

lure.

No

IAR

Incremented

to Store First

Card.

Then Reset

to

Begin

Pr09ram.

Check

Logi cs

NOTE:

If

cards

are

loaded

in

display

mode I no

processing

occurs

and

then

switching

to

single

instruction

mode

permits

stepping

through program

operction.

*NOTE:

The

illustrations

in

this

manual

have

a

code

number

in

the

lower

comer.

This

is a

publishing

con-

trol

number

and

is

not

related

to

the

subject

matter.

1.2.7

Timing

Charts

(T)

•

Contains

diagrams

depicting

the

timing

con-

ditions

of

applicable

operations.

1.

3 DIAGNOSTIC PROGRAMMING AND MACHINE

CHECK OUT

Diagnostic

programs

provide

rapid

diagnosis

of

many

system

troubles.

The

console

panel

is

useful

for

controlling

manually

entered

tests

used

when

diag-

nostic

programs

cannot

be

run.

1.

3.1

Maintenance

Diagnostic

Programs

•

The

information

on the

diagnostic

programs

presented

here

is

for

general

use

only.

Detailed

descriptions

of

the

programs

and

their

use

are

provided

with

the

programs.

The

maintenance

programming

system

was

developed

to

test

and

check,

as

completely

as

possible,

the

data

paths,

checking

circuits,

control

functions,

timing

relationships,

registers,

mechanical

adjust-

ments,

and

I/o

interaction.

The

various

programs

that

test

the

individual

machine

functions

provide

detection,

degrees

of

localization,

and

communicate

to

the

CE

those

indi-

cations

of

machine

status

which

assist

him

in

repairing

the

problem

rapidly.

1.

3.2

Program

Language

The

maintenance

program

system

is

programmed

using

the

1800/1130

standard

assembler

program

language.

The

lis

tings

follow the-

standard

assembler

program

format

and

include

comments

and

explanations

to

help

the

CE

understand

and

follow

the

program

operation.

1.

3.

3

Program

Control

Manual

control

of

the

maintenance

program

system

is

provided

as

follows:

1.

Stop

or

continue

on

error.

2.

Loop

program,

loop

routine,

loop

function,

or

loop

on

error.

3.

Bypass

or

allow

error

type

out.

4.

The

program

can

bypass

or

allow

manual

intervention

requests.

1.

3.

4

Error

Messages

and

Documentation

These

items

are

included

in

either

the

error

messages

or

documentation,

or

both.

1.

The

location

in

the

program

of

the

failing

routine

or

function.

2. The

cause

of

the

program

halt

or

error

message.

3.

The

function

or

functions

that

failed.

4. A

comparison

of

the

actual

results

to

the

expected

results.

1.

3.

5

Program

Loading

The

maintenance

programs

are

provided

on

cards

and

paper

tape

•

1.

3.6

Tests

for

Device

Interaction

The

diagnostic

monitor

has

the

facility

for

con-

trolling

up to

six

test

programs

simultaneously,

depending

on

core

size,

to

provide

overlapped

or

interaction

operation

of

devices.

1.

3.7

Operation

Modes

The

maintenance

programs

are

designed

to

run

in

one

of

two

modes,

independent

mode

or

dependent

mode.

1.

3.

7.1

Independent

Processor

Tests

These

programs

assume

complete

control

of

the

system

and

run

independently

of

any

other

program.

All

I/o

functions

and

interrupt

controls

are

handled

within

the

program.

Errors

are

indicated

by

error

halts

which

are

described

in

the

documentation.

Function

Tests:

These

tests

are

engineered

specifi-

cally

to

exercise

and

evaluate

each

of

the

functions

of

the

system.

The

function

tests

are

designed

to

provide

thorough

fault

detection

(data,

sequence

and

inter-

action

related

problems

may

not

necessarily

be

de-

tected

by

a

function

test),

with

short

run

time

and

minimal

program

size.

These

programs

use

the

building

block

approach,

that

is,

the

simplest

instruction

is

tested

first

and

no

instruction

is

used

to

test

another

instruction

until

it

has

been

fully

tested

itself.

The

procedures

for

running

the

tests

are

given

in

the

CPU

test

index

in

the

test

documentation.

1.5

Tests

included

in

the

independent

mode

are:

1.

CPU

function

test

2.

Core

storage

function

test

3.

Core

storage

adjustment

test

4.

Basic

diagnostic

loader

5. One

card

diagnostic

programs

(7)

6.

Program

load

manual

tests

7.

Interrupt

test

The

program

load

manual

tests

are

used

when

none

of

the

other

function

tests

will

load.

To

diag-

nose

this

type

of

trouble,

the

CE

must

use

the

test

facilities

provided

on

the

console.

To

optimize

his

performance

in

the

use

of

these

facilities,

a

pro-

gram

load

diagnostic

guide,

in

the

test

documen-

tation,

has

been

developed.

Instructions

are

entered

one

at

a

time

through

the

bit

switches

and

the

instruc-

tion

operation

can

be

evaluated

by

the

CE.

1. 3. 7. 2

Monitor

Controlled

I/o

Tests

These

programs

run

under

control

of

the

diagnostic

monitor

and

may

be

over

lapped.

Errors

are

indi-

cated

by

error

messages

printed

out

on

the

1131

Console

Printer.

All

I/O

programs

run

under

control

of

this

monitor.

Under

this

control,

programs

can

be

run

one

at

a

time,

run

in

a

predetermined

sequence,

Program

1.

Monitor

2.

CPU

function

test

3.

Core

storage

function

test

4.

Disk

storage

function

test

5.

Disk

initialization

program

6.

1132

function

test

7.

1442

function

test

8.

1442

timing

test

9.

Paper

tape

function

test

10.

1627

function

test

11.

Console/keyboard

printer

function

test

12.

Core

adjustment

test

13.

Meter

test

14.

Basic

diagnostic

loader

15.

One

card

diagnostic

programs

16.

Program

load

manual

test

17.

Interrupt

function

test

18.

Maintenance

routines

1.6

or

run

simultaneously

in

any

combination,

except

as

limited

by

core

size.

Two

versions

are

available;

card

and

paper

tape.

Program

selection

is

via

the

bit

switches.

This

program

controls

the

I/o

function

tests

and

incorporates

the

functions

of

housekeeping,

program

loading

and

execution,

interrupt

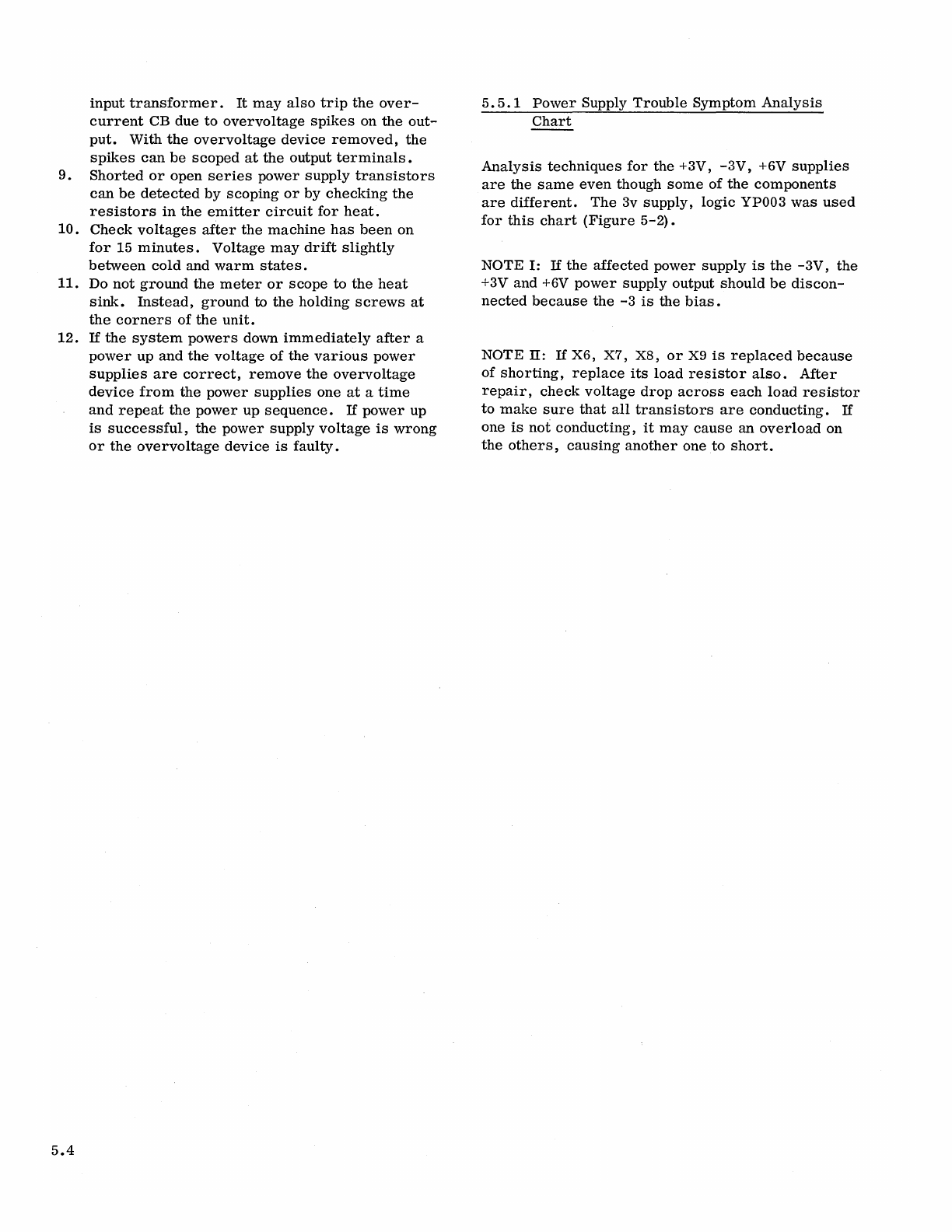

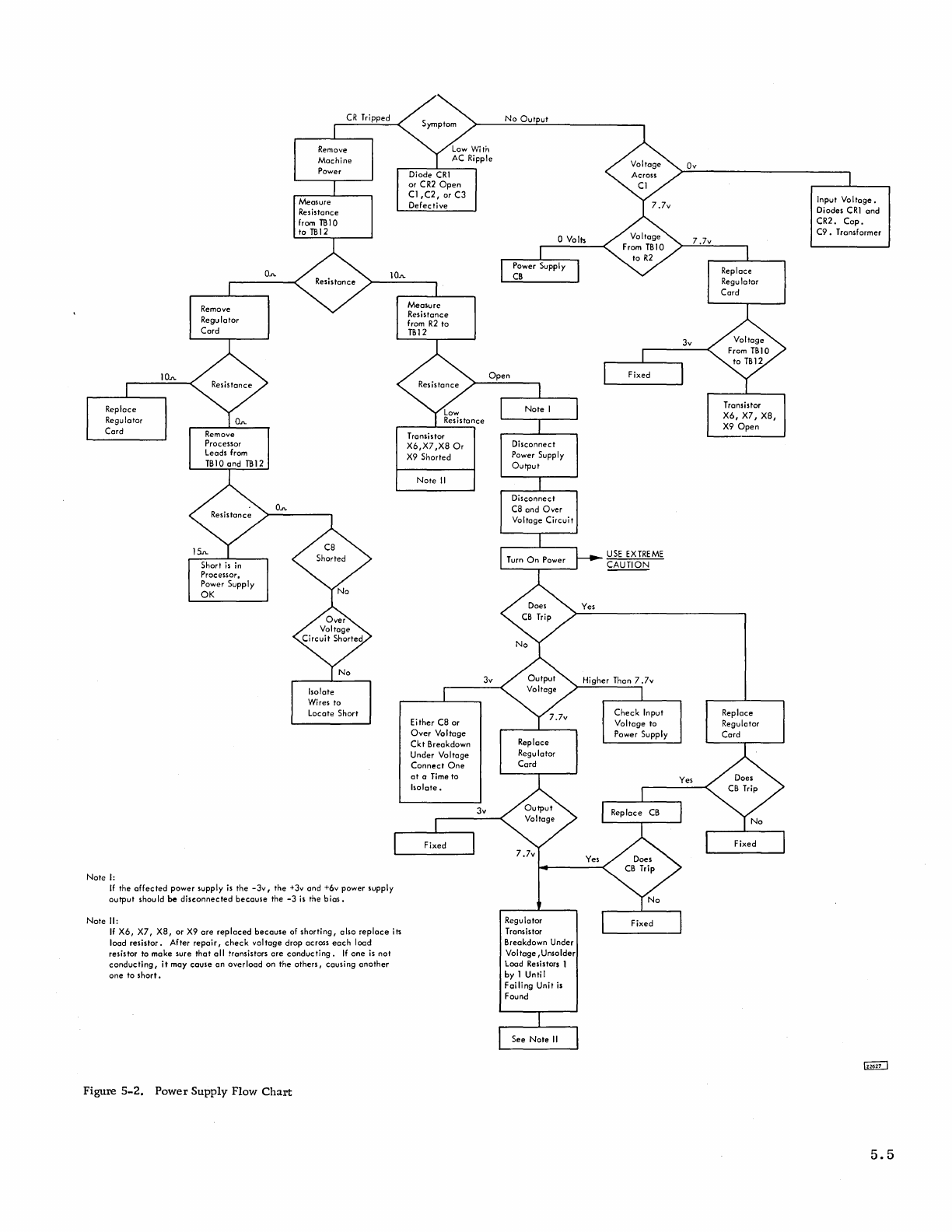

handling,

error

handling

and

customer

engineer

communi-

cation,

such

as

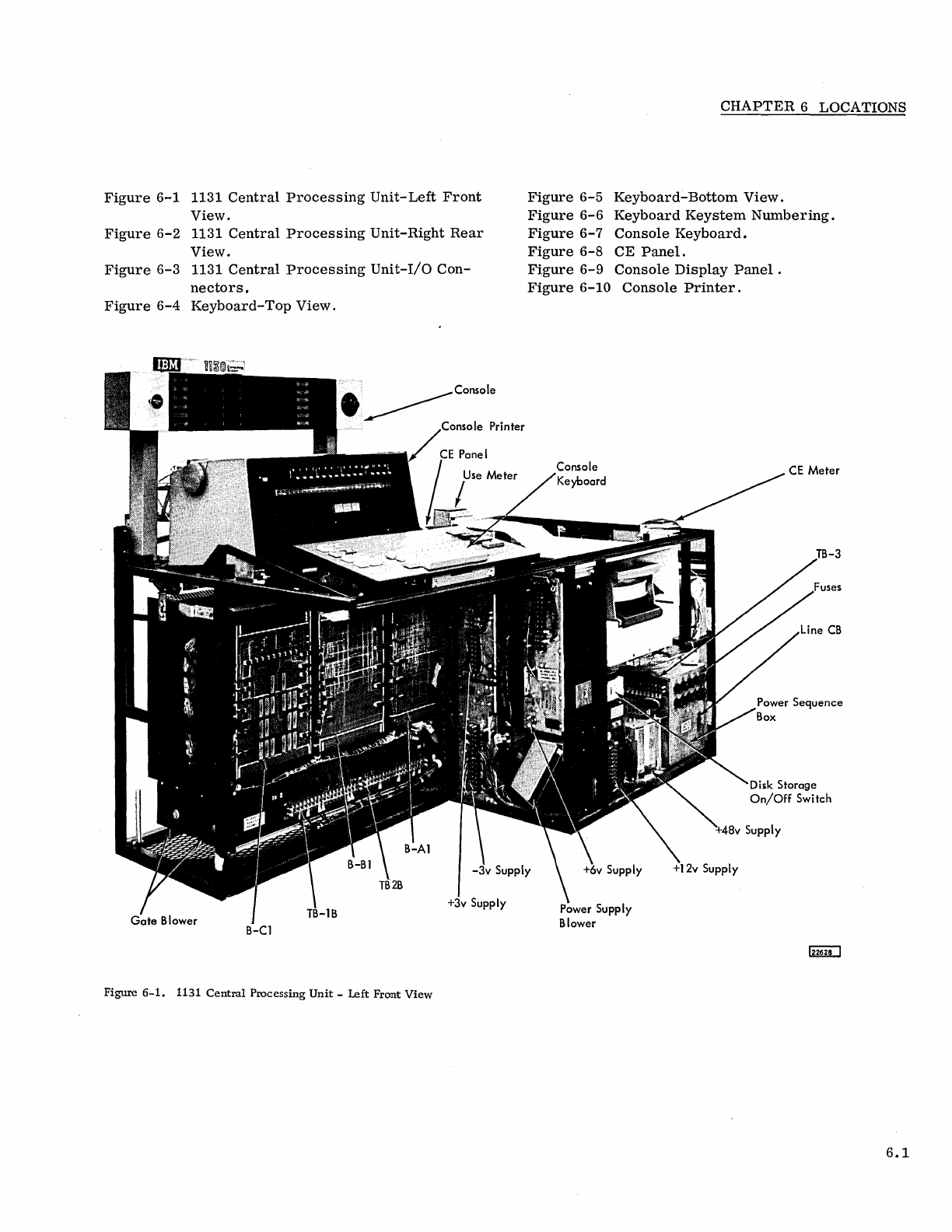

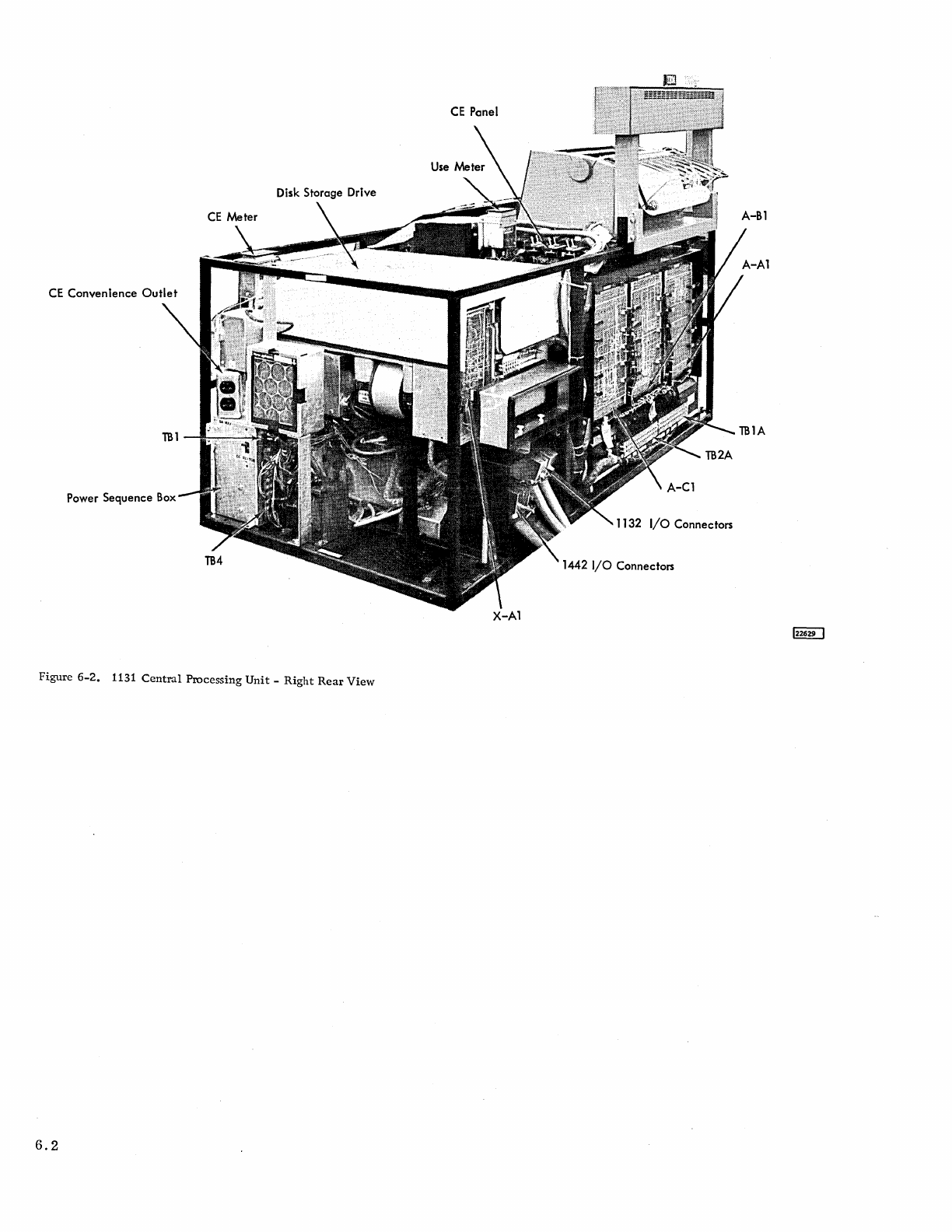

printouts.

The

documentation

pro-

vides

an

I/O

monitor

test

index

to

aid

in

running

these

tests.

The

following

programs

are

provided:

1.

Paper

tape

reader/punch

function

test

2. 1131

Console/keyboard

function

test

3. 1132

function

test

4. 1442

function

test

5. 1442

timing

test

6. 1627

function

test

7.

Disk

storage

function

test

8.

Disk

initialization

program

1. 3.

7.

3 1130

Maintenance

Diagnostics

Part

Numbers

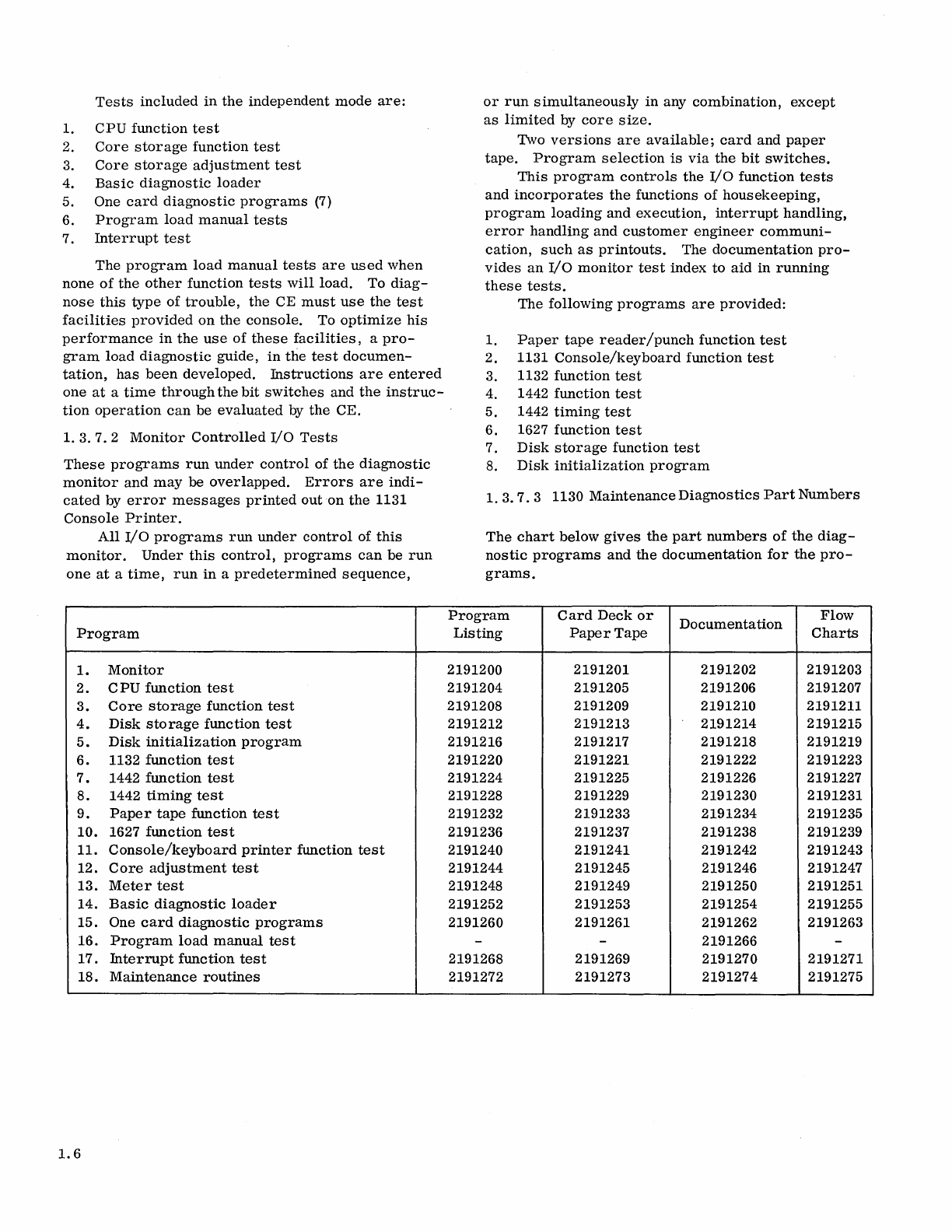

The

chart

below

gives

the

part

numbers

of

the

diag-

nostic

programs

and

the

documentation

for

the

pro-

grams.

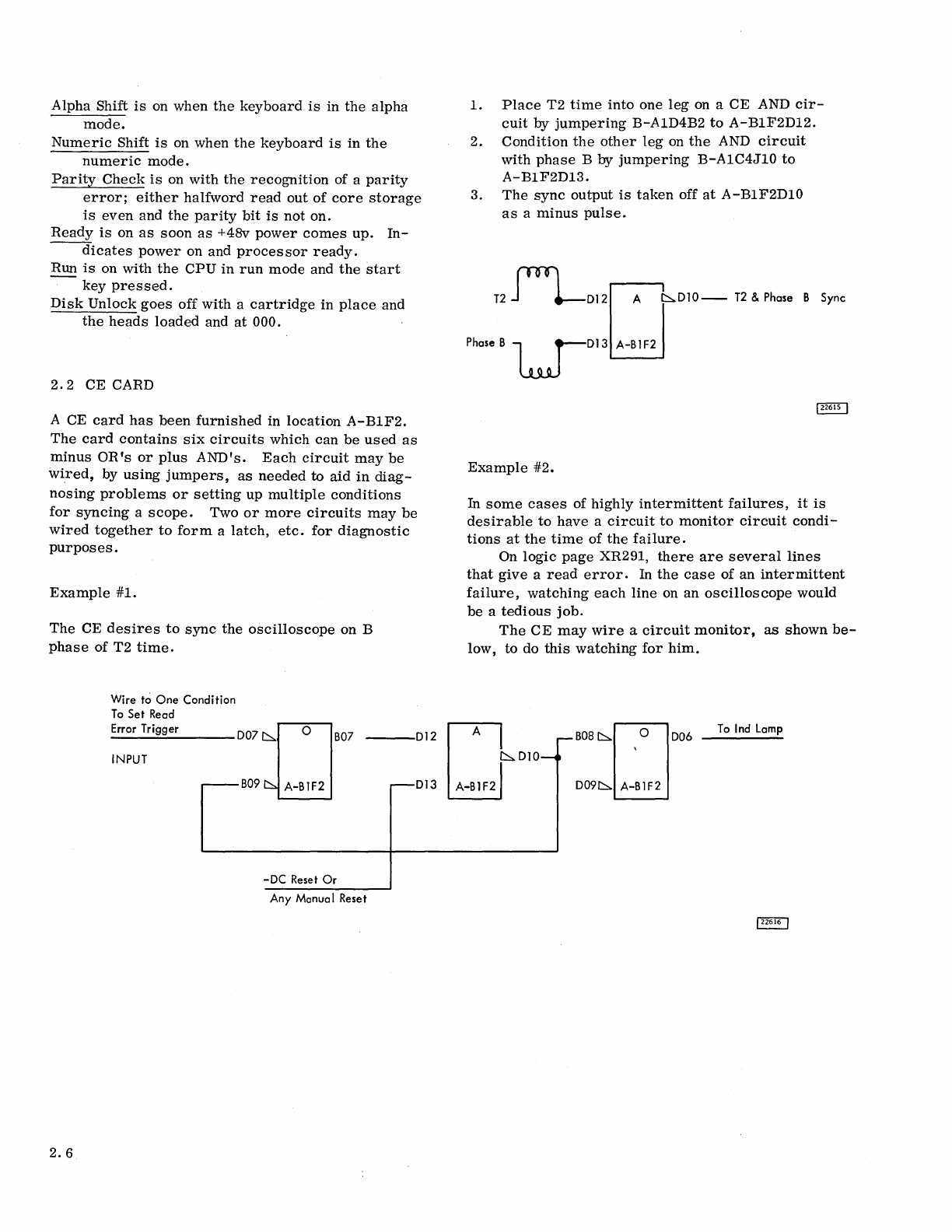

Program

Card

Deck

or

Documenta

tion

Flow

Listing

Paper

Tape

Charts

2191200

2191201

2191202 2191203

2191204 2191205 2191206 2191207

2191208 2191209 2191210 2191211

2191212 2191213 2191214 2191215

2191216 2191217 2191218 2191219

2191220 2191221 2191222 2191223

2191224 2191225 2191226 2191227

2191228 2191229 2191230 2191231

2191232 2191233

2191234

2191235

2191236 2191237 2191238 2191239

2191240 2191241 2191242 2191243

2191244 2191245 2191246 2191247

2191248 2191249 2191250 2191251

2191252 2191253 2191254 2191255

2191260 2191261 2191262 2191263

- - 2191266 -

2191268 2191269

2191270

2191271

2191272 2191273

2191274

2191275

1.

4 SERVICE CHECK LIST

1.

4.1

General

Information

1.

On

what

operation

does

the

machine

fail?

a.

Diagnostic

test.

b.

Customer

work

(Fortran,

etc.)

c.

Op

code

during

which

failure

occurred.

2-.

What

is

the

frequency

of

error?

a.

Time

of

day.

b.

Environment

(temperature,

etc.)

c.

Does

customer

power

fluctuate

at

certain

time

of

day?

(welder,

heavy

machinery,

etc.

)

1.

4.

2

General

Check

List

1.

Have

connectors

and

cards

been

checked

for

looseness

or

for

bent

contacts?

a.

Edge

connectors

b.

Laminar

bus

(pins

and

terminals)

c.

TB

connectors

(power

supply,

power

sequence,

etc.)

2.

Have

grounds

been

checked?

(1.

9.

1)

a.

DC

isolated

ground

b.

AC

isolated

ground

c.

Ground

straps

(check

contact

from

the

gate

to

the

frame)

3.

Have

power

supplies

been

checked?

a.

Voltage

levels

b.

Ripple

4.

Have

fans

and

blowers

been

checked?

a.

Power

supply

fans

b.

Gate

fans

and

blowers

5.

Does

the

machine

fail

on

margins?

a.

Normal

margins

± 4%.

1.

4.

3

Core

Storage

Check

List

1.

Which

lights

are

on?

2.

Has

indicator

lamp

test

switch

been

checked?

3.

What

is

the

pattern

of

the

failure?

a.

Greater

or

less

than

4K; odd

or

even,

etc.

b.

Picking

or

dropping

bits

-

c.

What

bits

are

affected?

4.

Is

the

trouble

in

B

register

rather

than

core

storage?

5.

Core

storage

air

flow

correct?

6.

Has

component

substitution

been

tried?

7.

Have

the

sense

lines

been

scoped?

WARNING:

Use

an

insulated

probe

tip

when

scoping

core

as

shorts

in

the

core

area

can

damage

the

core

array.

When

adjusting

pots

in

the

core

circuits,

use

the

plastic

alignment

screw

driver,

part

460811,

to

avoid

shorting

to

other

cards.

Adjustments

of

the

core

storage

timings

and

voltages

should

not

be

changed

until

proven

to

be

out

of

tolerance.

1.

4.

3.1

Solid

Core

Failure,

Limited

Area

of

Failure

1.

Record

mode

of

failure.

a.

Bit

pickup

or

drop

out.

b.

Addressing

failure.

2.

Record

pattern

of

failure.

a.

Build

table

of

failures.

b.

If

Y

drive

line

is

open,

replace

cards.

c.

If X

drive

line

is

open,

replace

cards.

d.

Make

continuity

check

for

open

drive

or

sense

lines.

e.

C

heck

diodes

on

array.

f.

Remove

array

and

check

welds,

and

wires

visually.

g. If

core

is

bad,

replace

array.

1.

4.

3.

2 Solid

Core

Failure,

General

Failure

1.

All

addresses

or

all

bits

a.

Tum

on

the

storage

load

CE

switch.

b.

Tum

on

all

bit

switches.

c.

System

cycles

through

all

of

core

and

tries

to

enter

all

bits.

d.

Check

SLT

voltages

to

core

(-Iii, +3,

-3).

e.

Check

+12v

and

output

of

regulator

voltage

at

8.5v.

1.

Adjust

voltages

if

out.

2.

Replace

regulator

cards.

Note: Do

not

replace

regulator

cards

if

the

output

is

ground,

as

the

new

card

will

be

shorted

out.

f.

Check

timing

signals

1.

Read/Write,

long

time,

short

time,

strobe,

emitter

strobe.

g.

Check

V

reference

and

VSA

voltages.

h.

Check

X

and

Y

current

by

scoping

voltage

test

points.

1.7

1. 4. 3. 3

Core

Failure,

Intermittent

1.

Check

SLT

voltages

to

core

(+6,

+3,

-3).

2.

Check

+

12v

and

output

of

regulator

voltage

at

8. 5v.

3.

Check

timing

signals.

4.

Check

V

reference

and

VSA

voltages.

5.

Check

X

and

Y

current

by

scoping

voltage

test

points.

1. 4. 4

Addressing

Failure

Check

List

Addressing

failures

can

be

very

elusive,

due

to

the

branching,

indirect

addressing,

and

effective

addressing

features

of

the

CPU.

This

list

will

help

the

CE

isolate

such

failures.

1.

Record

all

console

indications

of

the

failure

(IAR, M

register,

and

B

register).

2.

If

cycle

steal

addressing

trouble

is

suspected,

it

may

be

necessary

to

statically

check

the

addressing

circuits.

The

CE

indicators

can

be

wired

to

help

evaluate

the

addressing

circuits.

3.

Using

the

core

service

techniques,

try

to

eval-

uate

whether

the

trouble

is

in

core

storage

or

in

the

addressing

circuits.

4.

Trace

routines

us

ing

the

interrupt

run

mode

of

operation

should

be

considered.

A

simple

routine

which

stores

the

IAR

and

returns

to

the

mainline

program

on

any

branch

or

instruction

is

helpful

to

see

how

far

the

program

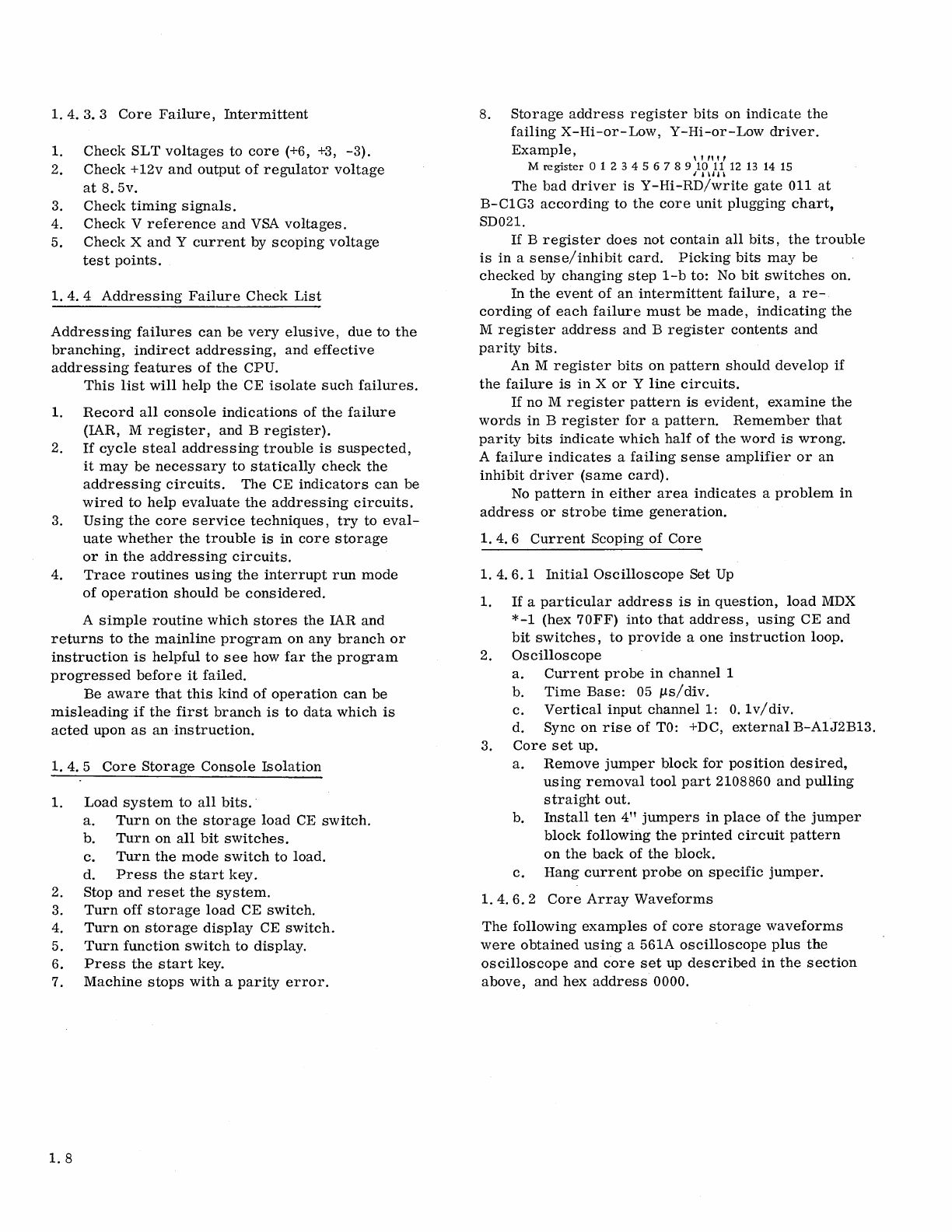

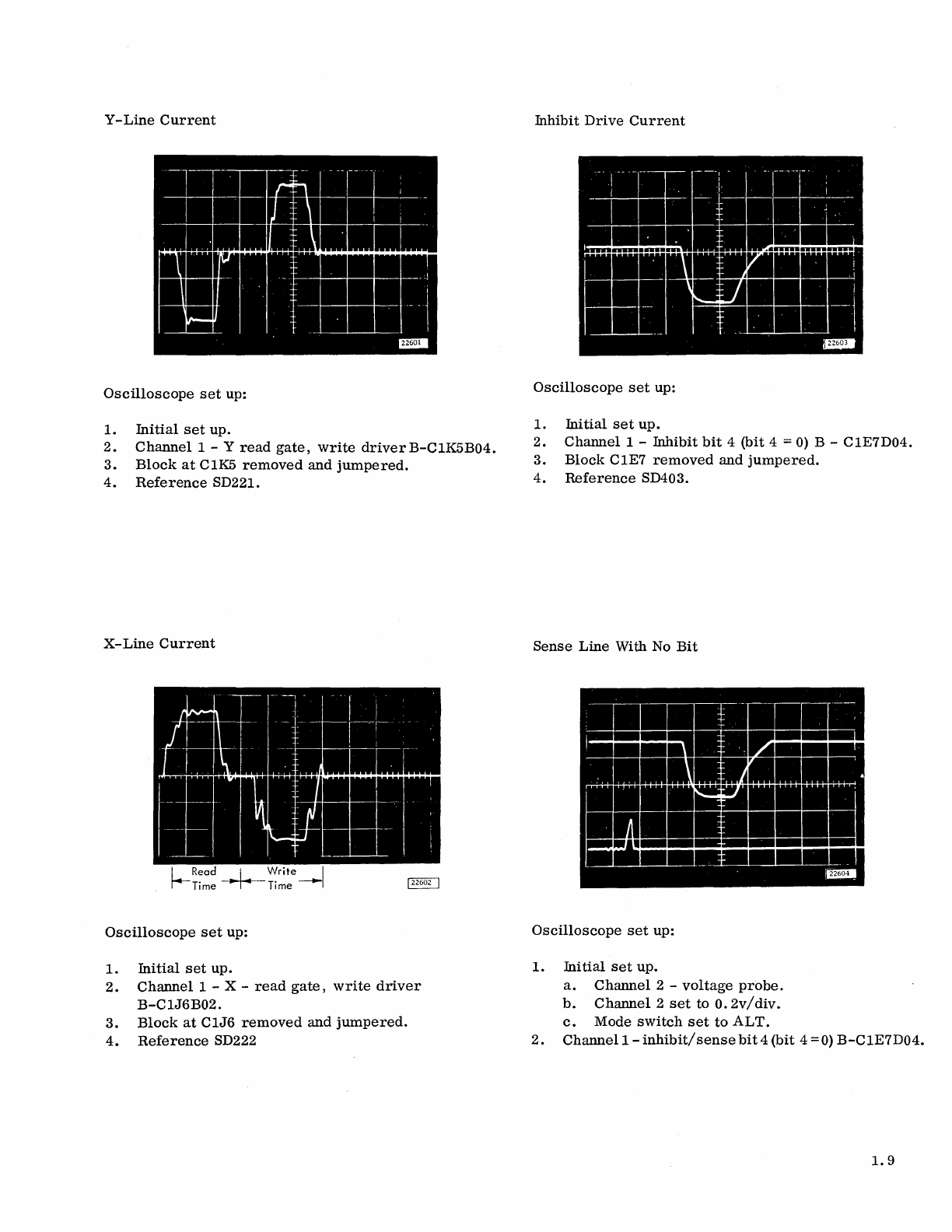

progressed