700925_PDP 1140_Technical_Memo_ 700925 PDP 1140 Technical Memo

User Manual: 700925_PDP-1140_Technical_Memo_

Open the PDF directly: View PDF ![]() .

.

Page Count: 22

COMPANY

CONFIDENTIAL,

This

drcl\~i~;~

an1.srteciffcaticns. herein. are the

pro,.

,

erty

of Olgl.a'

Equ'~en~

Corporation

and

shajl

flO'

w;

repr2d~ce-!

or

conic'

or

used in

w~~~

01

in r:art

,as'

th~

·.as s

'or

~:'.e

.'

:,-lOu;aeture

or

sa:~

:>1

items w!thout

written

pel;i~is~:o!l.

TITLE:

PDP-1I!40

TECHNICAL

HEMO

INDEX & ABSTRACTS

PDP-ll!40

Tech

Memo

#1

AUTHOR:

DATE:

.

REVISION:

INDEX KEY:

Dick

Clayton

September

25,

1970,

None

Index

Abstract

pages

OBSOLETE:

DISTRIBUTION KEY:

PDP-Il!40

Group

PDP-11!20

Group

PDP-II

CoordilLating

Committee

PDP-Il

Master

List

ABSTRAC'J:

None

This

memo

consists

of

the

Index,

the

Abstract;

and

'the

Alphabetical

Cross-Reference

of

Jndex

Keys

for

all

PDP-ll!40

Technical

Memos.

Copies

of

individual

memos

are

attainable

from

the

secretary

of

the

~DP-ll/40

Engineering

Group,

Doris

Covey,

as

of

the

writing

of

this

memo.

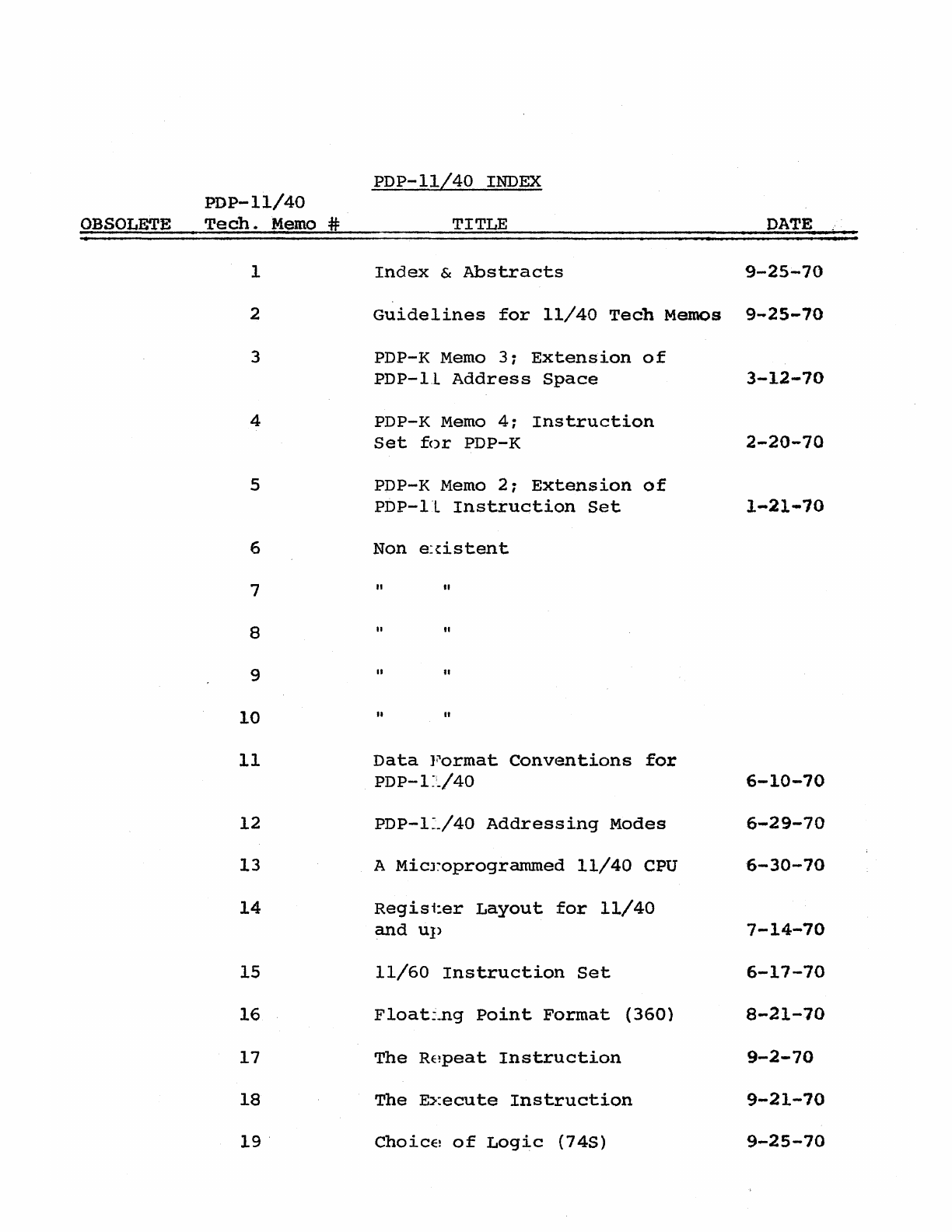

OBSOLETE

PDP-11/40

Tech.

Memo

#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

.

PDP-11/40

INDEX

TITLE

DATE,

Index

&

Abstracts

9-25-70

Guidelines

for

11/40

Tech

Memos

9-25-70

PDP-K

Memo

3;

Extension

of

PDP-LL

Address

Space

3-12-70

PDP-K

Memo

4;

Instruction

Set

for

PDP-K

2-20-70

PDP-K

Memo

2;

Extension

of

PDP-II

Instruction

Set

1-21-10

Non

e:{istent

II

"

"

II

II

"

II

"

Data

]i'ormat

Conventions

for

PD

P-l

~:./

40

PDP-l:./40

Addressing

Modes

A

Microprogrammed

11/40

CPU

Regisi:er

Layout

for

11/40

and

up

11/60

Instruction

Set

Float:.ng

Point

Format

(360)

The

RE~peat

Instruction

The

Execute

Instruction

ChoiCE!

of

Logic

(74S)

6-10-70

6-29-70

6-30-70

7-14-70

6-17-70

8-21-70

9-2-70

9-21-70

9-25-70

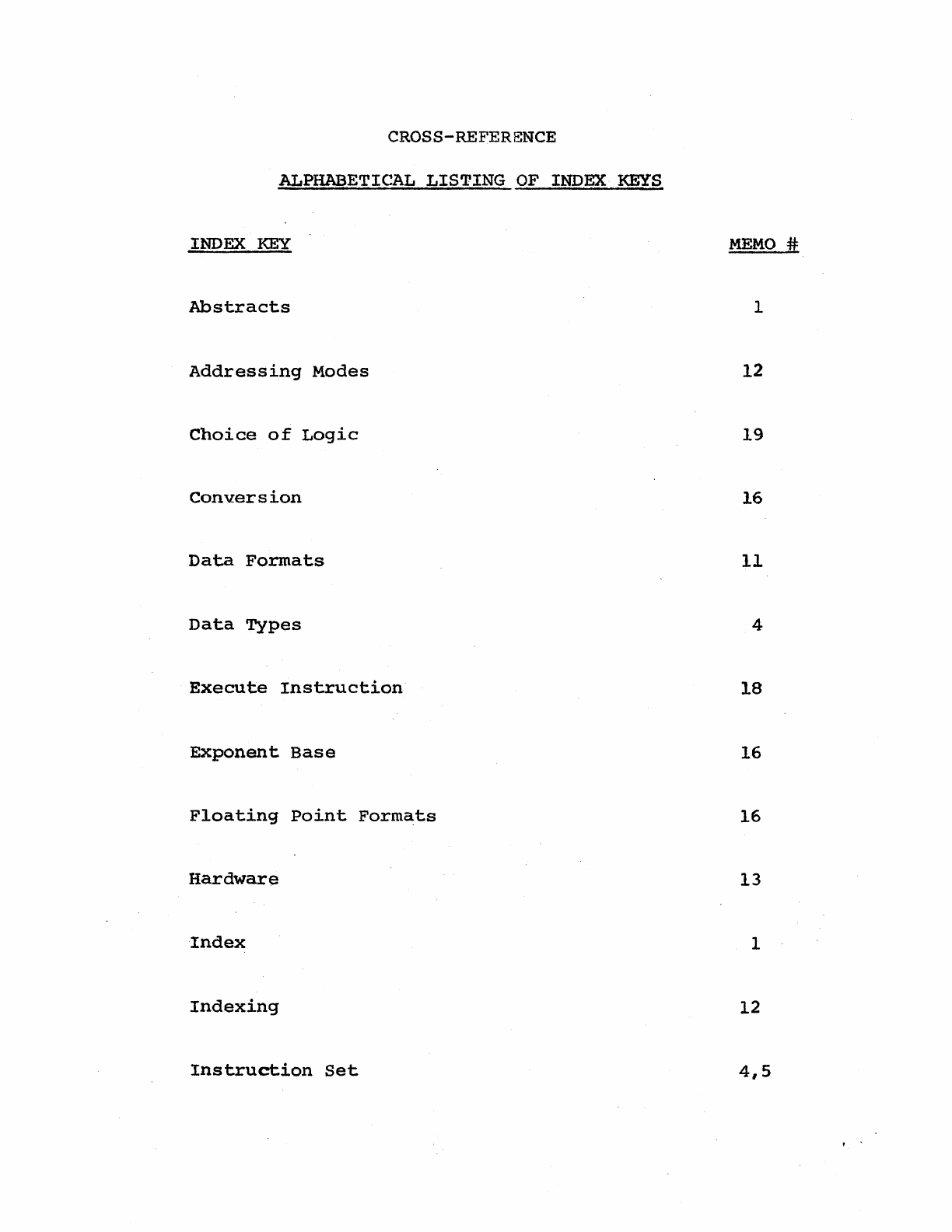

CROSS-REFERE!NCE

ALPHABETICAL

LISTING

OF INDEX

KEYS

INDEX

KEY

Abstracts

Addressing

Modes

Choice

of

Logic

Conversion

Data

Formats

Data

Types

Execute

Instruction

Exponent

Base

Floating

Point

Formats

Hardware

Index

Indexing

Instruction

Set

MEMO

it

1

12

19

16

11

4

18

16

16

13

1

12

4,5

, ,

.(

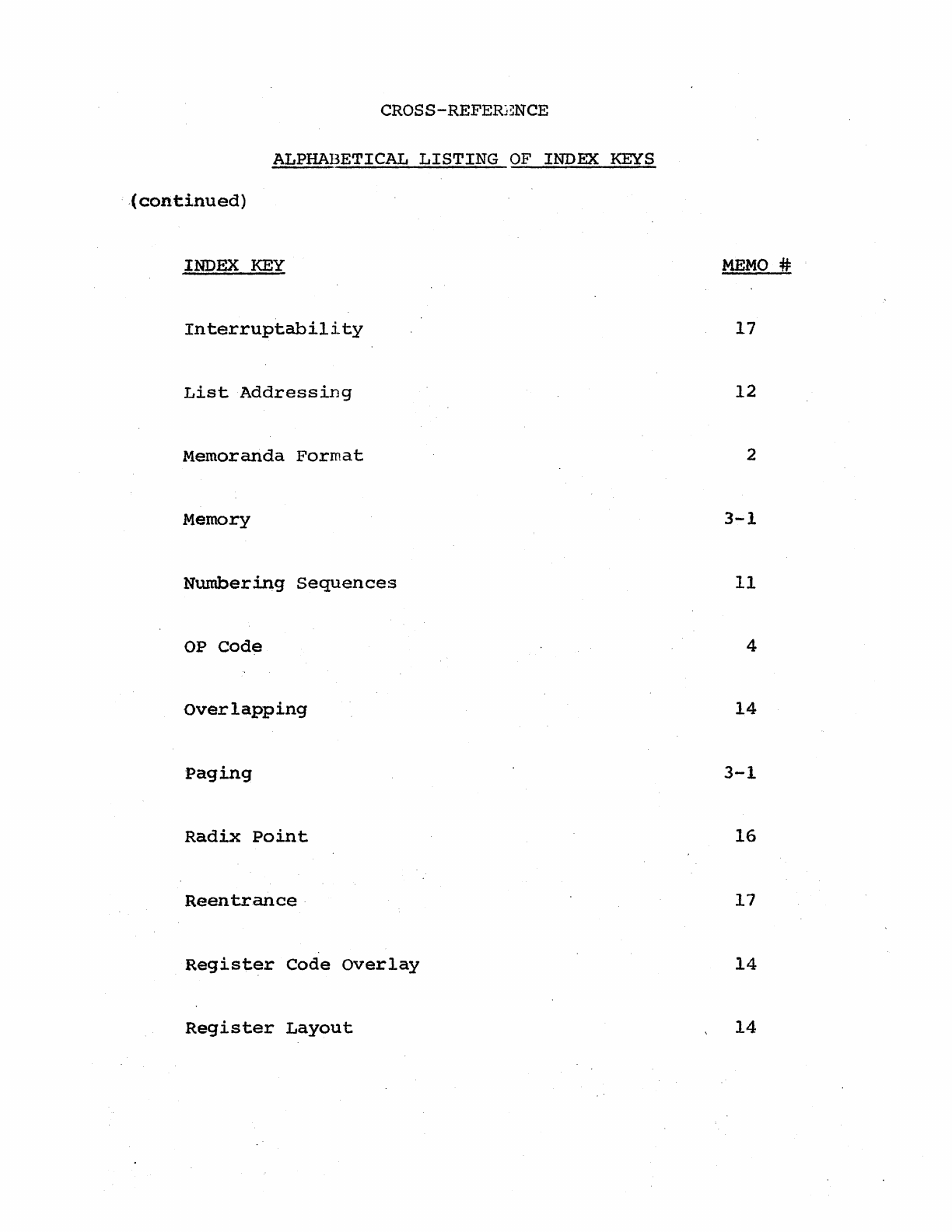

continued)

CROSS-

REFERj~NCE

ALPHABETICAL

LISTING

OF

INDEX

KEYS

INDEX KEY

Interruptability

List

Addressing

Memoranda

Format

Memory

Numbering

Sequences

OP

Code

Overlapping

Paging

Radix

Point

Reentrance·

Register

Code

Overlay

Register

Layout

MEMO #

17

12

2

3-1

11

4

14

3-1

16

17

14

14

(continued)

CROSS-REFEFENCE

ALPH1\BETICAL

LISTING

OF

INDEX

KEYS

INDEX

KEY

Repeat

Conditions

Repeat

Count

Resumption

Segmentation

Technical

MemJranda

MEMO

#

17

17

17

3-1

2

TITLE:

GUIDELINES

FOR

PDP-ll!40

TECHNICAL

MEMORANDA

PDP-ll!40

Tech

Memo

#2

AUTHOR:

Dick

Clayton

DATE:

September

25,

1970,

L

pages

REVISION:

None

OBSOLETE:

INDEX

KEY:

Technical

Memoranda

Memoranda

Formats

Format

DISTRIBUTION

KEY:

PDP-ll!40

Grcup

PDP-ll!20

Grcup

None

PDP-II

Coordjnating

Committee

ABSTRAC'l

This

memo

describes

the

conventions

and

purposes

of

the

PDP-ll!40

Technical

Memoranda

Set.

Suggested

formats

and

distributions

arE

presented.

TITLE:

EXTEN:3ION

OF

PDP-II

i\DDRESS SPACE

PDP-ll/40

Tech

Memo

#3

(PDP-K

Tech

Memo

#3-1)

AUTHOR:

DATE:

REVISION:

Robert

Gray

March

12,

1970,

I

INDEX

KEY:

Memory

paging

Segmentation

DISTRIBUTION

KEYS~

23

pages

OBSOLETE:

TECH

MEMO

#3

ABSTRAC

r

_'

This

memo

.discusses

the

limited

address

space

in

the

PDP-II

architecture.

The

PDP-ll

I6-bit

processor

can

address

a

maximum

of

32K

(indirect

or

indexed)

16-bit

words.

A

32-bit

version

of

the

.

PDP-II

could

address

16K

32-bit

\lords.

This

aspect

of

the

present

PDP-I:.

architecture

is

examined

as

a

potential

problem

in

larger

versions

(32-bits)

of

a

proposed

PDP-II

family.

The

16K

limit

is

compared

with

medium

size

computers

offered

by

other

nanufacturers.

It

is

also

compared

with

the

expected

user

J"equirements

of

machines

in

this

performance

category.

Fina~

ly,

this

memo

discusses

briefly

the

limit

and

advantages

of

two

possible

memory

ex-

pansion

techniques:

paging

and

~,egmentation.

It

is

concluded

that

the

16K

lim:-t

in

a

32-bit

PDP-li

would

be

a

severe·

competitive

handicap.

It

is

further

concluded

that

neither

paging

nor

segmenta1:ion

offers

an

efficient

way

to

run

procedures

that

exceed

16K

32-bit

words

TITLE:

PDP-K INSTRUCTION

SEr

PDP-ll/40

Tech

Memo

#4

AUTHOR:

DATE:

REVISION:

Ad

van

de

Goor

Febru~ry

20,

1970,

None

INDEX KEY:

InstrAction

Set

OP

Cole

Data

rypes

DISTRIBUTION KEYS:

32

pages

OBSOLETE:

ABSTRAC':1

None

An

instruction

set

fo]:'

an

18-bit

computer

l

is

proposed.

It

combines

theb~st

features

of

the

.,)DP-ll's

architecture

and

the

PDP-lOIs

instruction

set.

For

several

reaso."lS,

an

IS-bit

~()mputE~r

was

considered

superior;

it

solves

both

the

OP

code

and

address

space

problems

of

a

16-'oit

computer.

In

addition,

it

is

a

better

data

base

in

two

importan1:

areas.

Pulse

Height

Analysis

(PHA)

programs

hav,e

proven

the

need

'for

IS

bits.

Also,

the

36-bit

floating

point

representation

has

much

wider

acceptance,

due

to

its

supuriority

of

32-bit

formats.

1

i.e.,

a

computer

with

a

word

lE~ngth

of

IS-bits.

TITLE:

Extension

of

PDP-II

Instruction

Set

PDP-ll/40

Tech

Memo

#5

(PDP-K

Tech

Memo

#2)

AUTHOR:

Ad

van

de

Goer

DATE:

January

21,

1970,

24

pages

REVISION:

NONE

OBSOLETE:

NONE

INDEX XEYS:

Instruction

Sets

OP

Code

SpacE

Modes

Stack

Operatjons

DISTRIBUTION

KEYS:

1\BSTRACT

This

PDP-K

Memo

(#2)

desclibes

4

nethods

of

expanding

the

instruction

set

of

the

PDP-II.

They

are:

a)

Stack

instructions;

opera.nds

are

picked

up

from

and

results

returned

to

the

stack.

b)

Flag

word

instruc~tions:

A

single

instruction

indicates

that

the

instruction

space

is

to

extend

to

the

next

word.

This

allows

at

least

16-bits

free

for

new

instruction.

c)

Mode:

a

mode

bit

control::;

the

decoding

of

instruction

to

bo

from

one

of

two

sets.

d)

Use

of

Mul/Divid(~

space:

use

the

remaining

two

undefined

11/20

OP

code

spaces

for

new

instructions.

The

Mul/Divide

solution

(d)

appea::-s

to

be

preferable.

TITLE:

DATA

PORMA.T

CONVENTIO:~S

FOR

PDP-ll/40

PDP-ll/40

Tech

Memo

#11

AUTHOR:

Ad

van

de

Goer

DATE:

June

10,

1970,

6

pages

REVISION:

None

OBSOLETE:

None

INDEX

KEYS:

Data

Formats

Numbering

Sequences

DISTRIBUTION

KEYS:'

PDP-I1

Coordinating

Committee

PDP-l1/40

Grou.p

Alan

Kotok

Richerd

DeMorgan

ABSTRAC'I

This

memo

is

concnrned

with

certain

data

formats

being

proposed

for

the

PDP-ll/40.

It

is

proposed

that

multiple

word

data

be

stored

as

most

significant

data

before

least

significant

data.

The

proposed

formats

have

the

property

of

being

compatible

with

what

is

considered

standard

in

the

computer

industry,

and

people's

jntuition.

It

is,

however,

not

compatible

with

some

PDP-ll/~O

software

conventions.

The

masons

for

the

proposed

PDP-]

1/40

formats

are

given

.

together

with

guidelines

for

futlre

decisions.

Although

issue

is

taken

with

the

bit

and

l:yte

numbering

schemes

used

in

the

PDP-ll/20,

it

is

prolosed

that

these

remain

unchanged

because

of

hardware

an(

documentation

reasons.

TITLE:

PDP-11!40

ADDRESSING

MODES

PDP-Il!40

Tech

Memo

#12

AUTHOR:

Ad

van

de

Goor

DATE:

REVISION:

June

29,

1970,

7

pages

None

OBSOLETE:

None

INDEX KEYS:

Addressing

Modes

Indexing

List

Addressing

DISTRIBUTION KEYS:

PDP-II!40

Gre.up

PDP-li

Coordjnating

Dave

Knight

Ron

Brender

Jeff

Scott

ABSTRAC'l

Bruce

Delagi

Com.

Larry

McGowan

Jim

Bell

Jack

Richardson

The

auto

decrement

deferred

mode

II@-(R)"

as

implemented

on

the

PDP-II/20

has

been

found

to

he

of

very

little

use.

In

all

the

PDP-II

programs

the

author

has

seen,

it

has

been

used

only

twice.

Three

alternative

addressing

modos

are

discussed

to

replace

the

II@-(R)

II

mode.

·It

is

concluded

that

the

adjusting

index

mode

II

(R)A"

was

the

most

promising.

The

adjusting

index

mode

II(R)AII

is

very

similar

to

the

regular

index

mode

"A(R)

II

except

for

the

computation

of

the

effective

address

ilEA".

For

A(R),

the

EA

is:

EA=

(R) + A

For

(R)A,

the

EA

is:

EA= A + L * (R)

where

L=

length

of

data

in

bytes

TITLE:

A

Microprogrammed

11/40

CPU

PDP-ll/40

Technical

Memo

#13

AUTHOR:

DATE:

REVISION:

Rony

Elia-Shaoul

June

30,

1970,

14

pages

None

INDEX KEYS:

Hardware

DISTRIBUTION

KEYS: Ad

van

de

Goor

Dennis

O'Connor

Joe

Mangiafico

Jim

Bell

Don

Vonada

OBSOLETE:

None

Bob

Gray

Dick

Lewis

Jim

Murphy

Bruce

Delagi

Gerry

Butler

An

eight

bit

microprogram

CPU

wa3

looked

into

and

was

partially

designed

and

analyzed

with

diffe::-ent

existing

components.

The

purpose

of

the

above

project

was

to

aid

us

in

arriving

at

a

valid

estimate,

as

far

as

speed,

cost,

packaging,

and

power

dissipation

for

a

microprogram

11/40

CPU

with

using

different

types

of

semiconductor

components.

The

flow

diagram

used

for

such

an

implementation

is

shown

in

Figure

1.

A

breakdown

of

each

of

,

the

sections

drawn

in

the

diagram

as

far

as

cost,

technology,

speed,

power

dissipation,

and

packaging,

is

analyzed

in

this

report.

Finally,

a

similar

estimate

on

a

micropro9ram

11/40

CPU

is

made

using

today's

components.

It

is

concluded

that

present

microprogrammed

technology

would

be

more

expensive

until

about

1972.

A

speed

penalty

of

at

least

50%

would

be

paid

by

a

microprogrammed

system.

Micro-

programming

offers

significant

advantages

in

packaging

density

and

design

flexibility.

TITLE:

REGISTER

LAYOUT

FOR

11/40

AND

UP

PDP-ll/40

Tech

Memo

#14

AUTHOR:

DATE:

REVISION:

INDEX

KEY:S

Ad

van

de

Goor

July

14,

1970,

9

pages

None

Register

Layout

Overlapping

Register-Code

Overl~y

OBSOLETE:

None

DISTRIBUTION KEYS:

PDP-ll/40

Gro~p

PDP-II

Coordi'lating

Committee

Bruce

Delagi

ABSTRACT

Because

the

11/40

might,

and

bigger

versions

of

the

PDP-II

family

will,

have

32-bit

integer

and

floating

point

arith-

metic

capabilities,

the

need

for

more

general

purpose

hardware

registers

is

quite

clea.t.

The

competition

of

the

bigger

PDF-II's

(e.g.,

PDP-ll/60)

has

typically

sixteen

32-bit

genEral

purpose

registers.

Four

methods

of

adding,

in

a

comfatible

way,

new

registers

to

the

PDP-ll/20

architecture

are

discussed.

The

last

method,

section

1.4

"The

Disjoint

Scheme"

is

preferred

because

it

has

most

of

the

advantages

and

satisfies

im-

plementation

constraints.

This

scheme

provides

six

double

word

format

registers

(32-bits,

D¢-D5)

which

are

independent

of

the

standard

single

word

format

registers.

Both

the

single

and

double

registers

overlay

core

to

allow

program

manipulation

of

their

contents.

TITLE:

PDP-Il/60

INSTRUCTION SET

PDP-11/40

Tech

Memo

#15

AUTHOR:

Ad

van

de

Goar

DATE:

June

17,

1970

REVISION:

None

INDEX KEYS:

Instructions

Data

Formats

Interrupts

OBSOLETE:

None

Instruction

Formats

Addressing

Modes

Traps

DISTRIBUTION KEYS:

PDP-II

Coordinating

Committee

11/40

Group

11/60

Architecture

Design

Review

Committee

ABSTRACr

This

memo

describes

the

proposed

In.:>dification

to

the

11/20

instruction

set

to

allow

the

creation

of

the

11/60

instruction

set.

It

is

proposed

that

BISB,

BlCB,

and

BITB

be

placed

in

a

two

word

"flagged"

form

of

instrilction

and

that

the

instruc-

tion

set

be

expanded

using

this

and

the

Mul/nivide

space.

The

memo

covers

modification

of

the

addressing

modes,

multiple

word

arithmetic

instruction,

multiple

shift

instruction,

floating

point

instructions,

and

11/20

instructions.

paging

and

segmentation

are

not

covered

and

are

deferred

to

a

future

memo.

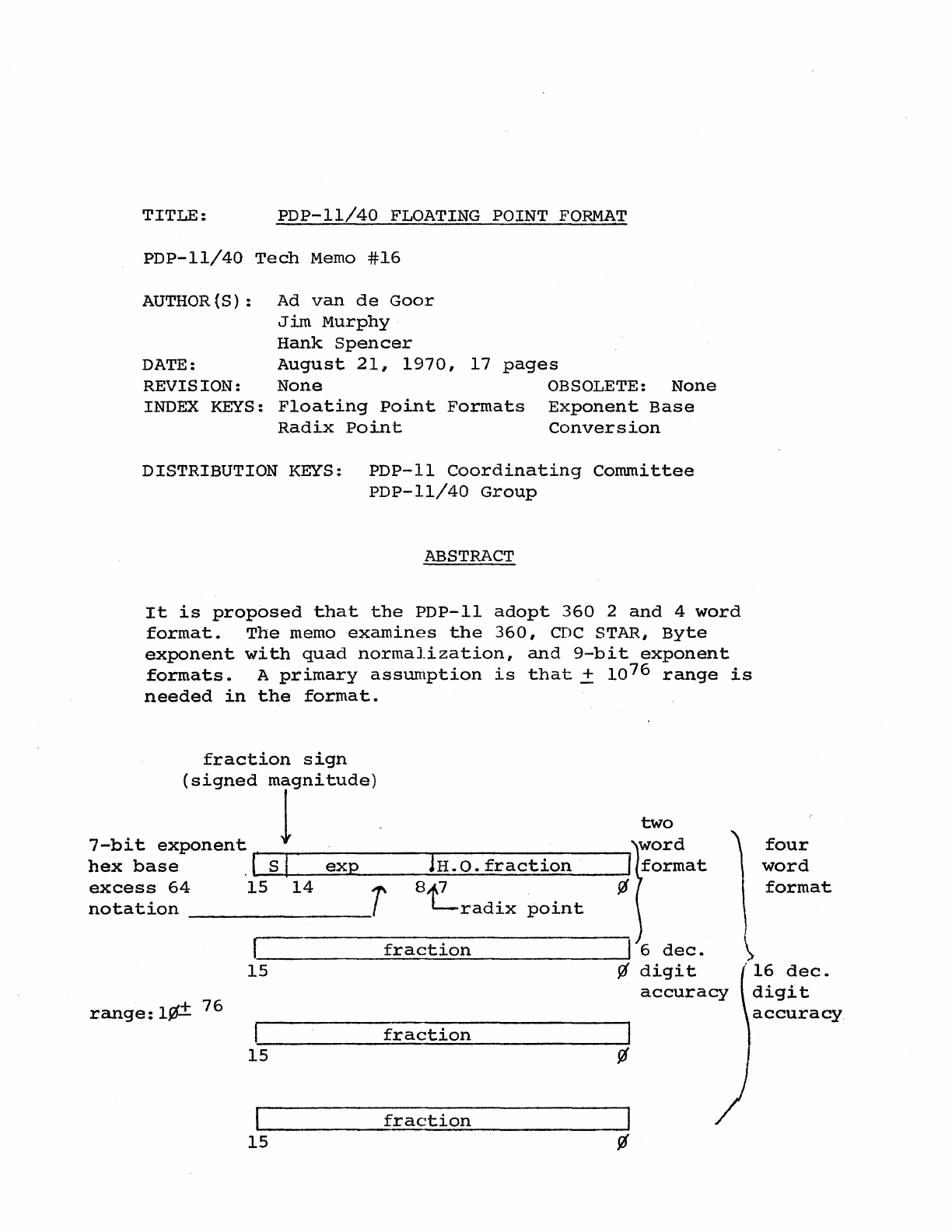

TITLE:

PDP-11/40

FLOATING POINT

FORMAT

PDP-11/40

Tech

Memo

#16

AUTHOR(S):

Ad

van

de

Goor

Jim

Murphy

Hank

Spencer

DATE:

August

21,

1970,

17

pages

REVISION:

None

OBSOLETE:

None

INDEX

KEYS:

Floating

Point

Formats

Exponent

Base

Radix

Point

Conversion

DISTRIBUTION KEYS:

PDP-11

Coordinating

Committee

PDP-ll/40

Group

ABSTRACT

It

is

proposed

that

the

PDP-II

adopt

360

2

and

4

word

format.

The

memo

examines

the

360,

CDC

STAR,

Byte

exponent

with

quad

normalization,

and

9-bit

exponent

formats.

A

primary

assumption

is

that

+

10

76

range

is

needed

in

the

format.

fraction

sign

(signed

mrgnitude)

two

7-bit

exponent

_--.--------,...----------.,

word

hex

base

.1

S I

exp

lH.

O.

fraction

I

excess

64

15

14

r

8~7

¢

notation

________________

L-radix

point

,

___________

~f~r_a_c~t~i~o~n~

___________

~1

6

dec.

four

word

format

15

fi

digit

'16

dec.

range:

l¢±

76

fraction

15

fraction

15

accuracy

digit

accuracy.

)

TITLE:

THE

REPEAT INSTRUCTION

PDP-ll/40

Tech

Memo

#17

AUTHOR:

DATE: Ad

van

de

Goor

September

2,

1970,

11

pages

REVISION:

None

INDEX KEYS:

Repeat

Count

Resumption

Interruptability

DISTRIBUTION KEYS:

PDP-ll/40

Group

Jud

Leonard

Jeff

Scott

ABSTRACT

OBSOLETE:

None

Repeat

Conditions

Reentrance

Bruce

Delagi

Richard

DeMorgan

Jack

Burness

The

desirability

of

a

conditional

repeat

instruction

has

been

demonstrated

on

several

occasions.

The

repeat

in-

struction

provides

for

the

shortest

possible

program

loop

(namely

a

single

instruction),

besides

that

it

seems

to

have

a

big

market

appeal.

Because

this

instruction

is

considered

for

the

11/25,

the

possible

11/40

implementations

are

considered

for

compati-

bility

reasons.

The

problems

with

this

instruction

are

two-fold:

1)

How

to

implement

it,

considering

implementa-

tion

cost

and

required

OP

code

space.

2)

Which

instructions

cannot

be

repeated,

or

repeated

with

restrictions.

It

is

concluded

that

a

format

allowing

small

counts

(0-8\

to

be

specified,

within

the

instruction,

is

desirable.

Using

a

skip

technique

to

separate

end

conditions

seems

reasonable.

At

this

time

there

does

not

seem

to

be

a

clear

concensus

as

to

the

way

repeat

should

operate.

A

revision

of

this

memo,

defining

the

11/40

final

choice,

is

needed.

TITLE:

THE

EXECUTE

INSTRUCTION

PDP-ll/40

Tech

Memo

#18

AUTHOR:

Ad

van

de

Goor

DATE:

September

21,

1970,

7

pages

REVISION:

None

OBSOLETE:

None

INDEX KEYS:

Execute,

Interruptability,

Addressing

Modes

DISTRIBUTION KEYS:

PDP-ll/40

Group

PDP-ll/60

Architecture

Review

Committee

Jud

Leonard

Jeff

Scott

Richard

DeMorgan

ABSTRACT

The

use

of

the

execute

"XCT

II

instruction

is

discussed

and

from

that

an

implementation

derived.

Interruptability

considerations

resulted

in

a

non-interruptable

execute

sequence.

(This

was

the

simplest

solution

hardware

wise.

)

considerations

of

the

addressing

modes

used

by

the

XCT

in-

structions

led

to

the

rule

that

when

the

-(R),

(R)+

and

(R)A

modes

are

used,

the

instruction

to

be

executed

is

"thought

of

ll

as

being

one

l6-bit

word

long,

independent

of

the

actual

length

of

the

instruction

to

be

executed.

In

order

to

have

no

surprises

or

side

effects

in

the

instructions

to

be

executed,

the

machine

is

required

to

have

two

program

counters:

1)

The

PC,

which

is

the

regular

program

counter.

Upon

completion

of

the

XCT

sequence,

it

usually

points

to

the

instruction

following

the

XCT

instruction.

2)

The

dummy

program

counter

uDPC",

which

is

only

used

for

the

address

computation

in

the

instruction

to

be

executed.

The

only

instructions

which

canno·t

be

executed

are

Execute

-and

Repeat.

TITLE:

CHOICE

OF

LOGIC

PDP-11/40

Tech

Memo

#19

AUTHOR:

Rony

E1ia-Shaou1

DATE:

September

29,

1970,

17

pages

REVISION:

NONE

OBSOLETE:

NONE

INDEX

KEY:

Hardware

DISTRIBUTION

KEY:

Engineering

Committee

11/40

Group

11/40

General

List

ABSTRACT

The

purpose

of

this

memo

is

to

aid

us

in

our

decision

on

the

technology

to

be

used

in

the

11/40

hardware

implemen-

tation.

with

a

goal

of

200

ns

maximum

cycle

time,

for

register-to-register

instruction,

the

need

for

circuits

faster

than

the

74

hundred

and

74H

hundred

TTL

integrated

circuits

(used

in

our

present

machine)

becomes

imperative.

We

presently

have

two

choices.

The

first

one

is

the

Schottky

74S

hundred

TTL

which

is

a

fast

version

of

the

74H

hundred

series.

The

second

is

the

emitter

coupled

logic

family

(ECL)

which

is

a

non-saturated

logic.

Although

the

ECL

family

offers

an

advantage

in

speed,

the

74S

hundred

logic

has

been

chosen

in

this

memo

for

the

11/40

hardware

due

to

technical,

cost,

and

product

availability

reasons.

Those

reasons

are

discussed

with

some

detail

in

the

following

sections

of

this

memo.

djc

COMPANY

CONFIDENTIAL

TITLE:

This dra"Yil)g

an·1

.s:-,~c!f:caL:ons.

here:!'!. are the prop-

erty

01

Digital

Equ

~:··:en;

Cor"'oration and shall

nol

be

reprod,,!ced

or

cop:e" or

u-c;ed

in whole

or

in part as

the

basIs

for

the manu;ac!ure

or

saJe

of

items

without

GUIDELINES

FOR

PDP-ll/40

TECHNI~teMDM~A

PDP-ll/40

Tech

Memo

# 2

AUTHOR:

Dick

Clayton

DATE:

September

2.5,

1970,

4

pages

REVISION:

None

OBSOLETE:

None

INDEX

KEY:'

Technical

Memoranda

Memoranda

Formats

Format

DISTRIBUTION

KEY:

PDP-ll/40

Group

PDP-ll/20

Group

PDP-II

Coordinating

Committee

ABSTRACT

This

memo

describes

the

conventions

and

purposes

of

the

PDP-ll/40

Technical

Memoranda

Set.

Suggested

formats

and

distributions

are

presented.

- 2 -

I.

INTRODUCTION

Documentation

of

PDP-ll/40

will

follow

the

procedures

outlined

below

to

permit

free

flow

of

information

be-

tween

persons

having

a

legitimate

interest

in

PDP-ll/40.

Every

document

should

clearly

state

whether

it

is

a

proposal,

suggestion,

edict,

etc.

All

technical

memoranda

will

have

a

Title-Abstract

page

.~.

in

a

format

identical

to

the

format

of

the

first

page

of

this

document.

All

original

copies

will

be

submitted

to

a

"coordinator.

II

II.

The

coordinator

will:

1.

Assign

a

number

and

date

to

the

memorandum.

2.

Distribute

copies

according

to

the

distribution

key.

3.

Update

11/40

Technical

Memo

#1;

the

Index,

Summary

of

Abstracts,

and

Cross

Reference.

4.

File

the

original.

III.

The

Title-Abstract

page

contains

the

following

information:

1.

Title

-

The

title

should

be

as

informative

as

possible.

2.

Memorandum

Number

-

This

is

left

blank

and

will

be

filled

in

by

the

coordinator.

3.

Author

(5)

4.

Date

-

To

be

filled

out

by

coordinator.

5.

Number

of

pages.

6.

Obsolete

-

This

list

will

indicate

all

memoranda

obsoleted

by

this

document.

The

index

will

be

updated

appropria'tely.

- 3 -

7.

Revision

-

This

list

will

indicate

all

memoranda

revised

by

this

document.

The

index

will

be

updated

appropriately.

8.

Index

Keys

-

Since

some

memoranda

may

affect

several

areas,

the

index

keys

are

maintained

in

a

cross-reference

directory

which

is

a

part

of

PDP-ll/40

Technical

Memo

#1.

For

example,

a

memorandum

on

the

design

and

programming

of

a

disk

file

might

have

the

following

index

keys:

Disk,

I/O,

Mass

Storage,

programming.

9.

Distribution

Keys

-

Since

not

all

of

the

documents

will

be

of

interest

to

everyone,

several

distri-

bution

lists

will

be

assigned.

These

presently

include:

11/40

Group

(all)

11/20

Group

(Managers

&

Supervisors)

PDP-II

Coordinating

Committee

PDP-II

General

List

This

list

will

be

modified

appropriately

in

the

future.

Names

may

be

added

to

or

deleted

from

any

of

these

lists

by

contacting

the

coordinator.

10.

Abstract

-

The

abstract

is

probably

the.most

~portant

part

of

the

document.

It

should

contain,

within

this

£irst

page,

if

possible,

a

statement

of

what

problem

is

investigated,

what

solutions

were

examined,

and

what

conclusions

were

reached.

Because

of

the

wide

involvement

of

many

PDP-II

groups,

total

distribution

of

all

Technical

Memos

is

impractical.

For

this

reason,

all

Title-Abstract

pages

will

be

appended

to

Technical

Memo

#1

(The

Index

and

Abstracts)

for

wide

distribution.

IV.

The

organization

of

the.

memo

will

usually

be

as

follows:

1.

Title-Abstract

page.

2.

Contents

3.

Introduction

4.

Problems

5.

possible

solutions,

their

adv~ntages

and

disadvantages

- 4 -

(Organization

-

continued)

6.

Conclusions

The

format

of

the

body

of

the

Technical

Memo

is

at

the

discretion

of

the

author

who

should

strive

to

present

the

maximum

amount

of

information

in

a

minimum

of

space

(i.e.

single

space

where

practical

and

state

things

concisely).

The

purpose

of

these

memos

is

to

educate

the

reader

and

provide

a

relatively

permanent

record

of

the

depth

of

study

and

rationale

behind

any

technical

decisions

or

problems.

For

this

reason

it

is

important

to

identifY

facts;

"gut

feel"

and

wild

guesses?all

have

a

place,

but

the

author

should

be

c'areful

to

distinguish

which

is

which.

djc