ASC2SMaint.dot ASC2S Maintenance Manual

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 120 [warning: Documents this large are best viewed by clicking the View PDF Link!]

ADVANCED SYSTEM

CONTROLLER

ASC/2S

MAINTENANCE MANUAL

P/N 37539-05

Copyright 1993 by Econolite Control Products, Inc. 010702

ii

WARRANTY

Econolite Control Products, Inc. warrants, for a period as shown below, from date of shipment,

all control equipment listed below to be free from defects in material or workmanship and to be

of the kind and quality designated or specified in the contract. This warranty does not extend to

products not manufactured or sold by Econolite. Econolite has the sole right to determine

whether or not an item is covered under our warranty policy.

Controller Warranty Period

ASC/2S Series Controller 2 years

Econolite is not responsible for damage caused by negligence, acts of God, or use of equipment

in a manner not originally intended. Econolite's liability under this warranty shall not exceed the

cost of correcting defects in the equipment. Upon the expiration of the warranty period, all such

liability shall terminate.

To obtain service under this warranty, deliver the product to the factory at the address listed be-

low. When returning products to Econolite, the following must be done:

Pack in original (or equivalent) shipping container

Insure it (or assume the risk of loss/damage during shipment)

Obtain Return Authorization number from your sales representative

Pay all shipping charges to factory. Econolite will pay the return shipping

charges

List on packing sheet inside carton the return Authorization No., Econo-

lite's Sales Order No., your Purchase Order No., equipment serial No.,

description of problem with equipment, and date of installation.

Ship to the nearest Econolite Service Department:

Econolite Control Products, Inc. or Econolite Control Products, Inc.

Attn: Service Department Attn: Service Department

3360 E. La Palma 446 Third Street, Suite #3

Anaheim, California 92806 Neptune Beach, Florida 32266

iii

Table of Contents

SECTION 1 ................................................................................................................................1-1

INTRODUCTION .......................................................................................................................1-1

ASC/2S FAMILY .................................................................................................................1-1

MANUALS ..........................................................................................................................1-3

Programming Manuals ....................................................................................................1-3

Maintenance Manual.......................................................................................................1-3

SECTION 2 ................................................................................................................................2-1

THEORY OF OPERATION........................................................................................................2-1

FUNCTIONAL DESCRIPTION ...........................................................................................2-1

Processor Module ...........................................................................................................2-3

I/O Interface Modules......................................................................................................2-4

Power Supply Module .....................................................................................................2-4

Telemetry Module ...........................................................................................................2-5

Transceiver Operation .................................................................................................2-5

Processor Module (Schematic document number 34251, pages 1-20) ........................2-10

Microprocessor ..........................................................................................................2-10

Clocks........................................................................................................................2-10

System Control Pins ..................................................................................................2-10

System Busses..........................................................................................................2-11

Decode And Control ..................................................................................................2-12

External Interrupt Sources.........................................................................................2-15

Internal Interrupt Sources ..........................................................................................2-15

Memory......................................................................................................................2-16

Voltage Monitor Control.............................................................................................2-17

Down Time Accumulator ...........................................................................................2-18

Local Voltage Regulators ..........................................................................................2-18

Back-Up Power Supply..............................................................................................2-19

Display.......................................................................................................................2-19

Keyboard ...................................................................................................................2-20

Buzzer .......................................................................................................................2-20

Parallel I/O Section .......................................................................................................2-21

Address Bus ..............................................................................................................2-22

Data Bus....................................................................................................................2-22

Logic Level Translators .............................................................................................2-22

Input Multiplexers ......................................................................................................2-23

Input Buffers ..............................................................................................................2-23

Overlap Program Inputs ............................................................................................2-23

Output Latches ..........................................................................................................2-24

SDLC (EIA-485) Interface..........................................................................................2-25

Terminal (EIA-232) Interface .....................................................................................2-25

Telemetry Interface....................................................................................................2-26

AC Power Input .............................................................................................................2-27

Line Reference Circuits .............................................................................................2-27

Processor-I/O DC input circuit ...................................................................................2-27

FSK Telemetry Module .................................................................................................2-28

Modulator-Transmitter Circuit ....................................................................................2-28

Receive Filter And Demodulator Circuit ....................................................................2-29

iv

Table of Contents (continued)

SECTION 3 ................................................................................................................................3-1

MAINTENANCE ........................................................................................................................3-1

UNPACKING ......................................................................................................................3-2

INSTALLATION PROCEDURE ..........................................................................................3-2

CONNECTOR CABLE ASSIGNMENT ...............................................................................3-3

ENVIRONMENTAL REQUIREMENTS...............................................................................3-4

TEST EQUIPMENT ............................................................................................................3-5

DISASSEMBLY ..................................................................................................................3-6

Processor Module ...........................................................................................................3-6

Power Supply ..................................................................................................................3-6

CLEANING AND INSPECTION..........................................................................................3-7

Cleaning ..........................................................................................................................3-7

Inspection........................................................................................................................3-8

Lithium Battery ................................................................................................................3-9

IMPORTANT SAFETY INFORMATION .............................................................................3-9

ADJUSTMENTS AND TESTS ..........................................................................................3-10

MODEM Check Out Procedure.....................................................................................3-10

Crystal Adjustment Procedure ......................................................................................3-12

Diagnostics Menu..........................................................................................................3-13

Outputs (2).................................................................................................................3-15

Display (3) .................................................................................................................3-16

Keyboard (4)..............................................................................................................3-17

Overlap (5).................................................................................................................3-17

Telemetry (6) .............................................................................................................3-18

Loopback (7)..............................................................................................................3-19

Memory Tests ...............................................................................................................3-20

SECTION 4 ................................................................................................................................4-1

TROUBLESHOOTING ..............................................................................................................4-1

PRECAUTIONS..................................................................................................................4-2

HARDWARE FAULT ISOLATION ......................................................................................4-3

SECTION 5 ................................................................................................................................5-1

PARTS LISTS............................................................................................................................5-1

SECTION 6 ..............................................................................................................................5-30

SCHEMATICS AND ASSEMBLY DRAWINGS.......................................................................5-30

v

LIST OF FIGURES

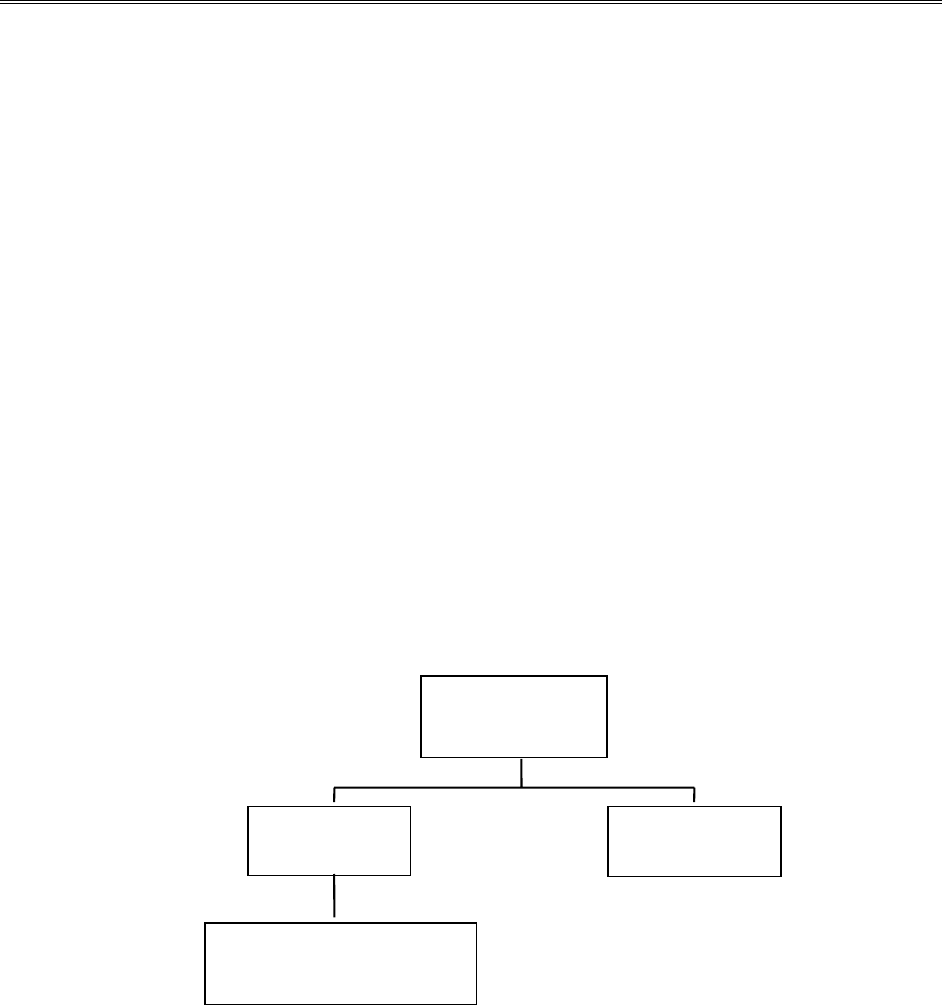

Figure 1-1. ASC/2S Family .......................................................................................................1-2

Figure 2-1. ASC/2S System Block Diagram .............................................................................2-2

Figure 2-2. Processor Section Block Diagram ..........................................................................2-7

Figure 2-3. I/O Section Block Diagram .....................................................................................2-8

Figure 2-4. Processor-I/O Module Component Placement .......................................................2-9

1-1

SECTION 1

INTRODUCTION

ASC/2S FAMILY

The ASC/2S family of actuated controllers consists of three models. Each provides the same

control functions but uses a different type of input/output (I/O) structure to interface with other

components of the traffic control cabinet.

The first model, the ASC/2S-1000, provides an I/O interface conforming to NEMA TS2 standard

requirements for Type 1 controllers. This interface controls all cabinet I/O over a serial commu-

nications channel (Port 1). This serial communications channel is used for data exchange with

a Malfunction Management Unit (MMU), to retrieve vehicle detector data from detector racks

and interface to Terminals and Facilities within the traffic control cabinet. All I/O functions are

handled by one or more Bus Interface Units (BIUs). Each BIU controls up to 15 outputs, 24 in-

put/outputs, 8 inputs and four optically coupled inputs. Type 1 I/O also includes EIA-232 com-

patible terminal (Port 2) and telemetry (Port 3) interfaces.

The second model of the ASC/2S family, the ASC/2S-2000, has an I/O interface that conforms to both

NEMA TS1 and TS2 Type 2 controller requirements. This interface controls I/O functions through industry

standard circular connectors (A, B, & C) and includes the serial communications, terminal, and telemetry

interfaces of the Type 1 interface. TS1 operation allows the ASC/2-2000 to be used in existing traffic con-

trol cabinets without any cabinet changes. The Type 2 I/O operates in one of eight I/O modes. Each mode

assigns specific functions to 24 input and output connections. The first I/O mode (Mode 0) provides com-

patibility with the I/O requirements of the NEMA TS1 standard. This TS1 operational mode is selected by

setting the Type 2 I/O mode to Mode 0 (default) and disabling the serial communications channel.

The serial communications channel of the Type 2 interface is used to communicate with a Mal-

function Management Unit and detector racks as with the Type 1 interface. However, a mini-

mum of 20 vehicle detectors can optionally be connected directly to the controller using one of

the Type 2 I/O modes. The ASC/2S-2000 can also be programmed to operate as a Type 1 con-

troller. In this mode external I/O interface is disabled and all I/O functions are handled over the

serial communications channel. This allows the ASC/2S-2000 to duplicate the operation of the

ASC/2S-1000.

The ASC/2S-2100 is the third model of the ASC/2S actuated controller family. The ASC/2S-

2100 Processor-I/O module includes components that add additional I/O to the ASC/2S-2000

capabilities described above. The expansion I/O components include the "D" connector, 25-pin

telemetry connector, and optionally, the NEMA overlap card connector interfaces matching

those of the ASC-8000. This allows the ASC/2S-2100 to be used as a replacement for an ASC-

8000 or ASC/2-2100 in existing traffic control cabinets without any cabinet changes.

1-2

INTRODUCTION

ASC/2 FAMILY

The ASC/2S family of actuated controllers are made of a formed aluminum enclosure. Control-

ler fronts consist of the User Interface panel and the Connector Interface panel. The User Inter-

face panel consists of a custom, weather and dust-proof conductive rubber keyboard with

numeric, function and cursor keys, and a high-contrast 16 line by 40 character liquid crystal dis-

play with LED back lighting. The Connector Interface panel contains two fuses (115 VAC/1

Amp and +24 VDC/ 0.75 Amp) and various interface connectors. The type of connectors de-

pends on the controller model.

The ASC/2S controller unit contains two main electronic modules and a power supply. The first

main module is the Processor-I/O module which is installed directly in the enclosure. This mod-

ule contains the MC68302 microprocessor which controls all ASC/2S operations and circuitry

that transfers input and output signals between the I/O connectors and the processor. Also lo-

cated on the Processor-I/O module is a connector for installing a telemetry module. The sec-

ond main module is the User Interface assembly mounted to the hinged front panel. All versions

of the ASC/2S controller use the same modules. The model type is defined by the components

installed on the Processor-I/O module. The Processor-I/O and User Interface modules are inter-

connected by a ribbon cable located across the front panel hinge. The Processor-I/O module

together with the connector interface panel, is held in place by two quarter turn fasteners and a

card guide. The User Interface panel is held in place by 3 nuts. Both modules may be easily

removed.

The ASC/2S power supply furnishes +24VDC for controller unit operation. It is mounted inter-

nally on the back panel of the enclosure. The power supply is held in place four screws and is

connected to the processor-I/O module by two wire harnesses.

Figure 1-1. ASC/2S Family

ASC/2S

TYPE 1

ASC/2S-1000

TYPE 2

ASC/2S-2000

TYPE 2 WITH

EXPANDED

I/O ASC/2S-2100

1-3

INTRODUCTION

PROGRAMMING/MAINTENANCE MANUALS

MANUALS

Programming Manuals

Programming of the ASC/2S controller unit is covered in the ASC/2S programming manual.

However, maintenance information is provided for all ASC/2S family members in this manual.

Maintenance Manual

This manual contains the information needed to understand the hardware functions of the

ASC/2S controller family. Information about the circuitry, general maintenance requirements,

installation and disassembly is included. Fault isolation charts are provided to help the techni-

cian isolate problems or to at least provide a good starting point for troubleshooting. Schemat-

ics and comprehensive parts lists are included as well as several appendices to supplement the

hardware descriptions.

Section II contains the ASC/2S theory of operation beginning with a functional description of

each module followed by a detailed description of circuit operation.

Section III is a collection of procedures and check lists that should be used as part of regular

maintenance. Included are procedures for installation, disassembly, visual inspection, cleaning,

battery check, and various adjustments. Test equipment and connector-cable assignment lists

are included. ASC/2S diagnostic tests, the primary method for hardware verification and fault

isolation, are explained.

Section IV is a troubleshooting chart. The chart outlines a series of possible hardware, soft-

ware, and programming problems with associated possible causes and suggested solutions.

Section V contains controller assembly parts lists. It lists components, cables and assemblies

with both Econolite and manufacturer's part numbers.

Section VI contains schematics and assembly drawings.

Appendix A contains cable diagrams to be used when interfacing the ASC/2S to a printer or

personal computer or for data transfer.

Appendix B contains pin lists for all connectors A-D, SDLC, Terminal and Telemetry.

Appendix C describes standard system interconnection using Econolite telemetry interface

boards and transient suppressors.

Appendix D is a guide to lease-line installation used in Econolite system communication.

Appendix E lists and identifies loopback diagnostic error codes.

2-1

SECTION 2

FUNCTIONAL DESCRIPTION THEORY OF OPERATION

FUNCTIONAL DESCRIPTION

This section begins with a functional description of the ASC/2S modules. Each module is then

described in detail. The circuit and signal descriptions are best understood when studied to-

gether with the block diagrams and system schematics. The block diagrams are included in this

section and schematics are located in Section VI.

As an aid to finding circuitry described in the detail text, schematic zone references, which con-

tain the schematic coordinates of the circuitry, are included in the text where pertinent. A sche-

matic zone reference has the format [(D),N,X,Y] where (D) is the optional document number, N

is the schematic page, X is the horizontal coordinate and Y is the vertical coordinate of the

page. The document number is normally referenced at the beginning of each new section.

Also, all part numbers, pin, and signal names are printed in bold type.

2-2

Figure 2-1. ASC/2S System Block Diagram

2-3

THEORY OF OPERATION

Processor Module FUNCTIONAL DESCRIPTION

Processor Module

The Processor-I/O module contains the microprocessor chip, memory chips and support cir-

cuitry required to operate and control all ASC/2S functions. This module also includes all I/O

circuitry and controls the User Interface module keyboard and display operations. Ribbon con-

nector J3 connects this module to the User Interface module.

The system busses include the address bus that identifies the device or memory location tar-

geted for information exchange, the data bus, which carries the information, and the control bus

which synchronizes the data transfers. The communications busses include the Telemetry bus,

SDLC bus and Terminal bus which transfer serial data between the microprocessor and the

dual asynchronous receiver transmitter (DUART) chips and their associated interface chips.

The Processor-I/O module is connected to the power supply module via connectors J18 and

J19. The power supply provides +24VDC.

Auxiliary processor functions include a watchdog timer which checks for proper program opera-

tion, the voltage monitor which checks for power fail conditions, and the battery-backed clock

circuit which keeps accurate time when power is removed from the unit. System RAM is pow-

ered by the rechargeable, backup battery circuit so that data integrity is maintained during

power fail conditions.

Also included on the module are the AC line transient protection circuit and line referenced,

120Hz interrupt generator.

The I/O interface section connects external inputs and outputs, with the microprocessor system

address, data and serial communications busses. This allows the microprocessor to perform all

input and output functions.

2-4

THEORY OF OPERATION

FUNCTIONAL DESCRIPTION I/O Interface Module/Power Supply Module

I/O Interface Modules

The I/O section of the Processor-I/O module consists of input multiplexers, logic level transla-

tors, output latches, output drivers, serial communications interface circuits, the telemetry mod-

ule interface connector J4 and expansion I/O connector J1 (unused).

External parallel inputs are applied through front panel connectors A, B and C. The input volt-

age levels are translated to logic levels to be used by the system. The TRUE/FALSE

(LOW/HIGH) states are then applied to input multiplexers. The processor reads the input status

by addressing the input and enabling the multiplexer, thus transferring the input status onto the

system data bus.

The processor uses output latches to control the external parallel signals. It addresses a spe-

cific output and latches that output status from the data bus by enabling the latch. The signal is

then sent to external connectors A, B or C. In the event of a long power failure, the latches are

cleared to prepare for an orderly controller re-start.

The Terminal bus signals interface with external equipment through Terminal connector J13

(PORT 2). It is used to communicate with printers, computer terminals or other controllers in the

ASC family.

The SDLC bus signals interface with optional Bus Interface Units and/or a Malfunction Man-

agement Unit via SDLC connector J15(PORT 1).

The Telemetry bus signals attach to connector J4 and supply the signals required for FSK and

EIA-232/fiber optic telemetry interconnects. Once translated by the Modem module, the signals

interface with external signals via connectors J17(PORT 3) and J14 on the model ASC/2S-

2100.

VOLTAGE MONITOR CONTROL is generated by monitoring the power supply and battery volt-

ages and Processor signals. It is output to external equipment as VOLTAGE MONITOR.

When the processor-I/O module is configured as an ASC/2S-2100 it includes type D and 25-pin

Telemetry connectors and associated input multiplexers, logic level translators, output latches

and output drivers. External parallel inputs and outputs are processed as mentioned above. A

plug-in NEMA overlap programming card (optional) is connected to the input multiplexers by

connector J6. When programmed, the overlap inputs are read by the processor in the same

way as external inputs.

Power Supply Module

The Power Supply module is a 40 watt, 24 volt off-line switching supply set for 120VAC opera-

tion. When configured as an ASC/2S-2000 or ASC/2S-2100 controller, input power is applied

through the A-connector on the controller front panel and then routed, via the AC line transient

protection circuit, to J19 on the I/O module. A wire harness connects between J19 and the

power supply module. When used in the ASC/2S-1000 controller, input power is applied

through MS connector J16 on the front panel and then routed to the power supply module as

mentioned above. The +24VDC output from the supply is routed back to the Processor-I/O

module via a wire harness connected to J18.

2-5

THEORY OF OPERATION

Telemetry Module - Transceiver Operation FUNCTIONAL DESCRIPTION

Telemetry Module

The Telemetry module operates as a transceiver providing communication between the

ASC/2S-1000, ASC/2S-2000 or ASC/2S-2100 and an ASC/2M-1000 or KMC-10000 master

controller. The module is controlled by the Processor module and interfaces with to the Telem-

etry bus via connector J4. Transmit, and receive signals are interfaced through the Telemetry

connector(s) on the front panel.

Transceiver Operation

Communication between the local and master controllers is achieved over voice grade four-wire

(two data channels) type 3002 leased telephone lines, or customer owned cable. The telemetry

data channel is made up of command (master to local) and readback (local to master) lines.

Additional lease-line information is found in Appendix D. Each local transceiver is assigned a

unique telemetry address used by the master to identify the transceiver. The address is as-

signed by either direct keyboard entry (refer to the ASC/2S Programming Manual) or by activat-

ing External Address Enable (J14-15) and assigning the desired bit pattern to the appropriate D-

connector system inputs (refer to Appendix E). Devices connected to the local transceiver are

identified by subaddresses assigned and used by the master.

The master generates command messages containing local telemetry address, message type,

subaddress, data, and a horizontal parity word. Command messages are transmitted to the lo-

cal transceiver in a predefined sequence. The sequence begins with a zero address command

which simultaneously transmits, to all local controllers, the system traffic program and four spe-

cial functions. Local controllers do not respond to the zero address command. Subsequent

messages request the status of the devices (listed above) connected to the local transceiver.

The addressed local controller sends an appropriate response to the master on the readback

line. Transmission of commands and readbacks occurs simultaneously. An error status is gen-

erated if a readback is not received by the master within a predefined period. For more informa-

tion on master controller operation using telemetry, refer to the ASC/2M-1000 or KMC 10,000

Master Programming and Maintenance Manuals.

At the local transceiver, modulated command message signals are transformer coupled to the

receiver where they are filtered and demodulated to a serial-bit pattern. The serial-bit pattern is

converted by an SCC receive channel on the microprocessor into a parallel pattern, four-word

command message which is read by the microprocessor. If the message address corresponds

to that of the local transceiver and if the message is valid, the microprocessor performs the op-

eration specified by the message type. Where readbacks are required, the local transceiver

generates a three-word readback message containing the requested data and horizontal parity

word. The three data words from the microprocessor are converted to a serial bit pattern by a

transmit channel on the DUART. The serial bit pattern is then sent to the MODEM which pro-

vides frequency shift key (FSK) modulation for transmission. Valid data, transmit, and received

carrier LEDs are ON or flash during normal data transmission.

2-6

THEORY OF OPERATION

DETAILED DESCRIPTION

This section contains detailed descriptions of the various ASC/2S modules. Each module is de-

scribed in detail with references to schematics in the format [(D),N,X,Y] where (D) is the docu-

ment number, N is the schematic page, X is the horizontal coordinate and Y is the vertical

coordinate of the page. The document number (D) is not always provided in this format but it is

normally referenced at the beginning of each new section. Part numbers are identified in paren-

thesis (###) immediately before references to schematic coordinates. Example: U24

(74HCT244) [4,2,C]. Pin and signal names are also printed in bold type.

The schematics are found in Section VI of this manual. Also, a module block diagram is shown

before the discussion of each module. These block diagrams illustrate general functional opera-

tion.

2-7

Figure 2-2. Processor Section Block Diagram

2-8

Figure 2-3. I/O Section Block Diagram

2-9

Figure 2-4. Processor-I/O Module Component Placement

2-10

Processor Module THEORY OF OPERATION

Microprocessor/Clocks/System Control Pins DETAILED DESCRIPTION

Processor Module (Schematic document number 34251, pages 1-20)

Microprocessor

The ASC/2S family of controllers uses the Motorola MC68302 integrated multiprotocol proces-

sor. This is a Very Large Scale Integration (VLSI), CMOS device which includes a 16-bit, 68000

core processor, a system integration block and a (RISC) communications processor.

Features of the system integration block that are used by the ASC/2 include: the independent

DMA controller, a 19-level interrupt controller, the dual port RAM area, three programmable tim-

ers, the four programmable chip select lines, sixteen parallel I/O lines, the on-chip clock genera-

tor and several other "glue logic" functions.

The communications processor provides the following functions: the main controller (RISC

Processor), three independent full-duplex serial communications controllers (SCC), six serial

DMA channels for the three SCCs and an SCP channel for synchronous peripheral communica-

tions.

The following is the microprocessor signal description. All relevant information about the micro-

processor signals and their associated control circuits is discussed.

Clocks

The system clock synchronizes the internal operations of the microprocessor and all external

devices on the system busses. Microprocessor timing is controlled by a 14.7456 MHz crystal

attached to the on chip clock generator circuit through pins EXTAL and XTAL [2,2,B]. The

system clock rate is 14.7456 MHz. This system clock is output by the processor on the CLKO

pin [2,2,B]. The CLKO signal is divided by four by U21 (GAL16V8) [4,4,D], to provide a 3.6864

Mhz clock to DUART U20 (SCN2681)[4,5,A]. U20 divides the 3.6864 MHz clock by 96 and out-

puts a 19,200 Hz clock (16 X 1200 baud) on OP3 [4,5,A] for the external transmit clock inputs of

SCC1 (TCLK1) and SCC2 (TCLK2) on processor chip U12 [2,5,C]. This signal is also used to

trigger the processors data request line /DREQ [2,5,B] of the independent DMA controller which

transfers data to the LCD module.

System Control Pins

/RESET is a bi-directional pin, acting as an input and when asserted along with the /HALT pin

[2,3,B], it causes a total system reset. The /RESET and /HALT signals are generated by a

combination of U11 (74LS09), U5 (14538b) [8,2-4,B-C] and U4 (LM2598-5.0) [3,5,B]. U4 holds

the PWRGOOD signal low anytime VCC is out of tolerance. If the program running in the proc-

essor fails to toggle the /WDOG signal [8,5,B], the U5 watchdog timer circuit will time out and

generate a reset pulse. The /RESET pin can also act as an output which allows the program to

output a /RESET signal to peripheral devices.

/BERR, BUSW, DISCPU and /FRZ pins are not used.

2-11

THEORY OF OPERATION

Processor Module - System Busses DETAILED DESCRIPTION

System Busses

Data Bus (D0-D16)

This 16-bit, bi-directional, three-state bus is the general-purpose path for exchanging data with

memory and other system devices. It can transmit and accept data in either byte or word

widths. For all 16-bit accesses, byte 0, the high-order byte of a word, is available on D8-D15

and the low-order byte is available on D0-D7 [2,3,C]. The low order data lines are buffered by

the system data buffers before being routed to the various I/O circuits. Buffering to the parallel

I/O section is performed by U25 (74HCT245) [4,4,D]. Unbuffered data signals are labeled D(n)

and buffered signals are labeled BD(n). Buffering to the User Interface panel is performed by

U38 (74HCT245) [10,5,C]. Unbuffered data signals are labeled D(n) and buffered signals are

labeled FPD(n).

Address Bus (A1-A23)

Pins A1-A23 [2,3,D] form a 24-bit address bus when combined with the /LDS and /UDS pins

[2,3,B]. The address bus is a bi-directional, three-state bus capable of addressing 16M bytes of

data. On the ASC/2S, address lines A21-A23 are not used. All address lines are buffered be-

fore being routed to the various I/O circuits. Buffering to the parallel I/O section is performed by

U24 (74HCT244) [4,2,C]. Unbuffered address signals are labeled A(n) and buffered signals are

labeled BA(n). Buffering for the User Interface panel is performed by U39 (74HCT244) [10,5,B].

Buffered address signals are labeled FPA(n).

Control Bus

This is a multipurpose bus that includes all the Processor-I/O modules chip select, write enable

and output enable signals. These signals are used to control communications with the various

RAM and EPROM devices, parallel I/O devices, the data module and the User Interface mod-

ule. The control bus signals are generated by the decode and control section. These signals will

be explained when their associated circuitry is discussed.

Telemetry Bus

This bus contains the serial data and hand shaking signals which are routed to the Telemetry

module connector. Signals included in this bus are: the receive data line RXD1 [2,5,D] which

inputs serial data into SCC1 on the processor, the transmit data line TXDA [4,5,B] which trans-

mits data out of U20 and /CTSA, /RTSA/, /CDA, MDCTL1 and MDCTL2, generated by U20

[4,5,B], which control communications handshaking and provide modem control.

Terminal Bus

This bus contains the serial data and hand shaking signals which are routed to the Terminal

Port (PORT2) RS-232 interface chip U80 (MAX214) [7,2,C]. Signals included in this bus are: the

receive data line RXD2 which inputs serial data into SCC2 on the processor, the transmit data

line TXD2 which transmits data out of SCC2, /CTS2, /RTS2, and /CD2 generated by SCC2

[4,6,C] and /DTRT generated by U20 [4,5,A] which control communications handshaking and

provide modem control.

SDLC Bus

This bus contains the serial data and clock signals which are routed to the SDLC Port (PORT1)

RS-485 interface chips U81 and U82 (LT490) [7,D,6]. Signals included in this bus are: the re-

ceive data line RXD3, which inputs serial data into SCC3 on the processor, TXD3 which outputs

serial data from SCC3 and transmit and receive clocks TCLK3 and RCLK3 [2,5,C] which are

required to synchronize communications over the SDLC channel.

2-12

THEORY OF OPERATION Processor Module

DETAILED DESCRIPTION System Busses/Decode and Control

SPI Bus

This bus contains the serial data, clock and handshake signals which are used for communica-

tions with U3 (68HC68T) [8,4,D], the battery-backed clock. Signals included in this bus are: se-

rial transmit data line SPTXD, serial receive data line SPRXD, synchronizing clock line SPCLK

and slave select line SS [2,5,C].

Decode And Control

This section takes the microprocessors address, data strobe, address strobe, read/write, chip

select and clock signals and combines them in various ways to generate the control bus signals

required for proper interaction between devices on the Processor-I/O module and the User

Interface panel. These signals will be discussed below. All signals starting with a slash

character i.e. /xxx are low only when active otherwise they are normally high.

CLKO [2,2,D] outputs the 14.7456 MHz system clock.

/AS [2,3,B] indicates when there is a valid address on the address bus (/AS is not used outside

the processor chip in this design.).

R/W [2,3,B] defines the data bus transfer as a read or write cycle. It is HIGH during a read and

LOW only during a write cycle.

/UDS [2,3,B] is the upper data strobe signal. It controls the flow of data on data bus lines D8-

D15 by specifying when valid data should be on the bus.

/LDS [2,3,B] is the lower data strobe signal. It controls the flow of data on data bus lines D0-D7

by specifying when valid data should be on the bus.

/CS0-/CS3 [2,3,A] are the four system chip select signals. /CS0 is the primary chip select for all

EPROM accesses. /CS1 selects the RAM bank. /CS2 is the chip select signal for the data

module /CS3 is the primary chip select for all I/O accesses. Address decoding and DTACK and

Wait-State generation for these signals is performed onboard the processor chip.

RESETB [2,5,B] is an active high reset signal for the DUART (SCN2681) U20 [4,5,A].

/WEO [4,5,D] is the write enable signal for the odd addressed RAM chip. This signal is gener-

ated by U14B (74ALS32) [4,6,D] by ORing the lower data strobe /LDS from the processor and

the gated read/write signal GR/W from U21 (GAL16V8) [4,4,D]. GR/W is held inactive when

VCC fails which write protects the RAM when power is removed.

/OEO [4,5,D] is the output enable signal for the odd addressed RAM and EPROM chips and the

data module. This signal gates the data from the device onto the data bus allowing the proces-

sor to read the data. This signal is generated by U14A (74ALS32) [4,6,D] by ORing the lower

data strobe /LDS with the inverted read/write line /RW. /RW is generated by U15A (74ACT04)

[4,5,C] by inverting the R/W signal from the processor.

/WEE [4,5,D] is the write enable signal for the even addressed RAM chip. This signal allows the

processor to write data from the data bus into the device if the devices chip select line is active.

This signal is generated by U14D (74ALS32) [4,6,C] by ORing the upper data strobe /UDS from

the processor and the gated read/write signal GR/W from U21 (GAL16V8) [4,4,D]. GR/W is

held inactive when VCC fails which write protects the RAM when power is removed.

2-13

THEORY OF OPERATION

Processor Module - Decode and Control DETAILED DESCRIPTION

/OEE [4,5,D] is the output enable signal for the even addressed RAM and EPROM chips. This

signal gates the data from the device onto the data bus allowing the processor to read the data.

This signal is generated by U14C (74ALS32) [4,6,D] by ORing the upper data strobe /UDS with

the inverted read/write line /RW. /RW is generated by U15A by inverting the R/W signal from the

processor.

/CS0L [4,3,C] is the chip select signal for the onboard flash EPROM chip. This signal is gener-

ated by U13 (GAL16V8) [4,4,C] by combining the main EPROM chip select line /CS0 from the

processor with A20. /CS0L is active for the address range $000000-$0FFFFF

/CS0H [4,3,C] is the chip select signal for the off board flash EPROM memory space. This sig-

nal is generated by U13 (GAL16V8) [4,4,C] by combining the main EPROM chip select line

/CS0 from the processor with A20. /CS0H is active for the address range $100000-$1FFFFF

/CS1L [4,3,C] is the chip select signal for the onboard RAM chips. This signal is generated by

U13 (GAL16V8) [4,4,C] by combining the RAM chip select signal from the processor /CS1 and

A16. This signal utilizes the fact that GAL16V8 outputs float when power is removed. This

eliminates a current path out of the RAM chips during battery backup operation thus extending

battery life.

/CS1L [4,3,C] is the chip select signal for the off board RAM memory space. This signal is gen-

erated by U13 (GAL16V8) [4,4,C] by combining the RAM chip select signal from the processor

/CS1 and A16. This signal utilizes the fact that GAL16V8 outputs float when power is removed.

This eliminates a current path out of the RAM chips during battery backup operation thus ex-

tending battery life.

/CSWE [4,3,C] is the write enable signal for the data module. This signal allows the processor

to write data from the data bus into the device if the devices chip select line is active. This sig-

nal is generated by U13 (GAL16V8) [4,4,C] by combining input signals GR/W, A9-A13 and the

input from the EEPROM write protect jumper JP3 [4,4,B]. A9-A13 are used to differentiate be-

tween the write-protected and non write-protected areas of the module.

/SWAPCS0 [4,4,C] is used during flash EPROM download module.

3.6864 [4,3,D] provides a 3.6864 Mhz clock signal to the DUART U20 (SCN2681) [4,6,A]. This

signal is generated by U21 (GAL16V8) [4,4,D] by dividing the system clock CLKO by four.

STOP HERE

/DWEO [4,3,D] is the write enable signal for DUART U20 (SCN2681) [4,6,A]. This signal allows

the processor to write data from the data bus into the device if the devices chip select line is ac-

tive. This signal is buffered version of /WEO and is generated by U21 (GAL16V8) [4,4,D].

/DOEO [4,3,D] is the output enable signal for DUART U20 (SCN2681) [4,6,A]. This signal

gates the data from the device onto the data bus allowing the processor to read the data. This

signal is buffered version of /OEO and is generated by U21 (GAL16V8) [4,4,D].

/DUART [4,3,D] is the DUART chip enable line. This signal is generated by U21 (GAL16V8)

[4,4,D] by combining the system I/O enable signal /CS3 from the processor and address lines

A17-A19. It is routed to U20 (SCN2681) [4,5,A]. /DUART is active for the address range

$E00000-$E1FFFF.

2-14

THEORY OF OPERATION

DETAILED DESCRIPTION Processor Module - Decode and Control

/PIOSL [4,3,D] is the parallel I/O device enable line. It is generated by U21 (GAL16V8) [4,4,D]

by combining the system I/O enable signal /CS3 from the processor and address lines A17-

A19. This signal enables the I/O data buffer U25 (74HCT245) [4,2,D] and bank selector U23

[13,6,D]. /PIOSL is active for the address range $E20000-$E3FFFF.

GR/W [4,3,C] is the R/W line from the processor combined with the PWRGOOD signal. A write

to a memory device can not be accomplished until PWRGOOD is asserted high.

/FPSEL [10,5,D] is the User Interface buffer U38 (74HCT245) [10,5,C] enable line. This signal

is generated by U22 (GAL16V8) [10,5,D] by combining the system I/O enable signal /CS3 from

the processor and address lines A17-A19.

/KEYSEL [10,5,D] is the keyboard input buffer enable line that is routed to the User Interface

module connector J3 [10,5,A]. This signal is generated by U22 (GAL16V8) [10,5,D] by combin-

ing the system I/O enable signal /CS3 from the processor and address lines A17-A19.

/KEYSEL is active for the address range $EC0000-$EDFFFF.

/LCDSEL [10,5,D] is the LCD module select line. This signal is generated by U22 (GAL16V8)

[10,5,D] by combining the system I/O enable signal /CS3 from the processor and address lines

A17-A19. /LCDSEL is routed to the User Interface module connector J3 [10,5,A]. /LCDSEL is

active for the address range $E80000-$E9FFFF.

LCDEN is the LCD module enable line. This signal is generated by U22 (GAL16V8) [10,5,D] by

stretching /LCDSEL by one system clock period and then ANDing this signal with /LDS.

LCDEN is routed to the User Interface module connector J3 [10,5,A].

2-15

THEORY OF OPERATION

Processor Module - Interrupt Sources External /Internal DETAILED DESCRIPTION

External Interrupt Sources

An interrupt signal causes the processor to stop normal program execution and go to an ad-

dress that is the beginning of an interrupt service routine. Executing the routine provides what-

ever action is necessary to service the device generating the interrupt.

/IRQ41 [2,5,B] is a signal which requests service by the real-time clock interrupt routine. This

AC line referenced, 120Hz square wave signal is generated by U1B (14538) [8,5,A] in conjunc-

tion with optoisolator U91 [20,2,C]. This routine controls timing of all controller software activity

and provides real-time clock updates.

/IRQ6 [2,3,A] is an active LOW open drain signal generated by U20 (SCN2681) [4,5,B] during

telemetry transmissions.

/IRQ4F [2,5,B] interrupt is used to shut down the controller in the event of a power failure.

/IRQ4F is one of the highest priority interrupts thus causing the processor to take immediate ac-

tion for an orderly controller shut-down. /IRQ4F is generated by the missing pulse detector cir-

cuit U1A (14538) [8,4,A]. The missing pulse detector is used to detect a loss of 120 Hz pulses.

It is a re-triggerable one shot with a period of approximately 22 milliseconds. Positive transi-

tions of OPTO1, from U91 [20,2,C], are cleaned up by U1B then fed to U1A. This signal retrig-

gers the one shot every 8.33 milliseconds and also produces the /IRQ41 signal. During a power

failure the one shot will not be retriggered and will time out, causing an /IRQ4F interrupt. Also, if

the power supply output voltage is out of tolerance, VM24 will go LOW, thus forcing an /IRQ4F

interrupt.

Internal Interrupt Sources

The 68302 processor contains 16 on-board sources which can generate interrupts. The ASC/2

controller family uses the following interrupts: SCC1-SCC3 and Timers 1-2. The receive chan-

nel of SCC1 which is used for the telemetry channel, is set up to generate an interrupt when: 1.

The controllers' address is recognized on the telemetry line, 2. After the block of data has been

received and 3. When the checksum has been received.

The receive channel of SCC2 which is used for the terminal interface, generates an interrupt

when: 1. An XON or XOFF character is recognized while the port is used for printing, 2. Blocks

of data of various predefined lengths are received from another device during the direct connect

process.

The receive channel of SCC3 which is used for the SDLC interface, generates an interrupt after

a complete frame is received from a BIU or MMU.

Timer 1 is used for the telemetry channel and generates an interrupt when: 1. It is time to turn

on the carrier signal, 2. It is time to transmit the data packet and 3. It is time to turn off the car-

rier.

Timer 2 is used for the SDLC channel and generates interrupts that set the proper timing of the

transmission of SDLC frames to the BIUs and MMU.

2-16

THEORY OF OPERATION

DETAILED DESCRIPTION Processor Module - Memory

Memory

Flash EPROM Program Memory

The software program that controls processor operation is written into U2 (29F800AB-90)

[5,4,D]. This is a 90-nanosecond rewritable flash EPROM that provides 1 Megabyte of program

address space configured as 512K x 16 words. The EPROM is accessed using zero wait states.

The number of wait states are set using the processors internal wait state generator associated

with the master EPROM chip select signal /CS0. U2 is enabled by chip enable line /CS0L. U2

puts its data on the data bus (D0-D15) when the chip enable line is low and either or both output

enable lines /OEE or /OEO [5,6,C] are low. A write operation to U2 requires that /CS0L is low

and /WEO is low.

RAM

All variable data is stored in Random Access Memory (RAM) pair U6 and U7 (628128-) [5,3,D].

The standard ASC/2S configuration uses 128K x 8, 70 nanosecond devices. This provides

256K bytes of data memory . The RAM is accessed using zero wait states. This is set using

the processors internal wait state generator associated with the master RAM chip select signal

/CS1. RAM is powered by voltage BAT [5,4,B] so that data is not lost during power outages.

The RAM read/write operations function as follows:

When the RAM chip select signal /CS1L and the odd write enable signal /WEO are LOW, and

the odd output enable signal /OEO is HIGH, the RAM stores the data on the odd data bus (D0-

D7) in the location specified by the address bus (A1-A15).

When the RAM chip select signal /CS1L and the even write enable signal /WEE are LOW, and

the even output enable signal /OEE is HIGH, the RAM stores the data on the even data bus

(D8-D15) in the location specified by the address bus (A1-A15).

When the RAM chip select signal /CS1L is low and the odd write enable signal /WEO are high,

and the odd output enable signal /OEO is low, the RAM supplies the odd data bus (D0-D7) with

the data stored in the location specified by the address bus (A1-A15).

When the RAM chip select signal /CS1L is low and the even write enable signal /WEE are high,

and the even output enable signal /OEE is low, the RAM supplies the even data bus (D8-D15)

with the data stored in the location specified by the address bus (A1-A15).

When the processor does a word read or write access, both odd and even chips within the bank

are enabled simultaneously

Data Module

The Data module is mounted on the Processor-I/O module. The module is connected by J5

[6,5,C].

**CAUTION**

Do not remove or insert

data module with power

applied to controller.

2-17

THEORY OF OPERATION

Processor Module - Memory/Voltage Monitor Control DETAILED DESCRIPTION

EEPROM Memory

All user entered data is stored on the data module. The ASC/2S comes standard with a 32K x 8,

250 nanosecond Electrically Erasable Programmable Read Only Memory (EEPROM) installed

on its data module. During a write cycle, the address and data are latched internally and the

cycle is automatically completed by the EEPROM. The write cycle takes a maximum of 10 milli-

seconds during which the chip cannot be accessed. The EEPROM is accessed using three wait

states. This is set using the processors internal wait state generator associated with the master

EEPROM chip select signal /CS2.

The processor writes to EEPROM when the EEPROM chip enable signal /CS2 is low, the odd

output enable signal /OEO is HIGH, and the write enable signal /CSWE is LOW. When the

EEPROM chip enable signal /CS2 and the odd output enable signal /OEO are LOW, and the

write enable signal /CSWE is HIGH, the EEPROM supplies the data bus (D0-D7) with the data

stored in the location specified by address bus (A1-A14). The processor then reads the data

from the data bus. EEPROM retains all user data when power is not applied to the controller.

Memory Expansion Connector

Connector J2 [9,2-6,A-D] allows for several functions including memory system expansion,

Flash EPROM programming and system debugging. The Flash EPROM download module can

be inserted into this connector for rapid programming of the on board Flash EPROM. All 68000

bus signals used by the ASC/2S are present on this connector.

Voltage Monitor Control

The voltage monitor control circuit is used to force the Voltage Monitor output FALSE, thus set-

ting the intersection to flash and turning on LED1 [8,2,C]. The circuit consists of U11C and

U11D (74LS09) [8,1,C]. These two gates AND the VM24 and /CPUVM signals. VM24 is an

open collector output from comparator U10A (LM393) [3,4,B] that uses as its pull up voltage, the

output of the watchdog timer /DOG. If VM24, /CPUVM or /DOG goes low, VMC will go low

(FALSE). VM24 is the output from the power supply voltage monitor circuit. This signal is set

low if the +24VDC supply voltage goes out of tolerance. /CPUVM is an output from the proces-

sor chip. This line is set low when a flash condition is detected by the processor. /DOG is the

output from the system watchdog timer circuit U5 (14538) [8,4,B]. The watchdog input is tog-

gled by the processor approximately once every 100 milliseconds. /DOG is set low if, due to er-

ratic program behavior, the processor fails to toggle the watchdog input. Under normal

conditions all three inputs are high thus maintaining Voltage Monitor Control VMC HIGH. A

flash condition is indicated by a VMC LOW. The LOW VMC signal is inverted again at the I/O

Interface and output as Voltage Monitor. This signal can be used in conjunction with a conflict

monitor to set the intersection in flash.

2-18

THEORY OF OPERATION Processor Module

DETAILED DESCRIPTION Down Time Accumulator/Local Voltage Regulators

Down Time Accumulator

The Down Time Accumulator (DTA) is used to detect missing 120 Hz interrupts and to time the

length of power outages. The DTA consists of battery-backed real time clock chip U3

(68HC68T) [8,4,D] and the processor chips' internal Timer 3.

Timer 3 is used to determine whether the length of a power failure is less than or greater than

0.75 seconds. This time was selected as the limit, within NEMA range, in determining the action

to take after a short ( < 0.75) or long ( > 0.75) power failure. If the power failure is less than

0.75 seconds the controller continues to operate. If the power failure is greater than 0.75 sec-

onds the controller reverts to its start-up sequence. If power fails altogether, the processor

writes its internal RTC time out to U3 to keep accurate time until power is reapplied. U3 uses a

combination of VCC and battery B1 [8,5,C] voltage to operate. The processor communicates

with U3 over the SPI bus. When power is reapplied, the processor reads the time from U3 and

updates its internal RTC time.

Local Voltage Regulators

Switching regulator U4 (LM2598-5.0) [3,5,B] converts the incoming +24VDC into the +5VDC

VCC signal used throughout the module. U4 also generates the PWRGOOD signal used by the

reset circuit and GR/W generation. Diode CR11 protects other circuits in the event of a short

between U4-2 (+24VDC) and U4-3. Transient voltage suppressor CR1 (P6KE27A) [3,6,B] pro-

tects the input from any transients greater than about +30VDC.

Linear regulator U79 (LM7812) [7,3,D] provides a high current, short circuit protected +12VDC

source for use by the telemetry module and external fiber optic modems.

**CAUTION**

Do not attempt to adjust the crystal

oscillator C19 in the field. This is a

precision adjustment. See maintenance

section for proper adjustment procedure.

2-19

Processor Module THEORY OF OPERATION

Back up Power Supply/Display DETAILED DESCRIPTION

Back-Up Power Supply

The back-up power supply provides power to the RAM and the battery-backed clock during a

power failure. With power applied, the VCC power supply provides power to the battery-backed

real time clock U3 (68HC68T) [8,5,D] and the RAM chips via transistor Q1 (MMBT3904ALT1)

[8,5,B]. As long as VCC is greater than 4.74VDC, PWRGOOD will be high and Q1 will turn on.

When power is removed, Q1 turns off and diode CR3 conducts, thus supplying power from the

lithium battery B1 [8,5,C]. Jumper JP2 disconnects the battery during troubling shooting or pe-

riods of extended storage. B1 is a rechargeable lithium battery and uses resistors R36, R38 and

diode CR13 as the charging circuit.

Battery voltage is monitored by comparator circuit U10B (LM393) [3,4,A]. When battery voltage

drops below 2.2 VDC, the comparator triggers causing output signal /LOBAT to go low thus

signaling the processor that the battery is not recharging properly and replacement is required.

Display

The User Interface module contains a Liquid Crystal Display (LCD) formatted as 16 lines of 40

characters, the display contrast control, the display backlight circuit, the display heater circuit,

the keyboard matrix and the system buzzer. The display contains its own control and drive

electronics and appears as two registers to the processor. The display is connected to the

processor module via User Interface connector J3. Please note: The User interface panel

should be sent to Econolite for repair.

Display Interface

The processor uses its Independent Direct Memory Access (IDMA) channel to write to the dis-

play. When a screen update is required, the program fills a RAM buffer with screen data. The

program then initializes and activates the IDMA channel. The IDMA transfers one byte at a time

from the buffer to transceiver U38 (74HCT245) [10,5,C] via D00-D07. When /FPSEL [10,6,C] is

low and R/W is low, the data is transferred to the User Interface module data bus and routed to

the LCD modules data lines. The LCD module uses a combination of signals LCDEN,

/LCDSEL, A01 buffered by U39A (74HCT244) [106,B] and R/W buffered by U39B on its inputs

to transfer the data to its internal circuitry. The IDMA uses the signal TCLK1 [4,3,A] to generate

its data request signal /DREQ [2,5,B]. Thus one byte is transferred for each cycle of TCLK1.

The LCD module has a cycle time of 1 microsecond. The processor has a cycle time of 271

nanoseconds. The master I/O chip select signal /CS3 is generated using 6 wait states and sig-

nal LCDEN is stretched by U22 (GAL16V8) [10,5,D] to accommodate this discrepancy.

Display LED Backlight

The LCD module contains a matrix of yellow/green LEDs used to backlight the display. The

backlight is enabled from the front panel.

The processor uses its PB2 output signal LCD-B [2,5,B] to activate the backlight. The proces-

sor turns the backlight ON by setting PB2 HIGH. LCD-B is buffered before going to the User In-

terface module by U39B (74HCT244) [10,5,B].

2-20

THEORY OF OPERATION Processor Module

DETAILED DESCRIPTION Keyboard/Buzzer

Keyboard

The User Interface module keyboard consists of a matrix of conductive rubber switches. The

processor scans the matrix via J3 by reading specific addresses. The lower nibble of the ad-

dress bus (A01-A04), which generates the row strobes, is buffered by U39A (74HCT244)

[10,5,B]. The column data is input by buffer U38 (74HCT245) [10,5,C]. Scan circuitry on the

User Interface module is enabled by signal /KEYSEL. The processor then decodes the four

column status bytes to determine which key is pressed.

Buzzer

The processor uses its PB1 output signal BUZ [2,5,B] to activate the User Interface module

buzzer. The processor turns the buzzer ON by setting PB1 HIGH. BUZ is buffered before go-

ing to the User Interface module by U39B (74HCT244) [10,5,B].

2-21

THEORY OF OPERATION

Parallel I/O Interface DETAILED DESCRIPTION

Parallel I/O Section

The three members of the ASC/2S family use the same Processor-I/O module. The model type

is differentiated by which components are installed in the parallel I/O section. The following dis-

cussion will address the board generically. Any circuits associated with a particular model type

will be addressed separately.

All processor access to the parallel I/O section is done through buffers U25 (74HCT245) [4,2,D]

and U24 (74HCT244) [4,2,C]. These chips buffer the D00-D07 data lines, A01-A06 address

lines, /LDS and /RESET.

The I/O DECODER U23 (74HCT138) [12,6,D] divides the I/O block defined by parallel I/O chip

select signal /PIOSL into 8 sections, /LE0, /LE1, /I/O0, I/O1, /Y4, /Y5, /Y6 and /Y7. These sig-

nals are generated by combining the block select signal /PIOSL with the buffered lower data

strobe /BLDS and the addresses appearing on BA4-BA6 and BA17. The following signals are

generated:

/LE0 is the latch enable for the bank of outputs containing the following phase 1-8 functions:

PHASE ON, PHASE NEXT, PHASE CHECK, GREEN, YELLOW and RED DRIVERS, WALK

DRIVER and PED CLEAR DRIVER. It is selected by address $E20001.

/LE1 is the latch enable for the bank of outputs containing the following functions: Phase 1-8

DON'T WALK DRIVERS, RING 1 AND 2 STATUS BIT DRIVERS and OVERLAP DRIVERS.

/LE1 is also routed to the expansion I/O connector I/O2P1. It is selected by address ($E20011)

/I/O0 selects the input multiplexer bank containing the following functions: Phase 1-8 HOLD,

PHASE OMIT, PED OMIT, VEH CALL DET, PED CALL DET, RING 1 and 2 INH MAX TERM,

MAX II SELECT, OMIT ALL RED CLEAR, RED REST MODE, PED RECYCLE, FORCE OFF

and STOP TIME along with CALL TO NON-ACT, WALK REST MODIFIER, MIN RECALL,

INTERVAL ADVANCE, MANUAL CONTROL ENABLE, INDICATOR LAMP CONTROL AND

EXTERNAL START. It is selected by address $E20021.

/I/O1 selects the input multiplexer bank for the expanded I/O function of the ASC/2S-2100. It is

selected by address $E20031.

/Y4 selects the input buffer containing the following functions: MODE BIT A-C, PREEMPT DET

2,4,5,6 and the COORD FREE INPUT. It is selected by address $E20041.

/Y5 selects the input buffer containing the following functions: TEST C, SPARES 1-6 and the

signal that tells the controller that an expansion I/O module is present ASCIO. It is selected by

address $E20051.

/Y6 and /Y7 select the expanded I/O input buffers. They are selected by addresses $E20061

and $E20071, respectively.

2-22

THEORY OF OPERATION Parallel I/O Interface

DETAILED DESCRIPTION Address Bus/Data Bus/Logic Level Translators

Address Bus

This bus carries the address information used by the input multiplexers and output latches to

select a particular I/O line. It is a buffered subset of the processors address bus and includes

BA1-BA3.

Data Bus

This bus carries the data that is sent to the output latches or received from the input multiplex-

ers. It contains the buffered lower (ODD) data bus which includes BD0-BD7.

Logic Level Translators

Each logic level translator consists of a three resistor network (10K, 75K, and 18K) which con-

verts the 24 V (FALSE), 0 V (TRUE) logic levels of control signals from external equipment to

the HCMOS logic levels required by the input multiplexers.

A 10K pull-up resistor biases the input to the FALSE state when the external control input is not

connected. The voltage divider (75K and 18K) establishes the input level to the input multi-

plexer. An external input of 0 V to 8 V is detected as TRUE and an input of 16 V to 24 V is de-

tected as FALSE (inputs are inverted internal to the processor). The combination of the 75K

resistor, acting as a current limiter, and the internal protection circuit of the input multiplexer pro-

tects against transient input voltages exceeding 24 V.

2-23

Parallel I/O Interface THEORY OF OPERATION

Input Multiplexers/Input Buffers/Overlap Program Inputs DETAILED DESCRIPTION

Input Multiplexers

Input multiplexers interface external control inputs (from connectors A, B, C and D) with the sys-

tem data bus. The processor controls the multiplexer functions by enabling the multiplexer, ad-

dressing the inputs, and reading the input status. In this way, it controls the 16 HCMOS tri-

state, 8-bit multiplexers U51, U52, U53, U54, U55, U56, U58 and U60 (74HC251) [14-15,1-6,A-

D] on the ASC/2S-2000 plus U40, U41, U42, U43, U47, U48, U49, U50 on the ASC/2S-2100.

Each multiplexer receives eight external control inputs from a corresponding logic level transla-

tor. Each control input has a unique address associated with it. When the input is addressed

and the multiplexer is enabled, the input status (ON/OFF) is routed to a single data bit at the

multiplexer output pin (W) connected to the data bus.

The processor reads the input data by addressing it through the I/O Interface address bus BA1-

BA3. The selected input is gated onto the I/O data bus by the LOW state of signal I/O0 or I/O1.

The processor simultaneously reads eight I/O data bits from 8 different multiplexors onto BD0-

BD7.

Typical input operation is described below.

The signal from input pin A1-/h (PHASE 1 HOLD) [15,4,D] is applied, via logic level translator

RP22 [15,4,D] to input DO (pin 4), of input multiplexer U58. Coded address bits BA1-BA3 from

the address bus are applied to address select inputs S0, S1, and S2 (pins 11, 10, and 9) of in-

put multiplexer U29. When address lines BA1-BA3 are all LOW, input D0, pin 4 of input multi-

plexer U29 is selected. The LOW state of signal I/O0 enables the multiplexer and causes the

selected input to be inverted and output from /Y (pin 6) as I/O module data bit BD0.

Input Buffers

Input buffers U19A and U59 (74HCT244) [12,6,B-C] transfer local and external data to the data

bus. U59 receives its inputs from logic level translator RP23. U19A inputs a combination of ex-

ternal and local status inputs. On an ASC/2S-2100, input buffer U30B (74HCT244) [12,3,B-C]

and U57 get their inputs from the 25-pin telemetry connector via logic level translators RP36

and RP35 respectively. The buffers output their data onto the data bus when the proper chip

select line /Y4-/Y8 goes low. Among other signals, U19A inputs the signal that tells the proces-

sor, when low, that the board is configured as an ASC/2S-2100.

Overlap Program Inputs

On the ASC/2S-2100, a NEMA overlap program card is optionally available for programming

overlaps A-D. This plug-in card is connected to optional connector J6 [11,1,D]. Phase combi-

nations of the four programmable overlap phases A, B, C and D are programmed by installing

jumpers on the card. When the overlap card is installed, the jumpers ground the 10K pull-up

resistors, RP5-RP8 [17-18,3,B-D] at the (74HC251) multiplexer inputs. A ground at these inputs

indicates that the associated phase is assigned to the overlap while an open circuit indicates

that it is not. Program data for each overlap phase (A-D) is output by the multiplexers as eight

bits representing the eight controller phases N1-N8. The overlap inputs are read by the proces-

sor at the multiplexer output pins as described above.

2-24

THEORY OF OPERATION Parallel I/O Interface

DETAILED DESCRIPTION Output Latches

Output Latches

Output latches are used to interface data from the system data bus with external control output

lines. The processor controls the data transfer by enabling the latches and addressing the out-

put, thus latching the data from the data bus to be sent to external equipment. In this way, it

controls twelve addressable 8-bit output latches, U31, U32, U33, U34, U35, U36, U37, U44,

U45, U46, U61 and U62 (74HC259) [13-14,1-6,A-D] with associated output drivers, U67, U68,

U69, U70, U71, U72, U73, U74, U75, U76, U77 and U78 (ULN2803A) on an ASC/2S-2000. In

addition the ASC/2S-2100 also includes latches U26-U29 [19,1-6, A-D] and associated output

drivers U63-U66. All output drivers are biased to the 24 V (FALSE) state, when not asserted,

through a 10K pull-up resistor.

Latches are addressed by bits A1-A3 and enabled by the /LE0 and /LE1 signals from the I/O

device selector U23 [12,6,D]. At the same time, data bits DB0-DB7 are input to the addressed

latches.

Data is latched on the rising edges of the enable signals and remains latched until changed dur-

ing a data update from the processor, which occurs every 100 ms. The buffered /RESET signal,

/IORESET [4,2,B], clears all data from the latches at power on.

The Q outputs of each latch are applied to a high-current, high-voltage, Darlington transistor

output driver (ULN2803A). Logic level transition to +24V (FALSE) and 0 V (TRUE) occurs at

the driver outputs. Output lines are connected to interface connectors A, B C and D.

The ULN2803 output drivers are protected from transients on their output pins by Transient

Voltage Suppressors CR16 and CR19 (P6KE33A) [13,3,C] [19,3,C]. These provide the output

devices with a low impedance path to ground for voltages greater than 33VDC. This prevents

damage to a driver by the reverse voltage generated when a relay coil connected to the output

is de-energized or other transient occurs.

The FLASH LOGIC OUT output on A1-X [14,3,A] is derived from the Q4 output of latch U62

(74HC259) [14,6,B]. When this output is active, output driver U78 (ULN2803A), sinks current

from A1-X through diode CR15. When U78 is off, Q2 (MMBT2222ALT1) [14,4,A], is turned on

and current is sourced to A1-X through the current sourcing circuit consisting of transistor Q2

diodes CR17-CR20 and current limit resistors R57-R58. This output can source 50mA maxi-

mum and can sink 200mA maximum. Diode CR20 shunts any negative voltages on the output

to ground. CR17 shunts any voltage greater than 33VDC to ground.

On the ASC/2S-2100 the PREEMPT CMU INTERLOCK output associated with U27 (pin 5)

[19,5,B] is active only if there is a preemption requirement. The circuit consists of Q3

(MMBT2222ALT) [19,3,C] R62, CR16 and CR21. If a preemption sequence is not programmed,

this output is forced LOW. This output can be connected to the conflict monitor 24 V monitor

input to set the intersection to flash if a required preempt sequence is not programmed.

The voltage monitor VMC and fault monitor /FLTMN signals, generated by U11 [8,1,C], detect

out of tolerance voltage levels and processor failures and send control signals to the I/O section

to be output as VOLTAGE MONITOR and FAULT MONITOR. The VMC signal is inverted and

buffered by U78 (ULN2803A) [14,5,B] and routed to A1-C. The /FLTMN signal is inverted and

buffered by U74A (ULN2803A) [14,3,C] and routed to J16-F.

2-25

Parallel I/O Interface THEORY OF OPERATION

SDLC Interface/Terminal Interface DETAILED DESCRIPTION

SDLC (EIA-485) Interface

The SDLC interface circuit sends and receives its signals on the SDLC bus. All TTL to EIA-485

signal level translation is provided by U81 and U82 (LT690) [7,6,C]. These contain one EIA-485

driver and one EIA-485 receiver each. After the signals are translated to EIA-485, they are routed

to the outside world via connector J15 (DA15S) [7,4,D] The interface includes the following sig-

nals:

TXD+ and TXD- are the differential transmit data pair. The processor transmits this serial data

signal as TXD3 from SCC3 [2,5,C]. This signal is converted to a differential pair by U81. It is then

output on connector J15 pins 1 and 9.

TXC+ and TXC- are the differential transmit clock pair. The processor transmits this serial data

signal as TCLK3 from SCC3 [2,5,C]. The signal is converted to a differential pair by U82. It is

then output on connector J15 pins 3 and 11.

RXD+ and RXD- are the differential receive data pair. These signals appear on pins 5 and 13 of

connector I/O2P5. After conversion by U81, the single ended TTL signal is routed to SCC3 on the

processor as RXD3 [2,5,C].

RXC+ and RXC- are the differential receive clock pair. These signals appear on pins 7 and 15 of

connector I/O2P5. After translation by U82, the single ended TTL signal is routed to SCC3 on the

processor as RCLK3 [2,5,C].

Terminal (EIA-232) Interface

The terminal interface circuit sends and receives its signals on the terminal bus. All TTL to EIA-

232 signal level translation is provided by U80 (MAX214) [7,2,C] which contains three EIA-232

drivers and three EIA-232 receivers. U80 uses capacitors C66, C67, C71 and C72 for its onboard

positive and negative voltage generation circuits. U80 also has an internal DCE/DTE switch that is

controlled by TERMCTRL1 [7,3,B]. Terminal signals are routed to the outside world via connector

J13 (DB25) [7,1,C]. The EIA-232 level signals are protected against over voltage transients by

transient voltage suppressors (MMBZ15VDLT1) [7,1,B]. The interface contains the following sig-

nals:

TXD is the transmit data signal. The processor outputs this serial signal from SCC2 as TXD2

[2,5,C]. After translation, it appears on pin 2 of J13.

RXD is the receive data signal. This serial input signal appears on pin 3 of J13. It is translated

and routed to SCC2 of the processor as RXD2 [2,5,C]. This signal is also routed to the DUART

U20 [4,5,B] as RXDB.

CD is the Data Carrier Detect handshaking signal. This input signal appears on pin 8 of J13. It

is translated and routed to SCC2 of the processor as /CD2 [2,5,C].

CTS is the Clear To Send handshaking signal. This input signal appears on pin 5 of J13. It is

translated and routed to SCC2 of the processor as /CTS2 [2,5,C].

RTS is the Request To Send handshaking signal. The processor outputs this serial signal from

SCC2 as /RTS2 [2,5,C]. After translation, it appears on pin 4 of J13.

2-26

THEORY OF OPERATION Parallel I/O Interface

DETAILED DESCRIPTION SDLC Interface/Telemetry Interface

DTR is the Data Terminal Ready handshaking signal. DUART U2 [4,5,A] outputs this serial sig-

nal from OP2 as /DTRT. After translation, it appears on pin 20 of J13.

Signals RTS, CTS, CD and DTR are handled under program control and are implemented only

as required. Communications with a printer utilize the XON / XOFF software handshake proto-

col.

Telemetry Interface

The Telemetry interface sends and receives its signals on the Telemetry bus. The signals are

routed to the telemetry module connector J4 [7,5,B], translated by the telemetry module and

then routed to the outside world via connectors J17 (DE9P) [7,3,B] and J14 (DB25P) [7,4,A]. All

TTL to FSK, EIA-232 or EIA-485 signal level translation is provided by the telemetry module at-

tached to connector J4. The interface contains the following signals:

TXD is the transmit data signal. The DUART U20 [4,5,B] outputs this serial signal to the telem-

etry module as TXDA. After translation, it is routed to J17, pins 1 and 2, and expansion I/O

connector J14 as signal pair XMIT+ and XMIT-.

RXD is the receive data signal. This serial input signal appears on pins 4 and 5 of J17 and ex-

pansion I/O connector J14 as RECV+ and RECV- then routed to J4. It is translated by the Te-

lemetry module and routed to SCC1 of the processor as RXD1 [2,5,D].

CD is the Data Carrier Detect handshaking signal. This signal is generated by the FSK teleme-

try module and appears on pin 9 of J4. It is routed to the DUART as /CDA [4,5,B]. EIA-232 te-

lemetry modules input this signal form J17 pin 1.

CTS is the Clear To Send handshaking signal. This input signal, generated by the telemetry