Arm Cortex M0 And M0+ System Design Kit Example Guide M0+System DUI0559D R1p1 00rel0

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 100

- Arm Cortex-M0 and Cortex-M0+ System Design Kit Example System Guide

- Contents

- Preface

- 1: Introduction

- 2: Functional description

- 2.1 System-level design and design hierarchy

- 2.2 Design files

- 2.3 Processor file locations

- 2.4 Configuration options

- 2.5 Memory map

- 2.6 System controller

- 2.7 I/O pins

- 2.8 Interrupts and event functions

- 2.9 AHB system ROM table

- 2.10 Clock and reset

- 2.11 SysTick support

- 2.12 Handling the Engineering Change Order (ECO) Revision Number in ID registers

- 3: Example system testbench

- 4: Using the simulation environment

- 5: Software examples

- 6: Synthesis

- A: Debug tester

- B: Revisions

Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved.

ARM DUI 0559D (ID110117)

Arm® Cortex®-M0 and Cortex-M0+

System Design Kit

Revision: r1p1

Example System Guide

Confidential

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. ii

ID110117 Confidential

Arm Cortex-M0 and Cortex-M0+ System Design Kit

Example System Guide

Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved.

Release Information

The following changes have been made to this book.

Proprietary Notice

This document is CONFIDENTIAL and any use by you is subject to the terms of the agreement between you and Arm

or the terms of the agreement between you and the party authorised by Arm to disclose this document to you.

This document is protected by copyright and other related rights and the practice or implementation of the information

contained in this document may be protected by one or more patents or pending patent applications. No part of this

document may be reproduced in any form by any means without the express prior written permission of Arm. No

license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this

document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit

others to use the information: (i) for the purposes of determining whether implementations infringe any third party

patents; (ii) for developing technology or products which avoid any of Arm’s intellectual property; or (iii) as a reference

for modifying existing patents or patent applications or creating any continuation, continuation in part, or extension of

existing patents or patent applications; or (iv) for generating data for publication or disclosure to third parties, which

compares the performance or functionality of the Arm technology described in this document with any other products

created by you or a third party, without obtaining Arm’s prior written consent.

THIS DOCUMENT IS PROVIDED “AS IS”. ARM PROVIDES NO REPRESENTATIONS AND NO

WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED

WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS

FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes

no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of,

third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES,

INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR

CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY,

ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written

agreement covering this document with Arm, then the click through or signed written agreement prevails over and

supersedes the conflicting provisions of these terms. This document may be translated into other languages for

convenience, and you agree that if there is any conflict between the English version of this document and any

translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or

its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document

may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at

http://www.arm.com/company/policies/trademarks.

Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

Change history

Date Issue Confidentiality Change

17 March 2011 A Non-Confidential First release for r0p0

15 June 2011 B Confidential Second release for r0p0

19 April 2013 C Confidential First release for r1p0

31 October 2017 D Confidential First release for r1p1

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. iii

ID110117 Confidential

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20348

Confidentiality Status

This document is Confidential. This document may only be used and distributed in accordance with the terms of the

agreement entered into by Arm and the party that Arm delivered this document to.

Product Status

The information in this document is final, that is for a developed product.

Web Address

http://www.arm.com

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. iv

ID110117 Confidential

Contents

Arm Cortex-M0 and Cortex-M0+ System Design Kit

Example System Guide

Preface

About this book .......................................................................................................... vii

Feedback .................................................................................................................... xi

Chapter 1 Introduction

1.1 About the Cortex-M0 and Cortex-M0+ System Design Kit ...................................... 1-2

1.2 Cortex-M0 and Cortex-M0+ System Design Kit directory structure ......................... 1-3

1.3 Limitations of the design kit ..................................................................................... 1-5

Chapter 2 Functional description

2.1 System-level design and design hierarchy .............................................................. 2-2

2.2 Design files .............................................................................................................. 2-8

2.3 Processor file locations .......................................................................................... 2-10

2.4 Configuration options ............................................................................................. 2-11

2.5 Memory map .......................................................................................................... 2-16

2.6 System controller ................................................................................................... 2-19

2.7 I/O pins .................................................................................................................. 2-22

2.8 Interrupts and event functions ............................................................................... 2-24

2.9 AHB system ROM table ......................................................................................... 2-26

2.10 Clock and reset ...................................................................................................... 2-27

2.11 SysTick support ..................................................................................................... 2-28

2.12 Handling the Engineering Change Order (ECO) Revision Number in ID registers 2-29

Chapter 3 Example system testbench

3.1 About the testbench design ..................................................................................... 3-2

3.2 UART text output capturing and escape code ......................................................... 3-3

Contents

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. v

ID110117 Confidential

3.3 Debug tester ............................................................................................................ 3-4

Chapter 4 Using the simulation environment

4.1 About the simulation environment ........................................................................... 4-2

4.2 Files and directory structure .................................................................................... 4-3

4.3 Setting up the simulation environment ..................................................................... 4-5

4.4 Running a simulation in the simulation environment ............................................... 4-8

Chapter 5 Software examples

5.1 Available simulation tests ........................................................................................ 5-2

5.2 Creating a new test .................................................................................................. 5-5

5.3 Example header files and device driver files ........................................................... 5-6

5.4 Retargeting .............................................................................................................. 5-8

5.5 Example device driver software ............................................................................... 5-9

Chapter 6 Synthesis

6.1 Implementation overview ......................................................................................... 6-2

6.2 Directory structure and files ..................................................................................... 6-3

6.3 Implementation flow ................................................................................................. 6-4

6.4 Timing constraints .................................................................................................... 6-5

Appendix A Debug tester

A.1 About the debug tester ............................................................................................ A-2

A.2 Memory map ............................................................................................................ A-3

A.3 Debug tester software .............................................................................................. A-4

Appendix B Revisions

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. vi

ID110117 Confidential

Preface

This preface introduces the Cortex-M0 and Cortex-M0+ System Design Kit Example System

Guide. It contains the following sections:

•About this book on page vii.

•Feedback on page xi.

Preface

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. vii

ID110117 Confidential

About this book

This book is for the Cortex-M0 and Cortex-M0+ System Design Kit.

Implementation obligations

This book is designed to help you implement an Arm product. The extent to which the

deliverables can be modified or disclosed is governed by the contract between Arm and the

Licensee. There might be validation requirements which, if applicable, are detailed in the

contract between Arm and the Licensee and which, if present, must be complied with prior to

the distribution of any devices incorporating the technology described in this document.

Reproduction of this document is only permitted in accordance with the licenses granted to the

Licensee.

Arm assumes no liability for your overall system design and performance. Verification

procedures defined by Arm are only intended to verify the correct implementation of the

technology licensed by Arm, and are not intended to test the functionality or performance of the

overall system. You or the Licensee are responsible for performing system level tests.

You are responsible for applications that are used in conjunction with the Arm technology

described in this document, and to minimize risks, adequate design and operating safeguards

must be provided for by you. Publishing information by Arm in this book of information

regarding third party products or services is not an express or implied approval or endorsement

of the use thereof.

Product revision status

The rnpn identifier indicates the revision status of the product described in this book, where:

rn Identifies the major revision of the product.

pn Identifies the minor revision or modification status of the product.

Intended audience

This book is written for hardware engineers, software engineers, system integrators, and system

designers, who might not have previous experience of Arm products, but want to run a complete

example of a working system.

Using this book

This book is organized into the following chapters:

Chapter 1 Introduction

Read this for an introduction to the Cortex-M0 and Cortex-M0+ System Design

Kit and its features.

Chapter 2 Functional description

Read this for a description of the design and layout of the design kit.

Chapter 3 Example system testbench

Read this for a description of the testbench components.

Chapter 4 Using the simulation environment

Read this for a description of how to set up and run simulation tests.

Chapter 5 Software examples

Read this for a description of the example software tests and the device drivers.

Preface

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. viii

ID110117 Confidential

Chapter 6 Synthesis

Read this for a description of how to run synthesis for the example system.

Appendix A Debug tester

Read this for a description of the debug components in the design kit.

Appendix B Revisions

Read this for a description of the technical changes between released issues of this

book.

Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for

those terms. The Arm® Glossary does not contain terms that are industry standard unless the

Arm meaning differs from the generally accepted meaning.

See Arm® Glossary

http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html

.

Conventions

This book uses the conventions that are described in:

•Typographical conventions.

•Timing diagrams.

•Signals on page ix.

Typographical conventions

The following table describes the typographical conventions:

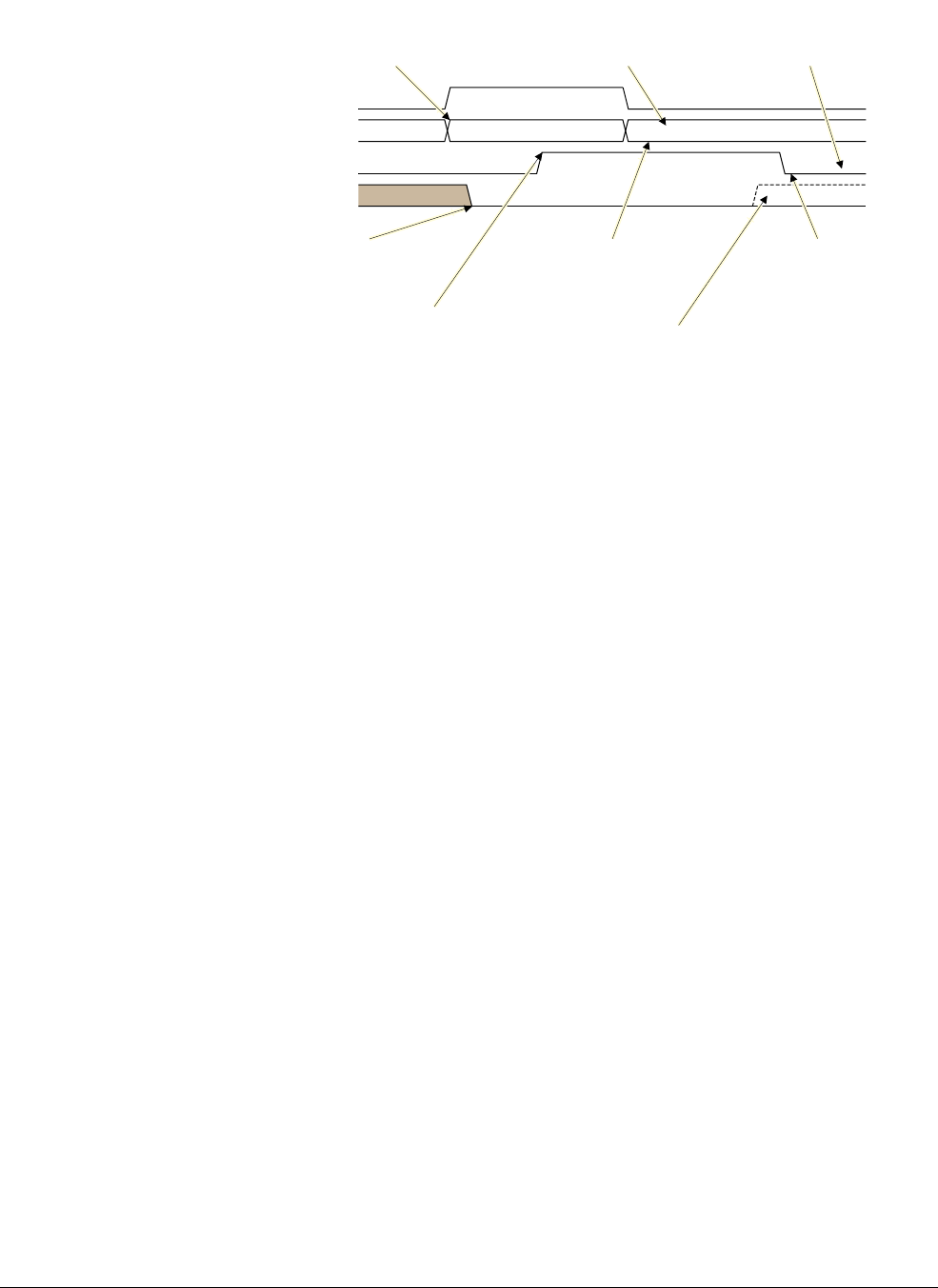

Timing diagrams

The figure named Key to timing diagram conventions on page ix explains the components used

in timing diagrams. Variations, when they occur, have clear labels. You must not assume any

timing information that is not explicit in the diagrams.

Style Purpose

italic Introduces special terminology, denotes cross-references, and citations.

bold Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive

lists, where appropriate.

monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full

command or option name.

monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

monospace bold

Denotes language keywords when used outside example code.

<and> Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode_2>

SMALL CAPITALS Used in body text for a few terms that have specific technical meanings, that are defined in the Arm glossary.

For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

Preface

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. ix

ID110117 Confidential

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the

shaded area at that time. The actual level is unimportant and does not affect normal operation.

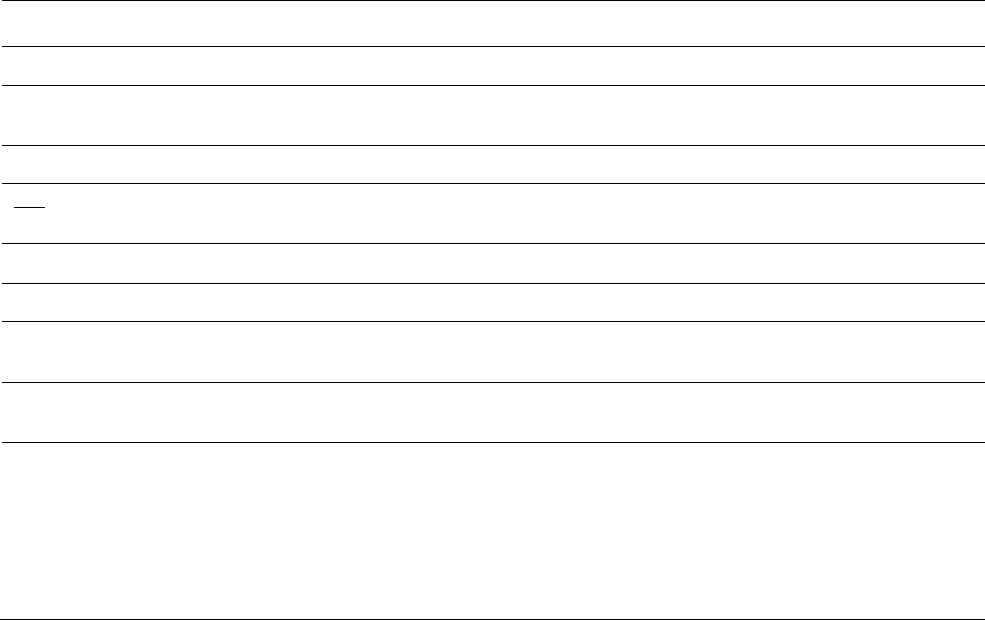

Key to timing diagram conventions

Timing diagrams sometimes show single-bit signals as HIGH and LOW at the same time and

they look similar to the bus change shown in Key to timing diagram conventions. If a timing

diagram shows a single-bit signal in this way then its value does not affect the accompanying

description.

Signals

The signal conventions are:

Signal level The level of an asserted signal depends on whether the signal is

active-HIGH or active-LOW. Asserted means:

• HIGH for active-HIGH signals.

• LOW for active-LOW signals.

Lowercase n At the start or end of a signal name denotes an active-LOW signal.

Additional reading

This section lists publications by Arm and by third parties.

See Infocenter

http://infocenter.arm.com

, for access to Arm documentation.

See Arm CMSIS-Core

http://www.arm.com/cmsis

, for embedded software development

resources including the Cortex Microcontroller Software Interface Standard (CMSIS).

Arm publications

This book contains information that is specific to this product. See the following documents for

other relevant information:

•Arm® Cortex®-M System Design Kit Technical Reference Manual (ARM DDI 0479).

•Arm® Cortex®-M0 Devices Generic User Guide (ARM DUI 0497).

•Arm® Cortex®-M0 Integration and Implementation Manual (ARM DII 0238).

•Arm® Cortex®-M0 User Guide Reference Material (ARM DUI 0467).

•Arm® Cortex®-M0 Technical Reference Manual (ARM DDI 0432).

•Arm® Cortex®-M0+ Devices Generic User Guide (ARM DUI 0662).

•Arm® Cortex®-M0+ Integration and Implementation Manual (ARM DIT 0032).

Clock

HIGH to LOW

Transient

HIGH/LOW to HIGH

Bus stable

Bus to high impedance

Bus change

High impedance to stable bus

Preface

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. x

ID110117 Confidential

•Arm® Cortex®-M0+ User Guide Reference Material (ARM DUI 0605).

•Arm® Cortex®-M0+ Technical Reference Manual (ARM DDI 0484).

Preface

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. xi

ID110117 Confidential

Feedback

Arm welcomes feedback on this product and its documentation.

Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

• The product name.

• The product revision or version.

• An explanation with as much information as you can provide. Include symptoms and

diagnostic procedures if appropriate.

Feedback on content

If you have comments on content then send an e-mail to

errata@arm.com

. Give:

• The title.

• The number, ARM DUI 0559D.

• The page numbers to which your comments apply.

• A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

Note

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality

of the represented document when used with any other PDF reader.

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 1-1

ID110117 Confidential

Chapter 1

Introduction

This chapter introduces the Cortex-M0 and Cortex-M0+ System Design Kit. It contains the

following sections:

•About the Cortex-M0 and Cortex-M0+ System Design Kit on page 1-2.

•Cortex-M0 and Cortex-M0+ System Design Kit directory structure on page 1-3.

•Limitations of the design kit on page 1-5.

Introduction

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 1-2

ID110117 Confidential

1.1 About the Cortex-M0 and Cortex-M0+ System Design Kit

The Cortex-M0 and Cortex-M0+ System Design Kit provides:

• An example system-level design for the Arm Cortex-M0 and Cortex-M0+ processors.

• Reusable AMBA components for system-level development.

For information on the AMBA components that the design kit uses, see the Arm® Cortex®-M

System Design Kit Technical Reference Manual.

This document describes an example system for the Cortex-M0 and Cortex-M0+ processors.

The example system is a simple microcontroller design.

Introduction

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 1-3

ID110117 Confidential

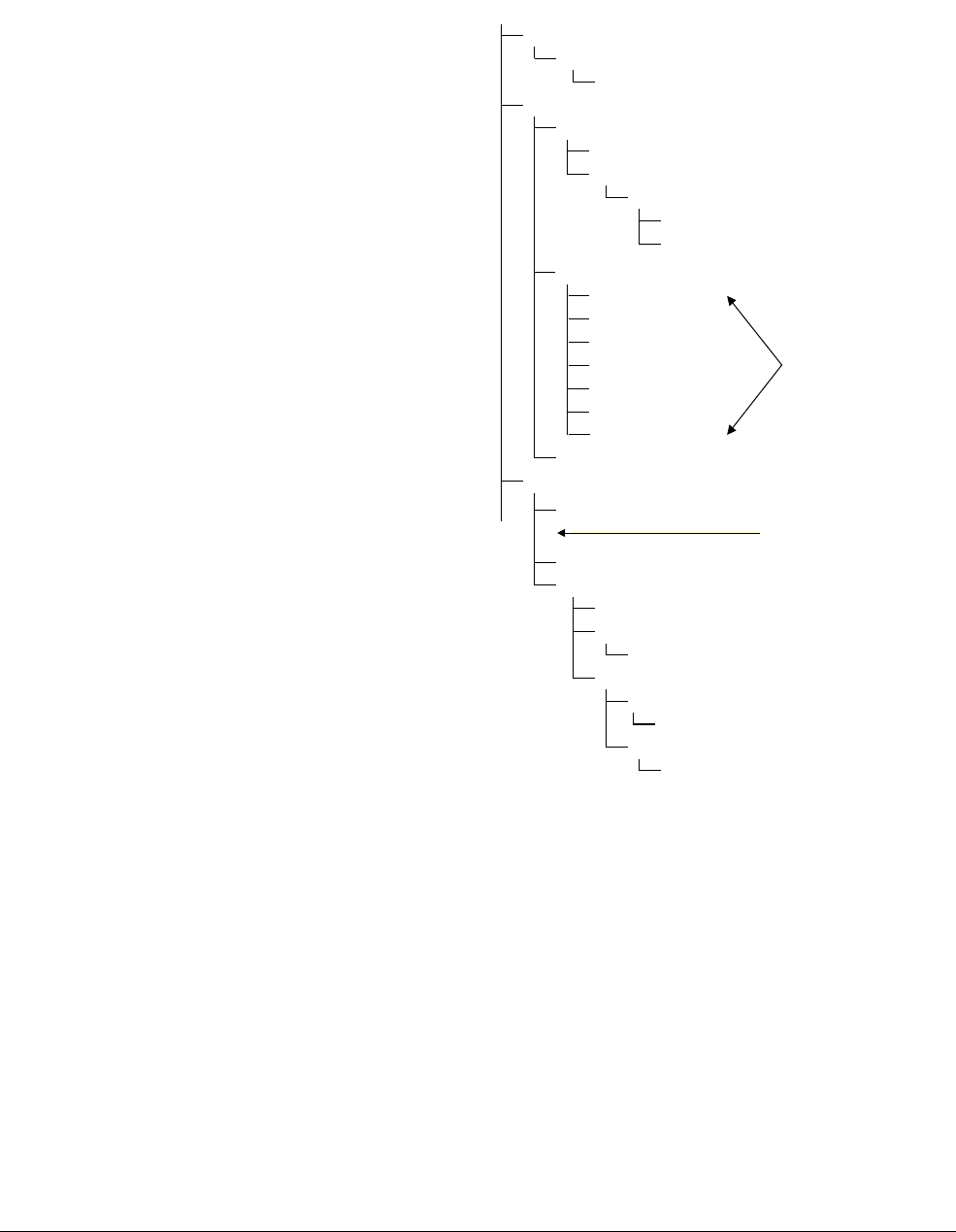

1.2 Cortex-M0 and Cortex-M0+ System Design Kit directory structure

Table 1-1 describes the main directories of the design kit.

Figure 1-1 on page 1-4 shows the location of the file directories in the design kit.

Table 1-1 Main directory descriptions

Directory name Directory contents

logical

Verilog components including AHB-Lite and APB infrastructure components, peripherals, the APB subsystem,

and the AHB-Lite and APB protocol checkers.

systems

Design files, testbench files, and simulation setup files for the example system.

implementation

Synthesis setup files for the example system. The files support the Synopsys Design Compiler.

software

Software files. These include:

• CMSIS compatible C header files.

• Example program files for the example systems.

• An example device driver.

• The debug tester software for all the processors.

document

Documentation files.

cores

This is the default location for processor core RTL files. You can change this location by modifying the simulation

and synthesis setup. The design kit does not include the processor RTL files.

Introduction

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 1-4

ID110117 Confidential

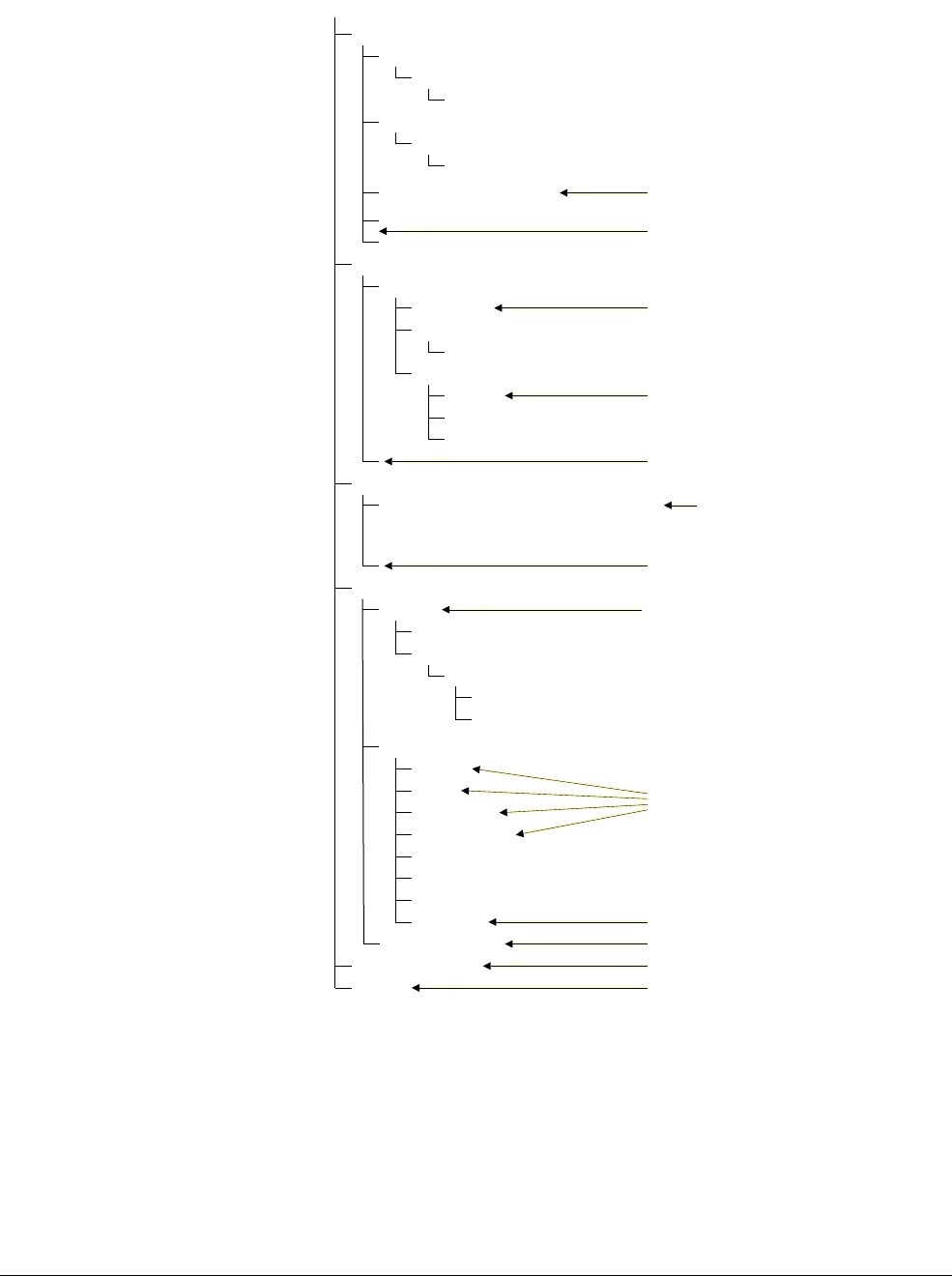

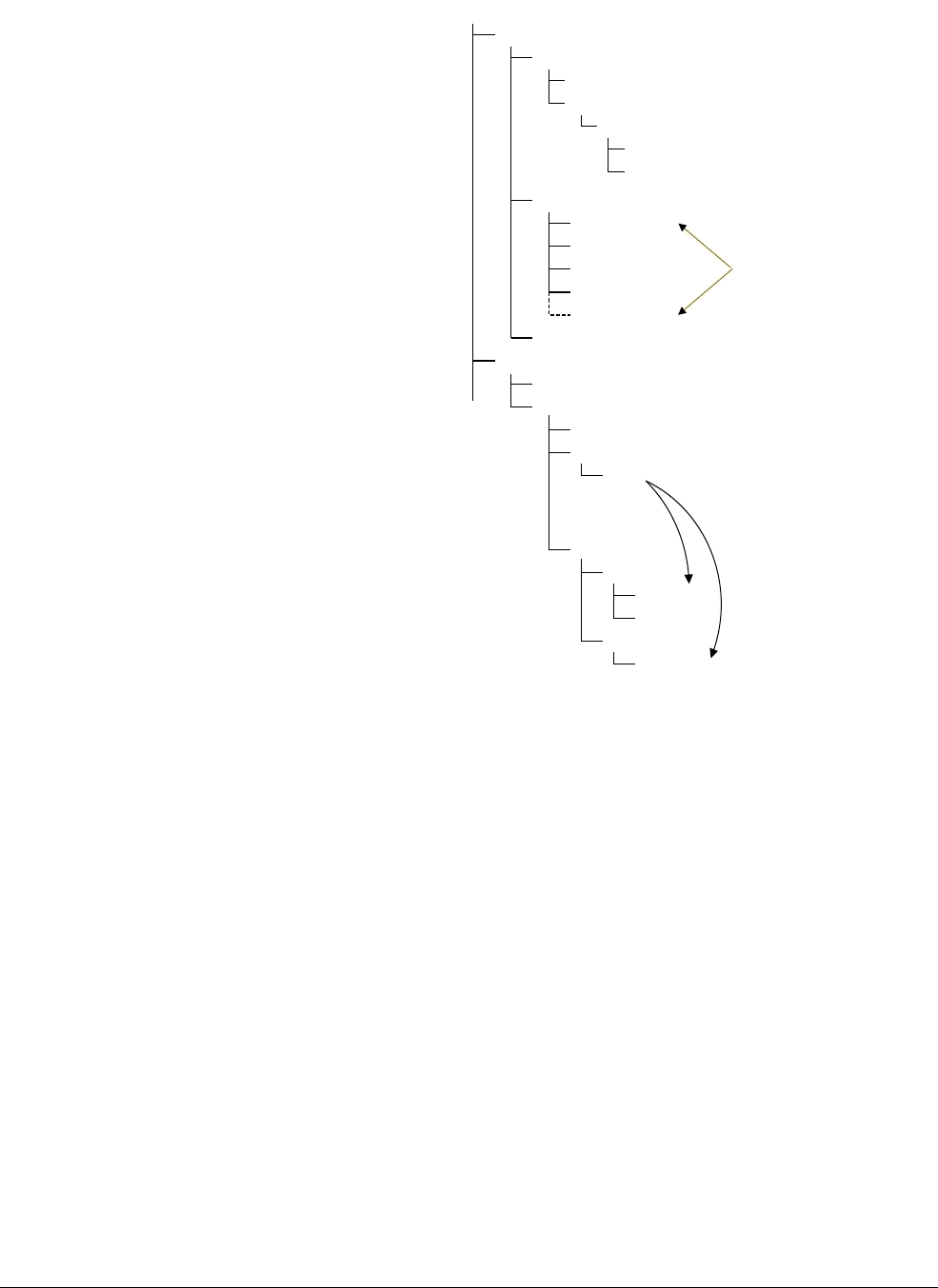

Figure 1-1 Directory structure

installation directory/

logical/

cmsdk_ahb_slave_mux/

verilog/

cmsdk_ahb_slave_mux.v

cmsdk_ahb_default_slave/

verilog/

cmsdk_ahb_default_slave.v

Directories that contain

other components

systems/

cortex_m0_mcu/

verilog/ Verilog and Verilog command files

rtl_sim/

simulation directory/

testcodes/

<testname>

cmsdk_debug_tester/ Testbench component to

test the debug interface

Other systems, when available

implementation_tsmc_ce018fg/

cortex_m0_mcu_system_synopsys/ Synthesis scripts for

synthesizable parts of the

example system

software/

cmsis/

CMSIS/

common/

demos/

dhry/

retarget/

bootloader/

scripts/

Common software files

Linker scripts and other utility scripts

documentation/ Documentation for the product

cores/ Default location for the processor RTL files

validation/

Other systems, when available

Device/

ARM/

CMSDK_CM0/

CMSDK_CM0plus/

CMSIS files, and header file for the

example system and the example

device driver code

hello/ Software compilation setup files

debug_tester/ Debug tester software

romtable_tests/

debug_tests/

Introduction

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 1-5

ID110117 Confidential

1.3 Limitations of the design kit

This section describes the limitations of the design kit.

1.3.1 Deliverables

The design kit does not include:

• Cortex-M0 processor RTL code.

• Cortex-M0+ processor RTL code.

•Direct Memory Access (DMA) Controller code.

• Software compilation tools.

You must license these products separately.

1.3.2 Processor support

The design kit supports the Cortex-M0 and Cortex-M0+ processors.

1.3.3 Endian support

The example system and its peripherals in the design kit are little-endian. The example system

also supports limited big-endian (BE)-8 byte-invariant mode for the following components:

AHB infrastructure components except the AHB bit band wrapper

These components are endian-independent.

AHB bit band wrapper

This component contains a Verilog parameter to enable you to operate in a

big-endian environment.

GPIO The AHB and I/O port GPIO support little-endian operation. They have a Verilog

parameter that you can configure to enable you to use them and their existing

device driver software in a big-endian environment. However, this increases the

gate count of the design because it introduces additional logic to control the byte

lane swapping.

Memory components

The behavioral models of the design kit components are designed to be

little-endian. However, they can also work in a big-endian system if the system

accesses each memory location with consistent transfer sizes.

APB peripherals

The APB peripherals are designed to be little-endian. The APB subsystem

provides a Verilog parameter that introduces additional endian conversion logic

to enable you to use these components and their device driver software in a

big-endian environment. Arm recommends that you do not use this parameter

because it adds extra hardware. To accomplish big-endian product design, Arm

recommends that you modify the peripherals and device drivers to use a

big-endian programmers model.

If you require a big-endian system design, Arm recommends that you redesign the peripherals

and memory blocks to achieve the lowest hardware overhead.

Introduction

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 1-6

ID110117 Confidential

1.3.4 Big-endian support with Arm GCC

By default, the GNU Tools for Arm embedded processors only support little-endian

configurations. If you use the Arm GCC in a big-endian system, you must rebuild the runtime

libraries. For information on rebuilding the toolchain, see Launchpad

https://launchpad.net/gcc-arm-embedded. You can also contact Arm for additional help.

1.3.5 Platform

This release of the Cortex-M0 and Cortex-M0+ System Design Kit supports Linux and Unix for

the simulation process and the synthesis process. If you use Keil® MDK-ARM for software

development, you can install the design kit in a location that is accessible from Linux, Unix, and

Windows. Do this using one of the following procedures:

• Install the design kit on a network drive that:

— A Linux or Unix terminal can access.

— Is mapped to a network drive on a Windows machine.

• Use a personal computer to do the following:

— Install virtualization software and install a guest Operating System (OS).

— Set up a shared folder to access the design kit through the host OS.

— Install the design kit in the shared folder.

Then compile the software with Keil MDK-ARM in the Windows environment, and run the

simulations in the Linux or Unix environment.

To run the design kit on other operating systems, modify the

makefiles

to meet your specific

requirements.

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-1

ID110117 Confidential

Chapter 2

Functional description

This chapter describes the design and layout of the design kit. It contains the following sections:

•System-level design and design hierarchy on page 2-2.

•Design files on page 2-8.

•Processor file locations on page 2-10.

•Configuration options on page 2-11.

•Memory map on page 2-16.

•System controller on page 2-19.

•I/O pins on page 2-22.

•Interrupts and event functions on page 2-24.

•AHB system ROM table on page 2-26.

•Clock and reset on page 2-27.

•SysTick support on page 2-28.

•Handling the Engineering Change Order (ECO) Revision Number in ID registers on

page 2-29.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-2

ID110117 Confidential

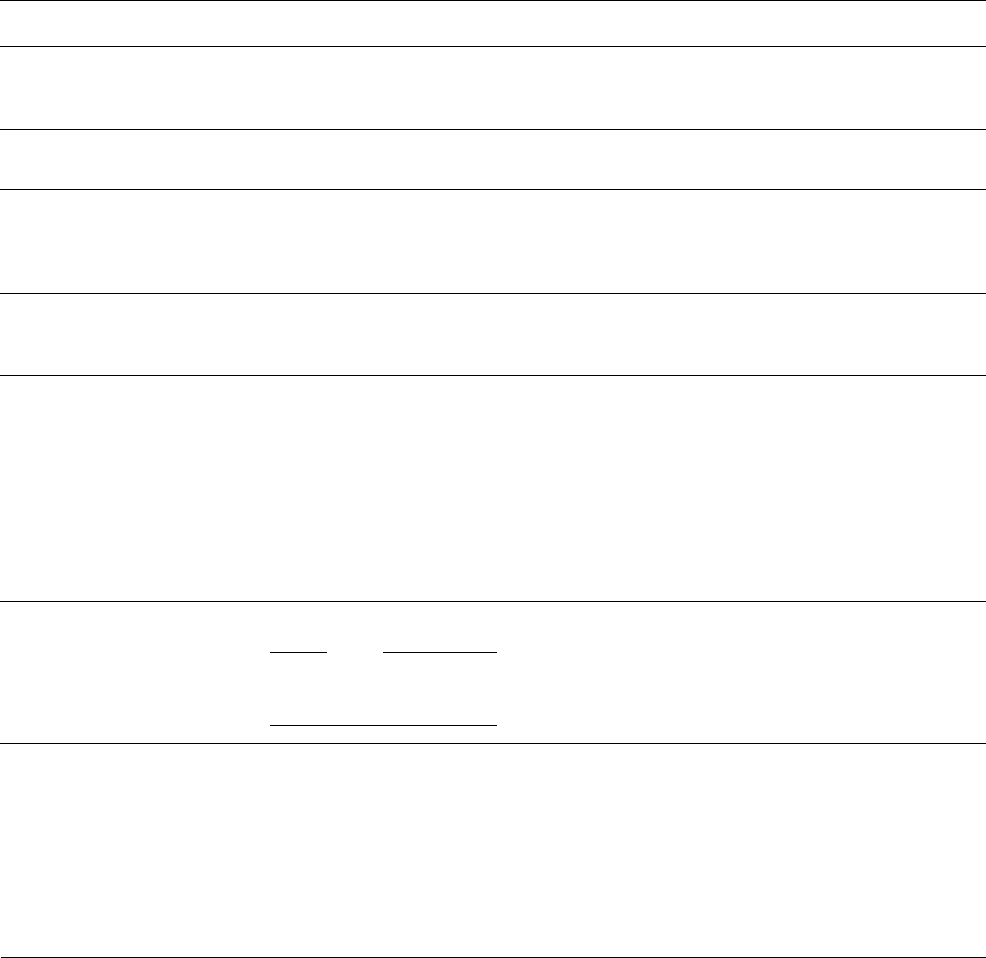

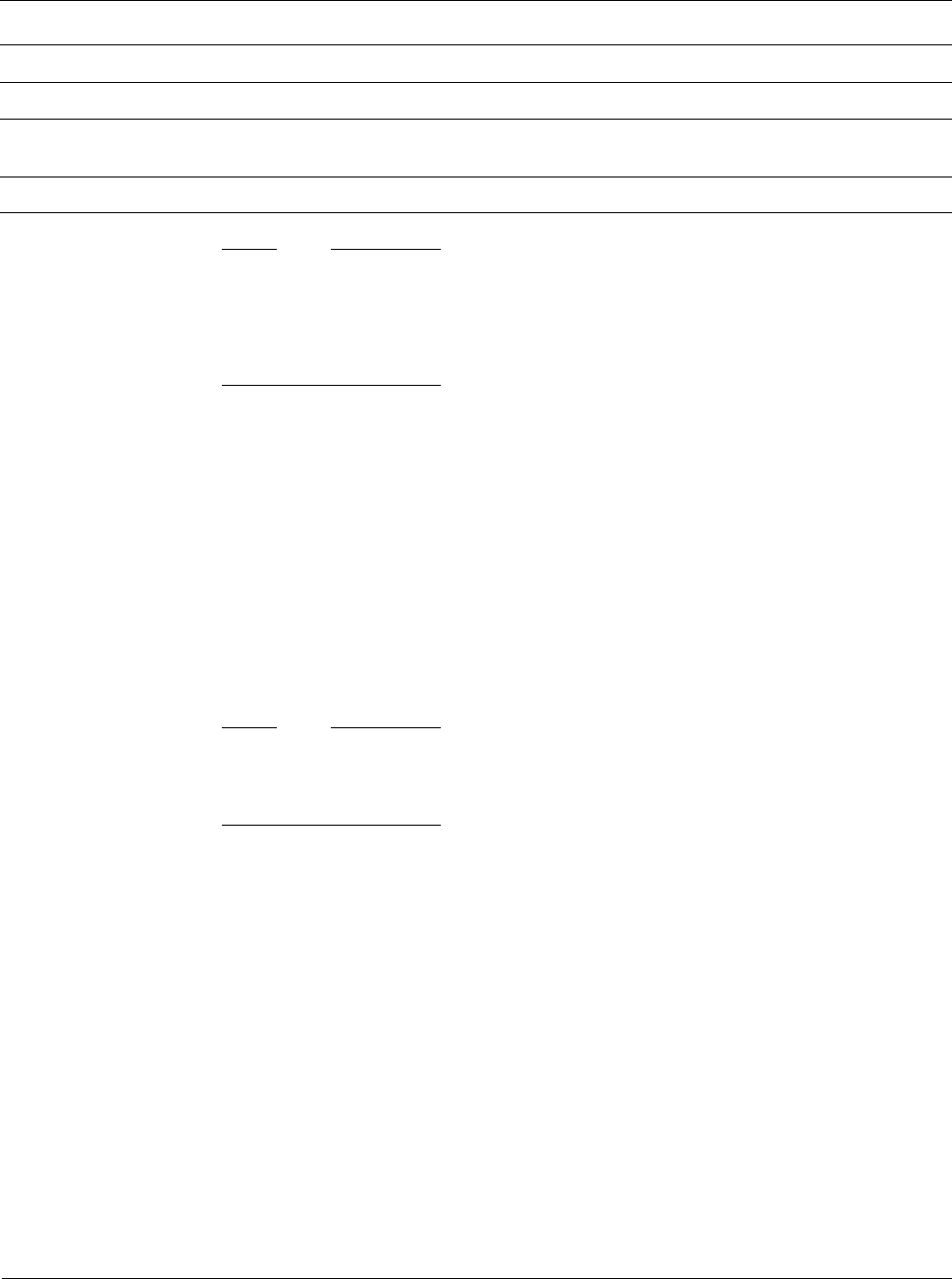

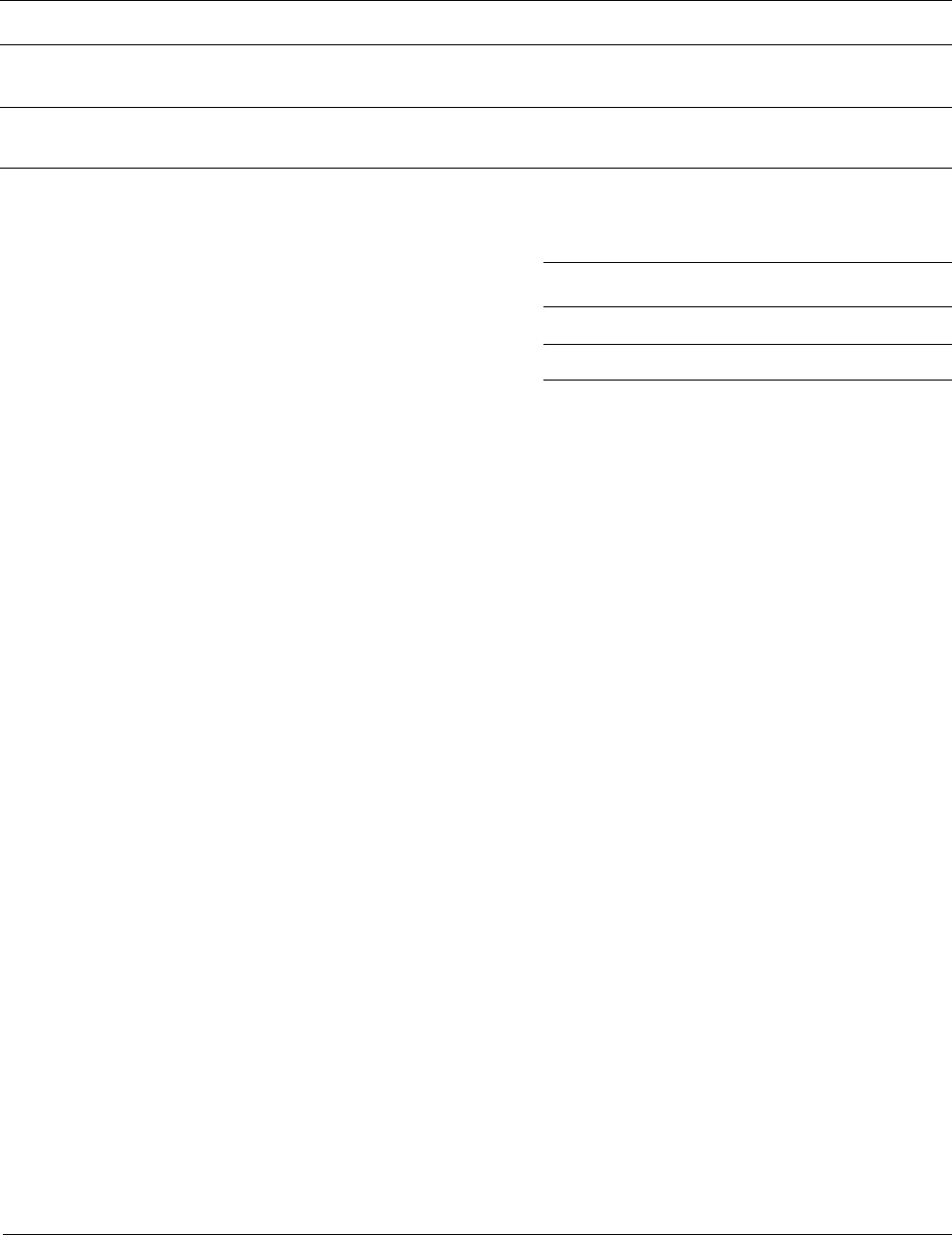

2.1 System-level design and design hierarchy

The example system is a simple microcontroller design. It contains the following:

• A single Cortex-M0 or Cortex-M0+ processor.

• Internal program memory.

• SRAM data memory.

• Boot loader.

• The following peripherals:

— Several timers.

—General Purpose Input Output (GPIO).

—Universal Asynchronous Receiver Transmitter (UART).

— Watchdog timer.

• Debug connection.

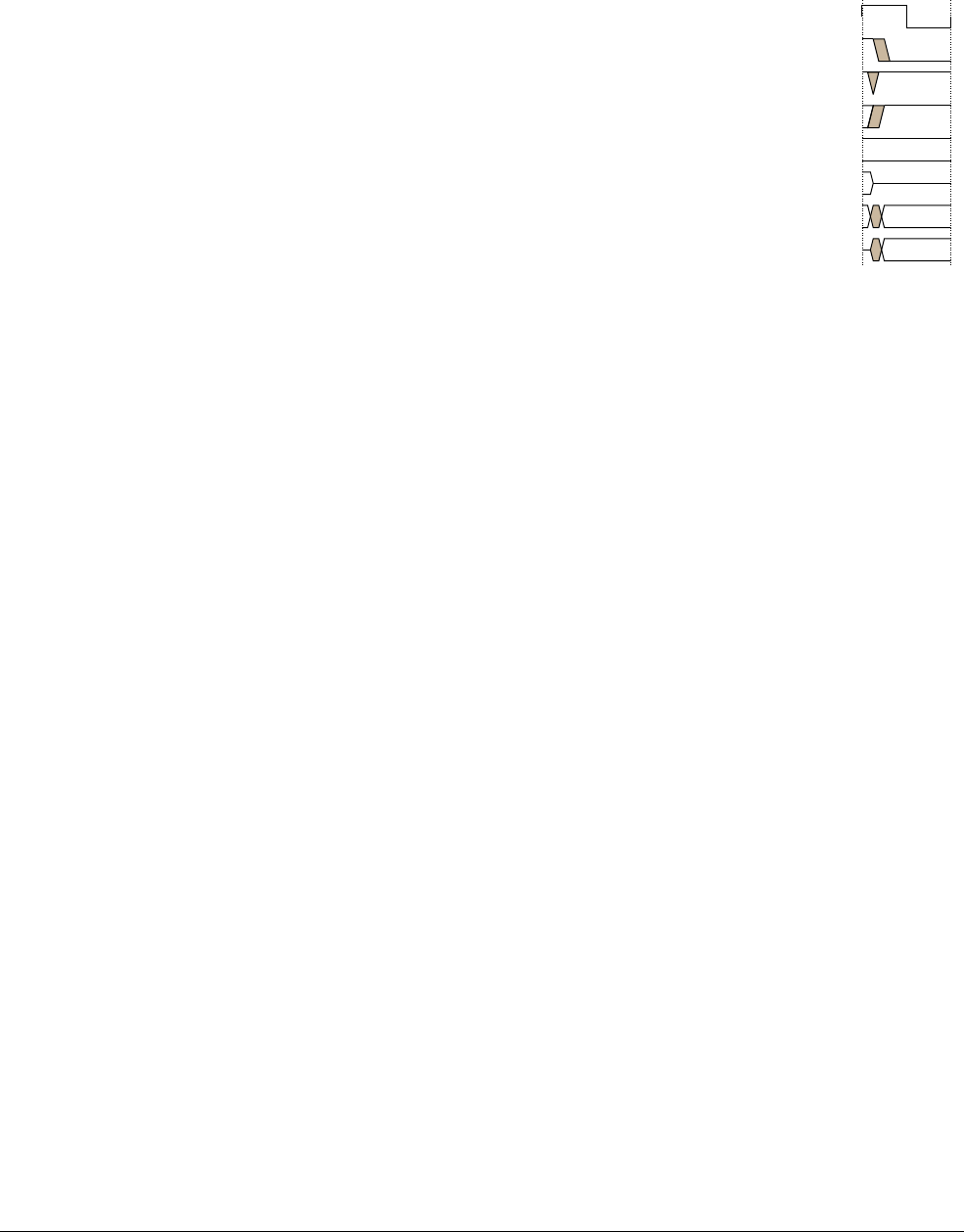

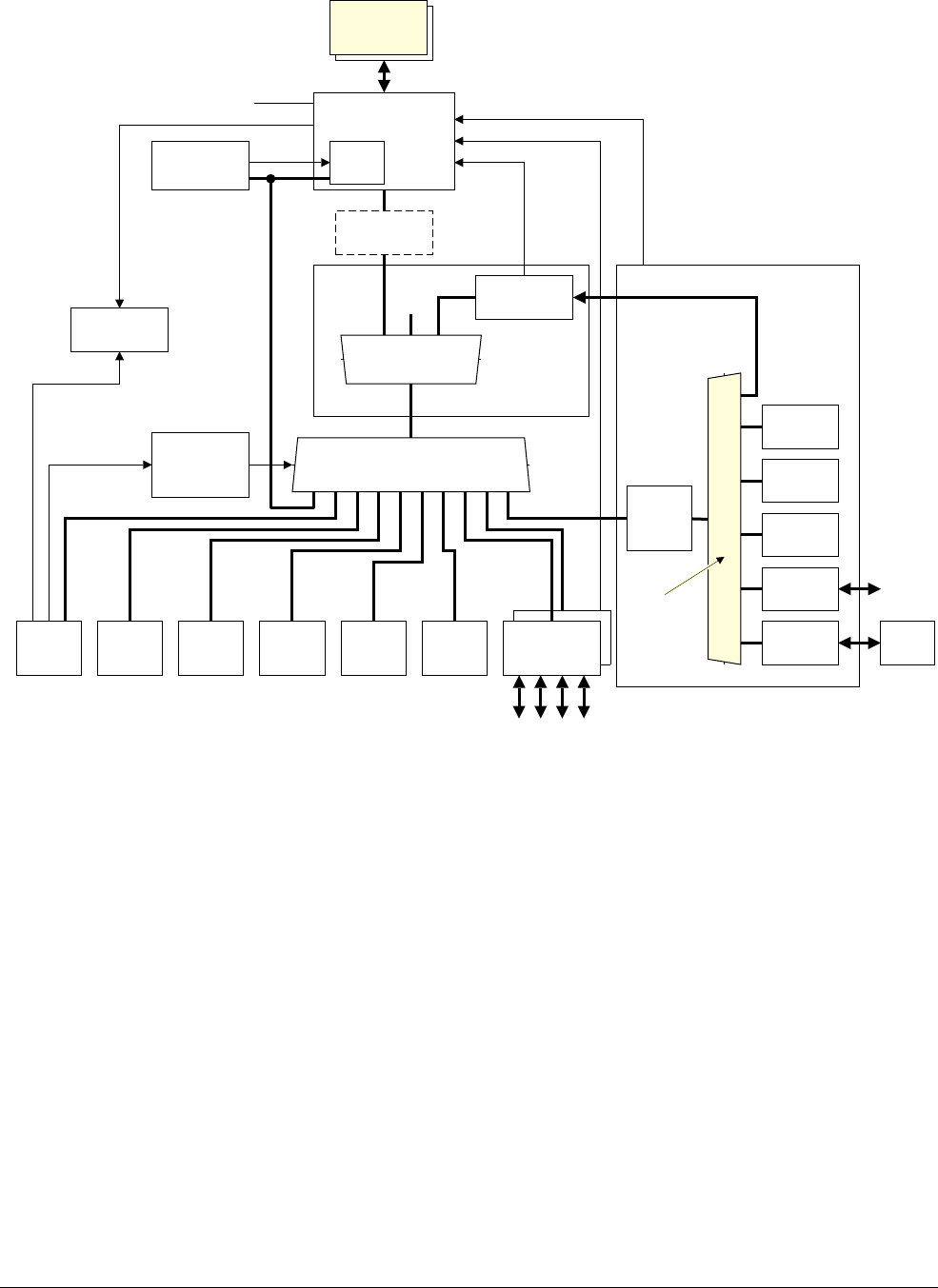

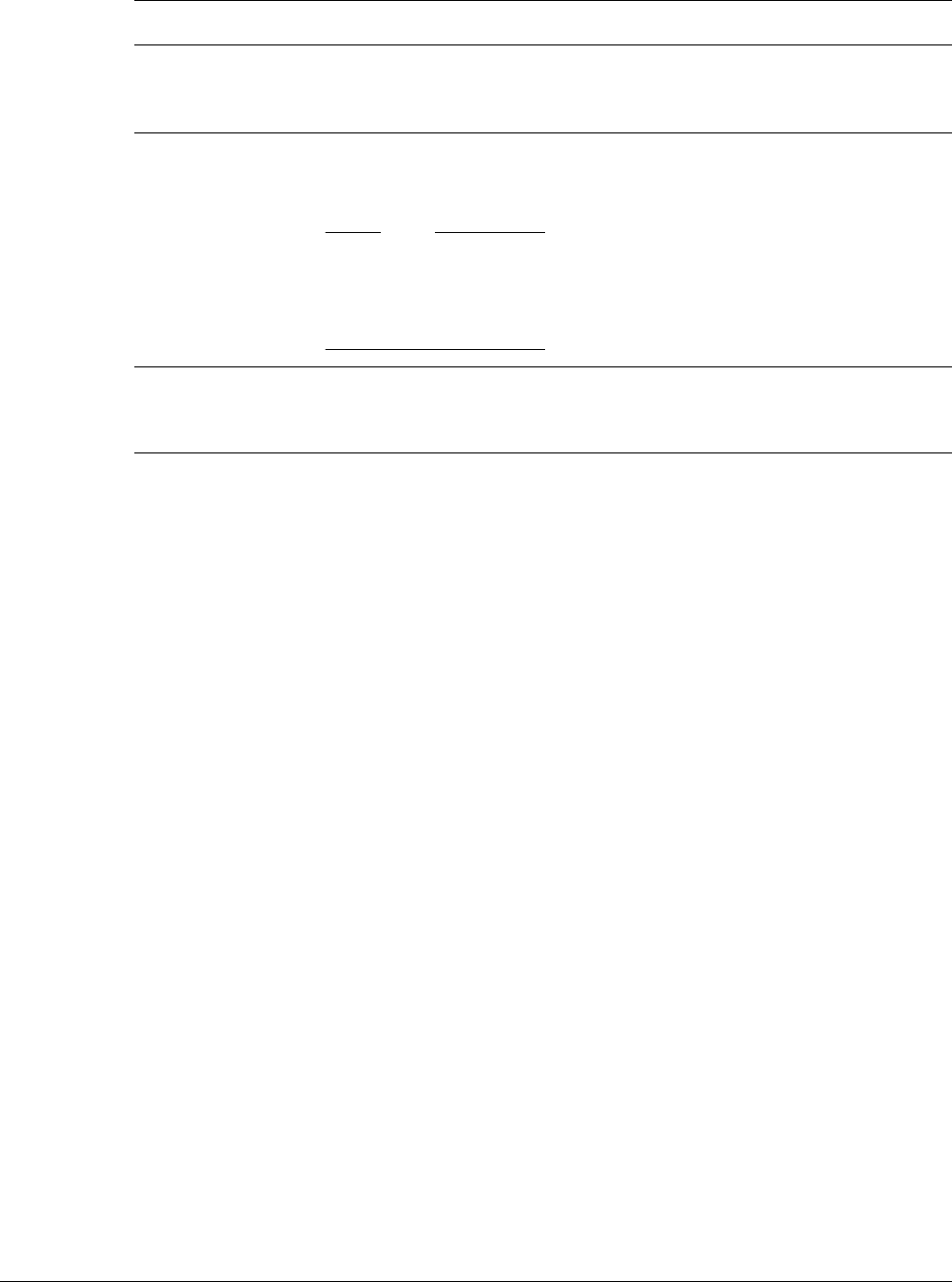

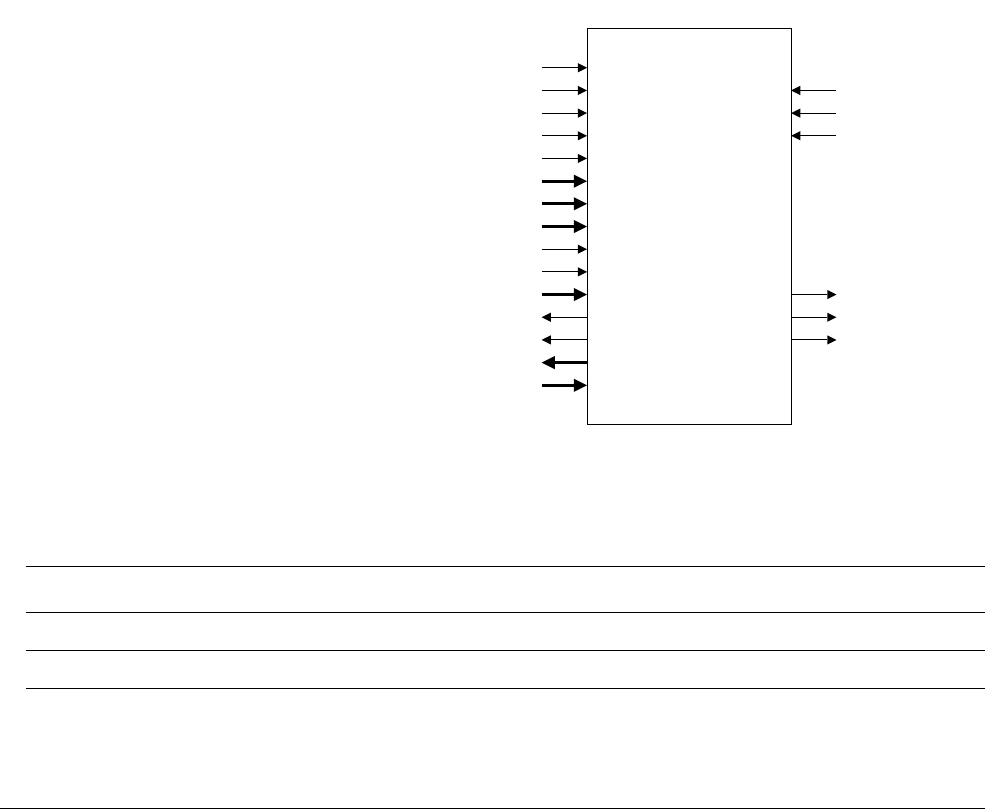

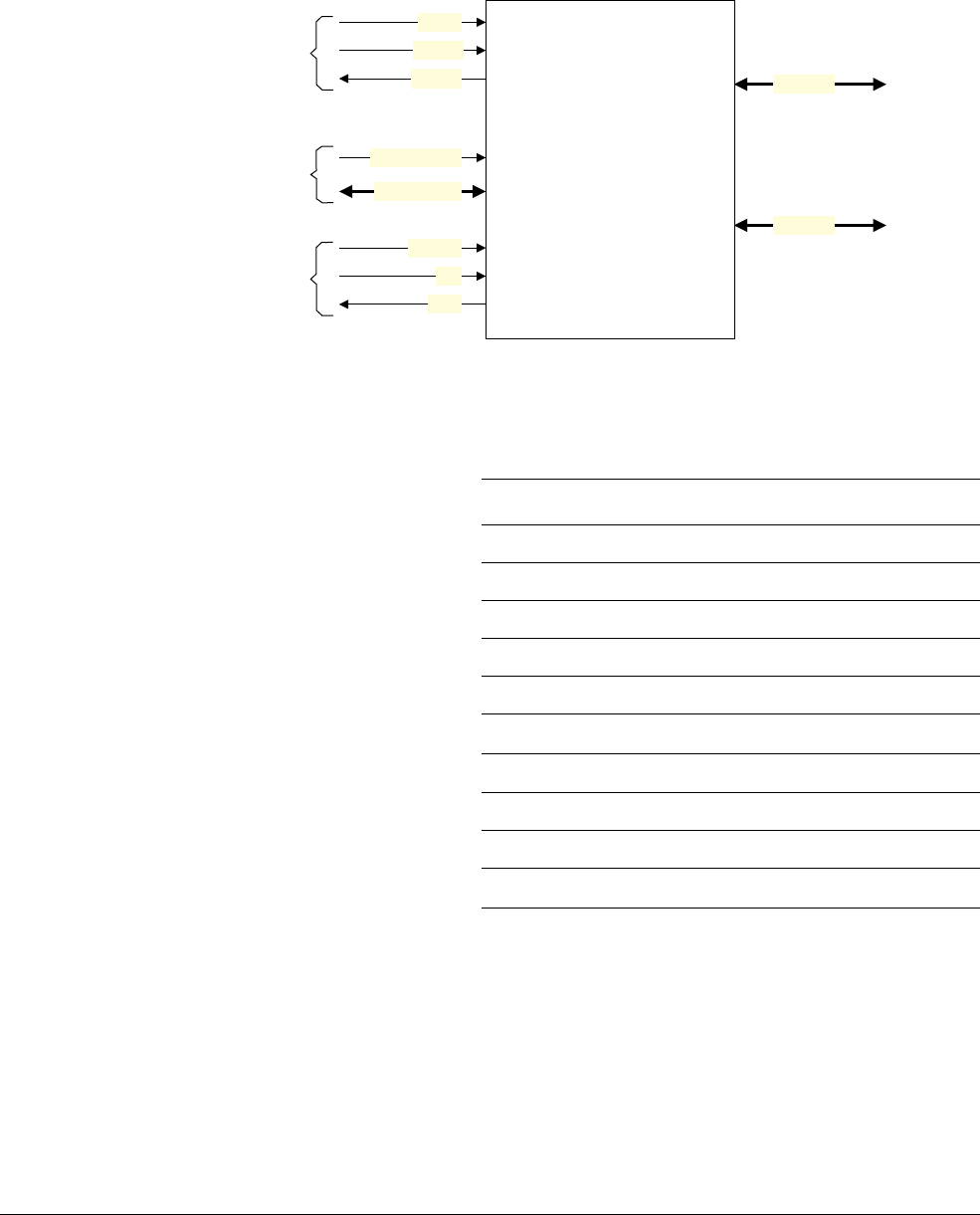

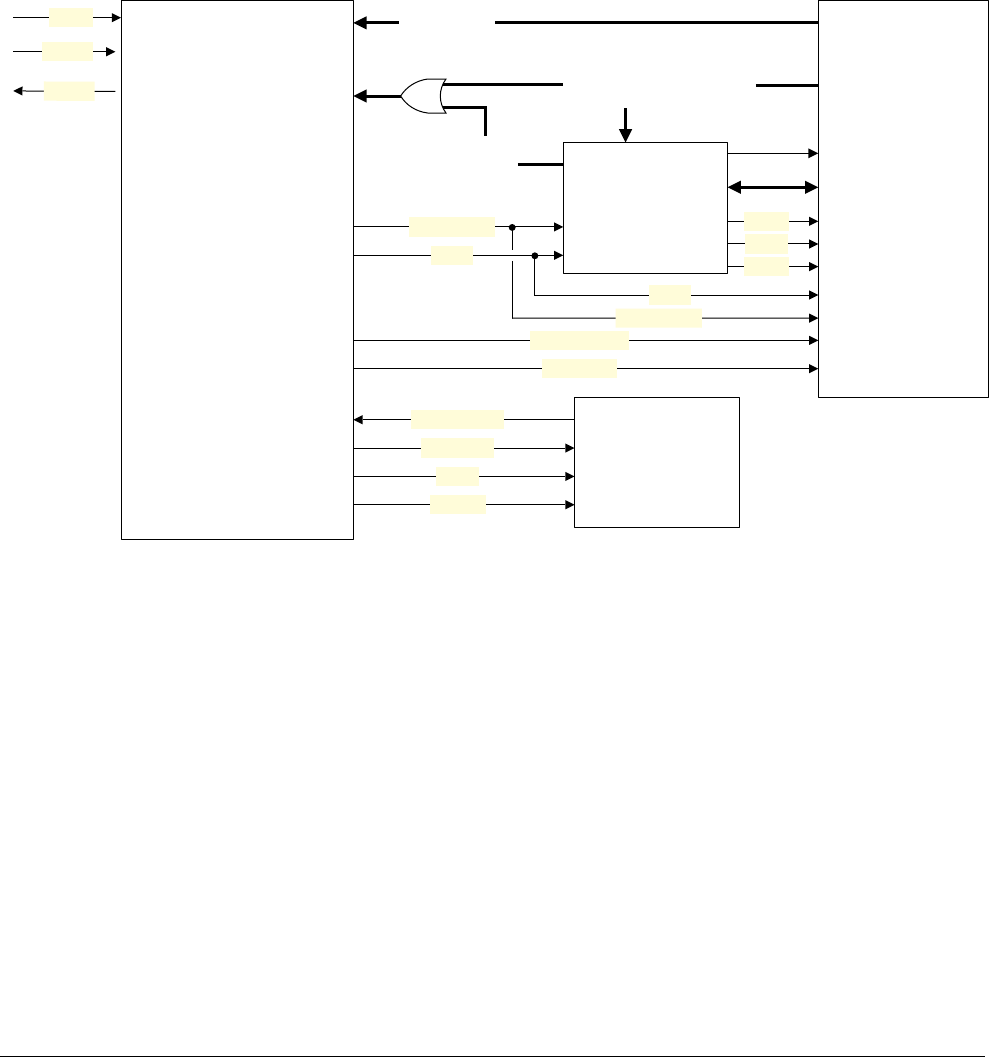

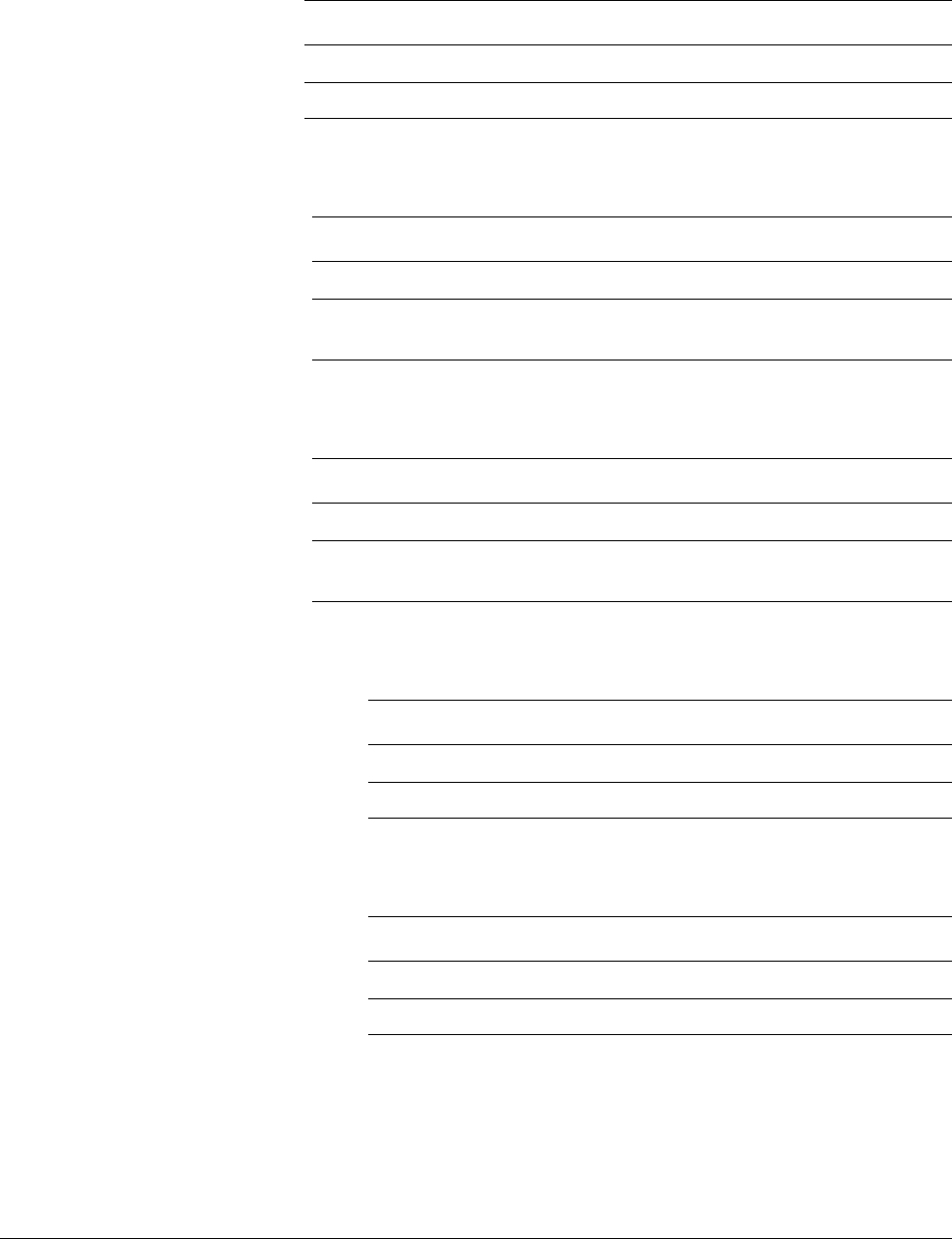

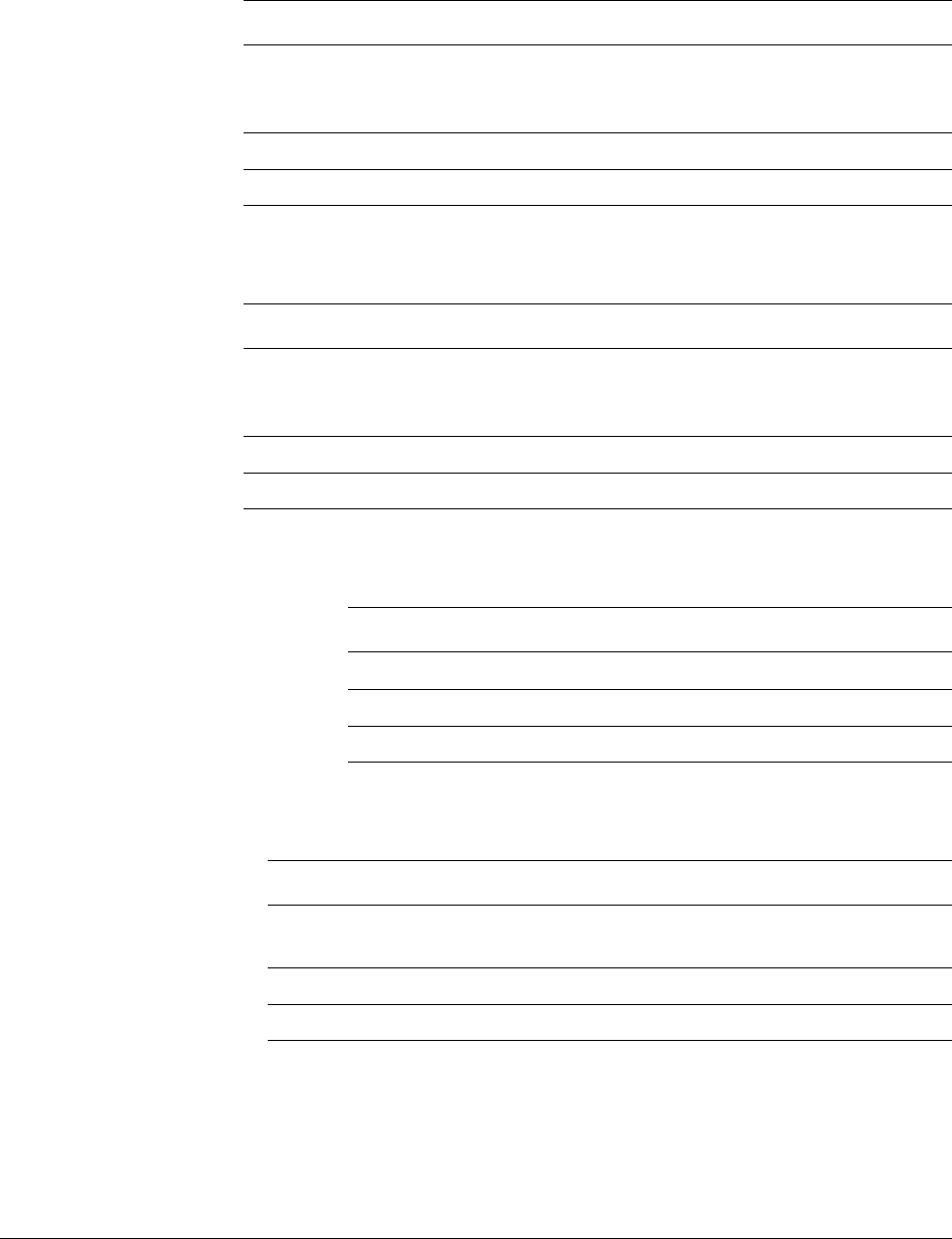

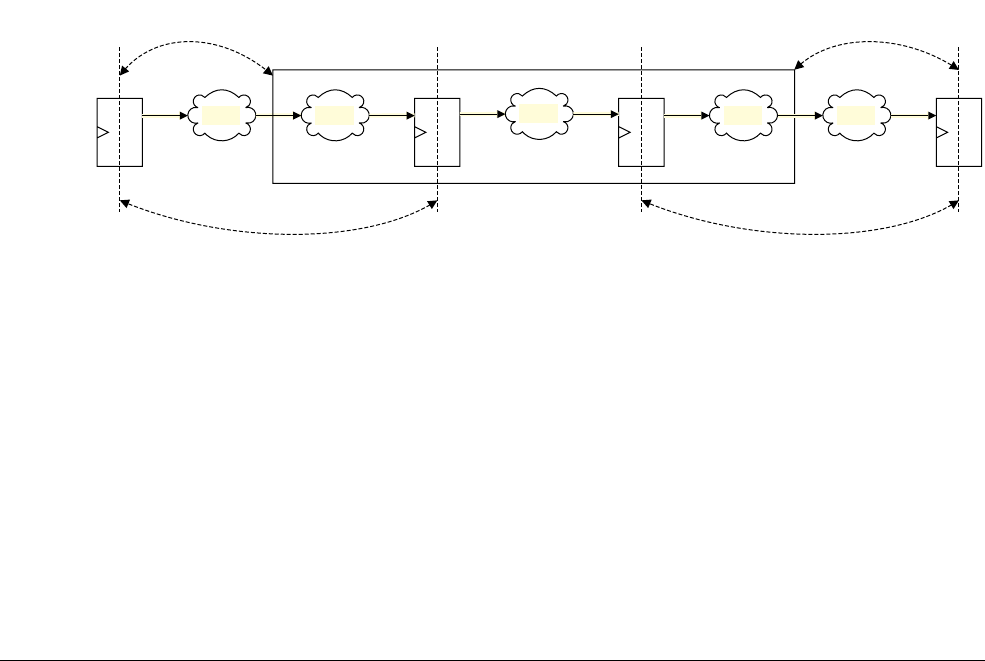

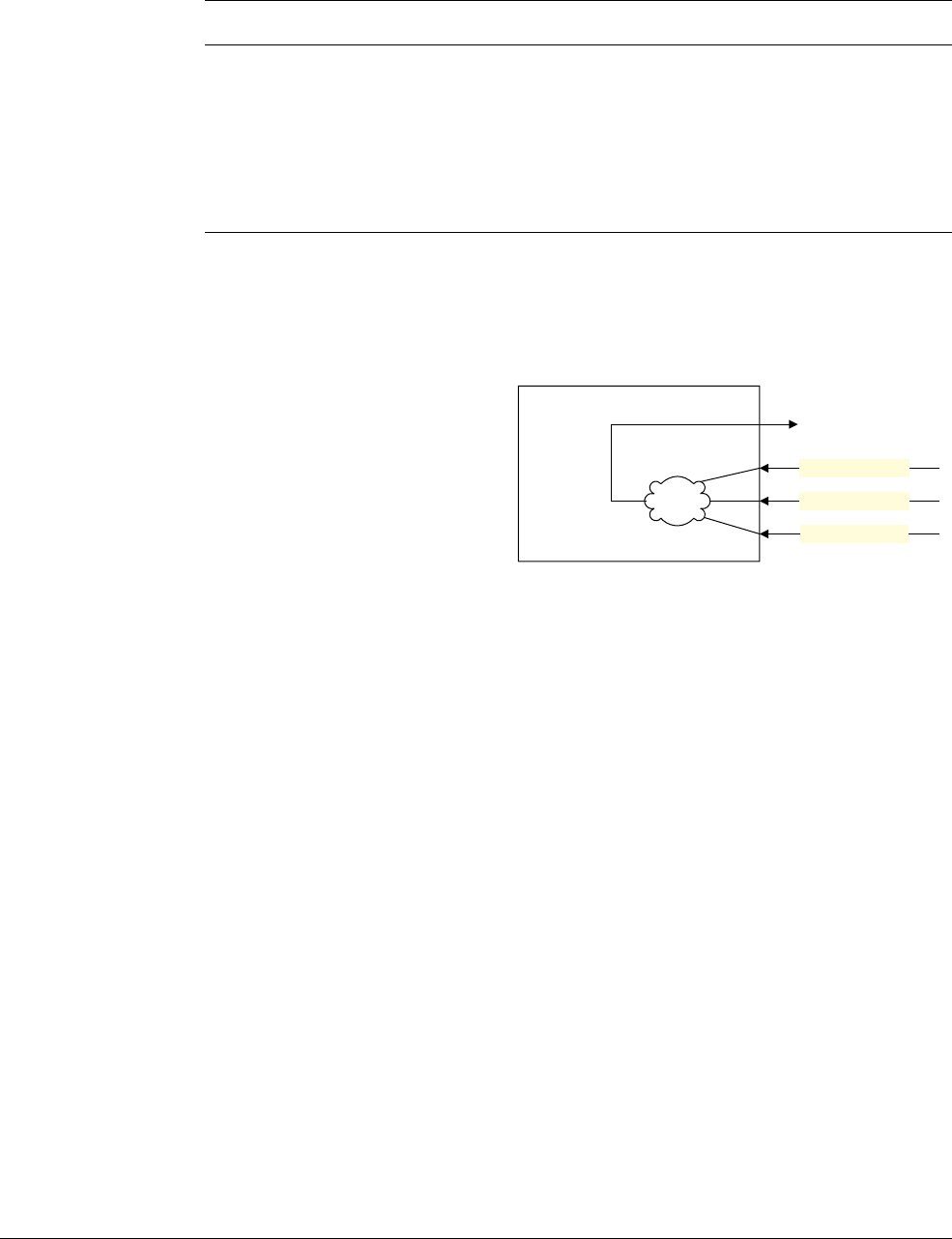

Figure 2-1 shows the top-level view of the example system.

Figure 2-1 Example microcontroller system top-level view

For the Cortex-M0+ system, the following components from the Cortex-M0+ integration kit are

reused:

•

cm0p_ik_rst_ctl

.

•

cm0p_ik_sram

.

CORTEXM0INTEGRATION or

CM0PMTBINTEGRATION

Processor and debug

interface

AHB Infrastructure including

several AHB components

Optional

PL230_udma

Micro DMA

controller

System

controller

SysTick

reference

clock

cmsdk_apb_

subsystem

cmsdk_ahb_ram

data memory

cmsdk_ahb_rom

program memory

cmsdk_ahb_rom

optional boot

loader

cmsdk_

clkreset

Crystal

oscillator

cmsdk_mcu_system

cmsdk_mcu_pin_mux

I/O pin multiplexor and tristate buffers

cmsdk_mcu_clkctrl

cortex_m0_pmu or

cm0p_ik_pmu

XTAL2

XTAL1

NRST

cmsdk_ahb_

gpio

Port 1

UART 2

TXD

Port 0

Debug

commands

and status

cmsdk_iop_

gpio*

*For use with Cortex-M0+ only

cmsdk_mcu microcontroller

System ROM

table

cmsdk_debug_tester Tristate buffers cmsdk_uart_capture

cms0p_ik_sram

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-3

ID110117 Confidential

•

cm0p_ik_pmu

.

Table 2-1 describes the items that the microcontroller contains.

Table 2-1 Microcontroller items

Item Description

cmsdk_mcu

The example microcontroller design. This level contains the behavioral memories and clock generation

components.

cmsdk_mcu_system

The synthesizable level of the microcontroller design. This instantiates the Cortex-M0 or the Cortex-M0+

processor.

CORTEXM0INTEGRATION

The Cortex-M0 Integration Layer. This is part of the Cortex-M0 deliverable. It integrates the Cortex-M0

processor and the debug interface module.

CM0PMTBINTEGRATION

The Cortex-M0+ Integration Layer. This is part of the Cortex-M0+ deliverable. It integrates the

Cortex-M0+ processor, CoreSight™ MTB-M0+ micro trace buffer, and the debug interface module. The

CoreSight -MTB-M0+ is licensed separately from the Cortex-M0+ processor. It is not included in this

deliverable.

cmsdk_apb_subsystem

A subsystem of APB peripherals and APB infrastructure.

System controller Contains programmable registers for system control, for example memory remap and power management

enable.

SysTick reference clock SysTick reference clock generation logic.

cmsdk_ahb_gpio

A low-latency GPIO with an AHB interface. Each GPIO module provides 16 I/O pins.

cmsdk_iop_gpio

A low-latency GPIO. Each GPIO module provides 16 I/O pins. Only used in Cortex-M0+.

PL230 DMA Controller An optional instantiation of the Arm CoreLink DMA-230 Micro DMA Controller. The DMA-230 is not

included in this deliverable, and you must license it separately.

cortex_m0_pmu

An optional Cortex-M0 Power Management Unit (PMU). This is included in the Cortex-M0 deliverable. It

is not included in this deliverable.

cm0p_ik_pmu

An optional Cortex-M0+ PMU. This is included in the Cortex-M0+ deliverable. It is not included in this

deliverable.

cmsdk_mcu_clkctrl

The clock and reset generation logic behavioral model.

cmsdk_mcu_pin_mux

The pin multiplexor and tristate buffers for the I/O ports.

cmsdk_ahb_rom

A memory wrapper for the ROM to test the behavior of different implementations of memory. You can

modify the Verilog parameters to change the implementation.

cmsdk_ahb_ram

A memory wrapper for the RAM to test the behavior of different implementations of memory. You can

modify the Verilog parameters to change the implementation.

cmsdk_ahb_cs_rom_table

An example system level CoreSight ROM table that enables a debugger to identify the system as a

Cortex-M0 or Cortex-M0+ based system.

cmsdk_mtb_sync.v

Includes the synchronizers for the CoreSight M0+ MTB signals, that is, TSTART and TSTOP.

cmsdk_mcu_addr_decode

Generates the HSELS for each memory mapped component based on the CMSDK address map.

cm0p_ik_sram

A synchronous SRAM model for the CoreSight MTB-M0+. Only used in Cortex-M0+.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-4

ID110117 Confidential

Table 2-2 describes the items that are in the testbench but outside the microcontroller.

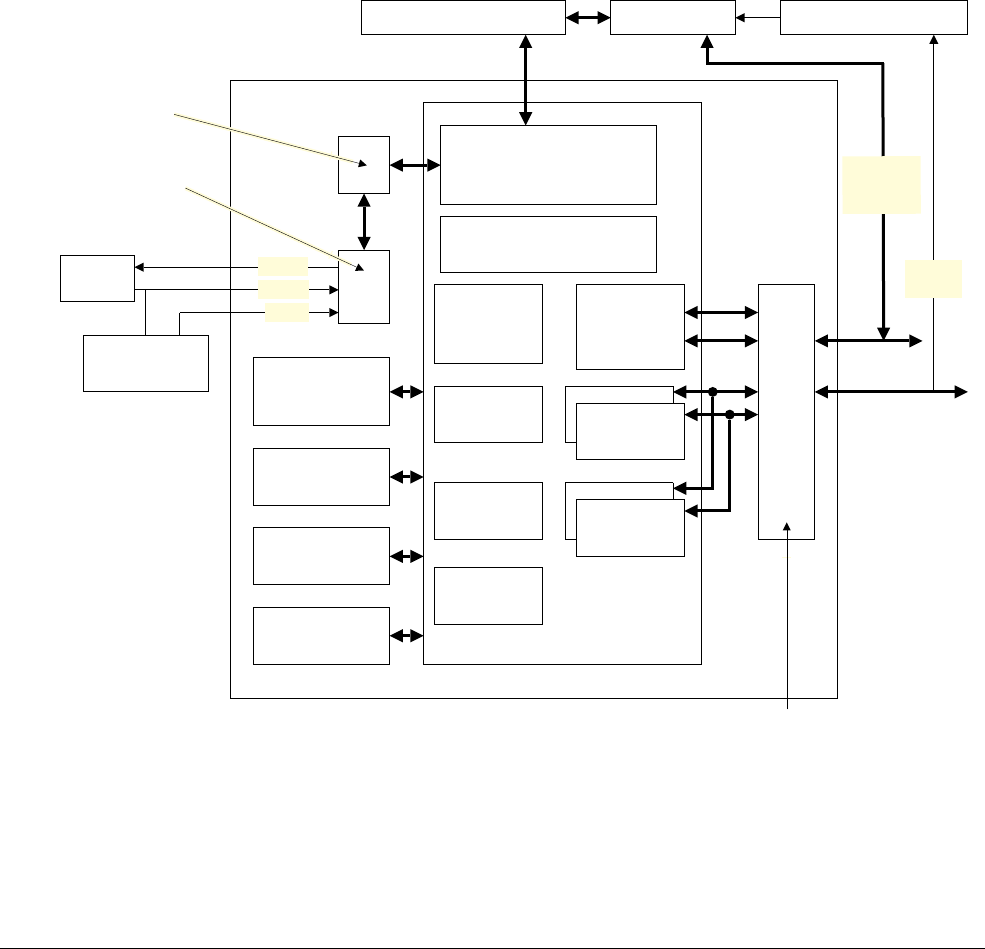

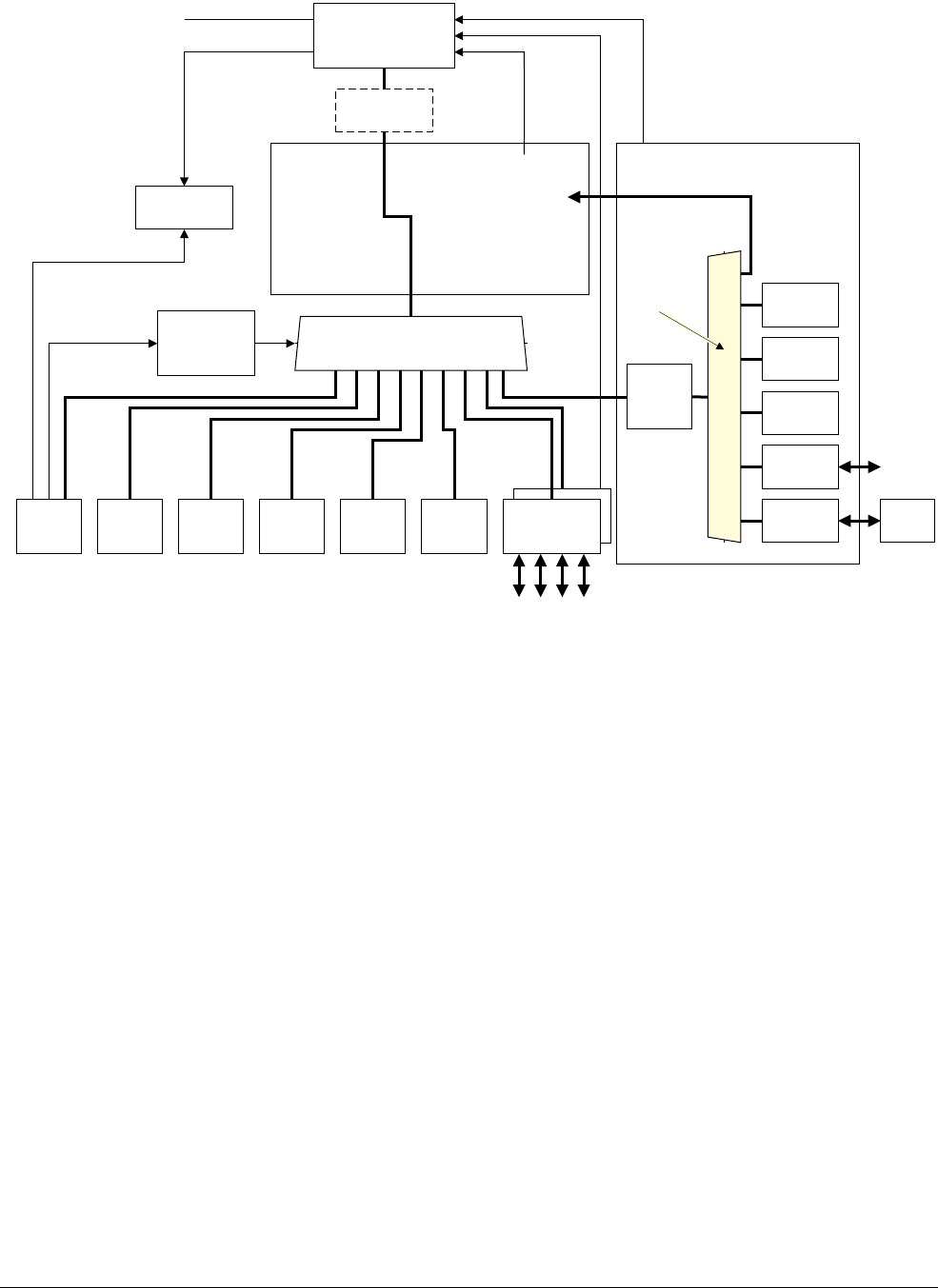

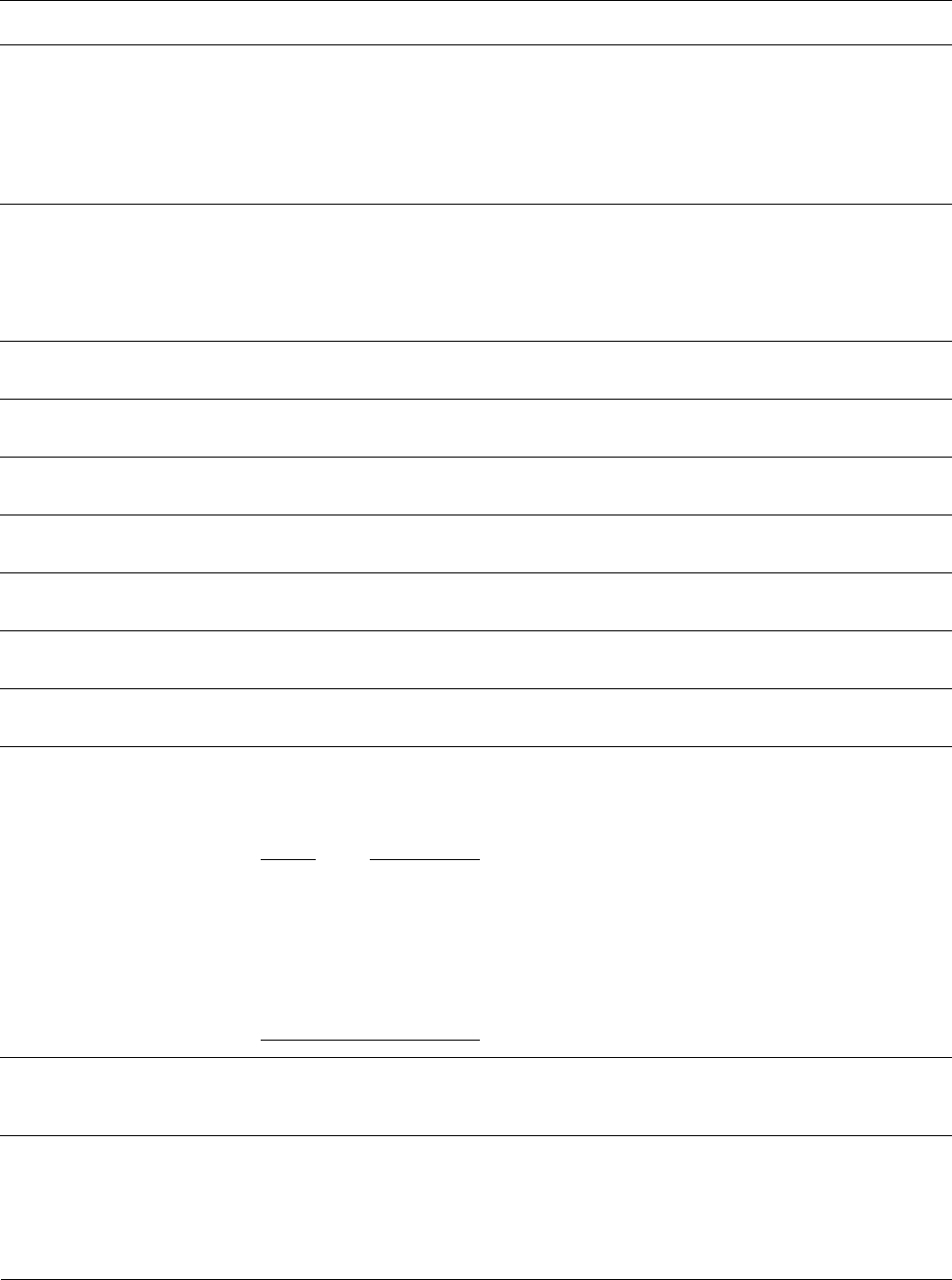

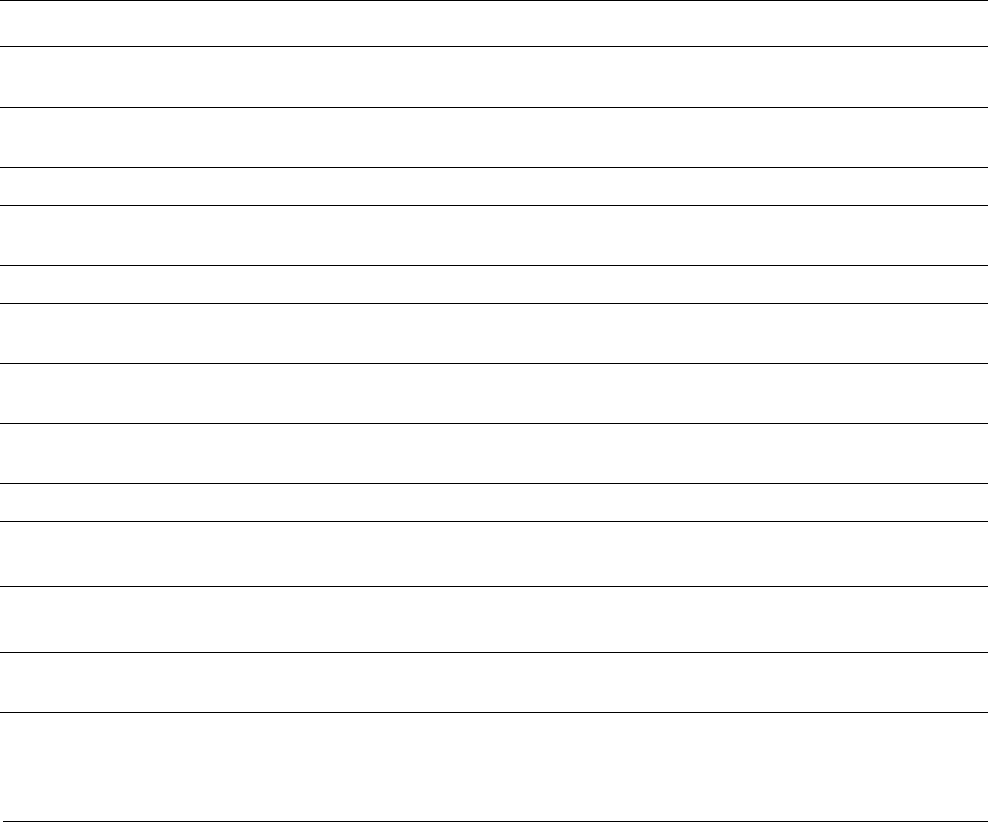

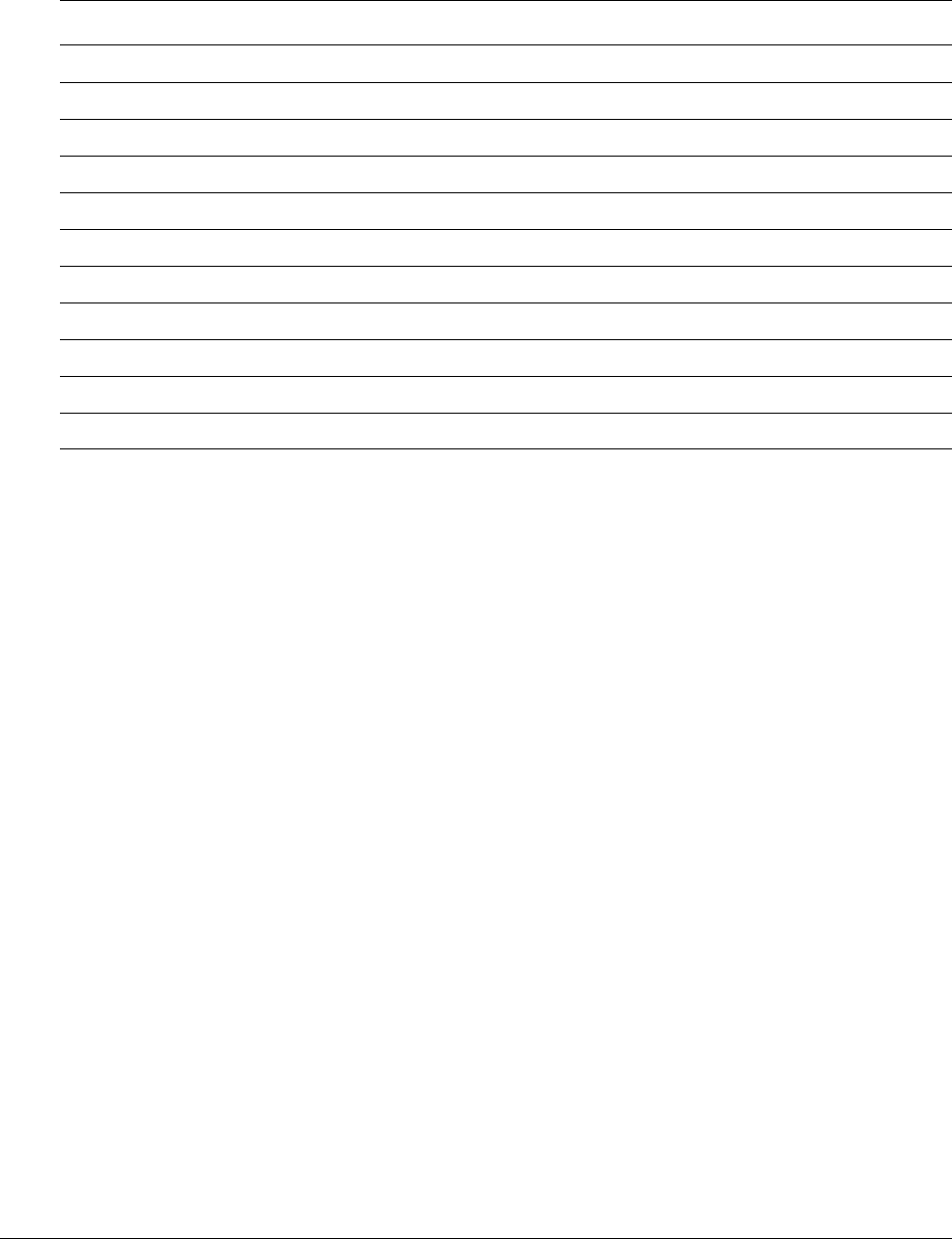

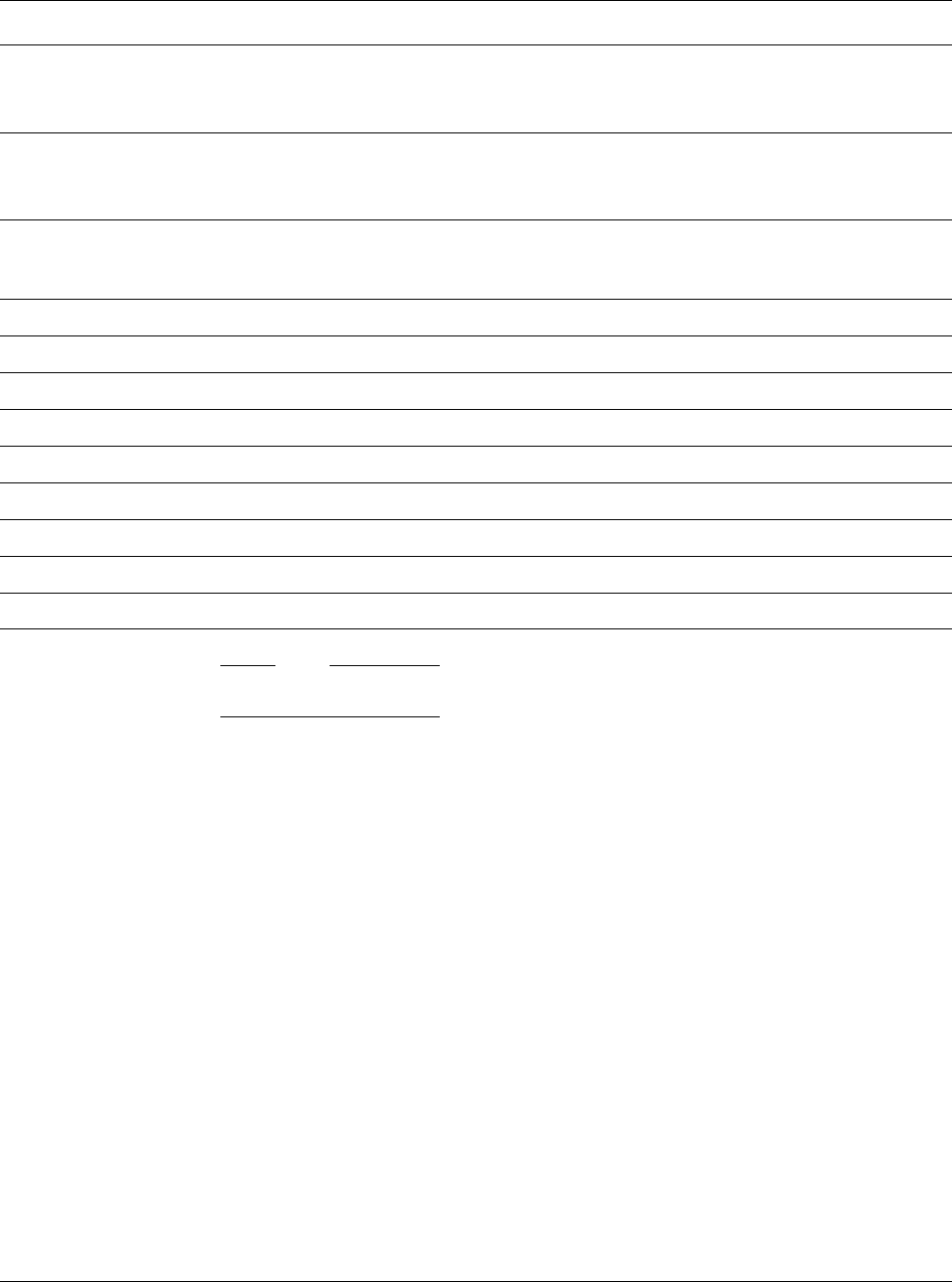

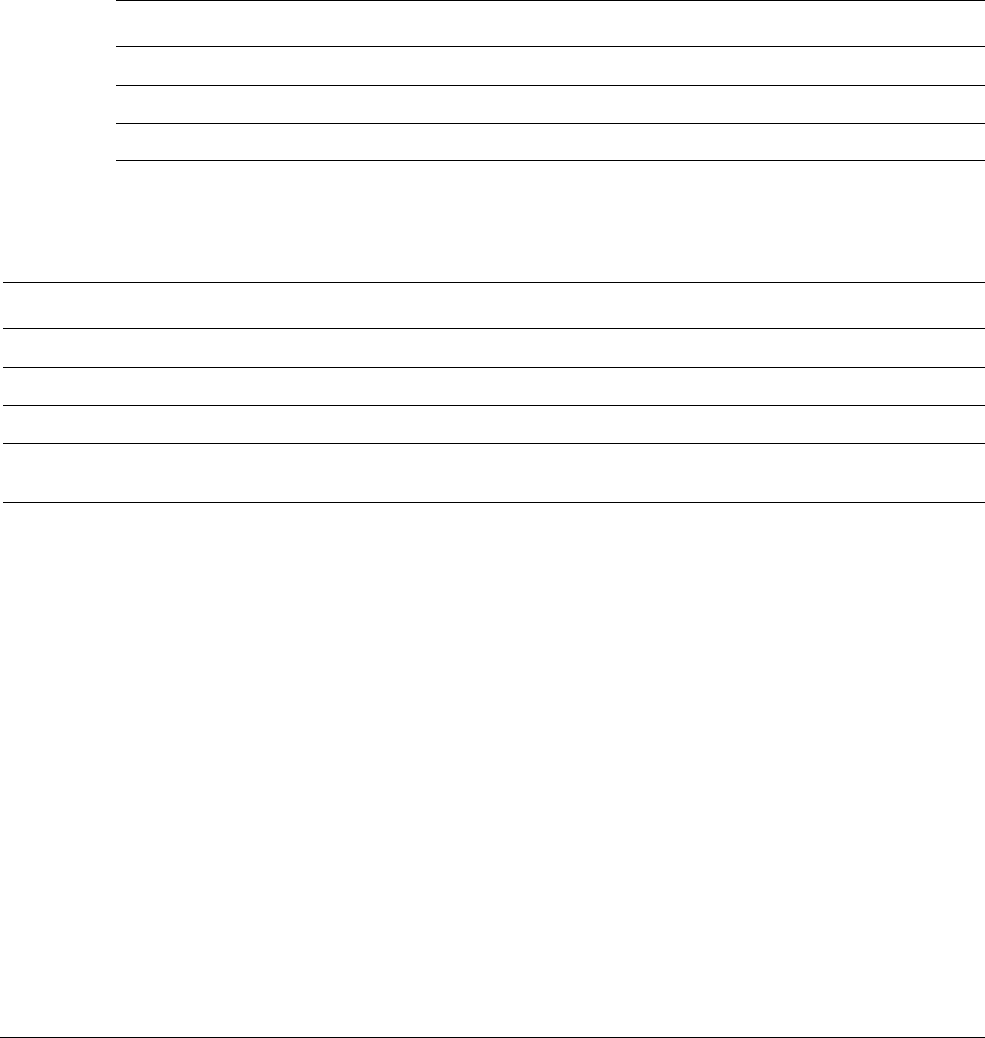

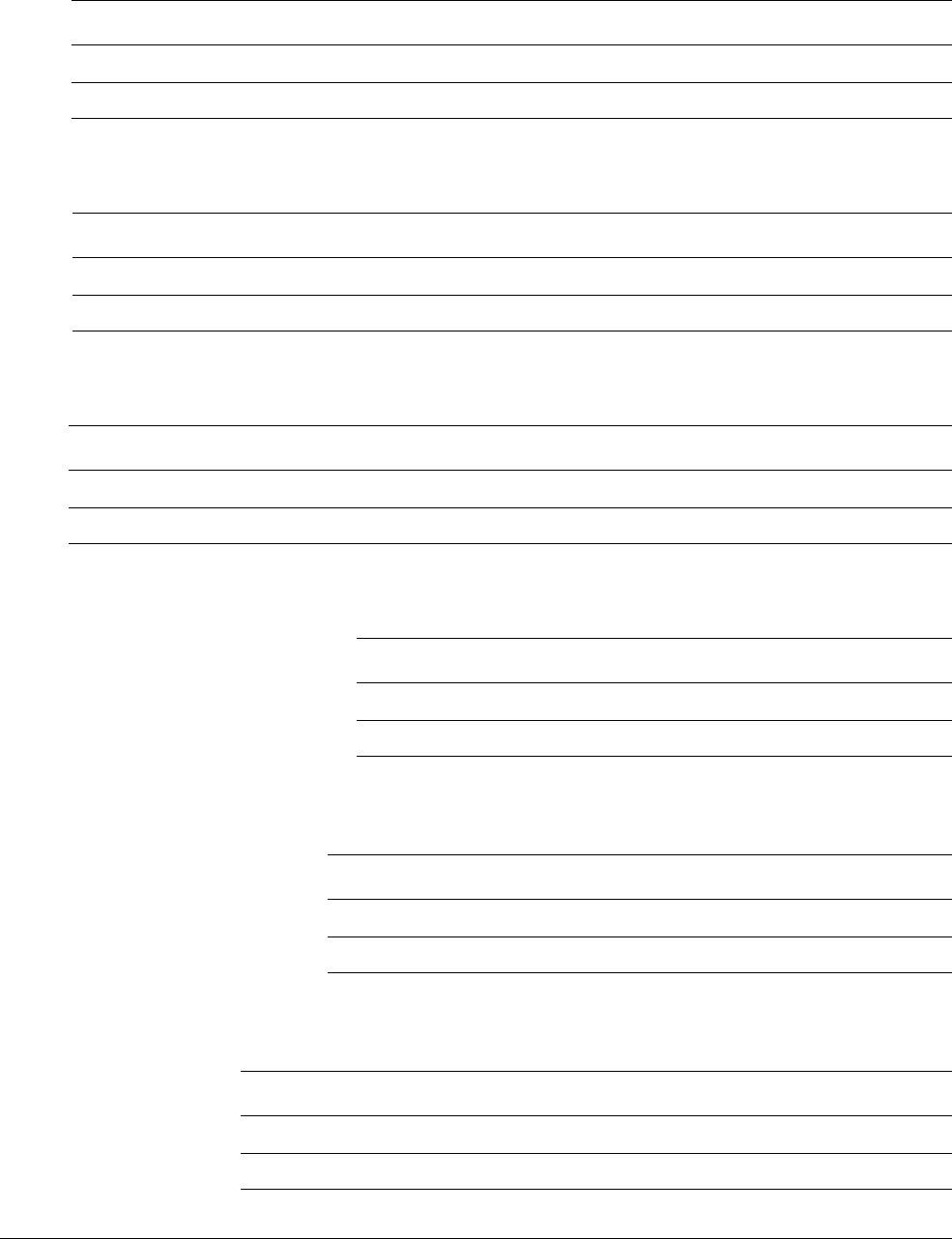

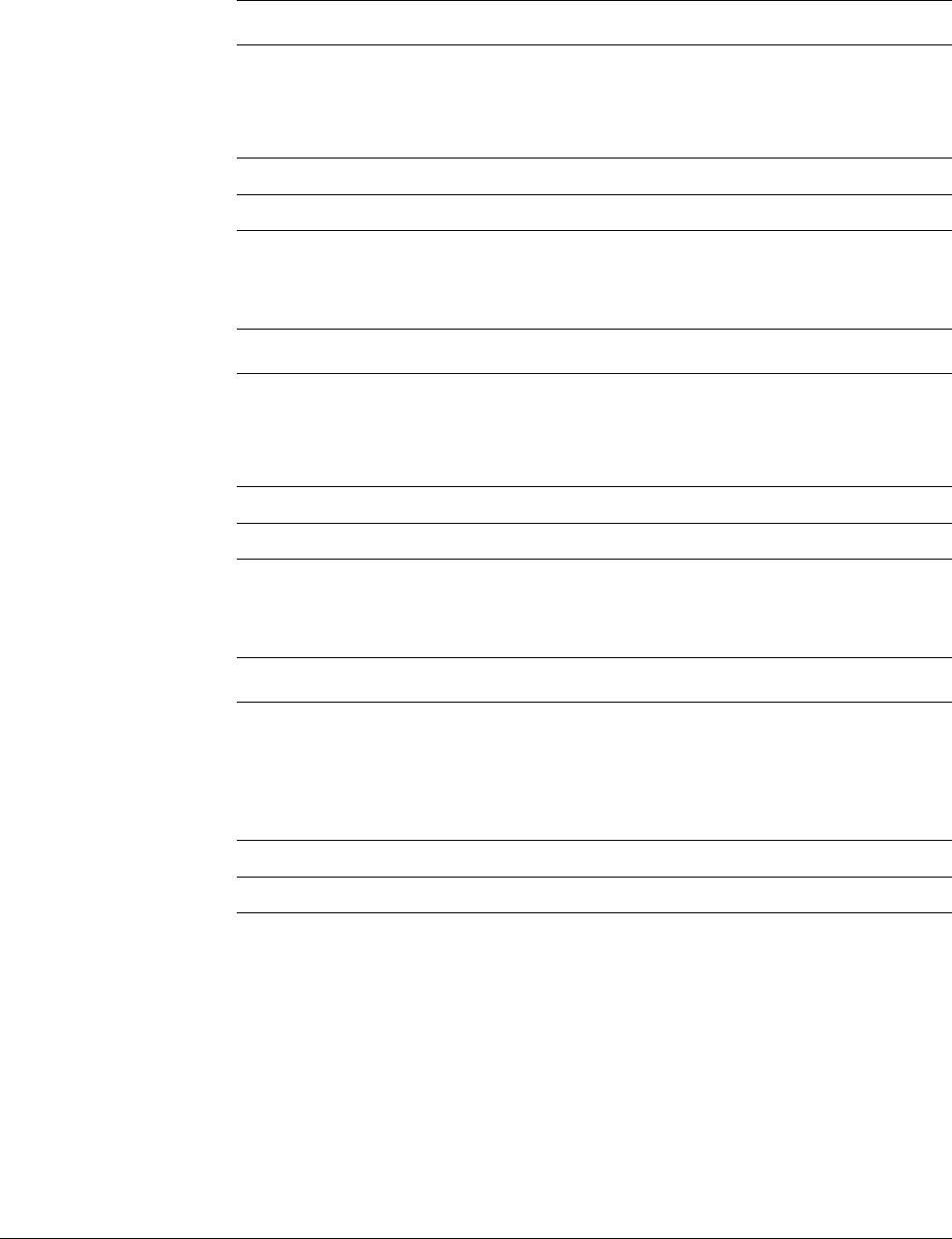

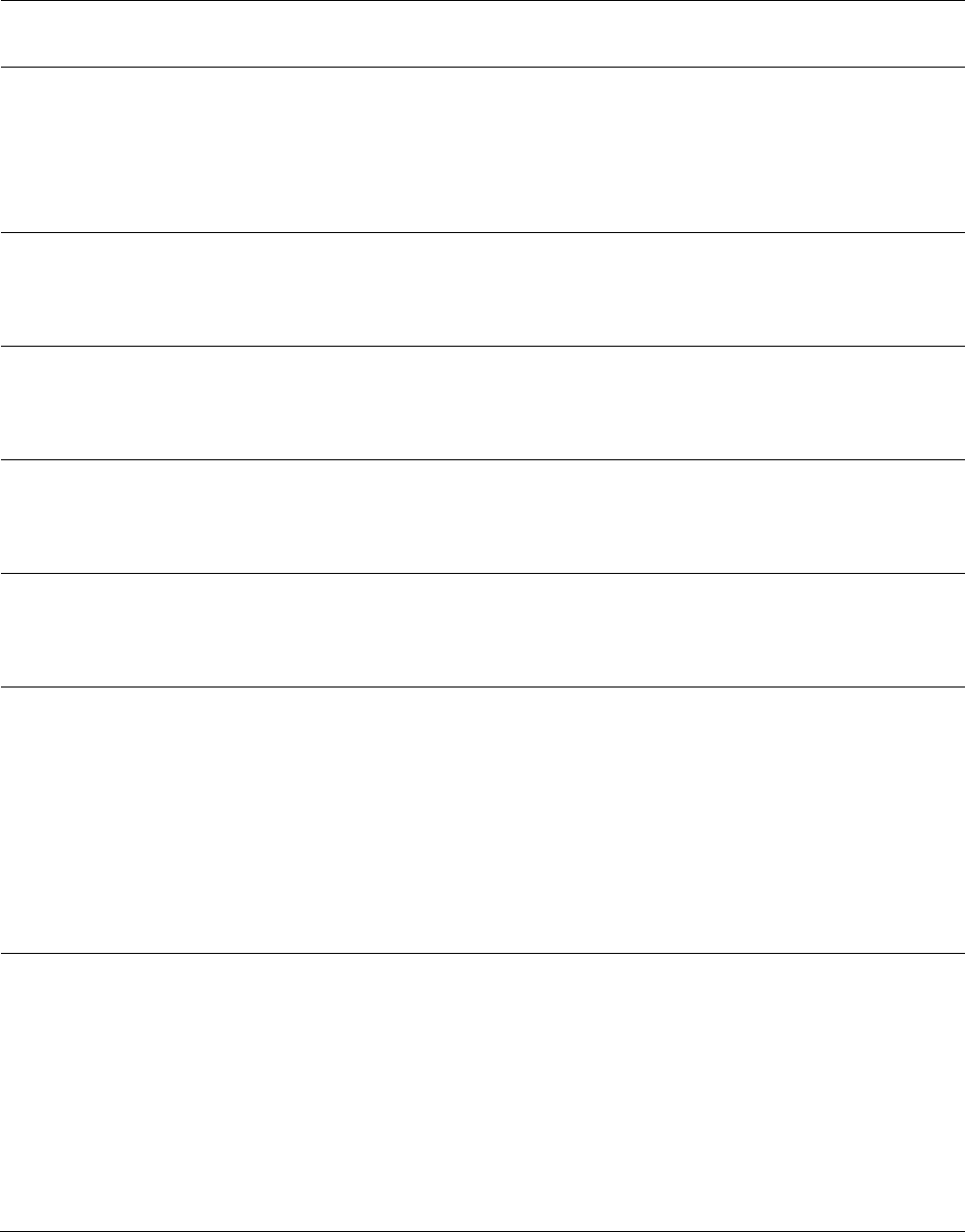

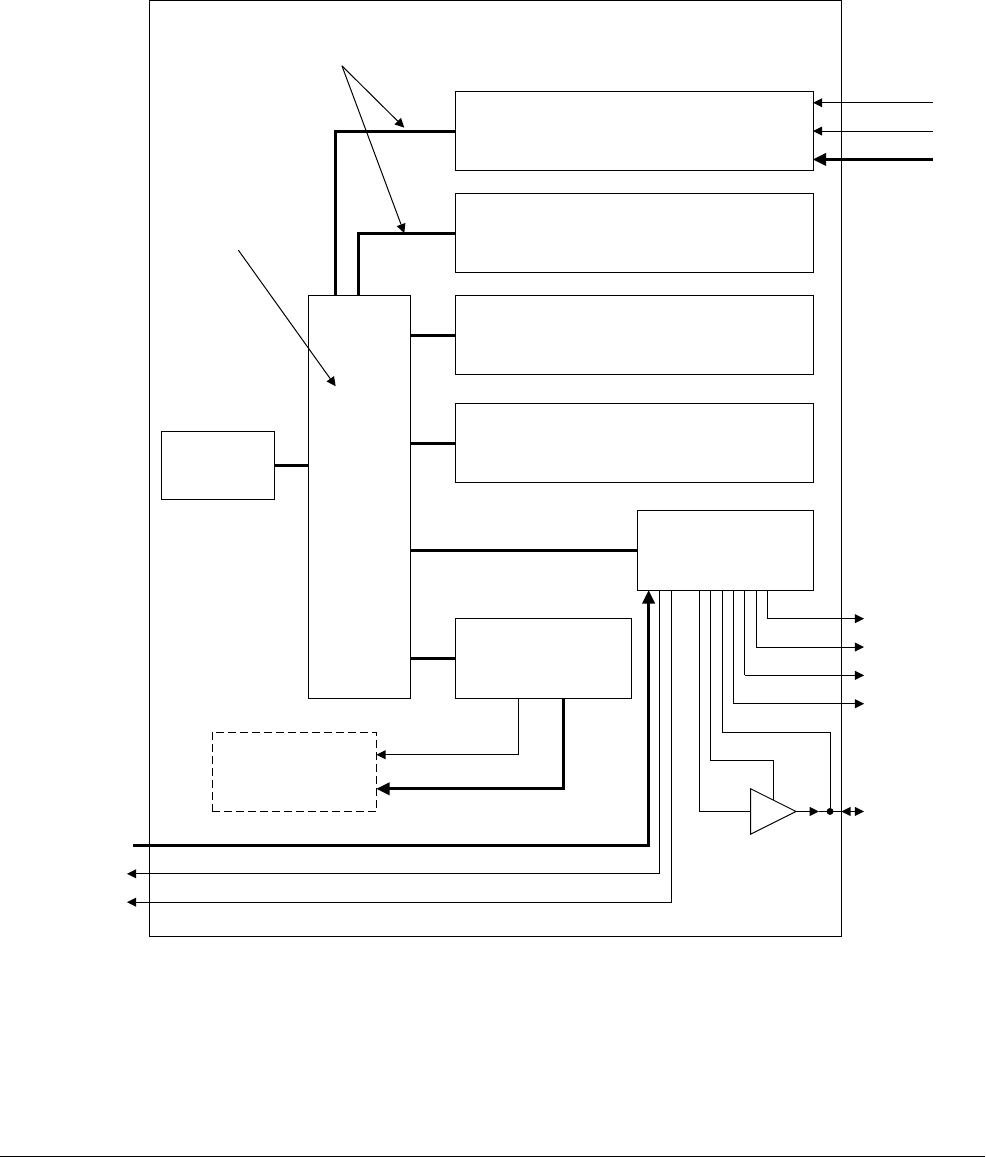

You can configure the system in a number of different ways. Figure 2-2 shows the interfaces of

the Cortex-M0 example system that includes a DMA controller.

Figure 2-2 Cortex-M0 example system with DMA controller

Figure 2-3 on page 2-5 shows the interfaces of the Cortex-M0+ example system that includes a

DMA controller.

Table 2-2 Testbench items

Item Descriptions

cmsdk_clkreset

Generates clock and reset signals. XTAL1 runs at 50MHz. It asserts NRST LOW for 5ns at the start of the

simulation.

cmsdk_uart_capture

Captures the text message from UART2 and displays the message during simulation. It displays each line

of the message after it receives a carriage return character. To reduce the simulation time, set the baud rate

to be same as the clock frequency. You must set the UART in the design kit to

high speed test mode

.

This unit also controls the tristate buffers that pass debug commands and status information between the

microcontroller and the debug tester. It does this by sending escape codes to the capture module.

cmsdk_debug_tester

The debug tester is a separate processor-based system that generates debug activities to test the debug

connection. To run these tests, the microcontroller communicates with the debug tester through GPIO 0 and

the I/O of port 0. By default, the testbench disables this communication with tristate buffers, so the

microcontroller can test the I/O port functionalities without starting a debug test.

Cortex-M0

Integration

DMA option

Low latency

GPIO

DMA-230

Clock

generator

AHB

address

decoder

Parameterizable 10 to 1

AHB slave multiplexor

External

3 to 1 Bus Master

multiplexor

Interrupts

Sleep

JTAG or Serial wire

Remap

Clock control

NC

System

control ROM Boot

ROM RAM Default

slave

ROM

table

Watch

dog

Simple

Timer x 2

Dual

Timer

Simple

UART

AHB to

APB

bridge

Text

output

Simple

UART x 2

16 to 1

multiplexor

Common APB sub-system

Bitband

wrapper Optional

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-5

ID110117 Confidential

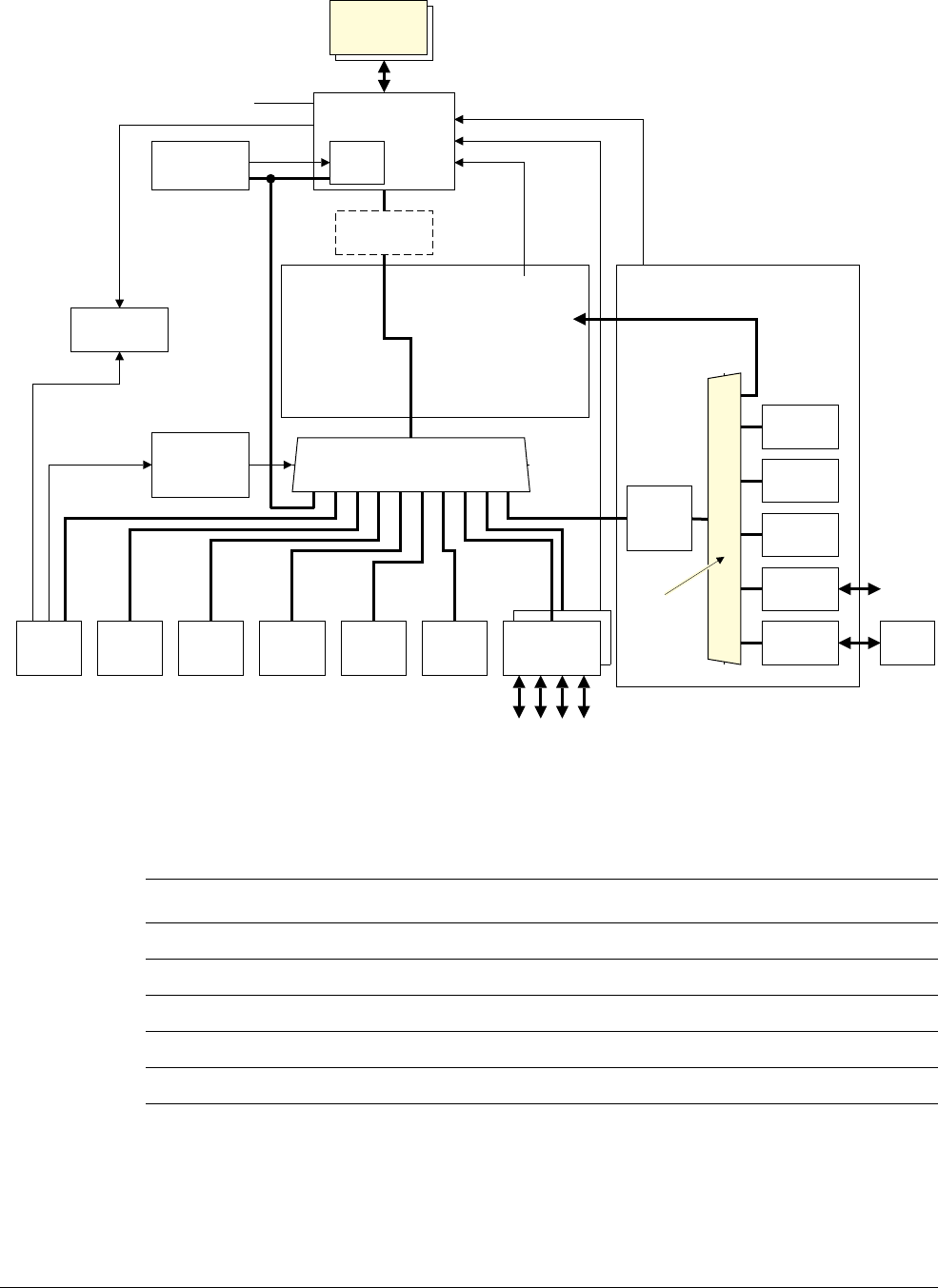

Figure 2-3 Cortex-M0+ example system with DMA controller

The processor connects to the rest of the system through an AHB Lite interface.

Figure 2-4 on page 2-6 shows the interfaces of the Cortex-M0 example system without a DMA

controller.

Cortex-M0+

Integration

DMA option

Low latency

GPIO

DMA-230

Clock

generator

AHB

address

decoder

Parameterizable 10 to 1

AHB slave multiplexor

System

control ROM Boot

ROM RAM Default

slave

External

3 to 1 Bus Master

multiplexor

Watch

dog

Simple

Timer x 2

Dual

Timer

Simple

UART

AHB to

APB

bridge

Text

output

Simple

UART x 2

16 to 1

multiplexor

Interrupts

Sleep

JTAG or Serial wire

Remap

Clock control

NC

ROM

table

I/O port

GPIO

MTB

Common APB sub-system

MTB RAM

Bitband

wrapper Optional

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-6

ID110117 Confidential

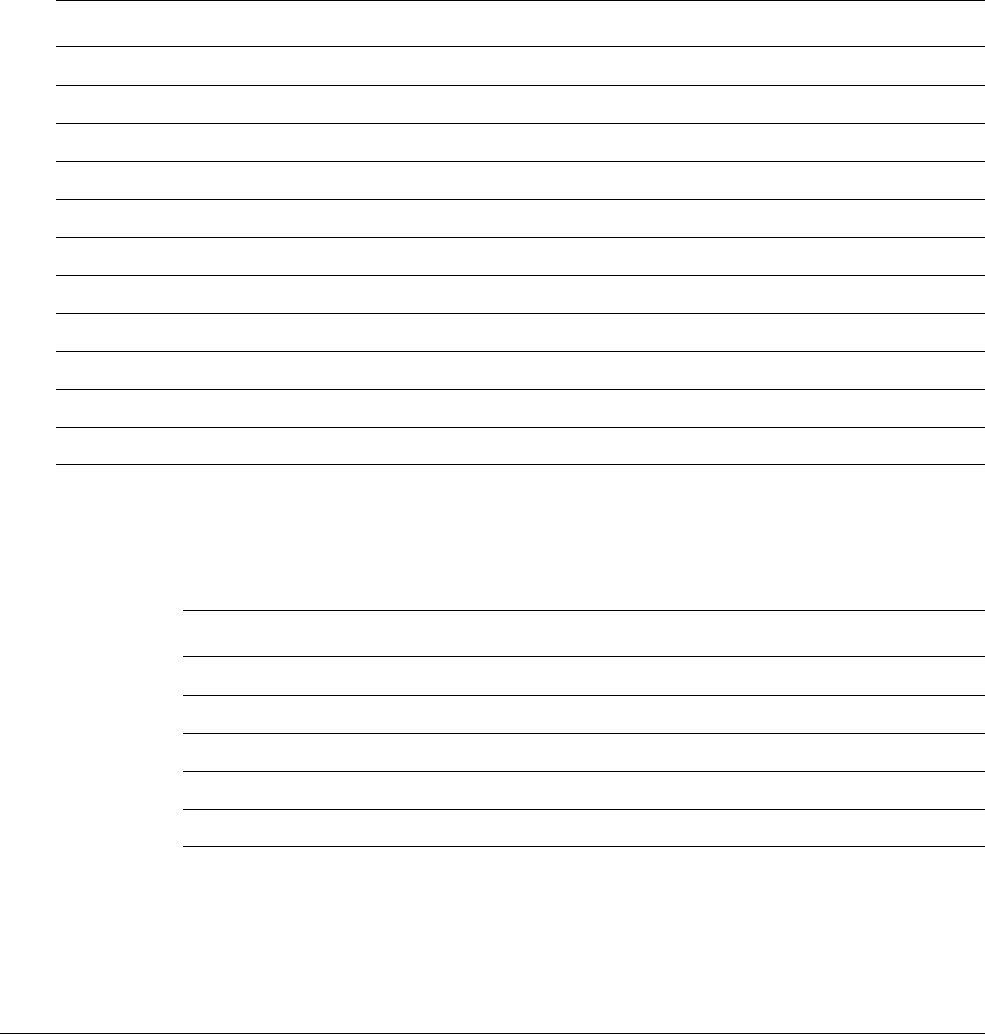

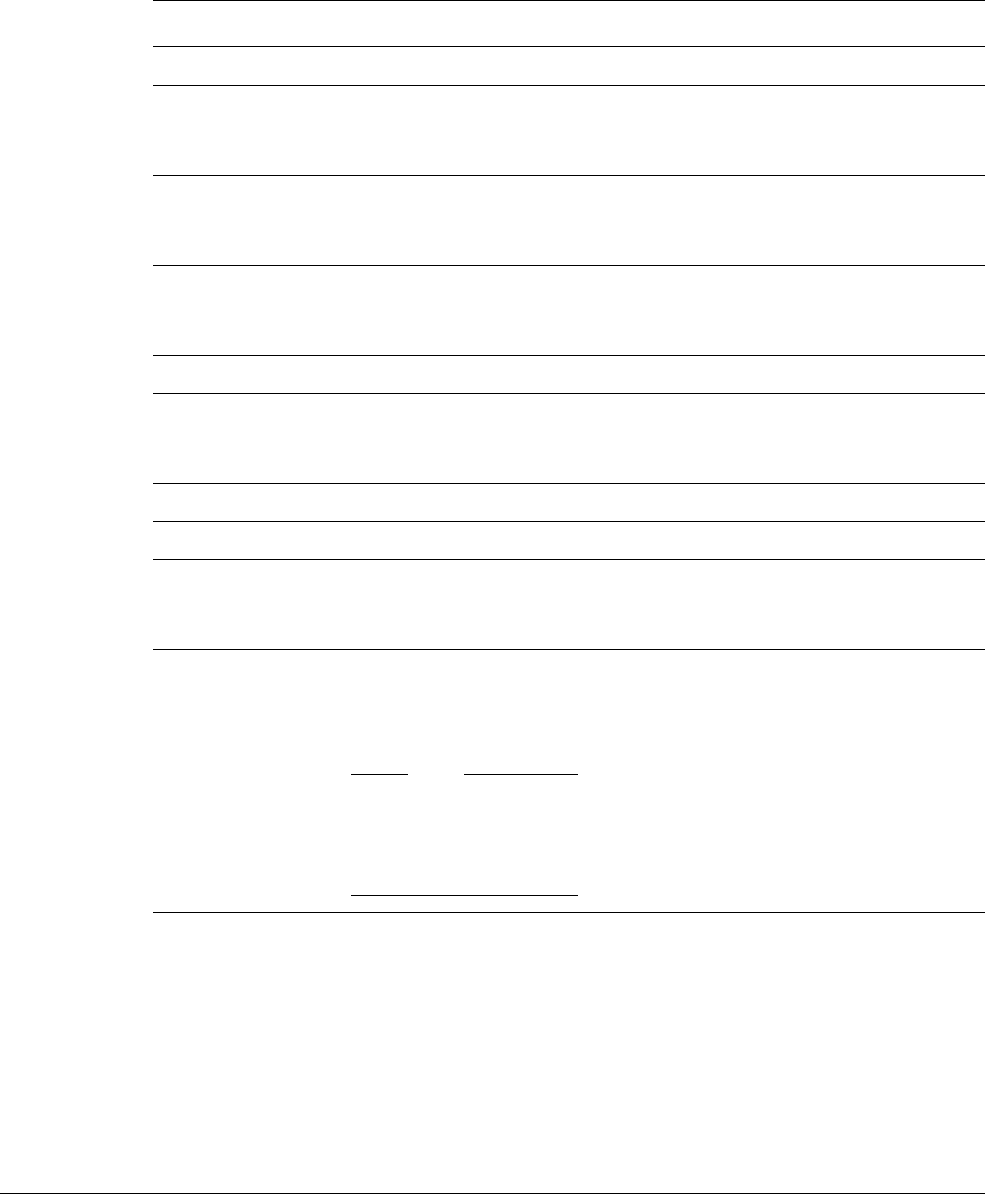

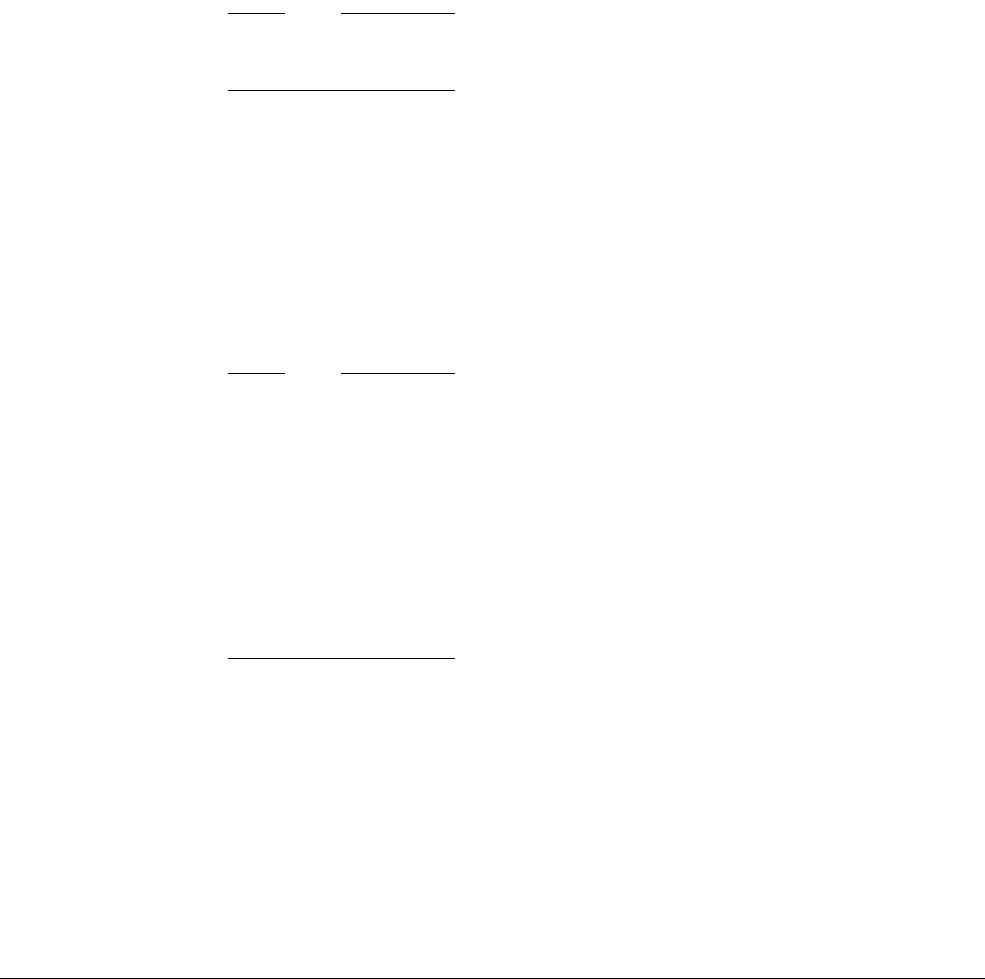

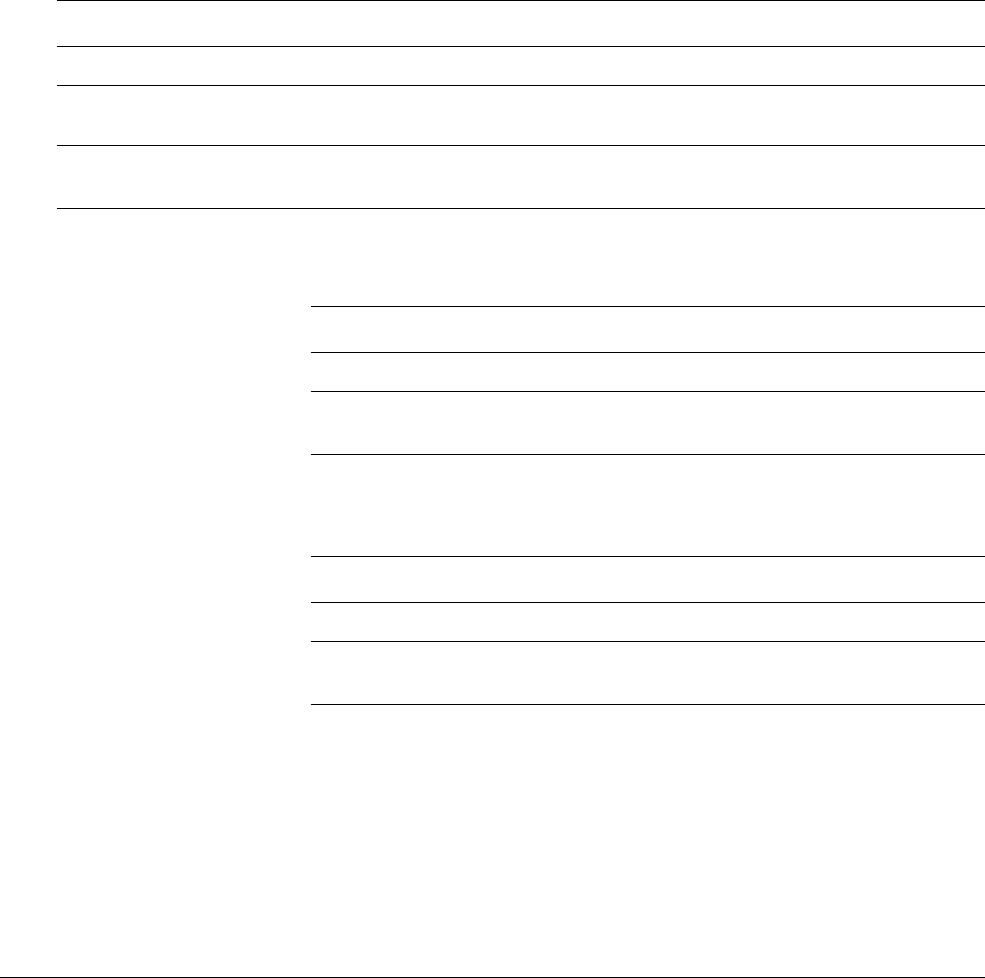

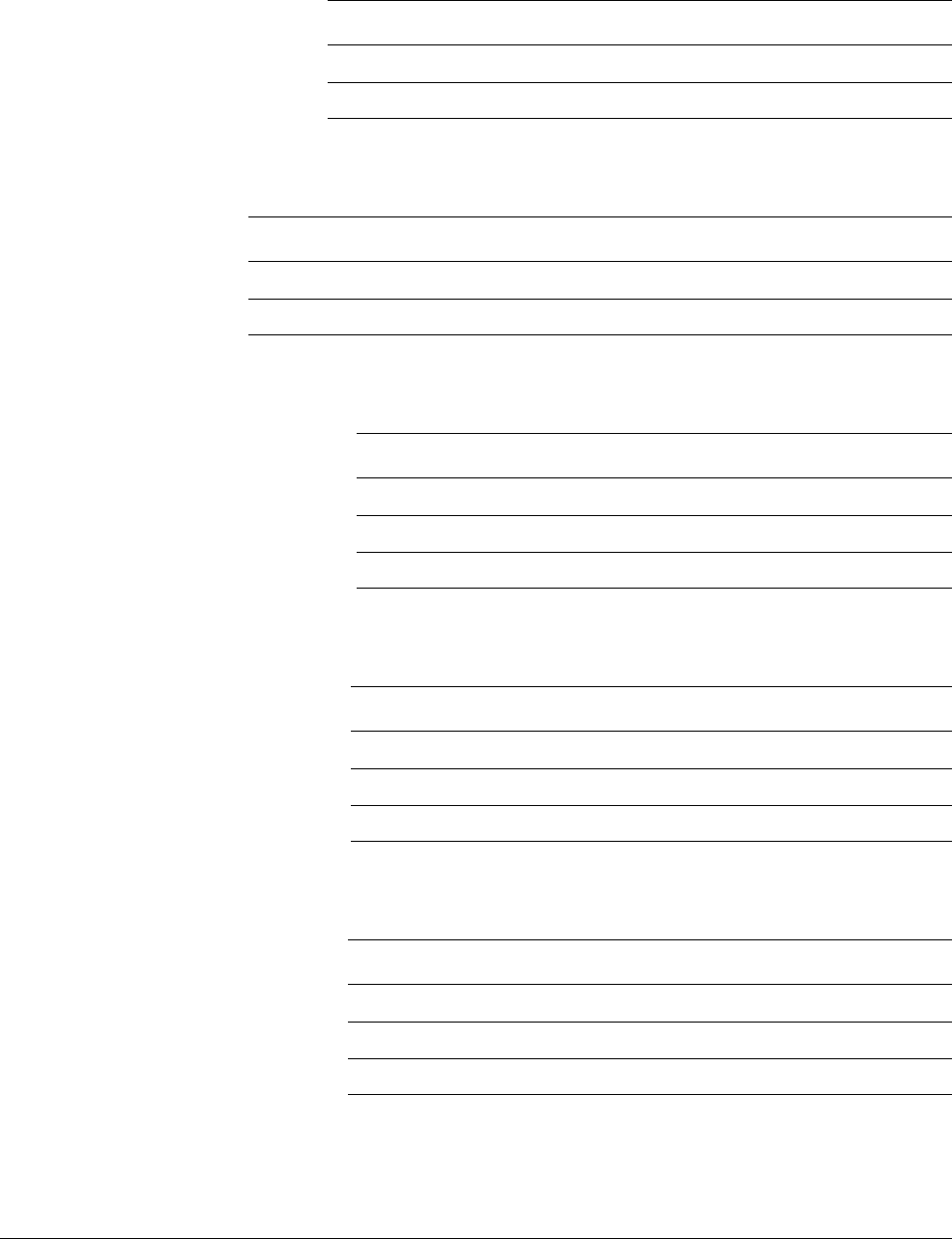

Figure 2-4 Cortex-M0 example system without DMA controller

Figure 2-5 on page 2-7 shows the interfaces of the Cortex-M0+ example system without a DMA

controller.

Cortex-M0

Integration

Without DMA

Low latency

GPIO

Clock

generator

AHB

address

decoder

Parameterizable 10 to 1

AHB slave multiplexor

External

Interrupts

Sleep

JTAG or Serial wire

Remap

Clock control

System

control ROM Boot

ROM RAM Default

slave

ROM

table

Watch

dog

Simple

Timer x 2

Dual

Timer

Simple

UART

AHB to

APB

bridge

Text

output

Simple

UART x 2

16 to 1

multiplexor

Common APB sub-system

Tied LOW

Not used

Bitband

wrapper Optional

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-7

ID110117 Confidential

Figure 2-5 Cortex-M0+ example system without DMA controller

Table 2-3 describes the design kit peripheral components that the system design includes.

The APB peripherals are instantiated in the APB subsystem block.

Cortex-M0+

Integration

Low latency

GPIO

Clock

generator

AHB

address

decoder

Parameterizable 10 to 1

AHB slave multiplexor

System

control ROM Boot

ROM RAM Default

slave

External

Watch

dog

Simple

Timer x 2

Dual

Timer

Simple

UART

AHB to

APB

bridge

Text

output

Simple

UART x 2

16 to 1

multiplexor

Interrupts

Sleep

JTAG or Serial wire

Remap

Clock control

ROM

table

I/O port

GPIO

MTB

Common APB sub-system

MTB RAM

Bitband

wrapper Optional

Without DMA

Tied LOW

Not used

Table 2-3 Design kit peripheral components

Item Descriptions

cmsdk_ahb_gpio

Two low latency GPIO with AHB interfaces. Each GPIO module provides 16 I/O pins.

cmsdk_apb_timer

A 32-bit timer.

cmsdk_apb_uart

A UART.

cmsdk_apb_watchdog

A watchdog component that is compatible with the watchdog in the AMBA design kit.

cmsdk_apb_dualtimers

A dual timer module that is compatible with the dual timer in the AMBA design kit.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-8

ID110117 Confidential

2.2 Design files

This section describes the following design files that are included in the design kit:

•Verilog files for the cmsdk_mcu example system.

•Verilog files for the cortex_m0_mcu testbench.

•Other files on page 2-9.

2.2.1 Verilog files for the cmsdk_mcu example system

Table 2-4 describes the Verilog files that are included in the Cortex-M0 and Cortex-M0+

microcontroller.

2.2.2 Verilog files for the cortex_m0_mcu testbench

Table 2-5 describes the Verilog files that are included in the testbench.

Table 2-4 Verilog files for the Cortex-M0 and Cortex-M0+ microcontroller

File name Description

cmsdk_mcu.v

Top level of the microcontroller

cmsdk_mcu_defs.v

Constant definitions and configuration definitions for the example microcontroller

cmsdk_mcu_system.v

Microcontroller system-level design

cmsdk_mcu_sysctrl.v

Programmable register block for system-level control

cmsdk_mcu_stclkctrl.v

SysTick reference clock generation logic

cmsdk_mcu_clkctrl.v

Clock and reset control

cmsdk_mcu_pin_mux.v

Pin multiplexer and tristate buffers for the I/O port

cmsdk_mcu_addr_decode.v

Generates the HSELS for each memory mapped component based on the CMSDK address map

cmsdk_mtb_sync.v

Synchronizer for Cortex-M0+ MTB trace start/stop control signals

cmsdk_iop_interconnect.v

Address decode and interconnection for Cortex-M0+ single cycle I/O port

cmsdk_ahb_cs_rom_table.v

CoreSight system level ROM table for CMSDK

Table 2-5 Verilog files for the Cortex-M0 and Cortex-M0+ microcontroller testbench

File name Description

tb_cmsdk_mcu.v

Testbench of the example microcontroller

cmsdk_clkreset.v

Clock and reset generator

cmsdk_uart_capture.v

UART capture for text message display and control of debug tester communication

tbench_M0.vc

Verilog command file for Cortex-M0

tbench_M0P.vc

Verilog command file for Cortex-M0+

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-9

ID110117 Confidential

The testbench also contains a debug tester that tests the debug connectivity. Table 2-6 describes

the Verilog files of the debug tester.

The debug tester Verilog files are located in the

logical/cmsdk_debug_tester/verilog/

directory.

The debug tester has its own program image. It is stored in

debug_tester_cm0.hex

for the

Cortex-M0 processor or

debug_tester_cm0plus.hex

for the Cortex-M0+ processor. The file is

located in the

software/debug_tester

directory. This directory also contains the source code for

the debug tester program, and the compilation makefile of the program for the Arm

Development Studio (DS-5) and Arm GCC, and the compile project setup for the Keil®

Microcontroller Development Kit (MDK).

2.2.3 Other files

See Chapter 4 Using the simulation environment for information on the simulation setup and the

test codes to run simulations.

Table 2-6 Verilog files of the debug tester

File Description

cmsdk_debug_tester.v

Top level of the debug tester.

cmsdk_debug_tester_ahb_interconnect.v

AHB interconnection inside the debug tester. The debug tester is a Cortex-M0 or

Cortex-M0+ based system that requires its own AHB infrastructure.

cmsdk_ahb_default_slave.v

CMSDK AHB default slave that is used by the debug tester.

cmsdk_ahb_rom.v

Program memory for the debug tester.

cmsdk_ahb_ram.v

CMSDK AHB SRAM used by the debug tester.

cmsdk_ahb_gpio.v

CMSDK AHB GPIO

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-10

ID110117 Confidential

2.3 Processor file locations

The default location of the Verilog RTL files for the processors is a subdirectory called

cores

.

For example:

• Cortex-M0 default RTL path is

cores/at510_cortexm0_r0p0_03rel2/logical/

• Cortex-M0+ default RTL path is

cores/at590_cortexm0p_r0p1/logical/

2.3.1 Modifying the location of the processor files for simulation

To modify the location of the Cortex-M0 default files for simulation, edit the Verilog command

file

tbench_M0.vc

.

To modify the location of the Cortex-M0+ default files for simulation, edit the Verilog command

file

tbench_M0P.vc

.

2.3.2 Modifying the location of the processor files for synthesis

Modify the synthesis script file

cmsdk_mcu_system_verilog.tcl

to match the location of the

source files.

2.3.3 Tarmac

The logging of instructions is provided in the Cortex-M0 and Cortex-M0+ using a simulation

model called Tarmac. This is enabled by default. You can disable it by editing the appropriate

vc

file and commenting out the

USE_TARMAC

define.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-11

ID110117 Confidential

2.4 Configuration options

The example microcontroller system contains several configurable options. You can define

these options in the following ways:

•Preprocessing definitions.

•Verilog parameters for Cortex-M0 on page 2-13.

•Verilog parameters for Cortex-M0+ on page 2-14.

•Changing the processor type on page 2-15.

2.4.1 Preprocessing definitions

The file

cortex_m0_mcu/verilog/cmsdk_mcu_defs.v

contains a number of Verilog preprocessing

definitions. To remove a definition, comment-out the line of Verilog code that describes the

preprocessing definitions. Table 2-7 describes the Verilog preprocessing definitions.

Table 2-7 Verilog preprocessing definitions

Preprocessing macro Descriptions

ARM_CMSDK_INCLUDE_BITBAND

Include this macro to add a bitband wrapper module to the example Cortex-M0 or Cortex-M0+

system. It enables these processors to have the same bitband capability as the Cortex-M3 and

Cortex-M4 processors. Comment this out to remove the bitband wrapper and reduce the gate count.

ARM_CMSDK_INCLUDE_DEBUG_TESTER

This macro includes the debug tester component that is in the simulation testbench. Remove this

macro option if you use a processor that does not have a debug feature.

ARM_CMSDK_INCLUDE_JTAG

If the debug feature is available, the debug interface can either use the JTAG protocol or the Serial

Wire protocol. Include this macro to specify the JTAG debugger protocol. Remove this macro to

specify the Serial Wire debug protocol. If you select the Serial Wire option, the example system

removes the redundant JTAG pins from the example microcontroller design.

ARM_CMSDK_INCLUDE_DMA

If you include this macro, the example system includes the instantiation of a DMA-230 Micro

DMA Controller and an AHB master multiplexer. The DMA-230 is not included in this deliverable,

and you must license it separately.

ARM_CMSDK_INCLUDE_CLKGATE

If you include this macro, the system:

•Sets the

CLKGATE_PRESENT

Verilog parameter of the Cortex-M0 or Cortex-M0+ instantiation

HIGH to enable the architectural clock gating feature.

• Includes clock gating cells in the clock controller file

cortex_m0_mcu_clkctrl.v

for gated

clock generation.

• Uses the gated clock, that the example Power Management Unit (PMU) generates, for the

connection of HCLK, DCLK, and SCLK of the Cortex-M0 or Cortex-M0+. When you

select this option and enable the Cortex-M0 or Cortex-M0+ PMU, the SysTick stops during

deep sleep mode because the PMU stops SCLK during deep sleep mode.

ARM_CMSDK_SLOWSPEED_PCLK

If you include this macro, the APB peripheral bus runs at half the speed of the AHB bus.

Note

This option is ignored when the clock gating option,

ARM_CMSDK_INCLUDE_CLKGATE

, or the

CLKGATE_PRESENT

parameter, is not set.

ARM_CMSDK_BOOT_MEM_TYPE

Defines the boot loader memory type. The options are:

•

AHB_ROM_NONE

for memory not present. This disables the bootloader feature.

•

AHB_ROM_BEH_MODEL

for behavioral ROM memory.

•

AHB_ROM_FPGA_SRAM_MODEL

for a behavioral FPGA SRAM model with an SRAM wrapper.

•

AHB_ROM_FLASH32_MODEL

for behavioral 32-bit flash memory.

•

AHB_ROM_FLASH16_MODEL

for behavioral 16-bit flash memory, for use with the Cortex-M0+

processor.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-12

ID110117 Confidential

ARM_CMSDK_ROM_MEM_TYPE

Defines the program memory type. The options are:

•

AHB_ROM_BEH_MODEL

for behavioral ROM memory.

•

AHB_ROM_FPGA_SRAM_MODEL

for a behavioral FPGA SRAM model with an SRAM wrapper.

•

AHB_ROM_FLASH32_MODEL

for behavioral 32-bit flash memory.

•

AHB_ROM_FLASH16_MODEL

for behavioral 16-bit flash memory, for use with the Cortex-M0+

processor.

ARM_CMSDK_RAM_MEM_TYPE

Defines the RAM memory type. The options are:

•

AHB_RAM_BEH_MODEL

for behavioral RAM memory.

•

AHB_RAM_FPGA_SRAM_MODEL

for behavioral SRAM model with SRAM wrapper.

•

AHB_RAM_EXT_SRAM16_MODEL

for benchmarking using 16-bit external asynchronous SRAM.

•

AHB_RAM_EXT_SRAM8_MODEL

for benchmarking using 8-bit external asynchronous SRAM.

ARM_CMSDK_BOOT_MEM_WS_N

Defines the number of wait states for boot loader ROM non-sequential accesses. See the Cortex-M

System Design Kit Technical Reference Manual.

ARM_CMSDK_BOOT_MEM_WS_S

Defines the number of wait states for boot loader ROM sequential accesses. See the Cortex-M

System Design Kit Technical Reference Manual.

ARM_CMSDK_ROM_MEM_WS_N

Defines the number of wait states for program ROM non-sequential accesses. See the Cortex-M

System Design Kit Technical Reference Manual.

ARM_CMSDK_ROM_MEM_WS_S

Defines the number of wait states for program ROM sequential accesses. See the Cortex-M System

Design Kit Technical Reference Manual.

ARM_CMSDK_RAM_MEM_WS_N

Defines the number of wait states for RAM non-sequential accesses. See the Cortex-M System

Design Kit Technical Reference Manual.

ARM_CMSDK_RAM_MEM_WS_S

Defines the number of wait states for RAM sequential accesses. See the Cortex-M System Design

Kit Technical Reference Manual.

ARM_CMSDK_INCLUDE_IOP

Defines the inclusion of the I/O Port GPIO in place of the AHB GPIO because they are mutually

exclusive. Only used in Cortex-M0+.

ARM_CMSDK_INCLUDE_MTB

Include this macro to instantiate the MTB and its associated RAM for trace storage. In this

configuration, the AHB RAM is removed from the system and the MTB provides the access for

data accesses. This enables the design to be kept small because only a single RAM is used for trace

and data. Only used in Cortex-M0+.

Note

When the MTB is included, the RAM that is used for the data accesses is shared with the MTB. If

you set the address width to be smaller than the default, that is,

AWIDTH = 16

, the addresses that some

tests use to write data to will alias to lower addresses, therefore some tests will not work with the

smaller memory.

It is also possible that, with a smaller address space, test data accesses and MTB accesses overwrite

each other within the shared memory space, so take care to limit each of these accesses to certain

ranges of addresses.

ARM_CMSDK_INCLUDE_F16

Configures a Cortex-M0+ based system to use 16-bit Flash. In this configuration, a 32-bit to 16-bit

converter,

cm0p_32to16_dnsize

, is used. This converter is supplied with the Cortex-M0+ integration

kit, and does not include burst support.

Table 2-7 Verilog preprocessing definitions (continued)

Preprocessing macro Descriptions

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-13

ID110117 Confidential

2.4.2 Verilog parameters for Cortex-M0

If you are using the full version of the Cortex-M0 processor, its Verilog parameters are

propagated from the testbench. You can edit file

cortex_m0_mcu/verilog/tb_cmsdk_mcu.v

to

modify these Verilog parameters. Table 2-8 describes the parameters.

Table 2-8 Verilog parameters for Cortex-M0

Verilog parameters Descriptions

NUMIRQ

Number of Interrupt ReQuest (IRQ) signals. The range is 1-32.

SMUL

Small multiplier. This can be one of the following values:

0 Single cycle multiplier.

1 Small multiplier with multicycle operation.

SYST

SysTick Timer, it can be one of the following values:

0 No timer.

1 Include the SysTick timer.

WIC

Wake-up Interrupt Controller (WIC) support. This can be one of the following values:

0 Remove WIC.

1 Enable WIC.

WICLINES

Number of interrupt lines that the WIC supports.

DBG

Debug configuration. This can be one of the following values:

0 Remove debug feature.

1 Include debug feature.

BKPT

Number of breakpoint comparators.

WPT

Number of watchpoint comparators.

BE

Big-endian. This can be one of the following values:

0 Little-endian.

1 Big-endian.

RESET_ALL_REGS

Specifies whether all synchronous states or only the architecturally required state is

reset.

0 Only resets the architecturally required state.

1 Resets all synchronous states.

Note

Setting this parameter increases the size of the registers that are not reset by default, and

therefore also increases the overall area of the implementation.

When some of the registers in the register bank are not reset, Xs might be seen on

WDATA and RDATA during simulation. This is normal behavior.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-14

ID110117 Confidential

2.4.3 Verilog parameters for Cortex-M0+

If you are using the full version of the Cortex-M0+ processor, its Verilog parameters are

propagated from the testbench. You can edit file

cortex_m0_mcu/verilog/tb_cmsdk_mcu.v

to

modify these Verilog parameters. Table 2-9 describes the parameters.

Table 2-9 Verilog parameters for Cortex-M0+

Verilog parameters Descriptions

NUMIRQ

Number of Interrupt ReQuest (IRQ) signals. The range is 0-32.

SMUL

Small multiplier. This can be one of the following values:

0 Single cycle multiplier.

1 Small multiplier with multicycle operation.

SYST

SysTick Timer. This can be one of the following values:

0 No timer.

1 Include the SysTick timer.

WIC

Wake-up Interrupt Controller (WIC) support. This can be one of the following values:

0 Remove WIC.

1 Enable WIC feature.

WICLINES

Number of interrupt lines that the WIC supports.

DBG

Debug configuration. This can be one of the following values:

0 Remove debug feature.

1 Include debug feature.

BKPT

Number of breakpoint comparators.

WPT

Number of watchpoint comparators.

BE

Big-endian. This can be one of the following values:

0 Little-endian.

1 Big-endian.

IOP

Single-cycle I/O port. This can be one of the following values:

0 Exclude single-cycle I/O port.

1 Include single-cycle I/O port.

MPU

Memory Protection Unit (MPU). This can be one of the following values:

0 No MPU.

8 8-region MPU.

VTOR

Vector Table Offset Register (VTOR). This can be one of the following values:

0 Exclude VTOR.

1 Include VTOR.

IRQDIS

IRQ Disable (IRQDIS). IRQDIS[i] disables IRQ[i], for example:

32'h00000000

No IRQ disabled.

32'h0000FFFF

IRQ[15:0] disabled.

MTB

Micro Trace Buffer (MTB). This can be one of the following values:

0 Exclude MTB.

1 Include MTB.

AWIDTH

Specifies the MTB SRAM address width.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-15

ID110117 Confidential

2.4.4 Changing the processor type

The Cortex-M0 and Cortex-M0+ example system supports the Cortex-M0 processor and the

Cortex-M0+ processor. To support all designs, the simulation setup provides the following

Verilog command files:

tbench_M0.vc

For the full version of the Cortex-M0 processor, with the processor RTL

path pointing to the default location of

cores/at510_cortexm0_r0p0_03rel2/logical/.

tbench_M0P.vc

For the full version of the Cortex-M0+ processor, with the processor RTL

path pointing to the default location of

cores/at590_cortexm0p_r0p1/logical/.

For simulation, the makefile

cortex_m0_mcu/rtl_sim/makefile

selects the correct Verilog

command file. This makefile also enables you to select your required processor by setting the

parameter

CPU_PRODUCT

to

CORTEX_M0

, or

CORTEX_M0PLUS

.

USER

User/Privilege support. This can be one of the following values:

0 Exclude User/Privilege support.

1 Include User/Privilege support.

RAR

Specifies whether all synchronous states or only the architecturally required state is reset.

0 Only resets the architecturally required state.

1 Resets all synchronous states.

Note

Setting this parameter increases the size of the registers that are not reset by default, and

therefore also increases the overall area of the implementation.

When some of the registers in the register bank are not reset, Xs might be seen on

WDATA and RDATA during simulation. This is normal behavior.

HWF

Halfword fetching. This can be one of the following values:

0 Fetch instructions using 32-bit AHB-Lite accesses whenever possible.

1 Fetch instructions using only 16-bit AHB-Lite accesses.

Table 2-9 Verilog parameters for Cortex-M0+ (continued)

Verilog parameters Descriptions

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-16

ID110117 Confidential

2.5 Memory map

This section describes the system memory maps. It contains the following sections:

•AHB memory map.

•APB subsystem memory map on page 2-17.

2.5.1 AHB memory map

The AHB memory map has a 4GB linear address range, but the system only uses part of the

memory space. If a bus master accesses an invalid memory location with a valid transfer, the

default slave replies with an error response to the bus master.

The file

cmsdk_mcu_system.v

contains the address decoding logic. If you modify the memory

map, you must also modify the address decoding logic in this file.

If you require the example system program to execute from boot loader memory after powerup,

set the boot loader option. This enables the system remap feature. After the boot loader starts,

the program can switch off the remap feature to enable your program to execute from the start

of the memory.

Table 2-10 describes the AHB memory map with and without the remap function.

Table 2-10 AHB memory map

Address Without remap With remap

0xF0220000

-

0xFFFFFFFF

Unused, except for the private peripheral bus

addresses in the Cortex-M0 and Cortex-M0+. Unused, except for the private peripheral bus addresses

in the Cortex-M0 and Cortex-M0+.

0xF0210000

-

0xF021FFFF

(64KB) MTB RAMa.MTB RAM

a.

0xF0201000

-

0xF021FFFF

Unused. Unused.

0xF0200000

-

0xF0200FFF

(4KB) MTB SFRa.MTB SFR

a.

0xF0000401

-

0xF01FFFFF

Unused. Unused.

0xF0000000

-

0xF0000400

(4KB) System ROM table. System ROM table.

0x40020000

-

0xEFFFFFFF

Unused, except for the private peripheral bus

addresses in the Cortex-M0 and Cortex-M0+. Unused, except for the private peripheral bus addresses

in the Cortex-M0 and Cortex-M0+.

0x4001F000

-

0x4001FFFF

(4KB) System controller registers. System controller registers.

0x40012000

-

0x4001EFFF

Unused. Unused.

0x40011000

-

0x40011FFF

(4KB) AHB GPIO 1

I/O port GPIOa.

AHB GPIO 1

I/O port GPIOa.

0x40010000

-

0x40010FFF

(4KB) AHB GPIO 0

I/O port GPIOa.

AHB GPIO 0

I/O port GPIOa

0x40000000

-

0x4000FFFF

(64KB) APB subsystem peripherals. APB subsystem peripherals.

0x20010000

-

0x3FFFFFFF

Unused. Unused.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-17

ID110117 Confidential

If you enable the boot loader, the system executes the following sequence after reset:

1. The processor exits from reset with the remap feature on by default. The processor fetches

the initial Program Counter and stack pointer from boot loader memory. The reset vector

points to the reset handler at the boot loader address

0x0100XXXX

.

2. The processor executes the boot loader from boot loader address

0x0100XXXX

. The remap

feature is still on so the boot loader memory is also visible from the boot loader alias

address. This is necessary if the processor is required to handle interrupts, because the

vector table is at the start of the address space.

3. When the boot loader is ready to switch to program memory, it turns off the remap feature

by writing to a register in the System Controller. See System controller on page 2-19. The

program memory is then visible at the start of the program memory. After the boot loader

switches the memory map, the processor must execute the DSB instruction and then the

ISB instruction to ensure it uses the new memory map.

4. The boot loader loads the initial stack pointer value from the program memory, and

branches to the reset handler that the reset vector specifies in the program memory.

When the linking stage creates the boot loader image, it must specify the memory location of

the boot loader actual address, not the alias. The example software includes an example boot

loader in the

software/common/bootloader/bootloader.c

file.

2.5.2 APB subsystem memory map

Table 2-11 describes the peripherals in the APB subsystem.

0x20000000

-

0x2000FFFF

(64KB) RAM. RAM.

0x01010000

-

0x1FFFFFFF

Unused. Unused.

0x01000000

-

0x0100FFFF

(64KB) Optional boot loader memory. Actual size 4KB,

access above 4KB wraps round. Optional boot loader memory. Actual size 4KB, access

above 4KB wraps round.

0x00010000

-

0x00FFFFFF

Unused. Unused.

0x00000000

-

0x0000FFFF

(64KB) Program memory. Alias of optional boot loader memory. Actual size 4KB,

access above 4KB wraps round.

a. For use with the Cortex-M0+ only.

Table 2-10 AHB memory map (continued)

Address Without remap With remap

Table 2-11 APB subsystem peripherals

Address Item Notes

0x4000F000

-

0x4000FFFF

APB expansion port 15 Connected to micro DMA controller configuration port

0x4000E000

-

0x4000EFFF

APB expansion port 14 Not used

0x4000D000

-

0x4000DFFF

APB expansion port 13 Not used

0x4000C000

-

0x4000CFFF

APB expansion port 12 Not used

0x4000B000

-

0x4000BFFF

APB test slave For validation of AHB to APB bridge

0x40009000

-

0x4000AFFF

Not used Ports on APB slave multiplexer disabled

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-18

ID110117 Confidential

For more information on the APB subsystem, see the Arm® Cortex®-M System Design Kit

Technical Reference Manual.

0x40008000

-

0x40008FFF

Watchdog -

0x40007000

-

0x40007FFF

Not used Port on APB slave multiplexer disabled

0x40006000

-

0x40006FFF

UART2

Stdout

text message for simulations

0x40005000

-

0x40005FFF

UART1 -

0x40004000

-

0x40004FFF

UART0 -

0x40003000

-

0x40003FFF

Not used Port on APB slave multiplexer disabled

0x40002000

-

0x40002FFF

Dual timer -

0x40001000

-

0x40001FFF

Timer1 -

0x40000000

-

0x40000FFF

Timer0 -

Table 2-11 APB subsystem peripherals (continued)

Address Item Notes

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-19

ID110117 Confidential

2.6 System controller

This section describes the system controller. It contains the following sections:

•About the system controller.

•System controller block diagram.

•Programmers model on page 2-20.

2.6.1 About the system controller

The example system contains a simple system controller that provides:

• Control of the memory remap feature.

• The ability to enable or disable the operation of the Power Management Unit (PMU), if

available.

• The ability to enable an automatic reset if the system locks up.

• Information about the cause of the last reset.

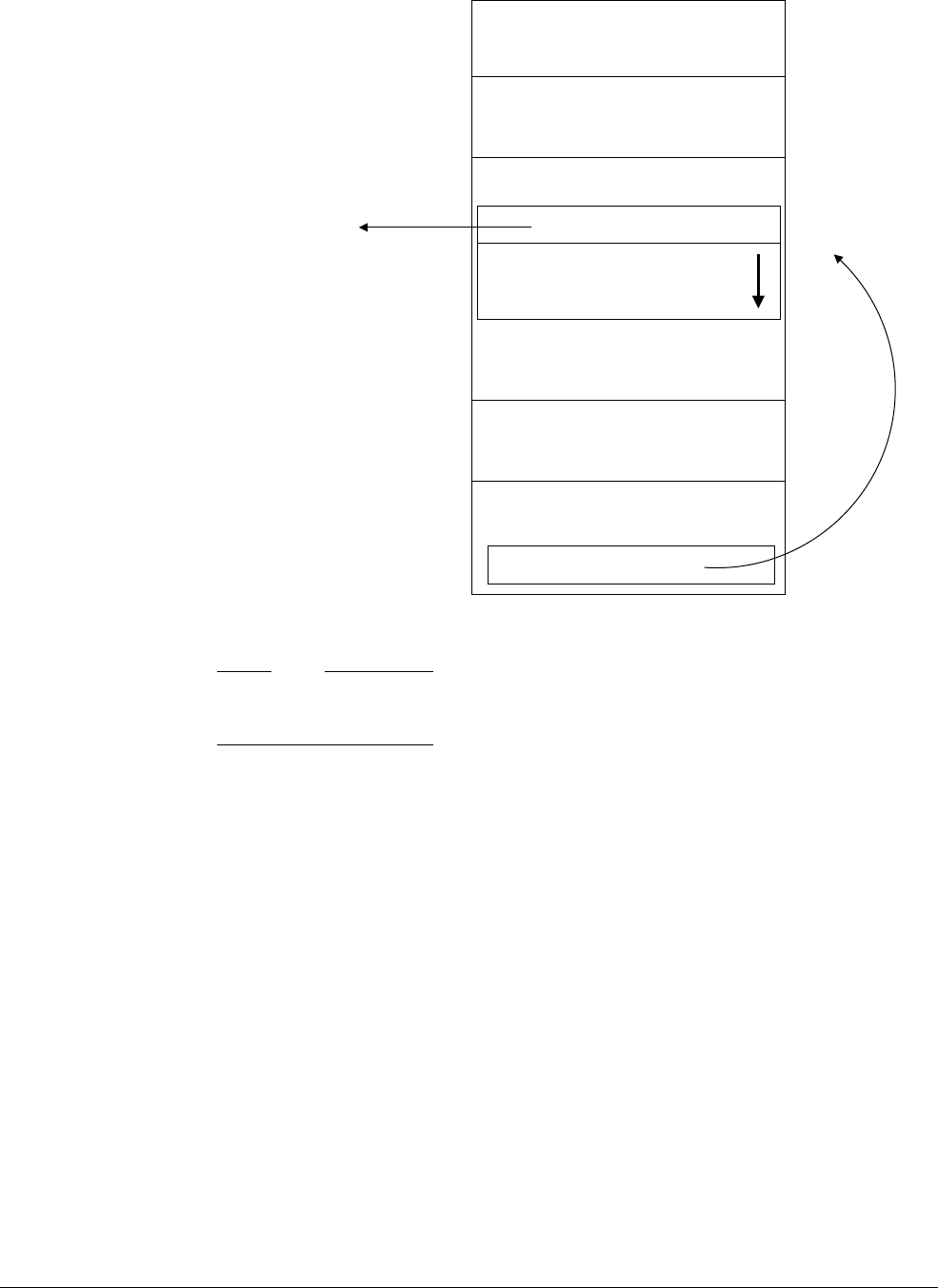

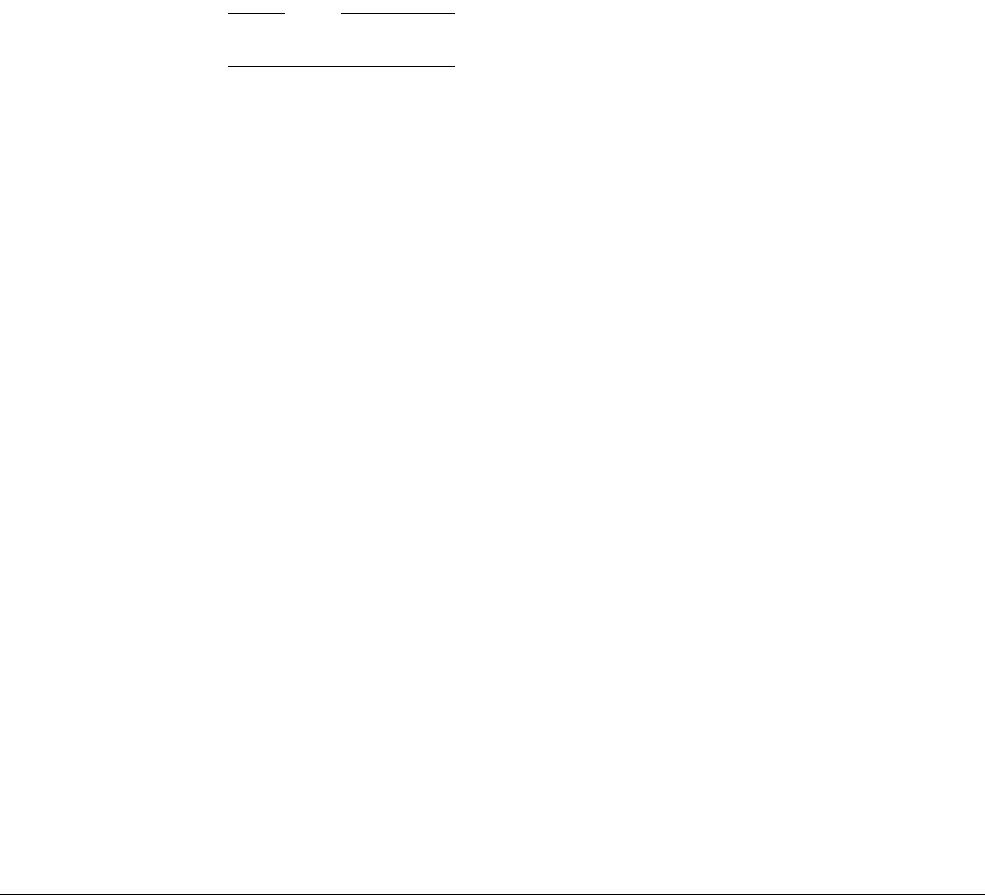

2.6.2 System controller block diagram

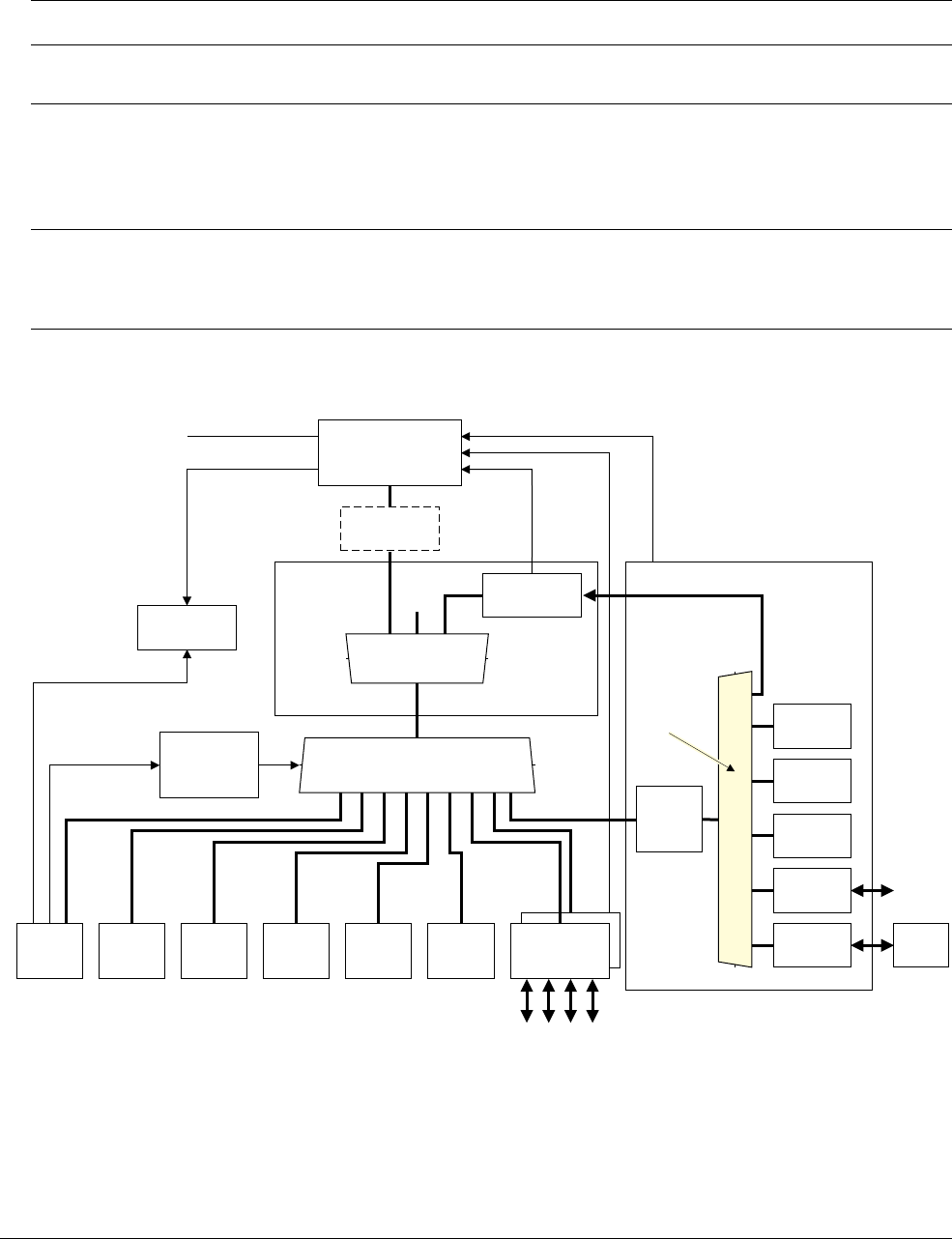

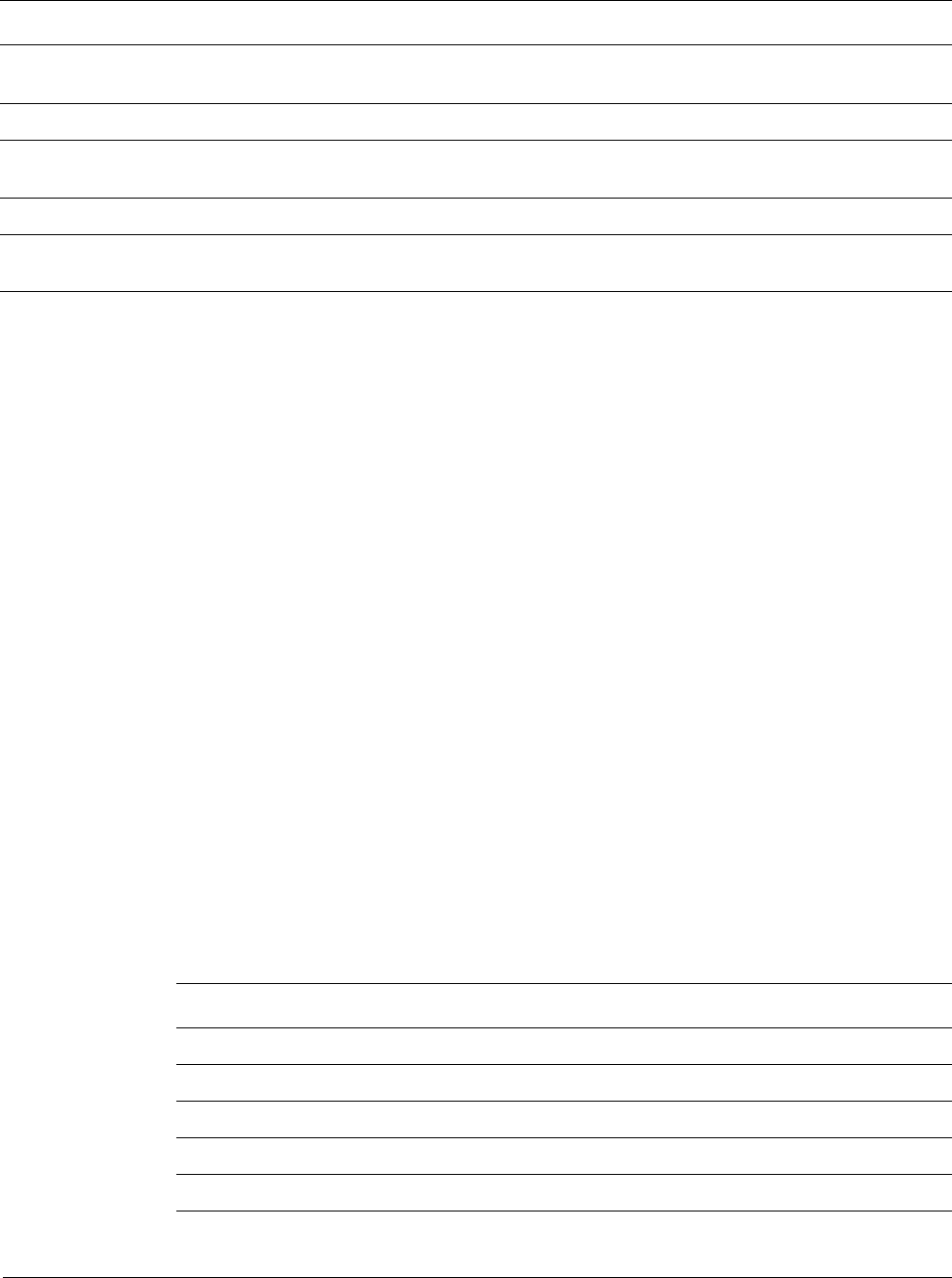

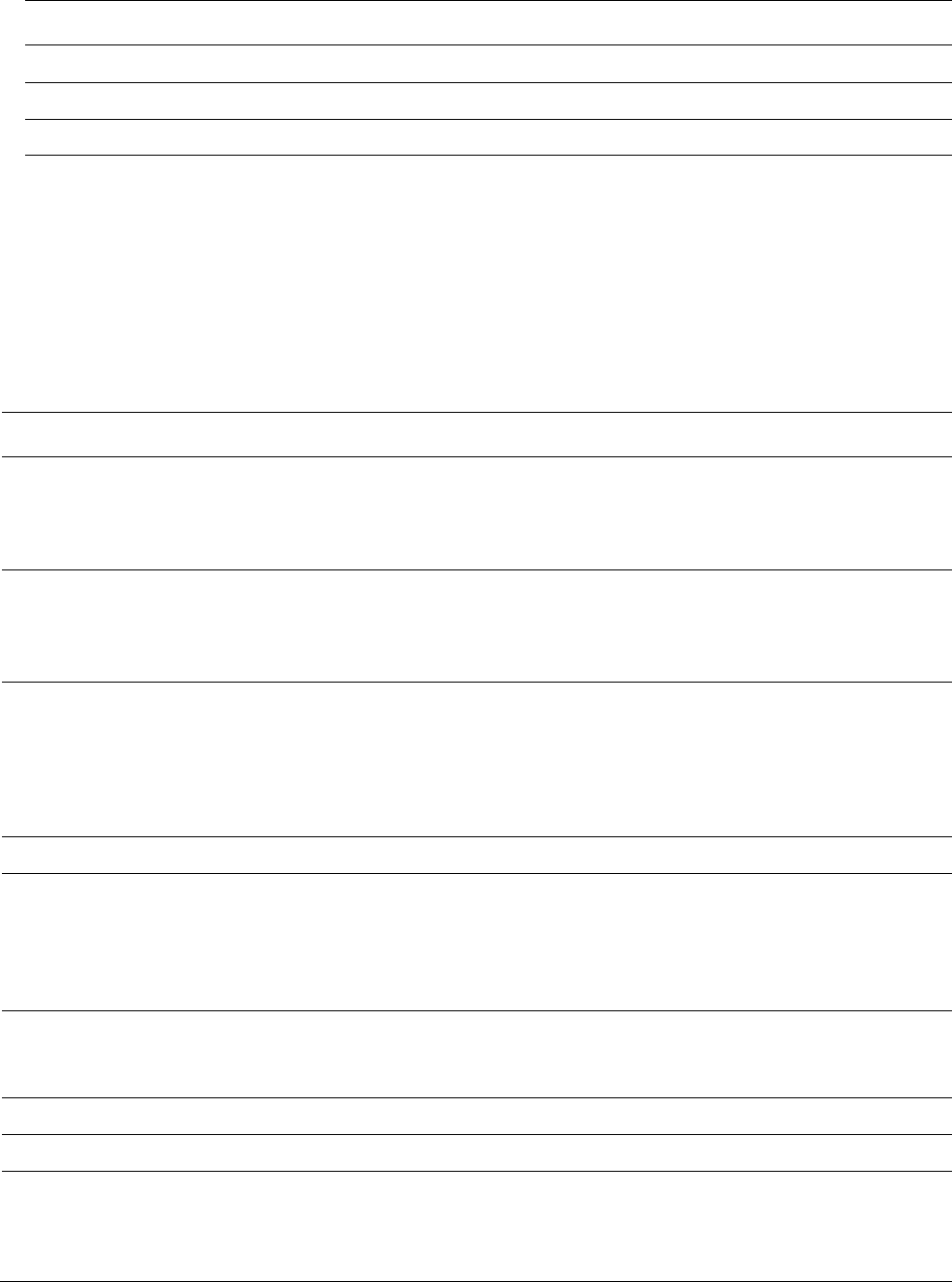

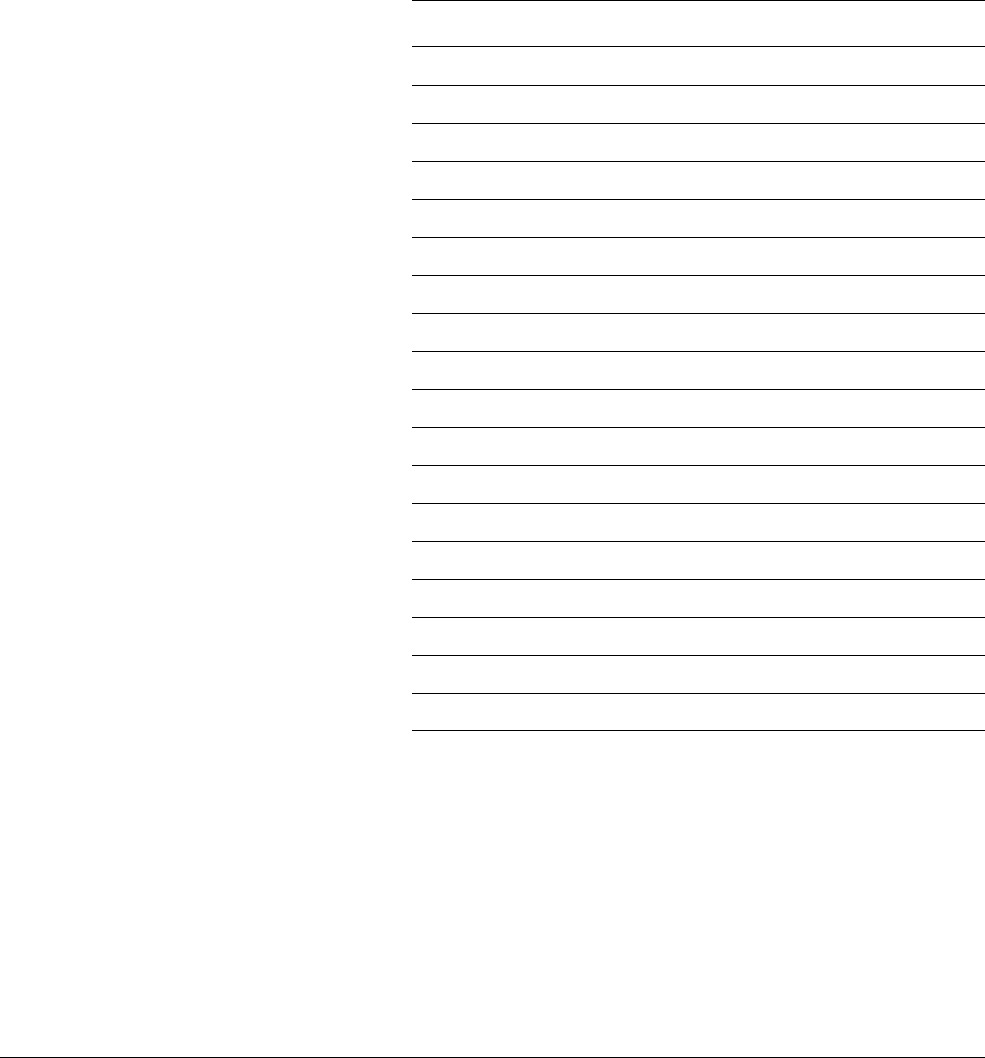

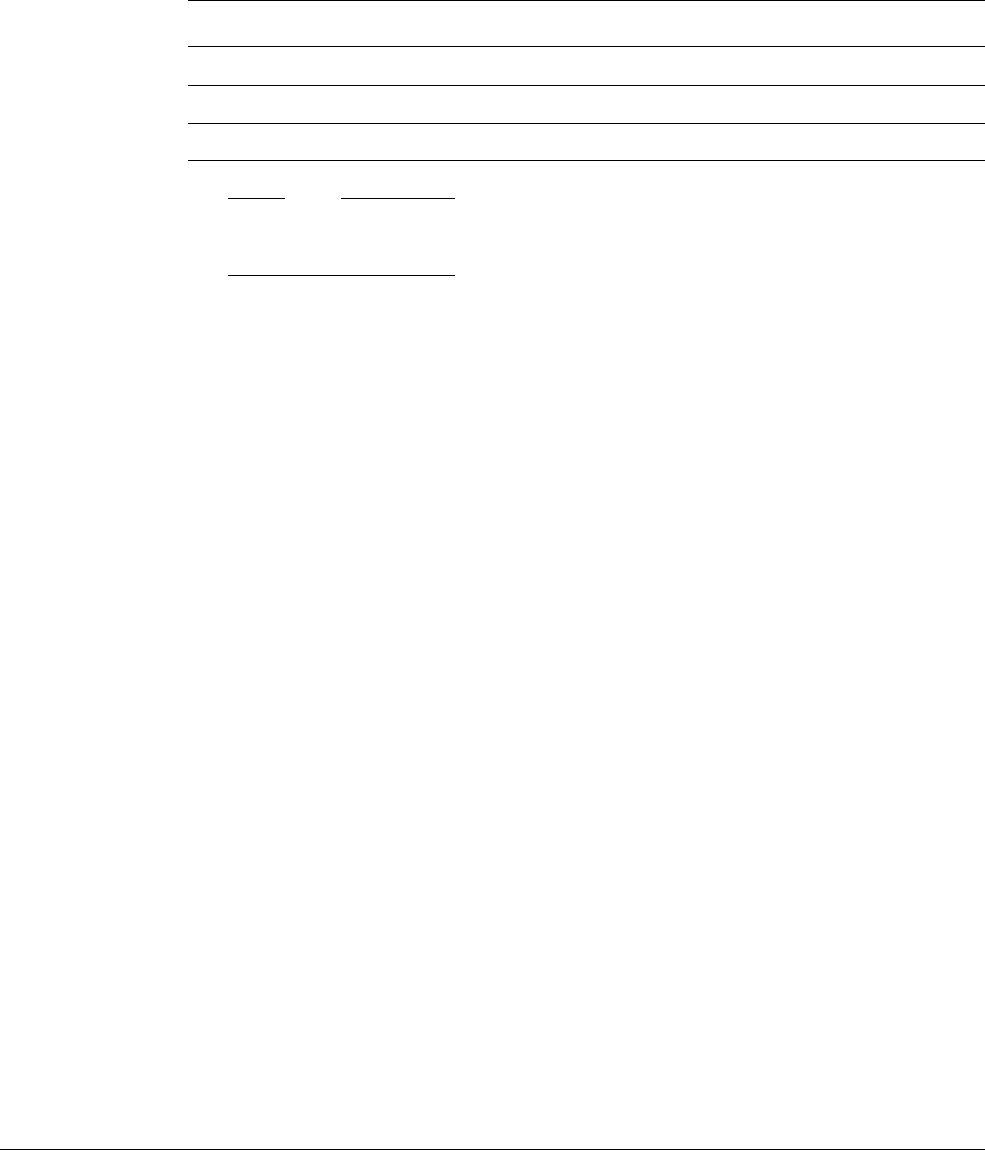

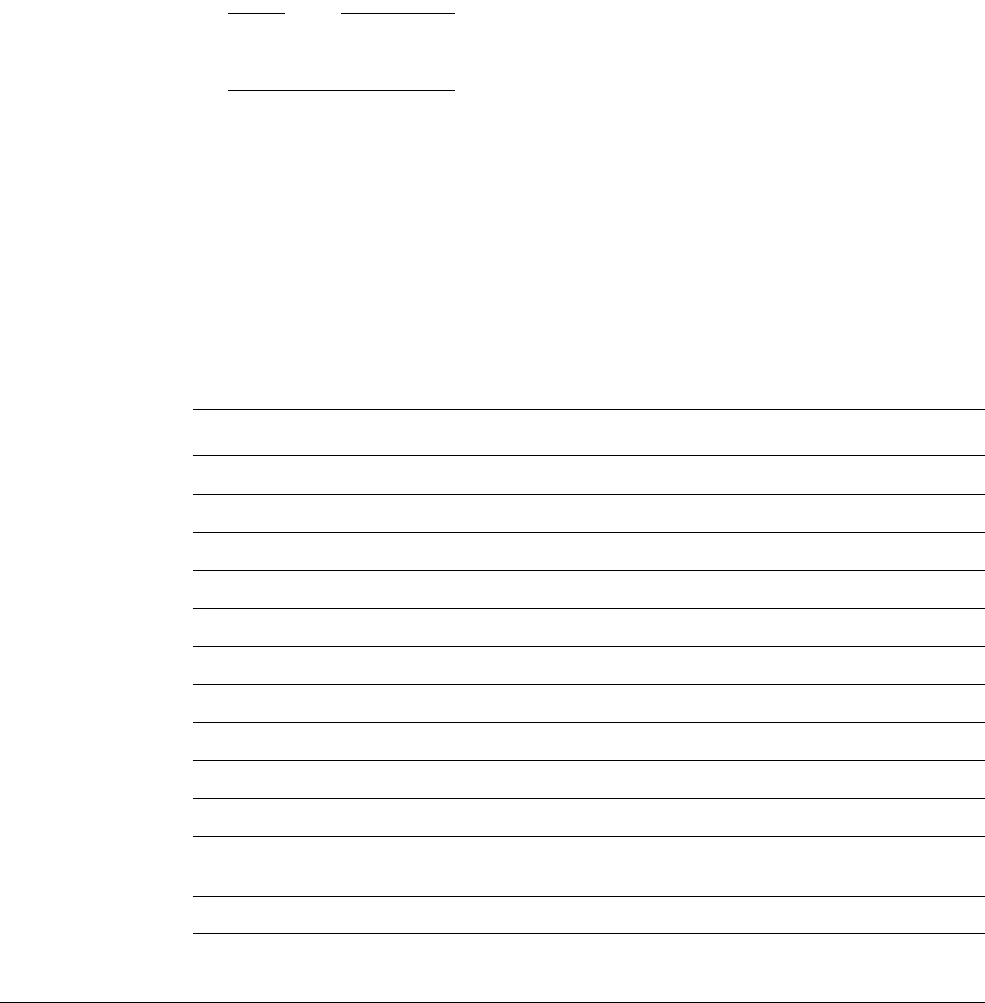

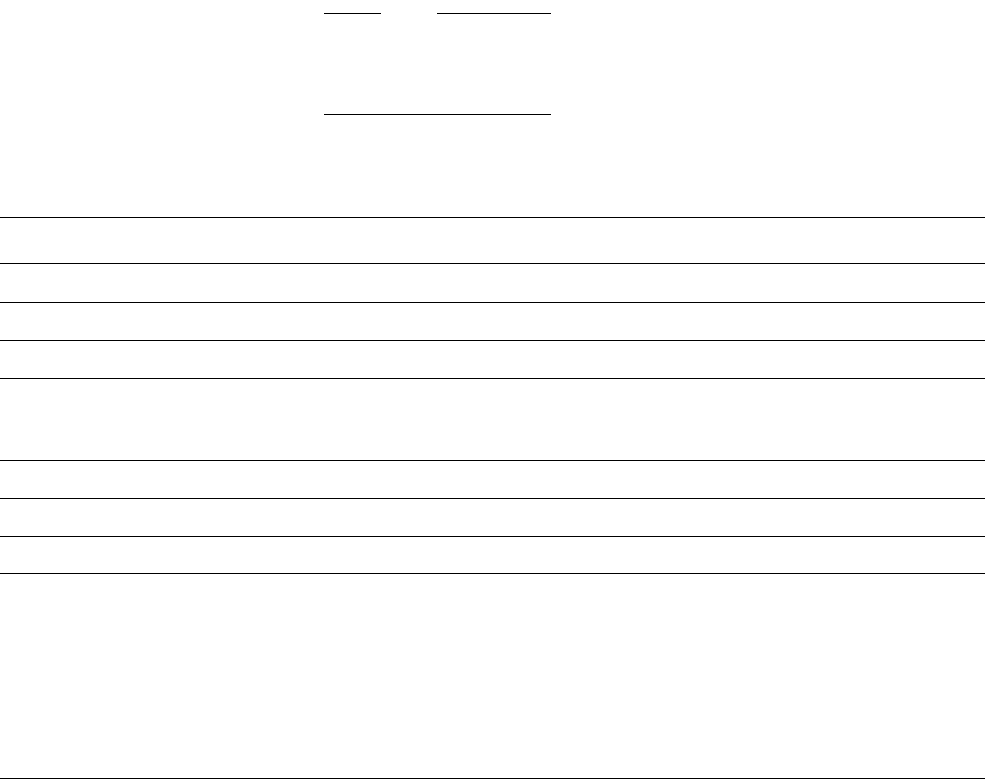

Figure 2-6 shows the example system controller.

Figure 2-6 Example system controller

Table 2-12 shows the non-AHB signals of the system controller.

FCLK

HCLK

HRESETn

PORESETn

HSEL

HADDR[11:0]

HTRANS[1:0]

HSIZE[2:0]

HWRITE

HREADY

HWDATA[31:0]

HREADYOUT

HRESP

HRDATA[31:0]

ECOREVNUM[3:0]

SYSRESETREQ

WDOGRESETREQ

REMAP

PMUENABLE

LOCKUPRESET

LOCKUP

cmsdk_mcu_sysctrl.v

Table 2-12 Example system controller non-AHB signals

Signals Descriptions

LOCKUP Tells the RSTINFO register that the cause of a system reset is because the processor enters the lockup state

SYSRESETREQ Enables a status register to capture the System Reset Request event

WDOGRESETREQ Enables a status register to capture the Watchdog Reset Request event

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-20

ID110117 Confidential

The design provides a 4-bit ECOREVNUM input that is connected to peripheral ID register 3.

It indicates the revision changes during an Engineering Change Order (ECO) of the chip design

process. You can tie this signal LOW, or connect it to special tie-off cells so that you can change

the ECO revision number in a silicon netlist, or at a lower level, for example the silicon mask.

2.6.3 Programmers model

Table 2-13 describes the system controller programmers model.

REMAP Enables the memory remap feature

PMUENABLE Enables the PMU for the WakeUp Interrupt Controller (WIC) mode deep sleep operation

LOCKUPRESET Enable the clock and reset controller to generate a system reset automatically if the system locks up

Table 2-12 Example system controller non-AHB signals (continued)

Signals Descriptions

Table 2-13 System controller programmers model

Address Name Type Reset Descriptions

0x4001F000

REMAP RW 1 Bit 0:

1 Enable remap feature.

0 Disable remap feature.

Software symbol: CMSDK_SYSCON->REMAP

0x4001F004

PMUCTRL RW 0 Bit 0:

1 Enable PMU. If not present, the value of this bit is ignored.

0 Disable PMU.

Software symbol CMSDK_SYSCON->PMUCTRL

0x4001F008

RESETOP RW 0 Bit 0:

1 Automatically generates system reset if the processor is in the

LOCKUP state.

0 Does not automatically generate reset when the processor is in the

LOCKUP state.

Software symbol CMSDK_SYSCON->RESETOP

0x4001F00C

- - - Reserved

0x4001F010

RSTINFO RW 0 Bit 2 - If 1, processor LOCKUP caused the reset.

Bit 1 - If 1, Watchdog caused the reset.

Bit 0 - If 1, SYSRESETREQ caused the reset.

Write 1 to each bit to clear.

Software symbol CMSDK_SYSCON-> RSTINFO

0x4001FFD0

PID4 RO

0x04

Peripheral ID 4.

[7:4] Block count.

[3:0] jep106_c_code.

0x4001FFD4

PID5 RO

0x00

Peripheral ID 5, not used.

0x4001FFD8

PID6 RO

0x00

Peripheral ID 6, not used.

0x4001FFDC

PID7 RO

0x00

Peripheral ID 7, not used.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-21

ID110117 Confidential

The PORESETn signal resets the RSTINFO register. The HRESETn signal resets all the other

resettable registers.

0x4001FFE0

PID0 RO

0x26

Peripheral ID 0.

[7:0] Part number.

0x4001FFE4

PID1 RO

0xB8

Peripheral ID 1.

[7:4] jep106_id_3_0.

[3:0] Part number[11:8].

0x4001FFE8

PID2 RO

0x1B

Peripheral ID 2.

[7:4] revision .

[3] jedec_used.

[2:0] jep106_id_6_4.

0x4001FFEC

PID3 RO

0x-0

Peripheral ID 3.

[7:4] ECO revision number.

[3:0] Customer modification number.

0x4001FFF0

CID0 RO

0x0D

Component ID 0.

0x4001FFF4

CID1 RO

0xF0

Component ID 1 (PrimeCell class).

0x4001FFF8

CID2 RO

0x05

Component ID 2.

0x4001FFFC

CID3 RO

0xB1

Component ID 3.

Table 2-13 System controller programmers model (continued)

Address Name Type Reset Descriptions

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-22

ID110117 Confidential

2.7 I/O pins

The example microcontroller has two 16-bit I/O ports and several debug signal connections.

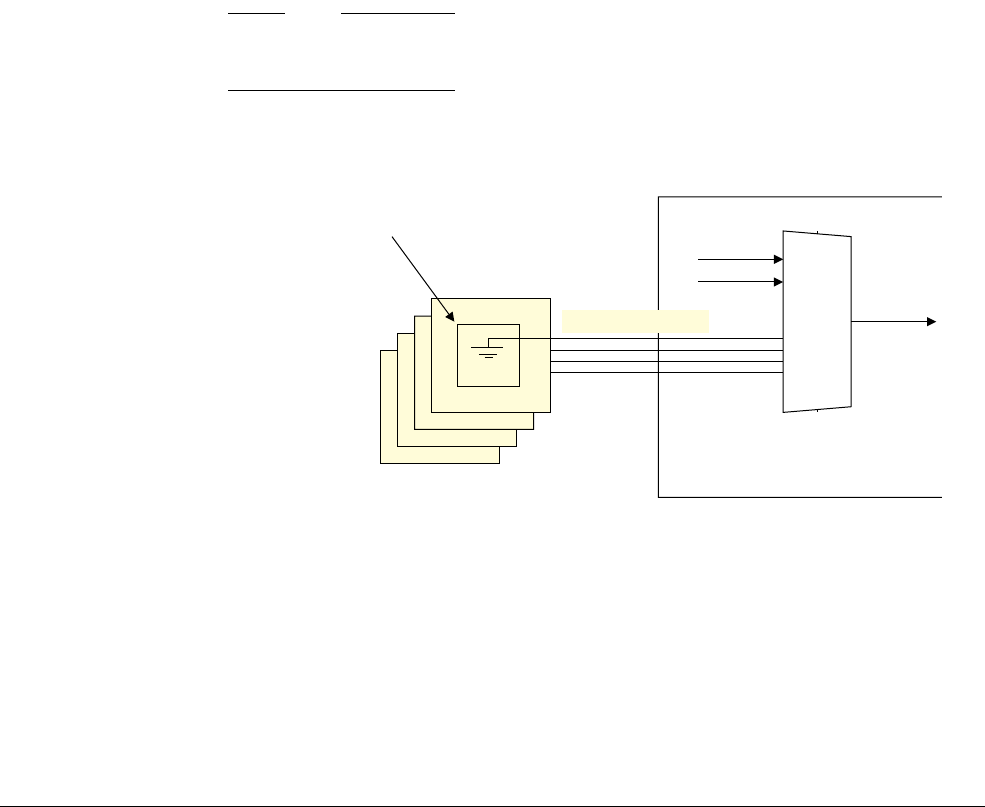

You can switch several I/O port pins to an alternate function. Figure 2-7 shows the interface of

the example microcontroller.

Figure 2-7 Example microcontroller interface

Table 2-14 describes the I/O of the example MicroController Unit (MCU).

cmsdk_mcu

Clock and

reset

signals

Optional debug

signal (only if

JTAG is included)

Debug

signals

I/O port 0

I/O port 1

NRST

XTAL1

XTAL2

SWCLKTCK

SWDIOTMS

nNRST

TDI

TDO

P0[15:0]

P1[15:0]

Table 2-14 Example MCU I/O

Signal Direction Description

XTAL1 Input Crystal oscillator

XTAL2 Output Crystal oscillator feedback

NRST Input Reset, active LOW

P0[15:0] Input GPIO

P1[15:0] Input GPIO

nTRST Input JTAG reset, active LOWa

a. This signal is only present when you select the JTAG option.

TDI Input JTAG data ina

SWDIOTMS Input Serial Wire Data or JTAG TMS

SWCLKTCK Input Serial Wire clock or JTAG clock

TDO Output JTAG data outa

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-23

ID110117 Confidential

Table 2-15 shows the alternate functions of the GPIO 1 ports that support pin multiplexing.

Before you use the I/O pins for alternate functions, you might want to program the

corresponding GPIO alternate function registers. This step might not be necessary when you use

the alternate function as an input.

Table 2-15 GPIO alternate functions

Pin Alternate function

GPIO 1 [15:10] No alternate function.

GPIO 1 [9] Timer 1 EXTIN. Always use as timer 1 external input. The GPIO 1 alternate function setting has no effect.

GPIO 1 [8] Timer 0 EXTIN. Always use as timer 0 external input. The GPIO 1 alternate function setting has no effect.

GPIO 1 [7] TSTART to MTB.

GPIO 1 [6] TSTOP to MTB.

GPIO 1 [5] UART2 TXD.

GPIO 1 [4] UART2 RXD. Always use as UART input. The GPIO 1 alternate function setting has no effect.

GPIO 1 [3] UART1 TXD.

GPIO 1 [2] UART1 RXD. Always use as UART input. The GPIO 1 alternate function setting has no effect.

GPIO 1 [1] UART0 TXD.

GPIO 1 [0] UART0 RXD. Always use as UART input. The GPIO 1 alternate function setting has no effect.

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-24

ID110117 Confidential

2.8 Interrupts and event functions

The example system contains:

• 32 Interrupt Request (IRQ) lines.

• One NonMaskable Interrupt (NMI).

• One event signal.

2.8.1 Interrupt assignments

Table 2-16 describes the interrupt assignments.

2.8.2 Interrupt synchronization

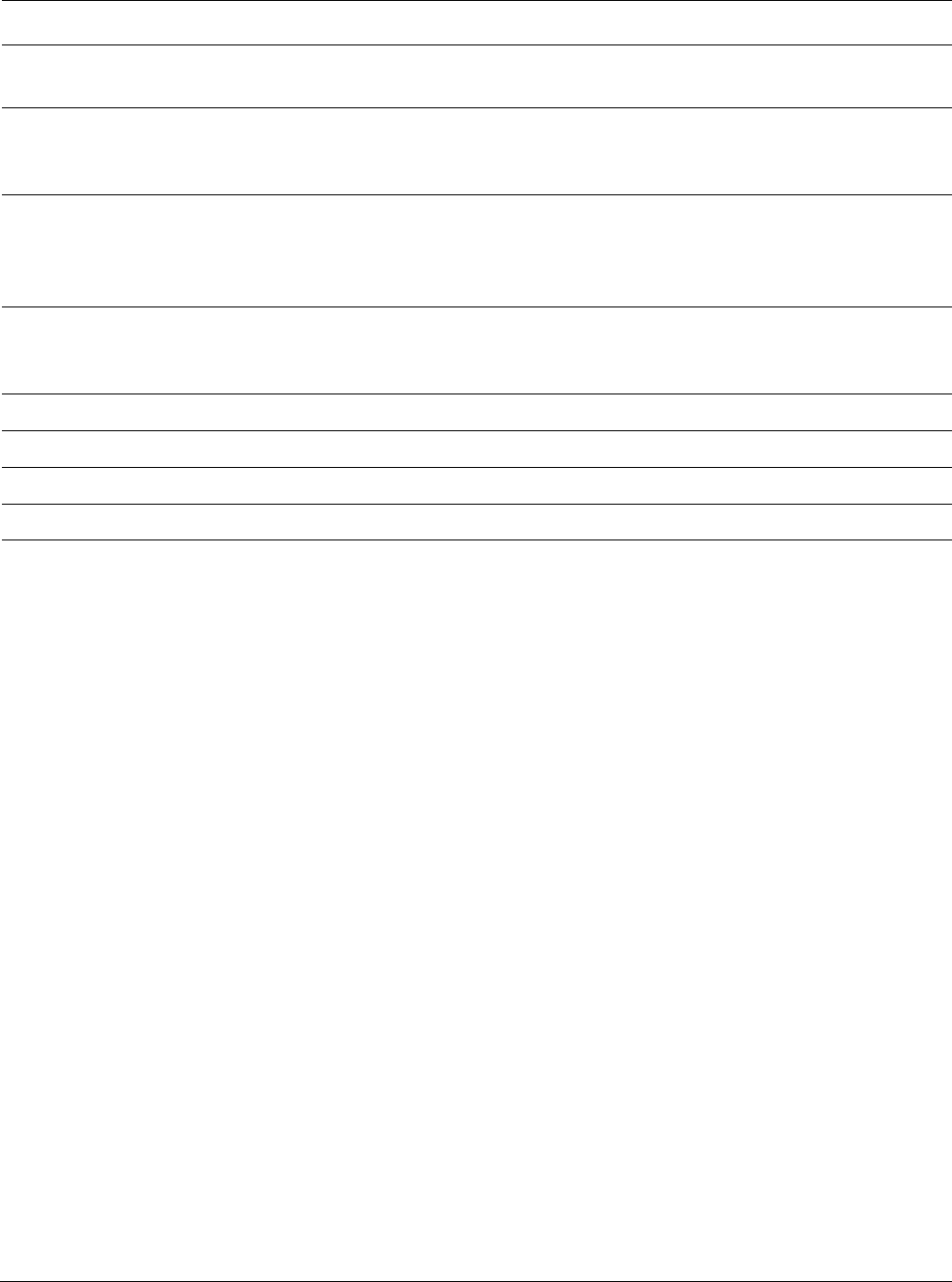

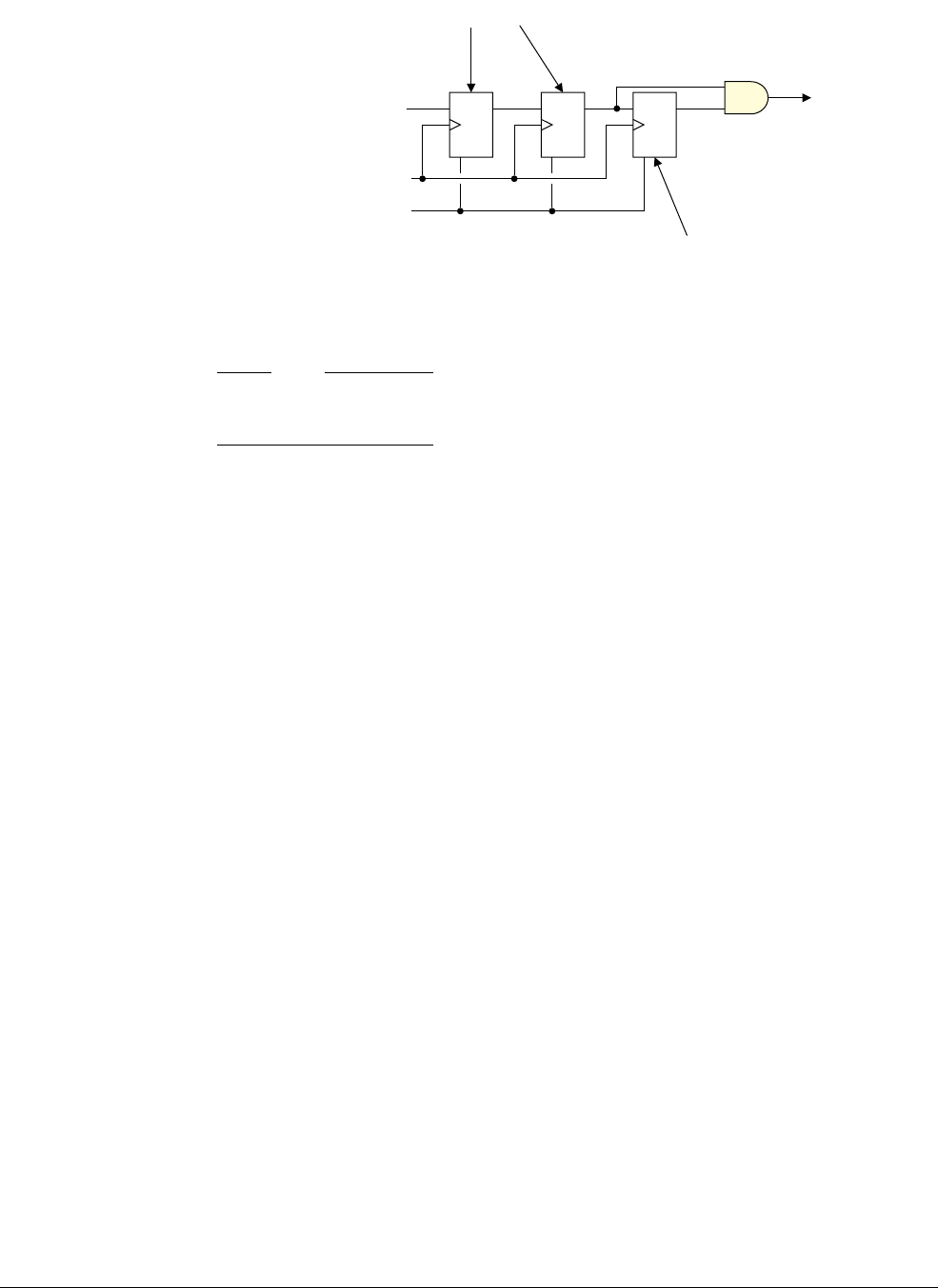

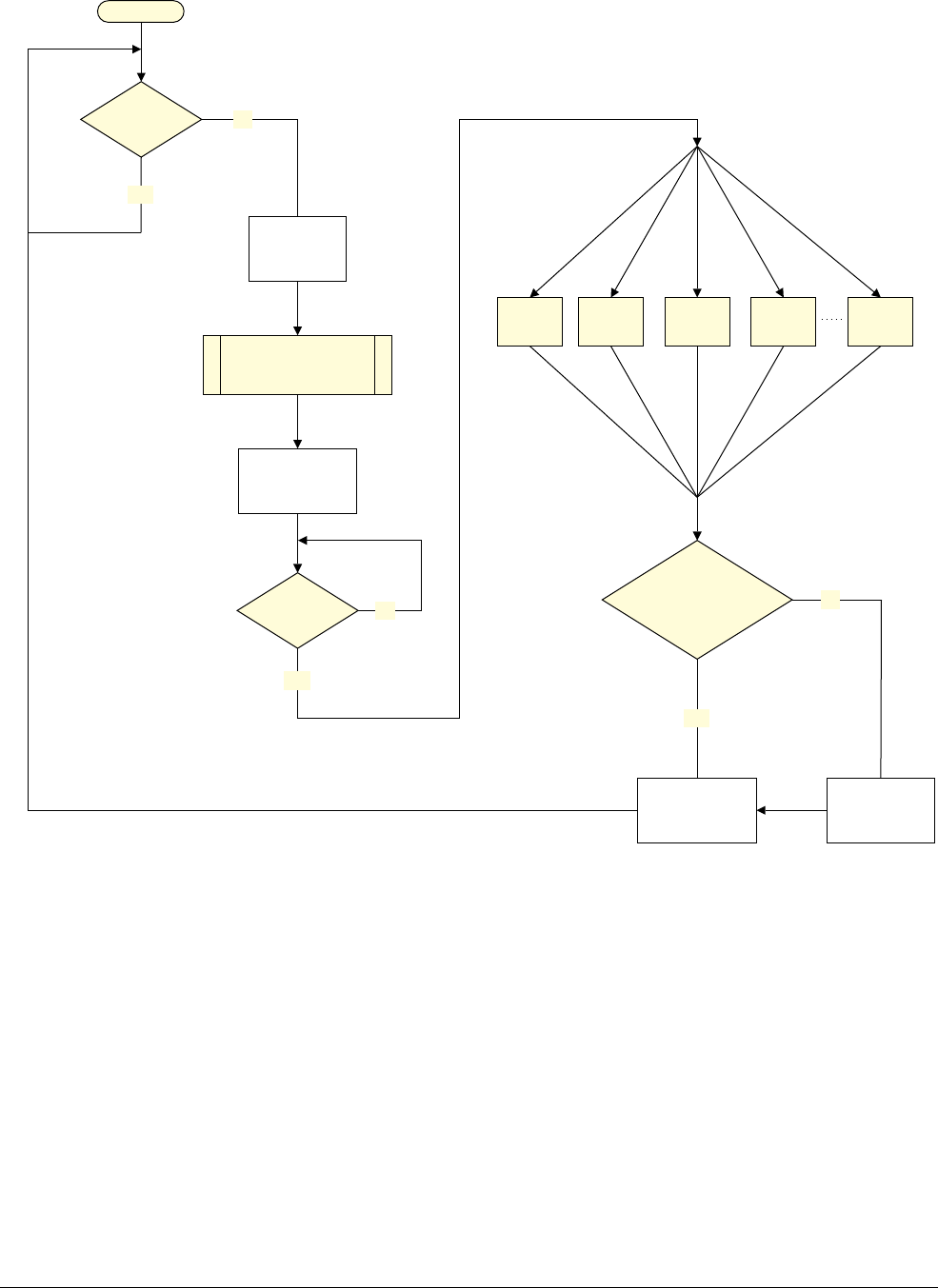

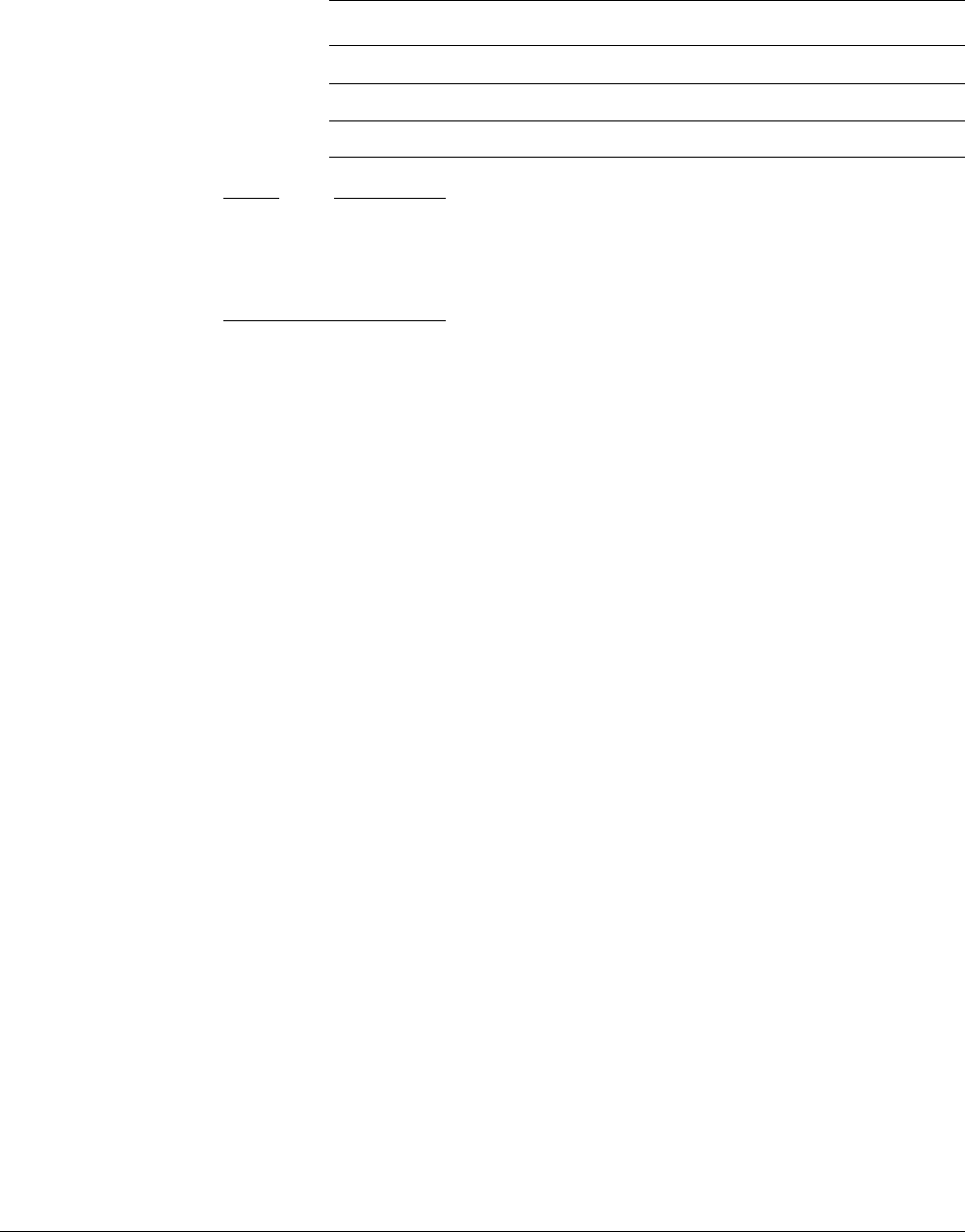

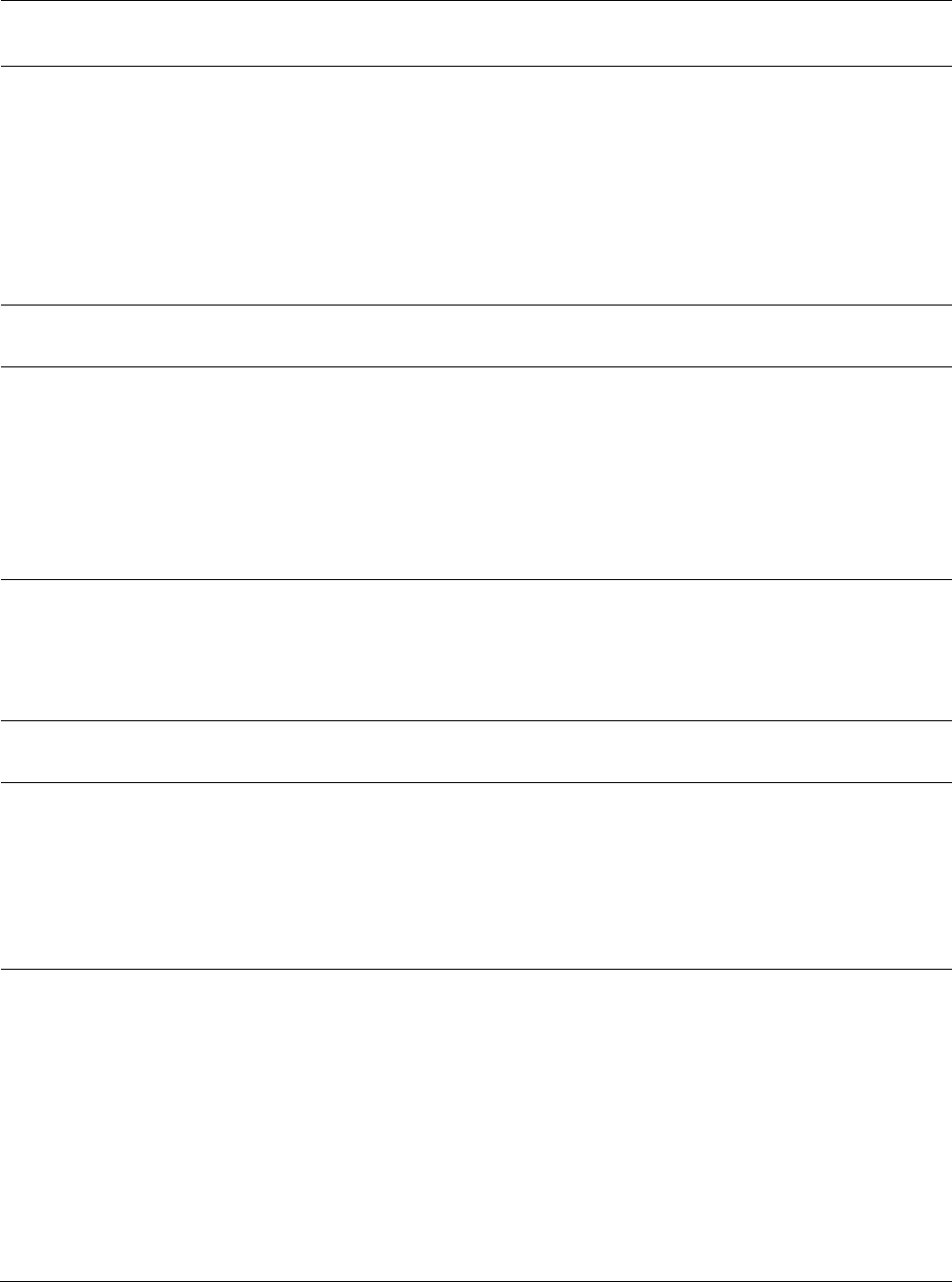

If a peripheral generates an interrupt signal in a clock domain that is asynchronous to the

processor clock, you must synchronize the interrupt signal to the processor clock domain before

you connect it to the NVIC of the processor. Figure 2-8 on page 2-25 shows an example circuit

that performs this synchronization.

Table 2-16 Interrupt assignments

IRQ/NMI Device

NMI Watchdog

0 UART 0 receive interrupt

1 UART 0 transmit interrupt

2 UART 1 receive interrupt

3 UART 1 transmit interrupt

4 UART 2 receive interrupt

5 UART 2 transmit interrupt

6 GPIO 0 combined interrupt for AHB GPIO and I/O port GPIO

7 GPIO 1 combined interrupt for AHB GPIO and I/O port GPIO

8Timer 0

9Timer 1

10 Dual timer

11 Not used

12 UART 0 overflow interrupt

13 UART 1 overflow interrupt

14 UART 2 overflow interrupt

15 DMA done and DMA error

16-31 GPIO 0 individual interrupts

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-25

ID110117 Confidential

Figure 2-8 IRQ synchronizer

Note

The IRQ synchronizer only works with a level-triggered interrupt source, so the peripheral must

hold the interrupt signal HIGH until the processor clears the ISR interrupt signal.

The APB subsystem contains several example IRQ synchronizers to demonstrate their use. The

synchronizers are optional. They are only enabled if you set the Verilog parameter

INCLUDE_IRQ_SYNCHRONIZER

to a nonzero value. This Verilog parameter is defined in the

apb_subsystem.v

file. It is not overridden in the

cmsdk_mcu_system.v

file.

The example system design uses the same clock source for the processor clock HCLK and the

peripheral clocks PCLK and PCLKG. Therefore there is no asynchronous clock domain

boundary, so this parameter is set LOW.

2.8.3 Event

The Cortex-M0 and Cortex-M0+ have an RXEV input signal. If software uses the

WFE

instruction to put the processor to sleep, an event received at RXEV wakes up the processor. In

the example system, RVEX is connected to dma_done of the DMA-230 Micro DMA

controller. This enables the processor to wake up from WFE sleep when the DMA process

finishes.

DQDQDQ

Synchronized

Interrupt signal

to the processor

Interrupt

source

Processor

clock

Reset

Extra D-type flip-flop to prevent

glitches generating an unwanted pulse

Prevents metastability

Functional description

ARM DUI 0559D Copyright © 2011, 2013, 2017 Arm Limited (or its affiliates). All rights reserved. 2-26

ID110117 Confidential

2.9 AHB system ROM table

This module,