Cupl 5

User Manual: Cupl 5 - powered by h5ai v0.28.1 (s://larsjung.de/h5ai/)

Open the PDF directly: View PDF ![]() .

.

Page Count: 2

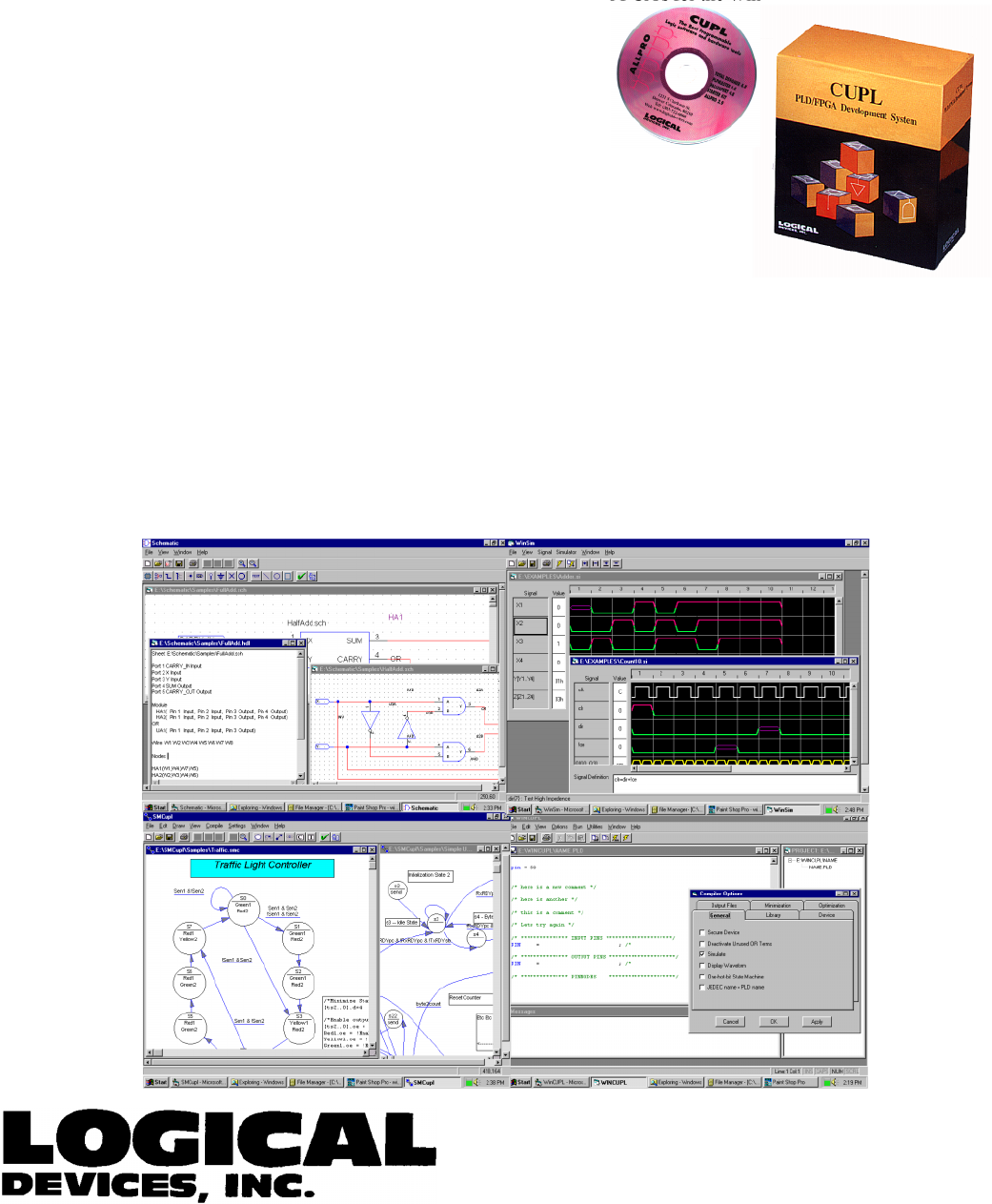

ChipDesigner 5.0 100% CUPL compatible $1995.00

32-BIT Window NT based EDA Tool for Programmable Logic

Logical Devices. Inc. announces a new fully integrated design tool for PLD and FPGA’s for the Windows NT platform including the

following components:

Graphical State Machine Design Entry

Schematic/Logic Capture Design Entry

Graphical Truth Table

HDL Editor with full syntax checking

Automatic Device Partitioning

Graphical Waveform Simulation input and output

Project Navigator

Optional VHDL Compiler

Direct EDIF , PLA, XNF, QDIF, AHDL output formats

Import Orcad, Viewlogic, Protel, Accel, PADs... etc. schematic net lists

Including 9 Free Fitters

ChipDesigner 5.0 is a true 32-bit native application and will run large PLD and FPGA design without any of the memory limitations

encountered with the 16 bit operating systems. CUPL is a universal development environment for PLD and FPGAs. In the past CUPL was

limited to text based HDL development methodology. The CUPL 5.0 has changed this to a product with a strong mix of text and graphics

design methodology for logic design. ChipDesigner 5.0 includes all devices and libraries, all of the software components listed above for

$995.00 only. This make ChipDesigner 5.0 this most cost effective EDA tool for programmable logic on the market. This level product was

previously marketed for nearly $3K now offered at such low price in order to make the product financially accessible to a larger engineering

audience.

www.logicaldevices.com

303-861-8200

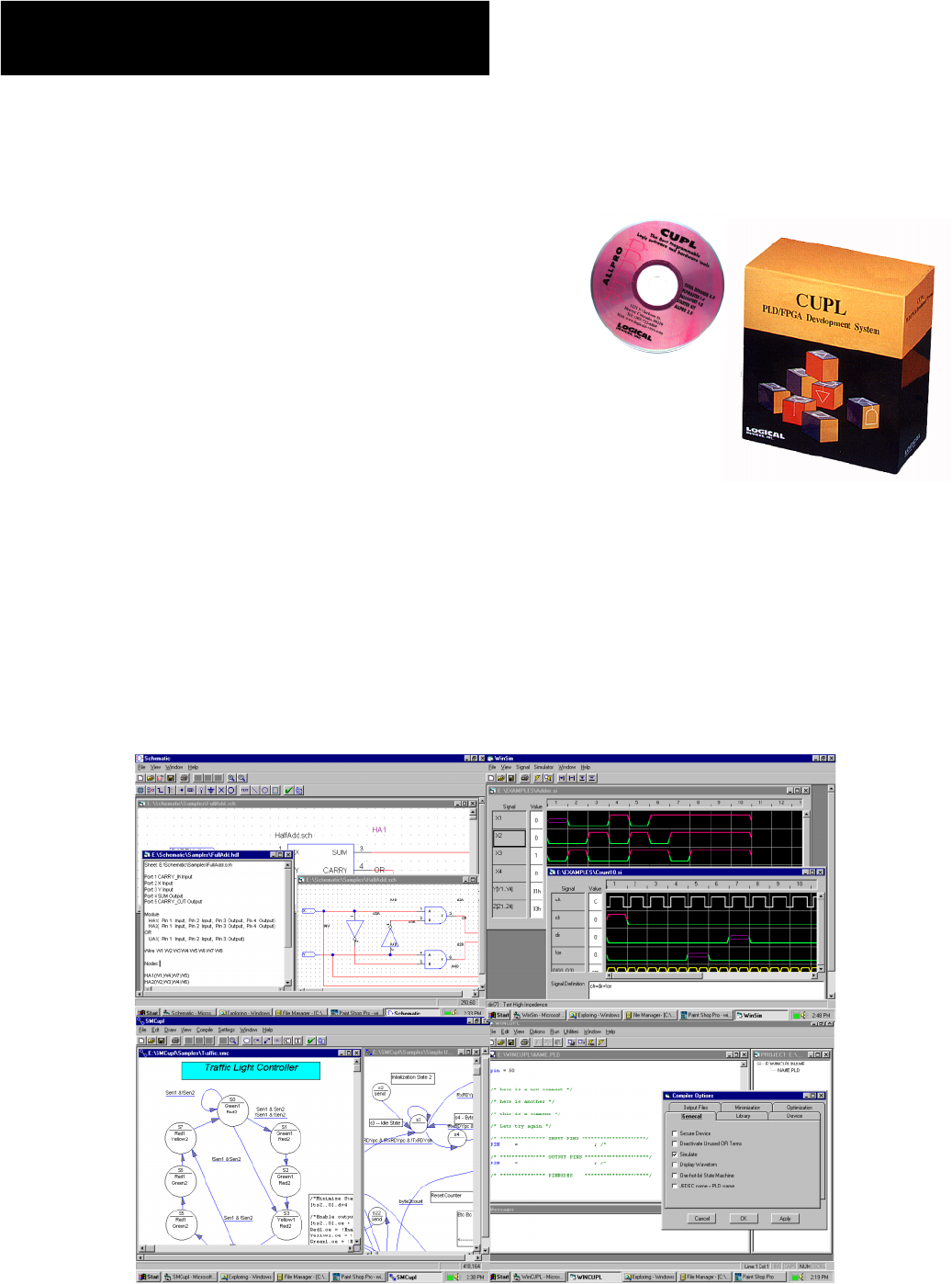

Logical Devices. Inc. announces a new fully integrated design tool for PLD and FPGA’s for the Windows NT platform including the

following components:

Graphical State Machine Design Entry

Schematic/Logic Capture Design Entry

Graphical Truth Table

HDL Editor with full syntax checking

Automatic Device Partitioning

Graphical Waveform Simulation input and output

Project Navigator

Optional VHDL Compiler

Direct EDIF , PLA, XNF, QDIF, AHDL output formats

Import Orcad, Viewlogic, Protel, Accel, PADs... etc. schematic net lists

Including 9 Free Fitters

CUPL 5.0 is a true 32-bit native application and will run large PLD and FPGA design without any of the memory limitations encountered

with the 16 bit operating systems. CUPL is a universal development environment for PLD and FPGAs. In the past CUPL was limited to

text based HDL development methodology. The CUPL 5.0 has changed this to a product with a strong mix of text and graphics design

methodology for logic design. CUPL 5.0 (Version Total Designer) includes all devices and libraries, all of the software components listed

above for $995.00 only. This make CUPL this most cost effective EDA tool for programmable logic on the market. This level product was

previously marketed for nearly $3K now offered at such low price in order to make the product financially accessible to a larger engineer-

ing audience.

32-BIT Window NT based EDA Tool for Programmable Logic

ChipDesigner 5.0

CUPL COMPATIBLE