NEON Programmer’s Guide DEN0018A Programmers

User Manual:

Open the PDF directly: View PDF ![]() .

.

Page Count: 411 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- NEON Programmer’s Guide

- Contents

- Preface

- 1: Introduction

- 2: Compiling NEON Instructions

- 2.1 Vectorization

- 2.1.1 Enabling auto-vectorization in ARM Compiler toolchain

- 2.1.2 Enabling auto-vectorization in GCC compiler

- 2.1.3 C pointer aliasing

- 2.1.4 Natural types

- 2.1.5 Array grouping

- 2.1.6 Inside knowledge

- 2.1.7 Enabling the NEON unit in bare-metal applications

- 2.1.8 Enabling the NEON unit in a Linux stock kernel

- 2.1.9 Enabling the NEON unit in a Linux custom kernel

- 2.1.10 Optimizing for vectorization

- 2.2 Generating NEON code using the vectorizing compiler

- 2.3 Vectorizing examples

- 2.4 NEON assembler and ABI restrictions

- 2.5 NEON libraries

- 2.6 Intrinsics

- 2.7 Detecting presence of a NEON unit

- 2.8 Writing code to imply SIMD

- 2.9 GCC command line options

- 2.1 Vectorization

- 3: NEON Instruction Set Architecture

- 4: NEON Intrinsics

- 4.1 Introduction

- 4.2 Vector data types for NEON intrinsics

- 4.3 Prototype of NEON Intrinsics

- 4.4 Using NEON intrinsics

- 4.5 Variables and constants in NEON code

- 4.6 Accessing vector types from C

- 4.7 Loading data from memory into vectors

- 4.8 Constructing a vector from a literal bit pattern

- 4.9 Constructing multiple vectors from interleaved memory

- 4.10 Loading a single lane of a vector from memory

- 4.11 Programming using NEON intrinsics

- 4.12 Instructions without an equivalent intrinsic

- 5: Optimizing NEON Code

- 5.1 Optimizing NEON assembler code

- 5.2 Scheduling

- 5.2.1 NEON instruction scheduling

- 5.2.2 Mixed ARM and NEON instruction sequences

- 5.2.3 Passing data between ARM general-purpose registers and NEON registers

- 5.2.4 Dual issue for NEON instructions

- 5.2.5 Example of how to read NEON instruction tables

- 5.2.6 Optimizations by variable spreading

- 5.2.7 Optimizations when using lengthening instructions

- 6: NEON Code Examples with Intrinsics

- 7: NEON Code Examples with Mixed Operations

- 8: NEON Code Examples with Optimization

- A: NEON Microarchitecture

- B: Operating System Support

- C: NEON and VFP Instruction Summary

- C.1 List of all NEON and VFP instructions

- C.2 List of doubling instructions

- C.3 List of halving instructions

- C.4 List of widening or long instructions

- C.5 List of narrowing instructions

- C.6 List of rounding instructions

- C.7 List of saturating instructions

- C.8 NEON general data processing instructions

- C.9 NEON shift instructions

- C.10 NEON logical and compare operations

- C.11 NEON arithmetic instructions

- C.11.1 VABA{L}

- C.11.2 VABD{L}

- C.11.3 V{Q}ABS

- C.11.4 V{Q}ADD, VADDL, VADDW

- C.11.5 V{R}ADDHN

- C.11.6 VCLS

- C.11.7 VCLZ

- C.11.8 VCNT

- C.11.9 V{R}HADD

- C.11.10 VHSUB

- C.11.11 VMAX and VMIN

- C.11.12 V{Q}NEG

- C.11.13 VPADD{L}, VPADAL

- C.11.14 VPMAX and VPMIN

- C.11.15 VRECPE

- C.11.16 VRECPS

- C.11.17 VRSQRTE

- C.11.18 VRSQRTS

- C.11.19 V{Q}SUB, VSUBL and VSUBW

- C.11.20 V{R}SUBHN

- C.12 NEON multiply instructions

- C.13 NEON load and store instructions

- C.13.1 Interleaving

- C.13.2 Alignment restrictions in load and store, element and structure instructions

- C.13.3 VLDn and VSTn (single n-element structure to one lane)

- C.13.4 VLDn (single n-element structure to all lanes)

- C.13.5 VLDn and VSTn (multiple n-element structures)

- C.13.6 VLDR and VSTR

- C.13.7 VLDM, VSTM, VPOP, and VPUSH

- C.13.8 VMOV (between two ARM registers and a NEON register)

- C.13.9 VMOV (between an ARM register and a NEON scalar)

- C.13.10 VMRS and VMSR (between an ARM register and a NEON or VFP system register)

- C.14 VFP instructions

- C.14.1 VABS

- C.14.2 VADD

- C.14.3 VCMP (Floating-point compare)

- C.14.4 VCVT (between single-precision and double-precision)

- C.14.5 VCVT (between floating-point and integer)

- C.14.6 VCVT (between floating-point and fixed-point)

- C.14.7 VCVTB, VCVTT (half-precision extension)

- C.14.8 VDIV

- C.14.9 VFMA, VFMS, VFNMA, VFNMS (Fused floating-point multiply accumulate and fused floating-point multiply subtract with optional negation)

- C.14.10 VMOV

- C.14.11 VMOV

- C.14.12 VMUL, VMLA, VMLS, VNMUL, VNMLA, and VNMLS

- C.14.13 VNEG

- C.14.14 VSQRT

- C.14.15 VSUB

- C.15 NEON and VFP pseudo-instructions

- D: NEON Intrinsics Reference

- D.1 NEON intrinsics description

- D.2 Intrinsics type conversion

- D.3 Arithmetic

- D.4 Multiply

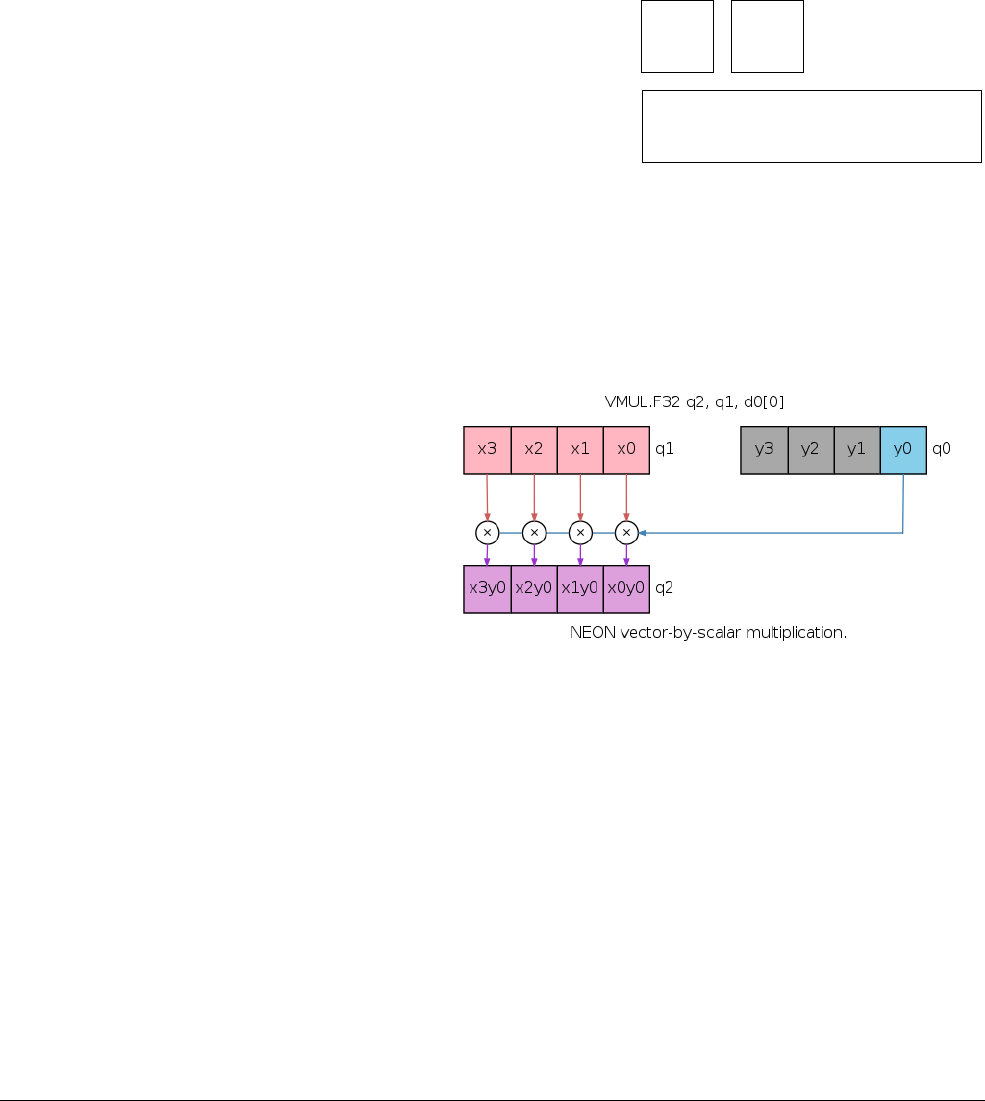

- D.4.1 VMUL

- D.4.2 VMLA

- D.4.3 VMLAL

- D.4.4 VMLS

- D.4.5 VMLSL

- D.4.6 VQDMULH

- D.4.7 VQRDMULH

- D.4.8 VQDMLAL

- D.4.9 VQDMLSL

- D.4.10 VMULL

- D.4.11 VQDMULL

- D.4.12 VMLA_LANE

- D.4.13 VMLAL_LANE

- D.4.14 VQDMLAL_LANE

- D.4.15 VMLS_LANE

- D.4.16 VMLSL_LANE

- D.4.17 VQDMLSL_LANE

- D.4.18 VMUL_N

- D.4.19 VMULL_N

- D.4.20 VMULL_LANE

- D.4.21 VQDMULL_N

- D.4.22 VQDMULL_LANE

- D.4.23 VQDMULH_N

- D.4.24 VQDMULH_LANE

- D.4.25 VQRDMULH_N

- D.4.26 VQRDMULH_LANE

- D.4.27 VMLA_LANE

- D.4.28 VMLAL_N

- D.4.29 VQDMLAL_N

- D.4.30 VMLSL_N

- D.4.31 VQDMLSL_N

- D.5 Data processing

- D.5.1 VPADD

- D.5.2 VPADDL

- D.5.3 VPADAL

- D.5.4 VPMAX

- D.5.5 VPMIN

- D.5.6 VABD

- D.5.7 VABDL

- D.5.8 VABA

- D.5.9 VABAL

- D.5.10 VMAX

- D.5.11 VMIN

- D.5.12 VABS

- D.5.13 VQABS

- D.5.14 VNEG

- D.5.15 VQNEG

- D.5.16 VCLS

- D.5.17 VCLZ

- D.5.18 VCNT

- D.5.19 VRECPE

- D.5.20 VRECPS

- D.5.21 VRSQRTE

- D.5.22 VRSQRTS

- D.5.23 VMOVN

- D.5.24 VMOVL

- D.5.25 VQMOVN

- D.5.26 VQMOVUN

- D.6 Logical and compare

- D.7 Shift

- D.8 Floating-point

- D.9 Load and store

- D.10 Permutation

- D.11 Miscellaneous

Copyright © 2013 ARM. All rights reserved.

ARM DEN0018A (ID071613)

NEON™

Version: 1.0

Programmer’s Guide

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. ii

ID071613 Non-Confidential

NEON

Programmer’s Guide

Copyright © 2013 ARM. All rights reserved.

Release Information

The following changes have been made to this book.

Proprietary Notice

This document is protected by copyright and other related rights and the practice or implementation of the information

contained in this document may be protected by one or more patents or pending patent applications. No part of this

document may be reproduced in any form by any means without the express prior written permission of ARM. No

license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document

unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit

others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED “AS IS”. ARM PROVIDES NO REPRESENTATIONS AND NO

WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED

WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS

FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes

no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of,

third party patents, copyrights, trade secrets, or other rights.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES,

INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR

CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY,

ARISING OUT ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY

OF SUCH DAMAGES.

This document may include technical inaccuracies or typographical errors.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or

disclosure of this document complies fully with any relevant export laws and regulations to assure that this document

or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word “partner”

is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to

this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement

covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting

provisions of these terms.

Words and logos marked with ™ or ® are registered trademarks or trademarks of ARM Limited or its affiliates in the EU

and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of

their respective owners. Please follow ARM’s trademark usage guidelines at,

http://www.arm.com/about/trademark-usage-guidelines.php.

Copyright © 2013, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20318 v0.1

Web Address

http://www.arm.com

Change history

Date Issue Confidentiality Change

28 June 2013 A Non-Confidential First release

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. iii

ID071613 Non-Confidential

Contents

NEON Programmer’s Guide

Preface

References ................................................................................................................ vii

Typographical conventions ....................................................................................... viii

Feedback on this book ................................................................................................ ix

Glossary ....................................................................................................................... x

Chapter 1 Introduction

1.1 Data processing technologies .................................................................................. 1-2

1.2 Comparison between ARM NEON technology and other implementations ............. 1-4

1.3 Architecture support for NEON technology .............................................................. 1-7

1.4 Fundamentals of NEON technology ...................................................................... 1-10

Chapter 2 Compiling NEON Instructions

2.1 Vectorization ............................................................................................................ 2-2

2.2 Generating NEON code using the vectorizing compiler .......................................... 2-9

2.3 Vectorizing examples ............................................................................................. 2-11

2.4 NEON assembler and ABI restrictions ................................................................... 2-17

2.5 NEON libraries ....................................................................................................... 2-19

2.6 Intrinsics ................................................................................................................. 2-20

2.7 Detecting presence of a NEON unit ....................................................................... 2-21

2.8 Writing code to imply SIMD ................................................................................... 2-22

2.9 GCC command line options ................................................................................... 2-24

Chapter 3 NEON Instruction Set Architecture

3.1 Introduction to the NEON instruction syntax ............................................................ 3-2

3.2 Instruction syntax ..................................................................................................... 3-4

3.3 Specifying data types ............................................................................................... 3-8

3.4 Packing and unpacking data .................................................................................... 3-9

3.5 Alignment ............................................................................................................... 3-10

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. iv

ID071613 Non-Confidential

3.6 Saturation arithmetic .............................................................................................. 3-11

3.7 Floating-point operations ....................................................................................... 3-12

3.8 Flush-to-zero mode ................................................................................................ 3-13

3.9 Shift operations ...................................................................................................... 3-14

3.10 Polynomials ........................................................................................................... 3-17

3.11 Instructions to permute vectors .............................................................................. 3-19

Chapter 4 NEON Intrinsics

4.1 Introduction .............................................................................................................. 4-2

4.2 Vector data types for NEON intrinsics ..................................................................... 4-3

4.3 Prototype of NEON Intrinsics ................................................................................... 4-5

4.4 Using NEON intrinsics ............................................................................................. 4-6

4.5 Variables and constants in NEON code .................................................................. 4-8

4.6 Accessing vector types from C ................................................................................ 4-9

4.7 Loading data from memory into vectors ................................................................ 4-10

4.8 Constructing a vector from a literal bit pattern ....................................................... 4-11

4.9 Constructing multiple vectors from interleaved memory ........................................ 4-12

4.10 Loading a single lane of a vector from memory ..................................................... 4-13

4.11 Programming using NEON intrinsics ..................................................................... 4-14

4.12 Instructions without an equivalent intrinsic ............................................................ 4-16

Chapter 5 Optimizing NEON Code

5.1 Optimizing NEON assembler code .......................................................................... 5-2

5.2 Scheduling ............................................................................................................... 5-4

Chapter 6 NEON Code Examples with Intrinsics

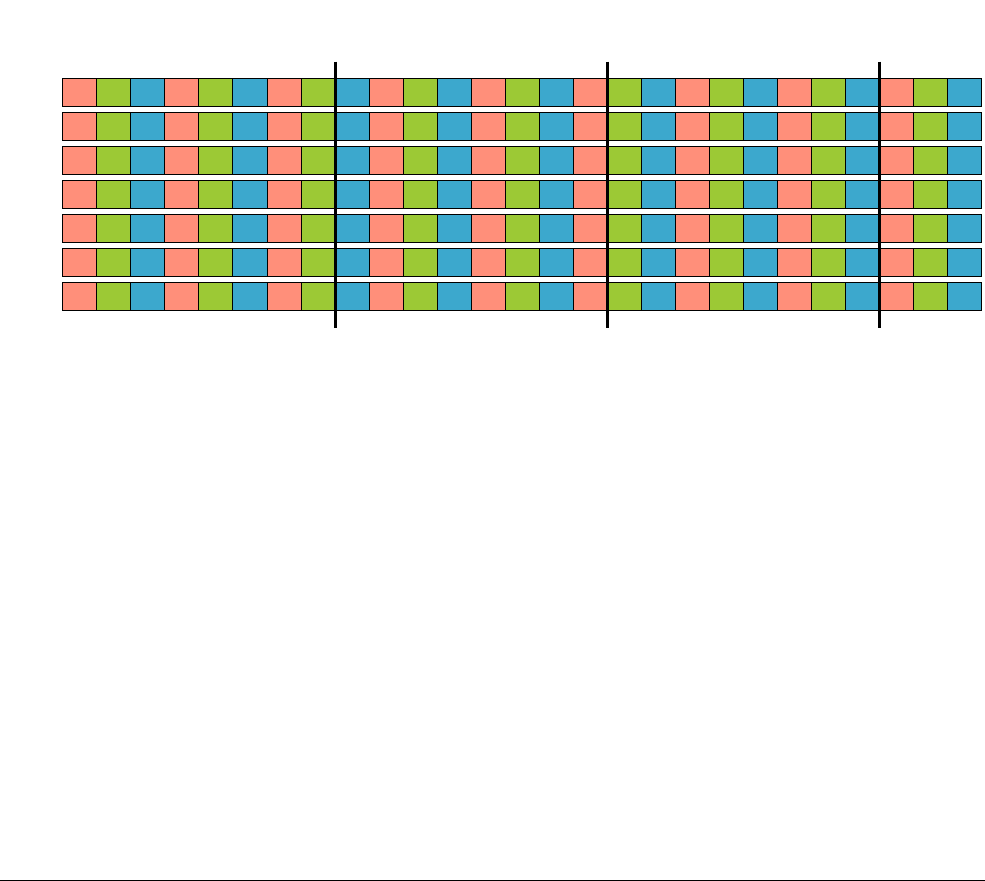

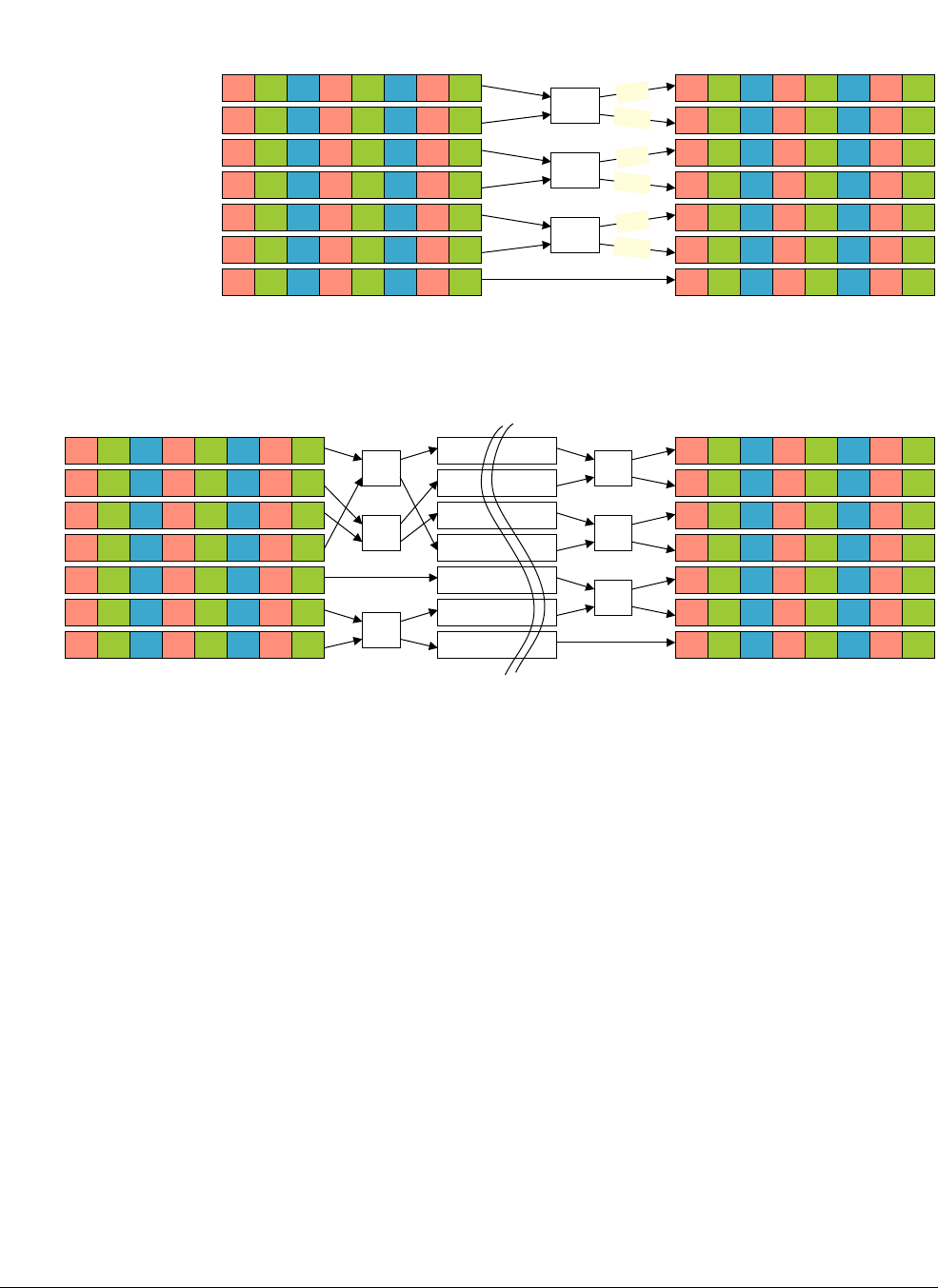

6.1 Swapping color channels ......................................................................................... 6-2

6.2 Handling non-multiple array lengths ........................................................................ 6-8

Chapter 7 NEON Code Examples with Mixed Operations

7.1 Matrix multiplication ................................................................................................. 7-2

7.2 Cross product .......................................................................................................... 7-6

Chapter 8 NEON Code Examples with Optimization

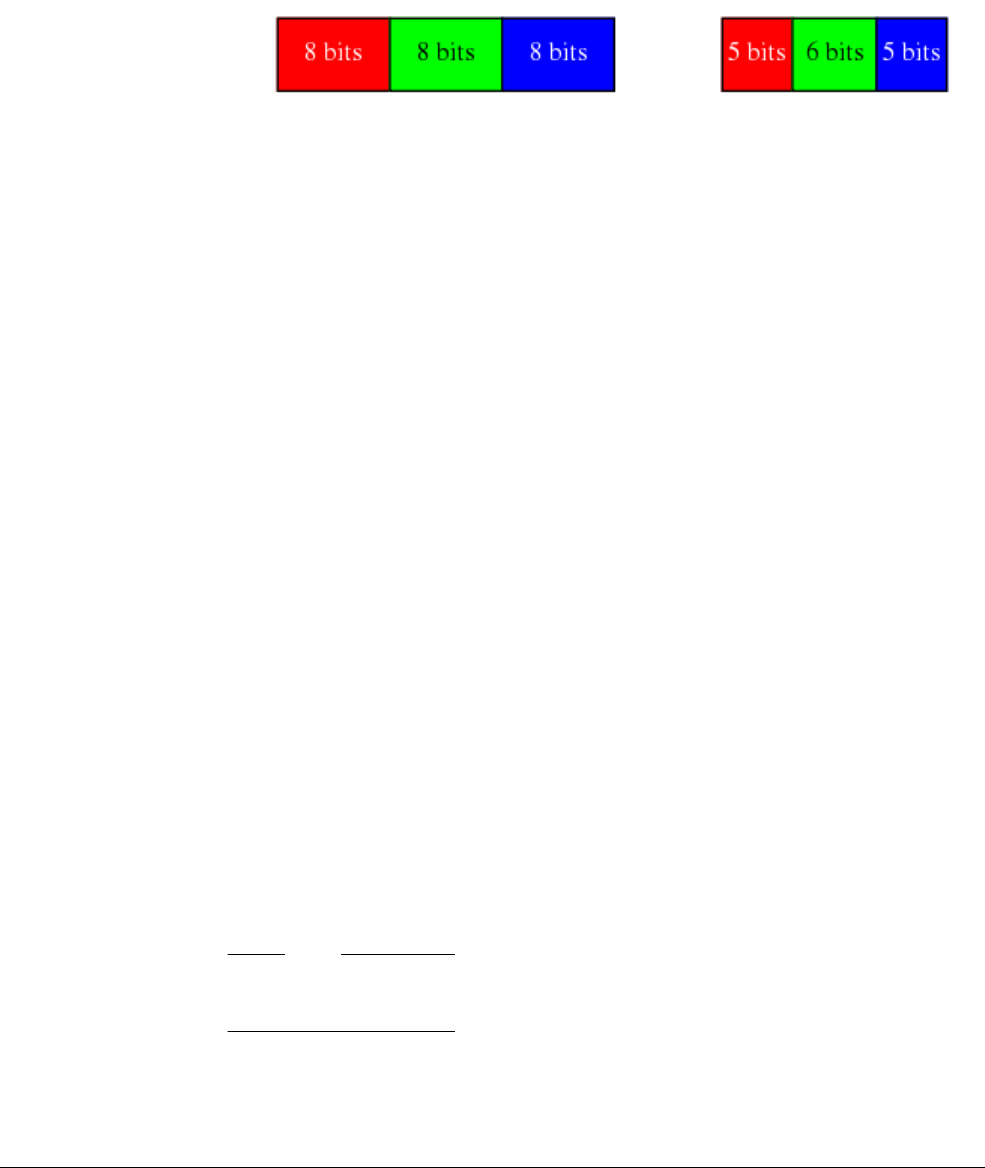

8.1 Converting color depth ............................................................................................. 8-2

8.2 Median filter ............................................................................................................. 8-5

8.3 FIR filter ................................................................................................................. 8-21

Appendix A NEON Microarchitecture

A.1 The Cortex-A5 processor ......................................................................................... A-2

A.2 The Cortex-A7 processor ......................................................................................... A-4

A.3 The Cortex-A8 processor ......................................................................................... A-5

A.4 The Cortex-A9 processor ......................................................................................... A-9

A.5 The Cortex-A15 processor ..................................................................................... A-11

Appendix B Operating System Support

B.1 FPSCR, the floating-point status and control register .............................................. B-2

B.2 FPEXC, the floating-point exception register ........................................................... B-4

B.3 FPSID, the floating-point system ID register ............................................................ B-5

B.4 MVFR0/1 Media and VFP Feature Registers .......................................................... B-6

Appendix C NEON and VFP Instruction Summary

C.1 List of all NEON and VFP instructions ..................................................................... C-2

C.2 List of doubling instructions ..................................................................................... C-7

C.3 List of halving instructions ........................................................................................ C-8

C.4 List of widening or long instructions ......................................................................... C-9

C.5 List of narrowing instructions ................................................................................. C-10

C.6 List of rounding instructions ................................................................................... C-11

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. v

ID071613 Non-Confidential

C.7 List of saturating instructions ................................................................................. C-12

C.8 NEON general data processing instructions .......................................................... C-14

C.9 NEON shift instructions .......................................................................................... C-25

C.10 NEON logical and compare operations ................................................................. C-31

C.11 NEON arithmetic instructions ................................................................................. C-41

C.12 NEON multiply instructions .................................................................................... C-55

C.13 NEON load and store instructions ......................................................................... C-60

C.14 VFP instructions ..................................................................................................... C-67

C.15 NEON and VFP pseudo-instructions ..................................................................... C-73

Appendix D NEON Intrinsics Reference

D.1 NEON intrinsics description ..................................................................................... D-2

D.2 Intrinsics type conversion ........................................................................................ D-3

D.3 Arithmetic ................................................................................................................. D-8

D.4 Multiply ................................................................................................................... D-24

D.5 Data processing ..................................................................................................... D-50

D.6 Logical and compare ............................................................................................. D-74

D.7 Shift ........................................................................................................................ D-93

D.8 Floating-point ....................................................................................................... D-114

D.9 Load and store ..................................................................................................... D-120

D.10 Permutation ......................................................................................................... D-151

D.11 Miscellaneous ...................................................................................................... D-166

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. vi

ID071613 Non-Confidential

Preface

This book provides a guide for programmers to effectively use NEON technology, the ARM

Advanced SIMD architecture extension. The book provides information that will be useful to

both assembly language and C programmers.

This is not an introductory level book:

• It assumes knowledge of the C and ARM assembler programming languages, but not any

ARM-specific background.

• Some chapters suggest further reading (referring either to books or web sites) that can give

a deeper level of background to the topic in hand, but this book focuses on the

ARM-specific detail.

• No particular tool chain is assumed, and there are some examples for both GNU and ARM

tools.

• This book complements other ARM documentation for these processors, including the

processor Technical Reference Manuals (TRMs), documentation for specific devices or

boards and the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition

(DDI0406).

•The Cortex™-A Series Programmer’s Guide covered basic principles of NEON

technology, but this book provides more detailed information on using NEON technology.

Preface

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. vii

ID071613 Non-Confidential

References

Hohl, William. “ARM Assembly Language: Fundamentals and Techniques” CRC Press, 2009.

ISBN: 9781439806104.

Sloss, Andrew N.; Symes, Dominic.; Wright, Chris. “ARM System Developer's Guide:

Designing and Optimizing System Software”, Morgan Kaufmann, 2004, ISBN:

9781558608740.

ANSI/IEEE Std 754-1985, “IEEE Standard for Binary Floating-Point Arithmetic”.

ANSI/IEEE Std 754-2008, “IEEE Standard for Binary Floating-Point Arithmetic”.

ANSI/IEEE Std 1003.1-1990, “Standard for Information Technology - Portable Operating

System Interface (POSIX) Base Specifications, Issue 7”.

ARM® Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406), the

ARM ARM.

Note

In the event of a contradiction between this book and the ARM ARM, the ARM ARM is

definitive and must take precedence.

ARM® Compiler Toolchain Assembler Reference (ARM DUI 0489).

Cortex™-A Series Programmer’s Guide (ARM DEN0013B).

Introducing NEON (ARM DHT 0002).

NEON™ Support in Compilation Tools (ARM DHT 0004).

ARM® Compiler Toolchain: Using the Assembler (ARM DUI 0473).

Cortex™-A5 Technical Reference Manual (ARM DDI 0433).

Cortex™-A5 NEON Media Processing Engine Technical Reference Manual (ARM DDI 0450).

Cortex™-A8 Technical Reference Manual (ARM DDI 0344).

Cortex™-A9 NEON Media Processing Engine Technical Reference Manual (ARM DDI 0409).

Cortex™-A9 Technical Reference Manual (ARM DDI 0308).

ARM® NEON™ support in the ARM compiler: White Paper Sept. 2008.

ARM® C Language Extensions (IHI0053).

Preface

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. viii

ID071613 Non-Confidential

Typographical conventions

This book uses the following typographical conventions:

italic Highlights important notes, introduces special terminology, denotes

internal cross-references, and citations.

bold Used for terms in descriptive lists, where appropriate.

monospace

Denotes text that you can enter at the keyboard, such as commands, file

and program names, instruction names, parameters and source code.

monospace

italic

Denotes arguments to monospace text where the argument is to be

replaced by a specific value.

< and > Enclose replaceable terms for assembler syntax where they appear in code

or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode_2>

Preface

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. ix

ID071613 Non-Confidential

Feedback on this book

If you have any comments on this book, do not understand our explanations, think something is

missing, incorrect, or could be better explained, send an e-mail to

errata@arm.com

. Give:

• the title, NEON Programmer’s Guide

• the number, ARM DEN0018A

• the page number(s) to which your comments apply

• a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

Preface

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. x

ID071613 Non-Confidential

Glossary

Abbreviations and terms used in this document are defined here.

AAPCS ARM Architecture Procedure Call Standard.

ABI Application Binary Interface.

AMBA® Advanced Microcontroller Bus Architecture.

AMP Asymmetric Multi-Processing.

ARM ARM The ARM Architecture Reference Manual.

ASIC Application Specific Integrated Circuit.

ASID Address Space ID.

ATPCS ARM Thumb® Procedure Call Standard.

CP15 Coprocessor 15 - System control coprocessor.

CPSR Current Program Status Register.

EABI Embedded ABI.

EOF End Of File.

FPEXC Floating-point Exception Register

FPSCR Floating-Point Status and Control Register.

FPSID Floating-Point System ID Register

FPU Floating-point Unit.

GCC GNU Compiler Collection.

GIC Generic Interrupt Controller.

IRQ Interrupt Request (normally external interrupts).

ISA Instruction Set Architecture.

MVFR0/1 Media and VFP Feature Registers.

NaN Not a Number.

NEON™ The ARM Advanced SIMD Extensions.

RVCT RealView® Compilation Tools (the “ARM Compiler”).

SIMD Single Instruction, Multiple Data.

SoC System on Chip.

SPSR Saved Program Status Register.

VFP The ARM floating-point instruction set. Before ARMv7, the VFP

extension was called the Vector Floating-Point architecture, and was used

for vector operations.

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-1

ID071613 Non-Confidential

Chapter 1

Introduction

This book introduces NEON technology as it is used on ARM Cortex™-A series processors that

implement the ARMv7–A or ARMv7–R architectures profiles. It contains the following topics:

•Data processing technologies on page 1-2.

•Comparison between ARM NEON technology and other implementations on page 1-4.

•Architecture support for NEON technology on page 1-7.

•Fundamentals of NEON technology on page 1-10.

Note

• If you are completely new to ARM technology, read the Cortex-A Series

Programmer’s Guide for information on the ARM architectures profiles and general

programming guidelines.

• NEON technology is the implementation of the ARM Advanced Single Instruction

Multiple Data (SIMD) extension.

• The NEON unit is the component of the processor that executes SIMD instructions. It is

also called the NEON Media Processing Engine (MPE).

• Some Cortex-A series processors that implement the ARMv7–A or ARMv7–R

architectures profiles do not contain a NEON unit.

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-2

ID071613 Non-Confidential

1.1 Data processing technologies

The common ways that microprocessor instructions process data are covered in the following

sections:

•Single Instruction Single Data.

•Single Instruction Multiple Data (vector mode).

•Single Instruction Multiple Data (packed data mode) on page 1-3.

1.1.1 Single Instruction Single Data

Each operation specified the single data source to process. Processing multiple data items

requires multiple instructions. The following code uses four instructions to add eight registers:

add r0, r5

add r1, r6

add r2, r7

add r3, r8

This method is slow and it can be difficult to see how different registers are related. To improve

performance and efficiency, media processing is often off-loaded to dedicated processors such

as a Graphics Processing Unit (GPU) or Media Processing Unit which can process more than

one data value with a single instruction.

On an ARM 32-bit processor, performing large numbers of individual 8-bit or 16-bit operations

does not use machine resources efficiently because processor, registers, and data path are all

designed for 32-bit calculations.

1.1.2 Single Instruction Multiple Data (vector mode)

An operation can specify that the same processing occurs for multiple data sources. If the

LEN

value is 4 in the control register, the single vector add instruction performs four adds:

VADD.F32 S24, S8, S16

// four operations occur

// S24 = S8 +S16

// S25 = S9 +S17

// S26 = S10 +S18

// S27 = S11 +S20

Although there is only one instruction, processing the four additions occurs sequentially in four

steps.

In ARM terminology this is called Vector Floating Point.

The Vector Floating Point (VFP) extension was introduced in the ARMv5 architecture and

executed short vector instructions to speed up floating point operations. The source and

destination registers could be either single registers for scalar operations or a sequence of two

to eight registers for vector operations.

Because SIMD operations perform vector calculation more efficiently than VFP operations,

vector mode operation was deprecated from the introduction of ARMv7, and replaced with

NEON technology which performs multiple operations on wide registers.

The floating-point and NEON use a common register bank for their operations.

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-3

ID071613 Non-Confidential

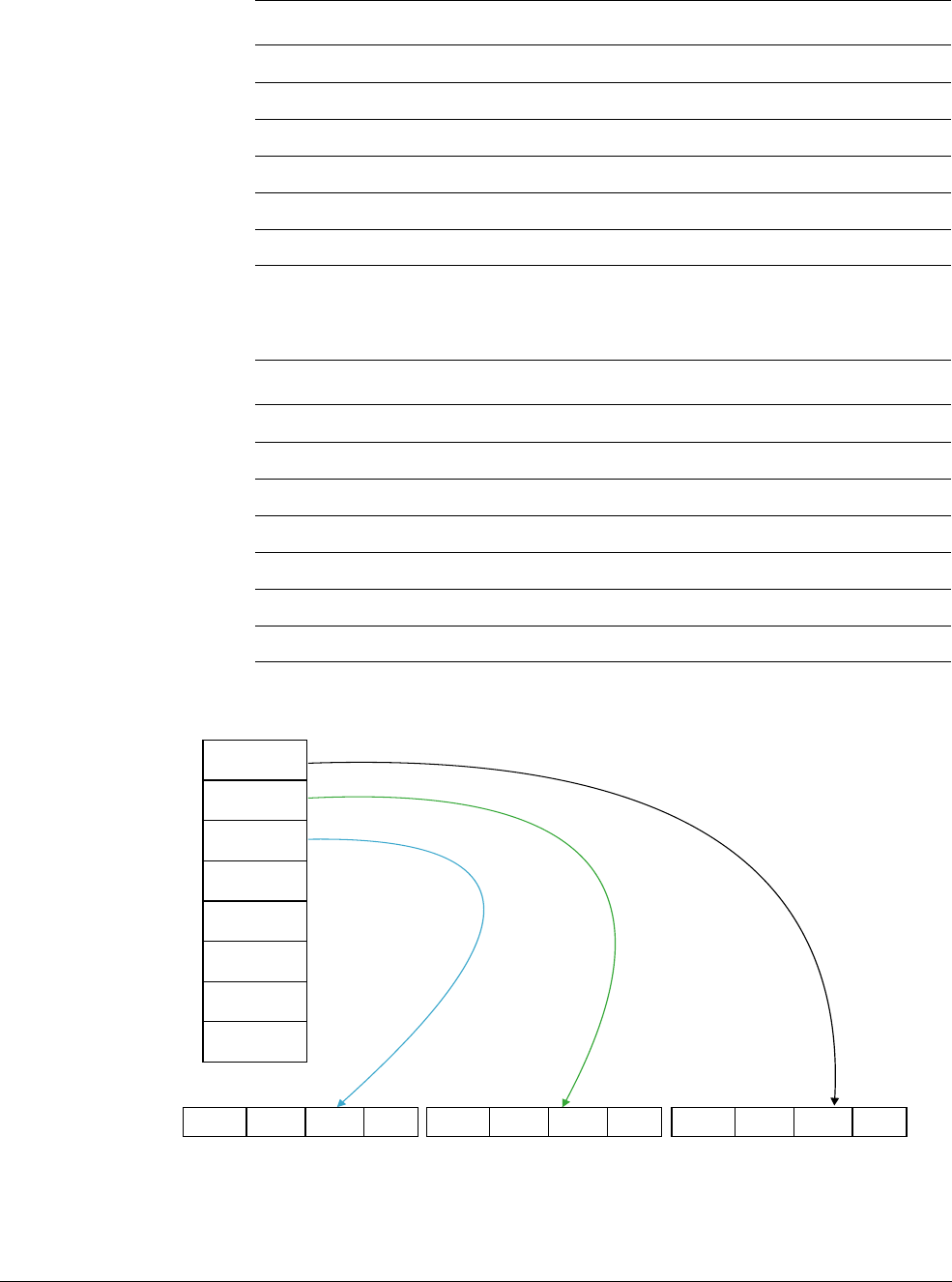

1.1.3 Single Instruction Multiple Data (packed data mode)

An operation can specify that the same processing occurs for multiple data fields stored in one

large register:

VADD.I16 Q10, Q8, Q9

// One operation adds two 64-bit registers,

// but each of the four 16-bit lanes in the register is added separately.

// There are no carries between the lanes

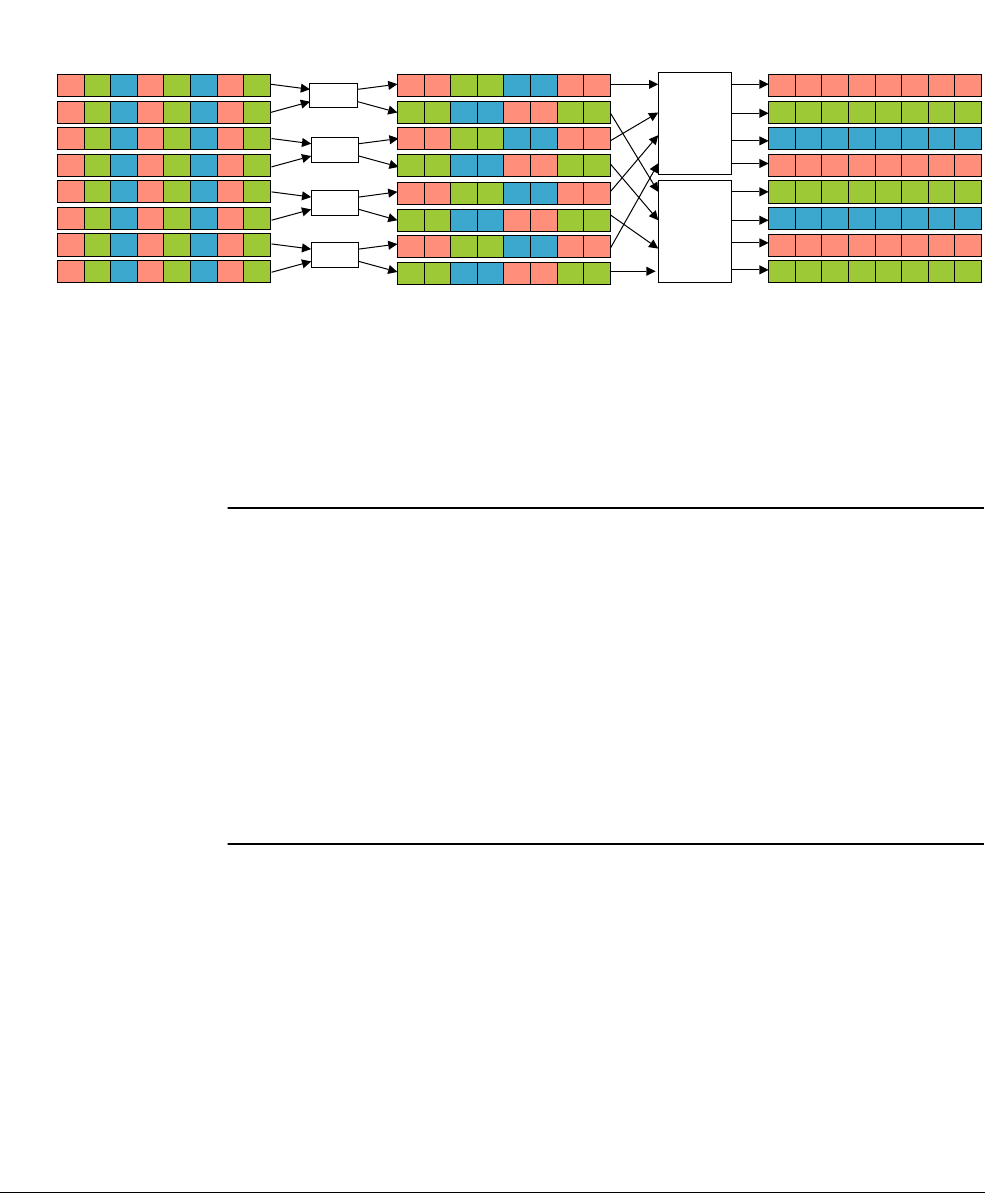

The single instruction operates on all data values in the large register at the same time as shown

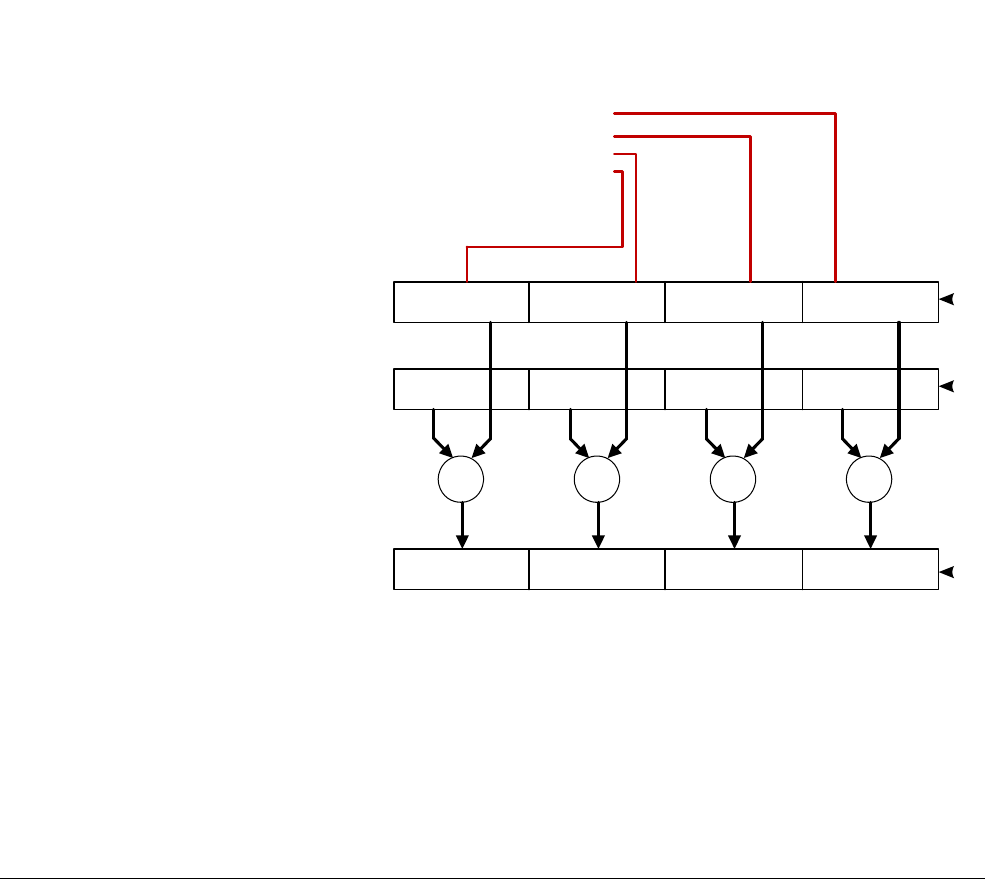

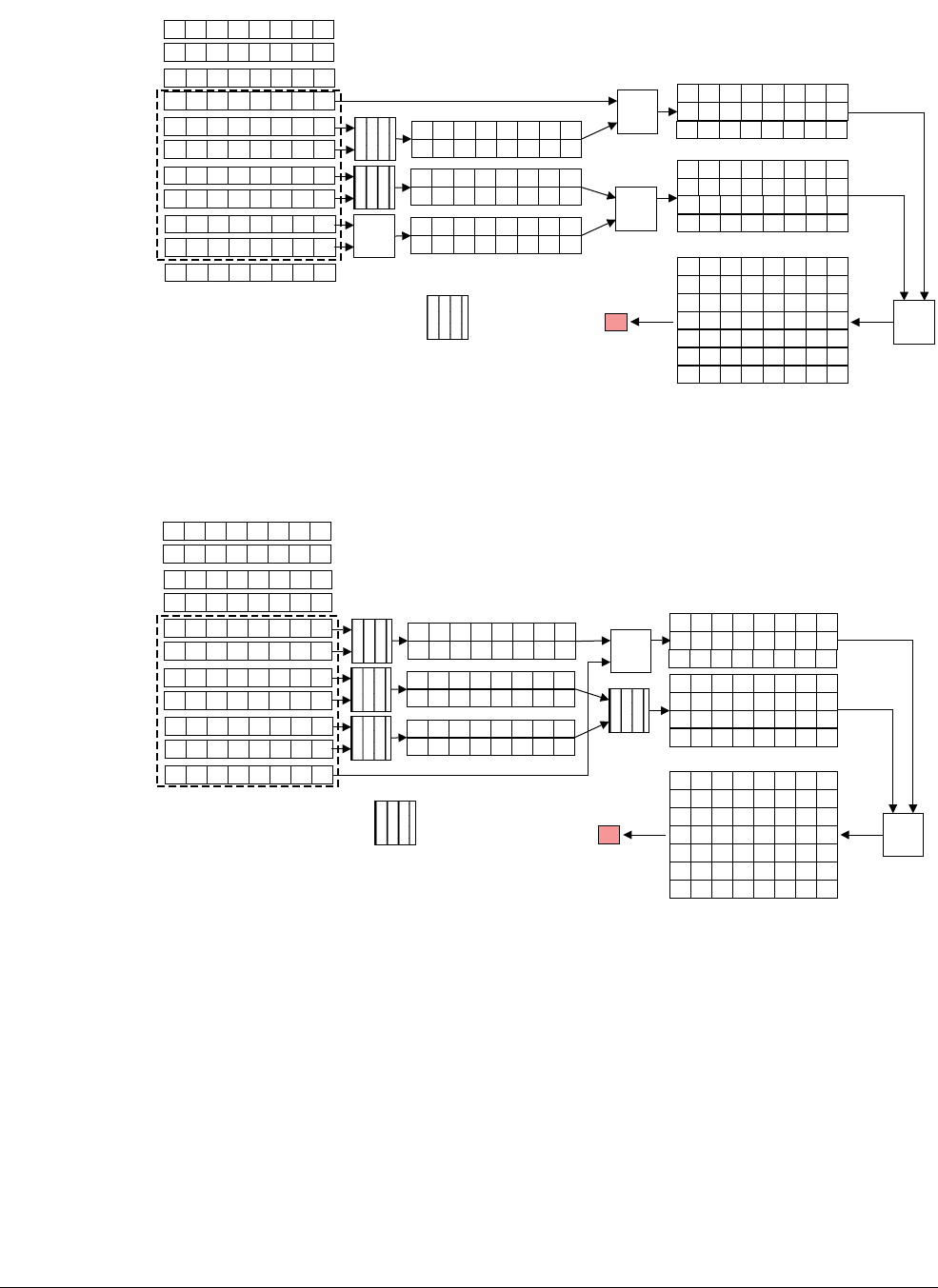

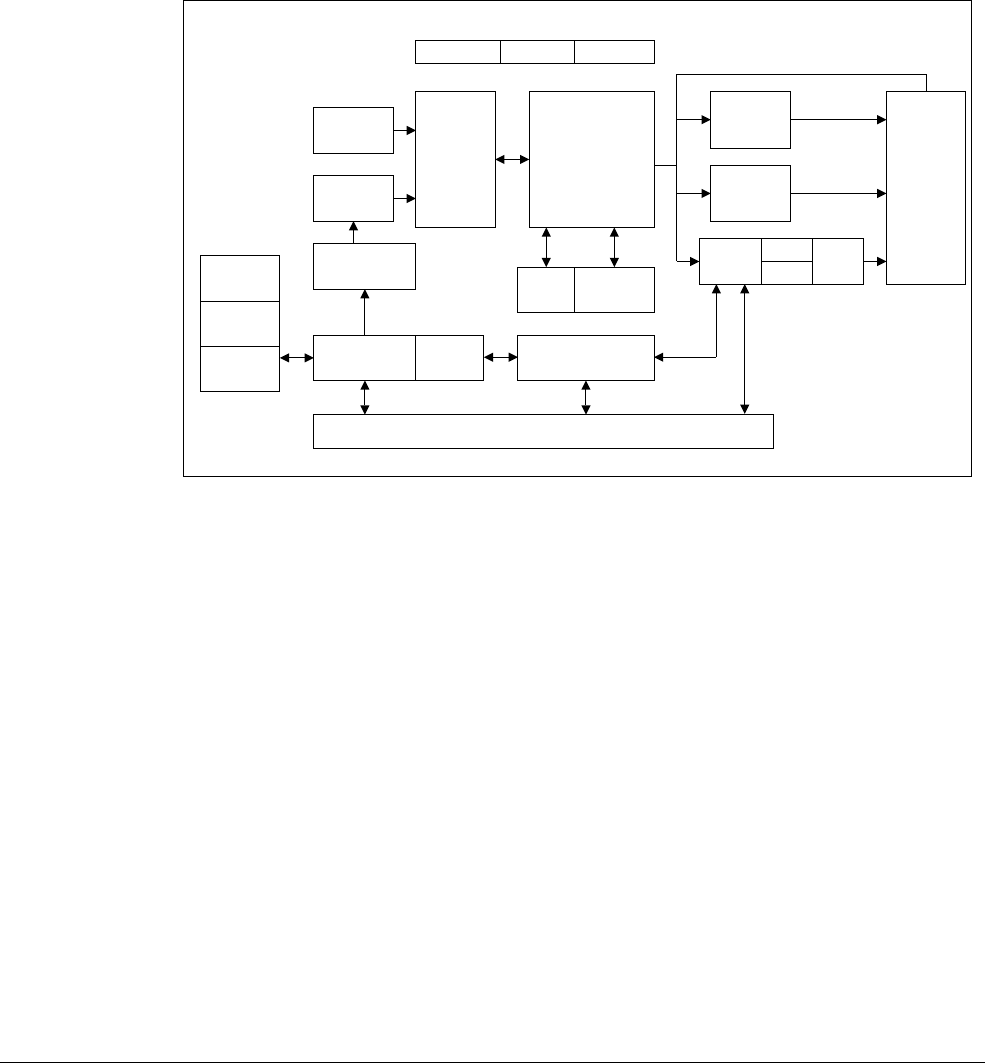

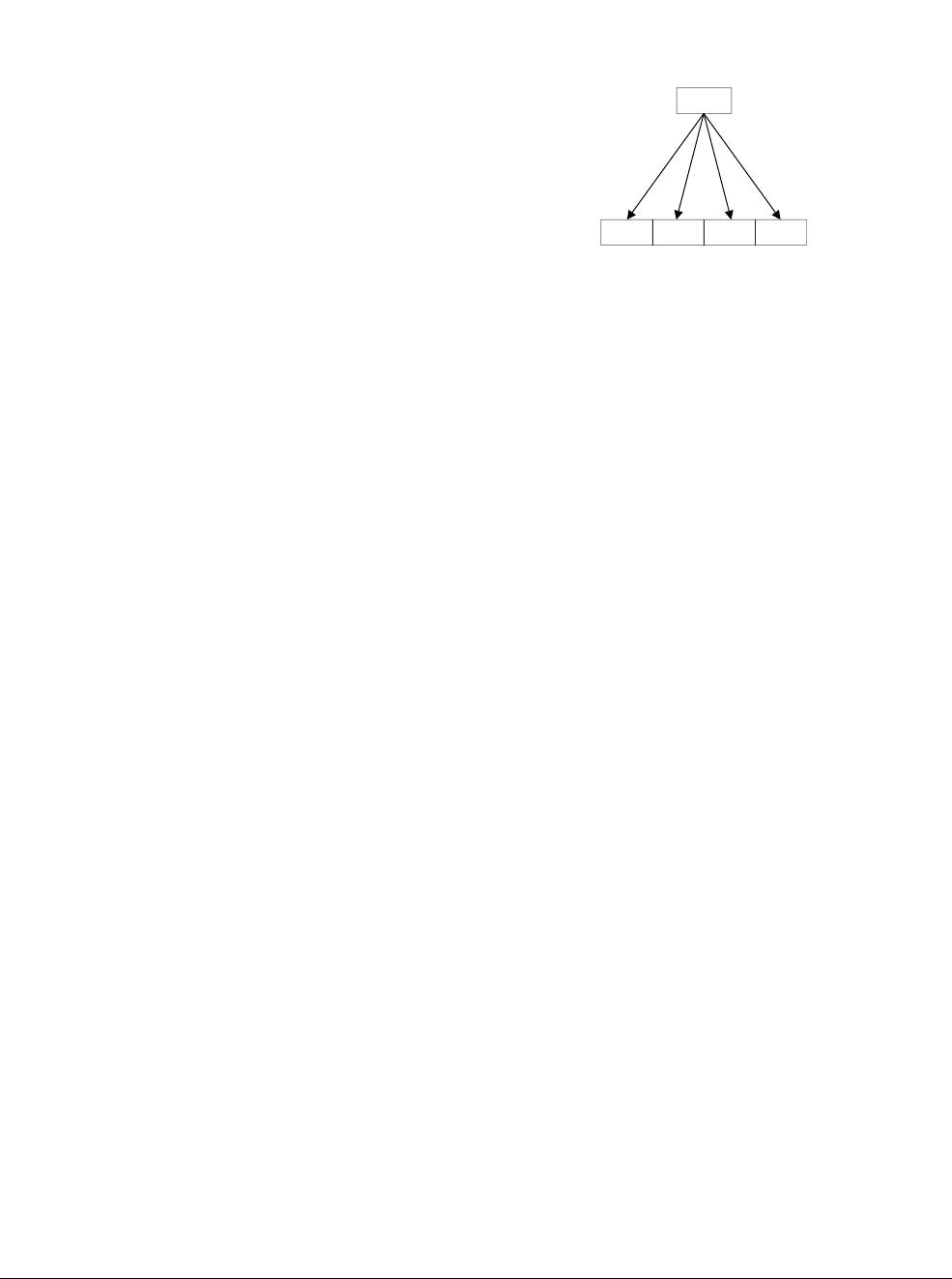

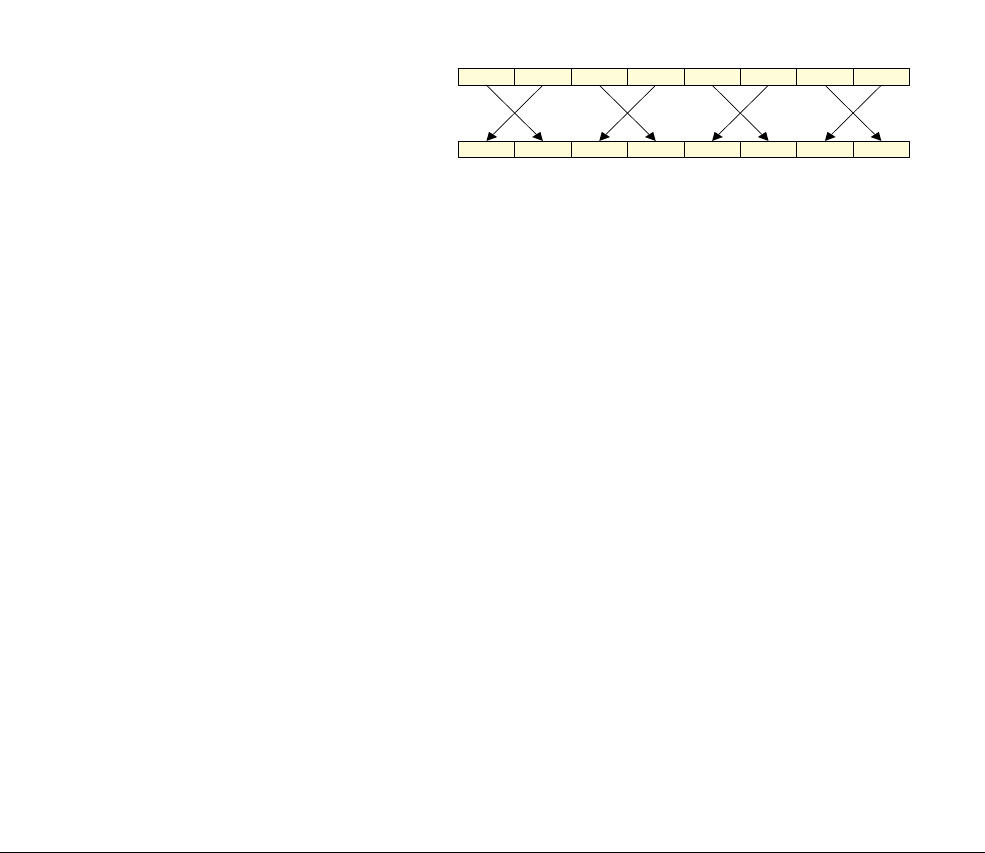

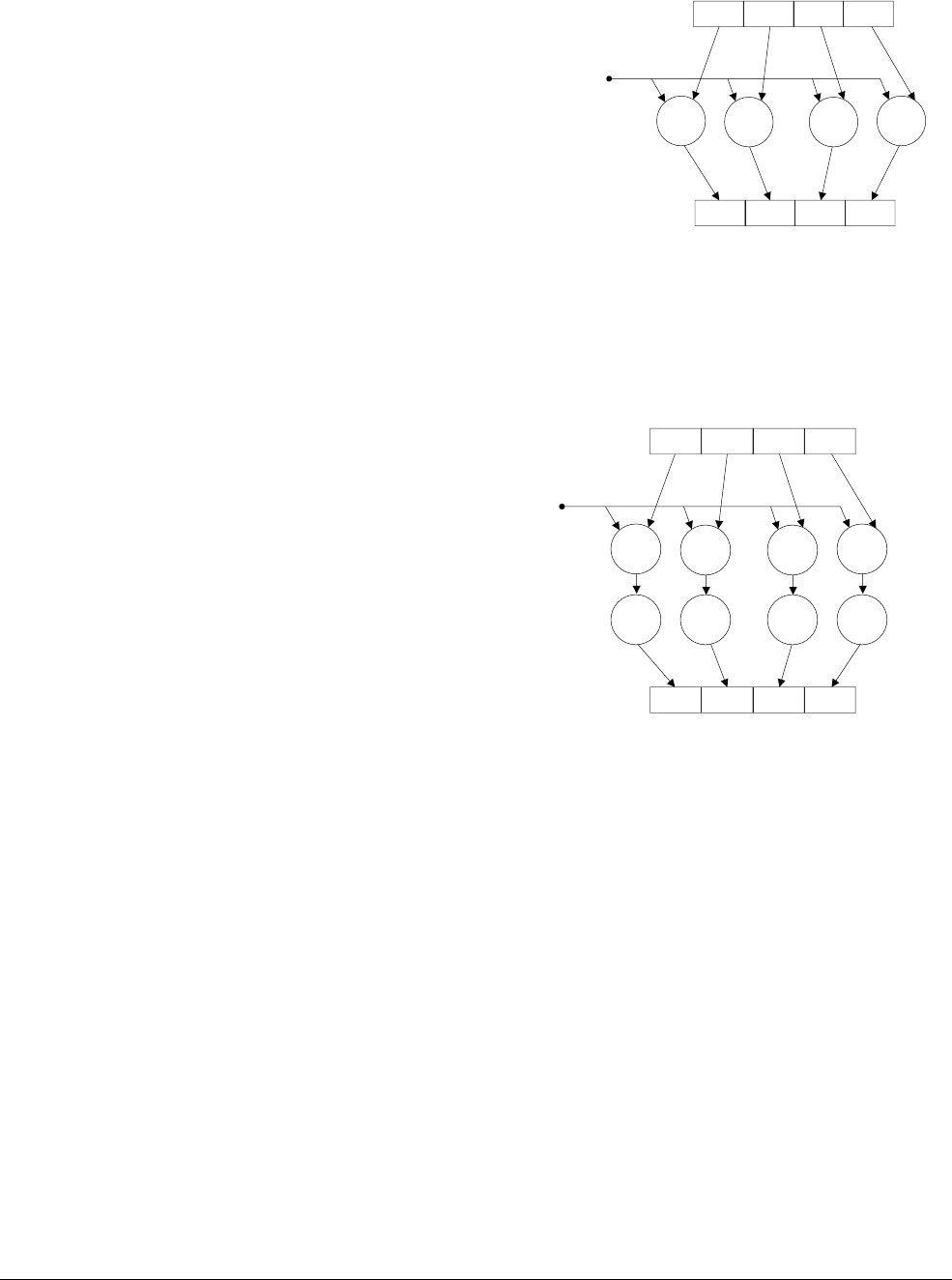

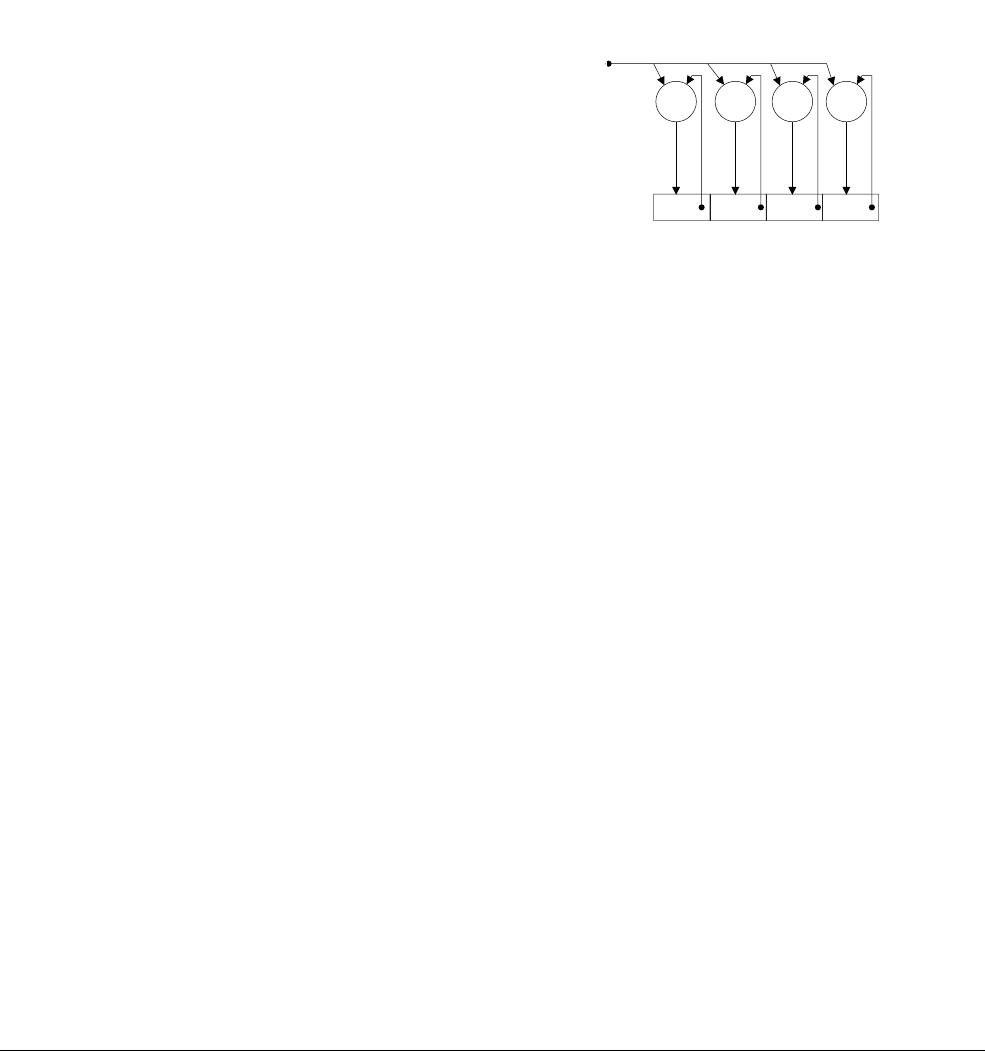

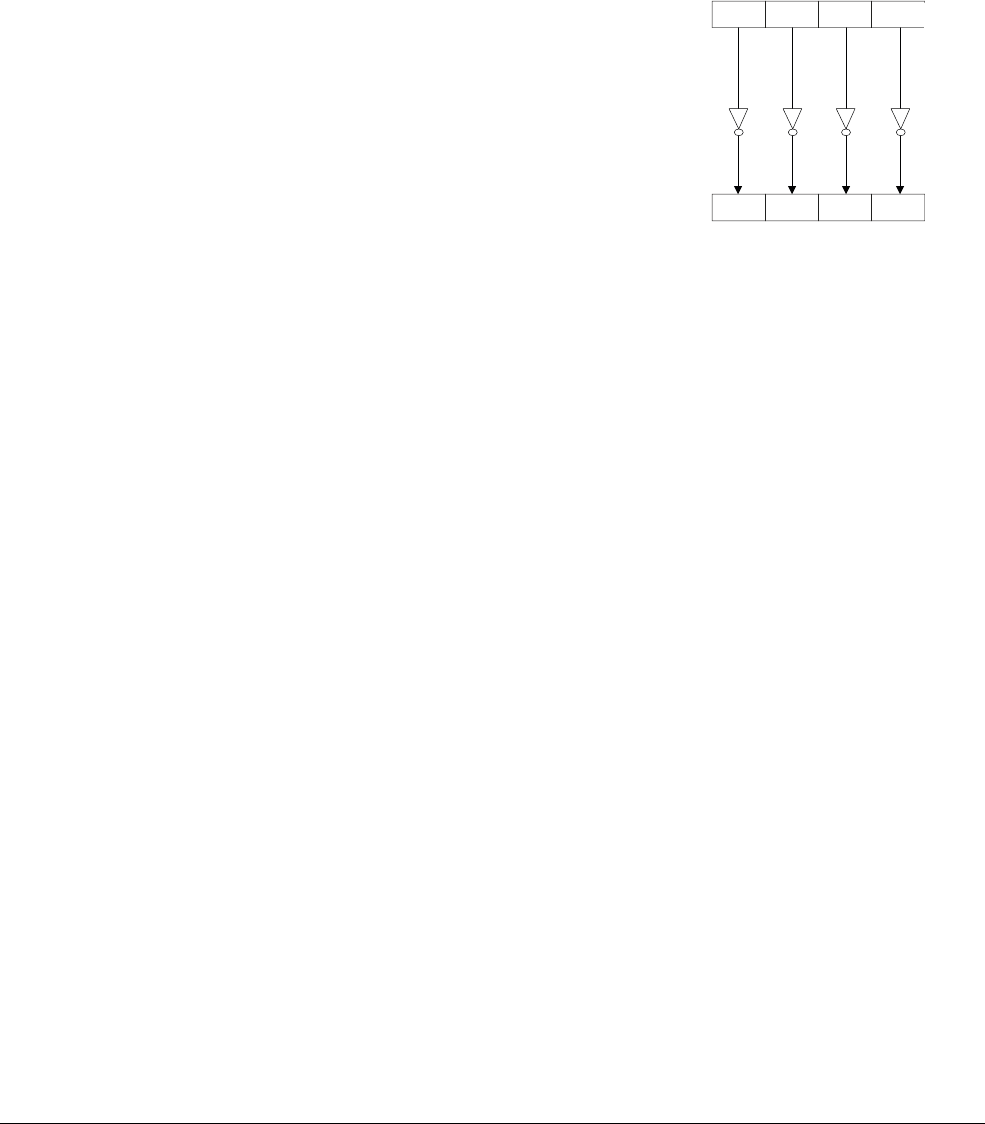

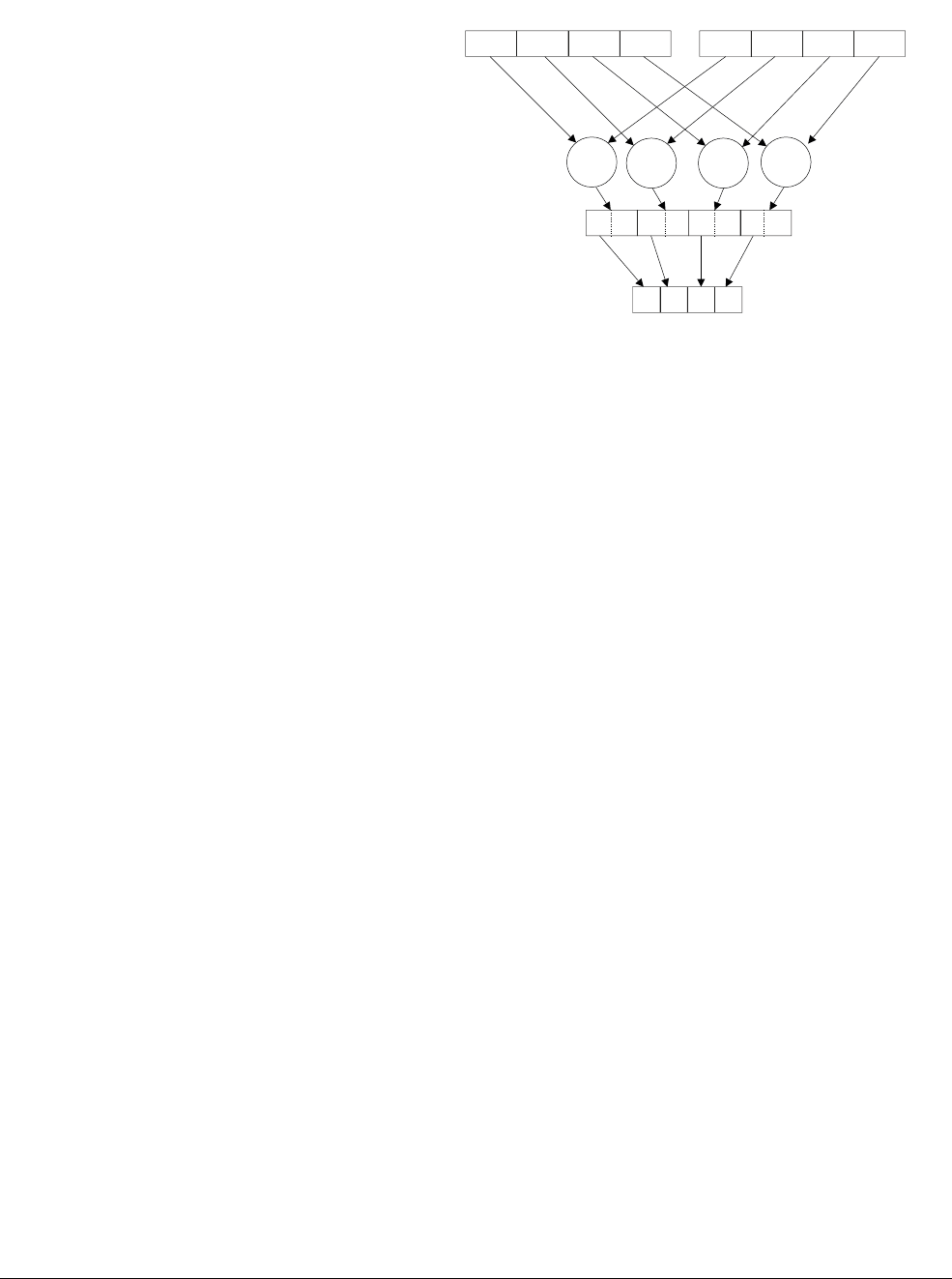

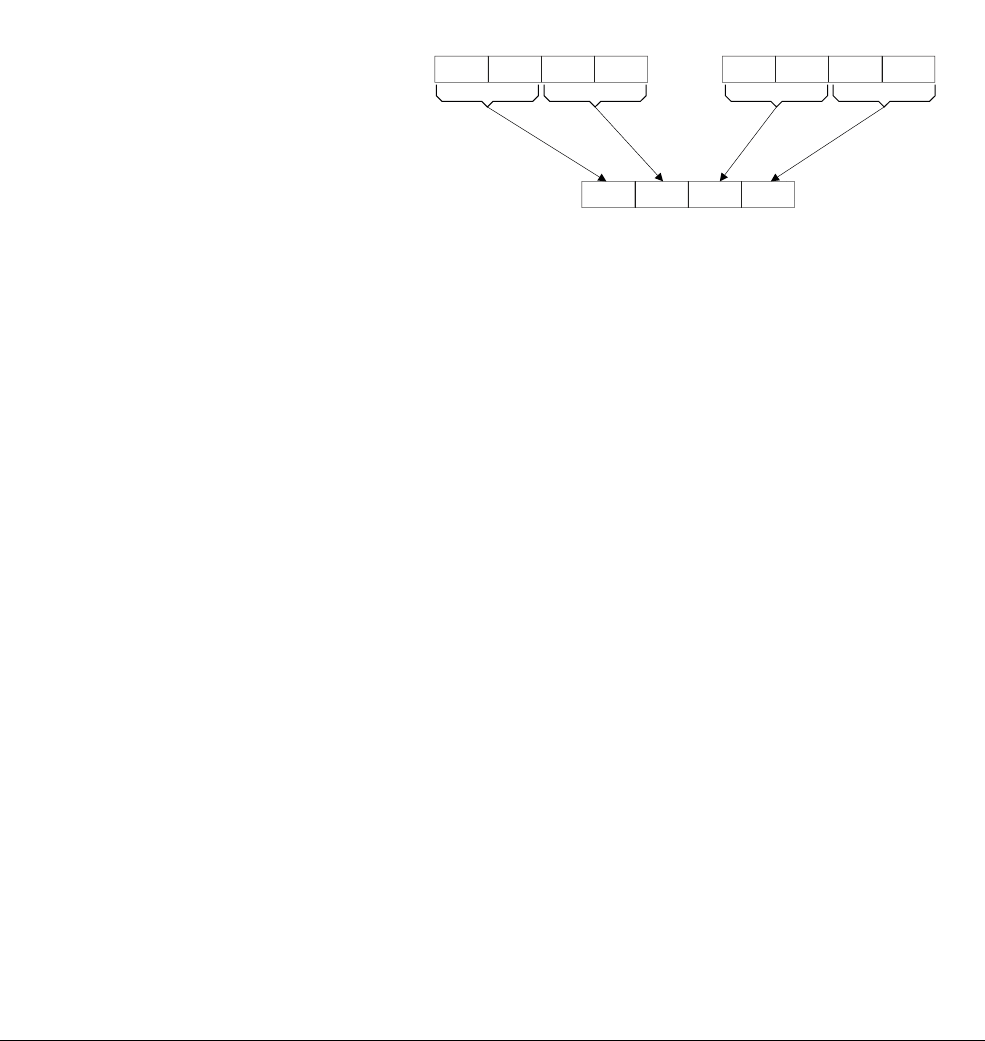

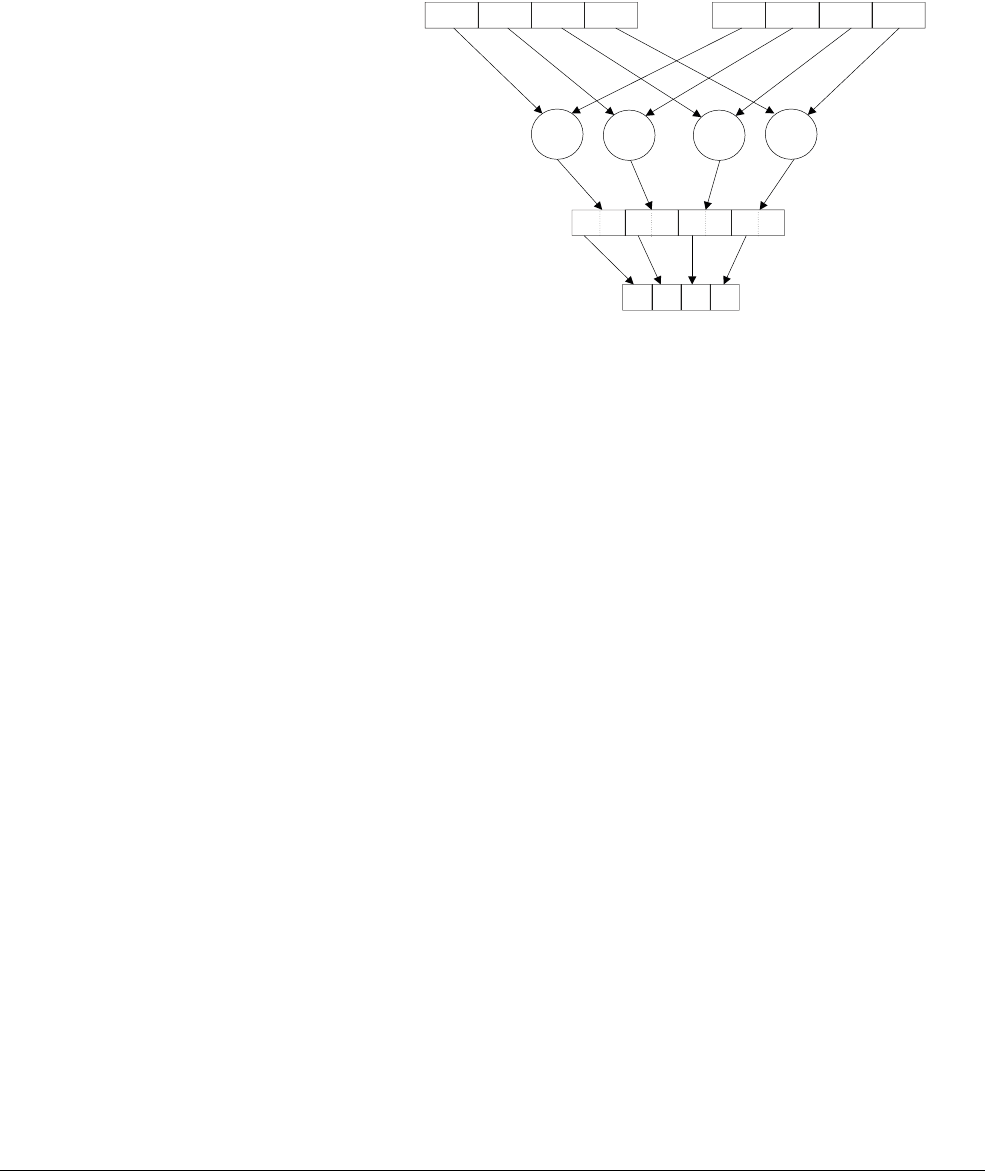

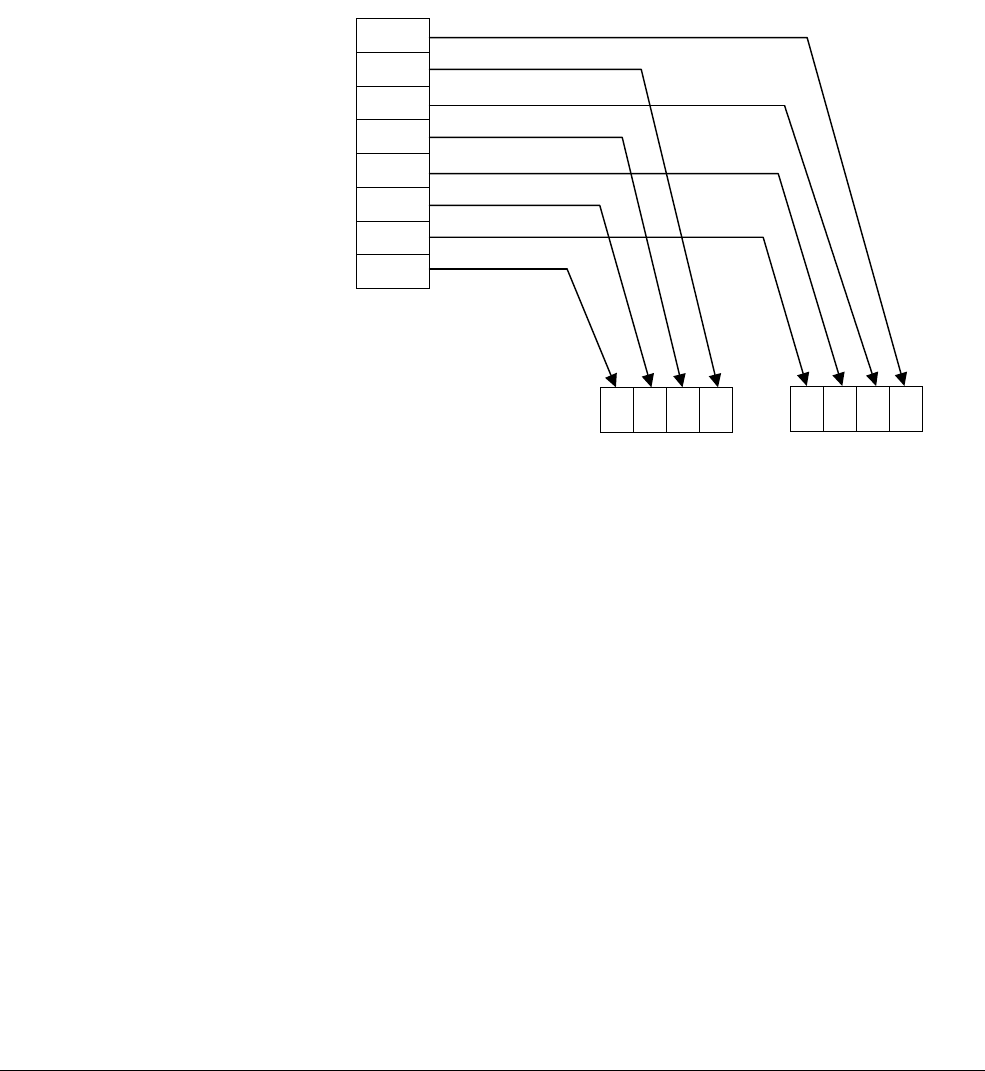

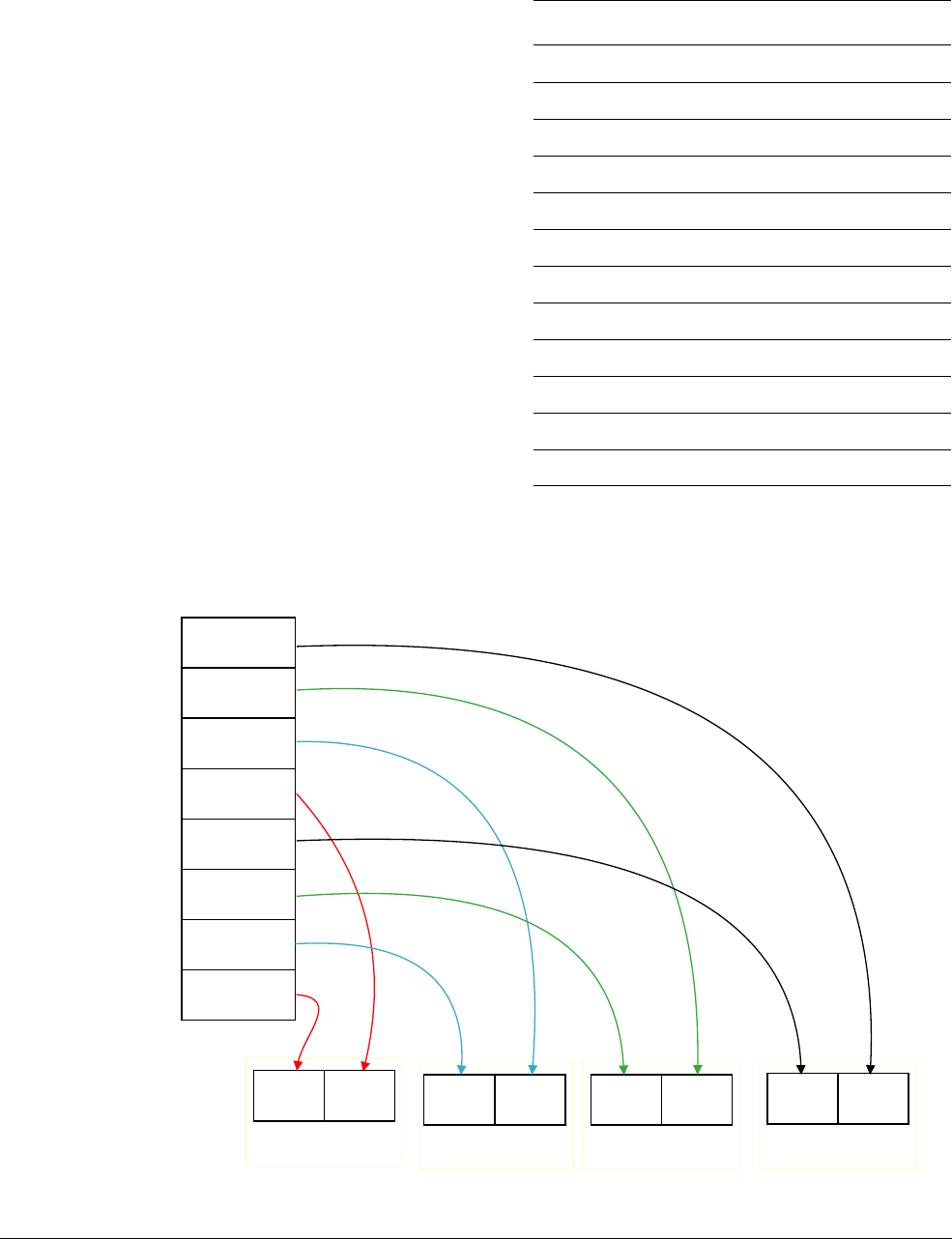

in Figure 1-1. This method is faster.

In ARM terminology this is called Advanced SIMD technology or NEON technology.

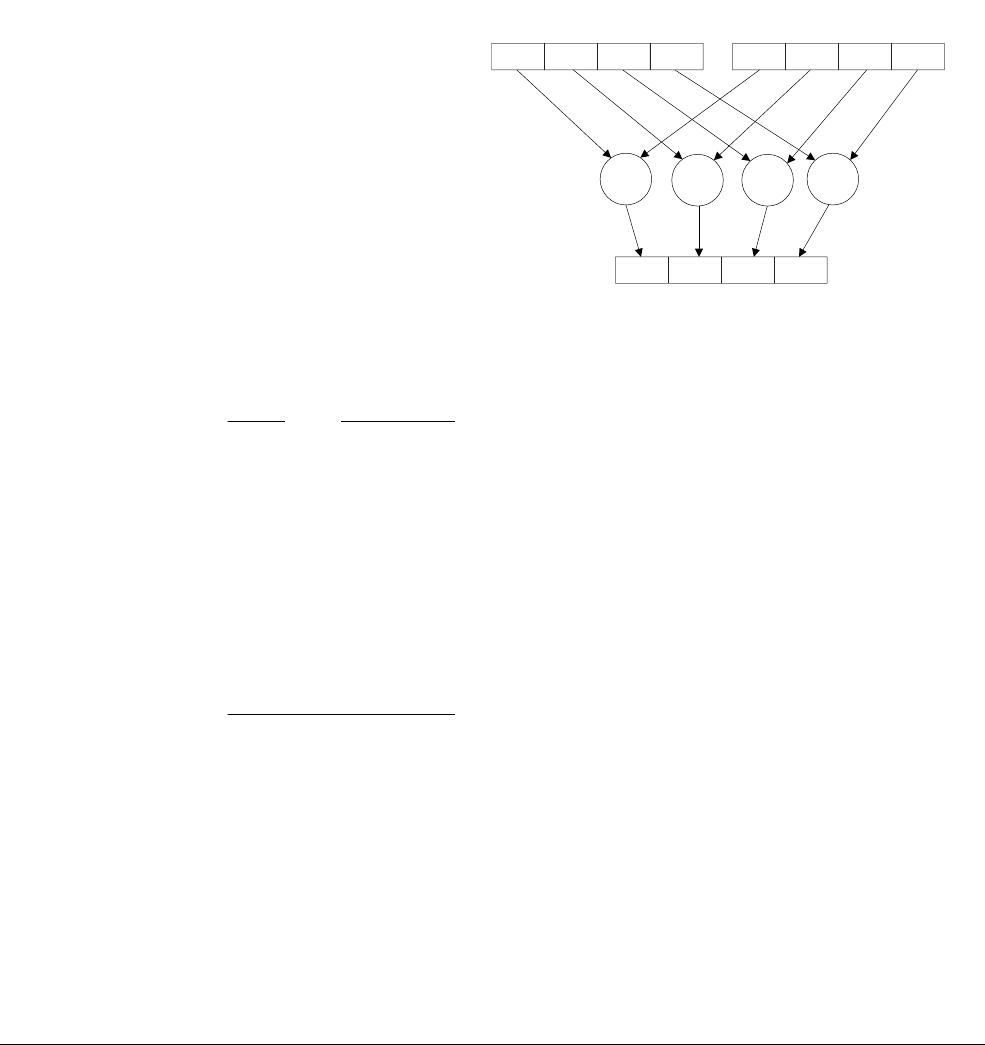

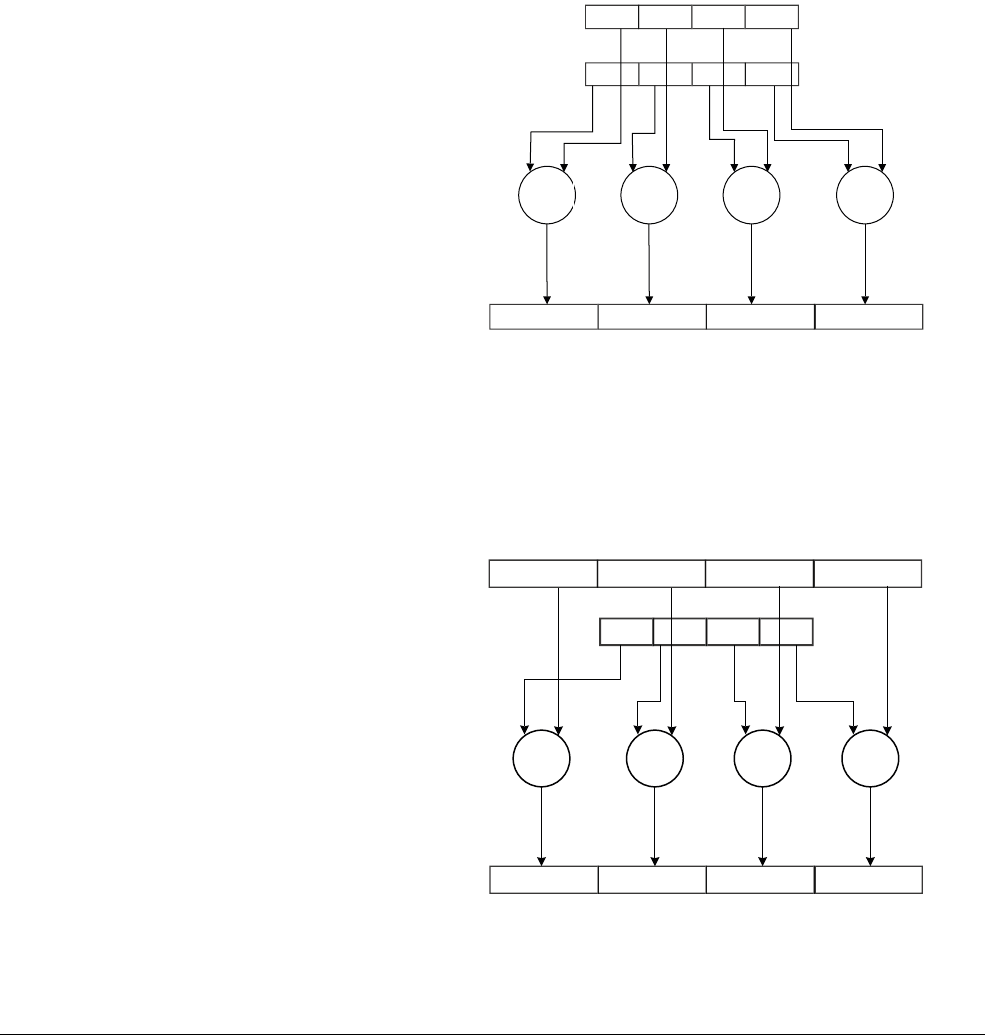

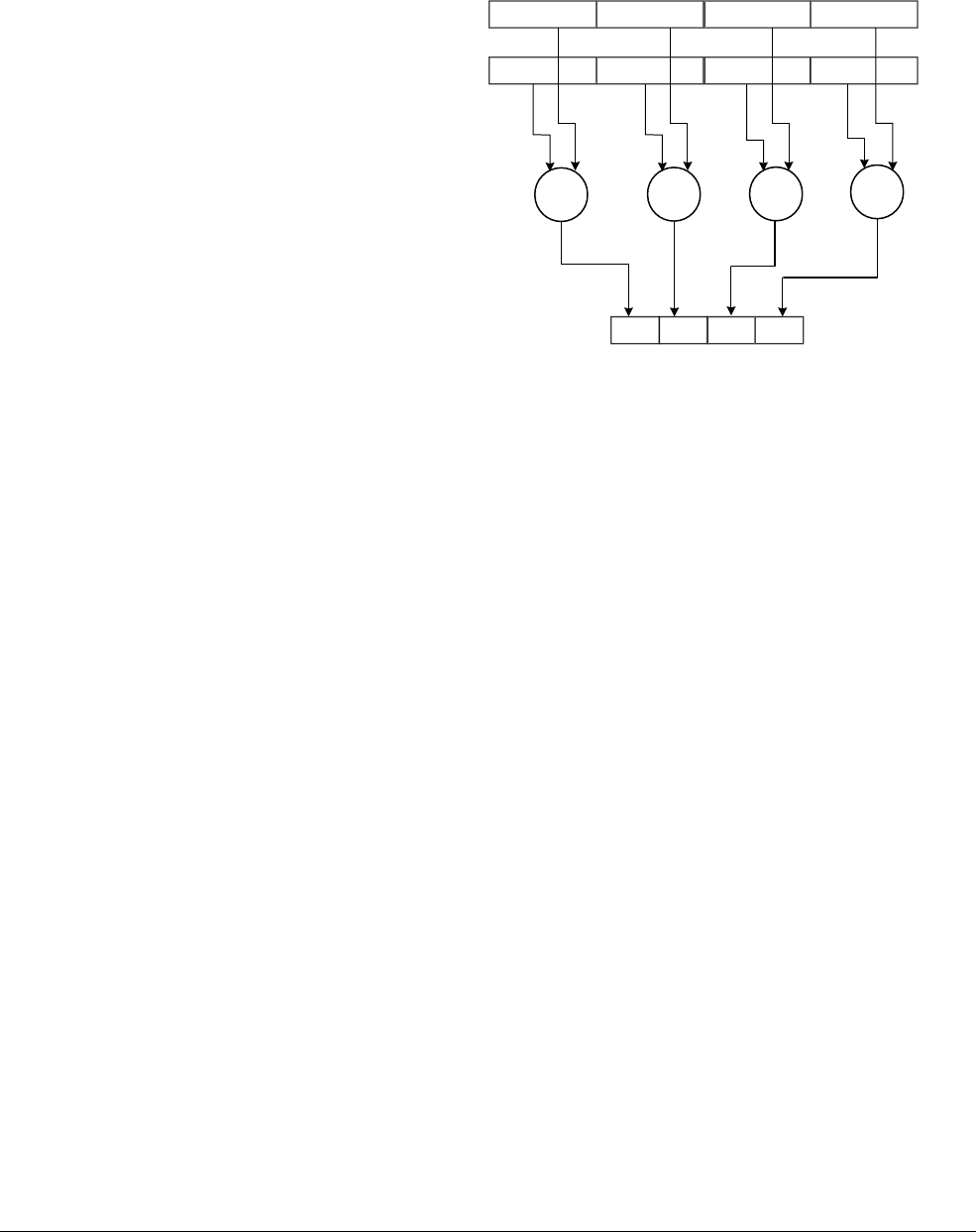

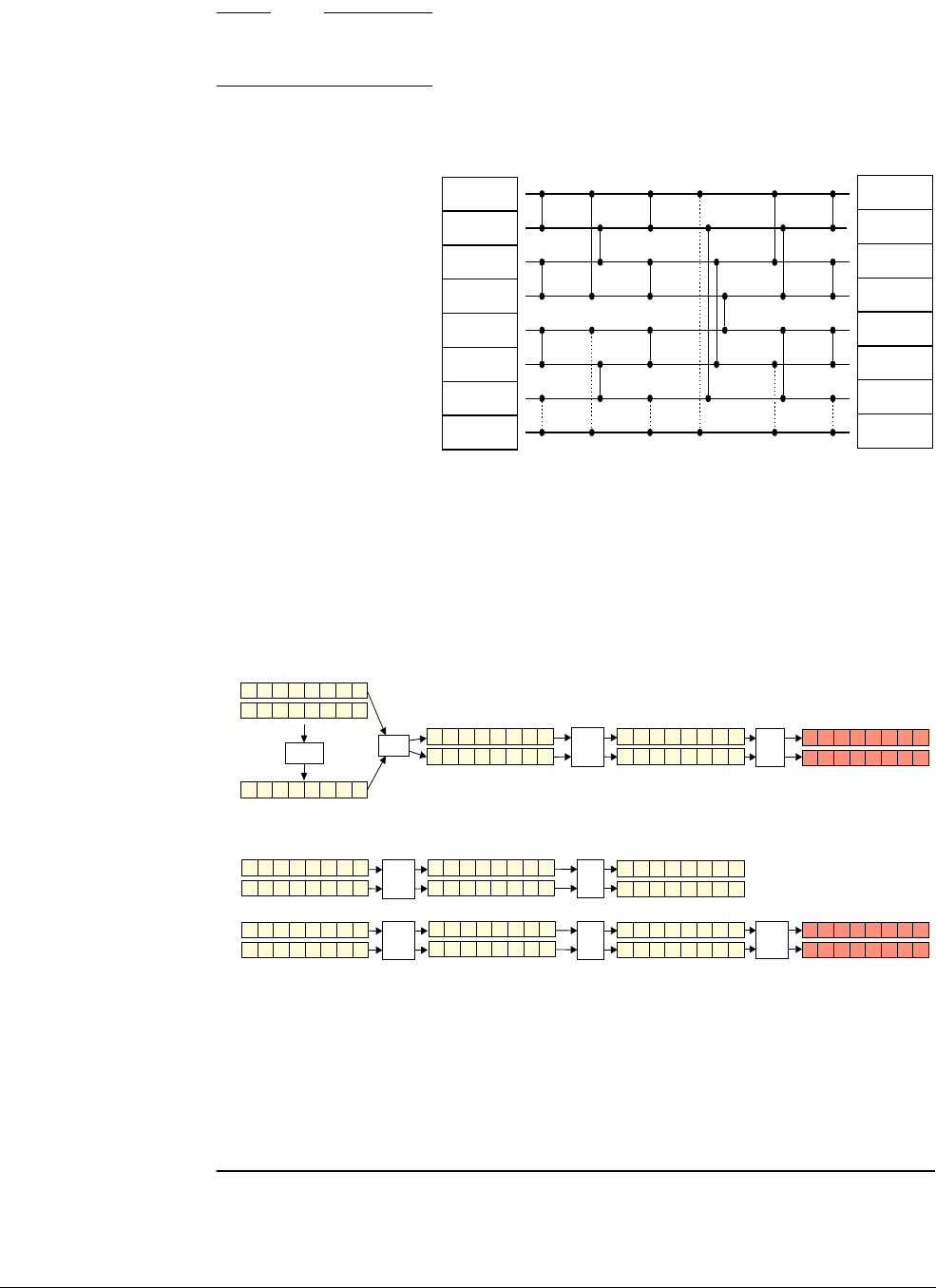

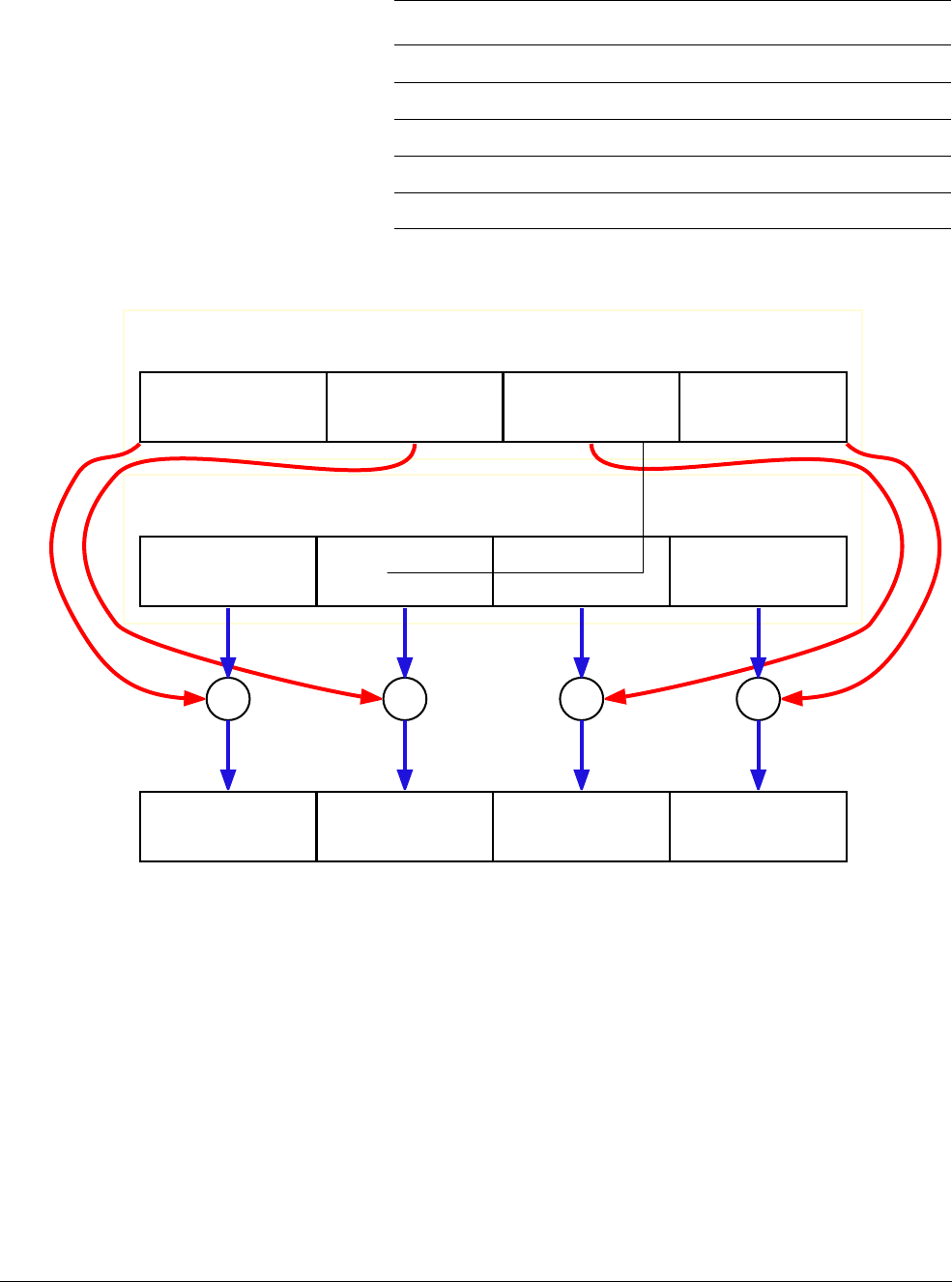

Figure 1-1 Four simultaneous additions

Note

• The addition operations in Figure 1-1 are truly independent.

• Any overflow or carry from bit 7 of lane 0 does not affect bit 8 of lane 1, which is used in

a separate calculation.

•Figure 1-1 shows a 64-bit register holding four 16-bit values, but other combinations are

possible for NEON registers:

— Two 32-bit, four 16-bit, or eight 8-bit integer data elements can be operated on

simultaneously in a single 64-bit register.

— Four 32-bit, eight 16-bit, or sixteen 8-bit integer data elements can be operated on

simultaneously in a single 128-bit register.

Media processors, such as used in mobile devices, often split each full data register into multiple

sub-registers and perform computations on the sub-registers in parallel. If the processing for the

data sets are simple and repeated many times, SIMD can give considerable performance

improvements. It is particularly beneficial for digital signal processing or multimedia

algorithms, such as:

• Audio, video, and image processing codecs.

• 2D graphics based on rectangular blocks of pixels.

• 3D graphics

• Color-space conversion.

• Physics simulations.

Dn Dm

Dd

+

+

+ + +

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-4

ID071613 Non-Confidential

1.2 Comparison between ARM NEON technology and other implementations

This section describes the difference between NEON technology and other ARM and

third-party data processing extensions:

•Comparison between NEON technology and the ARMv6 SIMD instructions.

•Comparison between NEON technology and other SIMD solutions on page 1-5.

•Comparison of NEON technology and Digital Signal Processors on page 1-6.

1.2.1 Comparison between NEON technology and the ARMv6 SIMD instructions

The ARMv6 architecture introduced a small set of SIMD instructions that operate on multiple

16-bit or 8-bit values packed into standard 32-bit ARM general-purpose registers. These

instructions permitted certain operations to execute two or four times as fast, without adding

additional computation units.

The ARMv6 SIMD instruction

UADD8

R0, R1, R2

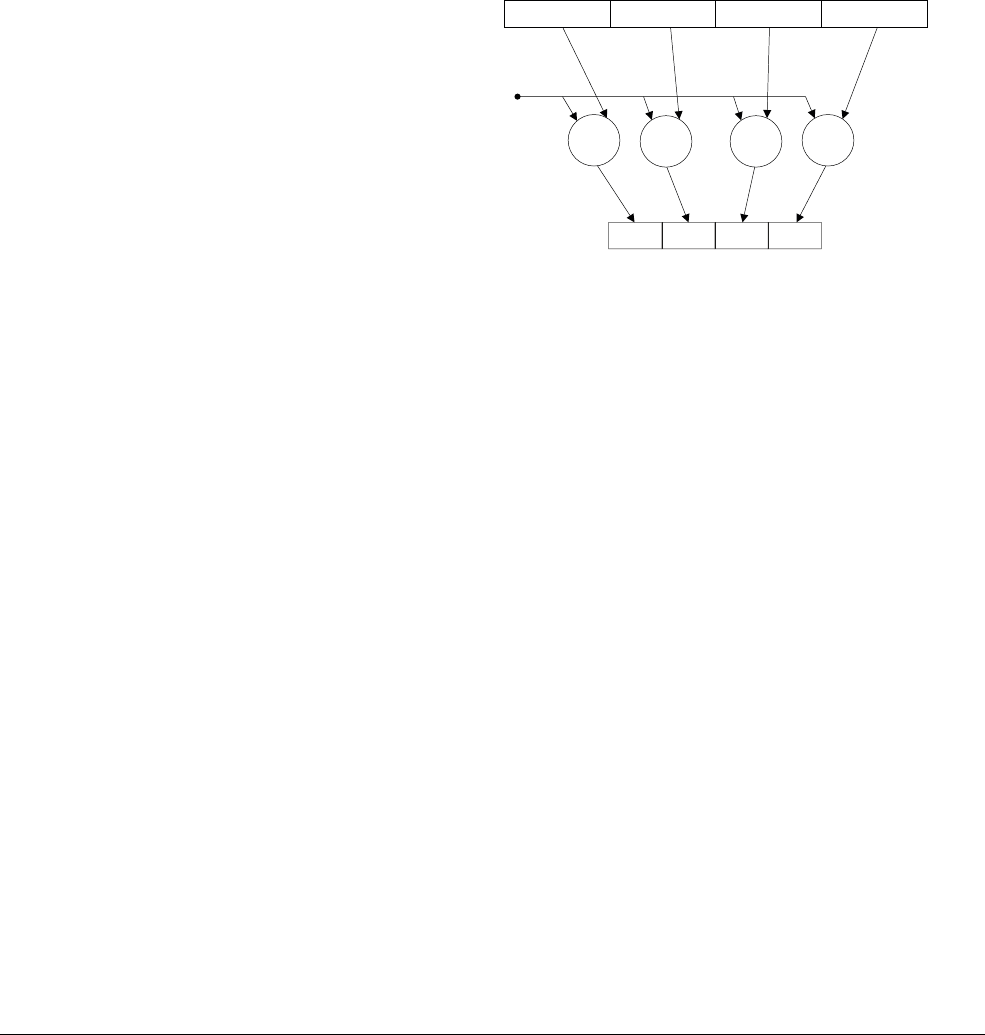

adds four 8-bit values in one 32-bit register to

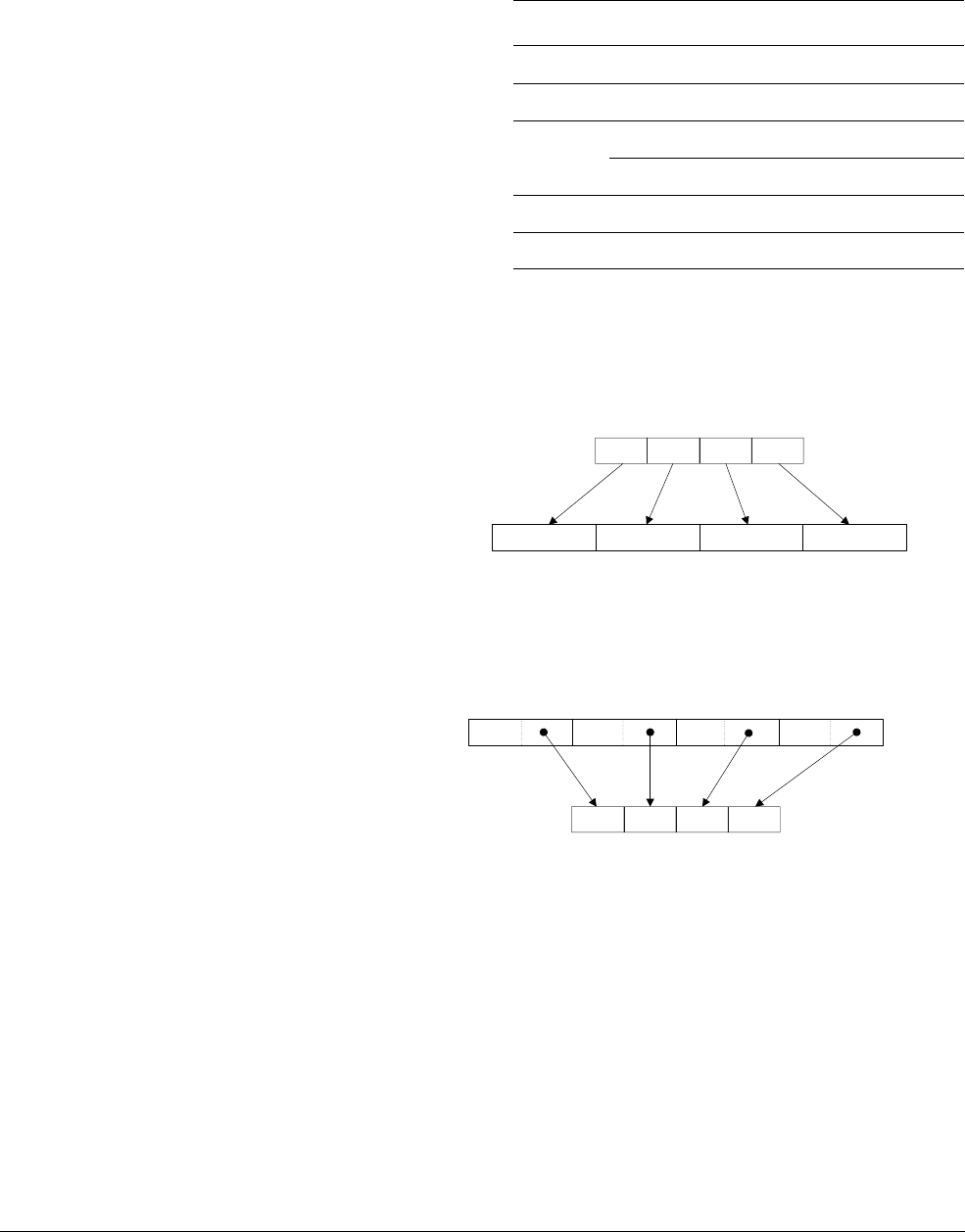

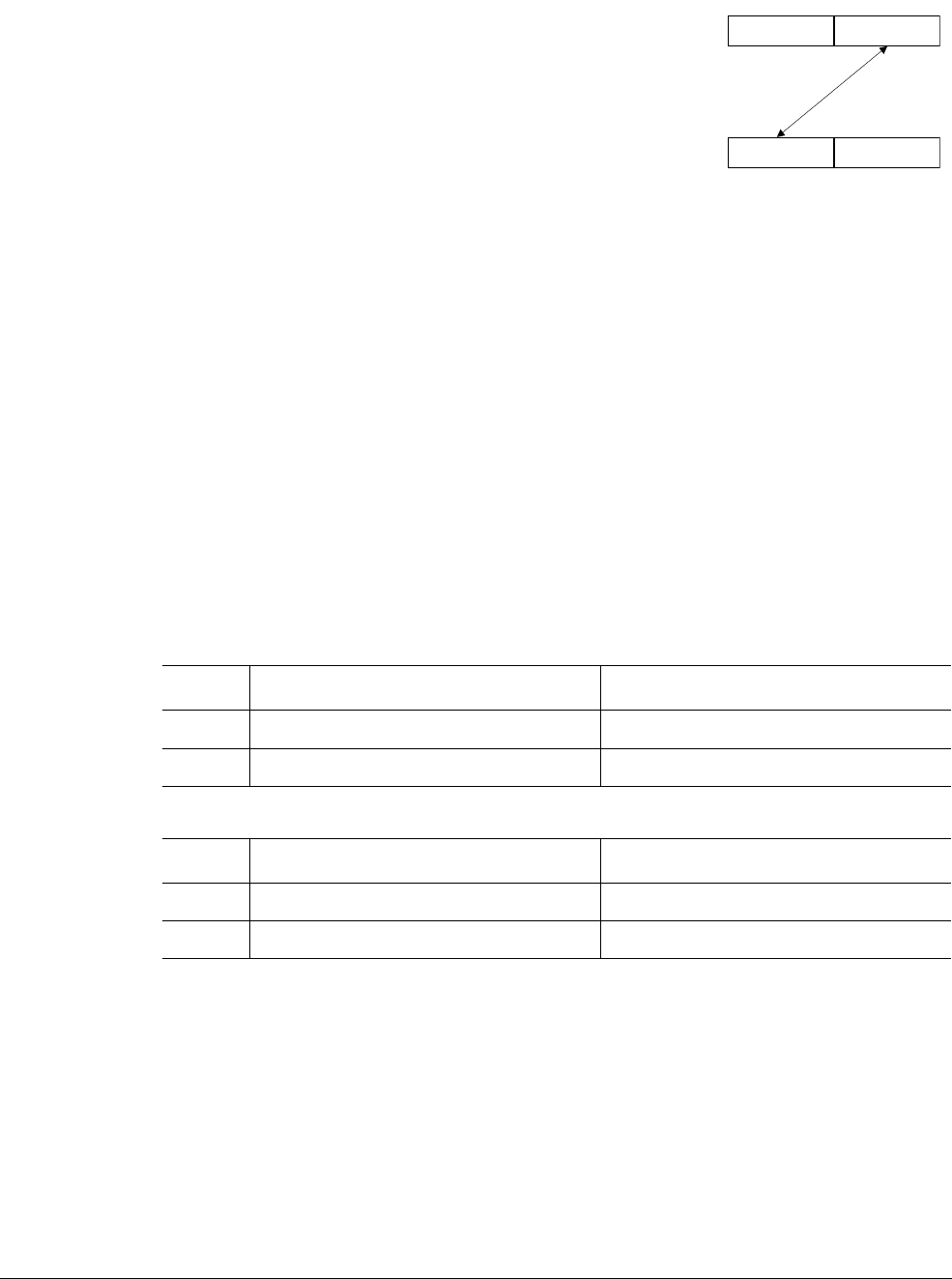

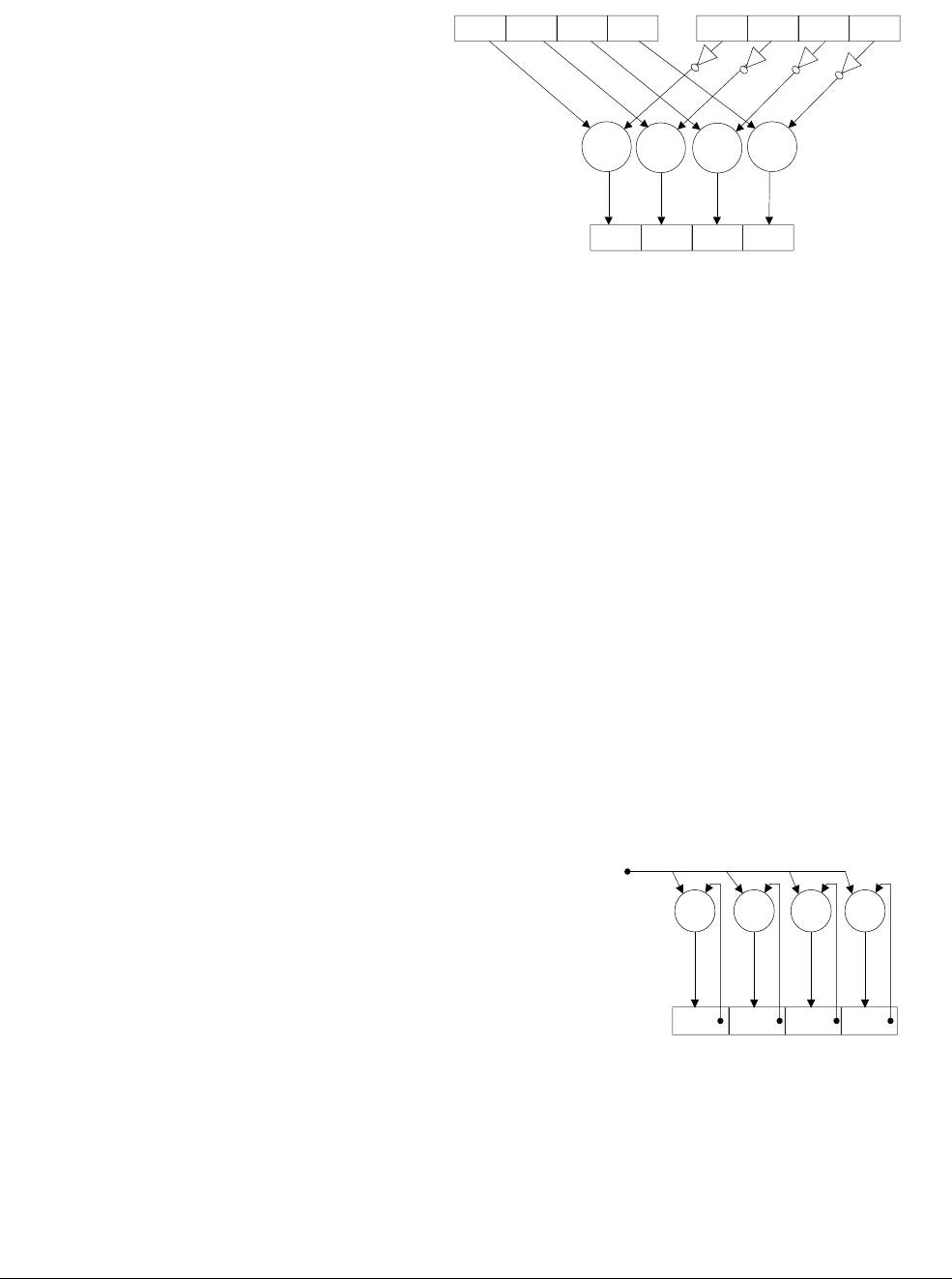

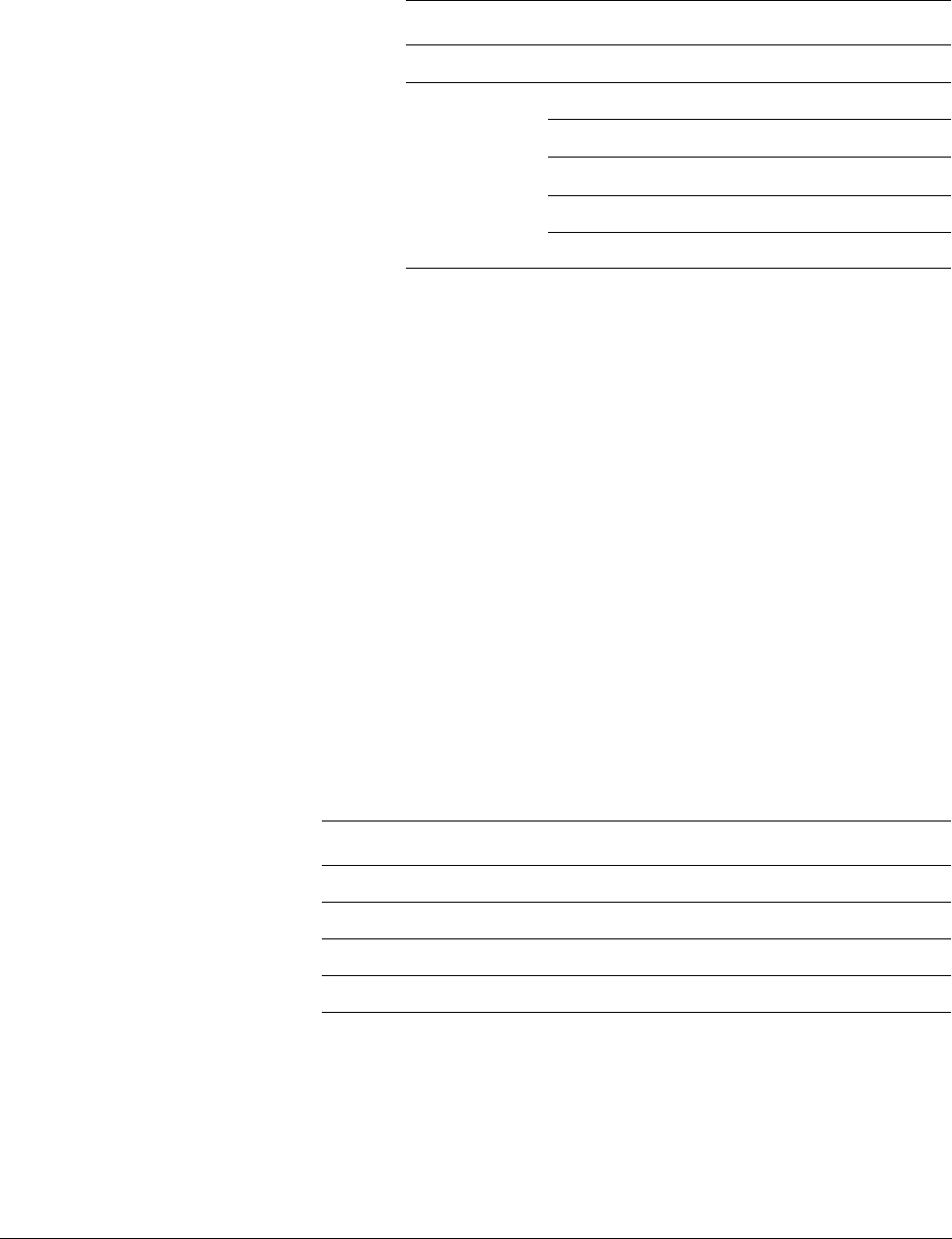

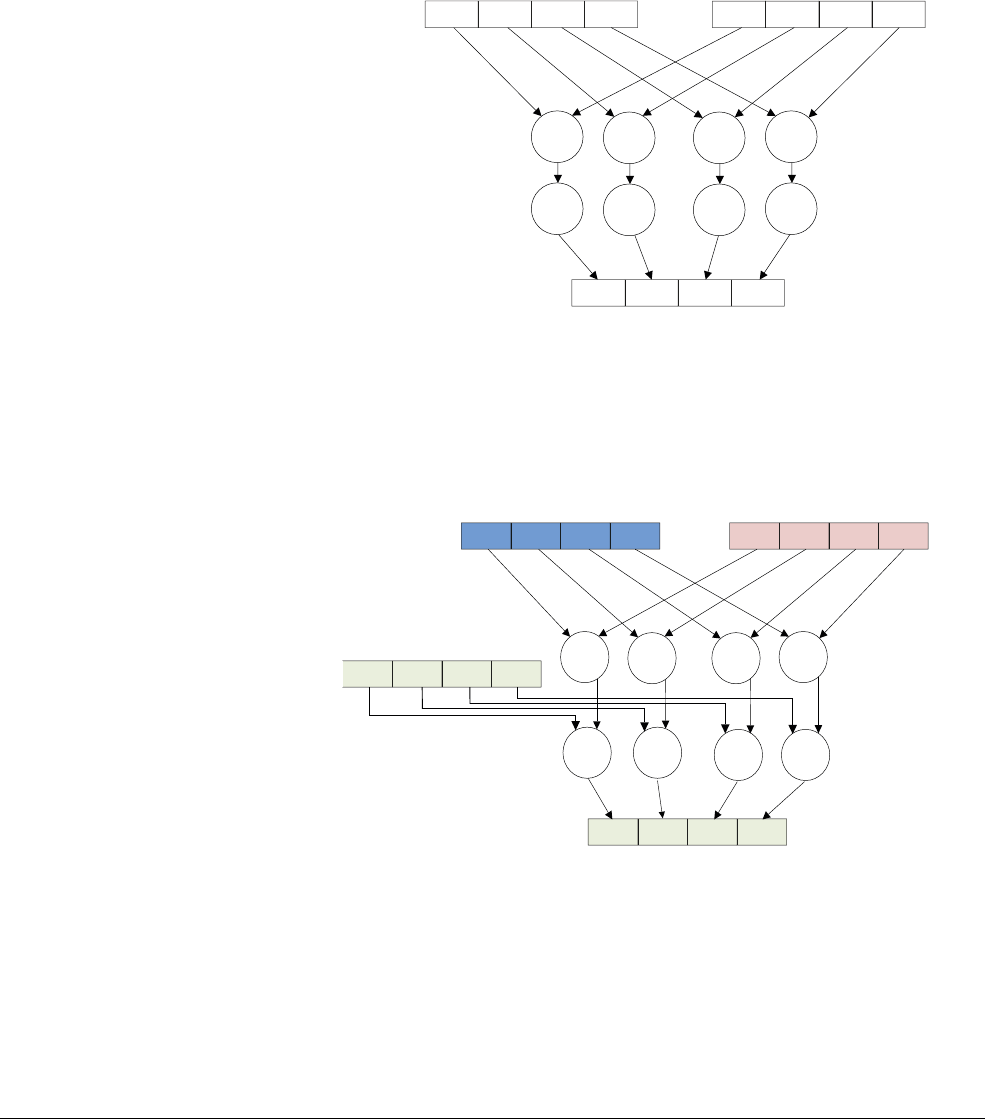

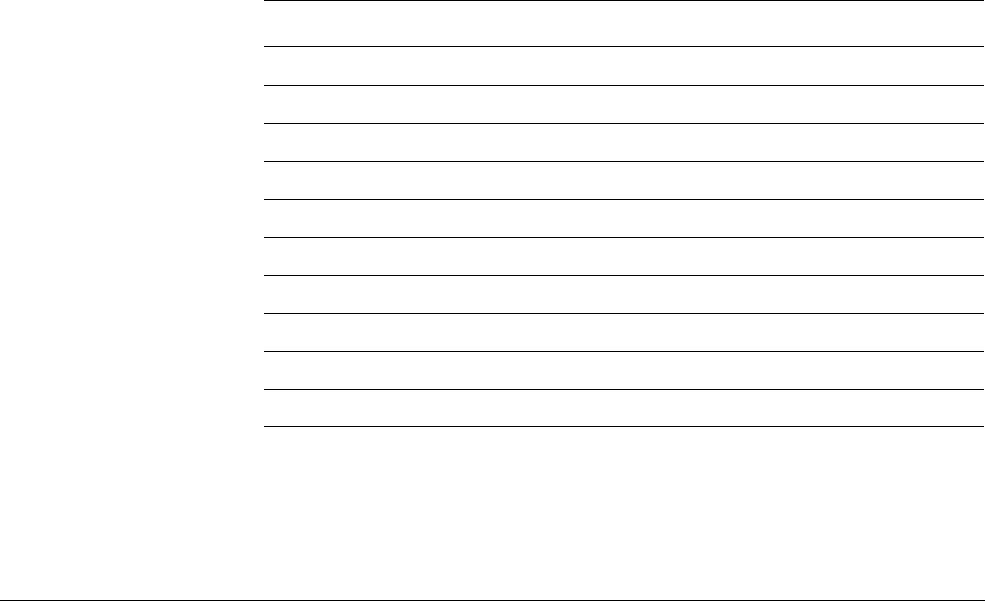

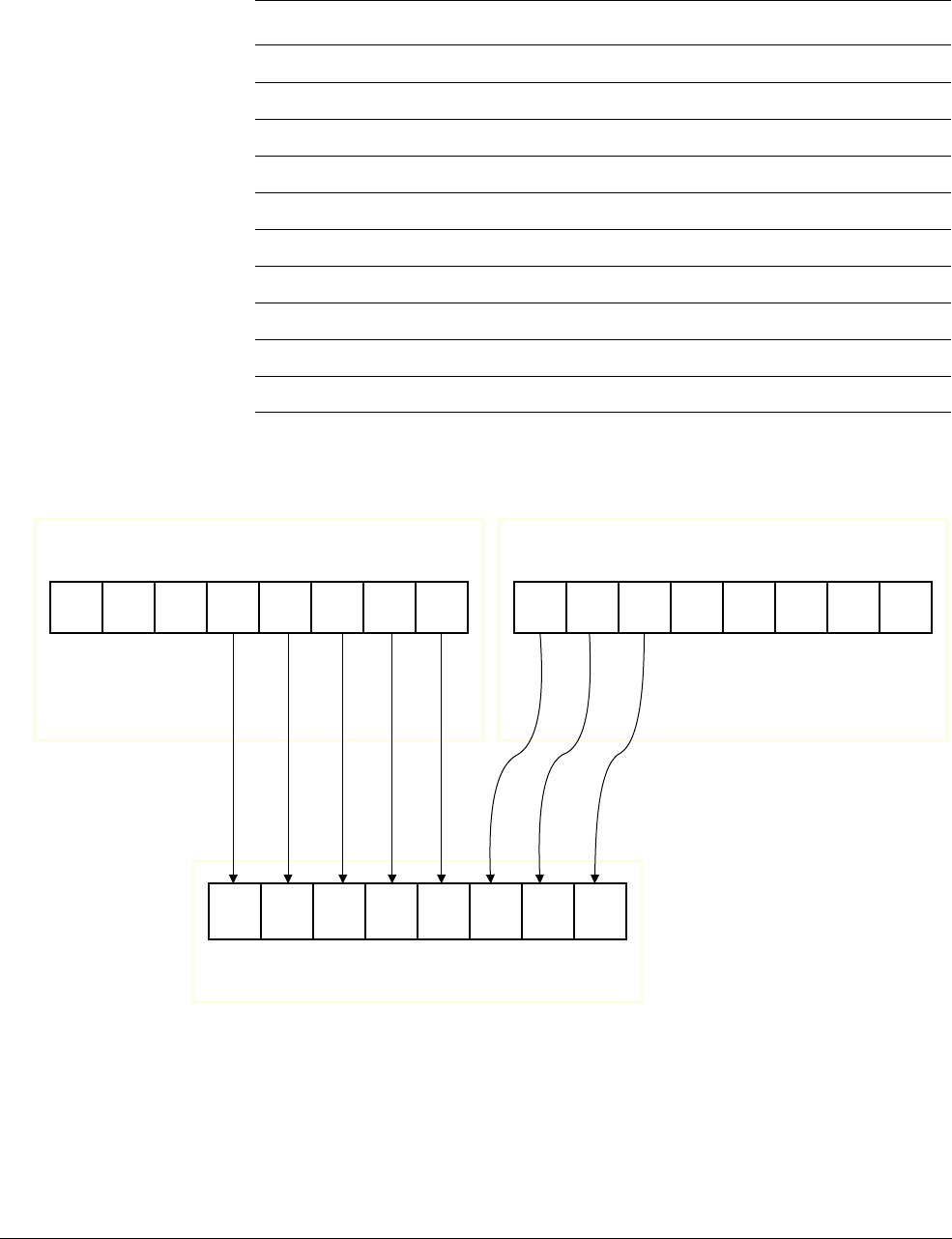

four 8-bit values in another 32-bit register as shown in Figure 1-2.

Figure 1-2 A 4-way 8-bit add operation is one of the ARMv6 SIMD instructions

This operation performs a parallel addition of four 8-bit elements (called lanes) packed into

vectors in the 32-bit registers R1 and R2, and places the result into a vector in register R0.

The ARM1176™ applications processors, for example, implement the ARMv6 architecture.

ARM NEON technology builds on the concept of SIMD and supports 128-bit vector operations

instead of the 32-bit vector operations in the ARMv6 architecture.

The NEON unit is included by default in the Cortex-A7 and Cortex-A15 processors, but is

optional in other ARMv7 Cortex-A series processors.

31

31

31

24 23

24 23

24 23

16 15

16 15

16 15

8 7

8 7

8 7

0

0

0

+

Lane 2

R2

R1

R0

Vector

Lane 1 Lane 0Lane 3

+

++

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-5

ID071613 Non-Confidential

Table 1-1 compares NEON technology with ARMv6 SIMD.

1.2.2 Comparison between NEON technology and other SIMD solutions

SIMD processing is not unique to ARM, and it is useful to consider other implementations and

compare them with NEON technology.

Table 1-1 Comparison of NEON extensions and ARMv6 SIMD instructions

Feature ARMv7 NEON extension ARMv6 SIMD instructions

Packed integers up to 8 x 8-bit, 4 x 16-bit, and 2 x 32 bit 4 x 8-bit

Data types Supports integer and, if the processor has a VFP unit,

single precision floating-point operations

Supports integer operations only

Simultaneous operations Maximum sixteen

(as 16 x 8-bit)

Maximum four

(as 4 x 8-bit)

Dedicated registers Operates on separate NEON register file that is shared

with the VFP unit

32 64-bit registers (or 16 128-bit registers)

Uses 32-bit general purpose ARM

registers

Pipeline Has dedicated pipeline that is optimized for NEON

execution

Uses the same pipeline as all other

instructions

Table 1-2 NEON technology compared with MMX and Altivec

NEON technology x86 MMX/SSE Altivec

Number of

registers

32 × 64-bit

(also visible as 16 × 128-bit)

SSE2: 8 × 128-bit XMM (in x86-32

mode)

Additional 8 registers in x86-64

mode

32 × 128-bit

Memory / register

operations

Register-based 3-operand

instructions

Mix of register and memory

operations

Register-based 3- and

4-operand instructions

Load/store support

for packed data

types

Yes as 2,3, or 4 element No No

Move between

scalar and vector

register

Yes Ye s No

Floating-point

support

Single-precision 32-bit Single-precision and

Double-precision

Single-precision

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-6

ID071613 Non-Confidential

1.2.3 Comparison of NEON technology and Digital Signal Processors

Many ARM processors also incorporate a Digital Signal Processor (DSP) or custom signal

processing hardware, so they can include both a NEON unit and a DSP. There are some

differences between using NEON technology compared with using a DSP:

NEON technology features:

• Extends the ARM processor pipeline.

• Uses the ARM core registers for memory addressing.

• Single thread of control providing easier development and debug.

• OS multitasking supported (if the OS saves or restores the NEON and floating-point

register file).

• SMP capability. There is one NEON unit for each ARM core within an MPCore processor.

With multiple cores, this can provide many times standard performance using standard

pthreads.

• As part of the ARM processor architecture, the NEON unit will be available on future

faster processors and is supported by many ARM processor based SoCs.

• Broad NEON tools support is provided in both the open-source community and the ARM

ecosystem.

DSP features:

• Runs in parallel with ARM processors.

• Lack of OS and task switching overhead can provide guaranteed performance, but only if

DSP system design provides predictable performance.

• Generally more difficult to use by applications programmers: two toolsets, separate

debugger, potential synchronization issues.

• Less tightly integrated with the ARM processor. There can be some cache clean or flush

overhead with transferring data between DSP and the ARM processor which makes using

a DSP less efficient for processing very small blocks of data.

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-7

ID071613 Non-Confidential

1.3 Architecture support for NEON technology

The NEON extension is implemented on some processors that implement the ARMv7-A or

ARMv7-R architecture profiles.

Note

• The ARMv8 architectural architecture extends the NEON support, and provides

backwards compatibility with ARMv7 implementations.

• This manual only covers cores that implement ARMv7-A and ARMv7-R.

• It is not guaranteed that the ARMv7-A or ARMv7-R processor that you are programming

contains either NEON or VFP technology. The possible combinations for cores that

conform to ARMv7 are:

— No NEON unit or VFP unit present.

— NEON unit present, but no VFP unit.

— No NEON unit present, but with a VFP unit.

— Both a NEON unit and a VFP unit are present.

• Processors that have a NEON unit, but no VPF unit, cannot execute floating-point

operations in hardware.

• Because NEON SIMD operations perform vector calculation more efficiently, vector

mode operation in the VFP unit was deprecated from the introduction of ARMv7. The

VFP unit is therefore sometimes referred to as the Floating Point Unit (FPU).

• Processors that do have a NEON or VFP unit, might not support the following extensions:

— Half precision.

— Fused Multiply-Add.

• If a VPF unit is present, there are versions that can access either 16 or 32 NEON

doubleword registers. See VFP views of the NEON and floating-point register file on

page 1-15.

1.3.1 Instruction timings

The NEON architecture does not specify instruction timings. An instruction might require a

different number of cycles to execute on different processors.

Even on the same processor, instruction timing can vary. One common cause of variation is

whether the instructions and data remain in the cache.

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-8

ID071613 Non-Confidential

1.3.2 Support for VFP-only systems

Some instructions are common to the NEON and VFP extensions. These are called shared

instructions.

Note

Both VFP and the NEON unit are use instructions in the CP10 and CP11 coprocessor instruction

space and share the same register file, leading to some confusion between the two types of

operation:

• VFP can provide fully IEEE-754 compatible floating point operations that can, depending

on the implementation, operate on single-precision and double-precision floating point

values.

• The NEON unit is a parallel data processing unit for integer and single-precision floating

point data, and single precision operations in the ARMv7 NEON unit are not fully

IEEE-754 compliant.

• The NEON unit does not replace VFP. There are some specialized instructions that VFP

offers which have no equivalent implementations in the NEON instruction set.

If your processor does however have both a NEON unit and a VFP unit:

• All the NEON registers overlap with the VFP registers.

• All VFP data-processing instructions can execute on the VFP unit.

• The shared instructions can execute on the NEON Floating-Point pipeline.

1.3.3 Support for the Half-precision extension

The half-precision instructions are only available on NEON and VFP systems that include the

half-precision extension.

The Half-precision extension extends both the VFP and the NEON architectures. It provides

floating-point and NEON instructions that perform conversion between single-precision

(32-bit) and half-precision (16-bit) floating-point numbers.

1.3.4 Support for the Fused Multiply-Add instructions

The Fused Multiply-Add instructions is an optional extension to both the VFP and the NEON

extensions. It provides VFP and NEON instructions that perform multiply and accumulate

operations with a single rounding step, so suffers from less loss of accuracy than performing a

multiplication followed by an add.

The fused multiply-add instructions are only available on NEON or VFP systems that

implement the fused multiply-add extension. VFPv4 and Advanced SIMDv2 include support

for Fused Multiply-Add instructions.

1.3.5 Security and virtualization

The Cortex-A9 and Cortex-A15 processors include the ARM Security Extensions. The

Cortex-A15 processors include the ARM Security Extensions and the Virtualization Extensions.

These extensions can affect how you write code for the NEON and VFP units. These extensions

are outside the scope of this document, see the ARM Architecture Reference Manual ARMv7-A

and ARMv7-R for more information.

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-9

ID071613 Non-Confidential

1.3.6 Undefined instructions

NEON instructions, including the half-precision half-precision and Fused Multiply-Add

instructions, are treated as Undefined Instructions on systems that do not support the necessary

architecture extension.

Even on systems that have the NEON unit and VFP unit, the instructions are undefined if they

are not enabled in the CP15 Coprocessor Access Control Register (CPACR). For more

information on enabling the NEON and VFP units, see the Technical Reference Manual for the

processor you are programming.

1.3.7 Support for ARMv6 SIMD instructions

ARMv6 architecture added a number of SIMD instructions for efficient software

implementation of multimedia algorithms. The ARM6 SIMD instructions were deprecated from

ARMv7. See Comparison between NEON technology and the ARMv6 SIMD instructions on

page 1-4.

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-10

ID071613 Non-Confidential

1.4 Fundamentals of NEON technology

If you are familiar with the ARM v7-A architecture profile, you will have noticed that the

ARMv7 cores are a 32-bit architecture and use 32-bit registers, but the NEON unit uses 64-bit

or 128-bit registers for SIMD processing.

This is possible because the NEON unit and VFP are extensions to the ARMv7 instruction sets

that operate on a separate register file of 64-bit registers. The NEON and VFP units are fully

integrated into the processor and share the processor resources for integer operation, loop

control, and caching. This significantly reduces the area and power cost compared to a hardware

accelerator. It also uses a much simpler programming model, since the NEON unit uses the same

address space as the application.

The components of the NEON unit are:

• NEON register file

• NEON integer execute pipeline

• NEON single-precision floating-point execute pipeline

• NEON load/store and permute pipeline.

1.4.1 Registers, vectors, lanes and elements

NEON instructions and floating-point instructions use the same register file, called the NEON

and floating-point register file. This is distinct from the ARM core register file. The NEON and

floating-point register file is a collection of registers which can be accessed as 32-bit, 64-bit, or

128-bit registers. Which registers are available for an instruction depends on whether it is a

NEON instruction or VFP instruction. This document refers to the NEON and floating-point

registers as the NEON registers. Certain VFP and NEON instructions move data between the

general-purpose registers and the NEON registers or use the ARM general-purpose registers to

address memory.

The contents of the NEON registers are vectors of elements of the same data type. A vector is

divided into lanes and each lane contains a data value called an element.

Usually each NEON instruction results in

n

operations occurring in parallel, where

n

is the

number of lanes that the input vectors are divided into. Each operation is contained within the

lane. There cannot be a carry or overflow from one lane to another.

The number of lanes in a NEON vector depends on the size of the vector and the data elements

in the vector:

• 64-bit NEON vectors can contain:

— Eight 8-bit elements.

— Four 16-bit elements.

— Two 32-bit elements.

— One 64-bit element.

• 128-bit NEON vectors can contain:

— Sixteen 8-bit elements.

— Eight 16-bit elements.

— Four 32-bit elements.

— Two 64-bit elements.

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-11

ID071613 Non-Confidential

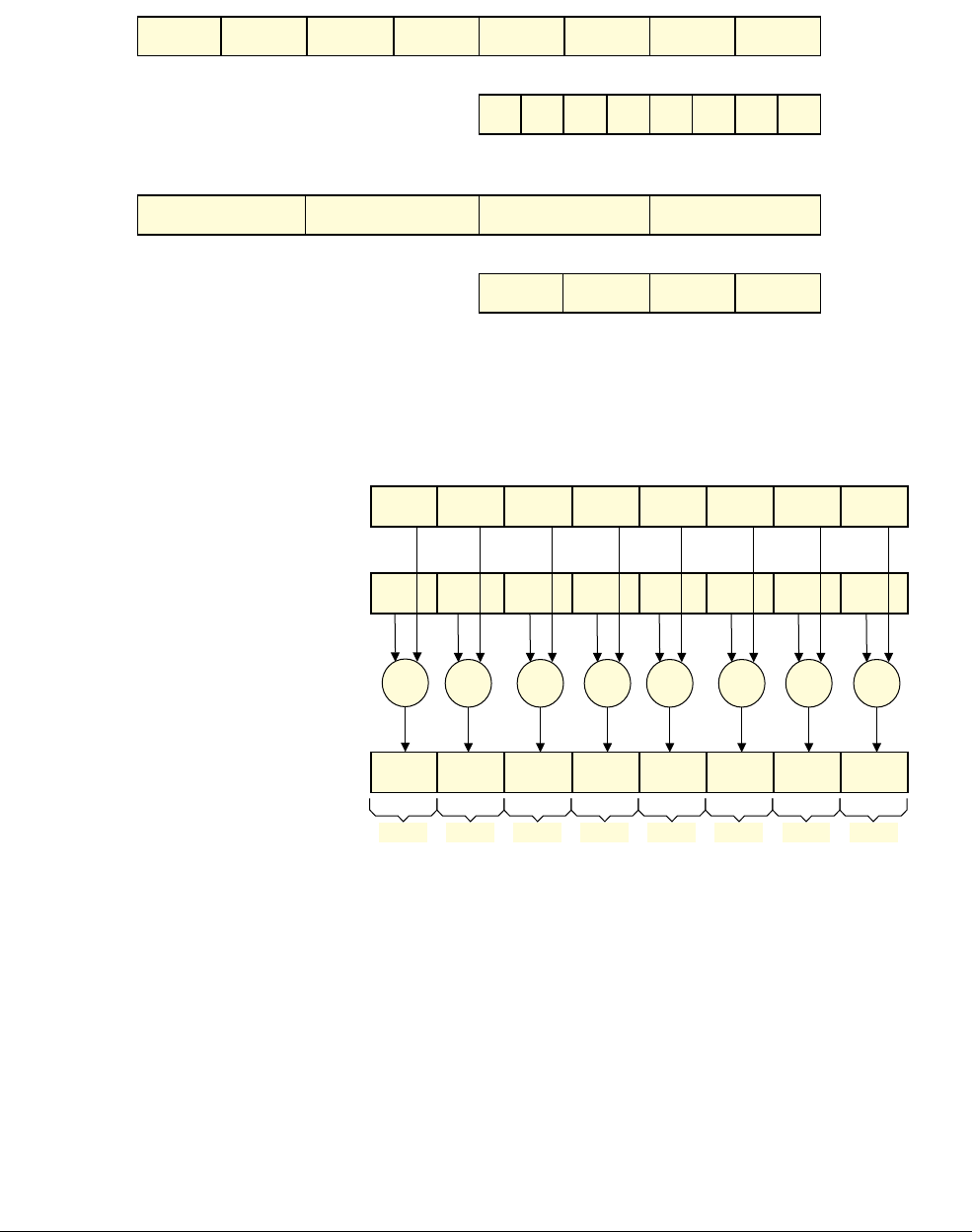

Element ordering

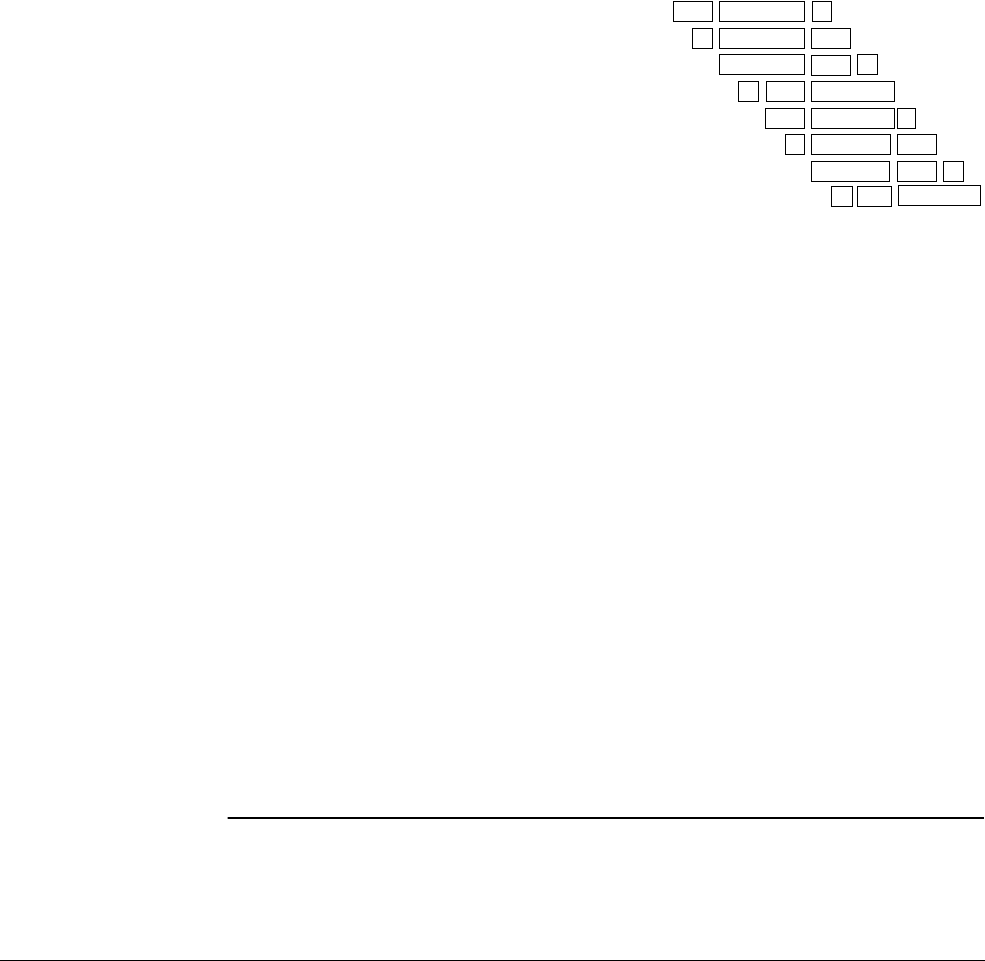

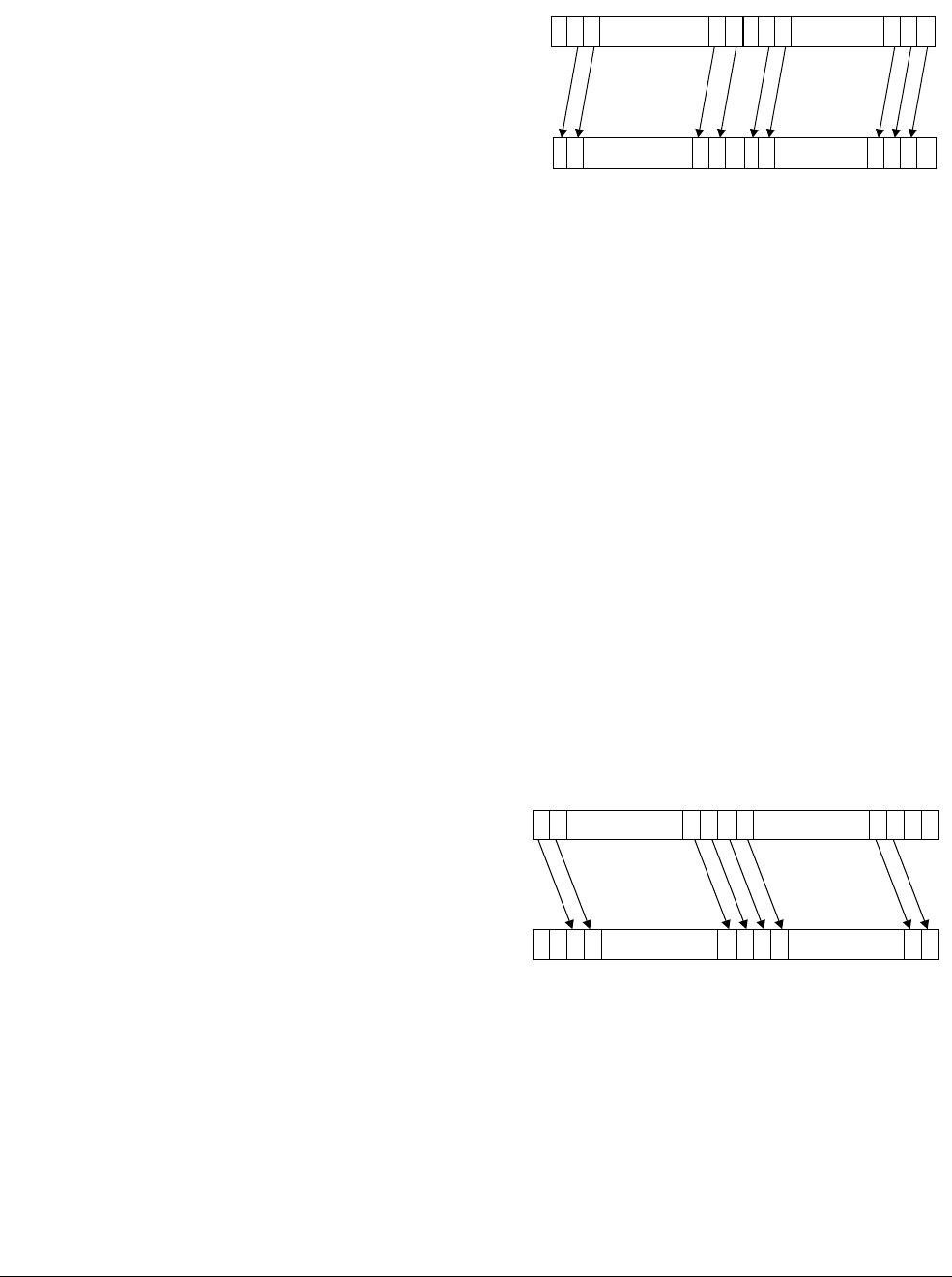

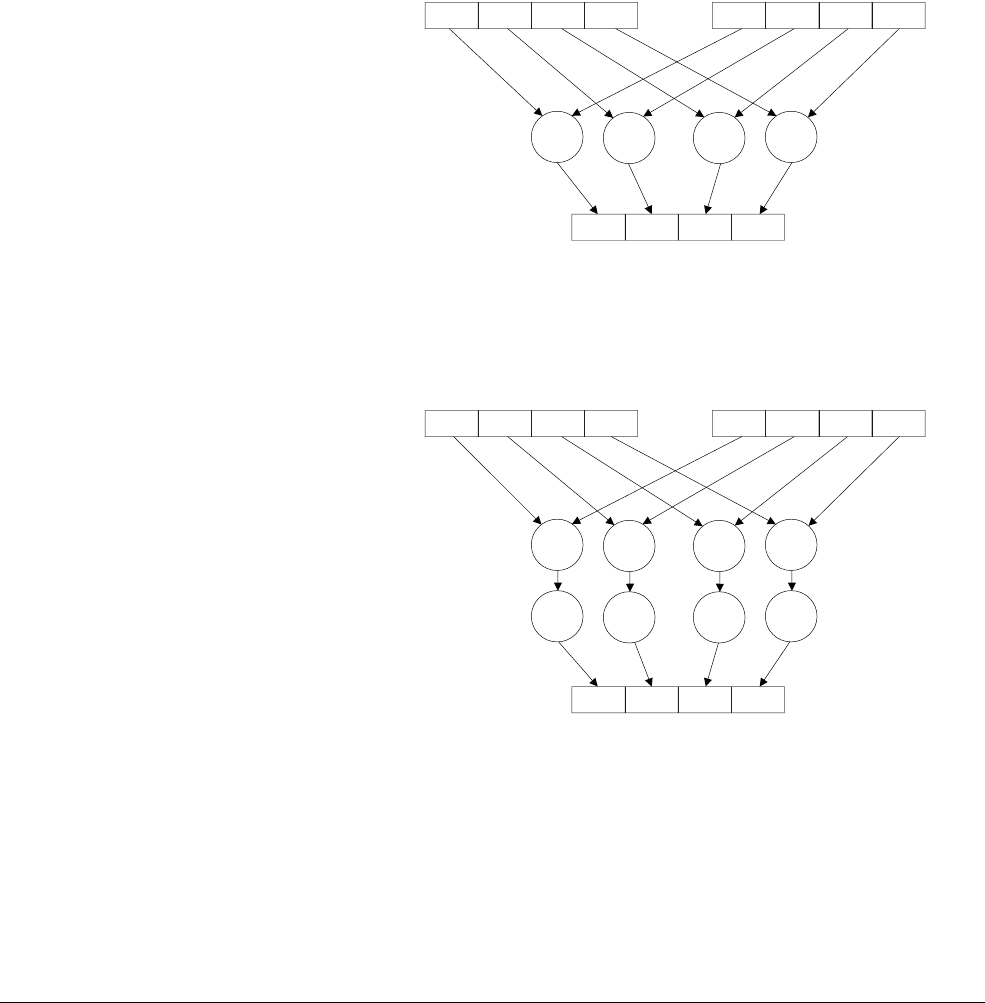

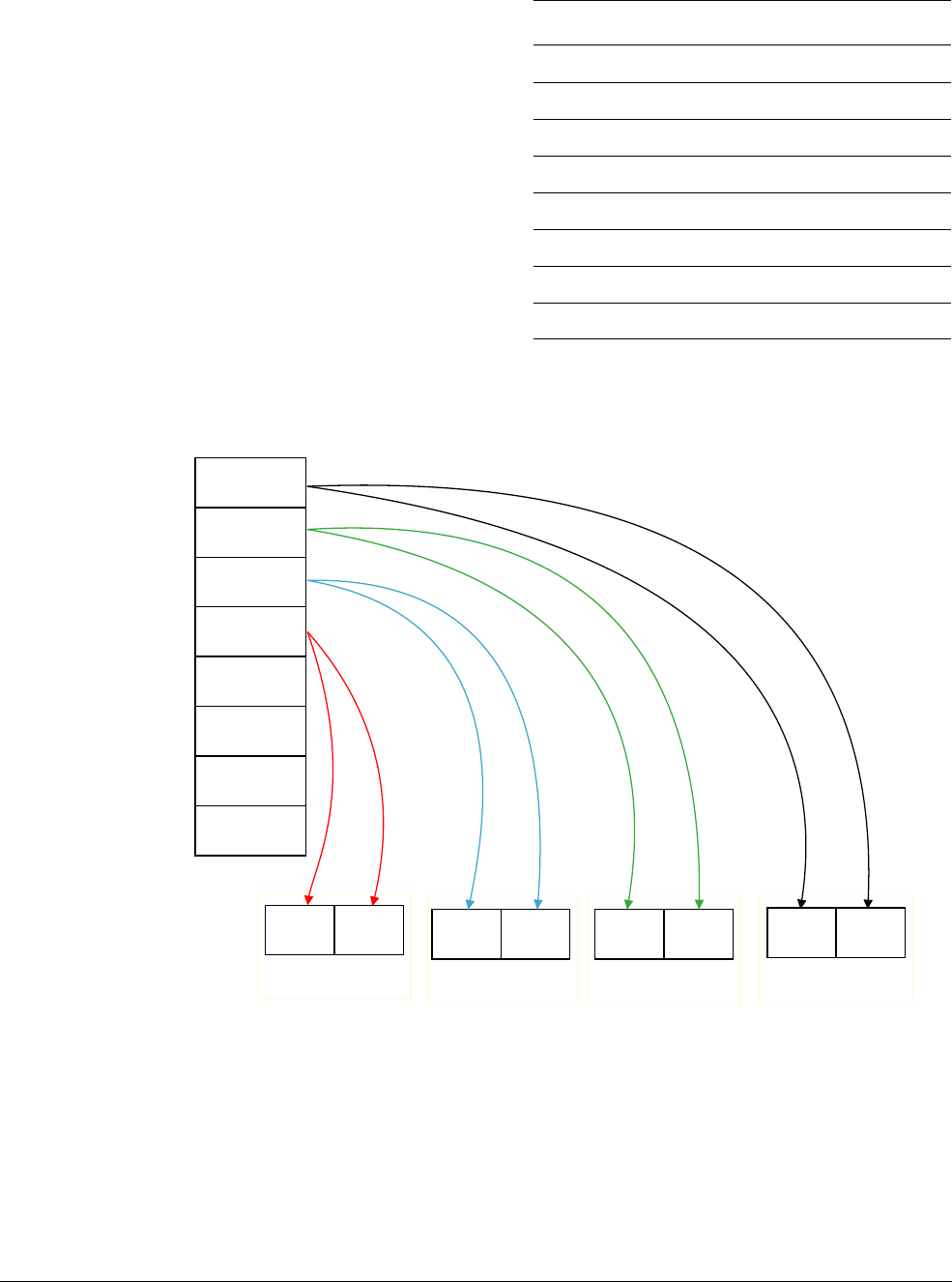

Figure 1-3 shows that the ordering of elements in the vector is from the least significant bit. This

means element 0 uses the least significant bits of the register.

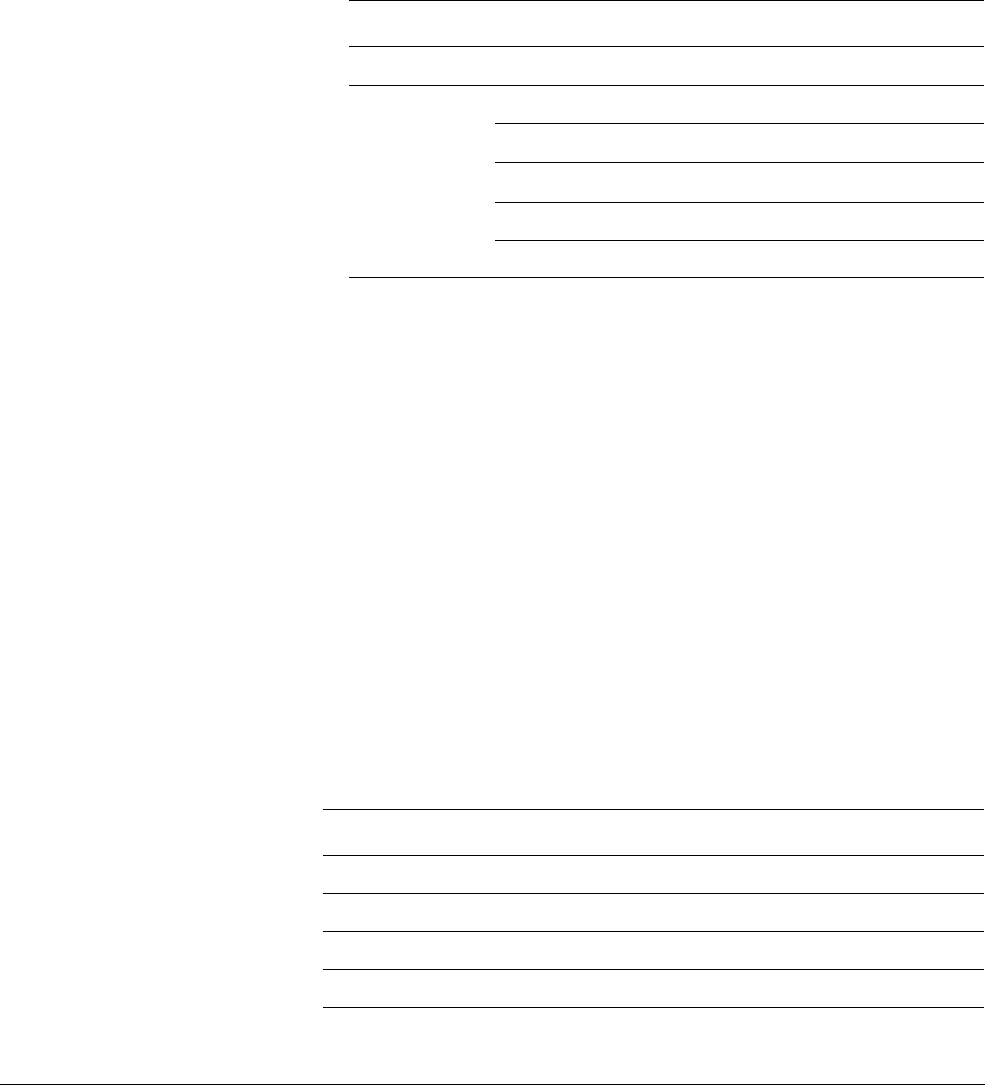

Figure 1-3 Lanes and elements

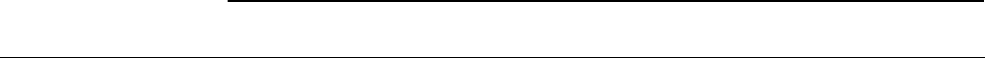

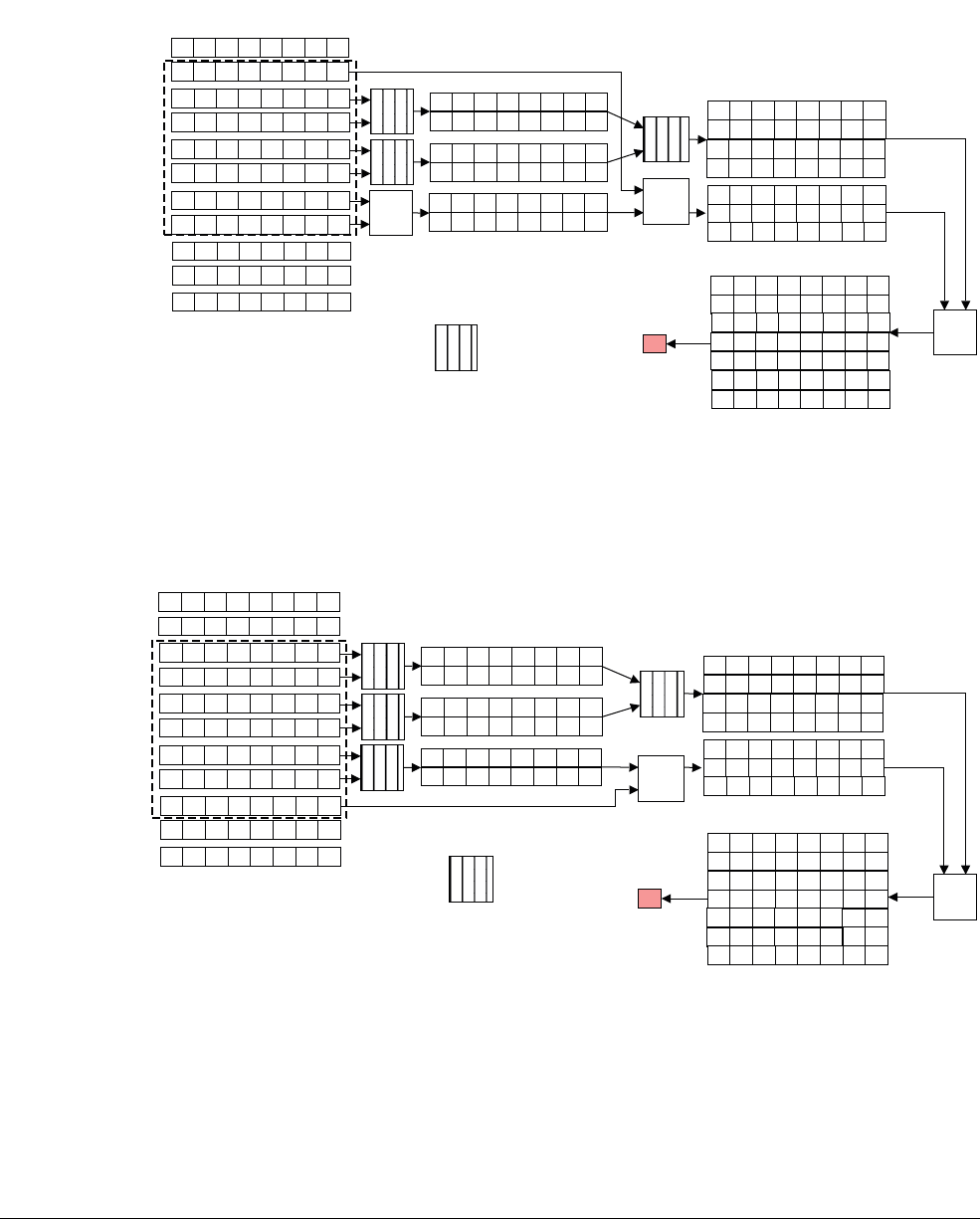

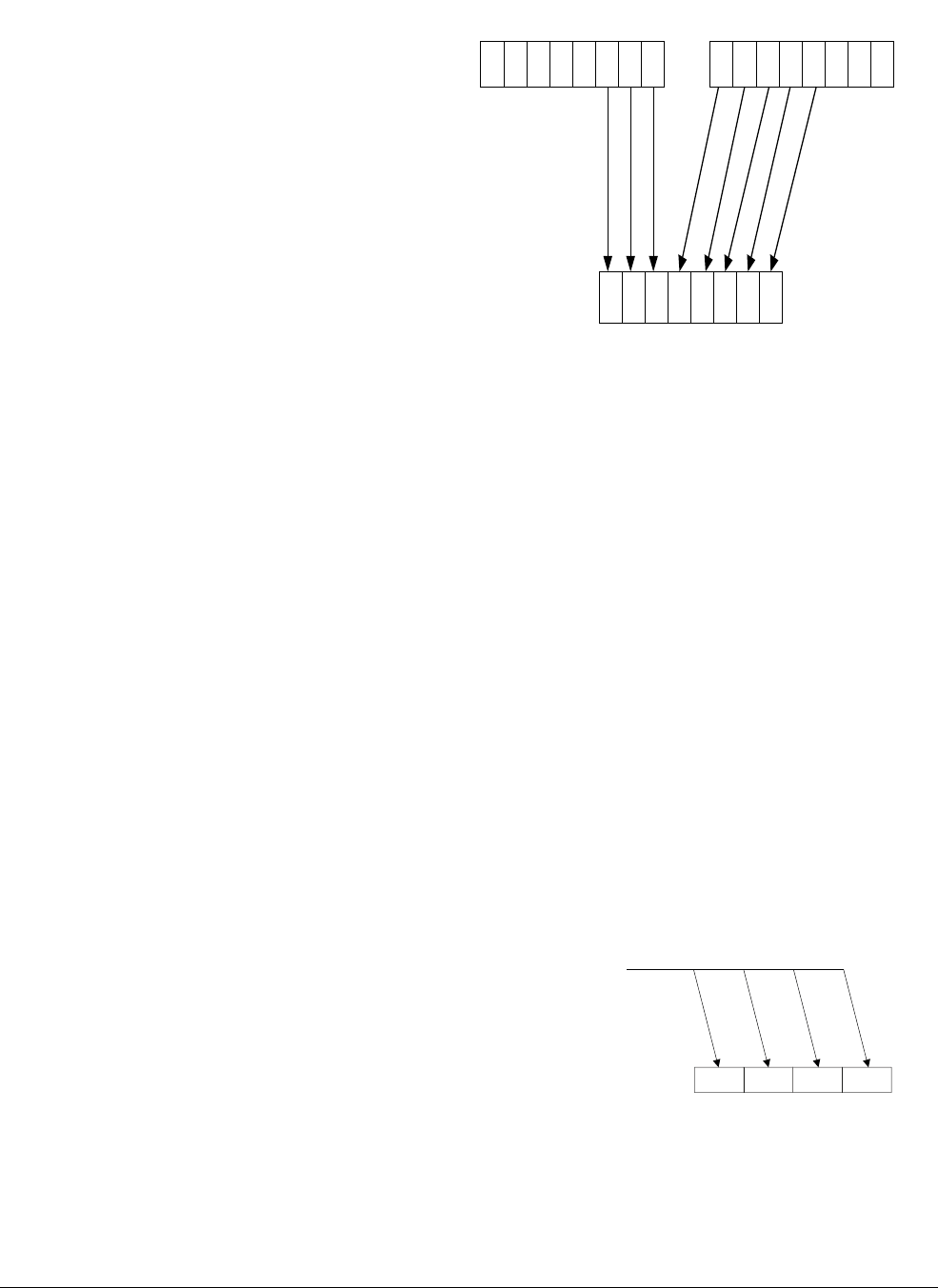

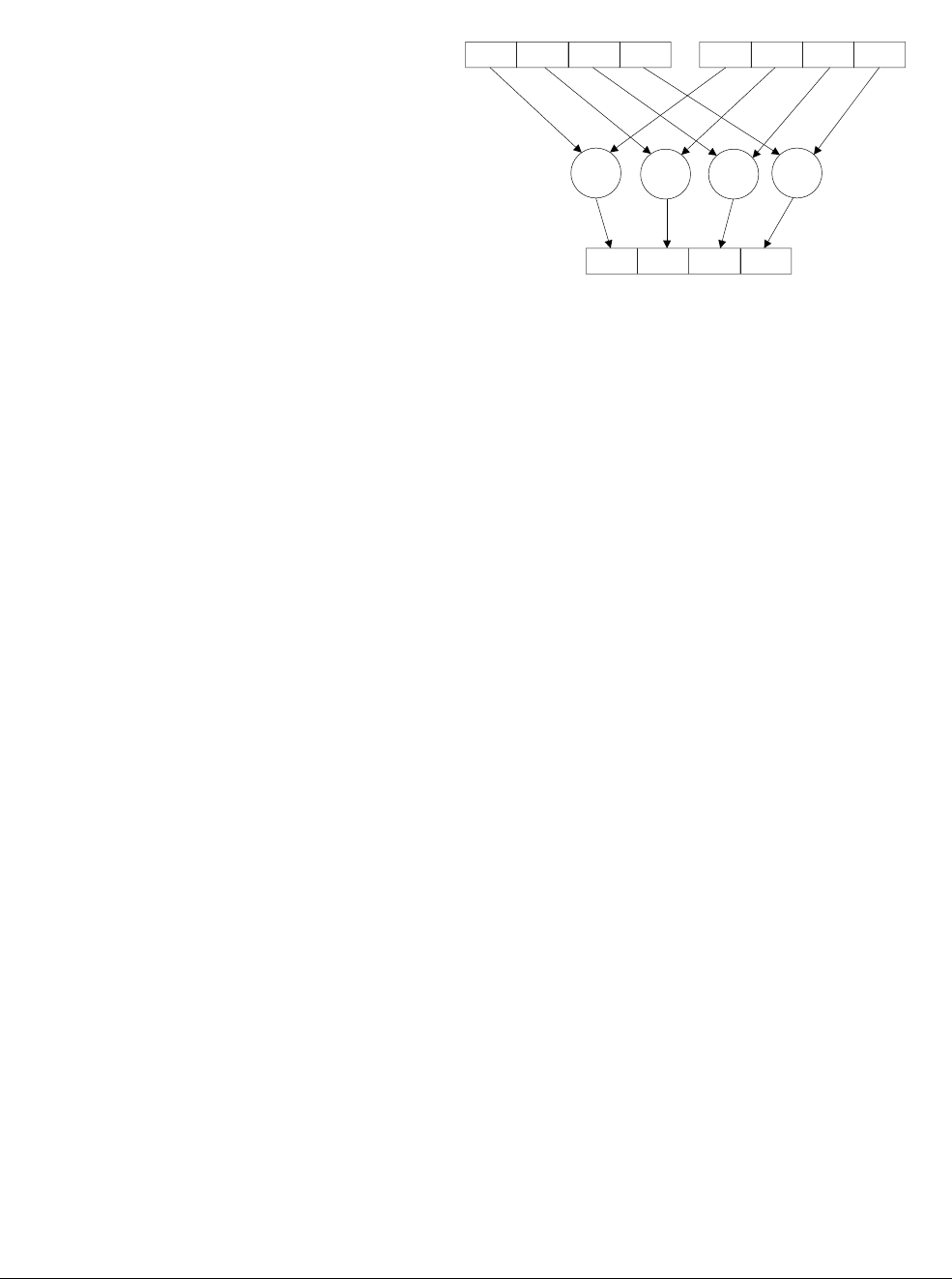

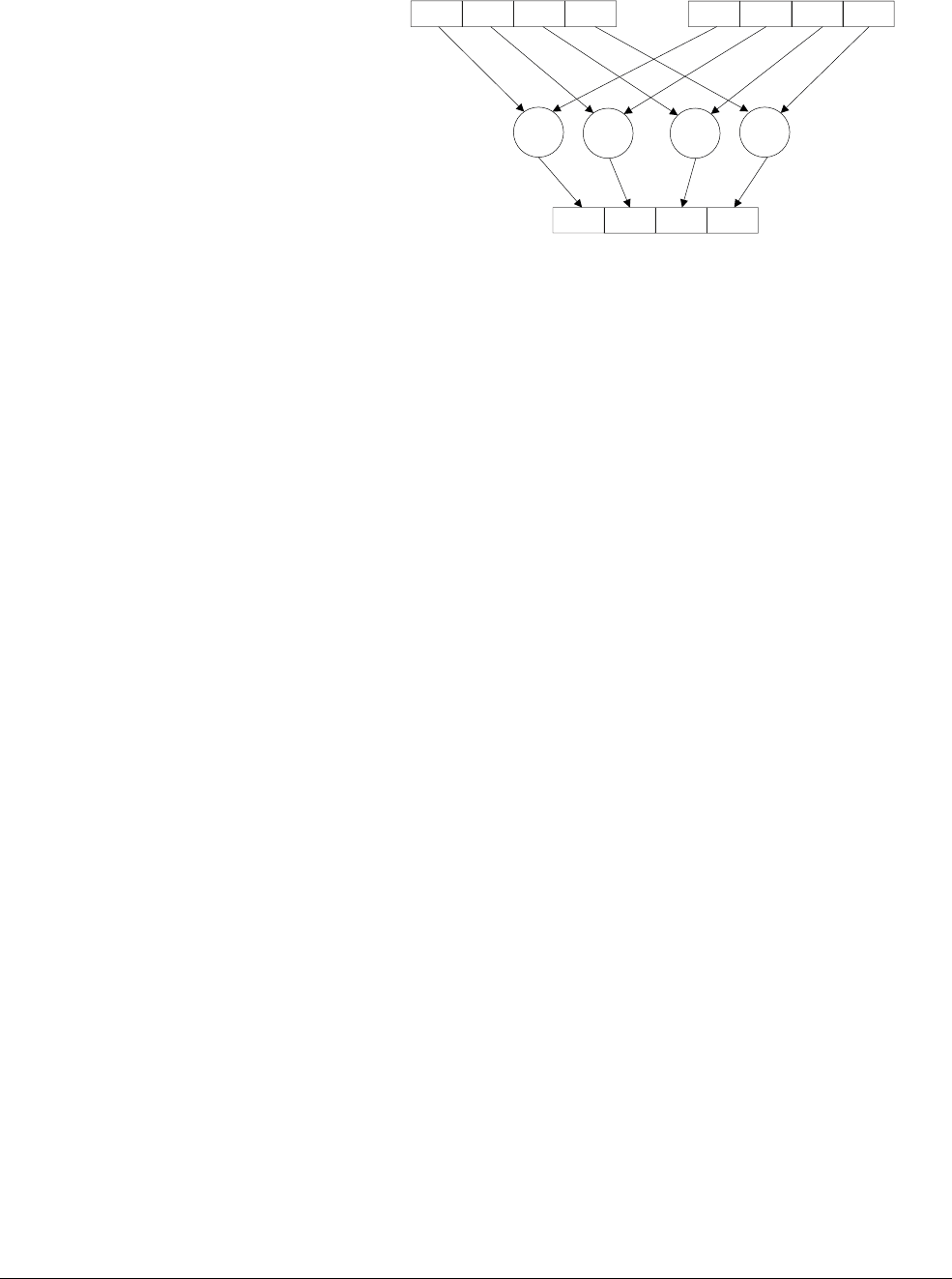

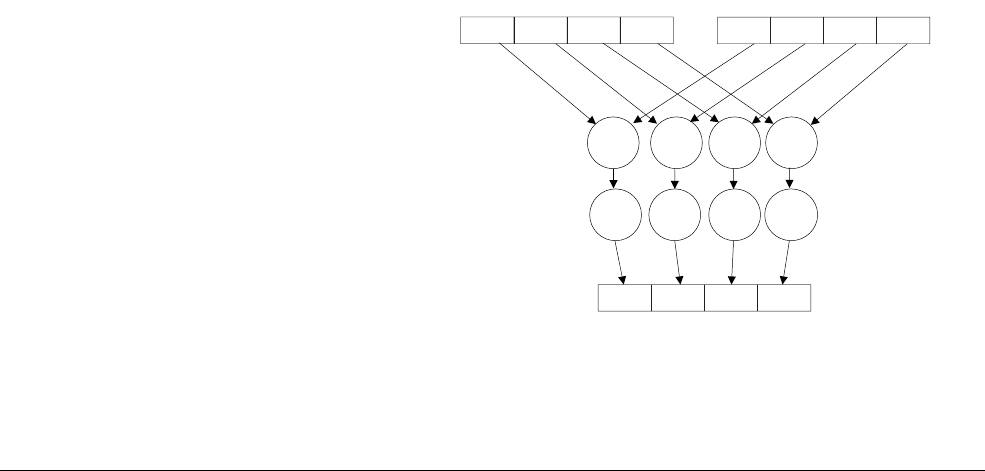

Figure 1-4 shows how the

VADD.I16

Q0, Q1, Q2

instruction performs a parallel addition of eight

lanes of 16-bit (8 x 16 = 128) integer (

I

) elements from vectors in Q1 and Q2, storing the result

in Q0.

Figure 1-4 8 way 16-bit integer add operation

127 112 111 96 95 80 79 64 63 48 47 32 31 16 15 0

Q register with

eight 16-bit lanes

63 56 55 48 47 40 39 32 31 24 23 16 15 8 7 0

D register with

eight 8-bit lanes

127 96 95 64 63 32 31 0

Q register with

four 32-bit lanes

63 48 47 32 31 16 15 0

D register with

four 16-bit lanes

127 112 111 96 95 80 79 64 63 48 47 32 31 16 15 0

127 112 111 96 95 80 79 64 63 48 47 32 31 16 15 0

Q2

Q1

Q0

Vector

Lane 6 Lane 5 Lane 4 Lane 3 Lane 2 Lane 1 Lane 0Lane 7

++ + + + + + +

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-12

ID071613 Non-Confidential

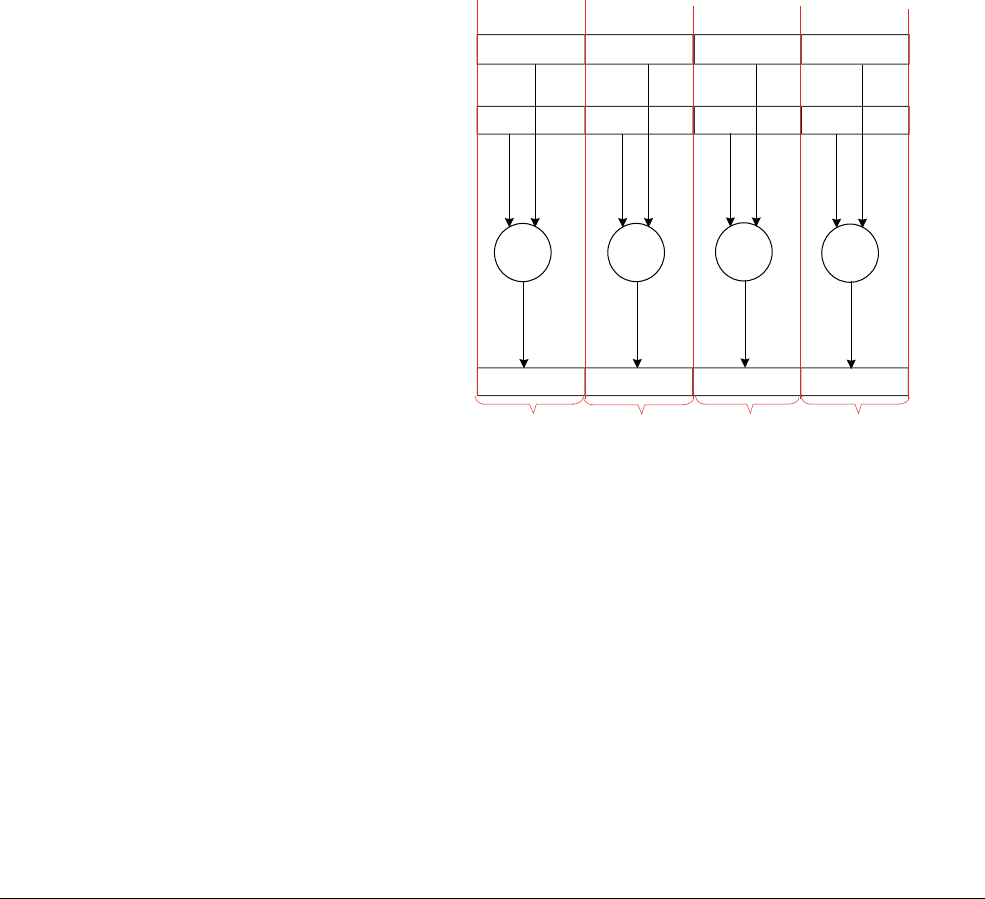

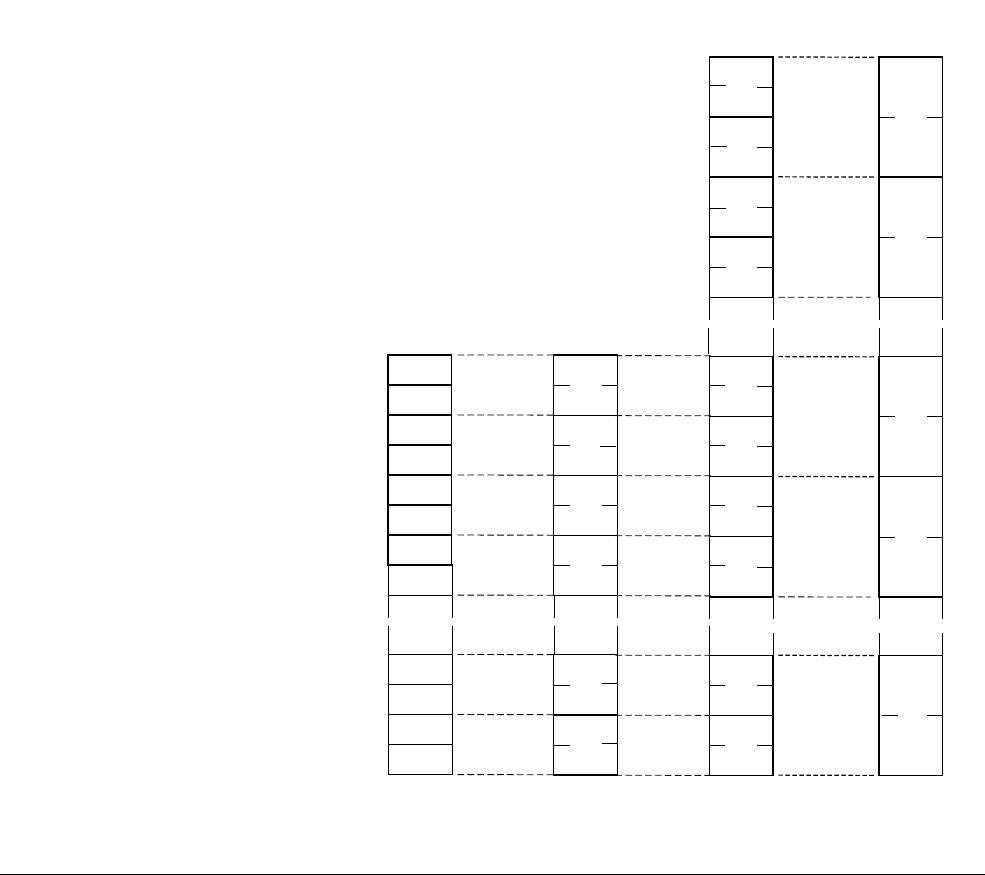

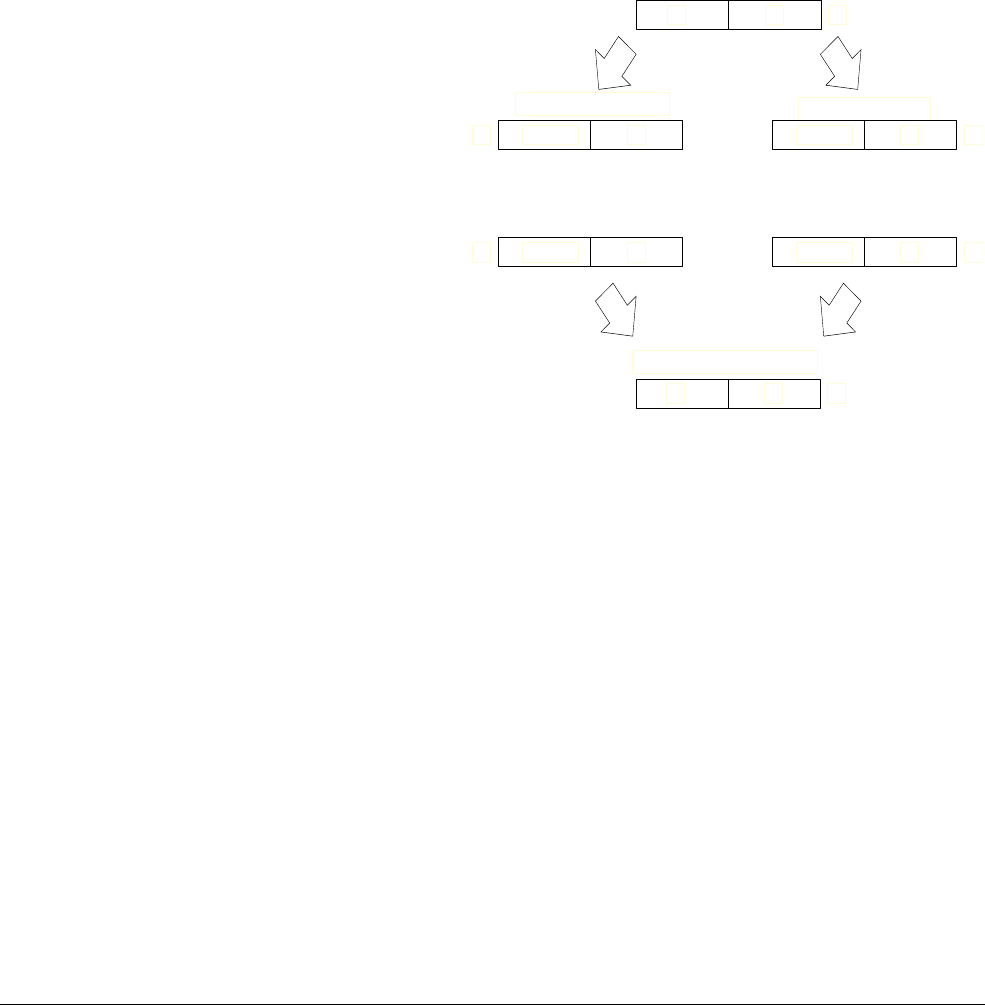

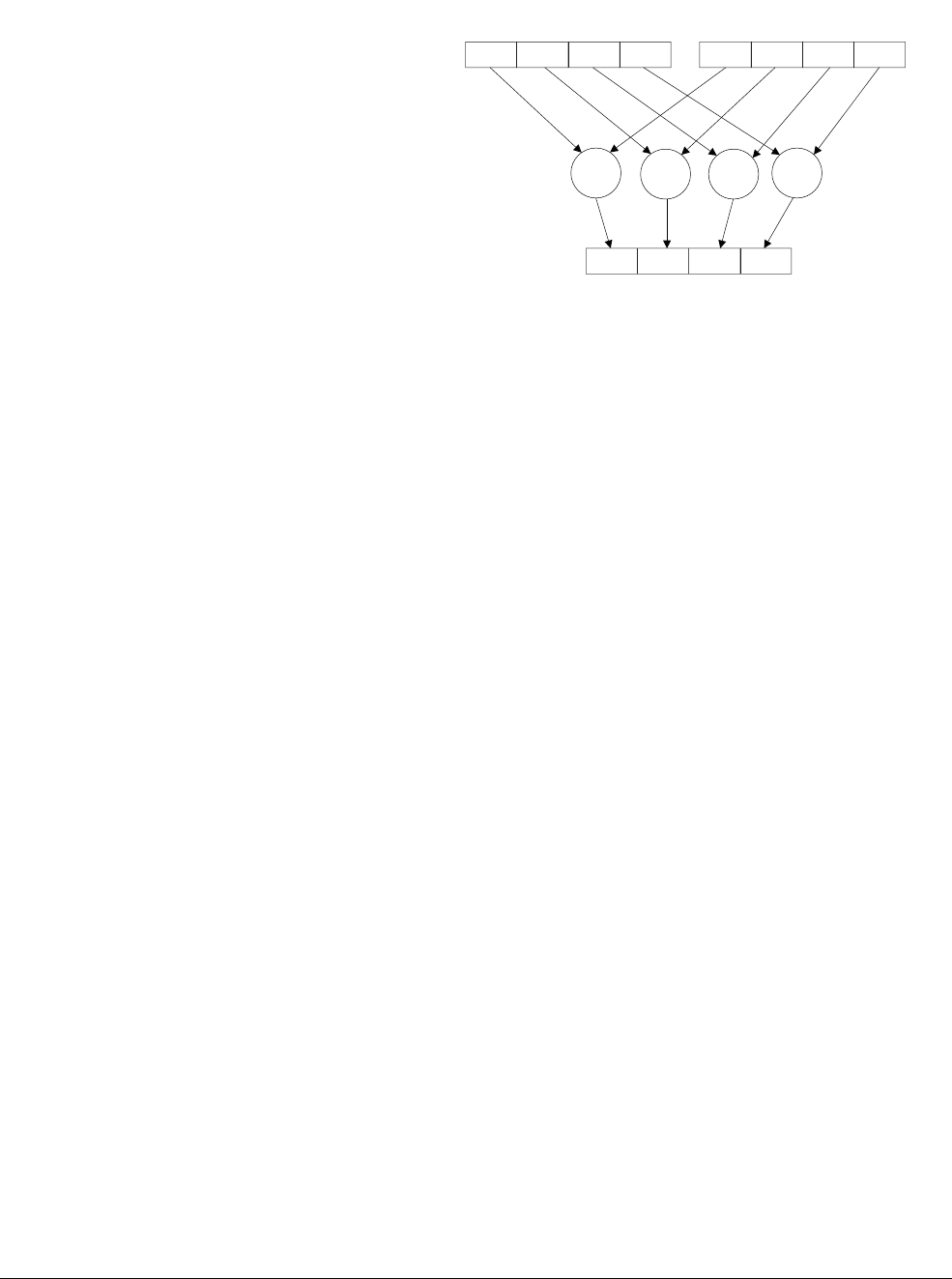

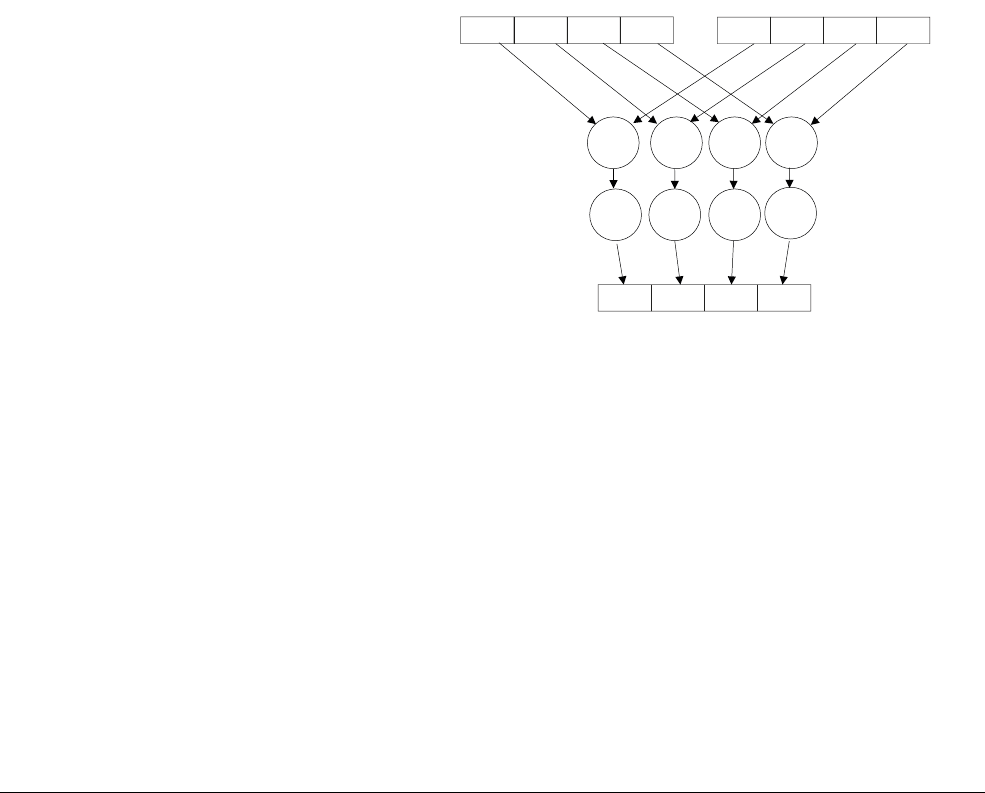

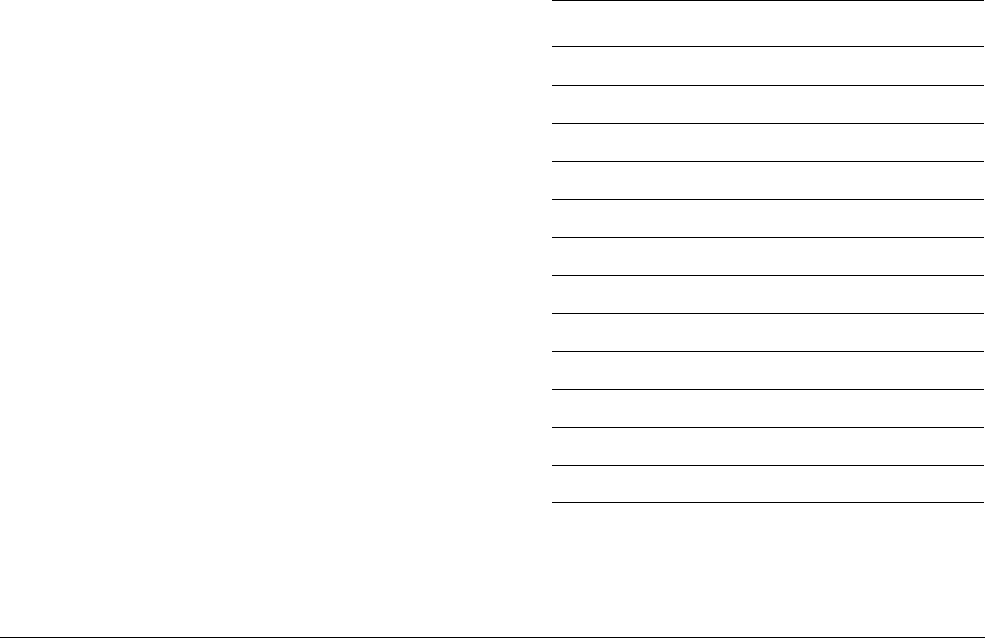

Register overlap

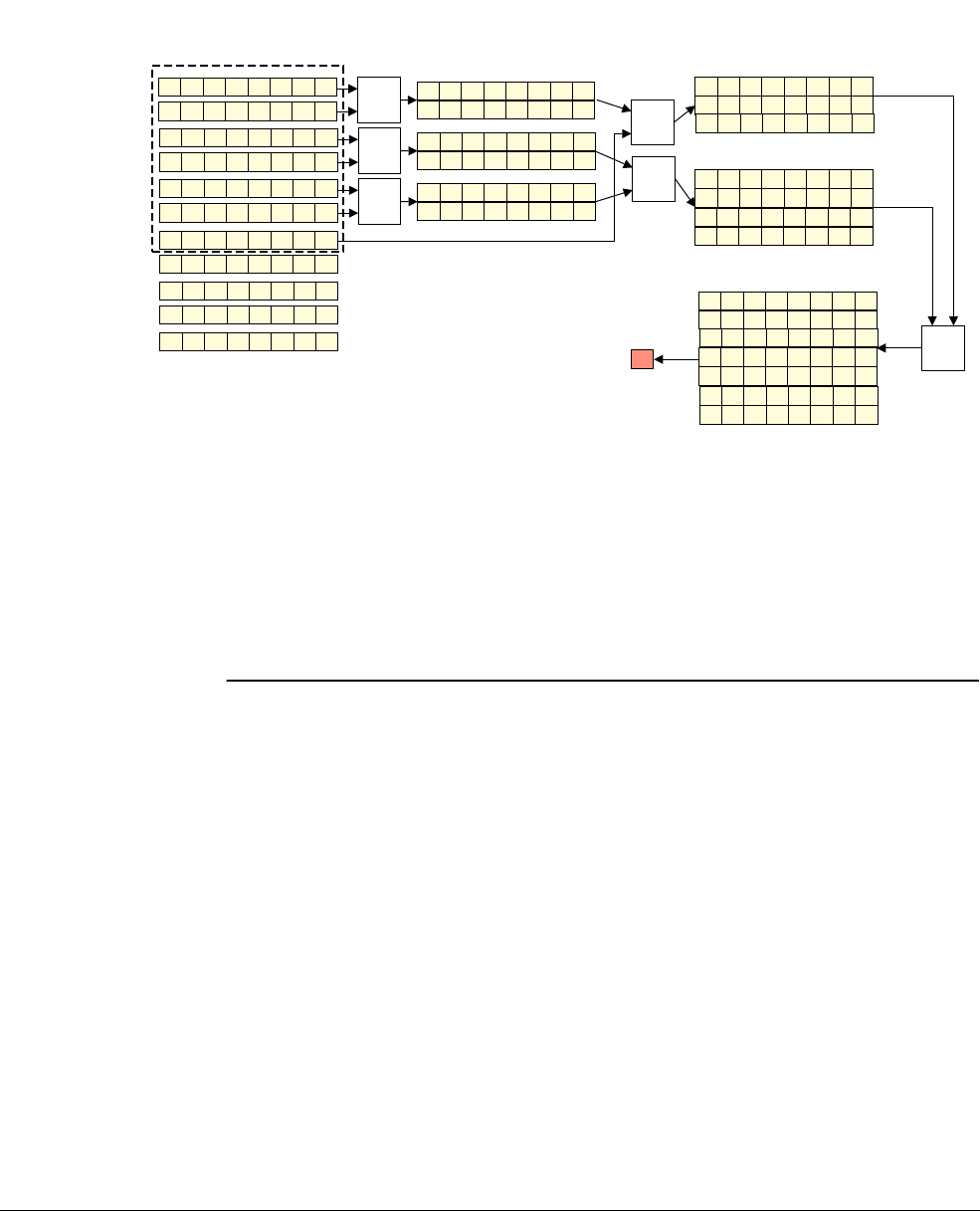

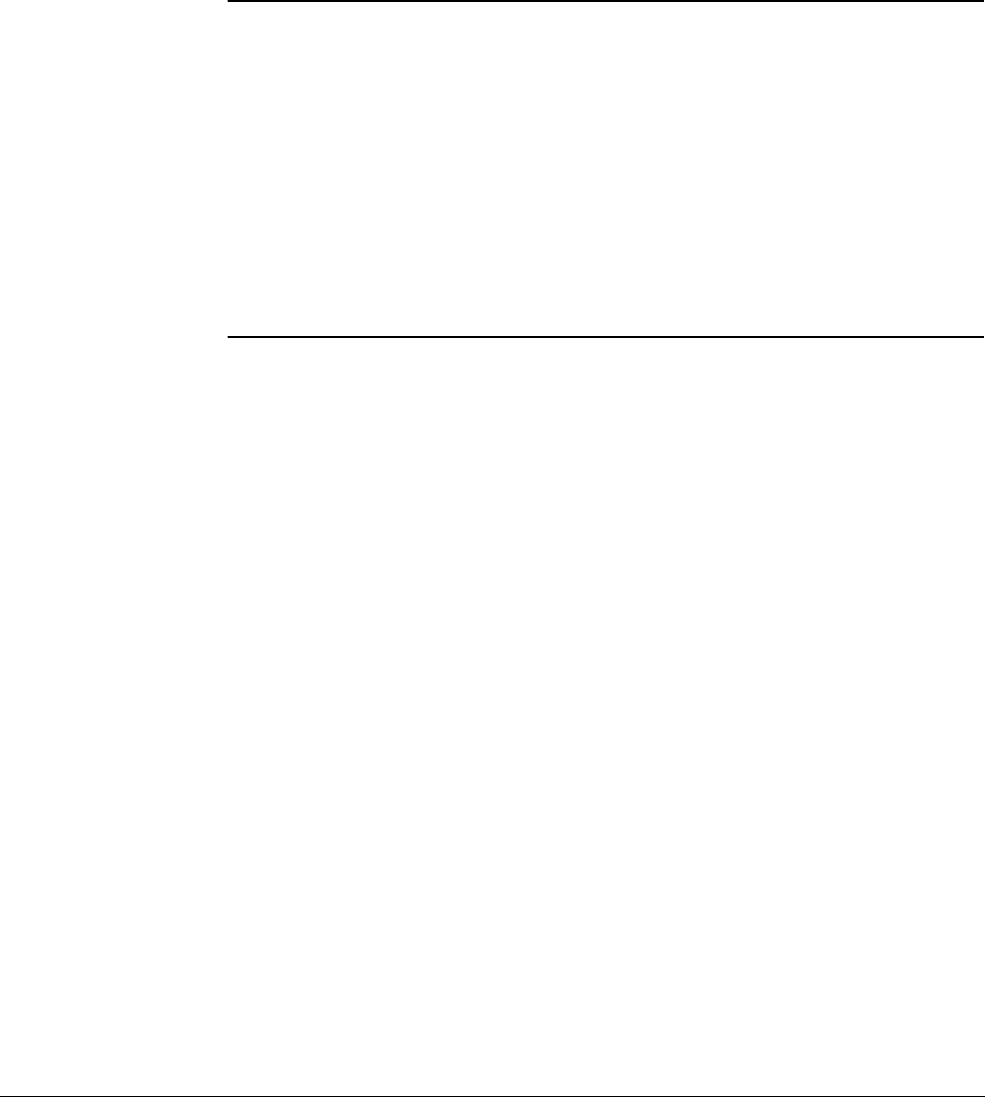

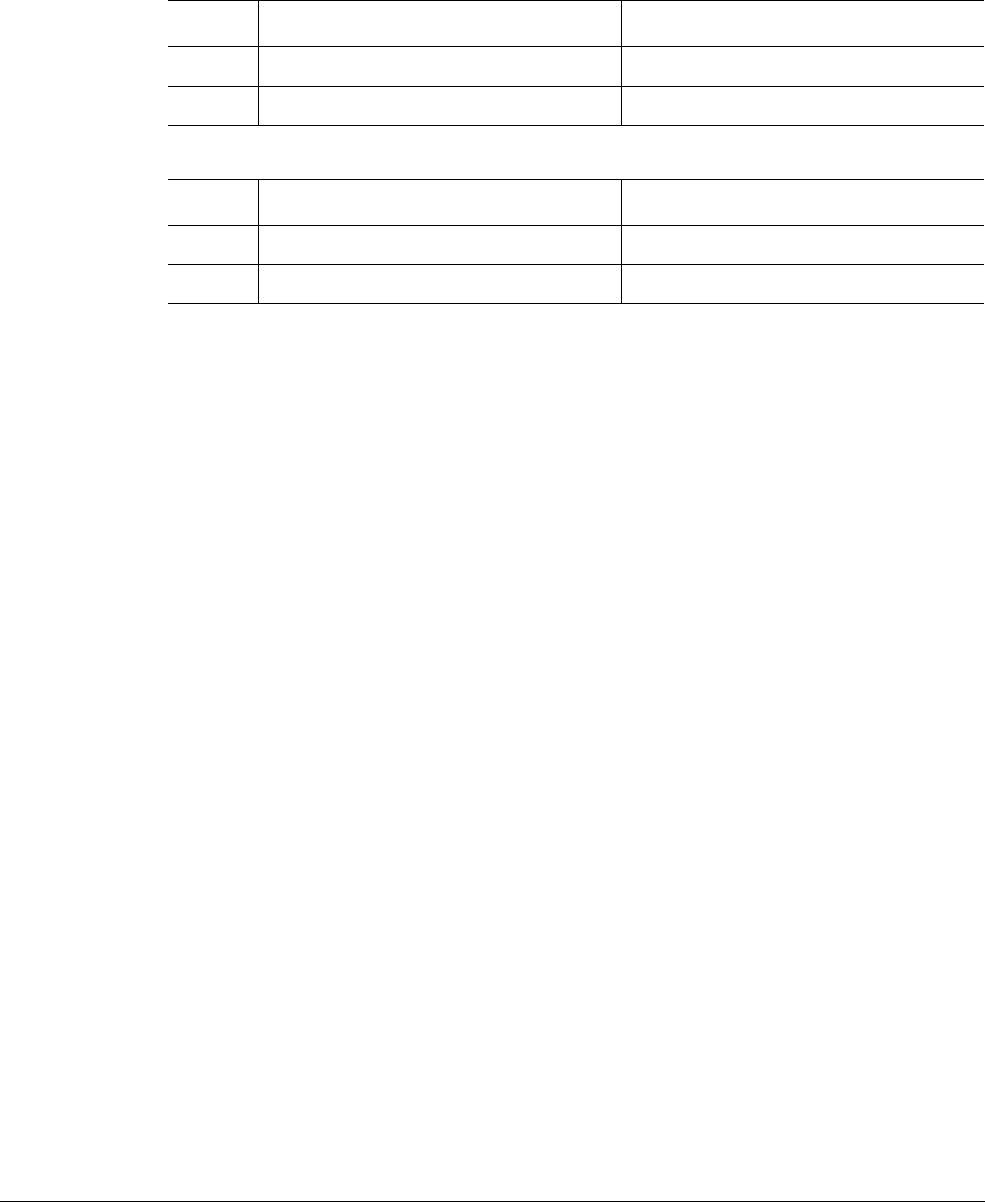

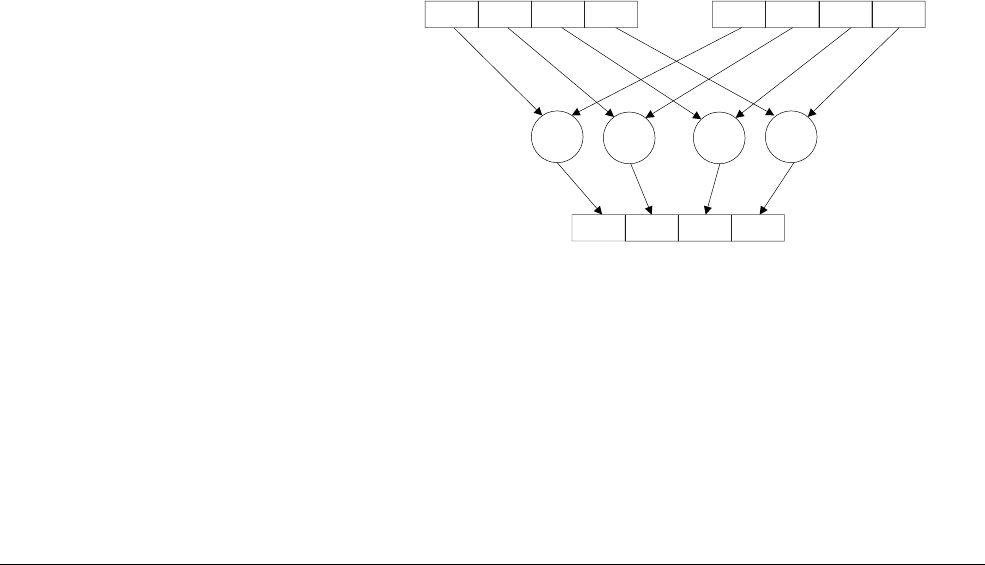

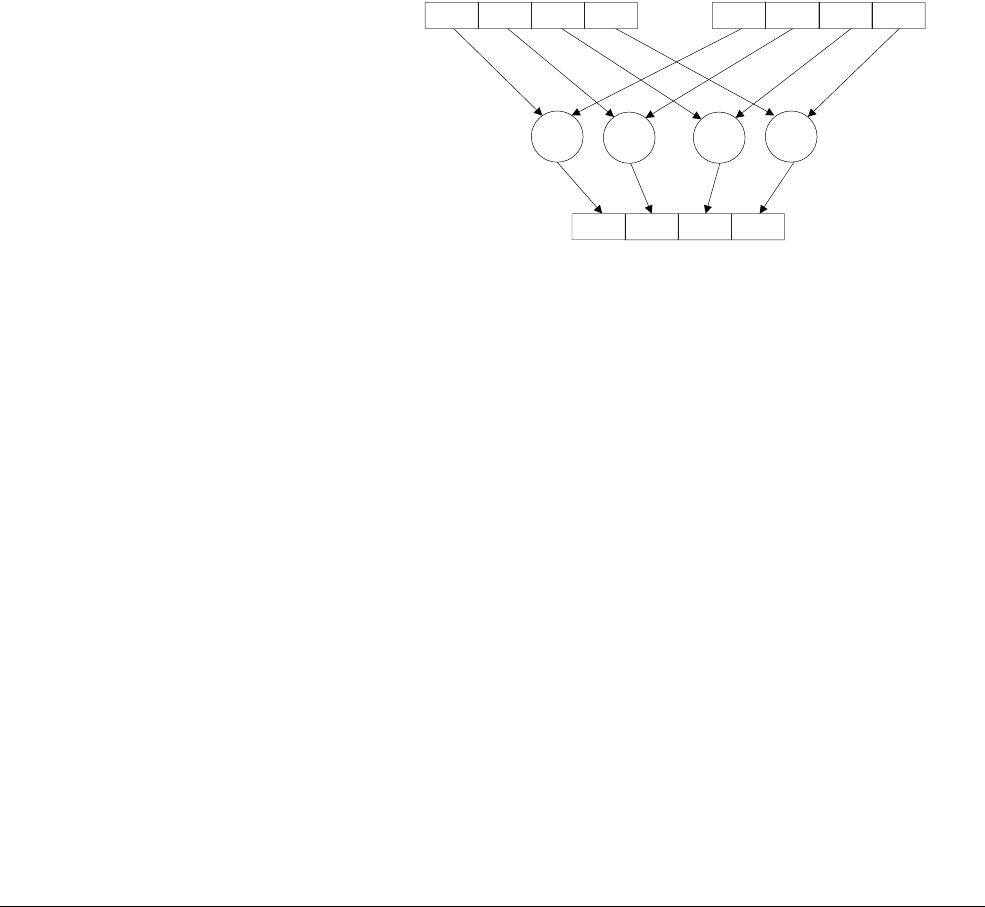

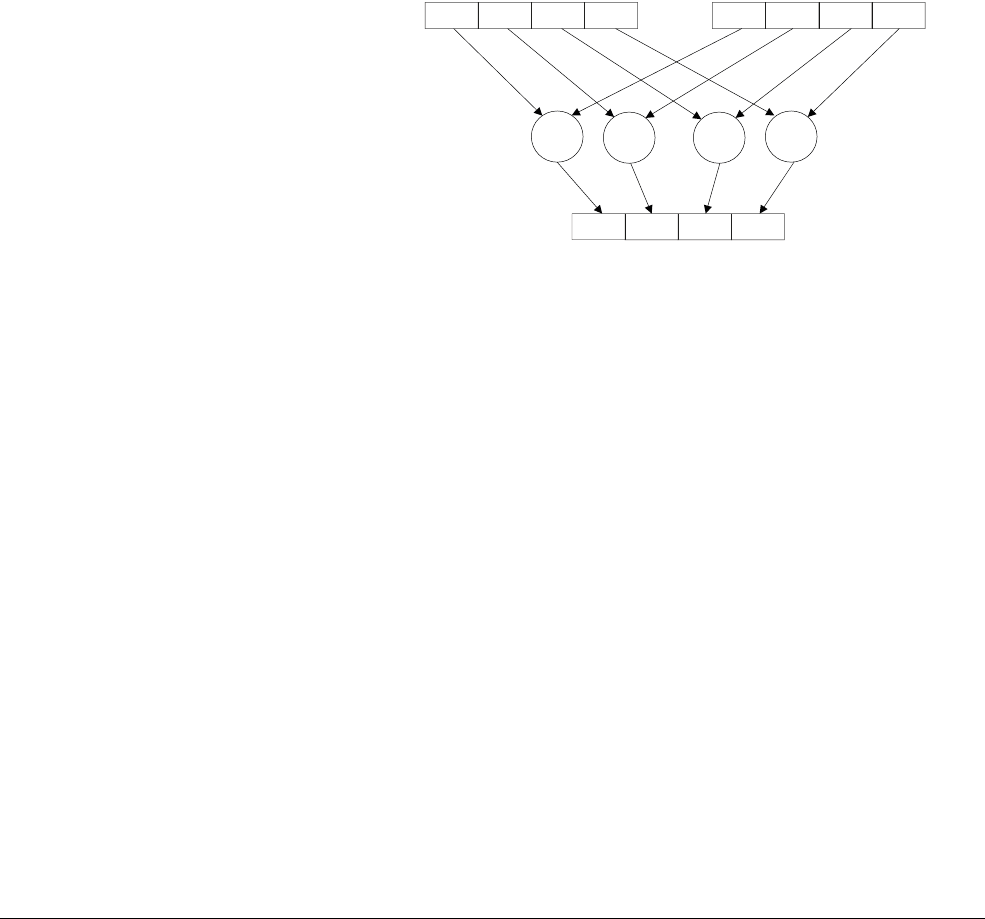

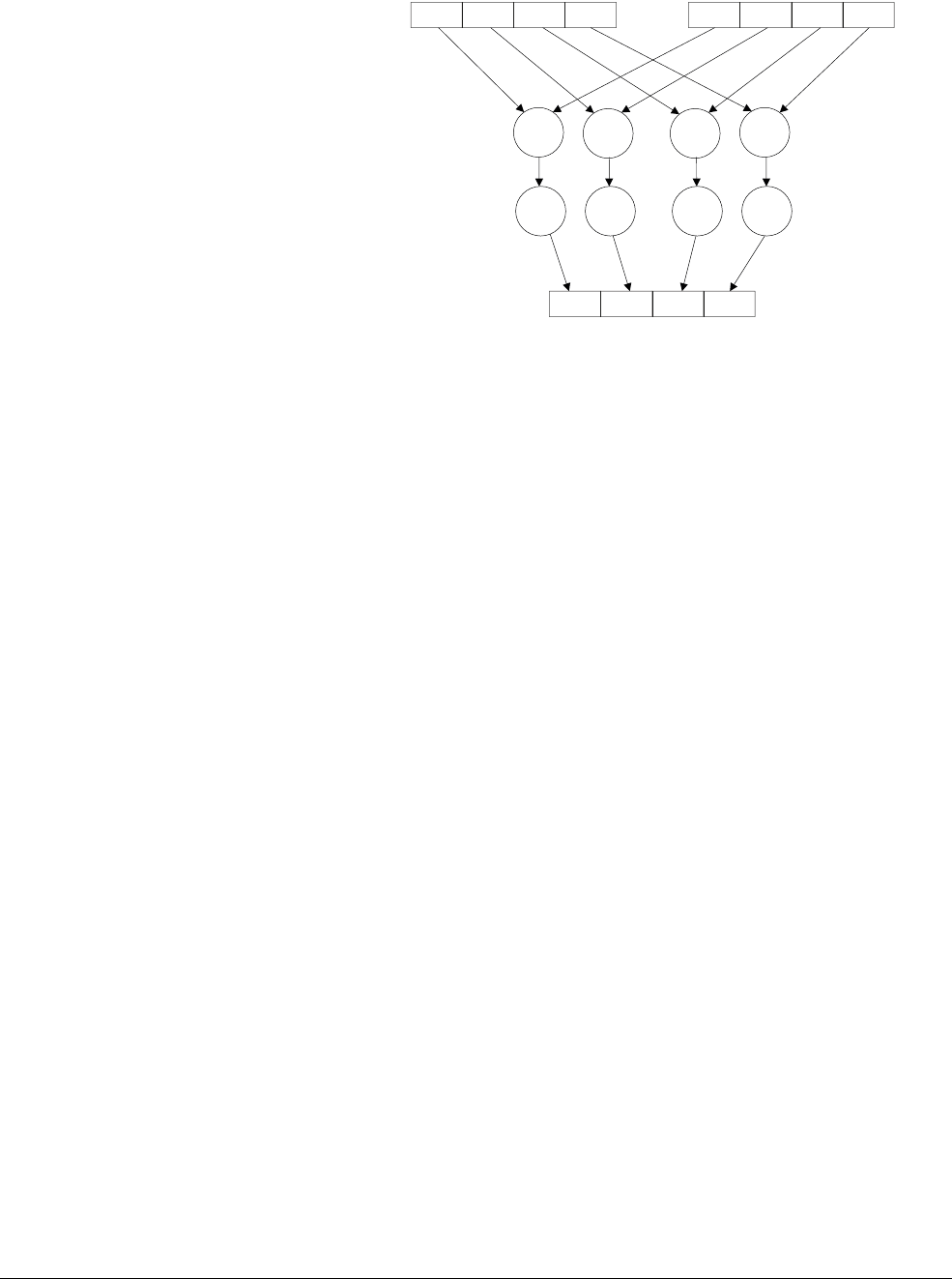

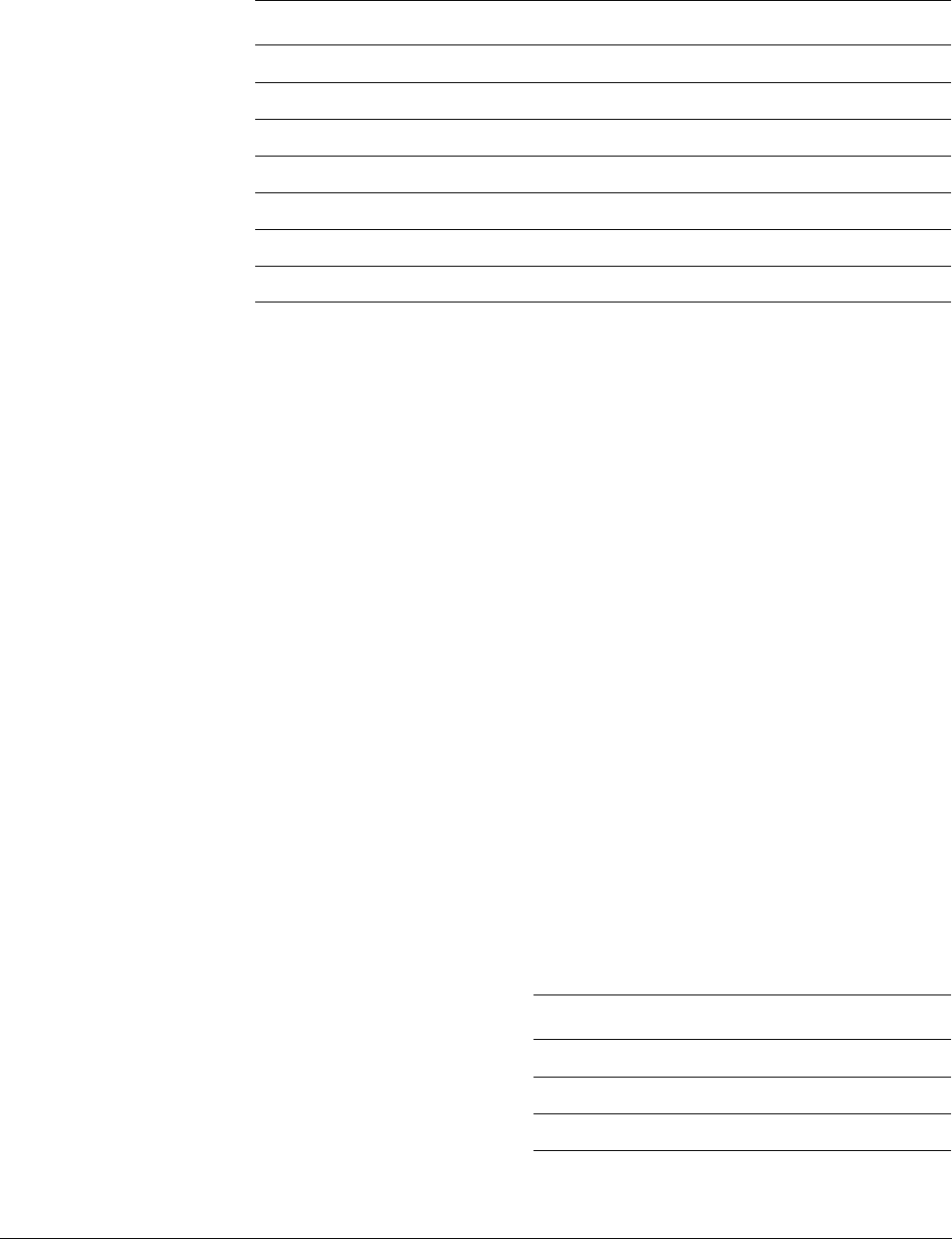

Figure 1-5 shows the NEON and floating-point register file and how the registers overlap.

The NEON unit views the register file as:

• Sixteen 128-bit Q, or quadword, registers,

Q0-Q15

.

• Thirty-two 64-bit D, or doubleword, registers,

D0-D31

. (Sixteen 64-bit D registers for

VFPv3-D16.)

The mapping for the D registers is:

—

D<2n>

maps to the least significant half of

Q<n>

—

D<2n+1>

maps to the most significant half of

Q<n>

.

• A combination of Q and D registers.

• The NEON unit cannot directly access the individual 32-bit VPF S registers. See VFP

views of the NEON and floating-point register file on page 1-15.

The mapping for the S registers is:

—

S<2n>

maps to the least significant half of

D<n>

—

S<2n+1>

maps to the most significant half of

D<n>.

Figure 1-5 NEON and floating-point register file

D0

D29

D31

D30

S3

S2

S24

S1

S0

...

D1

D28

D12

D13

D14

D15

...

Q0

Q6

Q7

Q15

...

...

...

~

~~

~~

~

~

~~

~~

~

~

~

~

~~

~~

~

S0-S31

VFP Only

D0

D1

D14

D15

...

~

~~

~

D0-D15

VFPv2 or

VFPv3-D16

D0-D31

VFPv3-D32

or NEON

Q0-Q15

NEON only

Q14

D13

D12

S25

S26

S27

S28

S29

S30

S31

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-13

ID071613 Non-Confidential

All of these registers are accessible at any time. Software does not have to explicitly switch

between them because the instruction used determines the appropriate view.

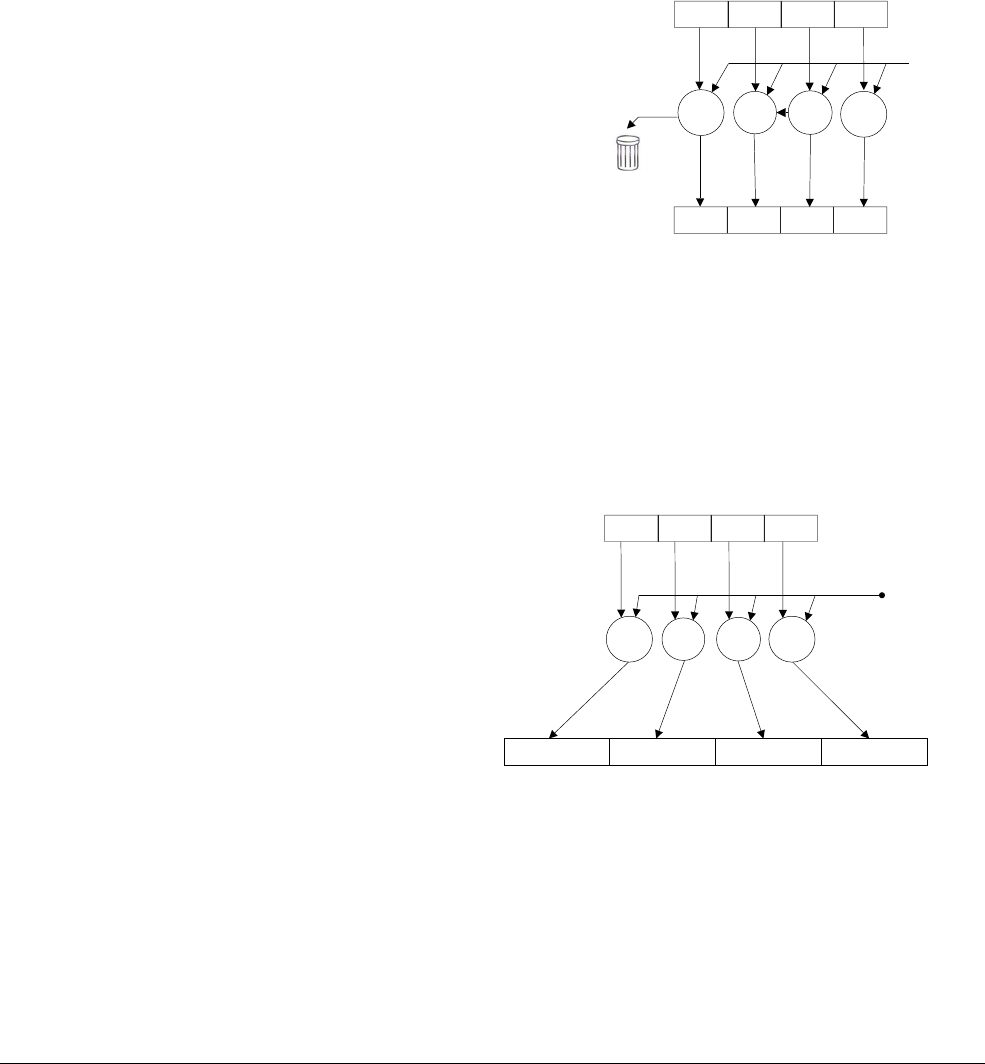

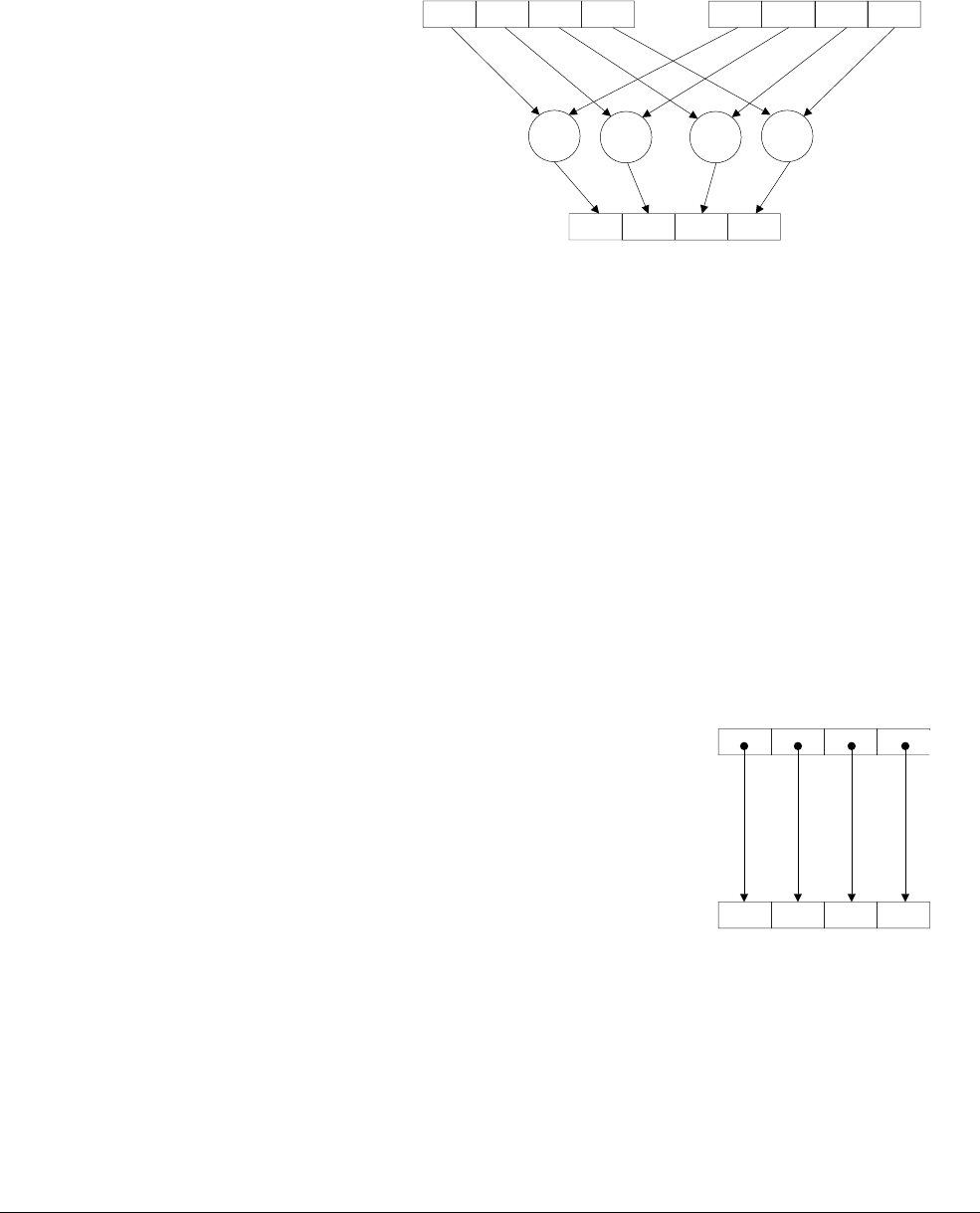

In Figure 1-6 the S, D, and Q registers are different views of the same register Q0:

• The NEON unit can access Q0 as an 128-bit register.

• The NEON unit can access Q0 as two consecutive 64-bit registers D0 and D1.

• The NEON unit cannot access the 32-bit S registers in Q0 individually.

If a VPF unit is present, it can however access them as S0, S1, S2, and S3.

Figure 1-6 Register overlap

Scalar data

Scalar refers to a single value instead of a vector containing multiple values. Some NEON

instructions use a scalar operand. A scalar inside a register is accessed by index into the vector

of values. The array notation to access individual elements of a vector is Dm[x] or Qm[x] where

x is the index in the vector Dm or Qm.

The instruction

VMOV.8 D0[3], R3

moves the least significant byte of register R3 into the fourth

byte in register D0.

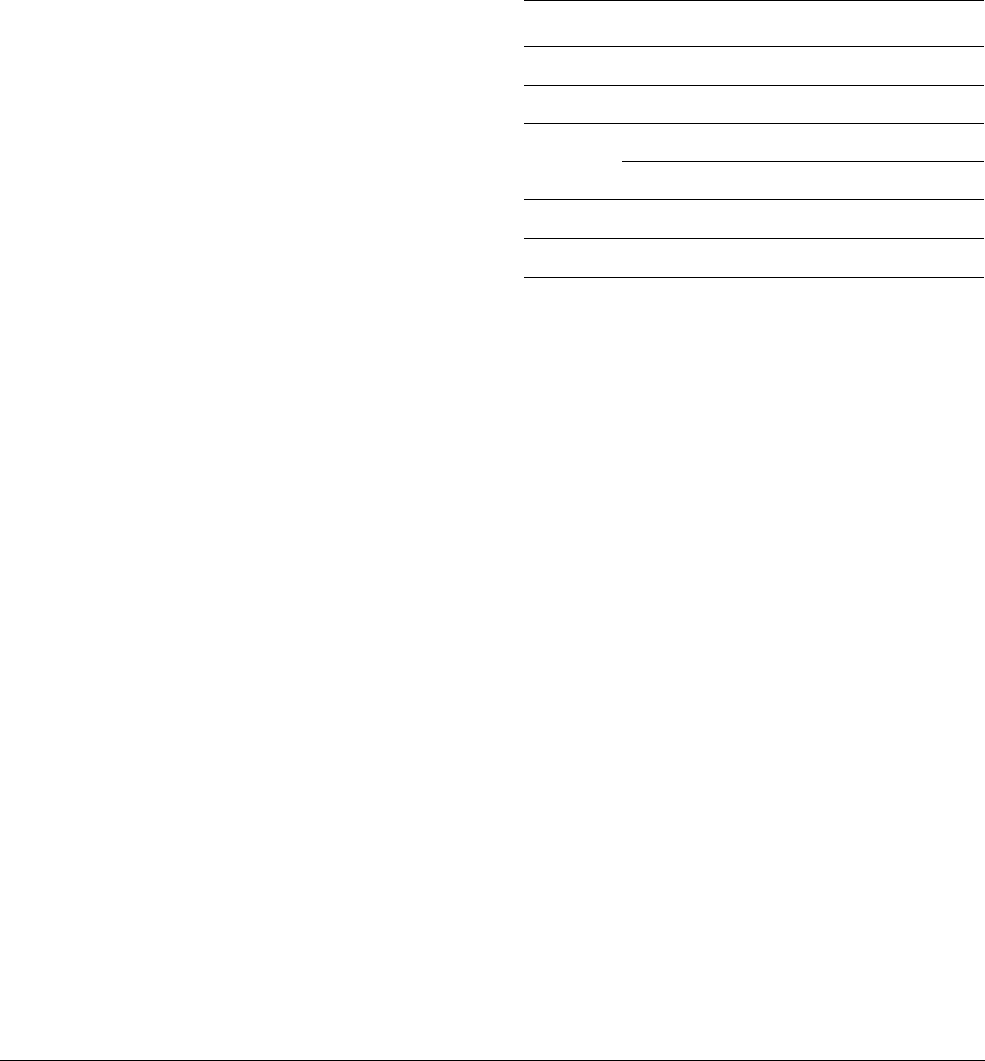

Figure 1-7 Moving a scalar to a lane

NEON scalars can be 8-bit, 16-bit, 32-bit, or 64-bit values. Other than multiply instructions,

instructions that access scalars can access any element in the register file.

Multiply instructions only allow 16-bit or 32-bit scalars, and can only access the first 32 scalars

in the register file:

• 16-bit scalars are restricted to registers D0[x]-D7[x], with x in the range 0 to 3

• 32-bit scalars are restricted to registers D0[x]-D15[x], with x either 0 or 1.

127 063 31

VFP only

VFP or NEON

NEON only

95 64 3296

S3 S2 S1 S0

D1 D0

Q0

L3

63 32 31 24 23 0

NEON register D0

31 8 7 0

ARM register R3

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-14

ID071613 Non-Confidential

1.4.2 NEON data type specifiers

The form and construction of NEON instructions is covered in Chapter 3 NEON Instruction Set

Architecture.

Although the ARM architecture does not require a processor to implement both VFP and NEON

technology, the common features in the programming for these extensions mean an operating

system that supports VFP requires little or no modifications to also support NEON technology.

However because the NEON unit is optional in some Cortex-A series processors, you cannot

rely on NEON code working on all processors.

Before using NEON or VFP instructions and compiling the code on a given processor, you must

check that the NEON or VFP unit is there! This is covered in Chapter 2 Compiling NEON

Instructions.

Data type specifiers in NEON and VFP instructions consist of a letter indicating the type of data,

usually followed by a number indicating the width. They are separated from the instruction

mnemonic by a point, for example,

VMLAL.S8

.

Table 1-3 shows the available NEON data types.

Note

The polynomial type is for operations that use power-of-two finite fields or simple polynomials

over {0,1}. These are described in Polynomials on page 3-17.

Table 1-3 NEON data types

8-bit 16-bit 32-bit 64-bit

Unsigned integer U8 U16 U32 U64

Signed integer S8 S16 S32 S64

Integer of unspecified type I8 I16 I32 I64

Floating-point number not available F16 F32 or F not available

Polynomial over {0,1} P8 P16 not available not available

Introduction

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 1-15

ID071613 Non-Confidential

1.4.3 VFP views of the NEON and floating-point register file

Processors that implement the ARMv7A and ARMV-7R architecture can optionally include one

of the following VFP extensions:

In version VFPv3-D16 and VPFv3-D16-FP16, the VFP unit views the NEON register file as:

• Sixteen 64-bit D registers

D0-D15

. The D registers are called double-precision registers

and contain double-precision floating-point values.

• Thirty-two 32-bit S registers

S0-S31

. The S registers are called single-precision registers

and contain single-precision floating-point values or 32-bit integers.

For VPFv3-D16-F16, the S registers can contain a half-precision floating-point value.

• A combination of registers from the above views.

In versions VFPv3, VFPv3-D32, and VFPv3-D32-FP16, the VFP unit views the NEON register

file as:

• Thirty-two 64-bit D registers,

D0-D31

.

• Thirty-two 32-bit S registers,

S0-S31

. The registers D0-D15 overlap S registers S0-S31.

For VPFv3-D-32-F16, the S registers can contain a half-precision floating-point value.

• A combination of registers from the above views.

Note

• The different views means half-precision, single-precision, and double-precision values,

and NEON vectors to coexist in different non-overlapped registers at the same time.

• You can also use the same overlapped registers to store half-precision, single-precision,

and double-precision values, and NEON vectors at different times.

Table 1-5 shows the available data types for VFP instructions.

See VFP instructions on page C-67 for a description of the instructions specific to the VFP unit.

Table 1-4 VFPv3 variants

Number of 64-bit D registers With half-precision extension Without half-precision extension

Sixteen VFPv3-D16-FP16 VFPv3-D16

Thirty-two VFPv3-D32-FP16

(Also called VFPv4 if the fused

multiply-add extension is present)

VFPv3-D32

(Sometimes called just VFPv3 if there is

no possibility of confusion with other

extensions)

Table 1-5 VFP data types

16-bit 32-bit 64-bit

Unsigned integer U16 U32 not available

Signed integer S16 S32 not available

Floating point number F16 F32 (or F) F64 (or D)

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-1

ID071613 Non-Confidential

Chapter 2

Compiling NEON Instructions

This chapter describes how code targeted at NEON hardware can be written in C or assembly

language, and the range of tools and libraries are available to support this. It contains the

following topics:

•Vectorization on page 2-2

•Generating NEON code using the vectorizing compiler on page 2-9

•Vectorizing examples on page 2-11

•NEON assembler and ABI restrictions on page 2-17

•NEON libraries on page 2-19

•Intrinsics on page 2-20

•Detecting presence of a NEON unit on page 2-21

•Writing code to imply SIMD on page 2-22

•GCC command line options on page 2-24

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-2

ID071613 Non-Confidential

2.1 Vectorization

NEON was designed as an additional load/store architecture to provide good vectorizing

compiler support for languages such as C/C++. This enables a high level of parallelism. You can

hand-code NEON instructions for applications that need very high performance. It includes low

cost promotion and demotion of data sizes. It also includes structure loads capable of accessing

multiple data streams which are interleaved in memory.

NEON instructions can be written as part of the normal ARM code. This makes NEON

programming simpler and more efficient than with an external hardware accelerator. There are

NEON instructions available to read and write external memory, move data between NEON

registers and other ARM registers and to perform SIMD operations.

All compiled code and subroutines will conform to the EABI, which specifies which registers

can be corrupted and which registers must be preserved.

A vectorizing compiler can take your C or C++ source code and vectorize it in a way that

enables efficient usage of NEON hardware. This means you can write portable C code, while

still obtaining the levels of performance made possible by NEON instructions.

To assist vectorization, make the number of loop iterations a multiple of the vector length. Both

GCC and ARM Compiler toolchain have options for enabling automatic vectorization for

NEON technology, but because the C and C++ standards do not cover the concurrency aspects,

you might have to provide the compiler with additional information to get full benefit. The

required source code modifications are part of the standard language specifications, so they do

not affect code portability between different platforms and architectures.

The vectorizing compiler works best when it can determine the intention of the programmer.

Simple code that is easy for a human to understand is much easier to vectorize than code highly

tuned for a specific processor.

2.1.1 Enabling auto-vectorization in ARM Compiler toolchain

The ARM Compiler toolchain in DS-5™ Professional includes support for the vectorizing

compiler. To enable automatic vectorization you must target a processor that has a NEON unit.

The required command line options are:

--vectorize

Enable vectorization

--cpu 7-A

or

--cpu Cortex-A8

Specify a core or architecture with NEON support

-O2

or

–O3

Select high level or aggressive optimization

-Otime

Optimize for speed rather than for space.

Use the

armcc

command line parameter

--remarks

to provide more information about the

optimizations performed, or problems preventing the compiler from performing certain

optimizations.

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-3

ID071613 Non-Confidential

2.1.2 Enabling auto-vectorization in GCC compiler

To enable automatic vectorization in GCC, use the command line options:

•

-ftree-vectorize

•

–mfpu=neon

•

-mcpu

to specify the core or architecture.

Compiling at optimization level

-O3

implies

-ftree-vectorize

.

If you do not specify an

-mcpu

option, then GCC will use its built-in default core. The resulting

code might run slowly or not run at all.

The option

-ftree-vectoriz

e is available for many architectures that support SIMD operations.

2.1.3 C pointer aliasing

A major challenge in optimizing Standard C (ISO C90) is because you can de-reference pointers

which might (according to the standard) point to the same or overlapping datasets.

As the C standard evolved, this issue was addressed by adding the keyword

restrict

to C99 and

C++. Adding

restrict

to a pointer declaration is a promise that only this pointer will access the

address it is pointing to. This enables the compiler to do the work in setup and exit restrictions,

preload data with plenty of advance notice, and cache the intermediate results.

The ARM Compiler allows the use of the keyword

__restrict

in all modes. If you specify the

command line option

--restrict

, you can use the keyword

restrict

without the leading

underscores. GCC has similar options. See the GCC documentation for more information.

2.1.4 Natural types

Often algorithms are written to expect certain types for legacy, memory size or peripheral

reasons. It is common to cast these up to the natural type for the processor as mathematical

operations on natural sized data are usually faster, and truncation and overflow are only

calculated when data is passed or stored.

2.1.5 Array grouping

For processor designs that have few registers for storing memory pointers (such as x86), it is

common to group several arrays into one. This permits several different offsets from the same

pointer to access to different parts of the data. Grouping arrays in this way can confuse the

compiler into thinking that the offsets cause overlapping datasets. Avoid this unless you can

guarantee that there are no writes into the array. Split composite arrays into individual arrays to

simplify pointer use and remove this risk.

2.1.6 Inside knowledge

To turn an array with no size information into NEON code, the compiler must assume the size

might be anywhere between 0 and 4GB. Without additional information the compiler must

generate setup code which tests if the array is too small to consume a whole NEON register as

well as cleanup code which consumes the last few items in the array using the scalar pipeline.

In some cases array sizes are known at compile time and should be specified directly rather than

passed as arguments. In other cases, it is common for the engineer to know more about the array

layouts than the compiler. For example, arrays are often expressed as powers of 2. A

programmer might know that a loop iteration count will always be a multiple of 2, 4, 8, 16, 32

and so on. It is possible to write code to exploit this. See Optimizing for vectorization on

page 2-6 and Adding inside knowledge on page 8-24 for more information.

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-4

ID071613 Non-Confidential

2.1.7 Enabling the NEON unit in bare-metal applications

A bare-metal application is one that runs directly on the hardware without a kernel or operating

system support.

The NEON unit is disabled at reset by default, so you must enable it manually for a bare metal

application that requires NEON instructions. The

EnableNEON

code snippet shows how to enable

the NEON unit manually.

#include <stdio.h>

// Bare-minimum start-up code to run NEON code

__asm void EnableNEON(void)

{

MRC p15,0,r0,c1,c0,2 // Read CP Access register

ORR r0,r0,#0x00f00000 // Enable full access to NEON/VFP by enabling access to

// Coprocessors 10 and 11

MCR p15,0,r0,c1,c0,2 // Write CP Access register

ISB

MOV r0,#0x40000000 // Switch on the VFP and NEON hardware

MSR FPEXC,r0 // Set EN bit in FPEXC

}

When compiling a bare-metal application for a processor with a NEON unit, the compiler might

use NEON instructions. For example the ARM Compiler toolchain

armcc

uses

-O2

optimization

by default, which tries to vectorize code for a processor with a NEON unit if

-Otime

and

--vectorize

options are specified.

You can compile the bare metal application,

hello.c

, as:

armcc -c --cpu=Cortex-A8 --debug hello.c -o hello.o

armlink --entry=EnableNEON hello.o -o hello.axf

2.1.8 Enabling the NEON unit in a Linux stock kernel

A stock kernel is the kernel released by Linux at www.kernel.org, without modification. If you

use a Linux stock kernel to run your application, there is no need to manually enable the NEON

unit. The kernel automatically enables the NEON unit when it encounters the first NEON

instruction.

If the NEON unit is disabled and the application tries to execute a NEON instruction, it throws

an Undefined Instruction exception. The kernel uses this exception to enable the NEON unit and

then executes the NEON instruction. The NEON unit remains enabled until there is a context

switch. When a context switch is required, the kernel might disable the NEON unit to save time

and power.

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-5

ID071613 Non-Confidential

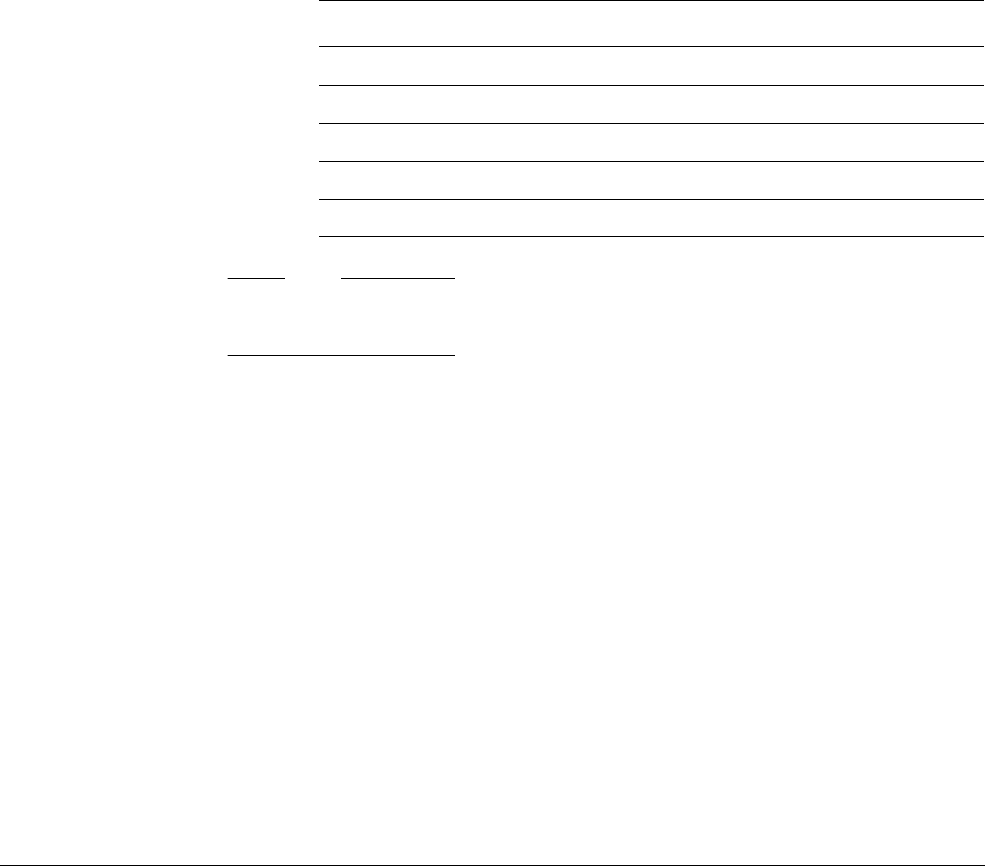

2.1.9 Enabling the NEON unit in a Linux custom kernel

If you use a Linux custom kernel to run your application, you must enable the NEON unit. To

enable the NEON unit, you must use the kernel configuration settings to select:

•Floating point emulation → VFP-format floating point maths

•Floating point emulation → Advanced SIMD (NEON) Extension support.

Figure 2-1 shows the configuration settings for a Versatile Express board.

Figure 2-1 Configuration of a custom kernel

If

/proc/config.gz

is present, you can test for NEON support in the kernel using the command:

zcat /proc/config.gz | grep NEON

If the NEON unit is present, the command outputs:

CONFIG_NEON=y

To ensure that the processor supports the NEON extension, you can issue the command:

cat /proc/cpuinfo | grep neon

If it supports the NEON extension, the output shows

neon

, for example:

Features : swp half thumb fastmult vfp edsp neon vfpv3 tls vfpv4 idiva idivt

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-6

ID071613 Non-Confidential

2.1.10 Optimizing for vectorization

The C and C++ languages do not provide syntax that specifies concurrent behavior, so compilers

cannot safely generate parallel code. However, the developer can provide additional information

to let the compiler know where it is safe to vectorize.

Unlike intrinsics, these modifications are not architecture dependent, and are likely to improve

vectorization on any target platform. These modifications usually do not have negative impact

on performance on targets where vectorization is not possible.

The following describe the main rules:

• Short, simple loops work best (even if it means multiple loops in your code).

• Avoid using a break statement to exit a loop.

• Try to make the number of iterations a power of two.

• Try to make sure the number of iterations is known to the compiler.

• Functions called inside a loop should be inlined.

• Using arrays with indexing vectorizes better than using pointers.

• Indirect addressing (multiple indexing or dereferencing) does not vectorize.

•Use the

restrict

keyword to tell the compiler that pointers do not reference overlapping

areas of memory.

Indicate knowledge of number of loop iterations

If a loop has a fixed iteration count, or if you know that the iteration count is always a power of

2, making this obvious to the compiler enables the compiler to perform optimizations that would

otherwise be unsafe or difficult.

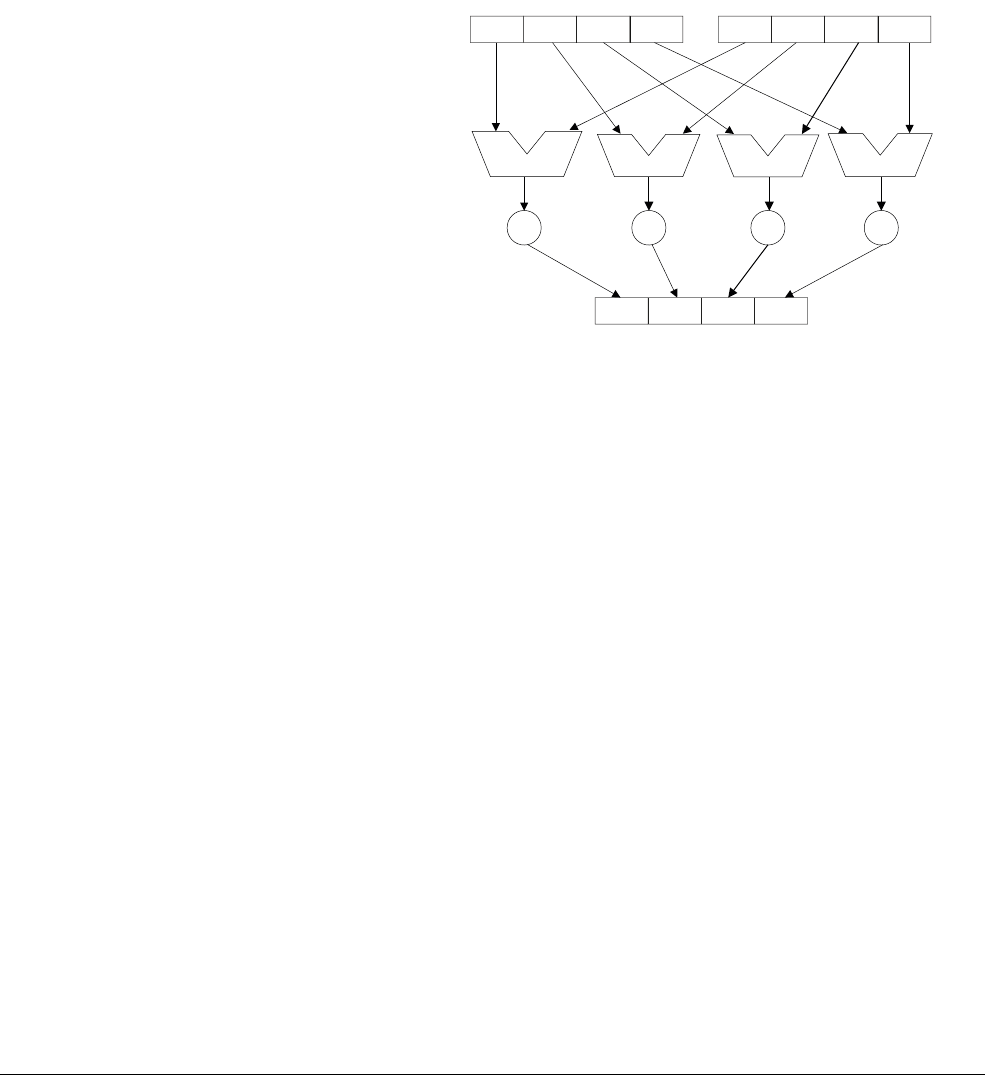

Example 2-1 shows a function accumulating a number (

len

) of

int

-sized elements. If you know

that the value passed as

len

is always a multiple of four, you can indicate this to the compiler by

masking off the bottom two bits when comparing the loop counter to

len

. This ensures that the

loop always executes a multiple of four times. Therefore the compiler can safely vectorize and:

• does not need to add code for runtime checks on

len

• does not need to add code to deal with over-hanging iterations.

Example 2-1 Specifying that the loop counter is a multiple of 4

int accumulate(int * c, int len)

{

int i, retval;

for(i = 0, retval = 0; i < (len & ~3) ; i++)

{

retval = retval + c[i]

}

return retval;

}

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-7

ID071613 Non-Confidential

Avoid loop-carried dependencies

If your code contains a loop where the result of one iteration is affected by the result of a

previous iteration, the compiler cannot vectorize it. If possible, restructure the code to remove

any loop-carried dependencies.

Use the

restrict

keyword

C99 introduced the

restrict

keyword, that you can use to inform the compiler that the location

accessed through a specific pointer is not accessed through any other pointer within the current

scope.

Example 2-2 shows a situation where using restrict on a pointer to a location being updated

makes vectorization safe when it otherwise would not be.

Example 2-2

int accumulate2(char * c, char * d, char * restrict e, int len)

{

int i;

for(i=0 ; i < (len & ~3) ; i++)

{

e[i] = d[i] + c[i];

}

return i;

}

Without the

restrict

keyword, the compiler must assume that

e[i]

can refer to the same

location as

d[i + 1]

, meaning that the possibility of a loop-carried dependency prevents it from

vectorizing this sequence. With

restrict

, the programmer informs the compiler that any

location accessed through

e i

s only accessed through pointer e in this function. This means the

compiler can ignore the possibility of aliasing and vectorize the sequence.

Using the

restrict

keyword does not enable the compiler to perform additional checks on the

function call. Hence, if the function is passed values for

c

or

d

that overlap with the value for

e

,

the vectorized code might not execute correctly.

Both GCC and ARM Compiler toolchain support the alternative forms

__restrict__

and

__restrict

when not compiling for C99. ARM Compiler toolchain also supports using the

restrict

keyword with C90 and C++ when

--restrict

is specified on the command line.

Avoid conditions inside loops

Normally, the compiler cannot vectorize loops containing conditional statements. In the best

case, it duplicates the loop, but in many cases it cannot vectorize it at all.

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-8

ID071613 Non-Confidential

Use suitable data types

When optimizing some algorithms operating on 16-bit or 8-bit data without SIMD, sometimes

you get better performance if you treat them as 32-bit variables. When producing software

targeting automatic vectorization, for best performance always use the smallest data type that

can hold the required values. This means a NEON register can hold more data elements and

execute more operations in parallel. In a given period, the NEON unit can process twice as many

8-bit values as 16-bit values.

Also, NEON technology does not support some data types, and some are only supported for

certain operations. For example, it does not support double-precision floating-point, so using a

double-precision double where a single-precision float is sufficient can prevent the compiler

from vectorizing code. NEON technology supports 64-bit integers only for certain operations,

so avoid using

long long

variables where possible.

Note

NEON technology includes a group of instructions that can perform structured load and store

operations. These instructions can only be used for vectorized access to data structures where

all members are of the same size.

Floating-point vectorization

Floating-point operations can result in loss of precision. The order of the operations or

floating-point inputs can be arranged to reduce the loss in precision. Changing the order of the

operations or inputs can result in further loss in precision. Hence some floating-point operations

are not vectorized by default because vectorizing can change the order of the operations. If the

algorithm does not require this level of precision, you can specify

--fpmode=fast

, for armcc, or

-ffast-math

, for GCC, on the command line to enable these optimizations.

Example 2-3 shows a sequence that can only be vectorized with one of these parameters

specified. In this case, it performs parallel accumulation, potentially reducing the precision of

the result.

Example 2-3

float g(float const *a)

{

float r = 0;

int i;

for (i = 0 ; i < 32 ; ++i)

r += a[i];

return r;

}

The NEON unit always operates in Flush-to-Zero mode (see Flush-to-zero mode on page 3-13),

making it non-compliant with IEEE 754. By default, armcc uses

--fpmode=std

, permitting the

deviations from the standard. However, if the command line parameters specify a mode option

requiring IEEE 754 compliance, for example

--fpmode=ieee_full

, most floating-point

operations cannot be vectorized.

Compiling NEON Instructions

ARM DEN0018A Copyright © 2013 ARM. All rights reserved. 2-9

ID071613 Non-Confidential

2.2 Generating NEON code using the vectorizing compiler

The vectorizing compiler evaluates vectorizable loops and potential NEON applications. If the

C or C++ code is written such that the compiler can determine the intent of the code, the

compiler optimizes it more efficiently. Although the compiler can generate some NEON code

without source modification, certain coding styles can promote more optimal output. Where the

vectorizer finds code with potential vectorizing opportunities but does not have enough

information, it can generate a remark to the user to prompt changes to the source code that can

provide more useful information. Although these modifications help the vectorizing compiler

they are all standard C notation and will allow re-compilation with any C99* compliant

compiler. C99 is required for parsing of the keyword

restrict

. In other compilation modes,

armcc also allows the use of the equivalent ARM-specific extension

__restrict

.

2.2.1 Compiler command line options

With the vectorizing licence option present, the compiler can be told to generate NEON code by

using the

O2

or

O3

,

Otime

,

vectorize

, and

cpu

options. The

cpu

option must specify a processor

that has NEON hardware.

SIMD code is sometimes bigger than the equivalent ARM code due to array cleanup and other

overheads.

To generate fast NEON code on a Cortex-A8 target, you should use the command line:

armcc --cpu=Cortex-A8 -O3 -Otime --vectorize ...

If you do not have a licence for the vectorizing compiler, this command will respond with an

error message.

Using the vectorizing compiler

We can now try using the vectorizing compiler on the addition example in Programming using

NEON intrinsics on page 4-14.

We can write the C code succinctly:

/* file.c */

unsigned int vector_add_of_n(unsigned int* ptr, unsigned int items)

{

unsigned int result=0;

unsigned int i;

for (i=0; i<(items*4); i+=1)

{

result+=ptr[i];

}

return result;

}

Note

• By using

(items*4)

we are telling the compiler that the size of the array is a multiple of

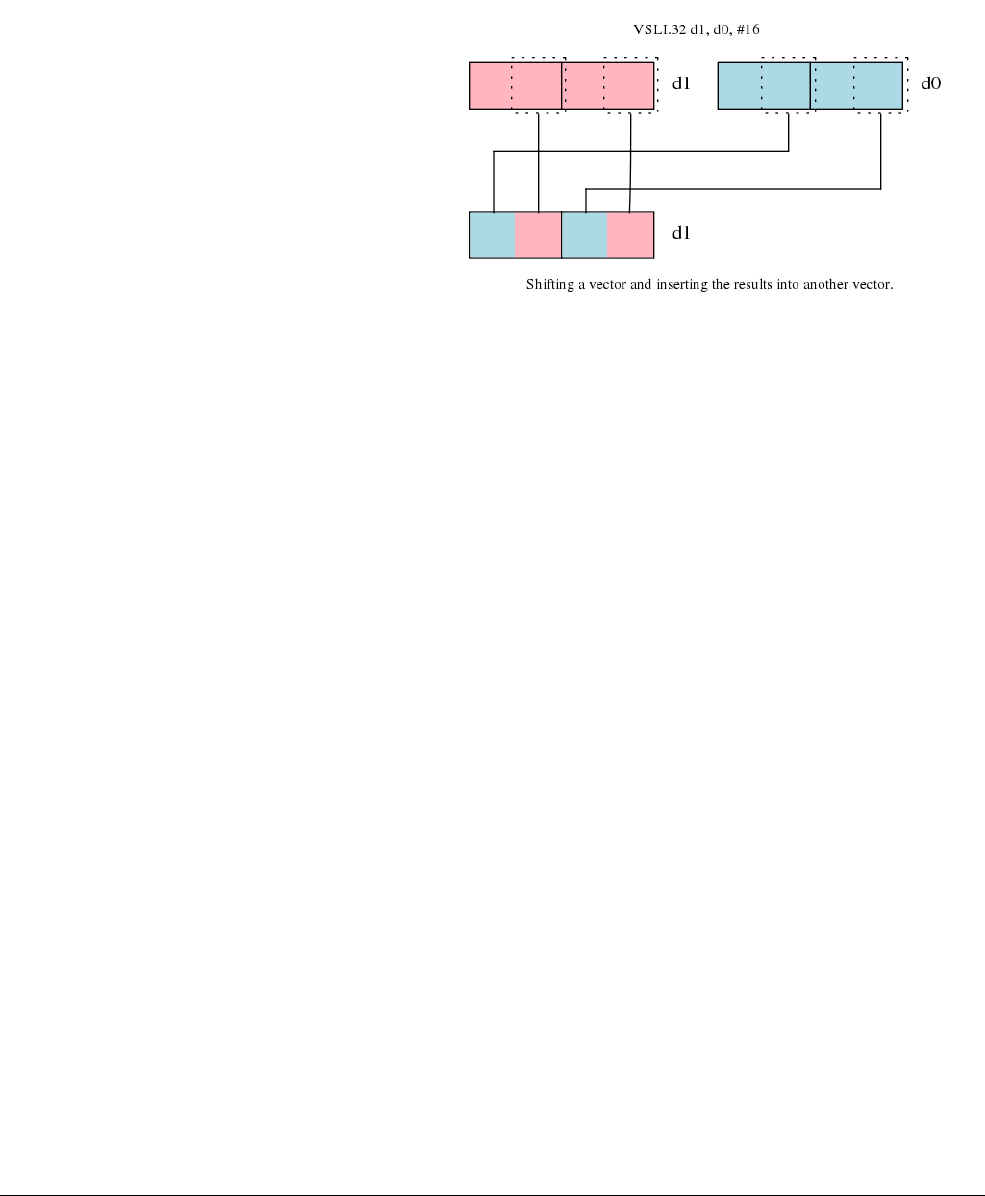

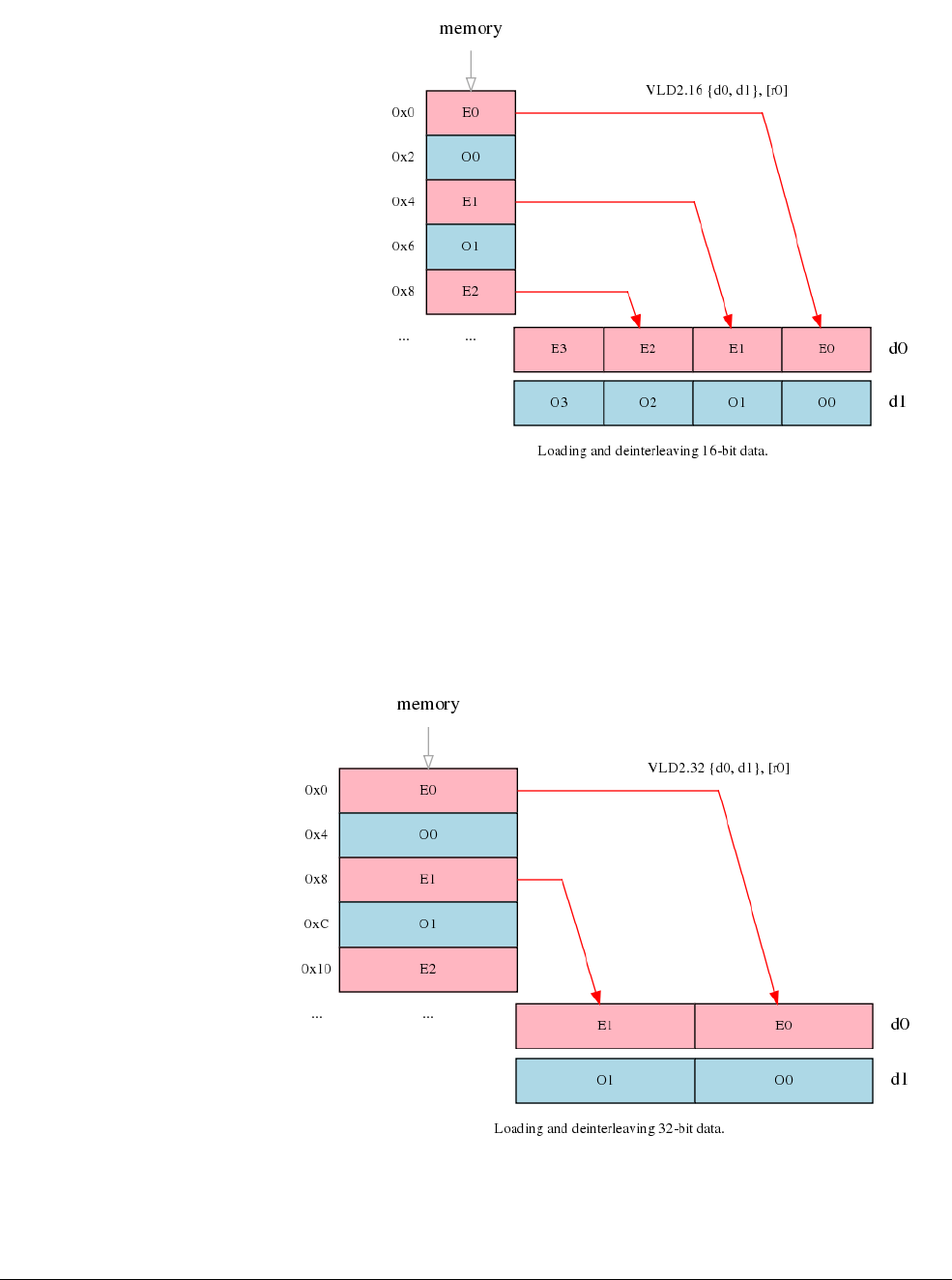

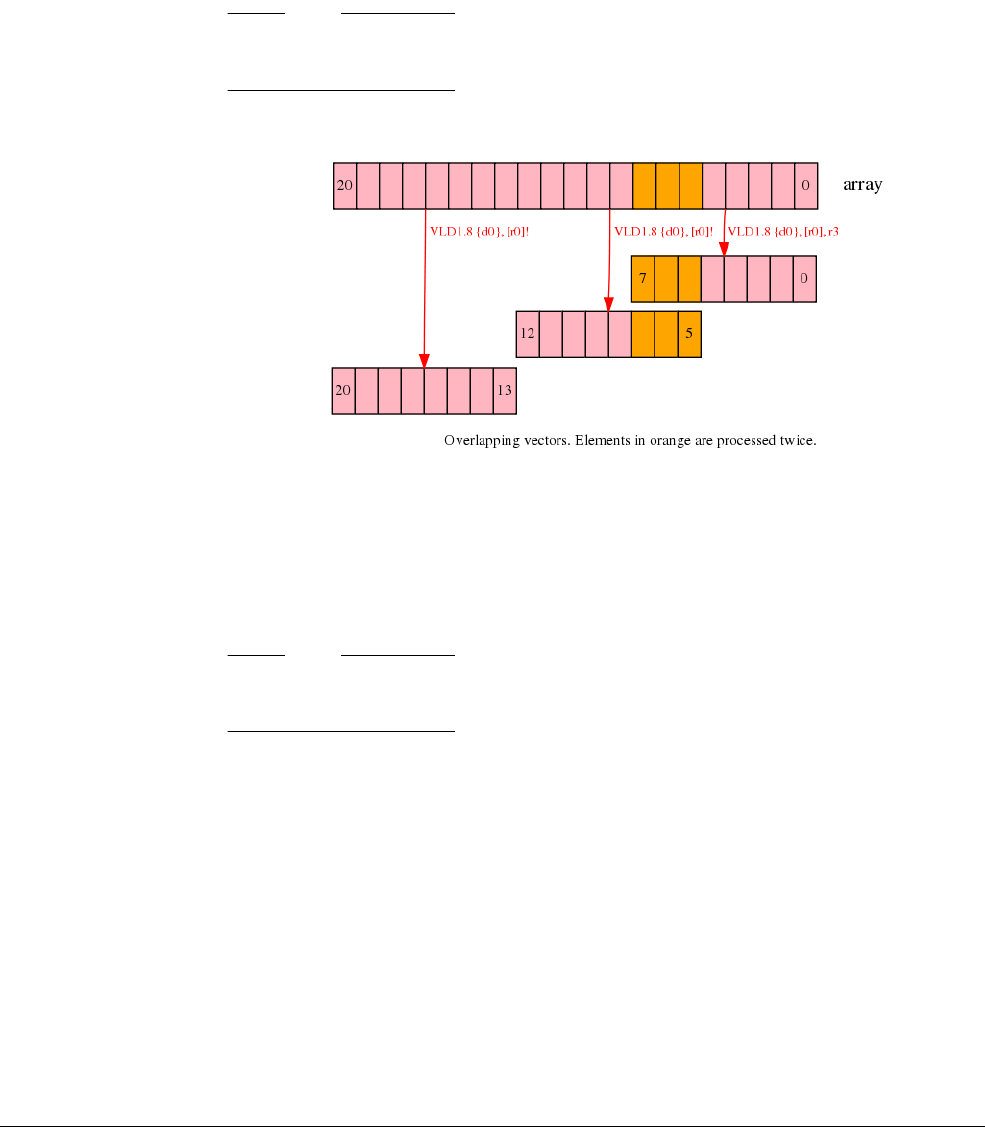

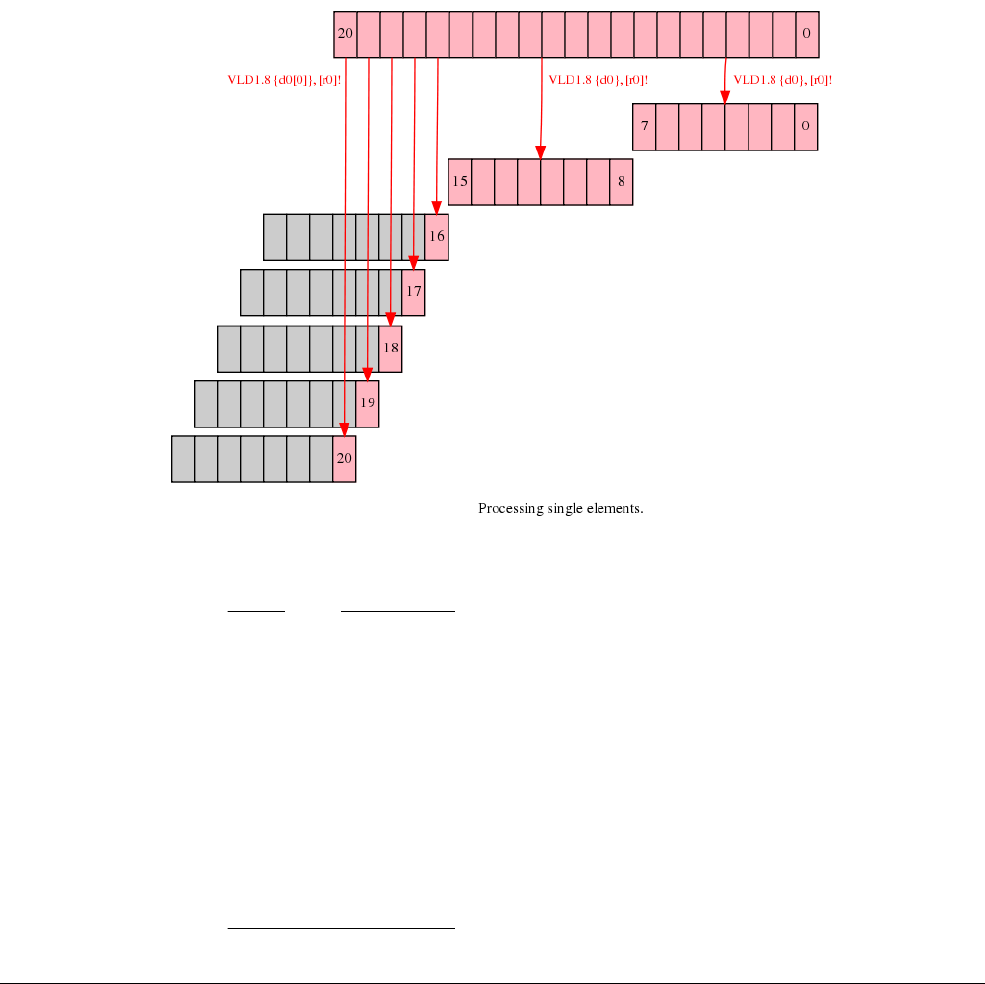

four. Although this is not required for the vectorizer to create NEON code, it provides the